Integrated

Circuit

Systems, Inc.

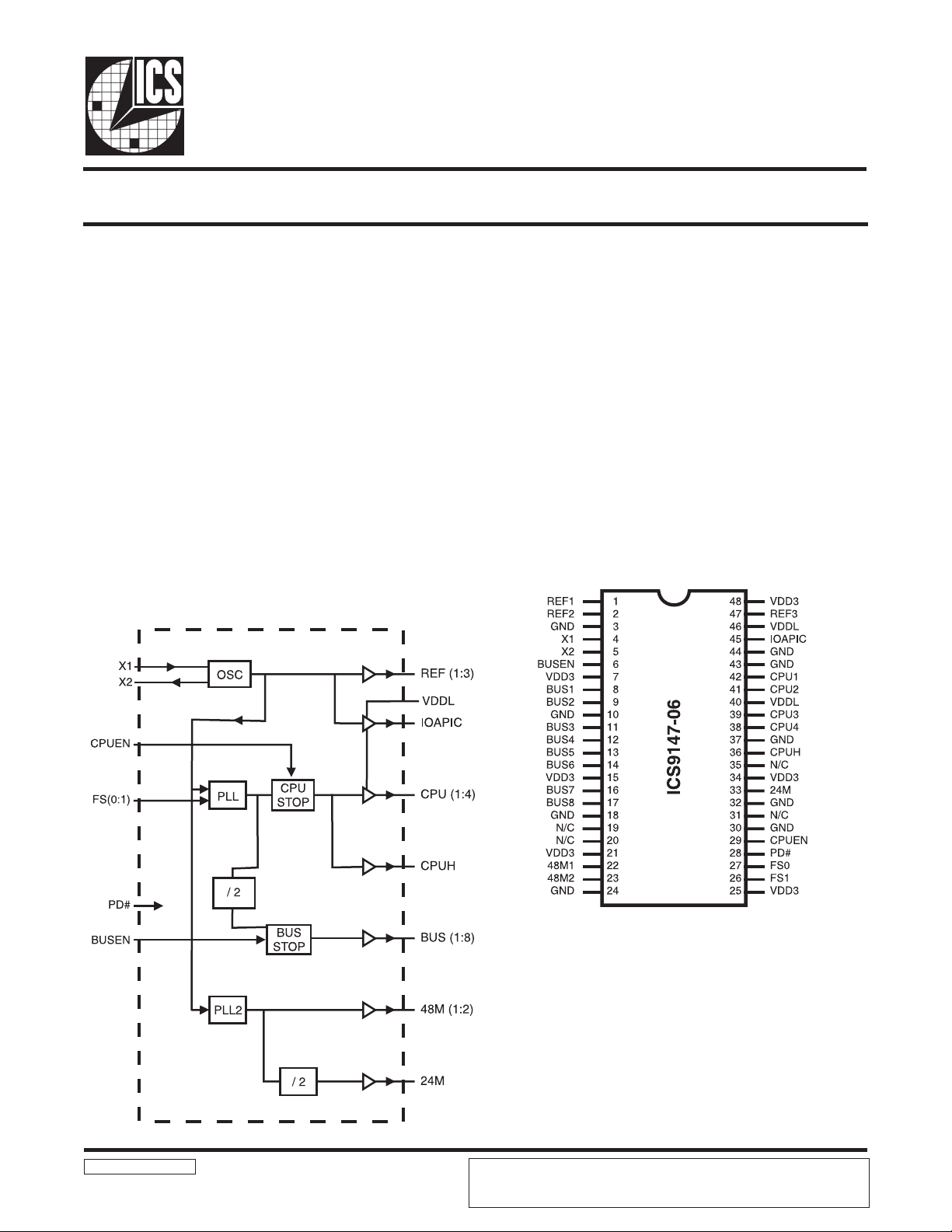

ICS9147-06

Frequency Generator & Integrated Buffers for PENTIUM

General Description Features

The ICS9147-06 generates all clocks required for high

speed RISC or CISC microprocessor systems such as Intel

PentiumPro. Two different reference frequency multiplying

factors are externally selectable with smooth frequency

transitions. Glitch-free Stop clock control is provided for

CPU and BUS clocks. Complete chip low current mode is

achieved with the Power Down# pin.

High drive BUS outputs typically provide greater than 1 V/

ns slew rate into 30pF loads. CPU outputs typically provide

better than 1V/ns slew rate into 20pF loads while

maintaining

outputs typically provide better than 0.5V/ns slew rates.

Separate buffer supply pins VDDL allow for nominal 3.3V

voltage or reduced voltage swing (from 2.9 to 2.5V) for

CPU (1:4) and IOAPIC outputs.

50±

5% duty cycle. The REF and IOAPIC clock

Block Diagram

Generates five processor, eight bus, four 14.31818 MHz,

two 48 MHz clocks for USB support and one 24 MHz

clock.

CPU to BUS clock skew 1 to 4ns (CPU early)

Synchronous clocks skew matched to 250ps window on

CPU and 500ps window on BUS.

Selectable multiplying ratios

Glitch free stop clock controls CPUEN and BUSEN

3.0V 3.7V supply range, 2.5V to VDD supply range for

CPU (1:4) clocks and IOAPIC clock.

48-pin SSOP package

Pin Configuration

TM

9147- 06 RevA 5/29/97P

48-Pin SSOP

Pentium is a trademark of Intel Corporation

ICS reserves the right to make changes in the device data identified in this publication

without further notice. ICS advises its customers to obtain the latest version of all

device data to verify that any information being relied upon by the customer is current

and accurate.

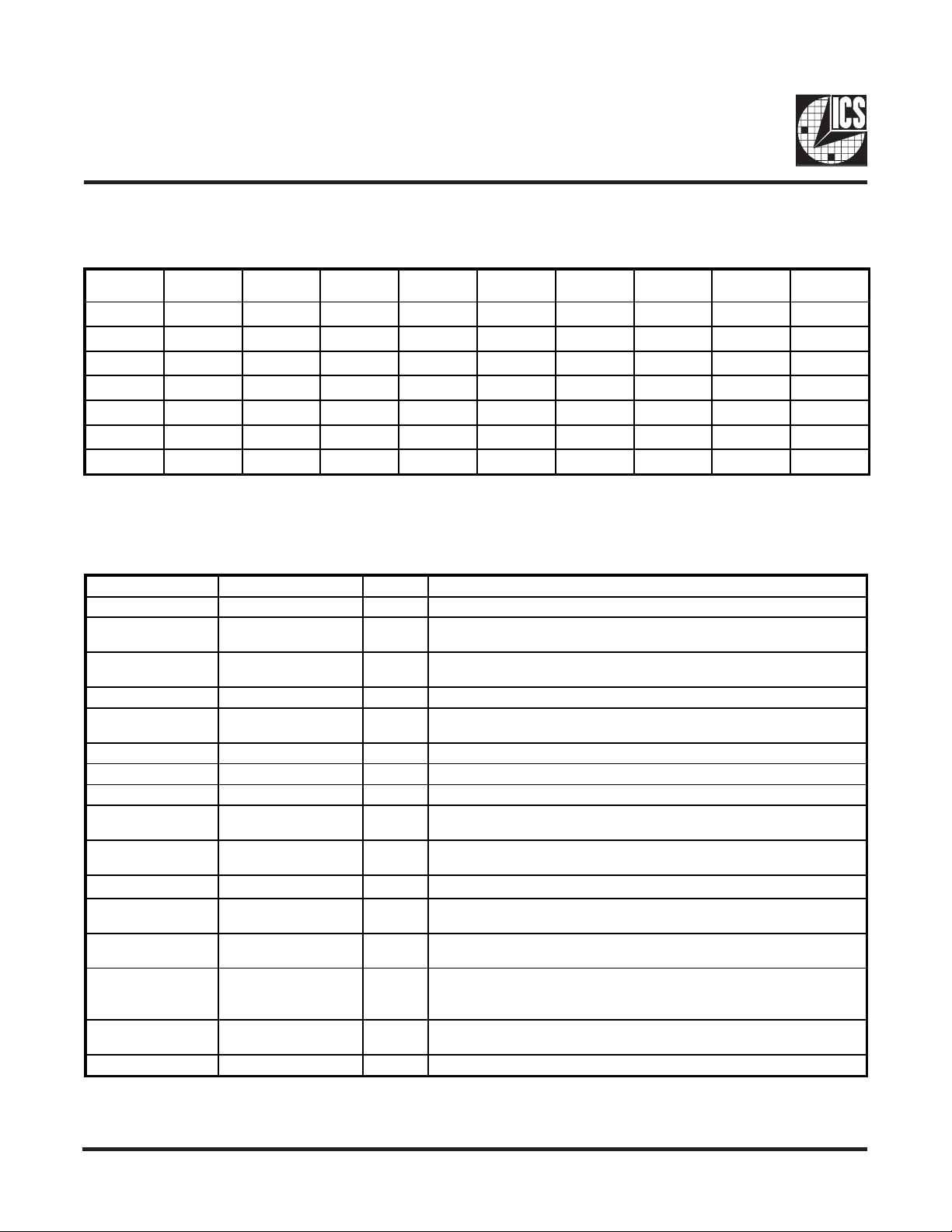

ICS9147-06

Functionality

PD# BUSEN CPUEN FS1 FS0

11100Tristate Tristate Tristate Tristate Tristate

11101603014.31818 24 48

1111066.633.314.31818 24 48

11111REF/2REF/4REFREF/4REF/2

1 1 0 X X LOW Running 14.31818 24 48

1 0 1 X X Running LOW 14.31818 24 48

0XXXXLOWLOWLOWLOWLOW

CPU (1:4)

CPUH

BUS

REF

IOAPIC

24

(MHz)

48

(MHz)

Pin Descriptions

PIN NUMBER PIN NAME TYPE DESCRIPTION

1, 2, 47 REF1, REF2, REF3 OUT 14.318 MHz reference clo ck out puts.

3, 10, 18, 24, 30, 32,

37, 43, 44

4X1 IN

5 X2 OUT Crystal out put, has inter nal crystal load capacitor

8, 9, 11, 12, 13, 14,

16, 17

26, 27 FS (0:1) IN Select pin for enablin g CPU a nd BUS clock f requenci es.*

7, 15, 21, 25, 34, 48 VDD3 PWR Core and Buf fer output clock power supply.

22, 23 48M (1:2) OUT 48 MHz clock output

28 PD# I N

29 CP U EN IN

36 CPUH OU T 3.3 (VDD3 dependent) CPU c lock output

38, 39, 41, 42 CPU (1:4) OUT

6BUSEN IN

45 IOAPIC OUT

40, 46 VDDL P WR

33 24M OUT 24 MHz clock output

GND PWR Ground.

Crystal input, has internal crystal load capacitor, and feedback resistor

from X2. Nominally 14.31818MHz.

BUS (1:8) OUT BUS clock out puts, ope rates synchronously at CP U/2.

Device power down input, stops outputs low and shuts off crystal

oscillator and PLLs when low.*

Output enable for all CPU cloc ks, a l ogic low will Stop low all CPU

clocks.*

CPU clock out put c locks, ope rates at VDDL s upply voltage (with

IOAPIC), e ither nominal 3.3V VDD or reduced voltage 2.9 t o 2.5V.

Output enable for all BUS clock, a logic low will stop Low all Bus

clocks.*

IOAPIC clock output. ( 14.318 MHz), operates at VDDL supply voltage

with CPU (1: 4), eithe r nomin al 3.3V VDD o r reduced vo ltage

2.9 to 2.5V.

Power supply for CPU and IOAPIC block buffers, operates at nominal

3.3V VDD or reduced volt age 2.9 to 2.5V.

* Has internal pull-up to V

DD3

.

2

Loading...

Loading...