Integrated

Circuit

ICS9147-03

Systems, Inc.

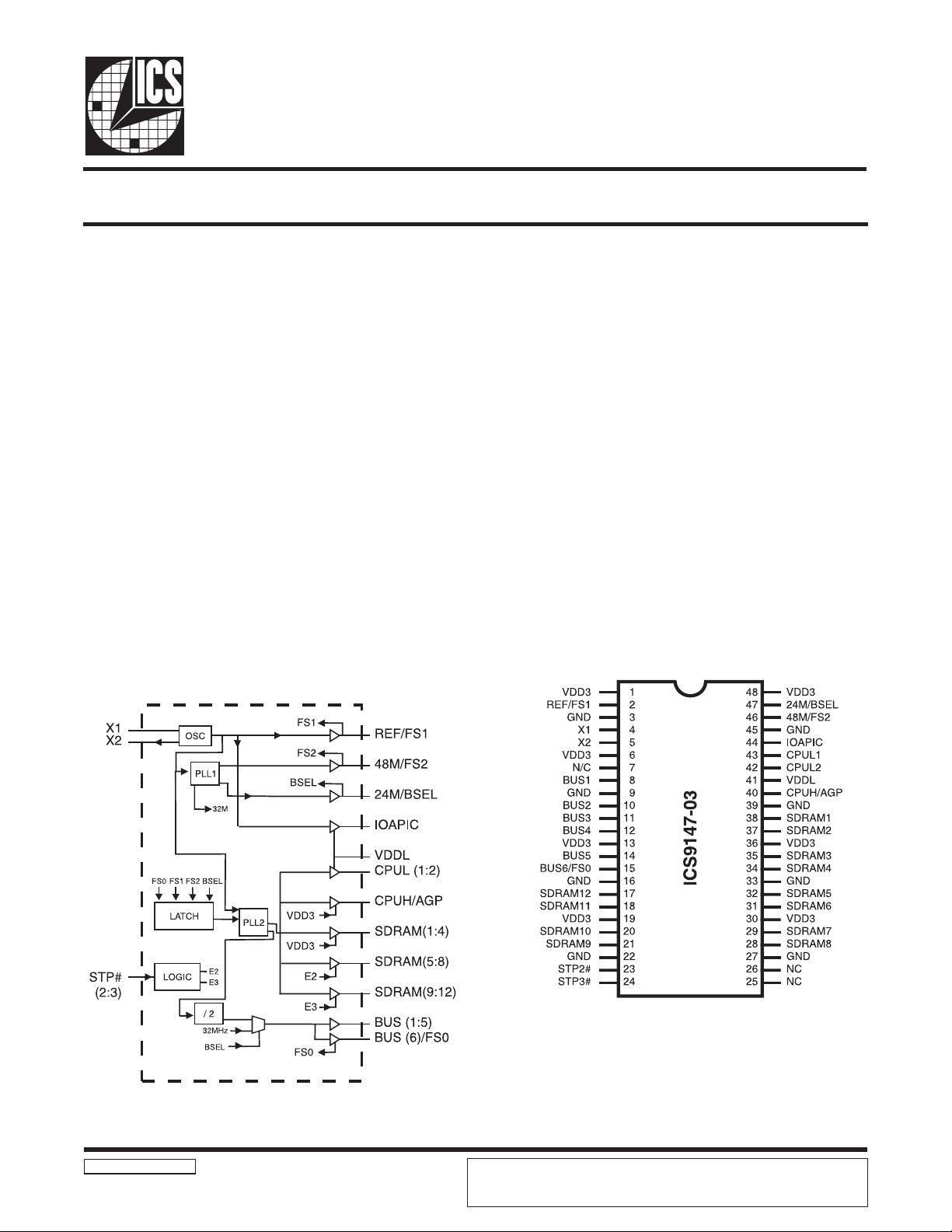

Frequency Generator & Integrated Buffers for 686 Series CPUs

General Description Features

The ICS9147-03 generates all clocks required for high

speed RISC or CISC microprocessor systems such as Intel

PentiumPro, AMD or Cyrix processors. Four bidirectional I/O

pins (FS0, FS1, FS2, BSEL) are latched at power-on to the

functionality table. The Six BUS clocks can be selected as

either synchronous at 1/2 CPU speed or asynchronous at

32MHz selected by BSEL latched input.The inputs provide

for tristate and test mode conditions to aid in system level

testing.These multiplying factors can be customized for

specific applications. Glitch-free stop clock controls

provided for SDRAM(5:8) and SDRAM (9:12) banks

(STP2#, STP3#).

High drive BUS and SDRAM outputs typically provide

greater than 1 V/ns slew rate into 30 pF loads. CPU outputs

typically provide better than 1V/ns slew rate into 20pF

loads while maintaining 50±5% duty cycle. The REF clock

outputs typically provide better than 0.5V/ns slew rates.

Seperate buffer supply pin VDDL allows for nominal 3.3V

voltage or reduced voltage swing (from 2.9 to 2.5V) for

CPUL (1:2) and IOAPIC outputs.

• Total of 15 CPU speed clocks:

- Two copies of CPU clock with VDDL (2.5 to 3.3V)

- Twelve (12) SDRAM (3.3v) plus one

CPUH/AGP (3.3V) clocks

• Six copies of BUS clocks (synchronous with CPU clock/2

or asynchronous 32 MHz)

• 250ps output skew window for CPU andSDRAM clocks

and 500ps window BUS clocks. CPU clocks to BUS clocks

skew 1-4ns (CPU early)

• Two copies of Ref. clock @14.31818 MHz (One driven by

VDDL as IOAPIC)

• One 48 MHz (3.3 V TTL) for USB support and single 24

MHz.

• Separate VDDL for CPUL (1:2) clock buffers and IOAPIC to

allow 2.5V output (or Std. Vdd)

• 3.0V – 3.7V supply range w/2.5V compatible outputs

• 48-pin SSOP package

Block Diagram

Pin Configuration

48-Pin SSOP

9147-03 Rev A 04/25/01

Pentium is a trademark of Intel Corporation

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

ICS9147-03

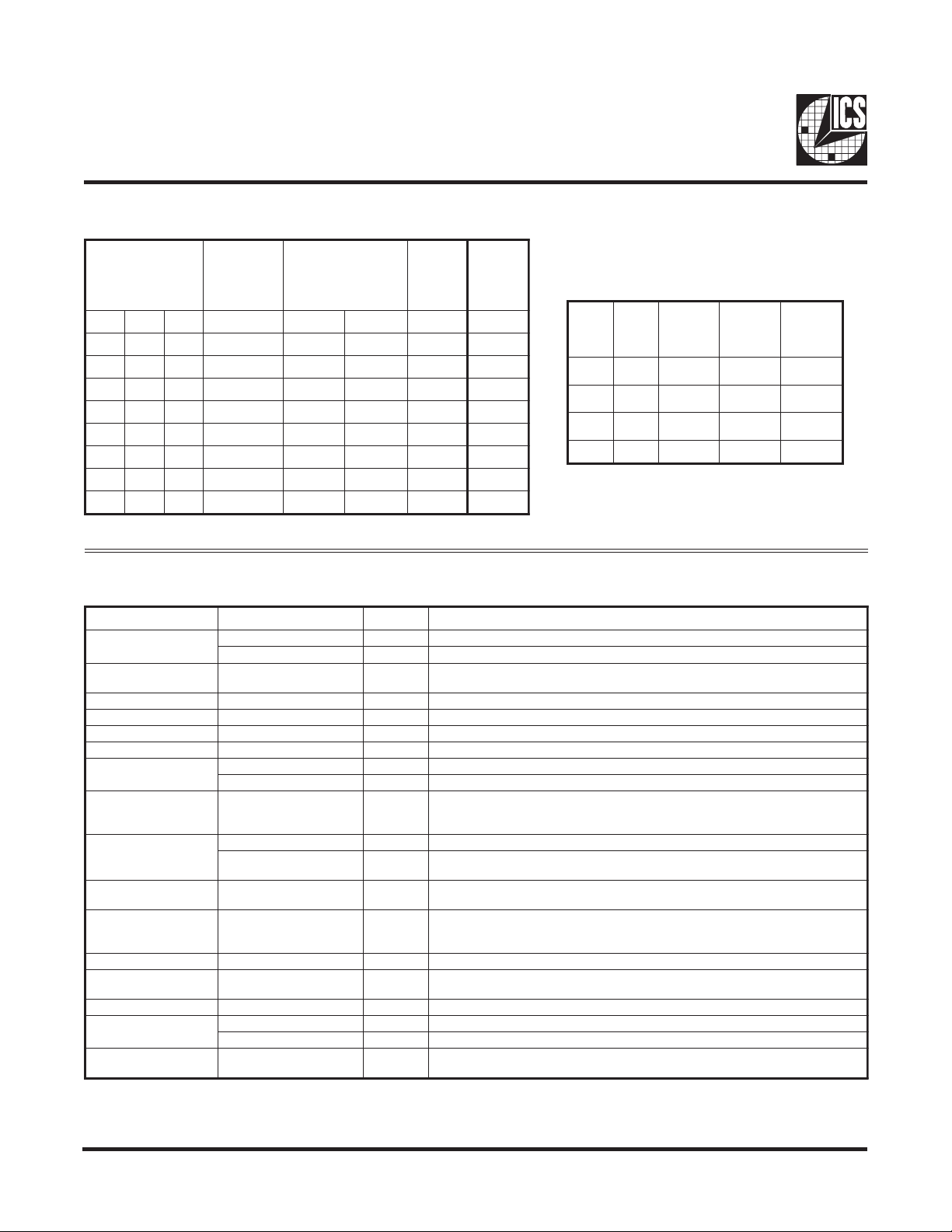

Functionality with (14.31818 MHz input)

)2:1(LUPC

tceleSsserddA

HUPC

MARDS

)6:1(SUB

)zHM(

)21:1(

2SF 1SF 0SF )zHM( 1=LESB 0=LESB )zHM( )zHM(

000 0603234284

001 8.664.33234284

010 0552234284

011 555.72234284

100 575.73234284

10 1 5.863.43234284

110 **2/tseT**4/tseT**3/tseT**4/tseT**2/tseT

111 etatsirTetatsirTetatsirTetatsirTetatsirT

**Test: is the frequency applied to the X1 input. Can be crystal or tester generated clock

overriding crystal at X1 pin.

M42

M84

)zHM(

)zHM(

SDRAM Clock Enable

MMID

#2PTS #3PTS

1KNAB

MARDS

)4:1(

00 NO

01 NO

10 NONO

MMID

2KNAB

MARDS

)8:5(

deppotS

woL

deppotS

woL

MMID

3KNAB

MARDS

)21:9(

deppotS

woL

NO

deppotS

woL

11 NONONO

Pin Descriptions

REBMUNNIP EMANNIP EPYT NOITPIRCSED

2

,22,61,9,3

54,93,33,72

41XNIpacdaollanretnisaH.zHM813.41yllanimoN.tupnilatsyrC

52XTUO1XotrotsiserkcadeefdnapacdaollanretnisaH.tuptuolatsyrC

14LDDVRWP.sreffubtuptuoCIPAOIdnaLUPCrofrewopreffubV3.3ro5.2

51

42,32)3:2(#PTSNI

74

,91,31,6,1

84,63,03

,43,23,13,92

83,73,53

04PGA/HUPCTUO.ctePGArof,)monV3.3(levelDDVMARDStasetarepokcolcUPC

34,24)2:1(LUPCTUO

62,52,7C/N— .detcennocyllanretnitonsniP

64

44CIPAOITUO

FERTUO*tuptuokcolcecnerefeR

1SFNI.norewoPtadehctaltupnI.*1tiBtcelesycneuqerftupnicigoL

DNGRWP.dnuorG

,41,21,11,01,8)5:1(SUBTUOycneuqerfrofelbattcelesees.stuptuokcolcSUB

0SFNI.norewoPtadehctaltupnI.*.0tiBtcelesycneuqerftupnicigoL

M42TUO*.kcolcdexifzHM42

,82,12,02,81,71

M84TUO.*tuptuokcolcdexifzHM84

2SFNI.norewoPtadehctaltupnI.*2tiBtcelesycneuqerftupnicigoL

6SUBTUO*.ycneuqerfrofelbattceleseeS.tuptuokcolcSUB

LESBNI

3DDVRWPrewopreffubdnacigoleroctlov3.3

)21:1(MARDSTUO.ycneuqerfrofelbattceleseeS.deepsUPCtaskcolcMARDS

eraskcolC,evobaelbateesskcolcMARDSrofsnoituloselbaneknaB

MMIDspots#3PTS,2knabMMIDspots#2PTS(.4fospuorgnidelbane

.)wolnehw3knab

-ycneuqerfSUBsuonorhcnysarosuonorhcnysgnitcelesrof*tupnicigoL

*.norewoPtadehctaltupnI.evobaelbatees

tasetarepO.ycneuqerfrofelbattceleseeS.skcolctuptuokcolcUPC

.nipLDDVybdellortnocV5.2otnwod

,LDDVybderewop)zHM813.41(kcolcecnerefeR

.V3.3ot5.2gnitarepo

* Bidirectional input/output pins, input logic level determined at internal power-on-reset are latched. Use 10Kohm resistor to

program logic Hi to VDD or GND for logic low.

2

ICS9147-03

Absolute Maximum Ratings

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . 7.0 V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND –0.5 V to VDD +0.5 V

Ambient Operating Temperature . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are

stress specifications only and functional operation of the device at these or any other conditions above those listed in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect product reliability.

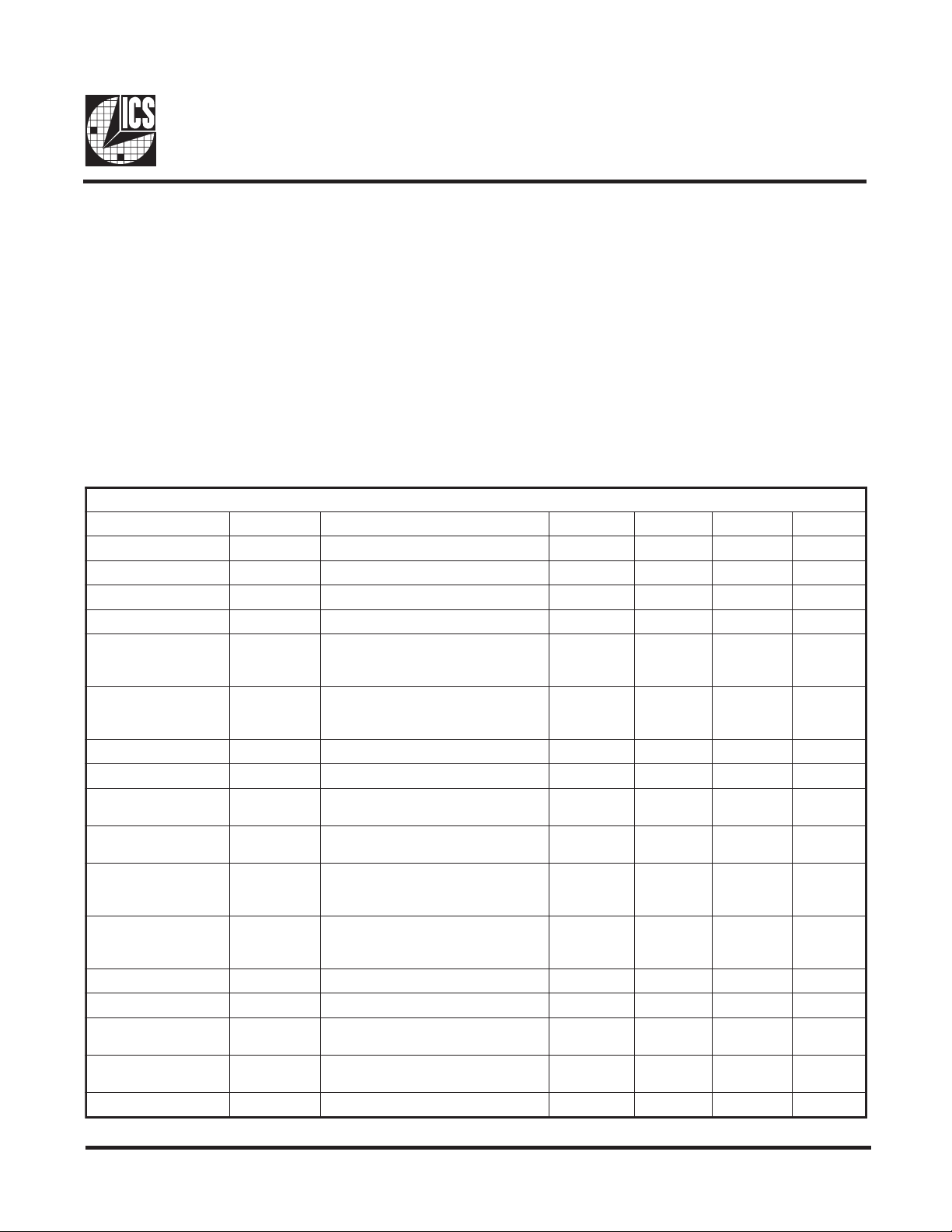

Electrical Characteristics at 3.3V

VDD = 3.0 – 3.7 V, TA = 0 – 70°C unless otherwise stated

scitsiretcarahCCD

RETEMARAPLOBMYSSNOITIDNOCTSETNIMPYTXAMSTINU

egatloVwoLtupnI

egatloVhgiHtupnI

tnerruCwoLtupnI

tnerruChgiHtupnI

tnerruCwoLtuptuO

tnerruChgiHtuptuO

tnerruCwoLtuptuO

tnerruChgiHtuptuO

tnerruCwoLtuptuO

tnerruChgiHtuptuO

egatloVwoLtuptuOV

egatloVhgiHtuptuOV

egatloVwoLtuptuO

egatloVhgiHtuptuO

egatloVwoLtuptuO

egatloVhgiHtuptuO

tnerruCylppuS

V

LI

V

HI

I

LI

I

HI

I

1LO

I

1HO

I

2LO

I

2HO

I

3LO

I

3HO

1LO

1HO

V

2LO

V

2HO

V

3LO

V

3HO

I

DD

V5.2=LDDV

V5.2=LDDV

V5.2=LDDV

;Am8-=HOItaLUPCrof

V5.2=LDDV

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

stupnidehctaldna#PTS--DDV2.0V

stupnidehctaldna#PTSV7.0

DD

--V

)stupni#PTS(V0=NIV0.82-5.01--A

)stupni#PTS(DDV=NIV0.5--0.5A

,CIPAOIrof;V8.0=LOV

FER&SUB,MARDS,HUPC

910.03-Am

)V7.3ot0.3=LDDVtaLUPCdna(

,CIPAOIrof;V0.2=HOV

FER&SUB,MARDS,HUPC

-0.62-61-Am

)V7.3ot0.3=LDDVtaLUPCdna(

sKLC84,42dexifrof;V8.0=LOV610.52-Am

sKLC84,42dexifrof;V0.2=HOV-0.22-41-Am

taLUPCrof;V8.0=LOV

taLUPCrof;V7.1=HOV

910.03-Am

-5.21-5.9-Am

,CIPAOIrofAm01-;Am01=LOI

FER&SUB,MARDS,HUPC

-22.04.0V

)V7.3ot0.3=LDDVtaLUPCdna(

;Am01-=HOI

FER&SUB,MARDS,HUPCrof

4.28.2-V

)V7.3ot0.3=LDDVtaLUPCdna(

sKLCdexifrof;Am8=LOI-52.04.0V

sKLCdexifrof;Am8-=HOI4.26.2-V

taLUPCrof;Am8=LOI

-52.04.0V

59.11.2-V

dedaolnustuptuolla;zHM6.66@-09081Am

3

Loading...

Loading...