Integrated

Circuit

Systems, Inc.

ICS9147-01

Frequency Generator & Integrated Buffers for PENTIUM

General Description Features

The ICS9147-01 generates all clocks required for high

speed RISC or CISC microprocessor systems such as Intel

PentiumPro. Two bidirectional I/O pins (FS1,FS2) are latched

at power-on to the functionality table, with FS0 selectable

in real-time to toggle between conditions. The inputs

provide for tristate and test mode conditions to aid in

system level testing. These multiplying factors can be

customized for specific applications. Glitch-free stop

clockcontrols are provided for CPU clocks and BUS clocks.

High drive BUS and SDRAM outputs typically provide

greater than 1 V/ns slew rate into 30pF loads. CPU outputs

typically provide better than 1V/ns slew rate into 20pF

loads while maintaining

outputs typically provide better than 0.5V/ns slew rates.

Seperate buffers supply pins VDD2 allow for 3.3V or

reduced voltage swing (from 2.9 to 2.5V) for CPU (1:4) and

IOAPIC outputs.

50 ±

5% duty cycle. The REF clock

• Four copies of CPU clock

• Six SDRAM (3.3 V TTL), usable as AGP clocks

• Seven copies of BUS clock (synchronous with CPU

clock/2 or CPU/2.5 for 75 and 83.3 MHz CPU)

• CPU clocks to BUS clocks skew 1-4ns (CPU early)

• One IOAPIC clock @14.31818 MHz

• Two copies of Ref. clock @14.31818 MHz

• One each 48/24 MHz (3.3 V TTL)

• This device is configured into the Mobile mode for

power management of Intel 430 TX

• Ref. 14.31818 MHz Xtal oscillator input

• Separate 66/60 MHz select pin (LSB of select pins)

• Separate V

buffers to allow 2.5V output (or Std. Vdd)

• Power Management Control Input pins

• 3.0V – 3.7V supply range w/2.5V compatible outputs

• 48-pin SSOP package

for four CPU and single IOAPIC output

DD2

TM

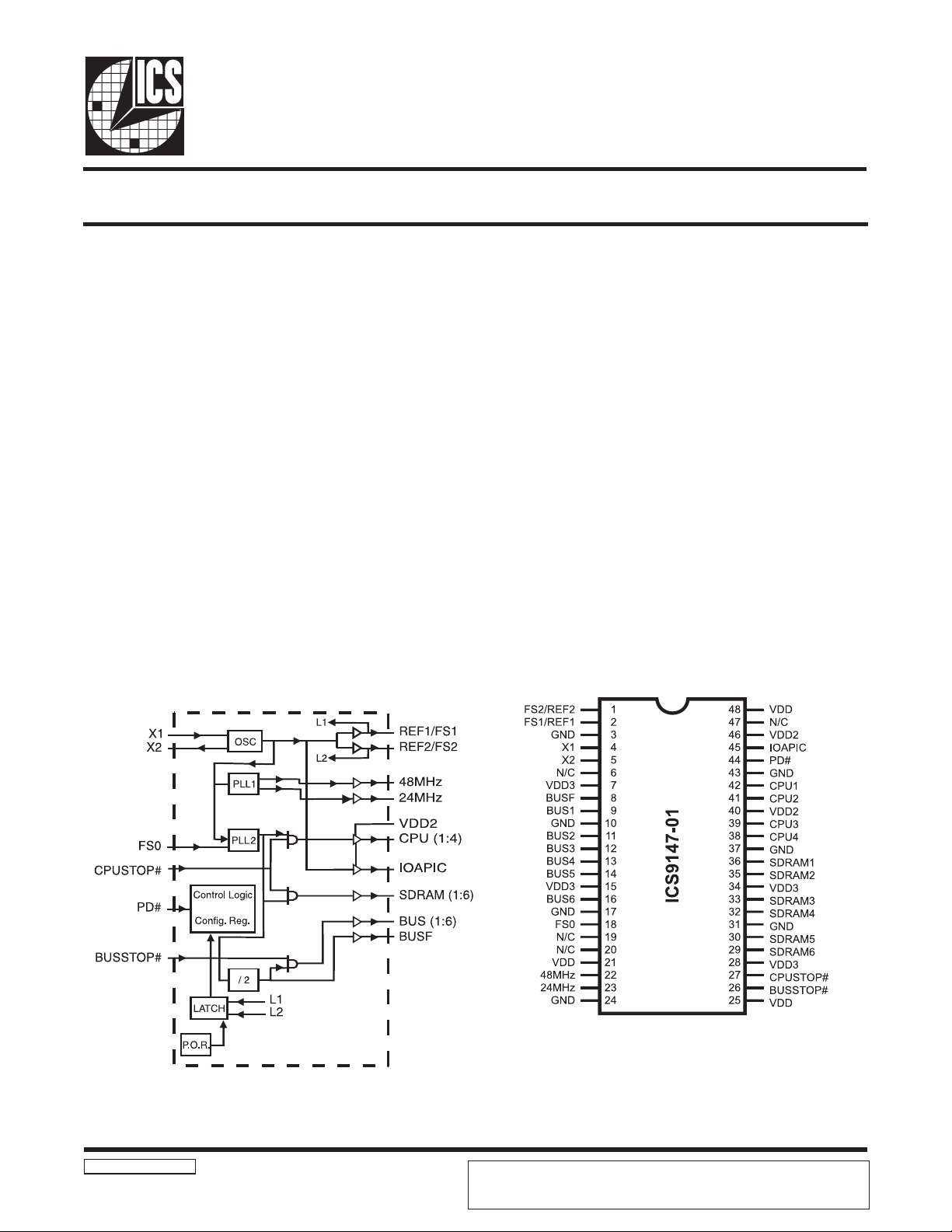

Block Diagram

Pin Configuration

48-Pin SSOP

9147-01Rev B 04/25/01

Pentium is a trademark of Intel Corporation

ICS reserves the right to make changes in the device data identified in this publication

without further notice. ICS advises its customers to obtain the latest version of all

device data to verify that any information being relied upon by the customer is current

and accurate.

ICS9147-01

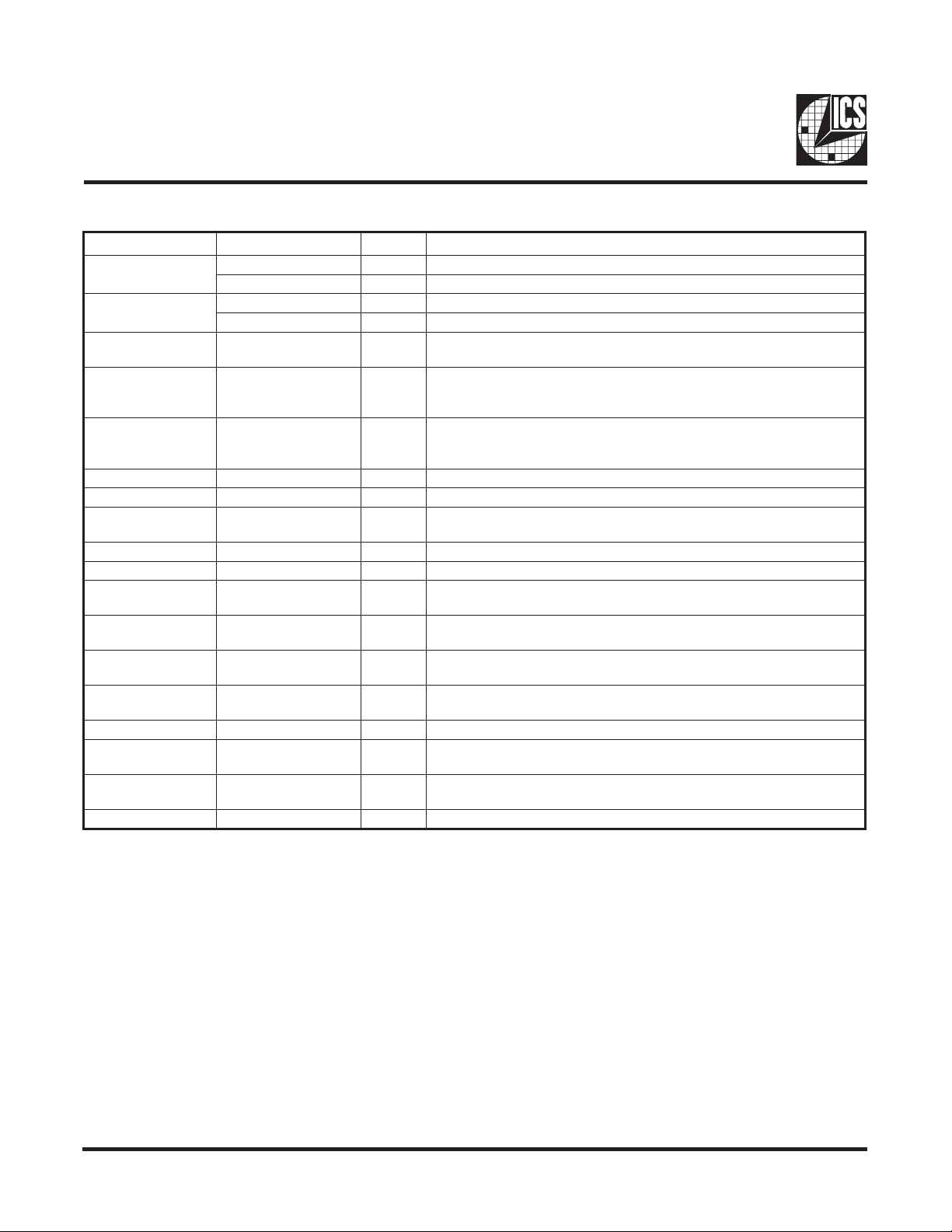

Pin Descriptions

REBMUNNIP EMANNIP EPYT NOITPIRCSED

1

2

,13,42,71,01,3

34,73

41XNI

52XTUO

43,82,51,73DDVRWP.ylppusreffubMARDSdnaSUB,ylppusrewopO/IV3.3

61,41,31,21,11,9,8)6:1(SUB,FSUBTUOycneuqerfrofelbattcelesees.stuptuokcolcSUB

81OSFNI

84,52,12DDVRWP.rewopkcolcdexifdna,ylppusrewoperoC

32,22zHM42,84TUOstuptuokcolczHM42,84

62#POTSSUBNI

72#POTSUPCNI

,03,23,33,53,63

92

64,042DDVRWP

83,93,24,14)4:1(UPCTUOycneuqerfrofelbattceleseeS.skcolctuptuokcolcUPC

44#DPNI

54CIPAOITUO

74,02,91,6C/N— .detcennocyllanretnitonsniP

2FERTUO*tuptuokcolcecnerefeR

2SFNI*2tiBtcelesycneuqerftupnicigoL

1FERTUO*tuptuokcolcecnerefeR

1SFNI*1tiBtcelesycneuqerftupnicigoL

DNGRWP.dnuorG

)6:1(MARDSTUO

lanretxE.pacdaollanretnisaH.zHM813.41yllanimoN.tupnilatsyrC

retsafnorewopDDVrofdednemmocerDNGotFp03fodaollatsyrc

.sm0.2naht

.1XotrotsiserkcabdeefdnapacdaollanretnisaH.tuptuolatsyrC

rewopDDVrofdednemmocerDNGotFp01fodaollatsyrclanretxE

.sm0.2nahtretsafno

nisnoitcelesrehtoro,zHM06rozHM6.66gnilbanerofniptceleS

.elbattcelesycneuqerf

sinipnehwskcolc)6:1(SUBllapotsylsuonorhcnysotniptupnI

.wol

nehwskcolcMARDSdnaUPCllapotsylsuonorhcnysotniptupnI

.wolsinip

.ycneuqerfrofelbattceleseeS.deepsUPCtaskcolcMARDS

.3DDVybderewoP

otdeitebnac,sreffubCIPAOIdnaUPCrofylppuSrewoPV5.2

noitarepoV3.3rof3DDV

LLPhtobffosrewop,wolnehW.tupnilortnoccigolnwodrewoP

.wolcigolotdecrofstuptuolladna

derewoP)latsyrclanimonhtiw813.41=qerF(tuptuokcolcCIPAOI

ylppus2DDVyb

* Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor to program logic

Hi to VDD or GND for logic low.

2

ICS9147-01

1(UPC

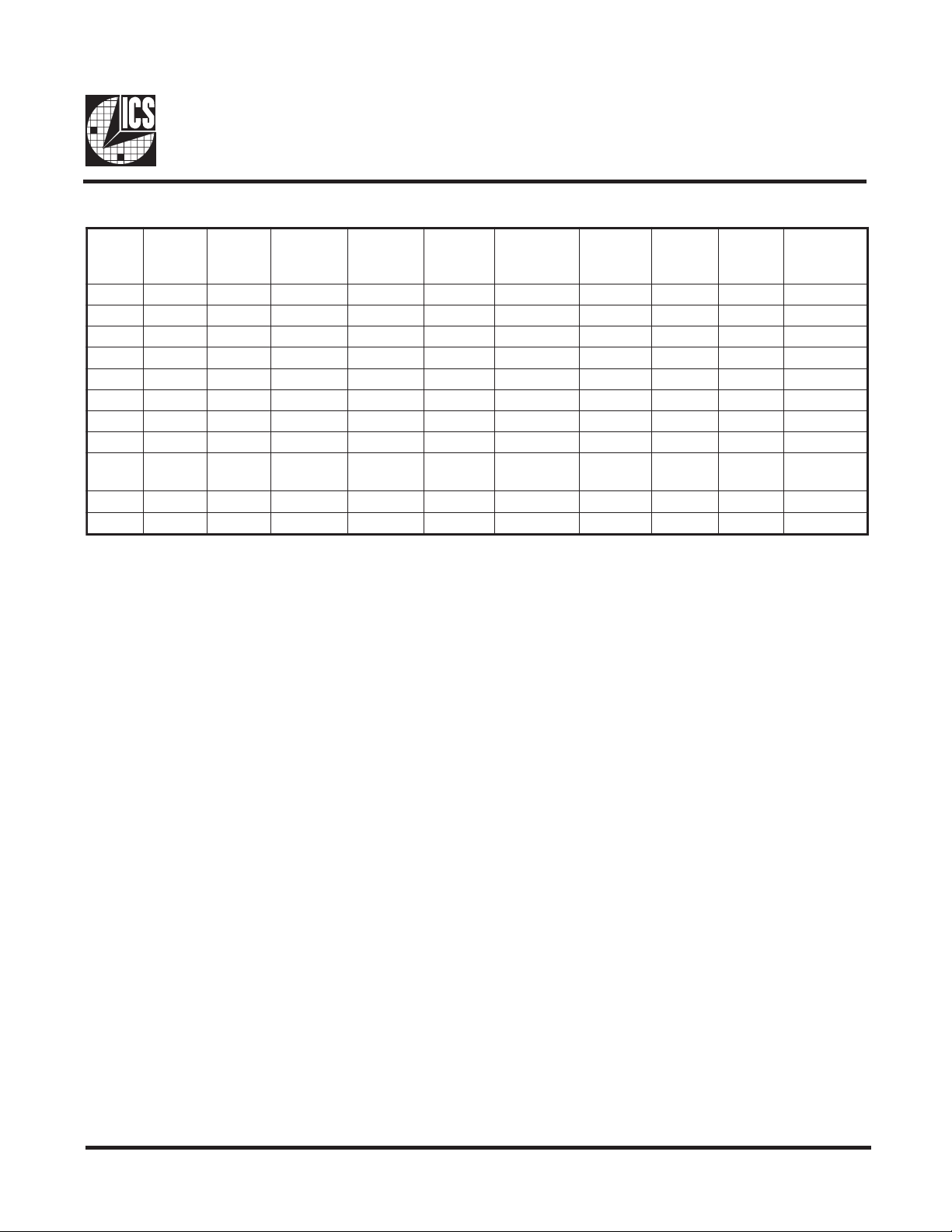

Functionality

,)4:

#DP

11 1 0 0 0 06038442813.41

11 1 0 0 1 6.663.338442813.41

11 1 0 1 0 05528442813.41

11 1 0 1 1 555.728442813.41

11 1 1 0 0 5703

11 1 1 0 1 3.383.33

11 1 1 1 0 2/FER4/FER2/FER4/FERFER

11 1 1 1 1 etatsirTetatsirTetatsirTetatsirTetatsirT

01 1 X X X

10 1 X X X WOLgninnurgninnurgninnurgninnur

11 0 X X X gninnurWOLgninnurgninnurgninnur

Note a: These frequency selections are at CPU/2.5 (internal VCO/5), not synchronous CPU/2

-UPC

#POTS

-SUB

#POTS

*2SF

)2FERta(

*1SF

)1FERta(

0SF

)81nip(

MRDS

)6:1(

)zHM(

WOL

ffoLLP

)6:1(SUB

FSUB

)zHM(

a

a

WOL

zHM84

)zHM(

8442813.41

8442813.41

WOL

ffoLLP

zHM42

)zHM(

WOL

,)2:1(FER

CIPAOI

)zHM(

WOL

ffOcsO

3

ICS9147-01

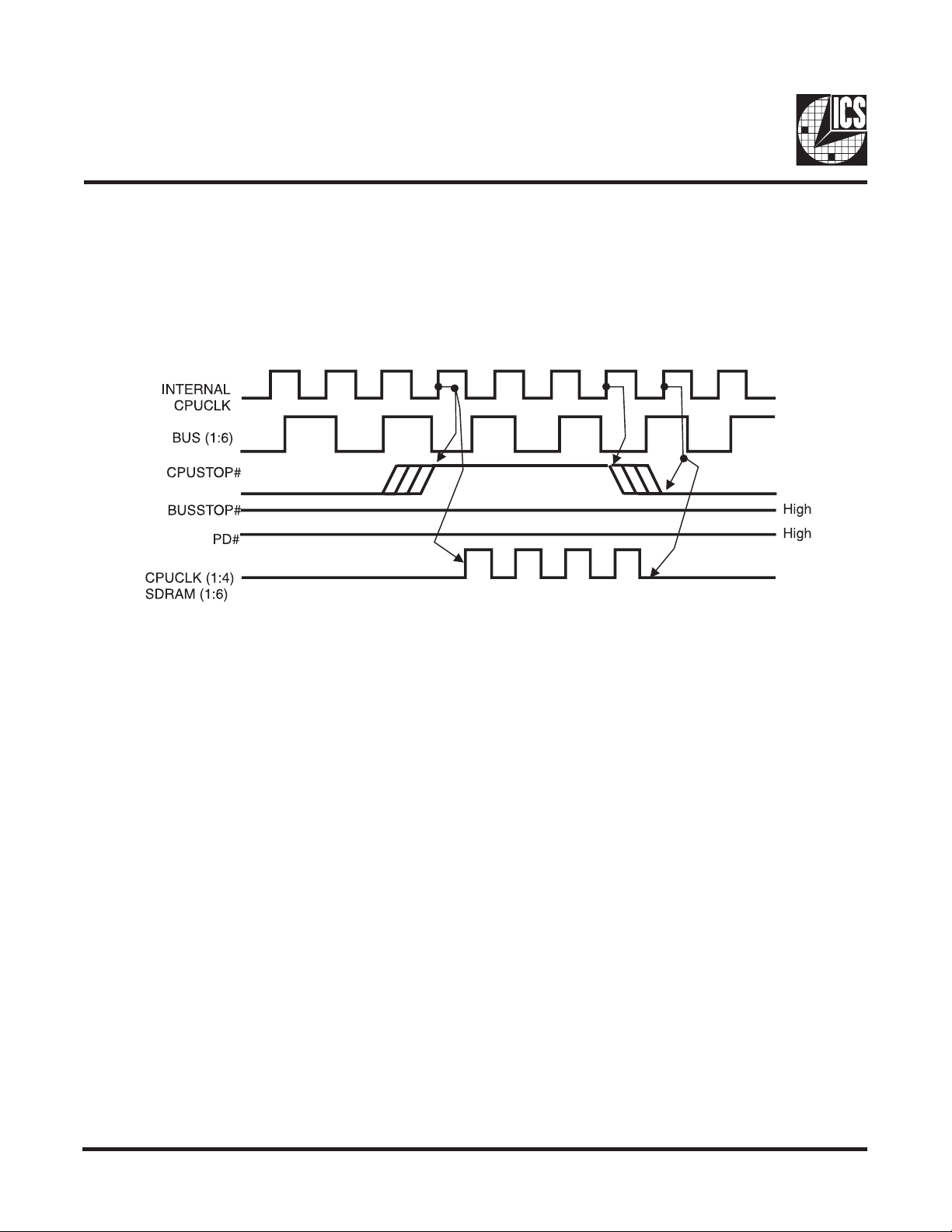

CPUSTOP# Timing Diagram

CPUSTOP# is an asychronous input to the clock synthesizer. It is used to turn off the CPU clocks for low power operation.

CPUSTOP# is synchronized by the ICS9147-01. All other clocks will continue to run while the CPU and SDRAM clocks

are disabled. The CPU and SDRAM clocks will always be stopped in a low state and start in such a manner that guarantees

the high pulse width is a full pulse. CPU clock on latency is 0 to 1 CPU clocks and CPU clock off latency is 0 to 1 CPU

clocks.

Notes:

1. All timing is referenced to the internal CPU clock.

2. CPUSTOP# is an asynchronous input and metastable conditions

may exist. This signal is synchronized to the CPU and SDRAM

clocks inside the ICS9147-01.

3. All other clocks continue to run undisturbed.

4. PD# and BUSSTOP# are shown in a high (true) state.

BUSSTOP# Timing Diagram

BUSSTOP# is an asynchronous input to the ICS9147-01. It is used to turn off the BUS (1:6) clocks for low power operation.

BUSSTOP# is synchronized by the ICS9147-01 internally. BUS (1:6) clocks are stopped in a low state and started with

a full high pulse width guaranteed. BUS (1:6) clock on latency cycles are less than 4 CPU clocks and BUS (1:6) clock off

latency is less than 4 clocks.

(Drawing shown on next page.)

4

Loading...

Loading...