Integrated

Circuit

Systems, Inc.

Modem and Audio Clock Generator

ICS9120-46

General Description

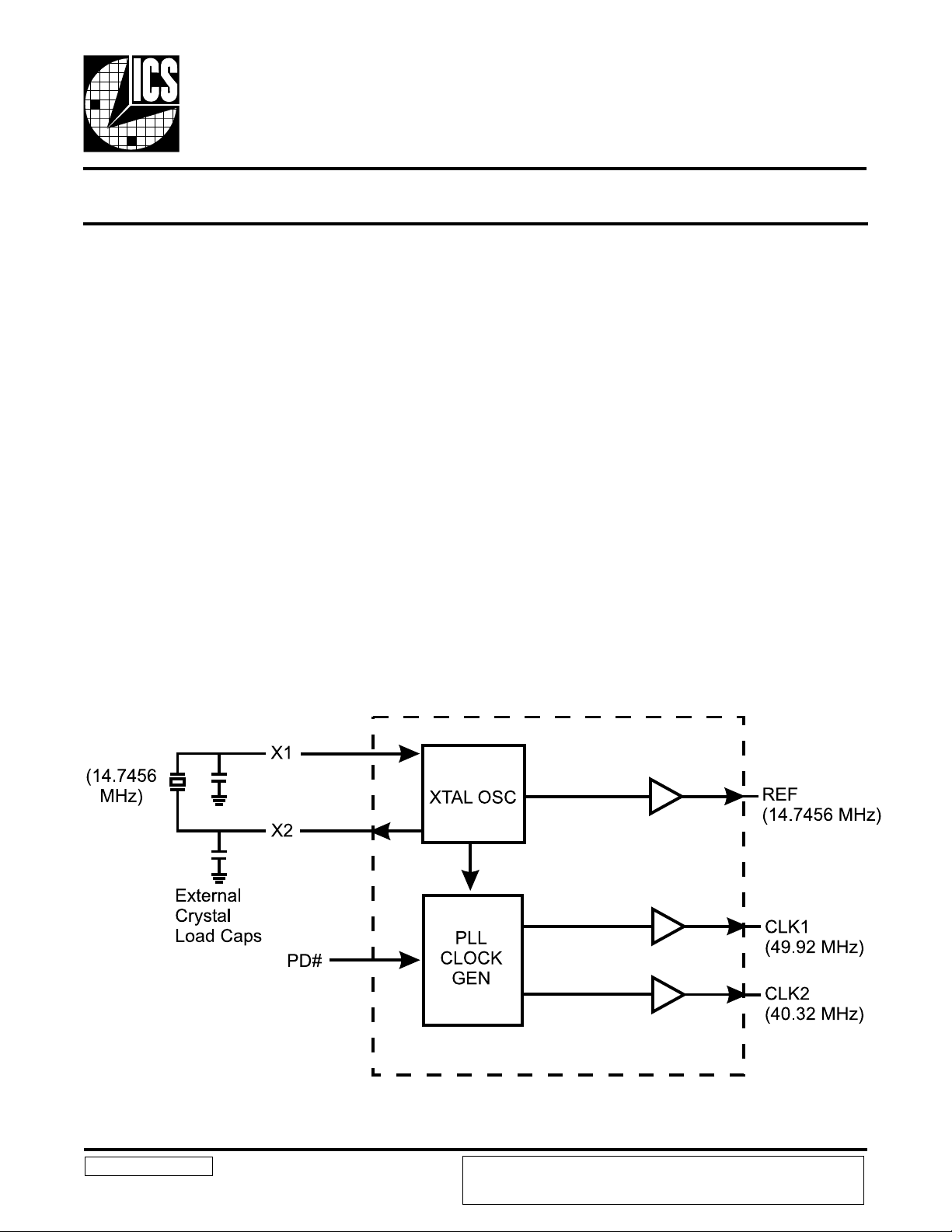

The ICS9120-46 is a high performance frequency generator

designed to support the clock requirements of communication

and audio interfaces. It offers the clock frequencies required

by 28.8 baud modem plus sound system. These frequencies

are synthesized from 14.7456 MHz reference oscillator whose

buffered output is available for the reference.

High accuracy, low-jitter PLLs meet the -96dB signal-tonoise ratios required by 16-bit audio systems. Fast output

clock edge rates minimize board induced jitter.

The on-chip XT AL oscillator accuracy is better than ±100ppm

for an AT cut, 18pF load crystal with initial accuracy of ppm

plus TC, aging and load variation of ±20ppm each assuming

33pF ±5% external load capacitors.

Block Diagram

Features

• Generates 49.92 MHz, 40.32 MHz and 14.7456 MHz

• Single 14.7456 MHz crystal reference

• 49.92 MHz accuracy tracks 40.32 MHz reference

• 80ps one sigma jitter maintains 16-bit performance

• Output rise/fall times less than 1.5ns

• On-chip loop filter components

• 3.0-5.5V supply range

• 8-pin, 150-mil SOIC package

Applications

• Specifically designed to support the high performance

requirements of communication and audio interfaces.

9120-46 Rev B 052497P

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

ICS9120-46

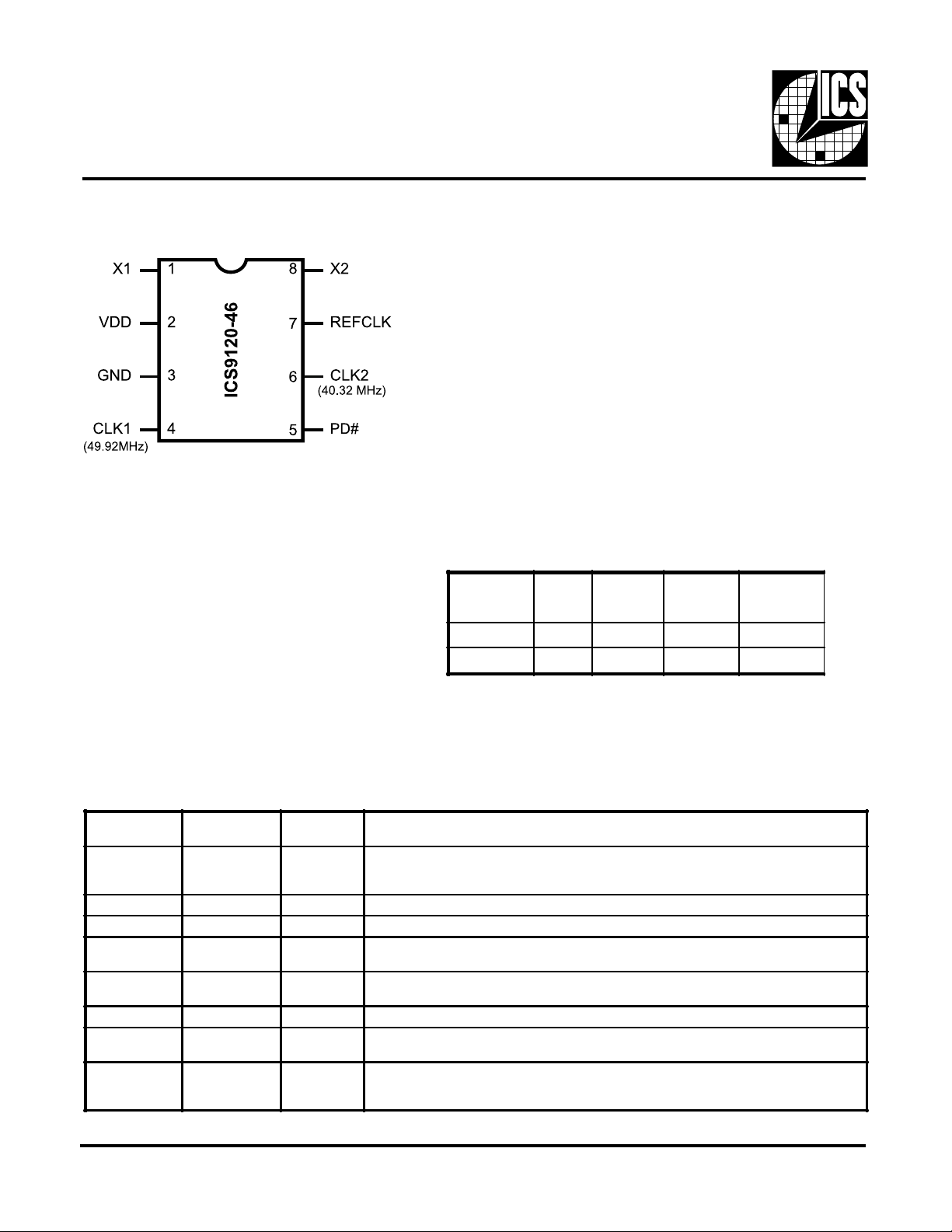

Pin Configuration

8-Pin SOIC

Functionality

The ICS9120-46 incorporates a crystal oscillator circuit designed

to provide 50% duty cycle over a range of operating conditions,

including the addition of external crystal load capacitors to pins

X1 and X2.

For the crystal oscillator, the crystal load capacitance must be

connected externally by adding a capacitor from each of the X1

and X2 pins to ground. A parallel resonant 14.7456 MHz crystal is

recommended.

Duty cycle is also maintained when using an external clock source

(connected to X1, X2 left unconnected) as long as the external

clock has good duty cycle.

Functionality

Pin Descriptions for ICS9120-46

PIN

NUMBER

1 X1 Input

2 VDD Power +Power supply input.

3 GND Power Ground return for Pin 2.

4 CLK1 Output

5 PD# Output

6 CLK2 Output 40.32 MHz target output clock.

7 REF Output

8 X2 Output

PIN

NAME

TYPE DESC RIPTION

Cr ystal or ex tern al clo ck s our ce. H as fe edba ck b ias f or cr ystal.

Nominally 14.7456<N>MH z input applied. (No internal load cap;

m ust co nnect externa l load cap to groun d for crysta l oscilla tor.)

49.92 MHz target output clock

(with nominal 14.7456 MHz input).

Power-down input. All outputs shut off and driven to low output state

w hen th is pin is at logic low le vel. H as pull- up.

14.7456 MHz reference clock buffered output

(with nominal 14.7456 MHz input).

Crystal output drive (leave this pin unconnected when using an

external clock). (No internal load cap; must connect external load cap

to g round for cr ystal os cillator).

X1 (MHz)

PD#

CLK1

(MHz)

CLK2

(MHz)

REF

(MHa)

- 0 Low Low Low

14.7456 1 49.92 40.32 14.7456

2

Loading...

Loading...