ICST GSP9108-10CS8, GSP9108-10CS14, GSP9108-10CN8, GSP9108-10CN14, GSP9108-05CS8 Datasheet

...

Integrated

Circuit

Systems, Inc.

AV9108

CPU Frequency Generator

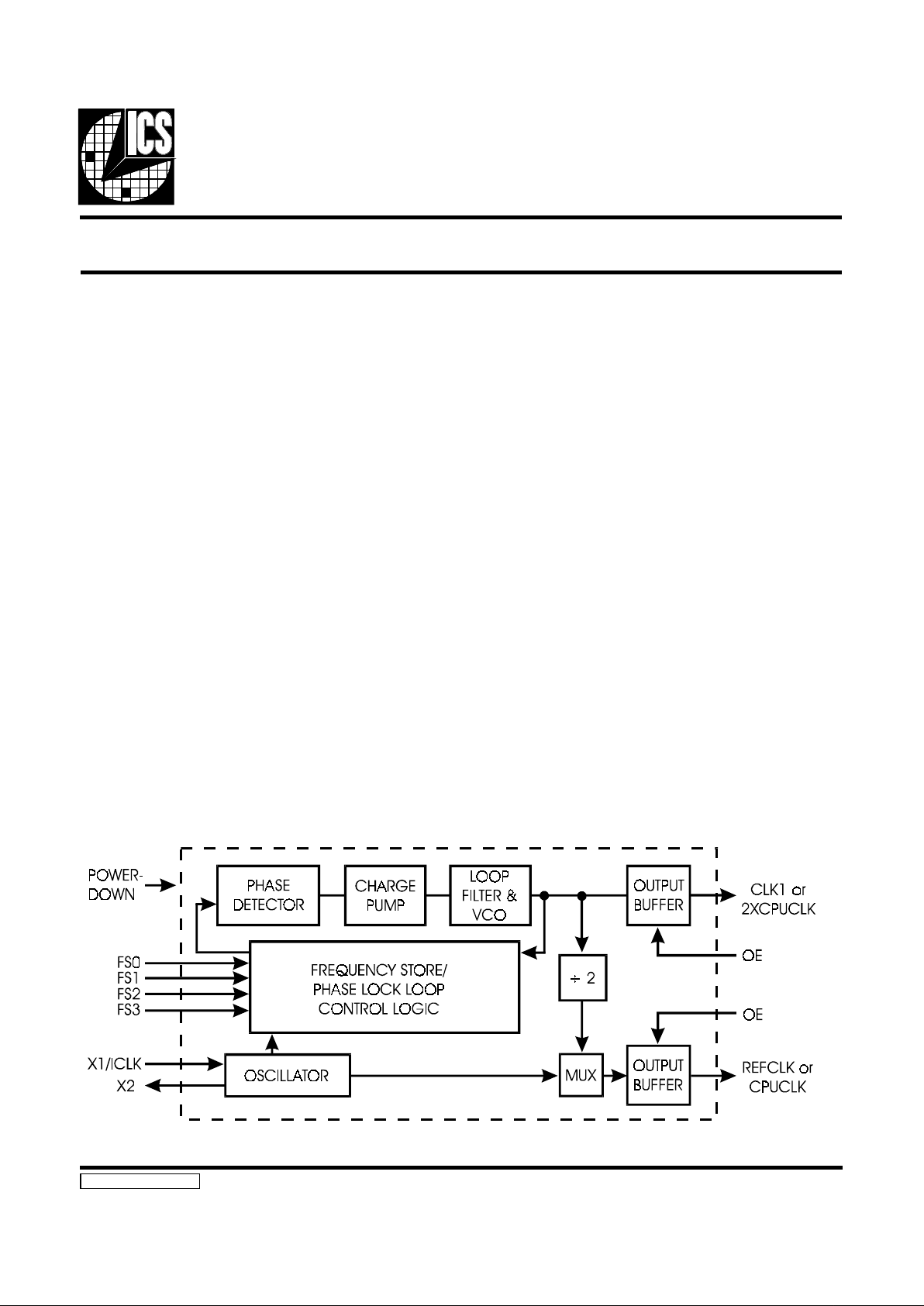

Block Diagram

AV 9108 RevB032195

General Description

The AV9108 offers a tiny footprint solution for generating two

simultaneous clocks. One clock, the REFCLK, is a fixed output

frequency which is the same as the input reference crystal (or

clock). The other clock, CLK1, can vary between 2 and 120

MHz, with up to 16 selectable preprogrammed frequencies

stored in internal ROM.

The ICS9108 is ideal for use in a 3.3V system. It can generate

a 66.66 MHz clock at 3.3V. In addition, the ICS9108 provides

a symmetrical wave form with a worst case duty cycle of 45/55.

The ICS9108 has very tight edge control between the CPU

clock and 2XCPU clock outputs, with a worst case skew of

250ps.

The device has advanced features which include on-chip loop

filters, tristate outputs, and power-down capability. A minimum of external components - two decoupling capacitors and

an optional ferrite bead - are all that are required for jitter-free

operation. Standard versions for computer motherboard applications are the AV9108-03, AV9108-05 and the ICS9108-10.

Custom masked versions, with customized frequencies and

features, are available in 6-8 weeks for a small NRE fee.

Features

•• Runs up to 80 MHz at 3.3V

•• 50/50 typical duty cycle at 5V

••±250ps absolute jitter

•• Generates frequencies from 2 to 140 MHz

•• 2 to 32 MHz input reference frequency

•• Up to 16 frequencies stored internally

•• Patented on-chip Phase Locked Loop with VCO for clock

generation

•• Provides reference clock and synthesized clock

•• On-chip loop filter

•• Low power 0.8µ CMOS technology

•• 8-pin or 14-pin DIP or SOIC package

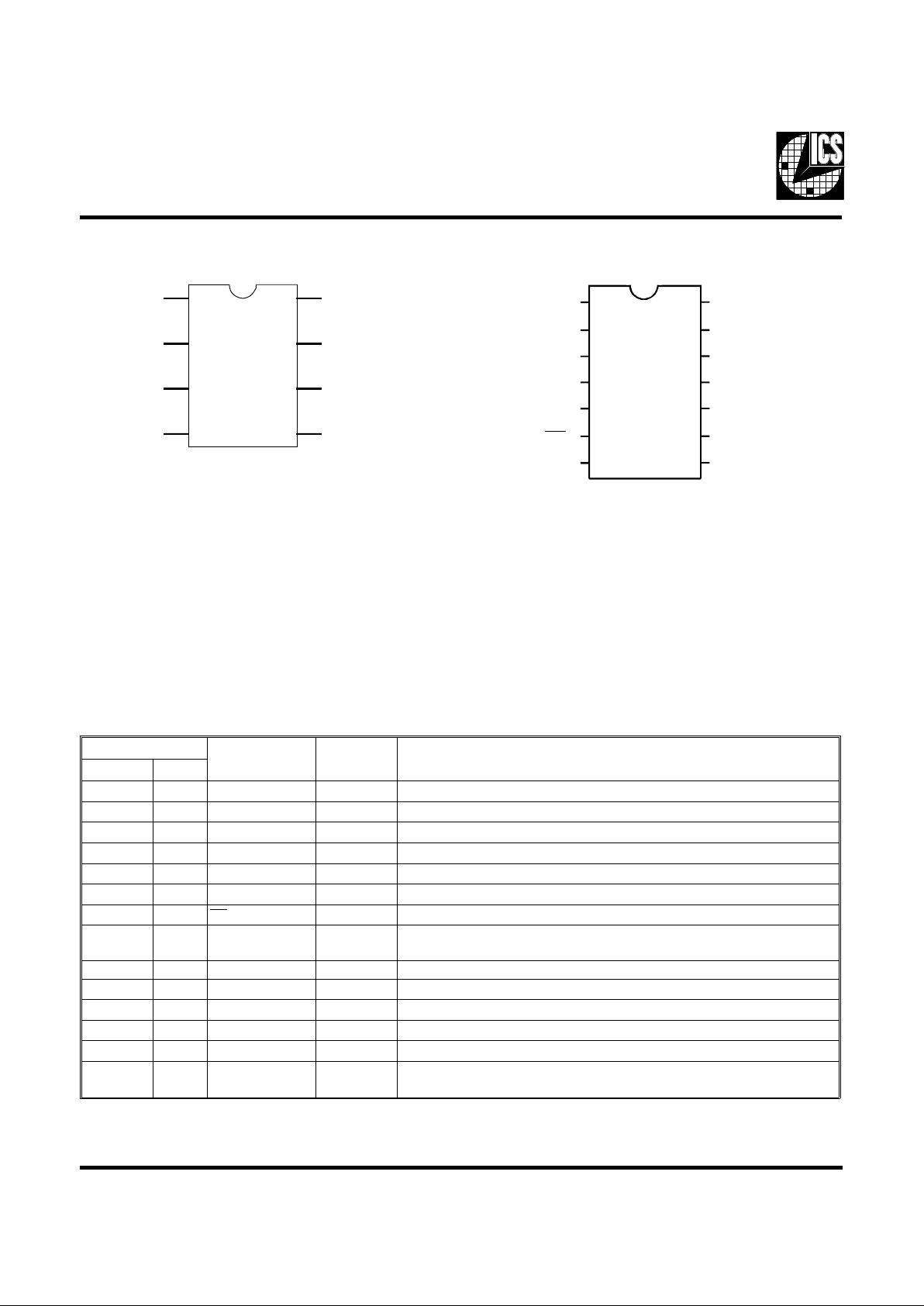

Pin Configuration

Pin Descriptions for

AV9108-03, AV9108-05 and AV9108-10

PIN NUMBER PIN

NAME TYPE DESCRIPTION

-05/-10/-13 -03

1 14 FS0 Input Frequency Select 0 for CLK1 (-03 has pull-up).

5 1 FS1 Input Frequency Select 1 for CLK1 (-03 has pull-up).

2 FS2 Input Frequency Select 2 for CLK1 (-03 has pull-up).

3 FS3 Input Frequency Select 3 for CLK1 (-03 has pull-up).

4 AGND - Analog GROUND.

2 5 GMD - Digital GROUND.

6

PD Input POWER-DOWN. Shuts off chip when low. Internal pull-up.

3 7 X1/ICLK Input CRYSTAL OUTPUT or INPUT CLOCK frequency. Typically 14.318 MHz

system clock.

4 8 X2 Output CRYSTAL OUTPUT (No Connect when clock used.).

9 OE(REFCLK) Input OUTPUT ENABLE. Tristates REFCLK when low. Pull-up.

10 OE(CLK1) Input OUTPUT ENABLE. Tristates CLK1 when low. Pull-up.

6 11 CLK1 Output CLOCK1 Output (see decoding tables).

7 12 VDD - Digital power supply (+3V DC).

8 13 REFCLK Output REFERENCE CLOCK output. Produces a buffered version of the input clock or

crystal frequency (typically 14.318 MHz).

FS0 1 8 REFCLK

GND 2 7 VDD

X1/ICLK 3 6 CLK1

X2 4 5 FS1

AV9108-05/-10

8-Pin DIP, SOIC

FS1 1 14 FS0

FS2 2 13 REFCLK

FS3 3 12 VDD

AGND 4 11 CLK1

GND 5 10 OE (CLK1)

PD 6 9 OE (REFCLK)

X1/ICLK 7 8 X2

AV9108-03/-11

14-Pin DIP, SOIC

AV9108

2

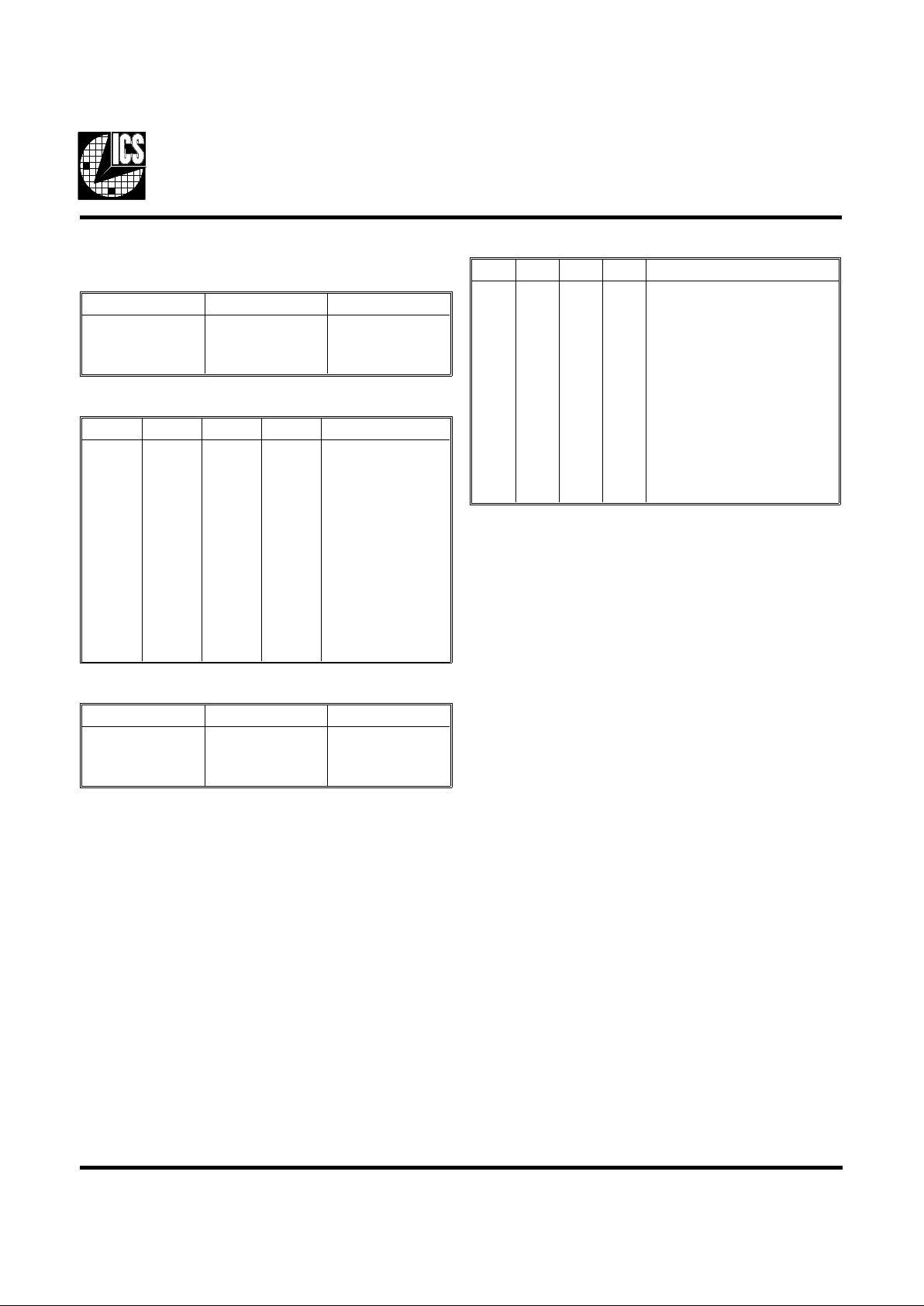

Actual Frequencies

Decoding Table for AV9108-05, 14.318 input

FS1 FS0 CLK1

0

0

1

1

0

1

0

1

40.01 MHz

50.11 MHz

66.61 MHz

80.01 MHz

Decoding Table for AV9108-03, 14.318 input

FS3 FS2 FS1 FS0 CLK1

0

0

0

1

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

16.00 MHz

39.99 MHz

50.11 MHz

80.01 MHz

66.58 MHz

100.23 MHz

8.02 MHz

4.01 MHz

8.02 MHz

20.00 MHz

25.06 MHz

40.01 MHz

33.29 MHz

50.11 MHz

4.01 MHz

2.05 MHz

Decoding Table for AV9108-10, 14.318 input

FS1 FS0 CLK1

0

0

1

1

0

1

0

1

25.057 MHz

33.289 MHz

40.006 MHz

50.113 MHz

Decoding Table for AV9108-11 (in MHz)

FS3 FS2 FS1 FS0 CLK1

0

0

0

1

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

16.00 MHz

33.39 MHz

50.11 MHz

80.01 MHz

66.58 MHz

100.23 MHz

60.00 MHz

4.01 MHz

8.02 MHz

20.05 MHz

25.06 MHz

39.99 MHz

33.25 MHz

50.11 MHz

30.00 MHz

4.01 MHz

Note: The dash number following ICS9108 must be included when ordering product since it specifies the frequ ency decoding

table being ordered. Decoding options can be created by a simple metal mask change.

AV9108

3

Loading...

Loading...