ICST ICS8521BY Datasheet

Integrated

Circuit

Systems, Inc.

ICS8521

LOW SKEW, 1-TO-9

D

IFFERENTIAL-TO-L VHSTL FANOUT BUFFER

GENERAL DESCRIPTION

,&6

HiPerClockS™

accept most standard differential input levels. The PCLK,

nPCLK pair can accept L VPECL, CML, or SSTL input levels.

The clock enable is internally synchronized to eliminate runt

pulseson the outputs during asynchronous assertion/

deassertion of the clock enable pin.

Guaranteed output skew, part-to-part skew and crossover

voltage characteristics make the ICS8521 ideal for today’s

most advanced applications, such as IA64 and static RAMs.

The ICS8521 is a low skew, 1-to-9 3.3V Differential-to-LVHSTL Fanout Buffer and a member of

the HiPerClockS™ family of High Performance

Clock Solutions from ICS. The ICS8521 has two

selectable clock inputs. The CLK, nCLK pair can

FEATURES

• 9 L VHSTL outputs

• Selectable CLK, nCLK or L VPECL clock inputs

• CLK, nCLK pair can accept the following differential input

levels: L VDS, L VPECL, L VHSTL, SSTL, HCSL

• PCLK, nPCLK supports the following input types:

LVPECL, CML, SSTL

• Maximum output frequency up to 500MHz

• Output skew: 50ps (maximum)

• Part-to-part skew: 250ps (maximum)

• Propagation delay: 1.8ns (maximum)

= 1.2V (maximum)

• V

OH

• 3.3V core, 1.8V output operating supply voltages

• 0°C to 70°C ambient operating temperature

• Industrial temperature information available upon request

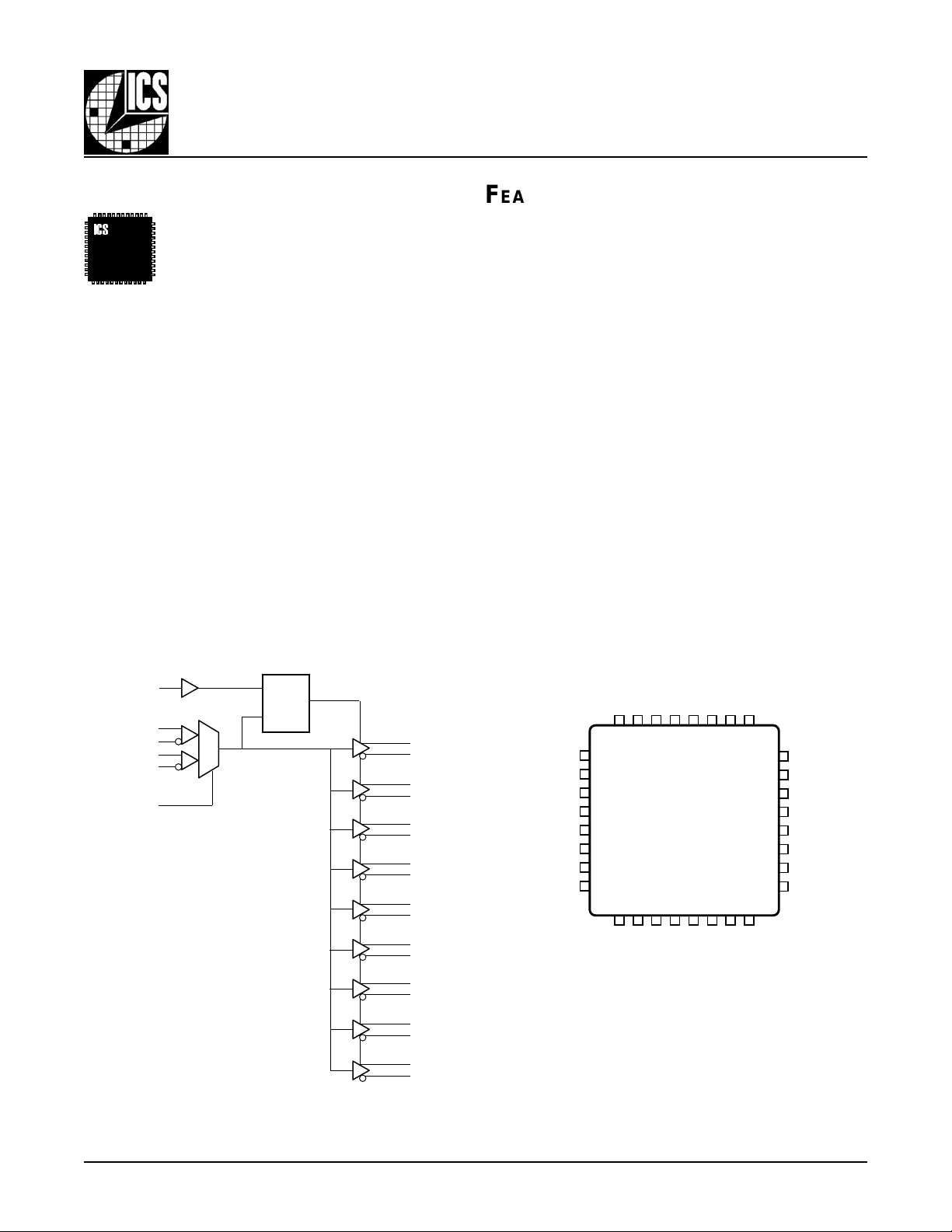

BLOCK DIAGRAM PIN ASSIGNMENT

CLK_EN

CLK

nCLK

PCLK

nPCLK

CLK_SEL

D

Q

LE

0

1

Q0

nQ0

Q1

nQ1

Q2

nQ2

Q3

nQ3

Q4

nQ4

Q5

nQ5

Q6

nQ6

Q7

nQ7

Q8

nQ8

VDD

CLK

nCLK

CLK_SEL

PCLK

nPCLK

GND

CLK_EN

7mm x 7mm x 1.4mm Package Body

V

DDO

Q0

32 31 30 29 28 27 26 25

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16

nQ8

V

DDO

32-Lead LQFP

nQ1

nQ0

Q1

ICS8521

Q7

nQ7

Q8

Y Package

Top View

Q2

nQ6

nQ2

Q6

VDDO

VDDO

24

VDDO

23

Q3

22

nQ3

21

Q4

20

nQ4

19

Q5

18

nQ5

17

VDDO

8521BY www.icst.com/products/hiperclocks.html REV. B JULY 31, 2001

1

Integrated

Circuit

Systems, Inc.

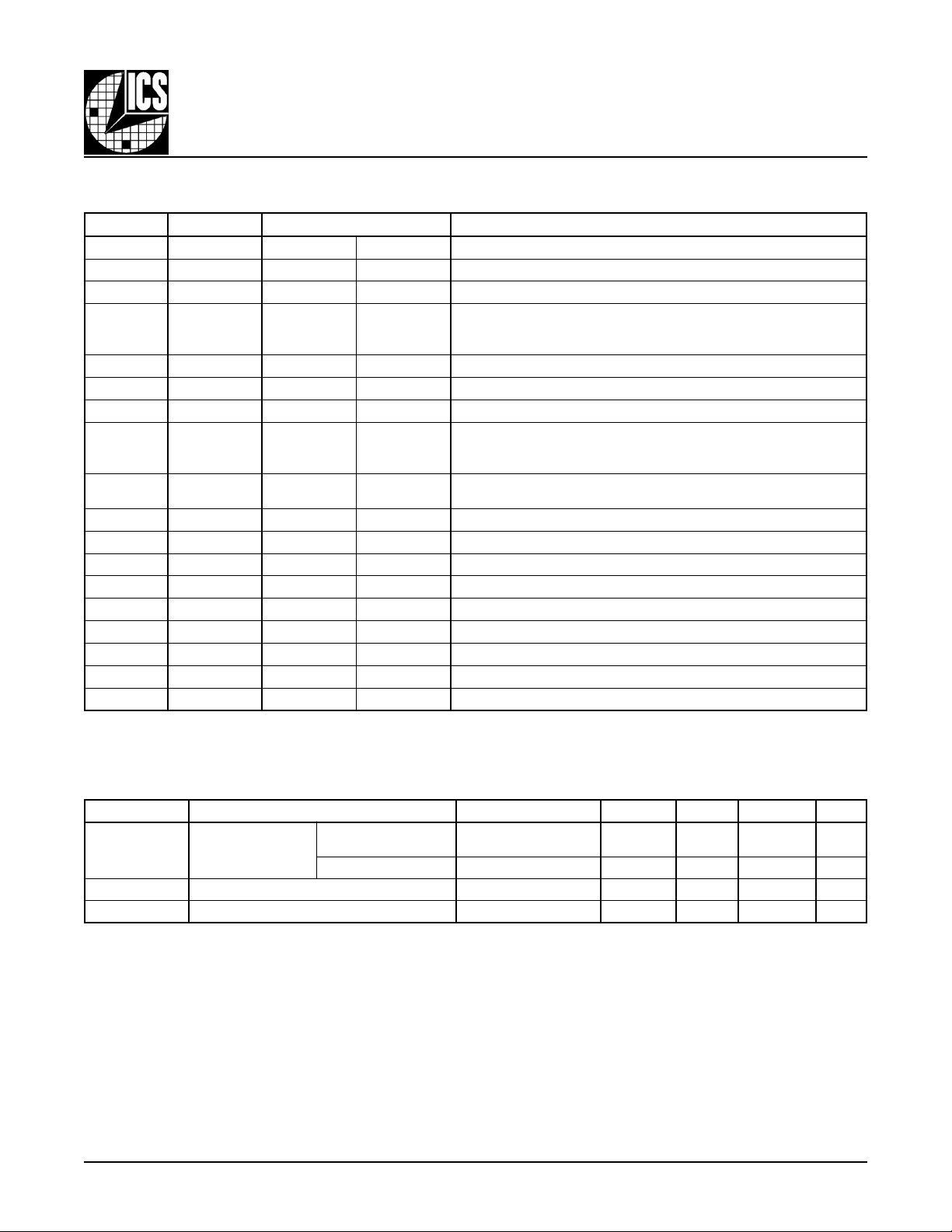

TABLE 1. PIN DESCRIPTIONS

rebmuNemaNepyTnoitpircseD

1V

2KLCtupnInwodlluP.tupnikcolclaitnereffidgnitrevni-noN

3KLCntupnIpulluP.tupnikcolclaitnereffidgnitrevnI

4LES_KLCtupnInwodlluP

5KLCPtupnInwodlluP.tupnikcolcLCEPVLlaitnereffidgnitrevni-noN

6KLCPntupnIpulluP.tupnikcolcLCEPVLlaitnereffidgnitrevnI

7DNGrewoP.dnuorgottcennoC.dnuorgylppusrewoP

8NE_KLCtupnIpulluP

,71,61,9

23,52,42

11,018Q,8QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

31,217Q,7QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

51,416Q,6QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

91,815Q,5QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

12,024Q,4QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

32,223Q3QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

72,622Q,2QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

92,821Q,1QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

13,030Q,0QntuptuO.levelecafretniLTSHVL.riaptuptuolaitnereffiD

:ETON

pulluP

DD

V

ODD

dna

nwodlluP

rewoP.V3.3ottcennoC.nipylppusevitisoP

rewoP.V8.1ottcennoC.snipylppustuptuO

ICS8521

LOW SKEW, 1-TO-9

D

IFFERENTIAL-TO-L VHSTL FANOUT BUFFER

stceles,WOLnehW.KLCn,KLC

.slevelecafretniSOMCVL/LTTVL

wollofstuptuokcolc,HGIHnehW.elbanekcolcgnizinorhcnyS

stuptuoQn,woldecroferastuptuoQ,WOLnehW.tupnikcolc

/SOMCVL.hgihdecroferaLTTVL.slevelecafretni

.seulavlacipytrof,scitsiretcarahCniP,2elbaTeeS.srotsisertupnilanretniotsrefer

.stupniKLCPn,KLCPstceles,HGIHnehW.tupnitceleskcolC

TABLE 2. PIN CHARACTERISTICS

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

,KLCn,KLC

C

NI

R

PULLUP

R

8521BY www.icst.com/products/hiperclocks.html REV. B JULY 31, 2001

NWODLLUP

ecnaticapaCtupnI

rotsiseRpulluPtupnI 15KΩ

rotsiseRnwodlluPtupnI 15KΩ

KCLPn,KLCP

LES_KLC,NE_KLC4Fp

2

4Fp

Integrated

Circuit

Systems, Inc.

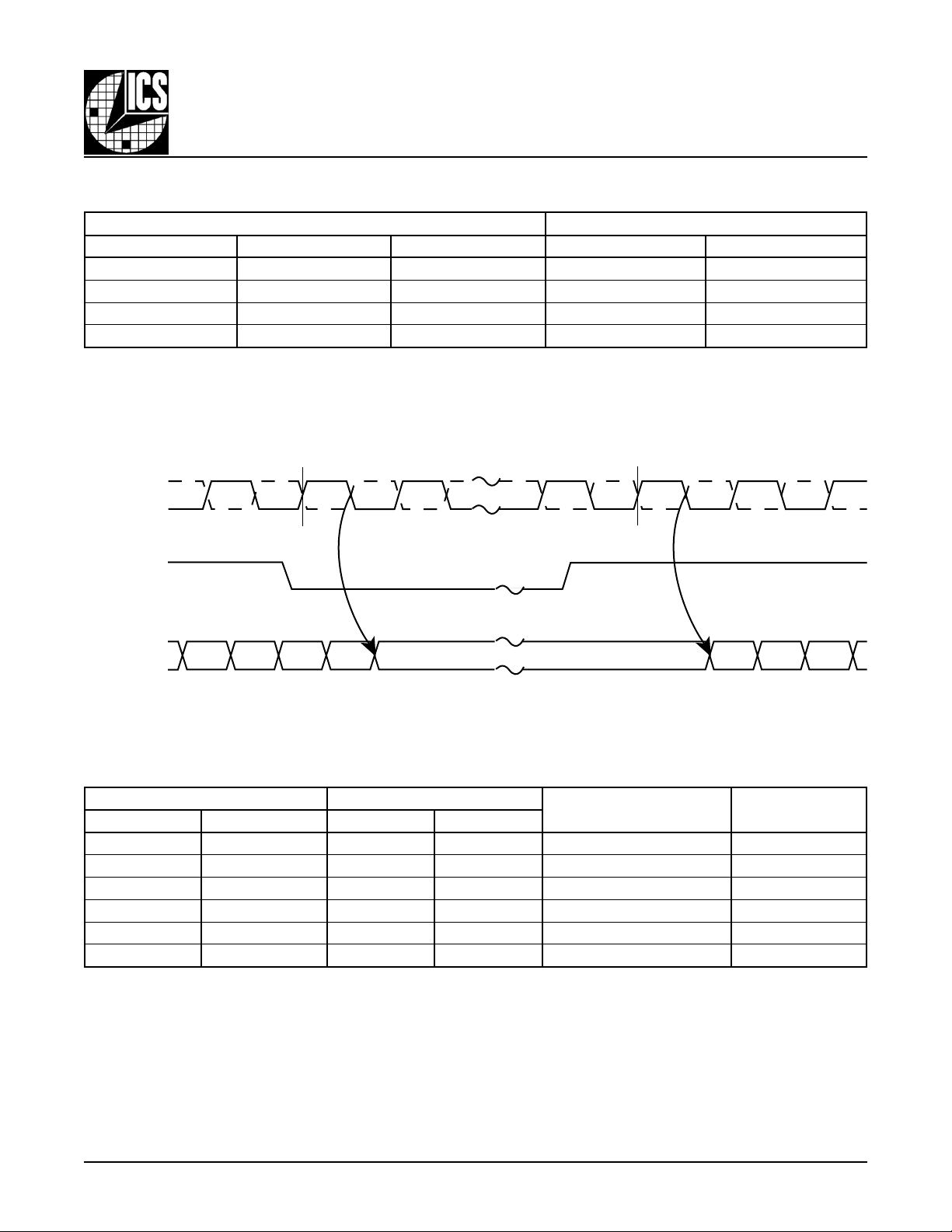

TABLE 3A. CONTROL INPUT FUNCTION TABLE

stupnIstuptuO

NE_KLCLES_KLCdecruoSdetceleS8Qurht0Q8Qnurht0Qn

00 KLCn,KLCWOL;delbasiDHGIH;delbasiD

01 KLCPn,KLCPWOL;delbasiDHGIH;delbasiD

10 KLCn,KLCdelbanEdelbanE

11 KLCPn,KLCPdelbanEdelbanE

.1erugiFninwohssa

.B3elbaTni

ICS8521

LOW SKEW, 1-TO-9

D

IFFERENTIAL-TO-L VHSTL FANOUT BUFFER

egdekcolctupnignillafdnagnisiragniwollofdelbanerodelbasiderastuptuokcolceht,sehctiwsNE_KLCretfA

debircsedsastupniKLCPn,KLCPdnaKLCn,KLCehtfonoitcnufaerastuptuoehtfoetatseht,edomevitcaehtnI

nCLK, nPCLK

CLK, PCLK

CLK_EN

nQ0 - nQ8

Q0 - Q8

Disabled

TABLE 3B. CLOCK INPUT FUNCTION TABLE

stupnIstuptuO

KLCProKLCKLCPnroKLCn8Qurht0Q8Qnurht0Qn

01WOLHGIHlaitnereffiDotlaitnereffiDgnitrevnInoN

10 HGIHWOLlaitnereffiDotlaitnereffiDgnitrevnInoN

01ETON;desaiBWOLHGIHlaitnereffiDotdednEelgniSgnitrevnInoN

11ETON;desaiBHGIHWOLlaitnereffiDotdednEelgniSgnitrevnInoN

1ETON;desaiB0HGIHWOLlaitnereffiDotdednEelgniSgnitrevnI

1ETON;desaiB1WOLHGIHlaitnereffiDotdednEelgniSgnitrevnI

.sleveldedneelgnistpeccaottupni

Enabled

FIGURE 1: CLK_EN TIMING DIAGRAM

edoMtuptuOottupnIytiraloP

laitnereffidehtgniriwsessucsidhcihw,9erugiF,8egapnonoitcesnoitamrofnInoitacilppAehtotreferesaelP:1ETON

8521BY www.icst.com/products/hiperclocks.html REV. B JULY 31, 2001

3

Integrated

Circuit

Systems, Inc.

LOW SKEW, 1-TO-9

D

IFFERENTIAL-TO-L VHSTL FANOUT BUFFER

ICS8521

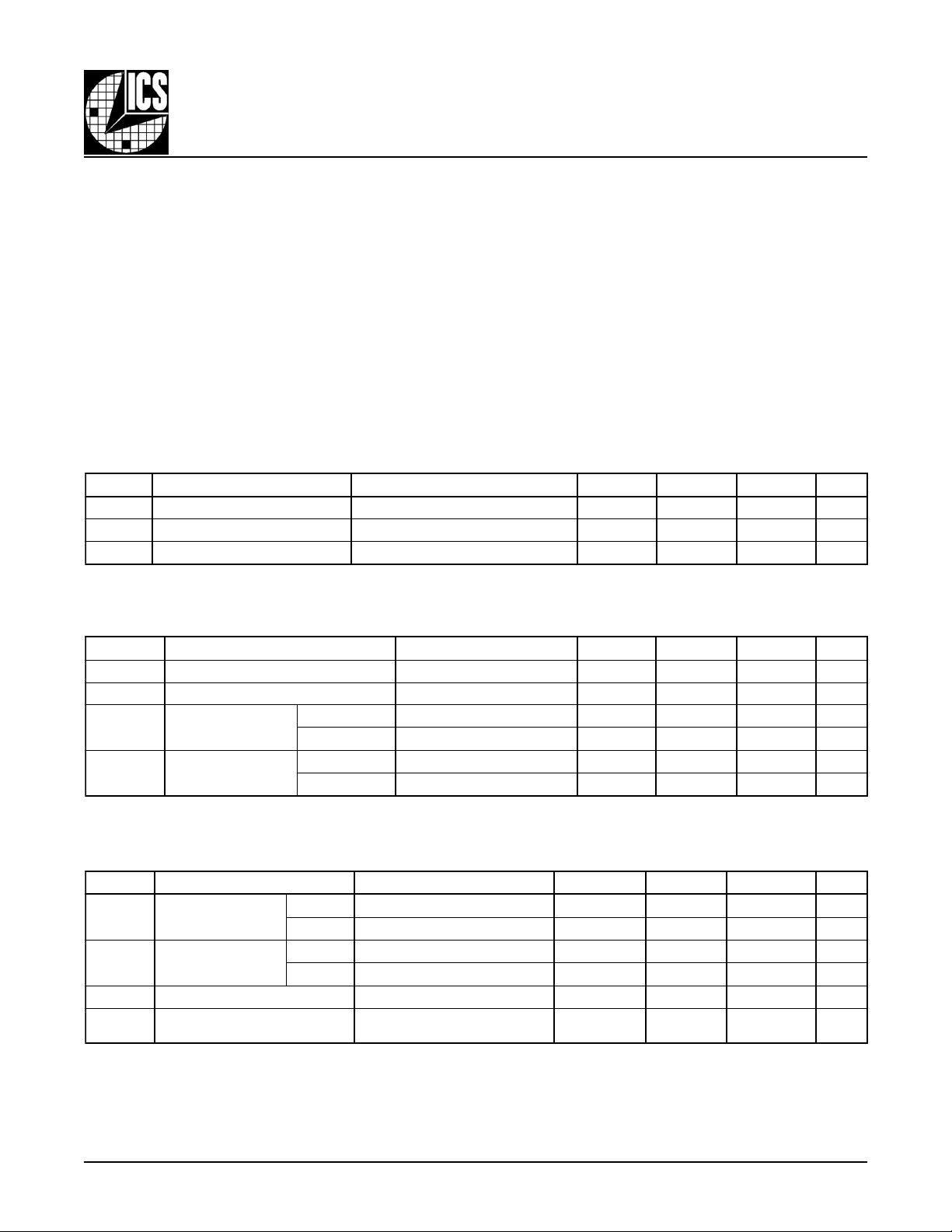

ABSOLUTE MAXIMUM RATINGS

Supply Voltage, V

Inputs, V

I

Outputs, V

Package Thermal Impedance, θ

Storage T emperature, T

DDx

O

JA

STG

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings

are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the

DC Characteristics

or

AC Characteristics

ods may affect product reliability.

4.6V

-0.5V to VDD + 0.5V

-0.5V to V

DDO

+ 0.5V

47.9°C/W

-65°C to 150°C

is not implied. Exposure to absolute maximum rating conditions for extended peri-

TABLE 4A. POWER SUPPLY DC CHARACTERISTICS, V

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

V

DD

V

ODD

I

DD

TABLE 4B. LVCMOS DC CHARACTERISTICS, V

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

V

HI

V

LI

I

HI

I

LI

TABLE 4C. DIFFERENTIAL DC CHARACTERISTICS, V

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

I

HI

I

LI

V

PP

V

RMC

2,1ETON

egatloVylppuSevitisoP 531.33.3564.3V

egatloVylppuStuptuO 6.18.10.2V

tnerruCylppuSrewoP 0608Am

= 3.3V±5%, V

DD

LES_KLC,NE_KLC2567.3V

LES_KLC,NE_KLC3.0-8.0V

tnerruChgiHtupnI

tnerruCwoLtupnI

tnerruChgiHtupnI

tnerruCwoLtupnI

NE_KLCV

LES_KLCV

NE_KLCV

LES_KLCV

DD

KLCV

KLCnV

KLCV

KLCnV

egatloVtupnIkaeP-ot-kaeP51.03.1V

;egatloVtupnIedoMnommoC

VsadenifedsiegatlovedomnommoC:2ETON

= 3.3V±5%, V

DD

NI

NI

NI

NI

= 3.3V±5%, V

V=

NI

DD

V=

NI

DD

V,V0=

NI

NI

DD

V,V0=

DD

.

= 1.8V±0.2V, TA = 0°C TO 70°C

DDO

= 1.8V±0.2V, TA = 0°C TO 70°C

DDO

V=

DD

V=

DD

V,V0=

V,V0=

V564.3=5Aµ

V564.3=051Aµ

DD

DD

DDO

V564.3=051-Aµ

V564.3=5-Aµ

= 1.8V±0.2V , TA = 0°C TO 70°C

V564.3=051Aµ

V564.3=5Aµ

V564.3=5-Aµ

V564.3=051-Aµ

5.0V

VsiKLCndnaKLCrofegatlovtupnimumixameht,snoitacilppadedneelgnisroF:1ETON

DD

.V3.0+

58.0-V

DD

8521BY www.icst.com/products/hiperclocks.html REV. B JULY 31, 2001

4

Loading...

Loading...