Integrated

Circuit

Systems, Inc.

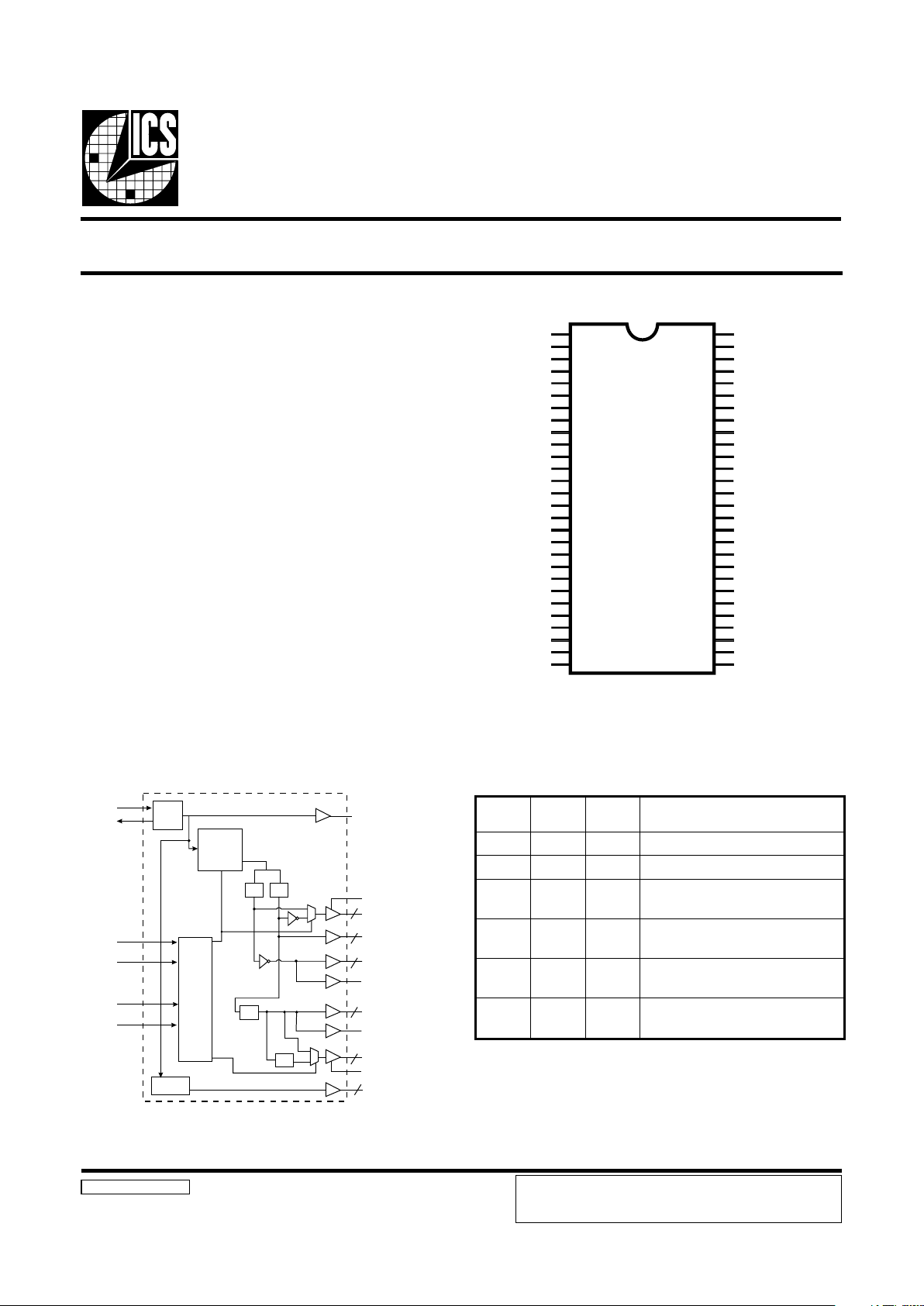

ICS9250-27

Third party brands and names are the property of their respective owners.

Block Diagram

9250-27 Rev B 02/15/01

Recommended Application:

810/810E and 815 type chipset.

Output Features:

• 3 CPU (2.5V) (up to 133MHz achievable through I

2

C)

• 9 SDRAM (3.3V) (up to 133MHz achievable

through I

2

C)

• 7 PCI (3.3 V) @33.3MHz

• 2 IOAPIC (2.5V) @ 33.3 MHz

• 3 Hublink clocks (3.3 V) @ 66.6 MHz

• 2 (3.3V) @ 48 MHz (Non spread spectrum)

• 1 REF (3.3V) @ 14.318 MHz

Features:

• Supports spread spectrum modulation,

0 to -0.5% down spread.

•I

2

C support for power management

• Efficient power management scheme through PD#

• Uses external 14.138 MHz crystal

• Alternate frequency selections available through I

2

C

control.

Functionality

Pin Configuration

56-Pin 300mil SSOP

* This input has a 50KΩ pull-down to GND.

*FS2//REF0

VDD

X1

X2

GND

GND

3V66-0

3V66-1

3V66-2

VDD

VDD

PCICLK_F

PCICLK0

GND

PCICLK1

PCICLK2

GND

PCICLK3

PCICLK4

PCICLK5

VDD

VDD

GND

GND

48MHz_0

48MHz_1

VDD

FS0

GND

IOAPIC0

IOAPIC1

VDDL

CPUCLK0

VDDL0

CPUCLK1

CPUCLK2

GNDL

GND

SDRAM0

SDRAM1

VDD

SDRAM2

SDRAM3

GND

SDRAM4

SDRAM5

VDD

SDRAM6

SDRAM7

GND

SDRAM_F

VDD

PD#

SCLK

S DATA

FS1

ICS9250-27

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

Frequency Generator & Integrated Buffers for Celeron & PII/III™

2SF1SF0SFnoitcnuF

X00 etatsirT

X0 1tseT

010

zHM66=UPCevitcA

zHM001=MARDS

011

zHM001=UPCevitcA

zHM001=MARDS

110

zHM331=UPCevitcA

zHM331=MARDS

111

zHM331=UPCevitcA

zHM001=MARDS

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

REF0

CPU66/100/133 (2:0)

VDDL

3V66 (2:0)

SDRAM (7:0)

PCICLK (5:0)

IOAPIC (1:0)

VDDL

SDRAM_F

PCICLK_F

PLL2

48MHz (1:0)

X1

X2

XTAL

OSC

Control

Logic

Config

Reg

FS (2:0)

PD#

2

3

3

8

6

2

/2

/2

/3

/2

PLL1

Spread

Spectrum

SDATA

SCLK

Power Groups

AVDD = Pin 22 Analog power for PLL

AGND = Pin 23 Analog ground

VDD48 = Pin 27 Analog power for 48MHz PLL

GND = Pin 24 Analog ground for 48MHz PLL

2

ICS9250-27

The ICS9250-27 is a single chip clock solution for 810/810E and 815 type chipset. It provides all necessary clock

signals for such a system.

Spread spectrum may be enabled through I

2

C programming. Spread spectrum typically reduces EMI by 8dB to 10

dB. This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS925027 employs a proprietary closed loop design, which tightly controls the percentage of spreading over process and

temperature variations.

General Description

Pin Configuration

REBMUNNIPEMANNIPEPYTNOITPIRCSED

1

2SFNIytilanoitcnuftuptuolla,ycneuqerfUPCsenimreteD.niptceleSnoitcnuF

0FERTUO.tuptuokcolcecnereferzHM813.41,V3.3

31XNI

kcabdeefdna)Fp33(pacdaollanretnisah,tupnilatsyrC

2Xmorfrotsiser

42XTUO

daollanretnisaH.zHM813.41yllanimon,tuptuolatsyrC

)Fp33(pac

,32,71,41,6,5

,74,14,53,42

65,84

DNGRWPylppusV3.3rofsnipdnuorG

7,8,9)0:2(66V3TUOBUHrofstuptuokcolczHM66dexiFV3.3

,12,11,01,2

44,83,33,72,22

DDVRWPylppusrewopV3.3

21F_KLCICPTUOtuptuokcolcICPV3.3gninnureerF

,61,81,91,02

31,51

)0:5(KLCICPTUOstuptuokcolcICPV3.3

520_zHM84TUOBSUrofstuptuokcolczHM84dexiFV3.3

621_zHM84TUO

oediv/scihpargroftuptuoregnortS.tuptuokcolczHM84dexifV3.3

)etaregdesn/V1muminim(ecafretni

82,92)0:1(SFNI

.ytilanoitcnuftuptuolla,ycneuqerfUPCsenimreteD.sniptceleSnoitcnuF

.3egapnoelbatytilanoitcnuFotreferesaelP

03ATADSO/IIrofnipataD

2

tnarelotV5yrtiucricC

13KLCSNIIfonipkcolC

2

tnarelotV5yrtiucricC

23#DPNI

otniecivedehtnwodrewopotdesuniptupniwolevitcasuonorhcnysA

dnaOCVehtdnadelbasideraskcolclanretniehT.etatsrewopwola

ebtonlliwnwodrewopehtfoycnetalehT.deppotseralatsyrceht

.sm3nahtretaerg

,04,93,73,63

64,54,34,24

)0:7(MARDSTUO

ffodenrutebnacstuptuoMARDSllA.zHM001gninnurtuptuoV3.3

Ihguorht

2

C

43F_MARDSTUOIhguorhtffodenrutebtonnac,MARDSzHM001gninnureerfV3.3

2

C

25,05,94)0:2(KLCUPCTUO

gnidnepedzHM331rozHM001,zHM66.tuptuokcolcsubtsoHV5.2

.snipSFno

35,15LDDVRWPCIPAOI&UPCrofylppyusrewopV5.2

55,45)0:1(CIPAOITUO.zHM3.33tagninnurstuptuokcolcV5.2

3

ICS9250-27

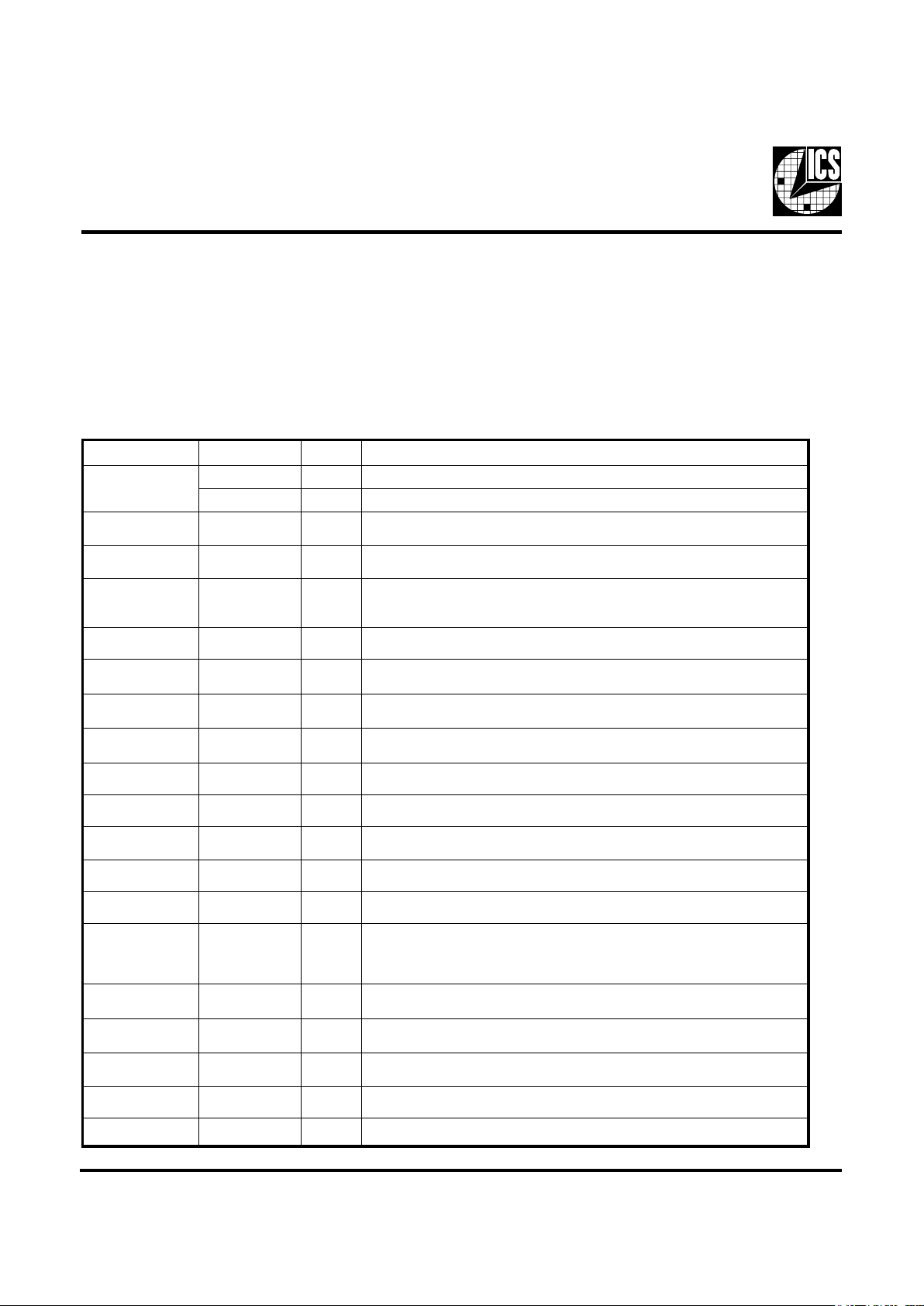

Power Down Waveform

Note

1. After PD# is sampled active (Low) for 2 consective rising edges of CPUCLKs, all

the output clocks are driven Low on their next High to Low tranistiion.

2. Power-up latency <3ms.

3. Waveform shown for 100MHz

Maximum Allowed Current

Clock Enable Configuration

#DPKLCUPCMARDSCIPAOIzHM66KLCICP

,FER

zHM84

csOsOCV

0WOLWOLWOLWOLWOLWOLFFOFFO

1NONONONONONONONO

518

noitidnoC

noitpmusnocylppusV5.2xaM

,sdaolpacetercsidxaM

V526.2=2qddV

DNGro3qddV=stupnicitatsllA

noitpmusnocylppusV5.2xaM

,sdaolpacetercsidxaM

V564.3=2qddV

DNGro3qddV=stupnicitatsllA

edoMnwodrewoP

0=#NWDRWP(

Am01Am01

zHM66evitcAlluF

010=]0:2[SF

Am07Am082

zHM001evitcAlluF

110=]0:2[SF

Am001Am082

zHM331evitcAlluF

111=]0:2[SF

4

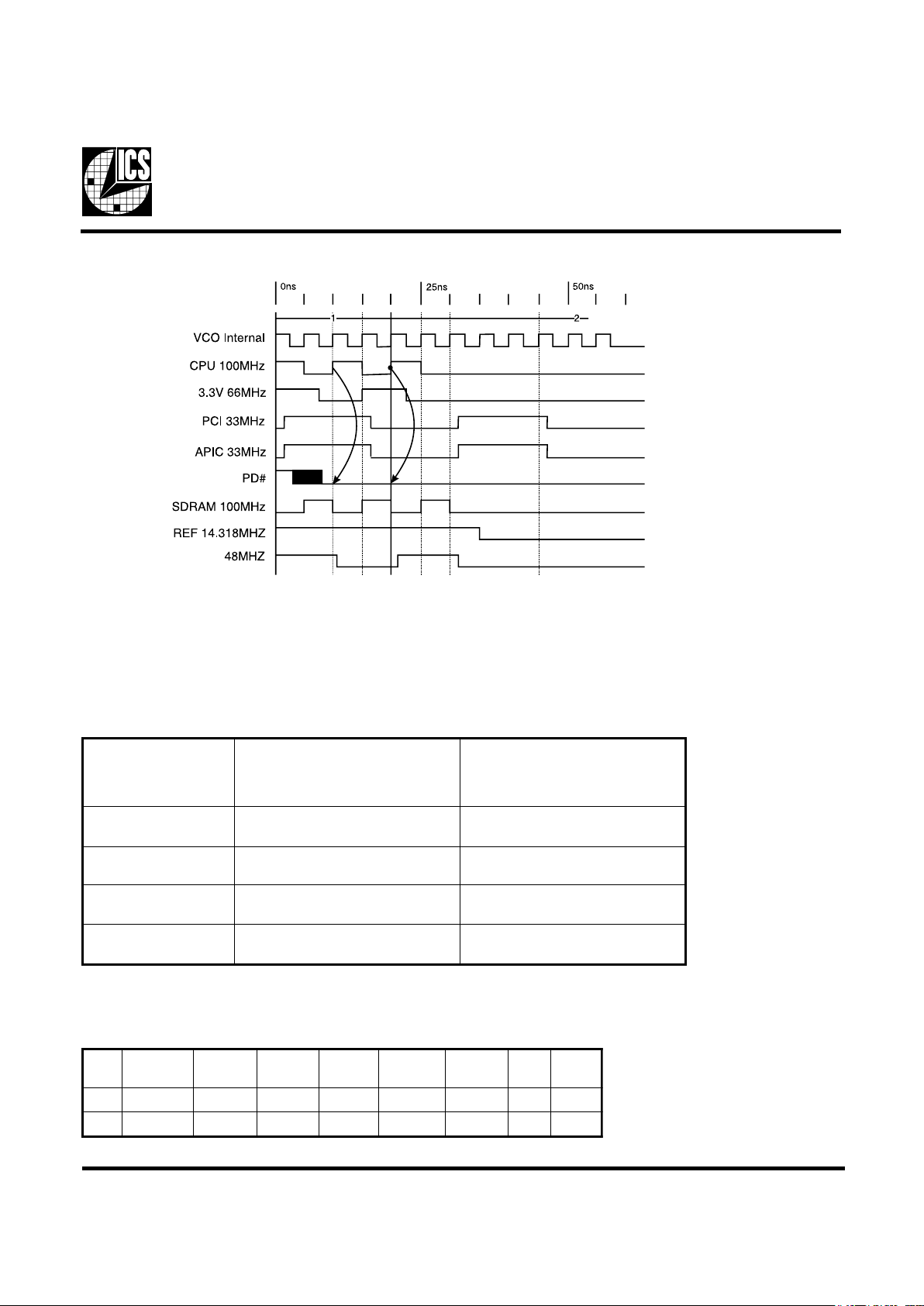

ICS9250-27

2SF1SF0SFUPCMARDS66V3ICPzHM84FERCIPAOI

X00 etatsirTetatsirTetatsirTetatsirTetatsirTetatsirTetatsirT

X0 1 2/KLCT2/KLCT3/KLCT6/KLCT2/KLCTKLCT6/KLCT

010 zHM6.66zHM001zHM6.66zHM3.33zHM84zHM813.41zHM3.33

011 zHM001zHM001zHM6.66zHM3.33zHM84zHM813.41zHM3.33

110 zHM331zHM331zHM6.66zHM3.33zHM84zHM813.41zHM3.33

111 zHM331zHM001zHM6.66zHM3.33zHM84zHM813.41zHM3.33

Truth Table

Byte 0: Control Register

(1 = enable, 0 = disable)

tiB#niPemaNDWPnoitpircseD

7tiBDIdevreseR0)evitcanI/evitcA(

6tiBDIdevreseR0)evitcanI/evitcA(

5tiBDIdevreseR0)evitcanI/evitcA(

4tiBDIdevreseR0)evitcanI/evitcA(

3tiB

murtcepSdaerpS

)ffO=0/nO=1(

1)evitcanI/evitcA(

2tiB621zHM841)evitcanI/evitcA(

1tiB520zHM841)evitcanI/evitcA(

0tiB942KLCUPC1)evitcanI/evitcA(

Note: Reserved ID bits must be wirtten as "0".

Byte 1: Control Register

(1 = enable, 0 = disable)

tiB#niPemaNDWPnoitpircseD

7tiB637MARDS1)evitcanI/evitcA(

6tiB736MARDS1)evitcanI/evitcA(

5tiB935MARDS1)evitcanI/evitcA(

4tiB044MARDS1)evitcanI/evitcA(

3tiB243MARDS1)evitcanI/evitcA(

2tiB342MARDS1)evitcanI/evitcA(

1tiB541MARDS1)evitcanI/evitcA(

0tiB640MARDS1)evitcanI/evitcA(

Notes:

1. Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be

configured at power-on and are not expected to be configured during the normal modes of operation.

2. PWD = Power on Default

5

ICS9250-27

Byte 3: ICS Reserved Functionality and frequency select register (Default as noted in PWD)

Note 1: For system operation, the BSEL lines of the CPU will program FS0, FS2 for the appropriate CPU speed, always with

SDRAM = 100MHz. After BIOS verifies the SDRAM is PC133 speed, then bit 0 can be written from the default 0 to

1 to change the SDRAM output frequency from 100MHz to 133MHz. This will only change if the CPU is at the

133MHz FSB speed as shown in this table. The CPU, 3v66, PCI, and IOAPIC clocks will be glitch free during this

transition, and only SDRAM will change.

Note 2: "ICS RESERVED BITS" must be writtern as "O".

Note3: Undefined bits can be written either as "1 or 0"

tiBnoitpitcseDDWP

7tiB)2etoN(tibdevreseRSCI 0

6tiB)2etoN(tibdevreseRSCI 0

5tiB)2etoN(tibdevreseRSCI 0

4tiB)2etoN(tibdevreseRSCI 0

3tiB)2etoN(tibdevreseRSCI 0

2tiB)3etoN(tibdenifednU X

1tiB)3etoN(tibdenifednU X

0tiB

0tiB0SF1SF

KLCUPC

zHM

MARDS

zHM

66V3

zHM

KLCICP

zHM

CIPAOI

zHM

0

1etoN

000 66.660.00166.6633.3333.33

010 0.0010.00166.6633.3333.33

001 23.33123.33166.6633.3333.33

011 23.3310.00166.6633.3333.33

100 66.660.00166.6633.3333.33

110 0.0010.00166.6633.3333.33

10 1 23.33123.33166.6633.3333.33

111 23.33123.33166.6633.3333.33

Byte 2: Control Register

(1 = enable, 0 = disable)

Notes:

1. Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be

configured at power-on and are not expected to be configured during the normal modes of operation.

2. PWD = Power on Default

3. Undefined bit can be wirtten with either a "1" or "0".

tiB#niPemaNDWPnoitpircseD

7tiB9 )PGA(2-66V31)evitcanI/evitcA(

6tiB025KLCICP1)evitcanI/evitcA(

5tiB914KLCICP1)evitcanI/evitcA(

4tiB813KLCICP1)evitcanI/evitcA(

3tiB612KLCICP1)evitcanI/evitcA(

2tiB511KLCICP1)evitcanI/evitcA(

1tiB310KLCICP1)evitcanI/evitcA(

0tiB- tibdenifednUX)evitcanI/evitcA(

6

ICS9250-27

Byte 4: Reserved Register

(1 = enable, 0 = disable)

Byte 5: Reserved Register

(1 = enable, 0 = disable)

tiB#niPemaNDWPnoitpircseD

7tiB- devreseR0)evitcanI/evitcA(

6tiB- devreseR0)evitcanI/evitcA(

5tiB- devreseR0)evitcanI/evitcA(

4tiB- devreseR0)evitcanI/evitcA(

3tiB- devreseR0)evitcanI/evitcA(

2tiB- devreseR0)evitcanI/evitcA(

1tiB- devreseR0)evitcanI/evitcA(

0tiB- devreseR0)evitcanI/evitcA(

tiB#niPemaNDWPnoitpircseD

7tiB- devreseR0)evitcanI/evitcA(

6tiB- devreseR0)evitcanI/evitcA(

5tiB- devreseR0)evitcanI/evitcA(

4tiB- devreseR0)evitcanI/evitcA(

3tiB- devreseR0)evitcanI/evitcA(

2tiB- devreseR0)evitcanI/evitcA(

1tiB- devreseR0)evitcanI/evitcA(

0tiB- devreseR0)evitcanI/evitcA(

Notes:

1. Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be

configured at power-on and are not expected to be configured during the normal modes of operation.

2. PWD = Power on Default

Group Timing Relationship Table

1

puorGzHM66UPC

zHM001MARDS

zHM001UPC

zHM001MARDS

zHM331UPC

zHM001MARDS

zHM331UPC

zHM331MARDS

tesffOecnareloTtesffOecnareloTtesffOecnareloTtesffOecnareloT

MARDSotUPCsn5.2sp005sn0.5sp005sn0.0sp005sn57.3sp005

66V3otUPCsn5.7sp005sn0.5sp005sn0.0sp005sn0.0sp005

66V3otMARDSsn0.0sp005sn0.0sp005sn0.0sp005sn57.3sp005

ICPot66V3sn5.3-5.1A/Nsn5.3-5.1A/Nsn5.3-5.1A/Nsn5.3-5.1A/N

ICPotCIPAOIsn0.0sn0.1sn0.0sn0.1sn0.0sn0.1sn0.0sn0.1

TOD&BSUhcnysAA/NhcnysAA/NhcnysAA/NhcnysAA/N

7

ICS9250-27

Absolute Maximum Ratings

Core Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . 4.6 V

I/O Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . 3.6V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND –0.5 V to V

DD

+0.5 V

Ambient Operating Temperature . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are

stress specifications only and functional operation of the device at these or any other conditions above those listed in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods

may affect product reliability.

Electrical Characteris tics - Input/Supply/Common Output Parameters

TA = 0 - 70C; Supply Voltage VDD = 3.3 V +/-5%, V

DDL

= 2.5 V +/-5% (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Input High Voltage V

IH

2V

DD

+0.3 V

Input Low Voltage V

IL

VSS-0.3 0.8 V

Input High Current I

IH

VIN = V

DD

-5 5

µ

A

I

IL1

VIN = 0 V; Inputs with no pull-up resistors -5 2

I

IL2

VIN = 0 V; Inputs with pull-up resistors -200 -100

C

L

= 0 pF; Select @ 66 MHz 97 115

C

L

= 0 pF; Select @ 100 MHz 91 110

C

L

= 0 pF; Select @ 133 MHz 100 165

C

L

= Max loads; Select @ 66 MHz 295 330

C

L

= Max loads; Select @ 100 MHz 280 320

C

L

= Max loads; Select @ 133 MHz 300 395

C

L

= 0 pF; Select @ 66 MHz 16 19

C

L

= 0 pF; Select @ 100 MHz 25 35

C

L

= 0 pF; Select @ 133 MHz 26 40

C

L

= Max loads; Select @ 66 MHz 19 30

C

L

= Max loads; Select @ 100 MHz 34 50

C

L

= Max loads; Select @ 133 MHz 40 70

I

DD3.3PD

CL = Max loads

220 400

I

DD.25PD

Input address VDD or GND

<1 10

Input Frequency F

i

VDD = 3.3 V 12 14.318 16 MHz

Pin Inductance L

p

in

7nH

C

IN

Logic Inputs 5 pF

C

OU

T

Output pin capacitance 6 pF

C

INX

X1 & X2 pins 27 45 pF

Transition time

1

T

trans

To 1st crossing of target frequency 5 ms

Settling time

1

T

s

From 1st crossing to 1% target frequency 5 ms

Clk Stabilization

1

T

STAB

From VDD = 3.3 V to 1% target frequency 5 ms

t

PZH,tPZL

Output enable delay (all outputs) 1 10 ns

t

PHZ,tPLZ

Output disable delay (all outputs) 1 10 ns

1

Guaranteed by design, not 100% tested in production.

Delay

1

mA

mA

Input Capacitance

1

I

DD2.5OP

µ

A

Powerdown Current

Operating Supply

Current

Input Low Current

µ

A

mA

mA

I

DD3.3OP

8

ICS9250-27

Electrical Characteristics - CPU

TA = 0 - 70C; V

DDL

= 2.5 V +/-5%; CL = 10-20 pF (unless otherwise specified)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Impedance R

DSP2B

1

VO = VDD*(0.5) 13.5 22 45 Ω

Output Impedance R

DSN2B

1

VO = VDD*(0.5) 13.5 23 45 Ω

Output High Voltage V

OH2B

IOH = -1 mA 2 V

Output Low Voltage V

OL2B

IOL = 1 mA 0.4 V

V

OH @ MIN

= 1.0 V -27 -68

V

OH @ MAX

= 2.375 V -9 -27

V

OL @ MIN

= 1.2 V 27 54

V

OL @ MAX

= 0.3 V 11 30

Rise Time

1

t

r2B

VOL = 0.4 V, VOH = 2.0 V 0.4 1.1 1.6 ns

Fall Time

1

t

f2B

VOH = 2.0 V, VOL = 0.4 V 0.4 1.1 1.6 ns

V

T

= 1.25 V, 66, 100 MHz 45 50 55

V

T

= 1.25 V, 133 MHz 45 53 55

Skew window

1

t

sk2B

VT = 1.25 V 118 175 ps

Jitter, Cycle-to-cycle

1

t

jcyc-cyc2B

VT = 1.25 V

148 250 ps

1

Guaranteed by design, not 100% tested in production.

%

d

t2B

Duty Cycle

1

mA

mA

Output High Current

Output Low Current

I

OH2B

I

OL2B

Electrical Characteristics - 3V66

TA = 0 - 70C; VDD = 3.3 V +/-5%; CL = 10-20 pF (unless otherwise specified)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Impedance R

DSP1

1

VO = VDD*(0.5) 12 17 55 Ω

Output Impedance R

DSN1

1

VO = VDD*(0.5) 12 18 55 Ω

Output High Voltage V

OH1

IOH = -1 mA 2.4 V

Output Low Voltage V

OL1

IOL = 1 mA 0.55 V

V

OH @ MIN

= 1.0 V -33 -108

V

OH @ MAX

= 3.135 V -9 -33

V

OL @ MIN

= 1.95 V 30 95

V

OL @ MAX

= 0.4 V 29 38

Rise Time

1

t

r1

VOL = 0.4 V, VOH = 2.4 V 0.4 1.2 1.8 ns

Fall Time

1

t

f1

VOH = 2.4 V, VOL = 0.4 V 0.4 1.3 1.8 ns

Duty Cycle

1

d

t1

VT = 1.5 V 45 50 55 %

Skew window

1

t

sk1

VT = 1.5 V 82 175 ps

Jitter, Cycle-to-cycle

1

t

jcyc-cyc1

VT = 1.5 V

123 500 ps

1

Guaranteed by design, not 100% tested in production.

Output High Current

Output Low Current

mA

mA

I

OH1

I

OL1

9

ICS9250-27

Electrical Characteristics - IOAPIC

TA = 0 - 70C; V

DDL

= 2.5 V +/-5%; CL = 10-20 pF (unless otherwise specified)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Impedance R

DSP4B

1

VO = VDD*(0.5) 9 21.5 30 Ω

Output Impedance R

DSN4B

1

VO = VDD*(0.5) 9 23 30 Ω

Output High Voltage V

OH4B

IOH = -1 mA 2 V

Output Low Voltage V

OL4B

IOL = 1 mA 0.4 V

V

OH @ MIN

= 1.0 V -27 -68

V

OH @ MAX

= 2.375 V -9 -27

V

OL @ MIN

= 1.2 V 27 54

V

OL @ MAX

= 0.3 V 11 30

Rise Time

1

t

r4B

VOL = 0.4 V, VOH = 2.0 V 0.4 1.1 1.6 ns

Fall Time

1

t

f4B

VOH = 2.0 V, VOL = 0.4 V 0.4 1.1 1.6 ns

Duty Cycle

1

d

t4B

VT = 1.25 V 45 50 55 %

Jitter, Cycle-to-cycle

1

t

jcyc-cyc4B

VT = 1.25 V

123 500 ps

1

Guaranteed by design, not 100% tested in production.

Output High Current

I

OH4B

mA

Output Low Current

I

OL4B

mA

Electrical Characteristics - SDRAM

TA = 0 - 70C; VDD = 3.3 V +/-5%; CL = 20-30 pF (unless otherwise specified)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Impedance R

DSP3

1

VO = VDD*(0.5) 10 14 24 Ω

Output Impedance R

DSN3

1

VO = VDD*(0.5) 10 18 24 Ω

Output High Voltage V

OH3

IOH = -1 mA 2.4 V

Output Low Voltage V

OL3

IOL = 1 mA 0.4 V

V

OH @ MIN

= 2.0 V -54 -92

V

OH @ MAX

= 3.135 V -16 -46

V

OL @ MIN

= 1.0 V 54 68

V

OL @ MAX

= 0.4 V 29 53

Rise Time

1

t

r3

VOL = 0.4 V, VOH = 2.4 V 0.4 1 1.6 ns

Fall Time

1

t

f3

VOH = 2.4 V, VOL = 0.4 V 0.4 1.5 1.6 ns

Duty Cycle

1

d

t3

VT = 1.5 V 45 52 55 %

Skew window

1

t

sk3

VT = 1.5 V 164 250 ps

1

Guaranteed by design, not 100% tested in production.

mA

mA

Output High Current

Output Low Current

I

OH3

I

OL3

250

Jitter, Cycle-to-cycle

1

t

jcyc-cyc3

ps

V

T

= 1.5 V, 66, 100 MHz

180

10

ICS9250-27

Electrical Characteristics - PCI

TA = 0 - 70C; VDD = 3.3 V +/-5%; CL = 10-30 pF (unless otherwise specified)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Impedance R

DSP1

1

VO = VDD*(0.5) 12 14 55 Ω

Output Impedance R

DSN1

1

VO = VDD*(0.5) 12 18 55 Ω

Output High Voltage V

OH1

IOH = -1 mA 2.4 V

Output Low Voltage V

OL1

IOL = 1 mA 0.55 V

V

OH @ MIN

= 1.0 V -33 -106

V

OH @ MAX

= 3.135 V -14 -33

V

OL @ MIN

= 1.95 V 30 94

V

OL @ MAX

= 0.4 V 29 38

Rise Time

1

t

r1

VOL = 0.4 V, VOH = 2.4 V 0.4 1.3 2 ns

Fall Time

1

t

f1

VOH = 2.4 V, VOL = 0.4 V 0.4 1.4 2 ns

Duty Cycle

1

d

t1

VT = 1.5 V 45 52 55 %

Skew window

1

t

sk1

VT = 1.5 V 304 500 ps

Jitter, Cycle-to-cycle

1

t

jcyc-cyc1

VT = 1.5 V

170 500 ps

1

Guaranteed by design, not 100% tested in production.

Output High Current

I

OH1

mA

Output Low Current

I

OL1

mA

Electrical Characteristics - REF, 48MHz_0 (Pin 25)

TA = 0 - 70C; VDD = 3.3 V +/-5%; CL = 10-20 pF (unless otherwise specified)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Impedance R

DSP5

1

VO = VDD*(0.5) 20 32.6 60 Ω

Output Impedance R

DSN5

1

VO = VDD*(0.5) 20 31 60 Ω

Output High Voltage V

OH15

IOH = -1 mA 2.4 V

Output Low Voltage V

OL5

IOL = 1 mA 0.55 V

V

OH @ MIN

= 1.0 V -29 -54

V

OH @ MAX

= 3.135 V -11 -23

V

OL @ MIN

= 1.95 V 29 54

V

OL @ MAX

= 0.4 V 16 27

Rise Time

1

t

r5

VOL = 0.4 V, VOH = 2.4 V 0.4 1.4 4 ns

Fall Time

1

t

f5

VOH = 2.4 V, VOL = 0.4 V 0.4 1.7 4 ns

Duty Cycle

1

d

t5

VT = 1.5 V 45 53 55 %

Jitter, Cycle-to-cycle

1

t

jcy

c-cyc5

VT = 1.5 V, Fixed clocks 215 500 ps

Jitter, Cycle-to-cycle

1

t

jcyc-cyc5

VT = 1.5 V, Ref clocks

930 1000 ps

1

Guaranteed by design, not 100% tested in production.

Output High Current

I

OH5

mA

Output Low Current

I

OL5

mA

11

ICS9250-27

Electrical Characteristics - 48MHz_1 (Pin 26)

TA = 0 - 70C; VDD = 3.3 V +/-5%; CL = 10-15 pF (unless otherwise specified)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Impedance R

DSP3

1

VO = VDD*(0.5) 10 16.7 24 Ω

Output Impedance R

DSN3

1

VO = VDD*(0.5) 10 18.4 24 Ω

Output High Voltage V

OH3

IOH = -1 mA 2.4 V

Output Low Voltage V

OL3

IOL = 1 mA 0.55 V

V

OH @ MIN

= 2.0 V -54 -82

V

OH @ MAX

= 3.135 V -20 -46

V

OL @ MIN

= 1.0 V 54 95

V

OL @ MAX

= 0.4 V 28 53

Rise Time

1

t

r3

VOL = 0.4 V, VOH = 2.4 V 0.4 1.1 1.6 ns

Fall Time

1

t

f3

VOH = 2.4 V, VOL = 0.4 V 0.4 1.1 1.6 ns

Duty Cycle

1

d

t3

VT = 1.5 V 45 51 55 %

Skew

t

sk3

VT = 1.5 V 116 250 ps

Jitter, Cycle-to-cycle

1

t

jcyc-cyc3B

VT = 1.5 V

196 500 ps

1

Guaranteed by design, not 100% tested in production.

Output High Current

I

OH3

mA

Output Low Current

I

OL3

mA

12

ICS9250-27

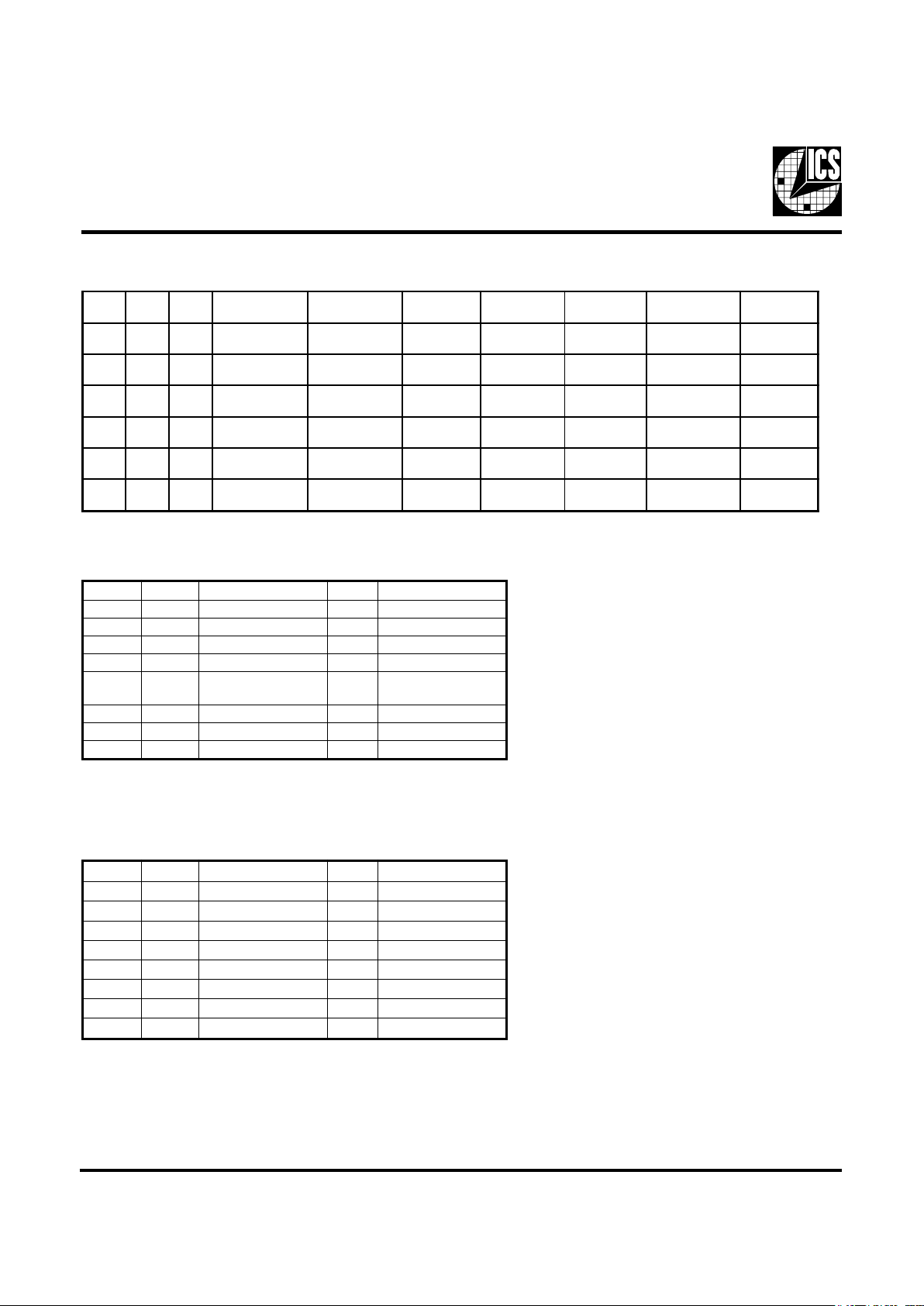

Group Offset Waveforms

Cycle Repeats

0ns

CPU 66MHz

CPU 100MHz

CPU 133MHz

SDRAM 133MHz

SDRAM 100MHz

3.3V 66MHz

PCI 33MHz

IOAPIC 33MHz

REF 14.318MHz

USB 48MHz

10ns 20ns 30ns 40ns

13

ICS9250-27

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for

verification. Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I

2

C interface, the protocol is set to use only "Block-Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I

2

C programming application note.

How to Write:

• Controller (host) sends a start bit.

• Controller (host) sends the write address D2

(H)

• ICS clock will acknowledge

• Controller (host) sends a dummy command code

• ICS clock will acknowledge

• Controller (host) sends a dummy byte count

• ICS clock will acknowledge

• Controller (host) starts sending first byte (Byte 0)

through byte 5

• ICS clock will acknowledge each byte one at a time.

• Controller (host) sends a Stop bit

How to Read:

• Controller (host) will send start bit.

• Controller (host) sends the read address D3

(H)

• ICS clock will acknowledge

• ICS clock will send the byte count

• Controller (host) acknowledges

• ICS clock sends first byte (Byte 0) through byte 5

• Controller (host) will need to acknowledge each byte

• Controller (host) will send a stop bit

Notes:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

A

CK

Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Stop Bit

How to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

A

CK

Dummy Command Code

A

CK

Dummy Byte Count

A

CK

Byte 0

A

CK

Byte 1

ACK

Byte 2

A

CK

Byte 3

A

CK

Byte 4

A

CK

Byte 5

A

CK

Stop Bit

How to Write:

14

ICS9250-27

ADVANCE INFORMATION documents contain information on products

in the formative or design phase development. Characteristic data and

other specifications are design goals. ICS reserves the right to change or

discontinue these products without notice.

Ordering Information

ICS9250yF-27-T

Designation for tape and reel packaging

Pattern Number (2 or 3 digit number for parts with ROM code patterns)

Package Type

F=SSOP

Revision Designator (will not correlate with datasheet revision)

Device Type (consists of 3 or 4 digit numbers)

Prefix

ICS, AV = Standard Device

Example:

ICS XXXX y F - PPP - T

MIN MAX MIN MAX

A 2.413 2.794 .095 .110

A1 0.203 0.406 .008 .016

b 0.203 0.343 .008 .0135

c 0.127 0.254 .005 .010

D

E 10.033 1 0.668 .395 .420

E1 7.391 7.595 .291 .299

e 0.635 BA SIC 0.025 BA SIC

h 0.381 0.635 .015 .025

L 0.508 1.016 .020 .040

N

α

0° 8° 0° 8°

VARIATIONS

MIN MAX MIN MAX

28 9.398

9.652

.370 .380

34 11.303

11.557

.445 .455

48 15.748

16.002

.620 .630

56 18.288

18.542

.720 .730

64 20.828

21.082

.820 .830

JEDEC MO-118

DOC# 10-0034

6/ 1/ 00

REV B

SY MBOL

SEE VARIATIONS

SEE VARIATIONS

In Millimet ers

COMMON DIMENSIONS

In In c h es

COMMON DIMENSIONS

SEE VARIATIONS

N

D mm.

D (inch)

SEE VARIATIONS

Loading...

Loading...