ICST AV9248F-72, ICS9248F-72 Datasheet

Integrated

Circuit

Systems, Inc.

General Description Features

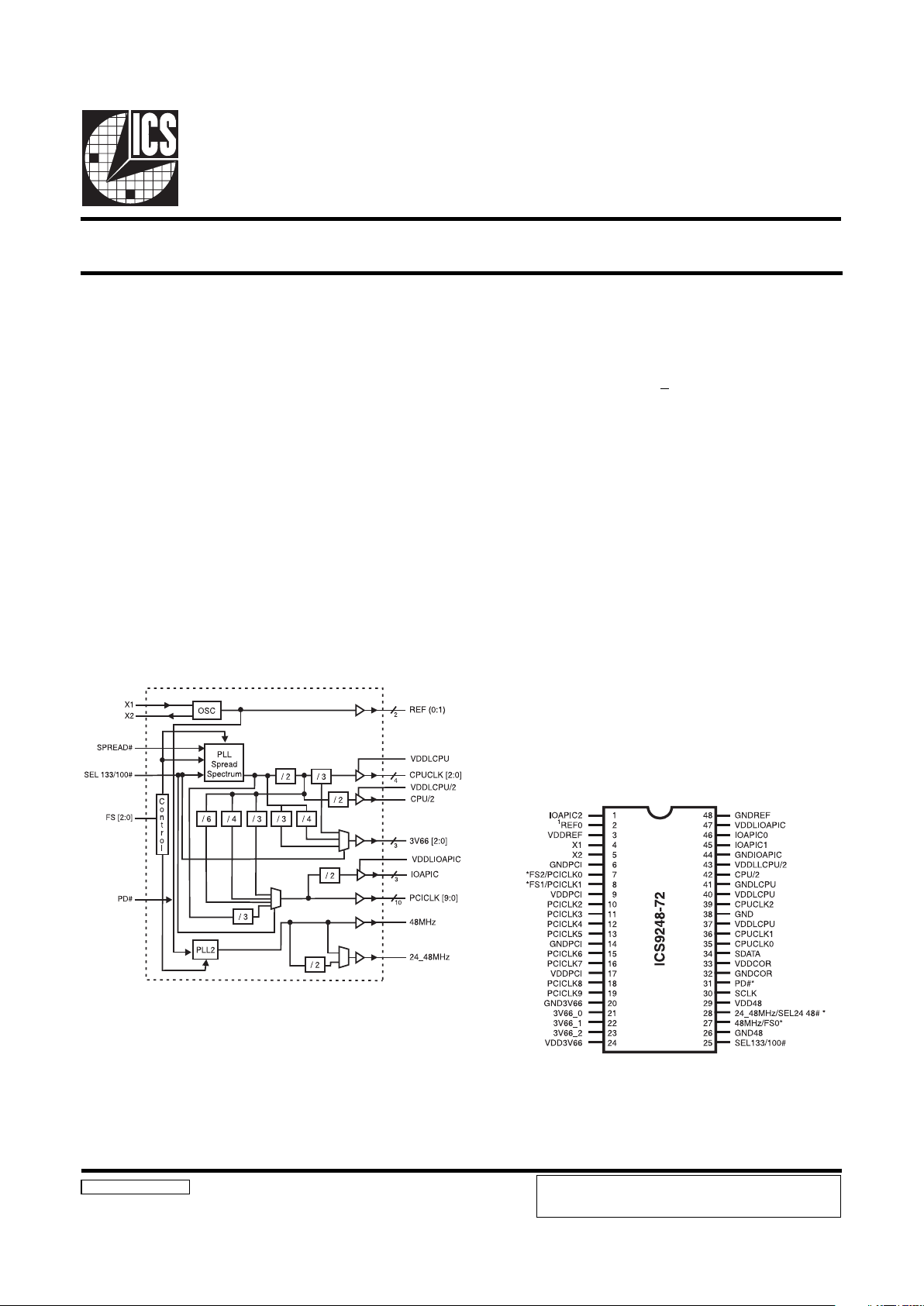

ICS9248-72

Block Diagram

Frequency Timing Generator for PENTIUM II Systems

9248-72 Rev B 7/28/99

Pin Configuration

48-pin SSOP

Up to 200MHz frequency support.

Power Down feature.

Spread Spectrum for EMI control

(0 to 0.5% down spread , + 0.25% center spread)

I2C interface.

VDDL=2.5V,VDD=3.3V

The ICS9248-72 is a main clock synthesizer chip for Pentium

II based systems using Rambus Interface DRAMs. This chip

provides all the clocks required for such a system when used

with a Direct Rambus Clock Generator(DRCG) chip such as

the ICS9211-01.

Spread Spectrum may be enabled by driving the SPREAD#

pin active. Spread spectrum typically reduces system EMI by

8dB to 10dB. This simplifies EMI qualification without resorting

to board design iterations or costly shielding. The ICS9248-

72 employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

The CPU/2 clocks are inputs to the DRCG.

Preliminary Product Preview

* 250K ohm pull-up to VDD on indicated inputs.

1.These pins will have 2X drive strength

Key Specification

CPU Output Jitter: <250ps

CPU/2 Output Jitter. <250ps

IOAPIC Output Jitter: <500ps

48MHz, 3V66, PCI Output Jitter: <500ps

Ref Output Jitter. <1000ps

CPU Output Skew: <175ps

IOAPIC Output Skew <250ps

PCI Output Skew: <500ps

3V66 Output Skew <250ps

CPU to 3V66 Output Offset: 0.0 - 1.5ns (CPU leads)

3V66 to PCI Output Offset: 1.5 - 4.0ns (3V66 leads)

CPU to IOAPIC Output Offset 1.5 - 4.0ns (CPU leads)

PRODUCT PREVIEW documents contain information on new

products in the sampling or preproduction phase of development.

Characteristic data and other specifications are subject to change

without notice.

2

ICS9248-72

Preliminary Product Preview

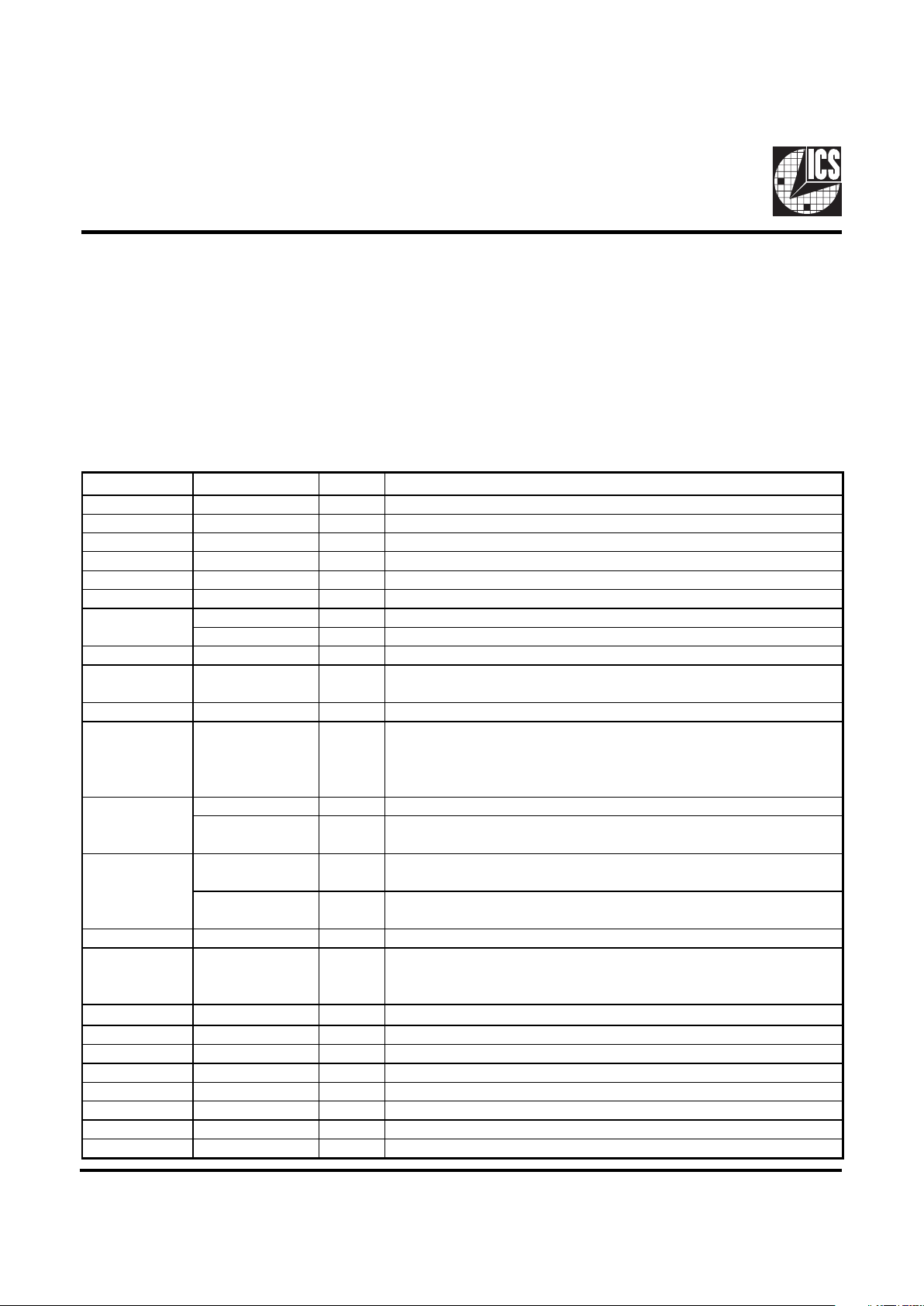

Pin Descriptions

Pin number Pin name Type Description

1, 45, 46 IOA P I C [ 2:0] O utput 2.5V IO AP I C clock ou tputs

2 REF0 O utput 3.3V, 14.318 M Hz re f e r enc e c lock output.

3, 24, 29, 33 VDD Power 3.3 V powe r

4 X 1 Input 14.318 M Hz cry sta l input

5 X 2 O utput 14.318 M Hz cry sta l output

6, 14, 20, 26, 32 GN D P ower G r ound

FS [2:1] IN Fr e quenc y s elect p ins. L atc hed I nputs de ter mins the CP U & P C I f r e quenc ies .

PC I C L K [1:0] O utput 3.3 V PCI clock outputs, ge ne r ating tim ing r equir e ments f or

9,17 VDD PCI Power 3.3 V powe r for the P C I cloc k outputs

19, 18, 16, 15, 13,

12, 11, 10

PC I C L K [9:2] O utput 3.3 V PCI clock outputs

23, 22, 21 3V 66 Outpu t 3.3 V 66 MH z c lock output, f ixe d f r e quenc y cloc k typically us ed with A GP

25 SE L 133/100# Input

control f or the f r eq uency of clocks a t the CPU output pins . I f logic "0" is us ed the

100 MHz fr eq uenc y is s e lecte d. I f L og ic " 1" is used, the 133 M Hz fr e quenc y is

selec ted. T he PCI c lock is multiplexed to run at 33. 3 M Hz for both selected c as e s.

FS0

IN Fr e quenc y s elect p in. L a tched Inputs deter mins the CP U & P C I frequenc ies .

48 MHz O utput

3.3 V 48 MH z clock outpu t, fixed fr eq uenc y clock typic ally us ed with U S B

devices

SEL24/48

IN

48/24 MHz sel ect option. Active low = 48 MHz output. Active High = 24

MHz

24_48MHz#

Output

3.3V 48 or 24 MHz clock output, fixed frequency clock typi cally us ed wi th

USB devices.

30 SC L K I N Clock input of I 2C input

31 PD # Input

As ync hr onous a ctive low input pin used to pow er down the device into a low

power state. The internal clocks are disabled and the VCO and the crystal are

stopped.

34 SDATA IN

D ata in put for I

2

C se r ial input.

36, 35 C P UCL K [1:0] 0 utput 2.5 V CP U and H os t cloc k outputs

37, 40 VDDLCPU Power 2.5 V power for the CPU and Host clock outputs

41 GNDLCPU/2 Power Ground for the CPU a nd Host clock outputs

42 CP U/2 O utput output running at 1/2 C P U clock f r e quenc y. S ync hr onous to the CPU outputs .

43 VDDLCPU/2 Power 2.5 V powe r for the CPU/2 c lock outputs

47 GNDLI OA P IC Pow er Ground f or IOAPIC c locks

48 G NDR E F Power Ground for 14. 318 M Hz re ference cloc k outputs

8, 7

28

27

Power Groups:

VDDREF, GNDREF = REF, X1, X2

GNDPCI, VDDPCI = PCICLK

VDD66, GND66 = 3V66

VDD48, GND48 = 48MHz

VDDCOR, GNDCOR = PLL Core

VDDLCPU/2 , GNDLCPU/2 = CPU/2

VDDLIOAPIC, GNDIOAPIC = IOAPIC

3

ICS9248-72

Preliminary Product Preview

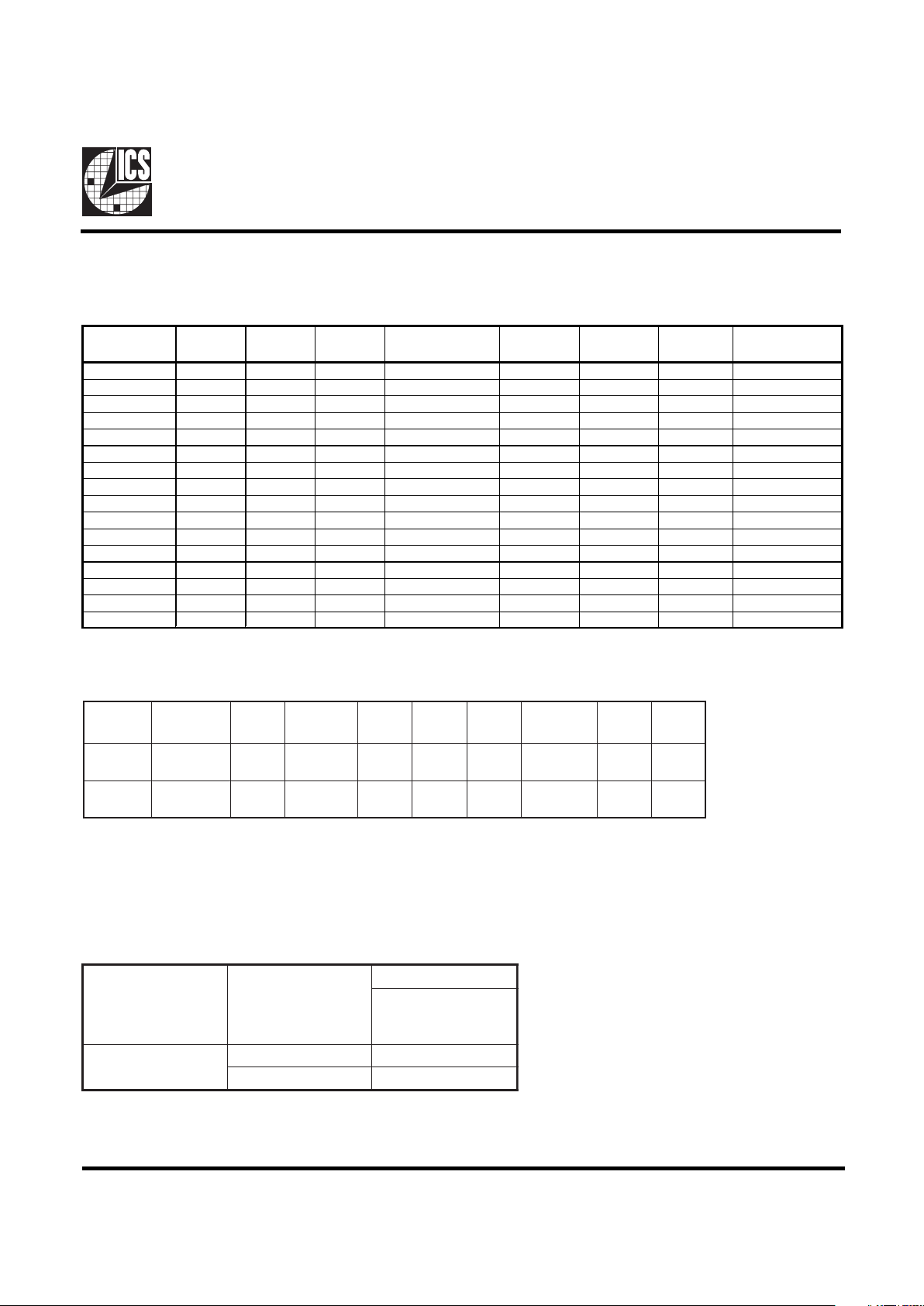

ICS9248-72 Power Management Features:

Note:

1. LOW means outputs held static LOW as per latency requirement next page.

2. On means active.

3. PD# pulled Low, impacts all outputs including REF and 48 MHz outputs.

#DPKLCUPC2/UPCCIPAOI66V3ICPF_ICP

.FER

zHM84

csOsOCV

0WOLWOLWOLWOLWOLWOLWOLFFOFFO

1NONONONONONONONONO

Power Management Requirements:

Note:

1. Clock on/off latency is defined in the number of rising edges of free running PCICLKs between the clock disable goes low/

high to the first valid clock comes out of the device.

2. Power up latency is when PWR_DWN# goes inactive (high to when the first valid clocks are dirven from the device.

lagniSetatSlagniS

ycnetaL

segdegnisirfo.oN

KLCICPfo

#DP

)noitarepolamron(1Sm3

)nwodrewop(0.xam2

Functionality

VDD = 3.3V±5%, V

DDL

= 2.5V ±5% TA= 0 to 70°C

Crystal (X1, X2) = 14.31818MHz

SEL133/100#

FS2

(MHz)

FS1

(MHz)

FS0

(MHz)

CPU

(MHz)

CPU/2

(MHz)

PCI

(MHz)

3V66

(MHz)

IOAPIC

(MHz)

1111

133.30 66.65 33.325 66.65 16.66

1

1

10

138.01 69.01 34.505 69.01 17.25

1

1

01

142.91 71.45 35.725 71.45 17.86

1

10

0

147.95 73.98 36.99 73.98 18.49

1011

152.49 76.24 38.12 76.24 19.06

1010

156.99 78.49 39.245 78.49 19.62

1001

162.02 81.01 40.505 81.01 20.25

1000

180.00 89.99 30.00 60.00 15.00

0111

100.23 50.11 33.405 66.81 16.70

0110

105.00 52.49 35 70.00 17.50

0101

113.99 56.99 37.83 75.66 18.91

0100

120.00 59.99 40.00 80.00 20.00

0011

128.51 64.25 32.125 64.25 16.06

0010

200.01 1 00.00 33.33 66.66 16.66

0001

170.03 85.01 28.33 56.66 14.16

0000

66.82 33.40 33.40 66.80 16.7

4

ICS9248-72

Preliminary Product Preview

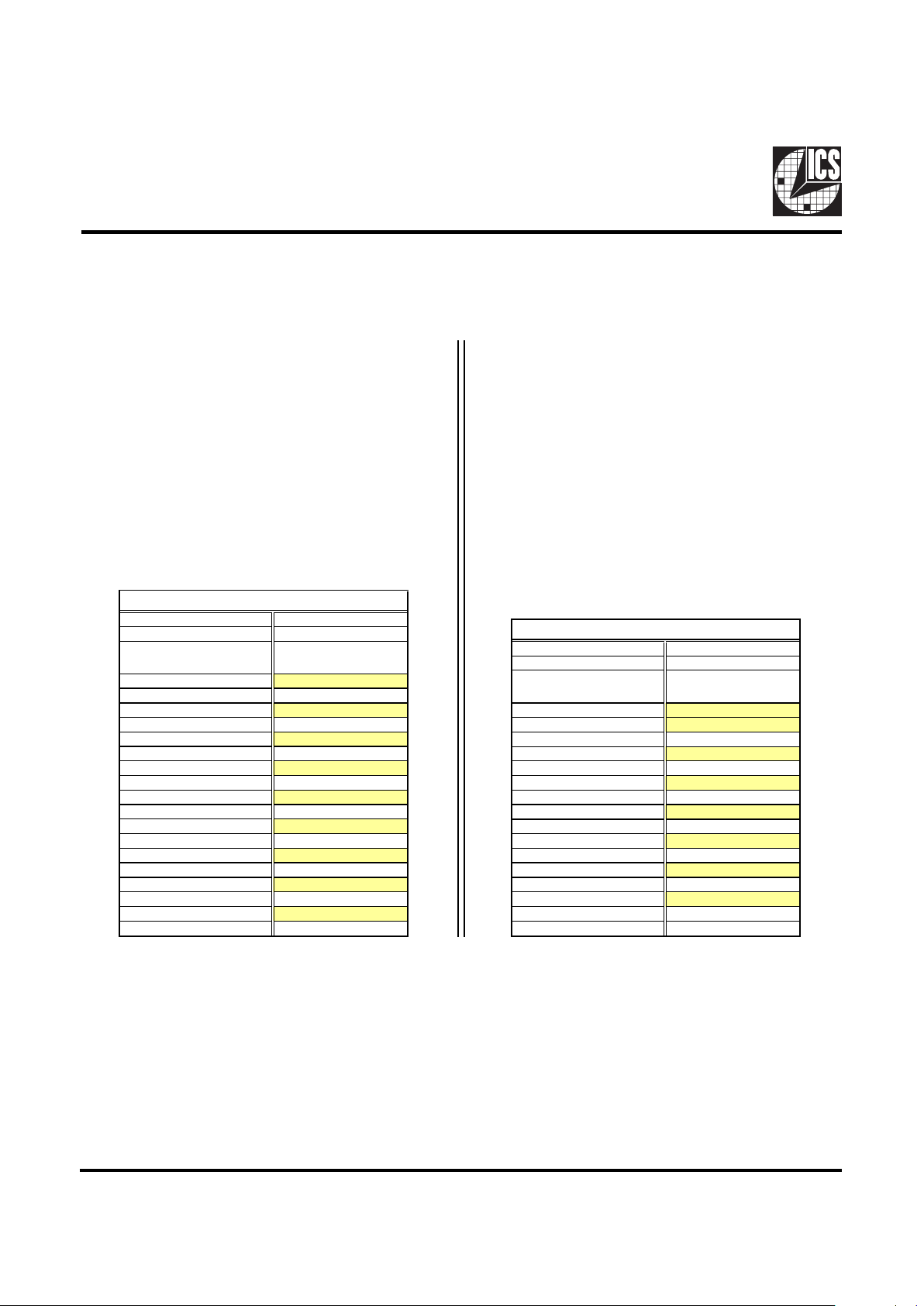

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for verification.

Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I2C interface, the protocol is set to use only "Block-Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I2C programming application note.

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

(H)

ICS clock will acknowledge

Controller (host) sends a dummy command code

ICS clock will acknowledge

Controller (host) sends a dummy byte count

ICS clock will acknowledge

Controller (host) starts sending first byte (Byte 0)

through byte 5

ICS clock will acknowledge each byte one at a time.

Controller (host) sends a Stop bit

How to Read:

Controller (host) will send start bit.

Controller (host) sends the read address D3

(H)

ICS clock will acknowledge

ICS clock will send the byte count

Controller (host) acknowledges

ICS clock sends first byte (Byte 0) through byte 5

Controller (host) will need to acknowledge each byte

Controller (host) will send a stop bit

Notes:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

AC

K

Byte Coun

t

ACK

Byte

0

ACK

Byte 1

ACK

Byte

2

ACK

Byte

3

ACK

Byte

4

ACK

Byte

5

ACK

Stop Bit

How to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

AC

K

Dummy Command Code

AC

K

Dummy Byte Count

AC

K

Byte 0

AC

K

Byte 1

AC

K

Byte 2

ACK

Byte 3

AC

K

Byte 4

AC

K

Byte 5

AC

K

Stop Bit

How to Write:

Loading...

Loading...