Integrated

Circuit

Systems, Inc.

General Description Features

ICS9248-64

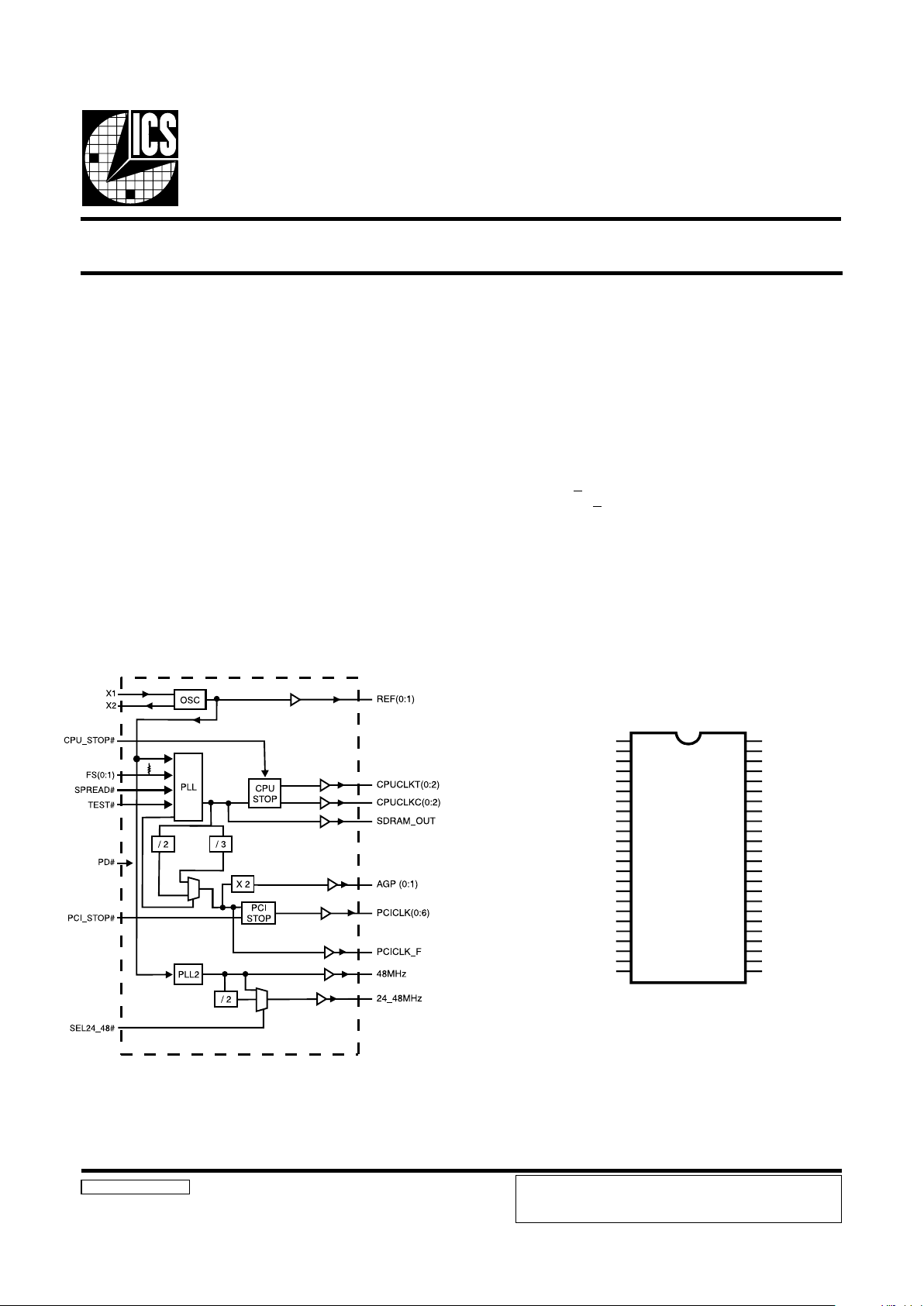

Block Diagram

9248-64 Rev C 03/19/01

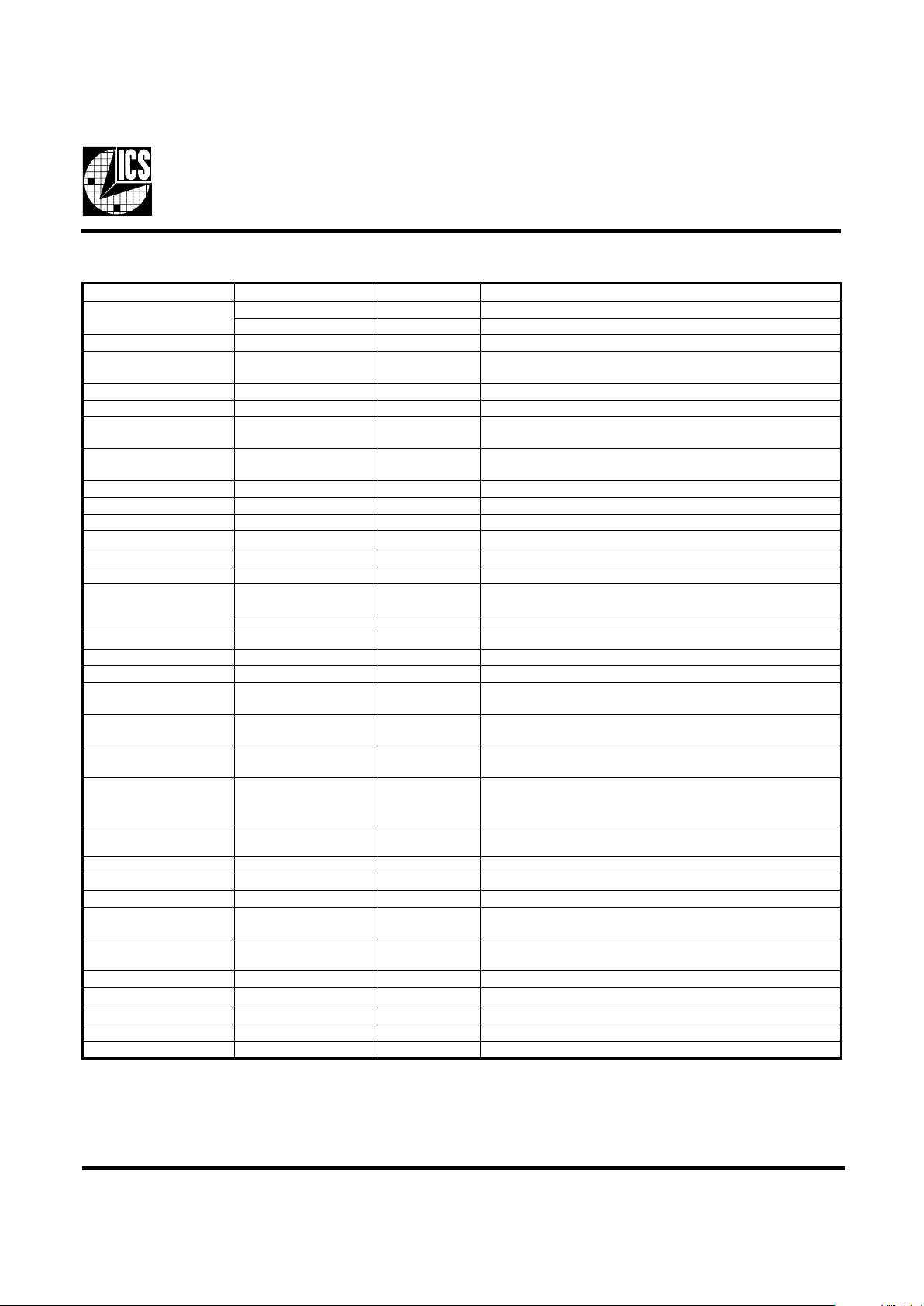

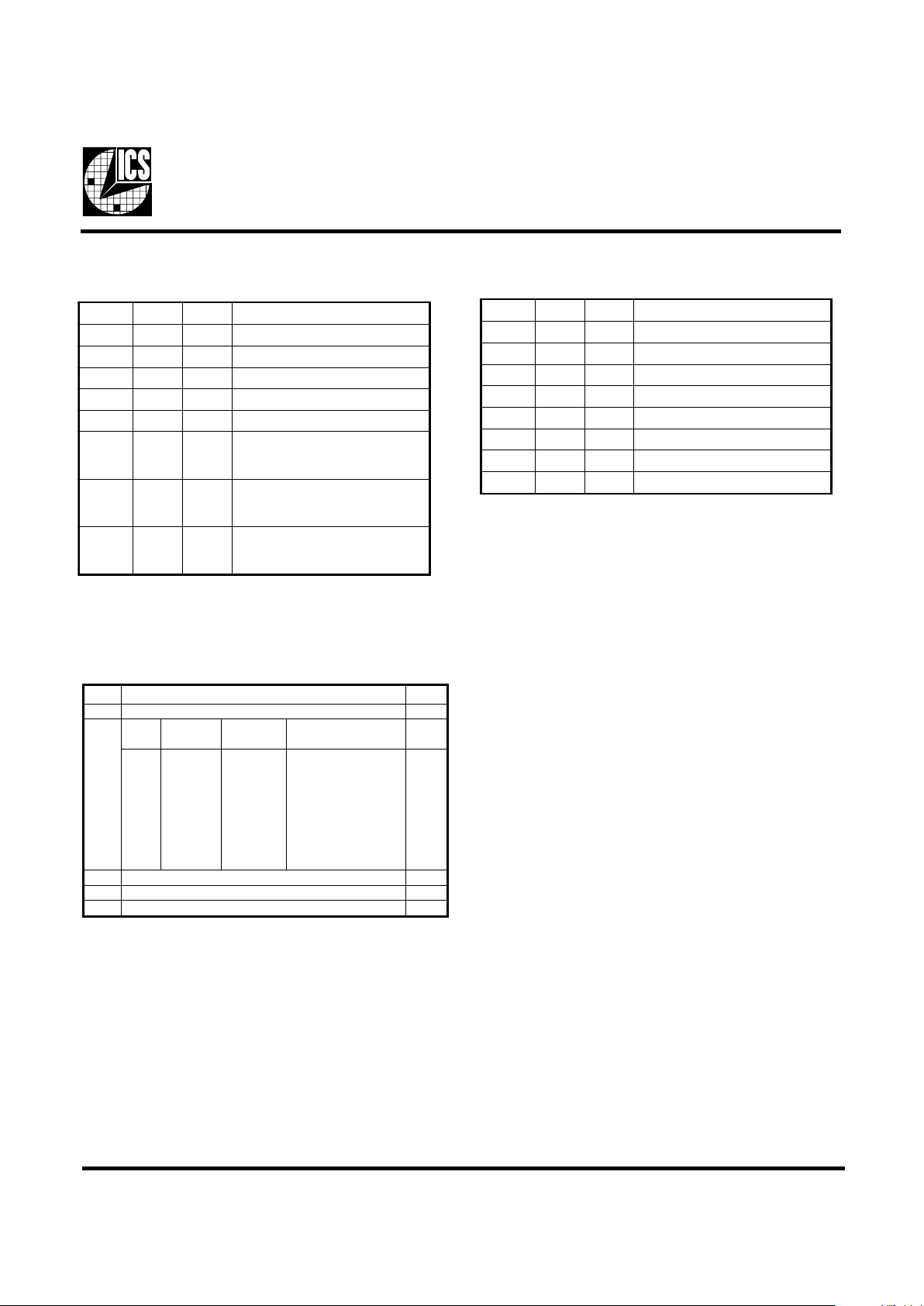

Pin Configuration

48-Pin SSOP

AMD-K is a trademark of Advanced Micro Devices.

• Generates the following system clocks:

- 3 differential pair open drain CPU clocks

(1.5V external

pull-up; up to 133MHz).

- 8 PCI including 1 free running (3.3V) @33.3MHz.

- 2 A GP(3.3V) up to 66.6MHz.

- 2 REF(3.3V)@14.318MHz

- 1 48MHz(3.3V)

- 24 / 48MHz(3.3V)

• Skew characteristics:

- CPU -CPU<250ps

- CPUt - CPUc <200ps (differential pair)

- PCI – PCI: <500ps

- CPU – SDRAM_OUT: < 250ps

- CPU – A GP <500ps

• Efficient Power Management through PD#, PCI_STOP#

and CPU_STOP#.

• Spread Spectrum option for EMI reduction

(-1.0% down spread).

• Uses external 14.318 MHz crystal

The ICS9248-64 is a main clock synthesizer chip for AMDK7 based systems. This provides all clocks required for such

a system when used with a Zero Delay Buffer Chip such as

the ICS9179-06.

Spread Spectrum may be enabled by driving the SPREAD#

pin active. Spread spectrum typically reduces system EMI by

8dB to 10dB. This simplifies EMI qualification without

resorting to board design iterations or costly shielding. The

ICS9248-64 employs a proprietary closed loop design, which

tightly controls the percentage of spreading over process and

temperature variations.

*FS0/REF0

*FS1/REF1

GNDREF

X1

X2

GNDPCI

PCICLK_F

PCICLK0

VDDPCI

PCICLK1

PCICLK2

GNDPCI

PCICLK3

PCICLK4

VDDPCI

PCICLK5

PCICLK6

VDDAGP

AGP0

AGP1

GNDAGP

VDD48

48MHz

SEL24_48#/24-48MHz

VDDREF

GNDSD

SDRAM_OUT

VDDSD

RESERVED

CPUCLKC2

CPUCLKT2

GNDCPU

CUCLKC1

CPUCLKT1

GND

CPUCLKC0

CPUCLKT0

RESERVED

VDD

GND

PCI_STOP#

CPU_STOP#

PD#

SPREAD#

TEST#

SDATA

SCLK

GND48

ICS9248-64

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

{

I

C

2

AMD-K7TM System Clock Chip

* Internal 120K pullup resistor on indicated inputs

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9248-64

Pin Descriptions

REBMUNNIPEMANNIPEPYTNOITPIRCSED

2,1

)1:0(SFNIDDVotpu-llupsah,sniptceleSycneuqerF

)1:0(FERTUOtuptuokcolczHM813.41

3FERDNGRWPstuptuoFERrofdnuorG

41XNI

daolFp33lanretnisah,tupnilatsyrCzHM813.41NI_LATX

2Xmorfrotsiserkcabdeefdnapac

52XTUOFp33pacdaollanretnisah,tuptuolatsyrCTUO_LATX

21,6ICPDNGRWPstuptuoICProfdnuorG

7F_KLCICPTUO

#POTS_ICPehtybdetceffatoN.tuptuoICPgninnuReerF

.tupni

,31,11,01,8

71,61,41

)6:0(KLCICPTUOV3.3elbitapmocLTT.stuptuokcolcICP

51,9ICPDDVRWPV3.3yllanimon,stuptuoKLCICProfrewoP

81PGADDVRWPV3.3yllanimon,stuptuoPGArofrewoP

02,91)1:0(PGATUO.deppotsebtonyamesehT.ICPX2sadenifedstuptuoPGA

12PGADNGRWPstuptuokcolcPGArofdnuorG

2284DDVRWPV3.3yllanimonstuptuoCDF,BSUrofrewoP

32zHM84TUOtuptuozHM84

42

#84-42LESNI

42niproftuptuozHM84ro42stceleS

zHM42=hgiHzHM84=woL

zHM84-42TUO#84-42LEShguorhtelbatcelestuokcolcdexiF

5284DNGRWPstuptuozHM84rofdnuorG

62KLCSNIIroftupnikcolC

2

C

72ATADSNIIroftupniataD

2

C

82#TSETNI

wolnehwedomtsetroetatSirT

)elbatycneuqerfotreferesaelp(

92#DAERPSNI

daerpSnwoD.WOLnehwerutaefmurtcepSdaerpSselbanE

zHK05=ycneuqerfnoitaludom%5.0

03#DPNI

erastuptuolla&LLPlanretnI.wolevitca,pihcnwodsrewoP

.delbasid

13#POTS_UPCNI

saerehwWOLnevirdsi)2:0(TKLCUPC.sKLCUPCstlaH

detressasinipsihtnehwHGIHnevirdsi)2:0(CKLCUPC

.)WOLevitcA(

23#POTS_ICPNI

F_KLCICP.wolnevirdnehwlevel"0"cigoltasuBICPstlaH

nipsihtybdetceffatonsi

33DNGRWPerocrofdnuorgdetalosI

43DDVRWPV3.3yllanimon,erocrofrewopdetalosI

44,53DEVRESERC/NliarrewopUPCerutruF

,24,93,63)2:0(TKLCUPCTUO

nepoesehT.stuptuoUPCriaplaitnereffidfoskcolc"eurT"

.pu-llupV5.1lanretxenadeenstuptuoniard

34,04,73)2:0(CKLCUPCTUO

esehT.tuptuoUPCriaplatnereffidfoskcolc"yrotnemelpmoC"

.pu_llupV5.1lanretxenadeenstuptuoniardnepo

14,83UPCDNGRWP.stuptuoKLCUPCrofdnuorG

54DSDDVRWPV3.3yllanimroN.nipTUO_MARDSrofrewoP

64TUO_MARDSTUOreffubyaledorezMARDSrofkcolcecnerefeR

74DSDNGRWPsnipTUO_MARDSrofdnuorG

84FERDDVRWPV3.3yllanimon,2X,1X,)1:0(FERrofrewoP

3

ICS9248-64

Notes:

1. TCLK is a test clock driven on the X1 (crystal in pin) input during test mode.

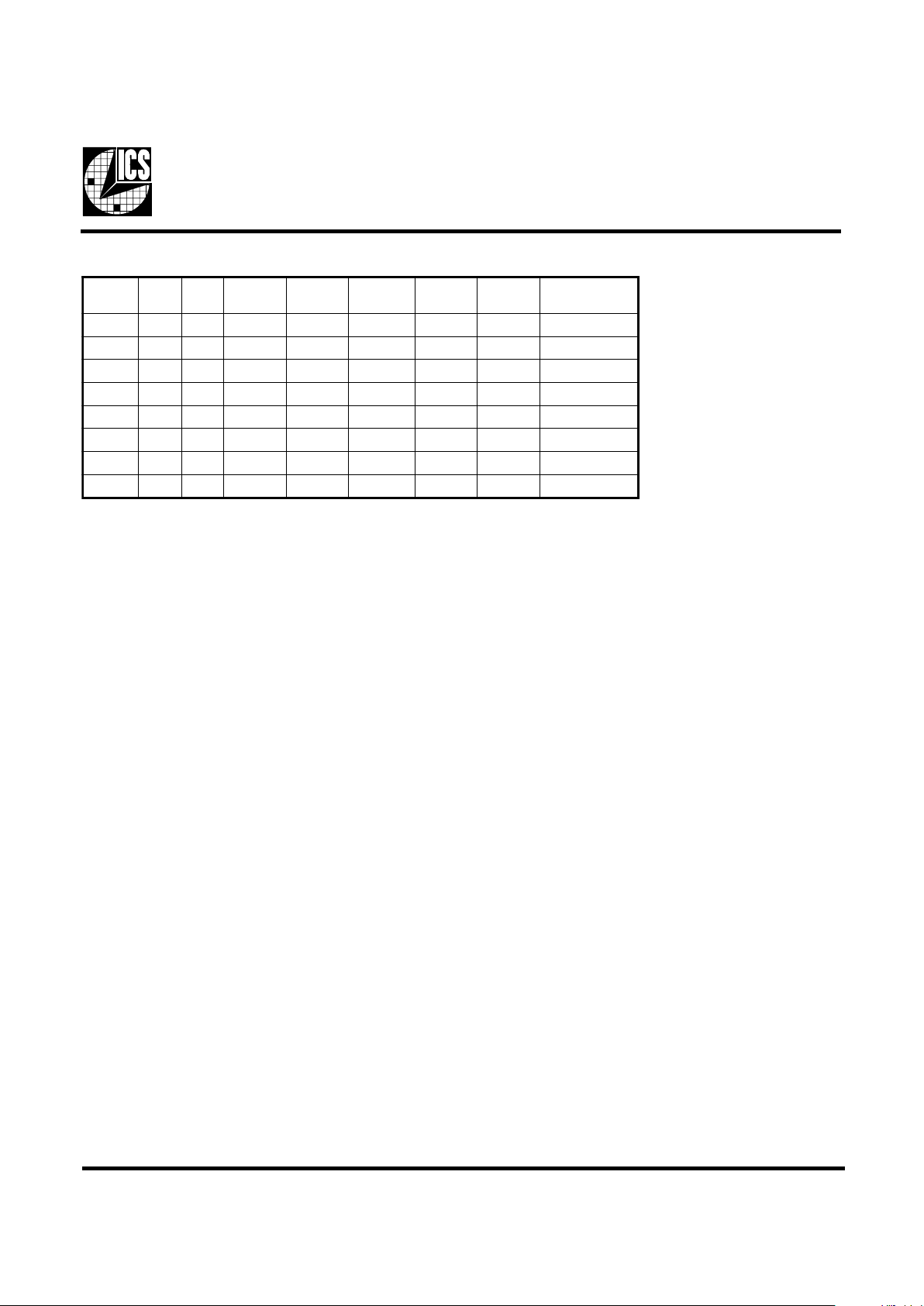

Frequency Select

#TSET1SF0SF

,UPC

MARDS

ICPPGAzHM84FERstnemmoC

000 Z-iHZ-iHZ-iHZ-iHZ-iHetats-irT

001 0.050.520.0584813.41

010 6.663.336.6684813.41

011 2/KLCT6/KLCT3/KLCT4/KLCTKLCT)1(edomtseT

100 0.090.030.0684813.41

101 3.3313.336.6684813.41

110 0.0210.030.0684813.41

111 0.0013.336.6684813.41

4

ICS9248-64

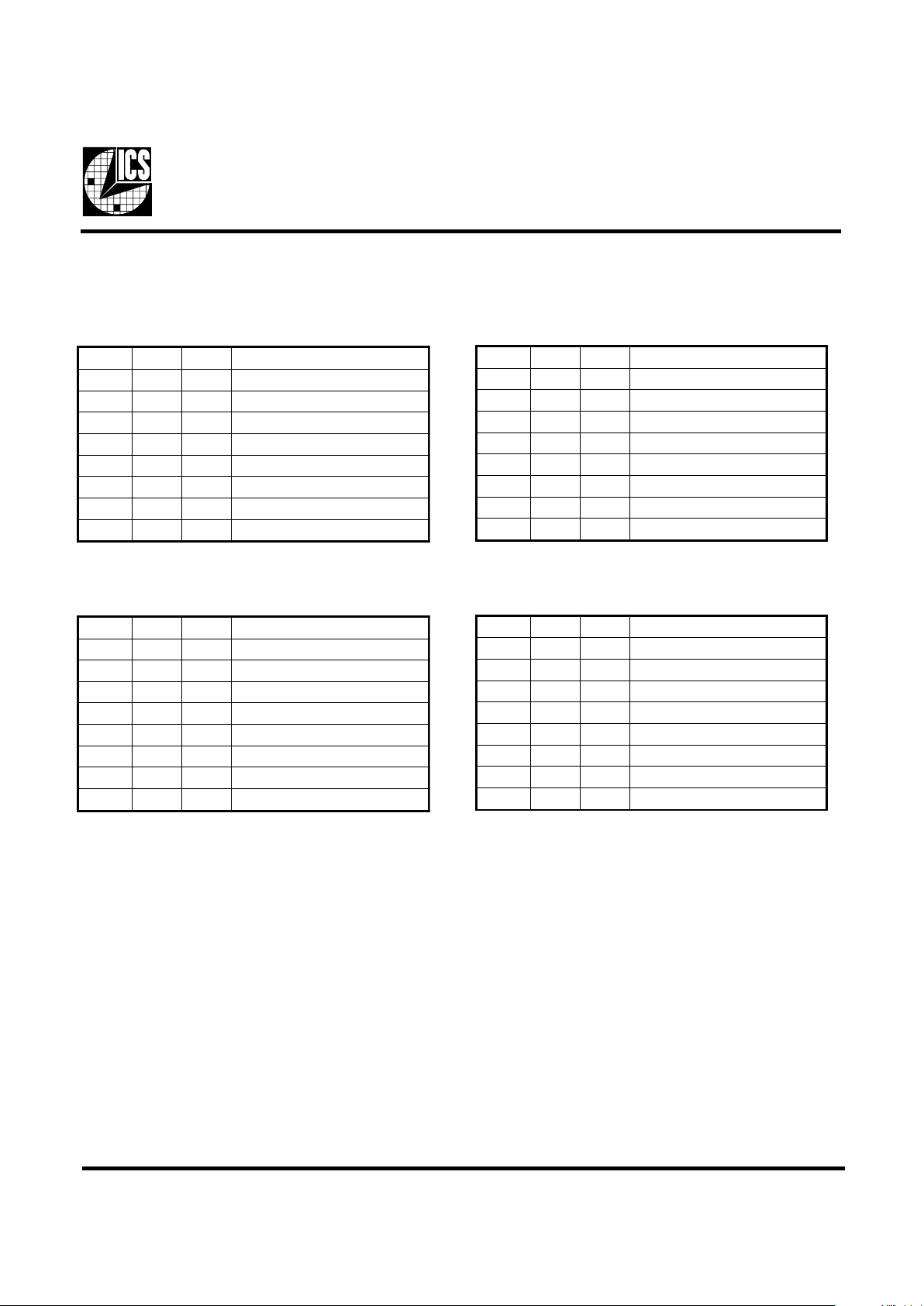

I2C Command Bitmaps

Byte 0: Reserved for Buffer

TIB#NIPDWPNOITPIRCSED

7tiB-1 )reffuBrofdevreseR(

6tiB-1 )reffuBrofdevreseR(

5tiB-1 )reffuBrofdevreseR(

4tiB-1 )reffuBrofdevreseR(

3tiB-1 )reffuBrofdevreseR(

2tiB-1 )reffuBrofdevreseR(

1tiB-1 )reffuBrofdevreseR(

0tiB-1 )reffuBrofdevreseR(

Byte 1: Reserved for Buffer

TIB#NIPDWPNOITPIRCSED

7tiB-1 )reffuBrofdevreseR(

6tiB-1 )reffuBrofdevreseR(

5tiB-1 )reffuBrofdevreseR(

4tiB-1 )reffuBrofdevreseR(

3tiB-1 )reffuBrofdevreseR(

2tiB-1 )reffuBrofdevreseR(

1tiB-1 )reffuBrofdevreseR(

0tiB-1 )reffuBrofdevreseR(

Byte 2: Reserved for Buffer

TIB#NIPDWPNOITPIRCSED

7tiB-1 )reffuBrofdevreseR(

6tiB-1 )reffuBrofdevreseR(

5tiB-1 )reffuBrofdevreseR(

4tiB-1 )reffuBrofdevreseR(

3tiB-1 )reffuBrofdevreseR(

2tiB-1 )reffuBrofdevreseR(

1tiB-1 )reffuBrofdevreseR(

0tiB-1 )reffuBrofdevreseR(

Byte 3: Reserved for Buffer

TIB#NIPDWPNOITPIRCSED

7tiB-1 )reffuBrofdevreseR(

6tiB-1 )reffuBrofdevreseR(

5tiB-1 )reffuBrofdevreseR(

4tiB-1 )reffuBrofdevreseR(

3tiB-1 )reffuBrofdevreseR(

2tiB-1 )reffuBrofdevreseR(

1tiB-1 )reffuBrofdevreseR(

0tiB-1 )reffuBrofdevreseR(

5

ICS9248-64

Byte 4: Clock Control Register

Notes: A value of '1'b is enable, '0'b is disable

Byte 6: SDRAM Clock & Generator Mode Control Register

Notes: A value of '1'b is enable, '0'b is disable

tiBnoitpircseDDWP

7daerpsnwodelbanemurtcepSdaerpS1

4:6

tiB

456

UPCICPegatnecrePdaerpS

111

011

101

001

110

010

100

000

001

021

331

09

2/KLCT

66

05

Z-IH

3.33

03

3.33

03

6/KLCT

33

52

Z-IH

daerpSnwoD%1

daerpSnwoD%1

daerpSnwoD%1

daerpSnwoD%5.0-

daerpSnwoD%1

daerpSnwoD%5.0daerpSnwoD%1

daerpSnwoD%1

1

3:2)devreseR(1

1I

2

elbaneC1

0elbanETUO_MARDS1

TIB#NIPDWPNOITPIRCSED

711 elbane0FER

6421 elbanezHM84/zHM42

5321 elbanezHM84

4021 elbane1PGA

3911 elbane0PGA

234,241

fohtob(elbane2KLCUPC

dna"eurT,riaplaitnereffid

"yratnemilpmoC"

104,931

fohtob(elbane1KLCUPC

dna"eurT,riaplaitnereffid

"yratnemilpmoC"

073,631

fohtob(elbane0KLCUPC

dna"eurT,riaplaitnereffid

"yratnemilpmoC"

Byte 5: PCI Clock Control Register

Notes: A value of '1'b is enable, '0'b is disable

TIB#NIPDWPNOITPIRCSED

721 elbane1FER

6711 elbane6KLCICP

5611 elbane5KLCICP

4411 elbane4KLCICP

3311 elbane3KLCICP

2111 elbane2KLCICP

1011 elbane1KLCICP

081 elbane0KLCICP

Loading...

Loading...