ICST AV9248F-61, ICS9248F-61 Datasheet

Integrated

Circuit

Systems, Inc.

General Description Features

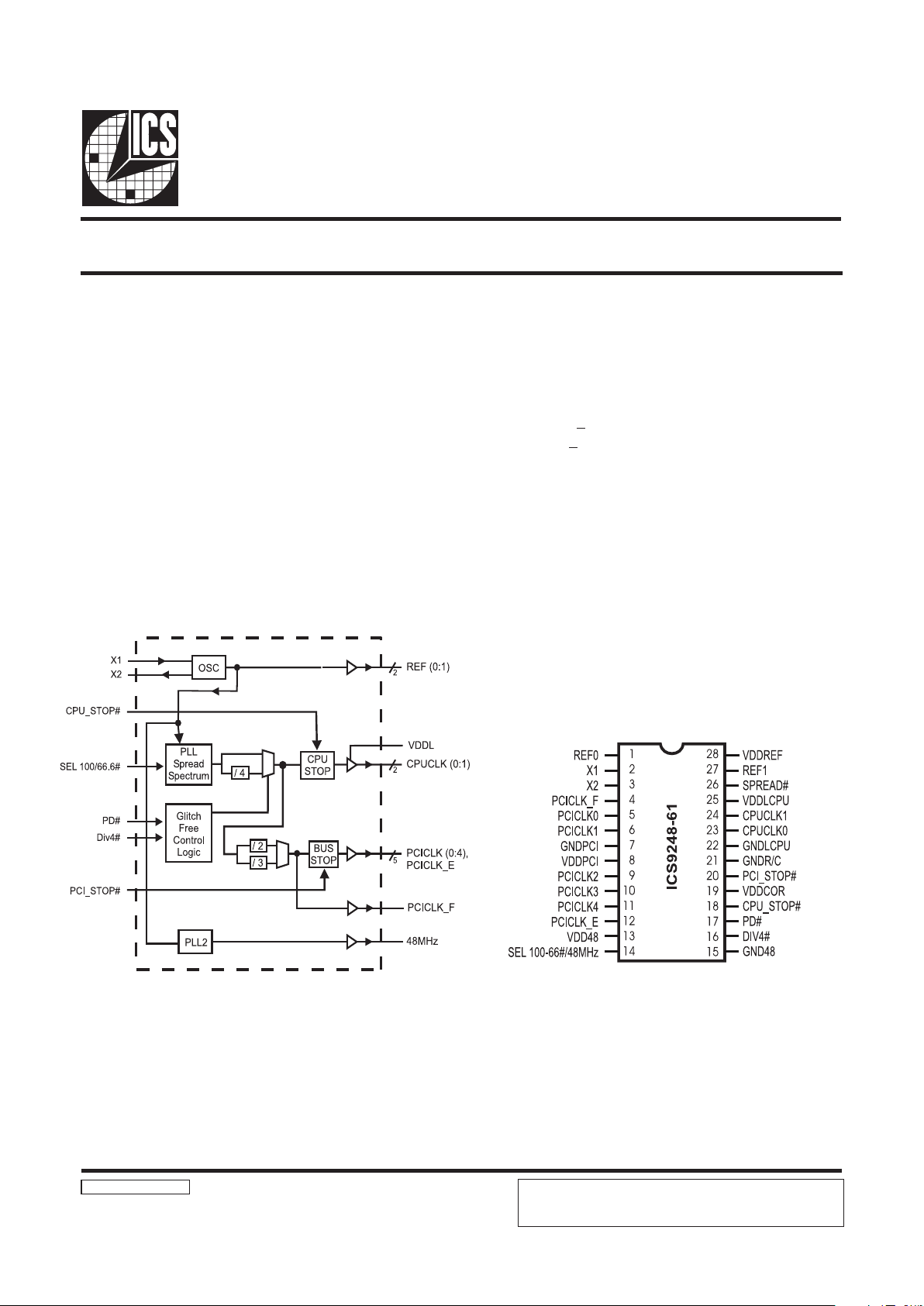

ICS9248-61

Block Diagram

Frequency Timing Generator for Pentium II Systems

9248-61 Rev B 1/8/99

Pin Configuration

28 pin SSOP

Pentium is a trademark on Intel Corporation.

Generates the following system clocks:

- 2CPU(2.5V) up to 100MHz.

- 7 PCI(3.3V) @ 33.3MHz (Includes one free running).

- 2 REF clks Fixed (3.3V) 48MHz at 14.318MHz.

Skew characteristics:

- CPU CPU<175ps

- PCI PCI < 250ps

- PCI_E (early) PCI = 2.1ns

- CPU(early) PCI = 1.5ns 4ns

Supports Spread Spectrum modulation for CPU and PCI

clocks, 0.5% down spread

Efficient Power management scheme through stop clocks

and power down modes.

Uses external 14.318MHz crystal, no external load cap

required for CL=18pF crystal.

28 pin 209mil SSOP.

The ICS9248-61 is the Main clock solution for Notebook

designs using the Intel 440BX style chipset. Along with an

SDRAM buffer such as the ICS9179-03, it provides all

necessary clock signals for such a system.

Spread spectrum may be enabled by driving pin 26, SPREAD#

active (Low) at power-on. Spread spectrum typically reduces

system EMI by 8dB to 10dB. This simplifies EMI qualification

without resorting to board design iterations or costly shielding.

The ICS9248-61 employs a proprietary closed loop design,

which tightly controls the percentage of spreading over

process and temperature variations.

Power Groups

GNDR/C = REFCLK, CORE, Crystal

VDDCOR = Core

GNDLCPU, VDDCPU = CPU

GND48, VDD48 = 48MHz

VDDPCI, GNDPCI - PCICLK, PCICLK_F, PCICLK_E

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9248-61

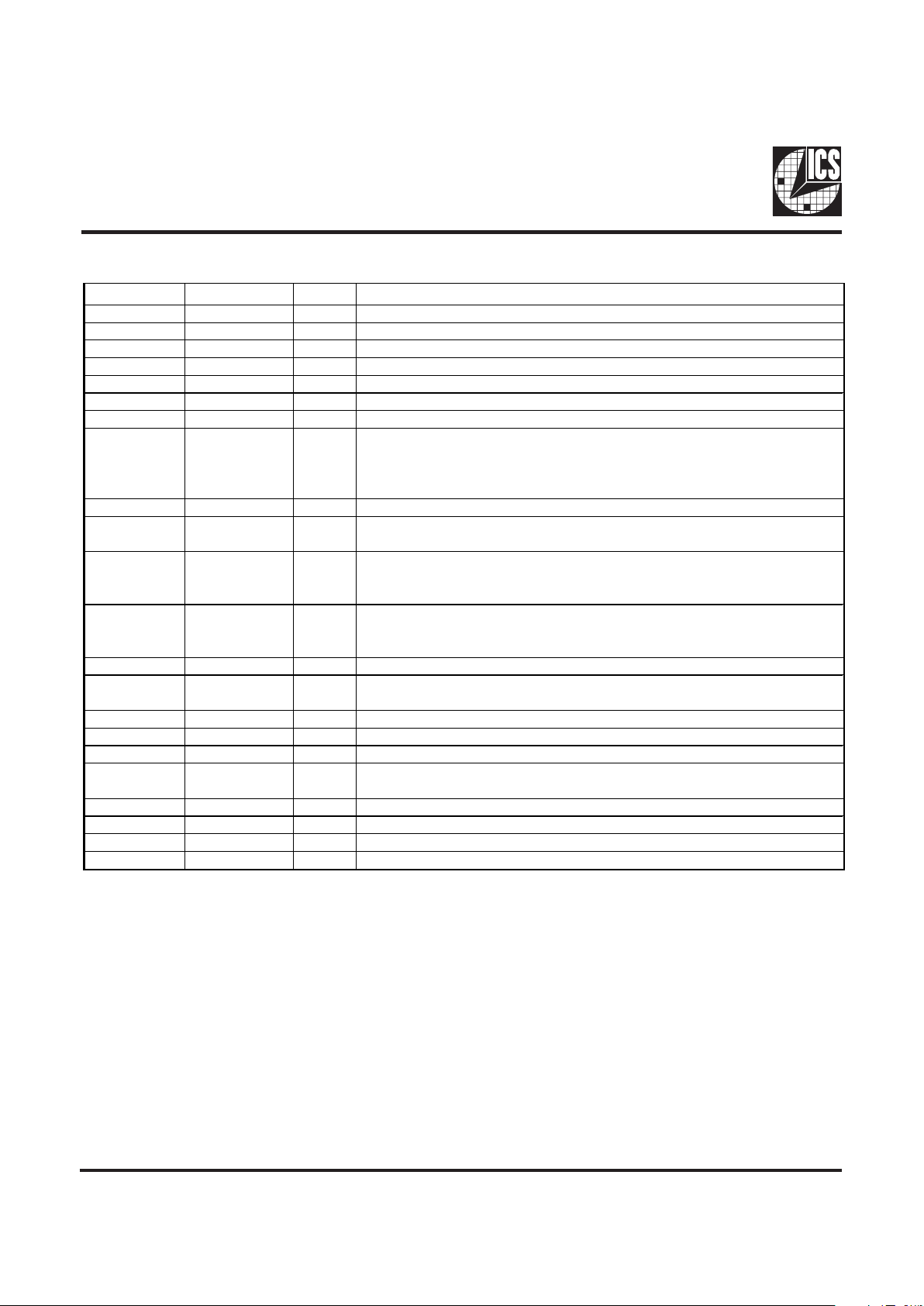

Pin Descriptions

Pin number Pin nam e Type Descripti on

2 X1 Input 14.318 MHz c rystal input

3 X2 Output 14.318 MHz crystal output

4 PCICLK _F Output 3.3 V free running PCI clock output, will not be stopped by the P CI_STOP#

7 GNDPCI Power Ground for PCI c lock output s

8 VDDPCI Power 3. 3 V power for the PCI clock output s

12 PCICLK_E Out put Earl y PCICLK output, offset from ot her P CICLKs, stopped by PCI - STOP#

13 VDD48 Power 3. 3 V power for 48 MHz c locks

14

SEL 100_66#/

48MHz

Input

on power-on cont rol for t he frequency of clocks at the CPU & PCICLK output pins. If

logi c "0" is used the 66.6 MHz frequency i s select ed. If Logic "1" i s used, the 100

MHz f r equency is select ed. The PCI cloc k is mult iplexed to run at 33.3 MHz f or both

selects

15 GND48 Power Ground for 48 MHz cl ocks

16 DIV4# Input

Ac tive low input , enables the CPUCLK and the P CICLK to run at 1/4 of the regular

frequecies

17 PD# Input

As ynchronous act ive l ow i nput pin used to power down the device into a low power

state. The internal clocks are disabled and the VCO and the crystal are stopped. The

latency of the power down will not be greater than 3ms.

18 CPU_ST OP# Input

As ynchronous act ive l ow i nput pin used to stop the CPUCLK i n active low state, all

other clocks will continue to run. The CPUCLK will have a "Turnon " latency of at

least 3 CPU clock s.

19 VDDCOR Input 3.3 V power for the core

20 PCI-S TOP# Input

Sy nchronous acti ve low input used t o stop the PCICLK i n active low state. It wil l not

effect PCICLK_F or any other out puts.

21 GNDR/C Input Ground for REFCLK, Crystal & Core

22 GNDLCPU Power Ground for the CPU and Host clock outputs

25 VDDLCPU Power 2. 5 V power for the CP U and Host clock outputs

26 SPREAD# Output

power-on spread spectrum enable option. Acti ve low = spread spectrum c lock ing

enable. Act ive hi gh = spread s pectrum cloc king disable.

28 VDDR Input 3.3 V power for the REFCLK and crystal clock outputs

1,27 REF(0:1) Output 3.3V , 14. 318 MHz refer ence clock output.

23,24 CPUCLK (0:1) 0utput 2.5 V CPU and Host clock outputs

5,6,9,10, 11 PCICLK (1:4) Output 3.3 V PCI clock outputs, generating t iming requir em ents

3

ICS9248-61

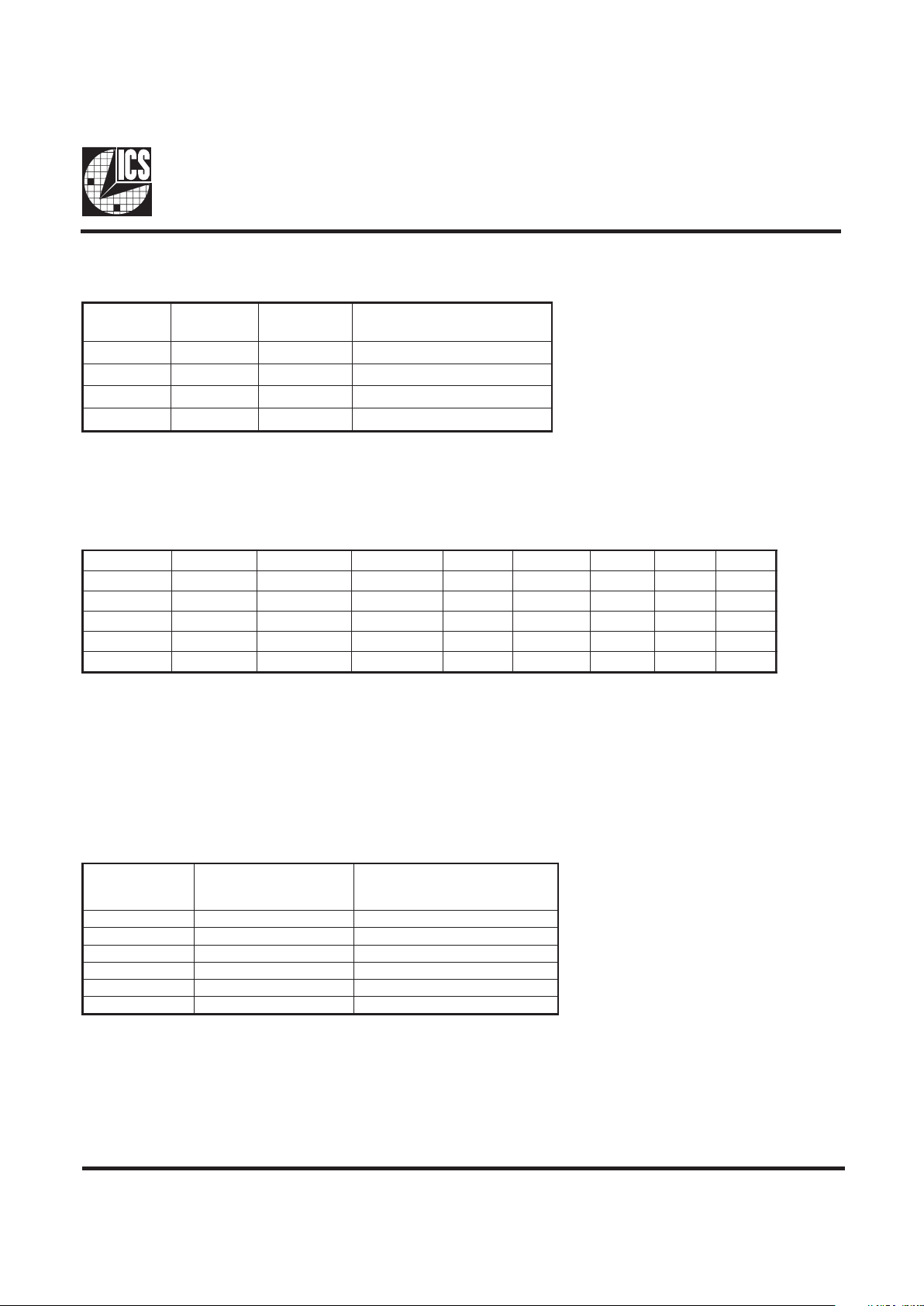

Frequency Table

Power Management

ICS9248-61 Power Management Requirements

Clock Enable Configuration

Full clock cycle timing is guaranteed at all times after the system has initially powered up except where noted. During power

up and power down operations using the PD# pin will not cause clocks of a short or longer pulse than that of the running clock.

The first clock pulse coming out of a stopped clock condition may be slightly distorted due to clock network charging circuitry.

Board routing and signal loading may have a large impact on the initial clock distortion also.

Notes.

1. Clock on latency is defined from when the clock enable goes active to when the first valid clock comes out of the device.

2. Clock off latency is defined from when the clock enable goes inactive to when the last clock is driven low out of the device.

3. Power up latency is when PD# goes inactive (high) to when the first valid clocks are output by the device.

4. Power down has controlled clock counts applicable to CPUCLK, PCICLK only.

The REF will be stopped independant of these.

LANGISETATSLANGIS

ycnetaL

gninnureerffosegdegnisirfo.oN

KLCICP

#POTS_UPC)delbasiD(0

2

1

)delbanE(1

1

1

#POTS_ICP)delbasiD(0

2

1

)delbanE(1

1

1

#DP)noitarepOlamroN(1

3

sm3

)nwoDrewoP(0

4

xam2

#POTS_UPC#POTS_ICP#NWD_RWPKLCUPCKLCICPF_KLCICPFERlatsyrCsOCV

XX 0 woLwoLwoLdeppotSffOffO

00 1 woLwoLzHM3.33gninnuRgninnuRgninnuR

011 woLzHM3.33zHM3.33gninnuRgninnuRgninnuR

10 1 zHM6.66/001woLzHM3.33gninnuRgninnuRgninnuR

11 1 zHM6.66/001zHM3.33zHM3.33gninnuRgninnuRgninnuR

#4VID

LES

#66/001

zHMUPCzHMICP

11 00133

10 96.6633

01 5223.8

00 56.6123.8

Loading...

Loading...