ICST AV9248F-153-T, ICS9248F-153-T Datasheet

Integrated

Circuit

Systems, Inc.

ICS9248-153

Third party brands and names are the property of their respective owners.

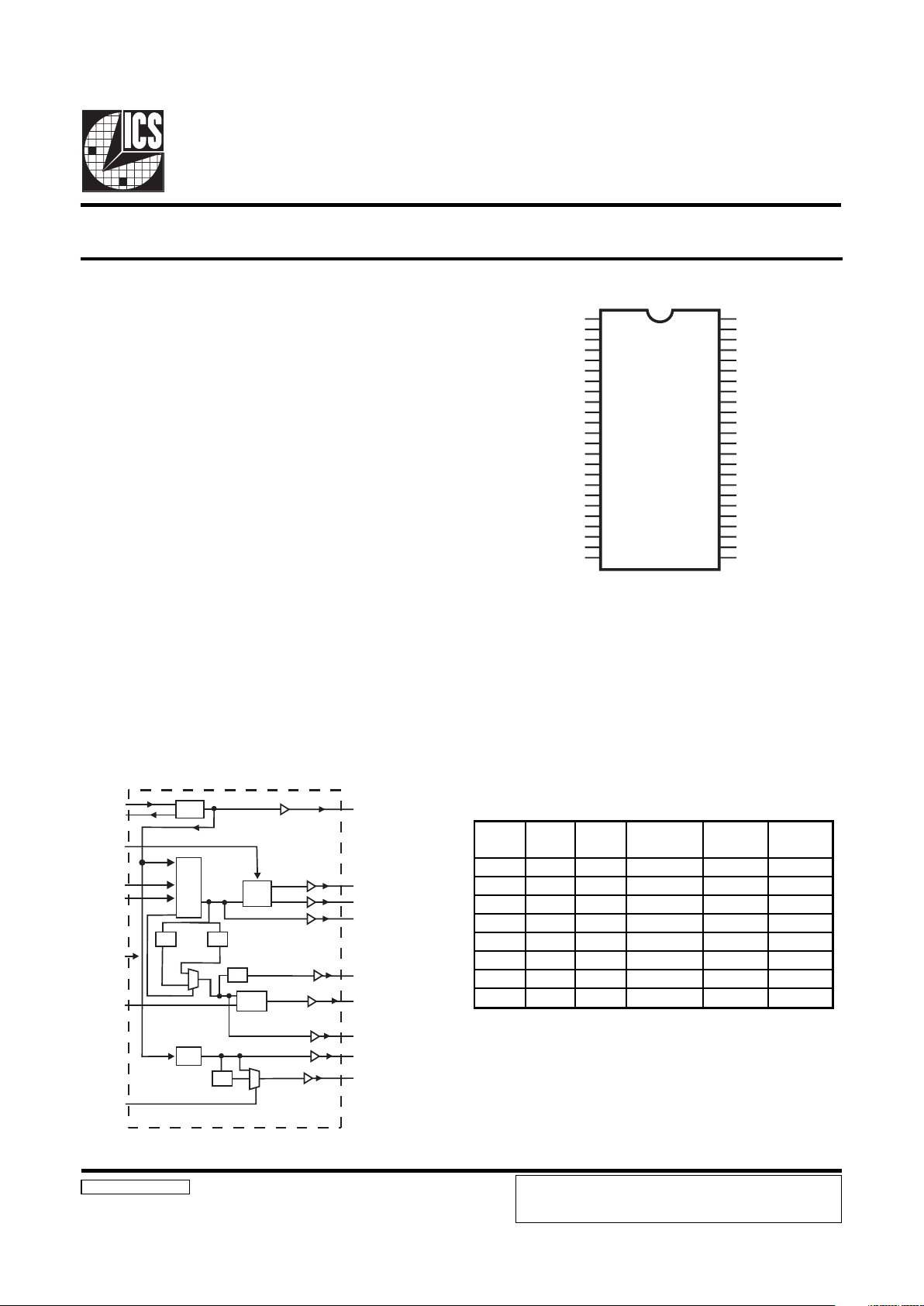

Block Diagram

9248-153 Rev B 5/10/01

Functionality

Pin Configuration

48-Pin 300mil SSOP

Recommended Application:

AMD-K7 (AMD 750, Irongate Chipset)

Output Features:

• 3 differential pair open drain CPU clocks (1.5V external

pull-up; up to 150MHz achieviable through I

2

C)

• 2 - AGPCLK @ 3.3V

• 8 - PCI @3.3V, including 1 free running

• 1 - 48MHz @ 3.3V

• 1 - 24/48MHz @ 3.3V

• 2- REF @3.3V, 14.318MHz.

Features:

• Up to 150MHz frequency support

• Support power management: CPU, PCI, stop and Power

down Mode from I

2

C programming.

• Spread spectrum for EMI control +/-0.25% center spread

• Uses external 14.318MHz crystal

• FS pins for frequency select

Key Specifications:

• CPU – CPU: <200ps

• AGP-AGP: <250ps

• PCI – PCI: <500ps

• CPU - SDRAM_OUT: |250ps|

• CPU-AGP: |250ps|

AMD-K7TM System Clock Chip

* Internal 120K pullup resistor on indicated inputs

** Internal 240K pullup resistor on indicated inputs

**FS0/REF0

**FS1/REF1

GNDREF

X1

X2

GNDPCI

PCICLK_F

PCICLK0

VDDPCI

PCICLK1

PCICLK2

GNDPCI

PCICLK3

PCICLK4

VDDPCI

PCICLK5

PCICLK6

VDDAGP

AGP0

AGP1

GNDAGP

VDD48

48MHz

SEL24_48#/24-48MHz

VDDREF

GNDSD

SDRAM_OUT

VDDSD

RESERVED

CPUCLKC2

CPUCLKT2

GNDCPU

CPUCLKC1

CPUCLKT1

GND

CPUCLKC0

CPUCLKT0

RESERVED

VDD

GND

PCI_STOP#

CPU_STOP#

PD#

SPREAD#

FS2*

S DATA

SCLK

GND48

ICS9248-153

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

FS (2:0)

SPREAD#

CPU_STOP#

X1

X2

OSC

PLL

CPU

STOP

PLL2

REF(1:0)

CPUCLKC(2:0)

CPUCLKT(2:0)

SDRAM_OUT

48MHz

PCICLK (6:0)

24_48MHz

PCICLK_F

PCI_STOP#

SEL24_48#

PD#

/ 2 / 3

PCI

STOP

X 2

/ 2

AGP (1:0)

Power Groups

VDD48, GND48 = 48MHz, PLL2

VDDREF, GNDREF= REF, X1, X2

VDD, GND = PLL Core

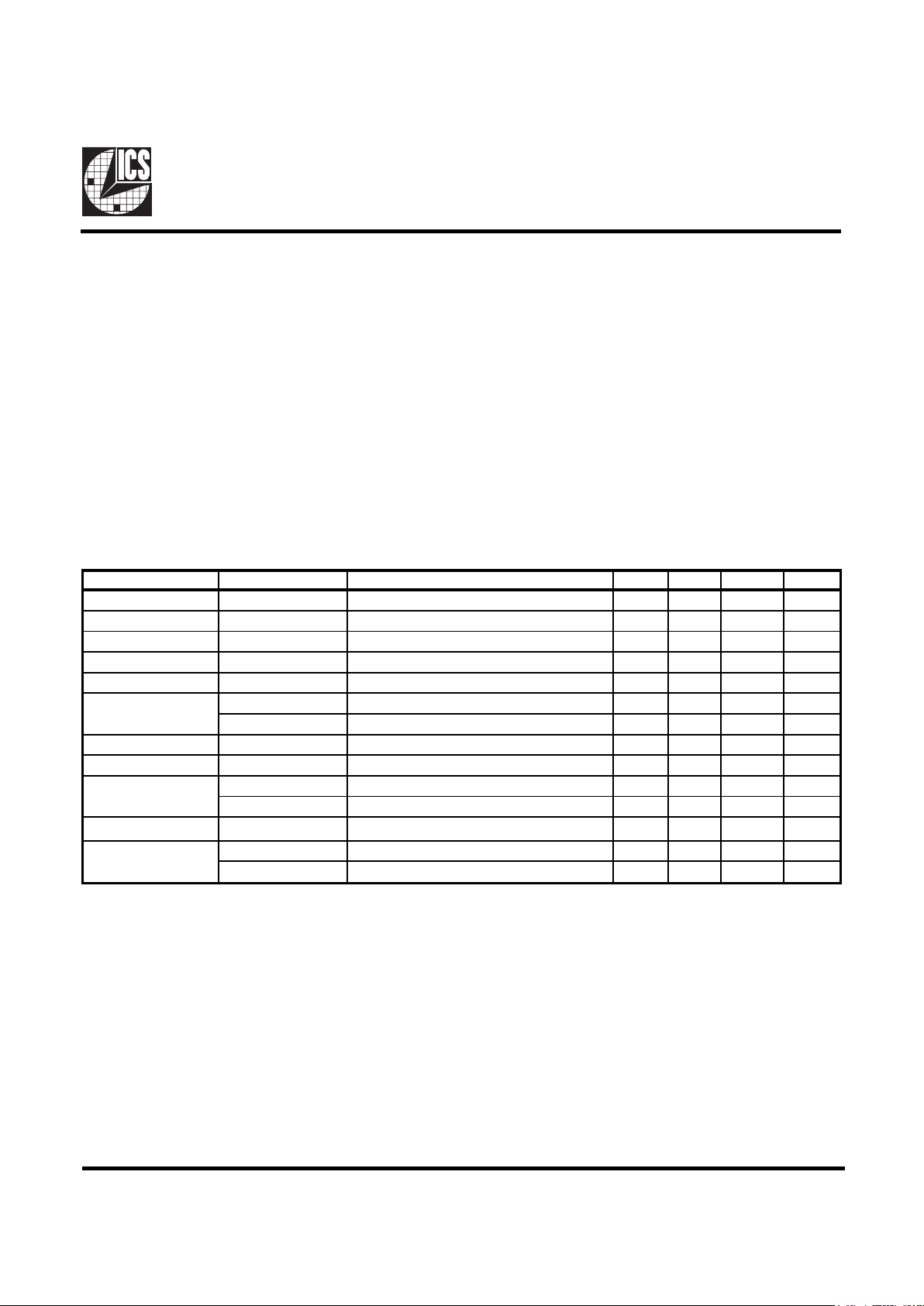

0 0 0 133.33 33.33 66.67

0 0 1 95 31.67 63.33

0 1 0 100.99 33.66 67.33

0 1 1 115 38.33 76.67

1 0 0 100.7 33.57 67.13

1 0 1 103 34.33 68.67

1 1 0 105 35.00 70.00

111

110

36.6

773.

33

PCI AGPFS2 FS1 FS0

CPU

,

SDRAM

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9248-153

Third party brands and names are the property of their respective owners.

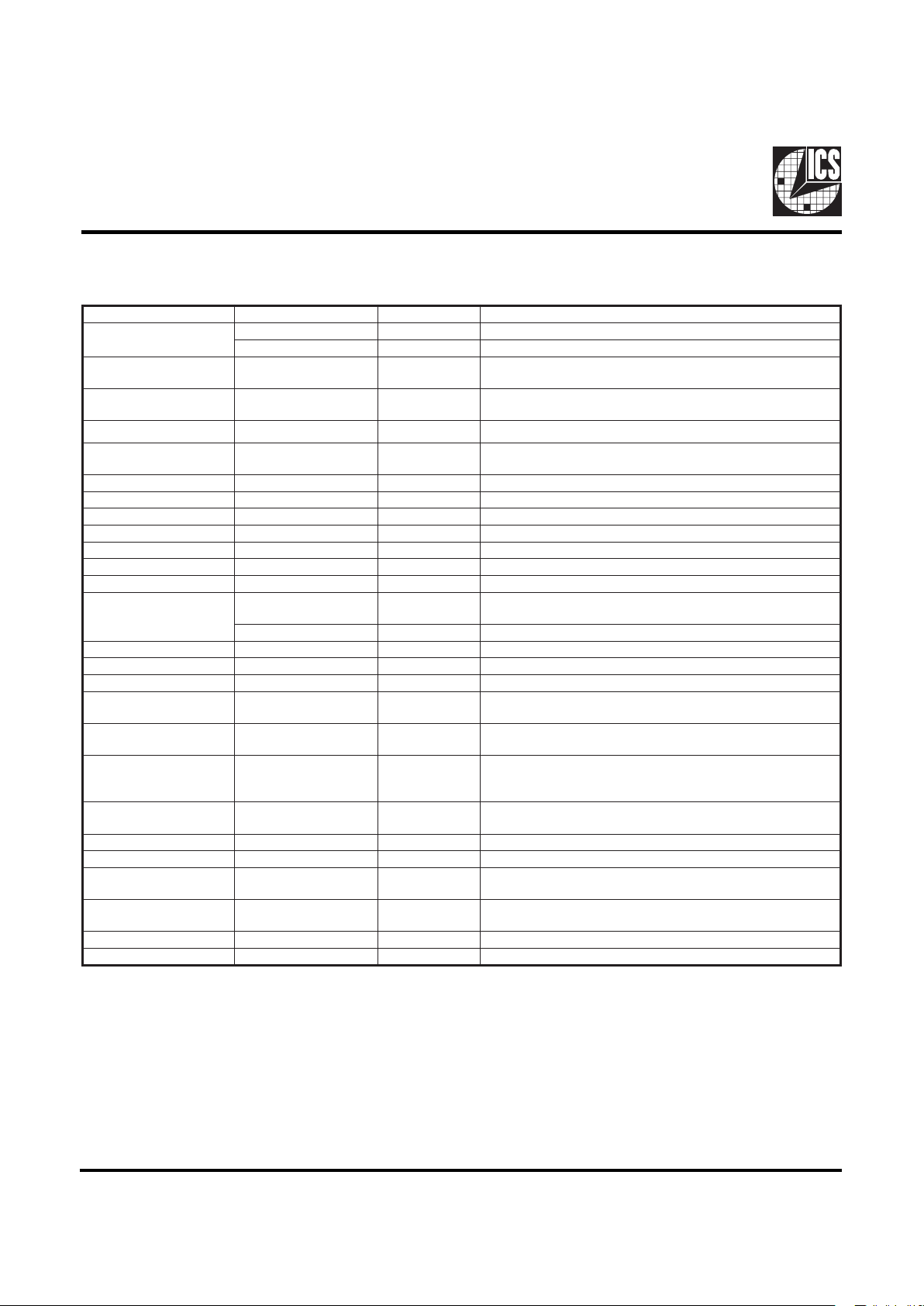

Pin Descriptions

REBMUNNIPEMANNIPEPYTNOITPIRCSED

1,2

)0:1(SFNIDDVotpu-llupsah,sniptceleSycneuqerF

)0:1(FERTUOtuptuokcolczHM813.41

,52,12,6,3

74,14,83,33

DNGRWPdnuorG

41XNI

daolFp33lanretnisah,tupnilatsyrCzHM813.41NI_LATX

2Xmorfrotsiserkcabdeefdnapac

52XTUOFp33pacdaollanretnisah,tuptuolatsyrCTUO_LATX

7F_KLCICPTUO

#POTS_ICPehtybdetceffatoN.tuptuoICPgninnuReerF

.tupni

8,01,11,31,41,61,71)0:6(KLCICPTUOV3.3elbitapmocLTT.stuptuokcolcICP

51,9ICPDDVRWPV3.3yllanimon,stuptuoKLCICProfrewoP

81PGADDVRWPV3.3yllanimon,stuptuoPGArofrewoP

91,02)0:1(PGATUO.deppotsebtonyamesehT.ICPX2sadenifedstuptuoPGA

43DDVRWPV3.3yllanimon,erocrofrewopdetalosI

2284DDVRWPV3.3yllanimonstuptuozHM42dnazHM84rofrewoP

32zHM84TUOtuptuozHM84

42

#84-42LESNI

42niproftuptuozHM84ro42stceleS

zHM42=hgiHzHM84=woL

zHM84-42TUO#84-42LEShguorhtelbatcelestuokcolcdexiF

62KLCSNIIfonipkcolC

2

tnarelotV5yrtiucricC

72ATADSO/IIrofnipataD

2

tnarelotV5yrtiucricC

822SFNIDDVotpu-llupsah,niptceleSycneuqerF

92#DAERPSNI

fodaerpsretneC.WOLnehwerutaefmurtcepSdaerpSselbanE

.%52.0-/+

03#DPNI

stuptuolla&LLPlanretnI.wolevitca,pihcnwodsrewoP

.delbasidera

13#POTS_UPCNI

sarehwWOLnevirdsiTKLCUPC.sKLCUPCstlaH

detressasinipsihtnehwHGIHnevirdsiCKLCUPC

.)WOLevitcA(

23#POTS_ICPNI

F_KLCICP.wolnevirdnehwlevel"0"cigoltasuBICPstlaH

nipsihtybdetceffatonsi

64TUO_MARDSTUOreffubyaledorezMARDSrofkcolcecnerefeR

44,53DEVRESERC/NliarrewopUPCerutuF

63,93,24)0:2(TKLCUPCTUO

nepoesehT.stuptuoUPCriaplaitnereffidfoskcolc"eurT"

.pu-llupV5.1lanretxenadeenstuptuoniard

73,04,34)0:2(CKLCUPCTUO

esehT.tuptuoUPCriaplatnereffidfoskcolc"yrotnemelpmoC"

.pu_llupV5.1lanretxenadeenstuptuoniardnepo

54DSDDVRWPV3.3yllanimroN.nipTUO_MARDSrofrewoP

84FERDDVRWPV3.3yllanimon,2X,1X,FERrofrewoP

3

ICS9248-153

Third party brands and names are the property of their respective owners.

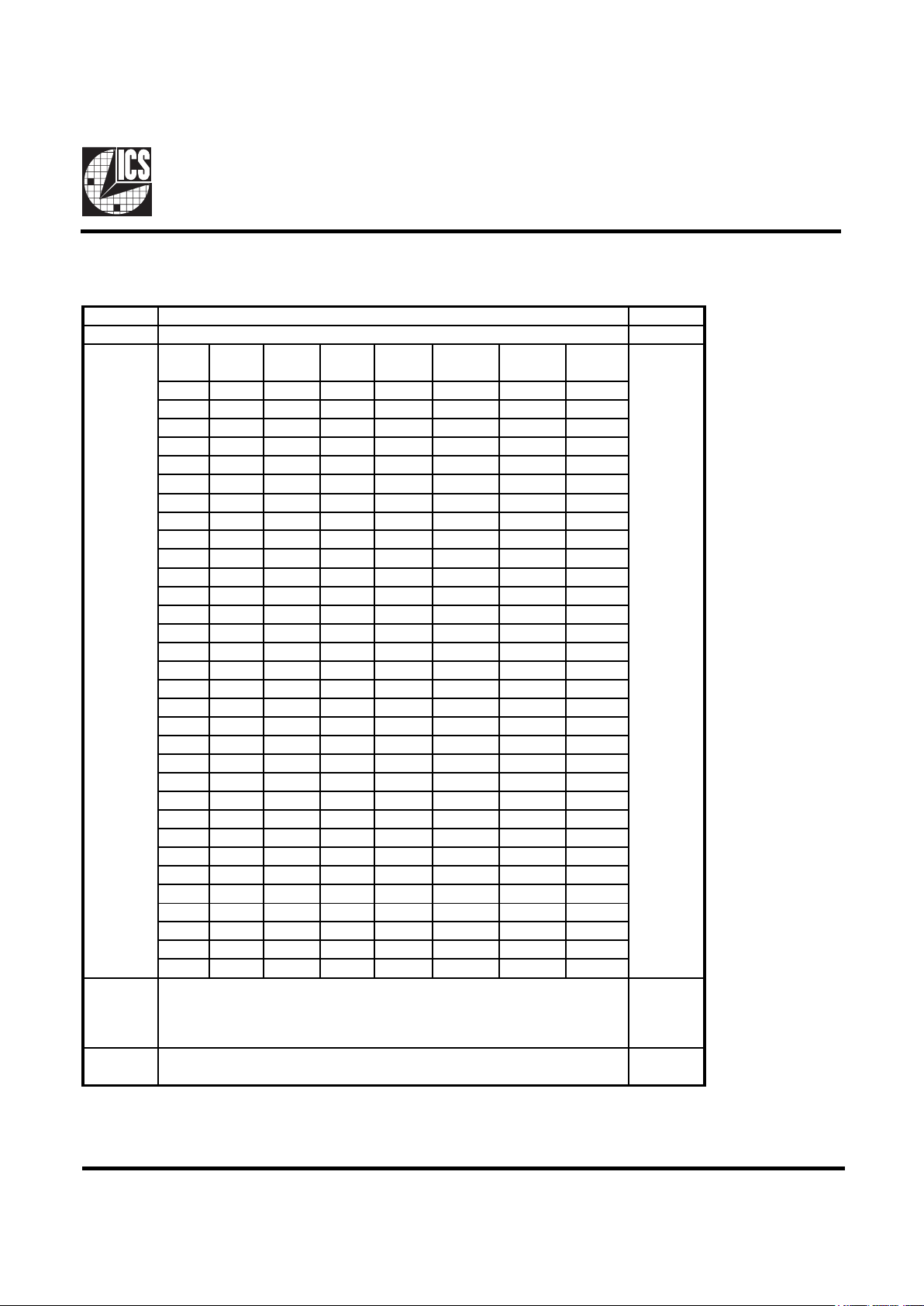

Notes:

1. Default at power-up will be latched logic inputs to define frequency, as displayed by Bit 1.

2. PWD = Power-Up Default

Byte 6: SDRAM Clock & Generator Mode Control Register

I2C Command Bitmaps

Bit PWD

7 0

00

0 0 0 133.33 33.33 66.67

00

0 0 1 95 31.67 63.33

00

0 1 0 100.99 33.66 67.33

00

0 1 1 115 38.33 76.67

00

1 0 0 100.7 33.57 67.13

00

1 0 1 103 34.33 68.67

00

1 1 0 105 35.00 70.00

00

1 1 1 110 36.67 73.33

01

0 0 0 102 34.00 68.00

01

0 0 1 104 34.67 69.33

01

0 1 0 106 35.33 70.67

01

0 1 1 107 35.67 71.33

01

1 0 0 108 36.00 72.00

01

1 0 1 109 36.33 72.67

01

1 1 0 90 30.00 60.00

01

1 1 1 111 37.00 74.00

10

0 0 0 112 37.33 74.67

10

0 0 1 113 37.67 75.33

10

0 1 0 114 38.00 76.00

10

0 1 1 116 38.67 77.33

10

1 0 0 117 39.00 78.00

10

1 0 1 118 39.33 78.67

10

1 1 0 119 39.67 79.33

10

1 1 1 120 30.00 60.00

11

0 0 0 142 35.50 71.00

11

0 0 1 144 36.00 72.00

11

0 1 0 146 36.50 73.00

11

0 1 1 138 34.50 69.00

11

1 0 0 136 34.00 68.00

11

1 0 1 135 33.75 67.50

11

1 1 0 140 35.00 70.00

11

1 1 1 150 37.50 75.00

0

0 - SDRAM_OUT Disable

1 - SDRAM

_

OUT Enable

1

AGP

01000

Note1

1

0 - Frequency is selected by hardware select, latched input;

Spread controlled by pin 29

1 - Frequency is selected by Bit (6:2); Spread controlled by Bit 7

0

Description

Spread Spectrum enable (+/- 0.25% center spread) 0=OFF 1=ON

6:2

Bit 3 Bit 2

FS2

Bit 6

FS1

Bit 5

FS0

Bit 4

CPU,

SDRAM

PCI

4

ICS9248-153

Third party brands and names are the property of their respective owners.

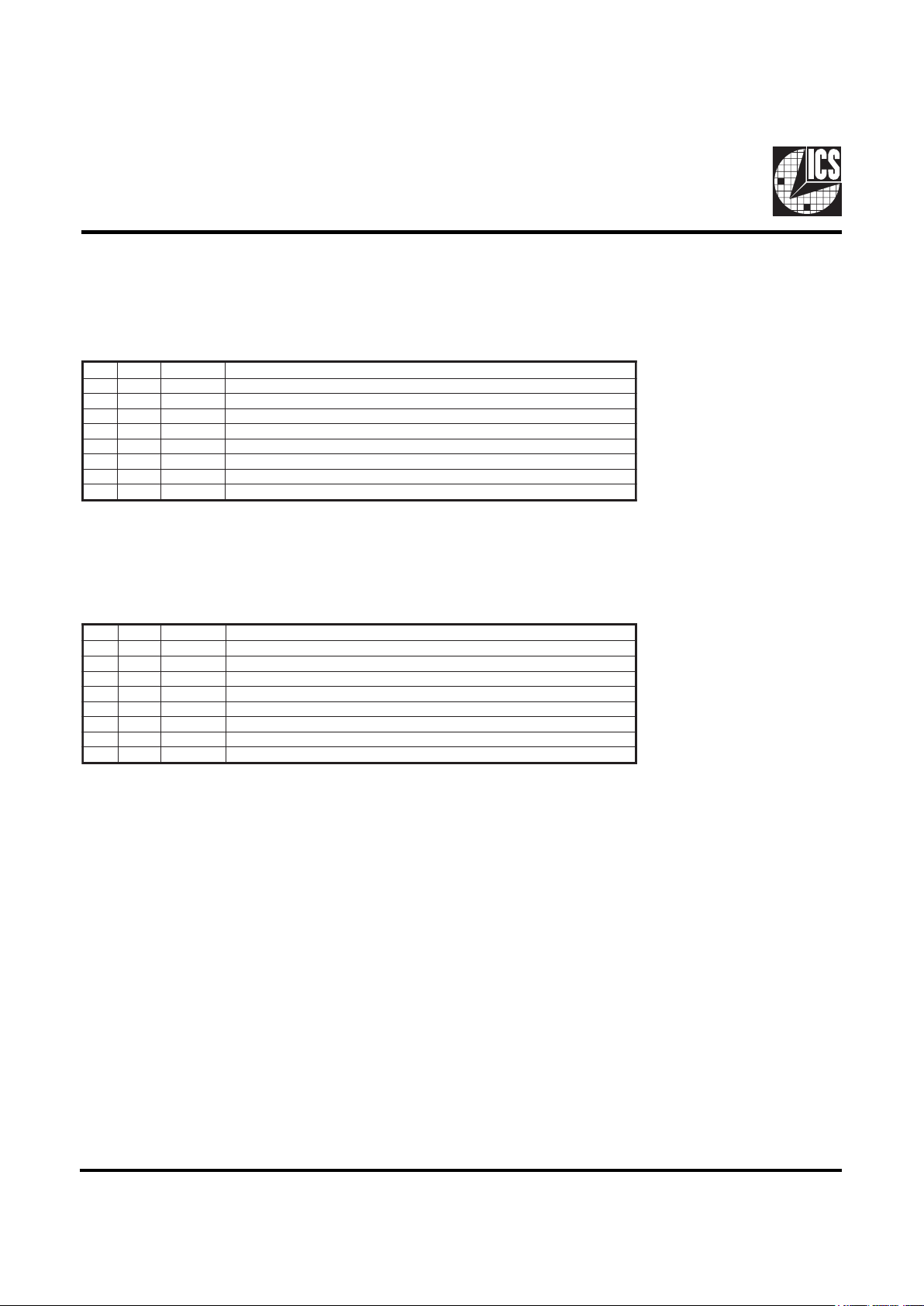

I2C Command Bitmaps

Byte 4: Clock Control Register

Notes: A value of '1' is enable, '0' is disable

tiB#niPtluafeDnoitpircseD

71 1 elbane0FER

6421 elbanezHM84/zHM42

5321 elbanezHM84

4021 elbane1PGA

3911 elbane0PGA

234,241 "yratnemilpmoC"dna"eurT,riaplaitnereffidfohtob(elbane2KLCUPC

104,931 "yratnemilpmoC"dna"eurT,riaplaitnereffidfohtob(elbane1KLCUPC

073,631 "yratnemilpmoC"dna"eurT,riaplaitnereffidfohtob(elbane0KLCUPC

Byte 5: PCI Clock Control Register

Notes: A value of '1' is enable, '0' is disable

tiB#niPtluafeDnoitpircseD

72 1 elbane1FER

6711 elbane6KLCICP

5611 elbane5KLCICP

4411 elbane4KLCICP

3311 elbane3KLCICP

2111 elbane2KLCICP

1011 elbane1KLCICP

08 1 elbane0KLCICP

5

ICS9248-153

Third party brands and names are the property of their respective owners.

Absolute Maximum Ratings

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5 V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND –0.5 V to V

DD

+0.5 V

Ambient Operating Temperature. . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are

stress specifications only and functional operation of the device at these or any other conditions above those listed in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect product reliability.

Electrical Characteristics - Input/Supply/Common Output Parameters

TA = 0 - 70C; Supply Voltage VDD = V

DDL

= 3.3 V +/-5% (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Input High Voltage V

IH

2V

DD

+0.3 V

Input Low Voltage V

IL

VSS-0.3 0.8 V

Input High Current I

IH

VIN = V

DD

5

µ

A

Input Low Current I

IL1

VIN = 0V; Inputs with no pull-up resistors -5

µ

A

Input Low Current I

IL2

VIN = 0V; Inputs with pull-up resistors -200

µ

A

I

DD3.3OP100

CL = 0 pF; Select @ 100 MHz 180 mA

I

DD3.3OP133

CL = 0 pF; Select @ 133 MHz 180 mA

Powerdown Current

I

DD3.3PD

CL = 0 pF; Input address to VDD or GND

600

µ

A

Input Frequency F

i

VDD = 3.3 V 12 14.318 16 MHz

C

IN

Logic Inputs 5 pF

C

INX

X1 & X2 pins 27 45 pF

Clk Stabilization

1

T

STAB

From VDD = 3.3 V to 1% target frequency 3 ms

T

CPU-SDRAM

VT = 50%, CPU=100MHz -250 -210 ps

T

CPU-AGP

VT = 50%, CPU=100MHz

-250 0 ps

1

Guaranteed by design, not 100% tested in production.

Input Capacitance

1

Operating Supply

Current

Skew

1

Loading...

Loading...