ICST AV9248F-150-T, AV9248G-150-T, ICS9248F-150-T, ICS9248G-150-T Datasheet

Integrated

Circuit

Systems, Inc.

ICS9248-150

Third party brands and names are the property of their respective owners.

9248-150 Rev B 06/12/01

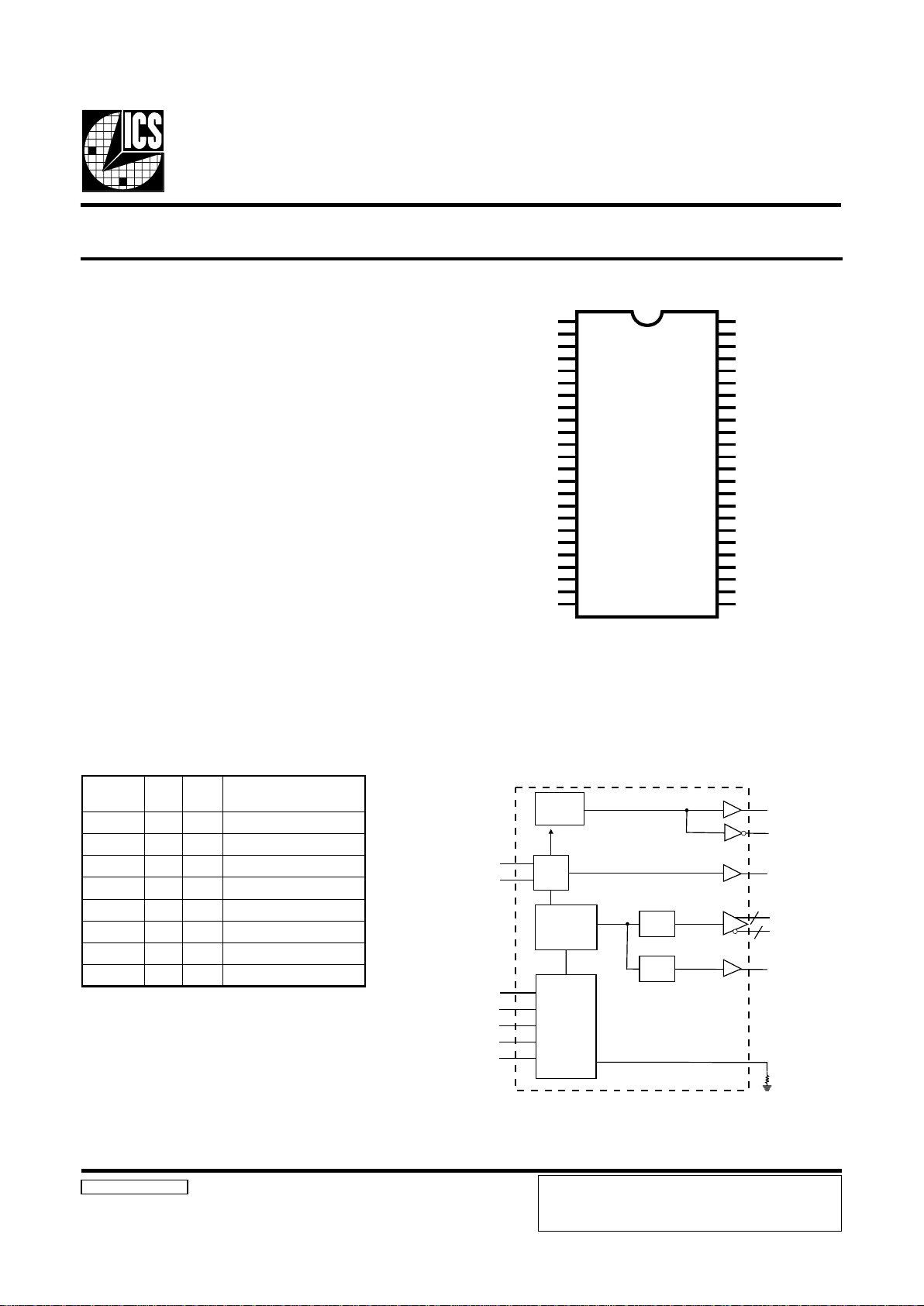

Pin Configuration

48-Pin SSOP and TSSOP

Recommended Application:

ServerWorks Grand Champion Systems.

Output Features:

• 8 - Differential CPU Clock Pairs @ 3.3V

• 1 - 3V 33MHz PCI clocks

• 1 - 48MHz clock

• 1 - Inverted 48MHz clock

• 1 - 14.318 reference output

Features:

• Up to 200MHz frequency support

• Support power management: Power Down Mode

• Supports Spread Spectrum modulation: 0 to -0.5% down

spread.

• Uses external 14.318MHz crystal

• Select logic for Differential Swing Control, Test mode,

Tristate, Power down, Spread Spectrum.

• External resistor for current reference

• FS pins for frequency select

Key Specifications:

• PCI Output jitter <500ps

• CPU Output jitter <200ps

• 48MHz Output jitter <350ps

• REF Output jitter < 1000ps

Frequency Generator for Multi - Processor Servers

Functionality

/331LES

001

0SF1SFnoitcnuF

000 zHM001evitcA

001 edoMtseTzHM001

010 edoMtseTzHM001

011 stuptuollaetatsirT

100 zHM331evitcA

101 edoMtseTzHM331

110 zHM002evitcA

111 devreseR

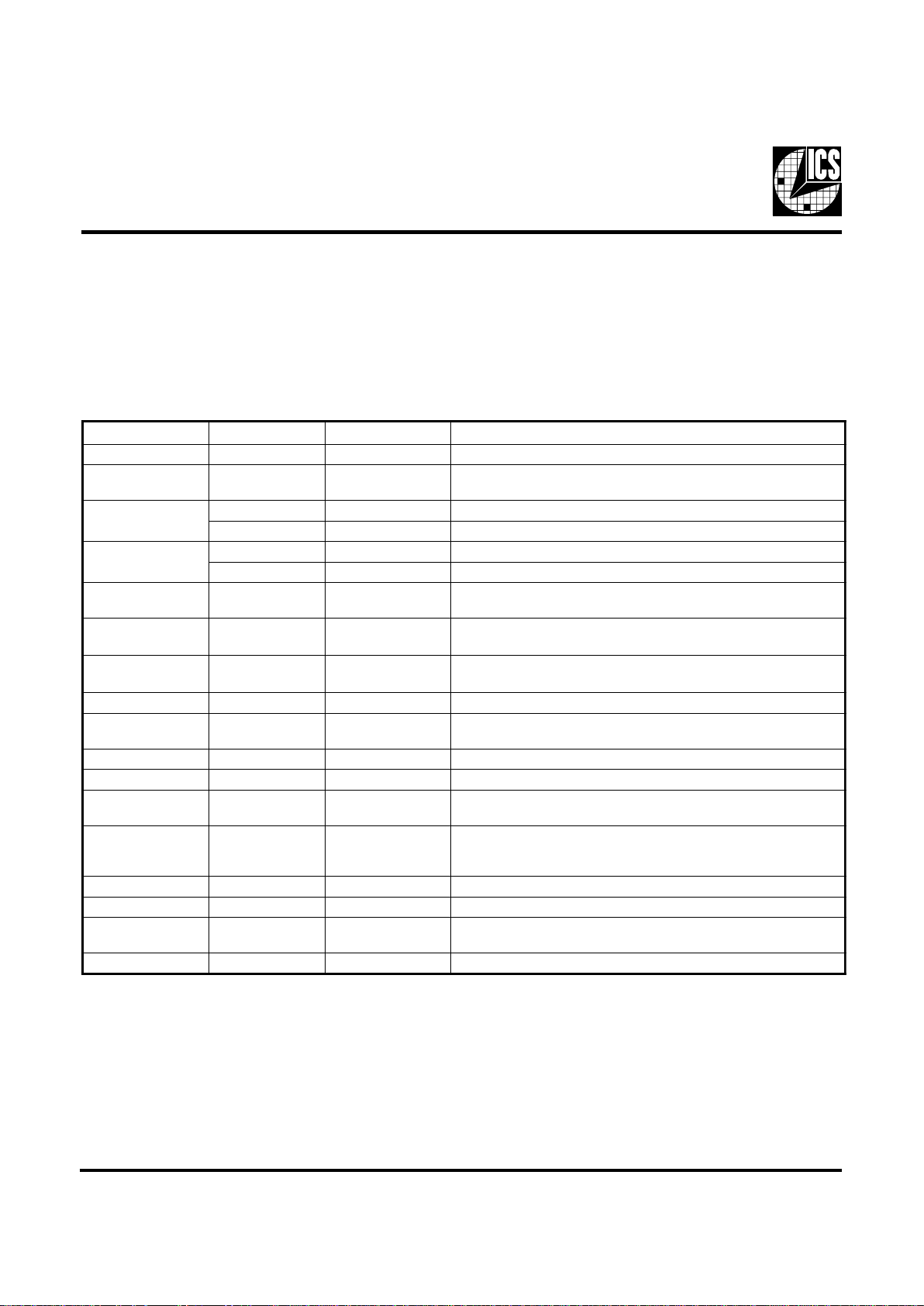

Block Diagram

PCICLK

VDD48

FS0/48MHz

FS1/48MHz#

GND48

VDDCPU

CPUCLKT0

CPUCLKC0

GNDCPU

CPUCLKT1

CPUCLKC1

VDDCPU

CPUCLKT2

CPUCLKC2

GNDCPU

CPUCLKT3

CPUCLKC3

VDDCPU

REF

SPREAD#

GNDREF

X1

X2

VDDREF

SEL100/133

GNDPCI

VDDA

GNDA

PD#

VDDCPU

CPUCLKT4

CPUCLKC4

GNDCPU

CPUCLKT5

CPUCLKC5

VDDCPU

CPUCLKT6

CPUCLKC6

GNDCPU

CPUCLKT7

CPUCLKC7

VDDCPU

MULTSEL0

MULTSEL1

GND

GNDI REF

I REF

VDDI REF

ICS9248-150

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

I REF

PLL2

PLL1

Spread

Spectrum

48MHz

PCICLK

48MHz#

X1

X2

XTAL

OSC

CPU

DIVDER

PCI

DIVDER

PD#

SPREAD#

MULTSEL(1:0)

SEL100/133

FS(1:0)

Control

Logic

Config.

Reg.

REF

8

8

CPUCLKT (7:0)

CPUCLKC (7:0)

ICS reserves the right to make changes in the device data

identified in this publication without further notice. ICS advises

its customers to obtain the latest version of all device data to

verify that any information being relied upon by the customer is

Analog Power Groups

VDD48, GND48 = 48MHz, PLL2

VDDA=VDD (core supply voltage 3.3V)

GNDA=Ground for core supply

Digital Power Group

VDDREF , GNDREF = REF, Xtal

2

ICS9248-150

Third party brands and names are the property of their respective owners.

General Description

Pin Configuration

The ICS9248-150 is a main clock for ServerWorks Grand Champion Systems.

Spread spectrum typically reduces system EMI by 8dB to 10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9248-150 employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and temperature variations.

REBMUNNIP

EMANNIPEPYTNOITPIRCSED

1KLCICPTUOtuptuokcolcICP

,13,42,81,21,6,2

,34,73

DDVRWPylppusrewopV3.3

3

0SFNIniptcelesycneuqerF

zHM84TUOtuptuokcolczHM84

4

1SFNIniptcelesycneuqerF

#zHM84TUOtuptuokcolczHM84detrevnI

,43,82,12,51,9,5

74,04

DNGRWPylppusV3.3rofsnipdnuorG

,61,24,93,63,33

7,01,31

)0:7(TKLCUPCTUO

tnerruceraesehT.stuptuoUPCriaplaitnereffidfoskcolc"eurT"

.saibegatlovrofderiuqererasrotsiserlanretxednastuptuo

,71,14,83,53,23

8,11,41

)0:7(CKLCUPCTUO

eraesehT.stuptuoUPCriaplaitnereffidfoskcolc"yrotnemelpmoC"

.saibegatlovrofderiuqererasrotsiserlanretxednastuptuotnerruc

91FERTUOzHM813.41tuptuoecnerefeR

02#DAERPSNI

tsohlaitnereffiDehtnoytilanoitcnufmurtcepSdaerpSsekovnI

woLevitcA,skcolc

221XtupnIlatsyrC2XtupnilatsyrCzHM813.41

322XtuptuOlatsyrC1XtuptuolatsyrCzHM813.41

64,52

FERIDDV

,ADDV

RWPV3.3ylppusrewopgolanA

62FERITUO

.sriapKLCUPCehtroftnerrucecnereferehtsehsilbatsenipsihT

otredronidnuorgotdeitrotsisernoisicerpdexifasekatnipsihT

.tnerrucderiuqerehthsilbatse

03,92)0:1(LESTLUMNIstupnitcelesgniwsUPC

44#DPNI.woLevitcA.edomnwod-rewopsekovnI

54,72

FERIDNG

ADNG

RWPylppusV3.3rofsnipdnuorGgolanA

84331/001LESNIzHM331=hgiH,zHM001=woL.tceleSycneuqerFUPC

3

ICS9248-150

Third party brands and names are the property of their respective owners.

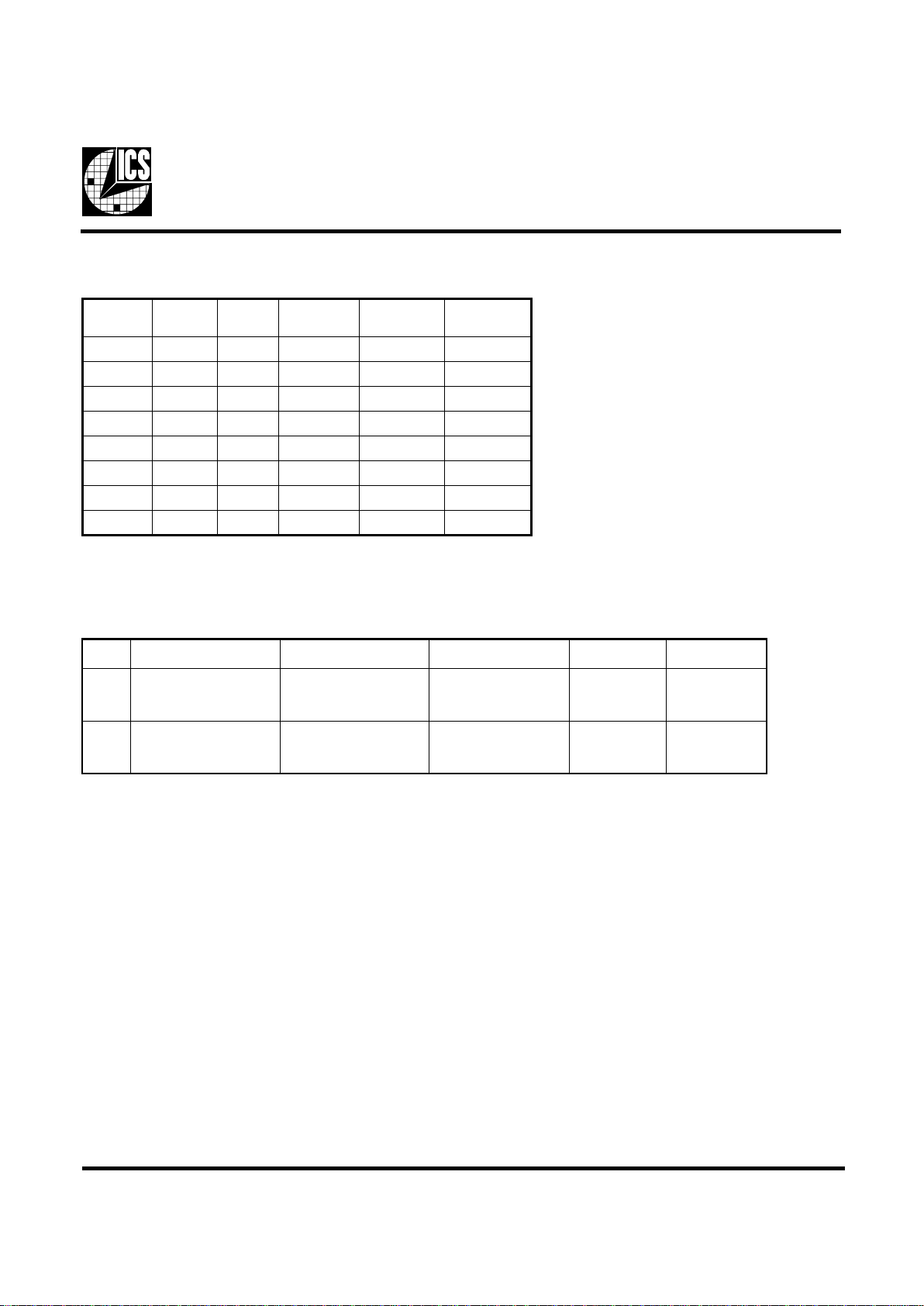

Truth Table

LES

001/331

0SF1SF

KLCUPC

zHM

KLCICP

ZHM

84

zHM

000 0013384

001 00133elbasiD

010 001elbasiDelbasiD

011 etatsirTetatsirTetatsirT

100 3313384

101 33133elbasiD

110 0023384

111 2/KLCT8/KLCT2/KLCT

CPUCLK Buffer Configuration

snoitidnoCnoitarugifnoCdaoLniMxaM

tuoI

)V03.3(lanimon=ddV

,0MfosnoitanibmocllA

ninwohsrRdna1M

wolebelbat

rofdaoltsetlanimoN

noitarugifnocnevig

%7- I lanimon%7+ I lanimon

tuoI

%5±03.3=ddV

,0MfosnoitanibmocllA

ninwohsrRdna1M

wolebelbat

rofdaoltsetlanimoN

noitarugifnocnevig

%21- I lanimon%21+ I lanimon

Loading...

Loading...