ICST AV9248F-128, ICS9248F-128 Datasheet

Integrated

Circuit

Systems, Inc.

ICS9248-128

Third party brands and names are the property of their respective owners.

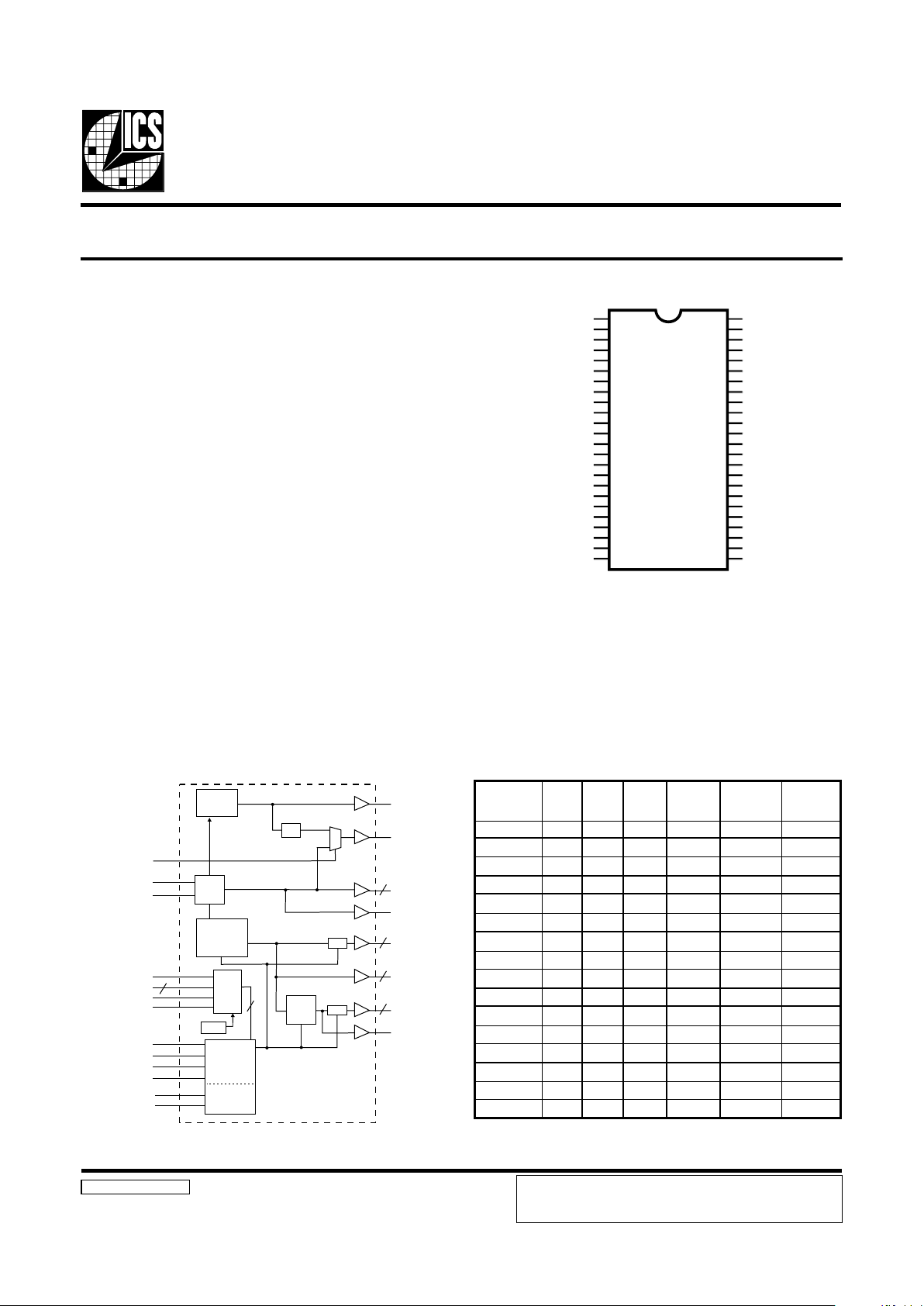

Block Diagram

9248-128 Rev B 11/16/00

Functionality

Pin Configuration

Recommended Application:

SIS 530/620 style chipset

Output Features:

• - 3 CPU @ 2.5V/3.3V up to 133.3 MHz.

• - 6 PCI @ 3.3V (including 1 free-running)

• - 13 SDRAMs @ 3.3V up to 133.3MHz.

• - 3 REF @ 3.3V , 14.318MHz

• - 1 clock @ 24/14.3 MHz selectable output for SIO

• - 1 Fixed clock at 48MHz (3.3V)

• - 1 IOAPIC @ 2.5V / 3.3V

Features:

• Up to 133MHz frequency support

• Support power management: CPU, PCI, SDRAM stop and

Power down Mode from I

2

C programming.

• Spread spectrum for EMI control ( ± 0.25% center spread

& 0 to -0.5% down spread).

• Uses external 14.318MHz crystal

• FS pins for frequency select

Key Specifications:

• CPU – CPU<175ps

• SDRAM – SDRAM < 350ps

• CPU–SDRAM < 500ps

• CPU(early) – PCI : 1-4ns (typ. 2ns)

• PCI – PCI <500ps

Frequency Generator & Integrated Buffers

VDDR/X

*MODE/REF0

GNDREF

X1

X2

VDDPCI

*FS1/PCICLK_F

*FS2.PCICLK0

GNDPCI

PCICLK1

PCICLK2

PCICLK3

PCICLK4

VDDPCI

SDRAM12

GNDSDR

*CPU_STOP# /SDRAM11

*PCI_STOP# /SDRAM10

VDDSD/C

*SDRAM_STOP# /SDRAM9

*PD# /SDRAM8

GNDFIX

SDATA

SCLK

VDDLAPIC

IOAPIC

REF1/SD_SEL#*

GNDLAPIC

REF2/CPU2.5_3.3#*

CPUCLK1

VDDLCPU

CPUCLK2

CPUCLK3

GNDCPU

SDRAM0

SDRAM1

VDDSDR

SDRAM2

SDRAM3

GNDSDR

SDRAM4

SDRAM5

VDDSDR

SDRAM6

SDRAM7

GNDSDR

48MHz/FS0*

SIO/SEL24_14#MHz

*

ICS9248-128

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

48-Pin SSOP

* Internal Pull-up Resistor of

120K to 3.3V on indicated inputs

CPU_STOP#

SDRAM_STOP#

PCI_STOP#

PD#

PLL2

PLL1

Spread

Spectrum

48MHz

SIO

REF(2:0)

IOAPIC

CPUCLK (3:1)

SDRAM (12:0)

PCICLK (4:0)

PCICLK_F

X1

X2

SEL24_14#

XTAL

OSC

PCI

CLOCK

DIVDER

STOP

STOP

SDATA

SCLK

MODE

FS(2:0)

CPU3.3#_2.5

SD_SEL#

Control

Logic

Config.

Reg.

LATCH

POR

PCI_STOP

CPU_STOP

3

3

13

5

5

3

/2

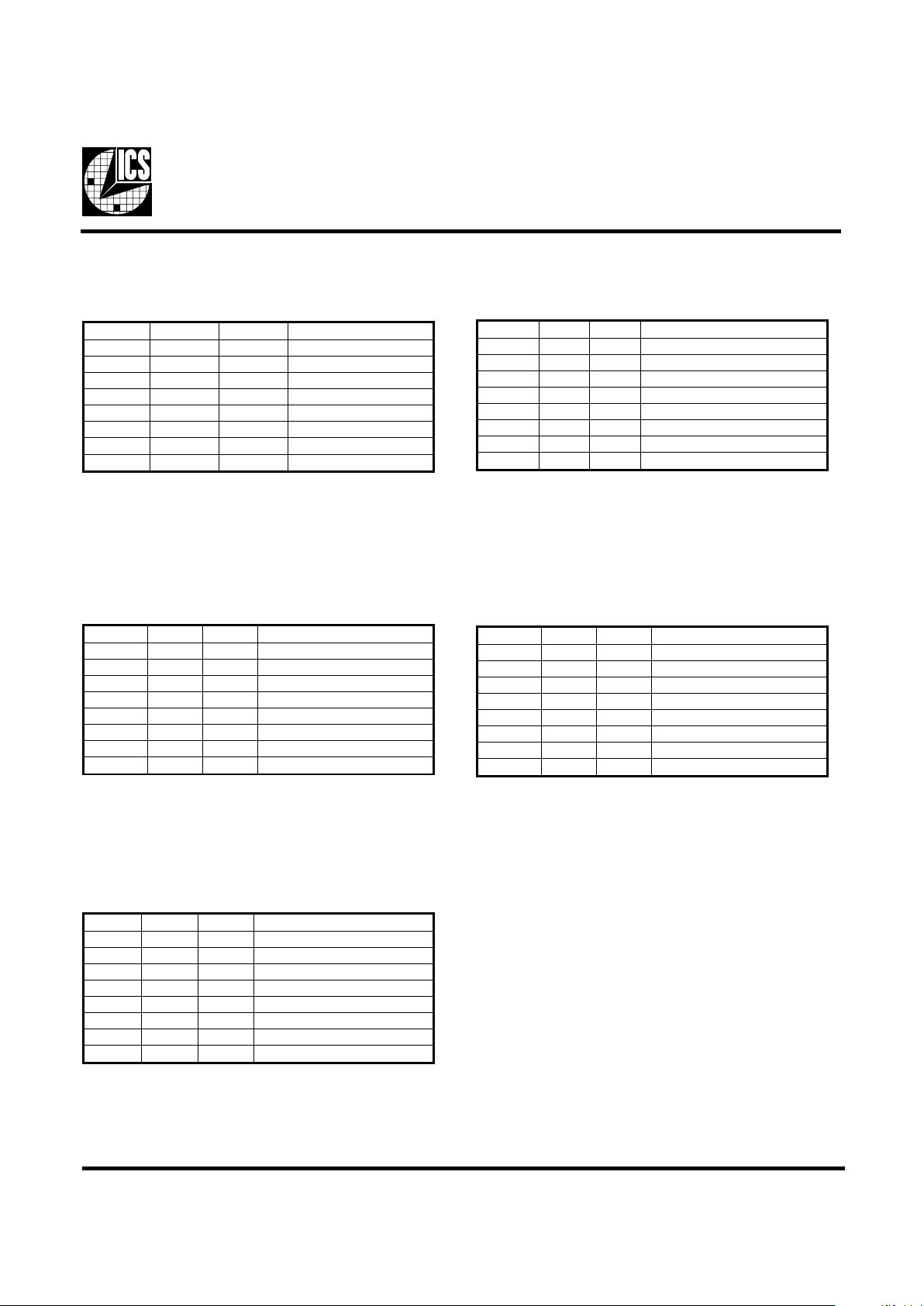

SD_SEL FS2 FS1 FS0

CPU

MHZ

SDRAM

MHZ

PCI

MHZ

0000

90.00 90.00 30.00

0 0 0 1 66.70 100.05 33.35

0 0 1 0 95.00 63.33 31.66

0 0 1 1 100. 00 66.66 33.33

0 1 0 0 100. 00 75.00 30.00

0 1 0 1 112. 00 74.66 37.33

0 1 1 0 124. 00 82.66 31.00

0 1 1 1 97.00 97.00 32.33

1 0 0 0 66.70 66.70 33.35

1 0 0 1 75.00 75.00 30.00

1 0 1 0 83.30 83.30 33.32

1 0 1 1 95.00 95.00 31.66

1 1 0 0 100. 00 100.00 33. 33

1 1 0 1 112. 00 112.00 37. 33

1 1 1 0 124. 00 124.00 31. 00

1 1 1 1 133. 30 133.30 33. 33

Note: REF , IOAPIC = 14.318MHz

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9248-128

Third party brands and names are the property of their respective owners.

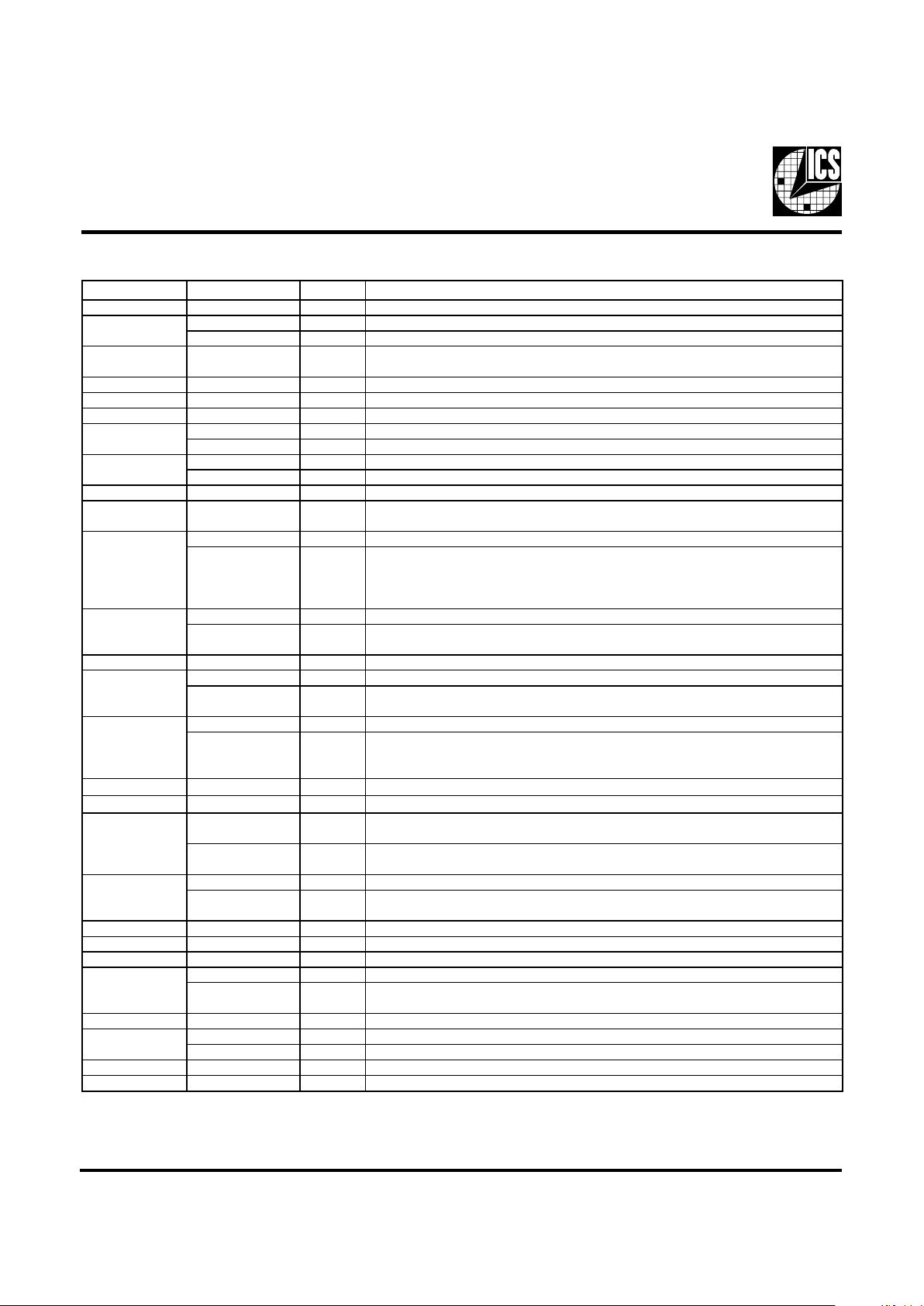

Pin Descriptions

Notes:

1: Internal Pull-up Resistor of 120K to 3.3V on indicated inputs

2: Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor

to program logic Hi to VDD or GND for logic low .

Pin number Pin name Type Description

1 VD DR/X P ower Is olat ed 3.3 V power for c rys tal & referenc e

RE F0 Outpu t 3.3V , 14.3 18 M Hz reference c loc k outpu t.

Mod e Input Fun ct ion s elec t pin, 1= des k to p m ode, 0= m obile m ode . Latc hed inpu t.

3,9,16, 22,

27,33,39

GND Pow er 3.3 V G round

4 X1 Input 14.3 18 M Hz c rys t al input

5 X2 Output 14.318 MHz c rys tal output

6,14 VD DP CI Power 3.3 V power for the P CI clo ck outp uts

FS1 Input Logic input frequency select bit. Input latched at power-on.

PC ICLK _F Out put 3.3 V free running PC I c loc k output, will not be s t opped by the P CI _S TO P #

PCICLK 0 Output 3.3 V PCI clock outputs, generating timing requirements for Pentium II

FS2 Input Logic input frequency select bit. Input latched at power-on.

13, 12, 11, 10 PC ICLK (4:1) Outpu t 3.3 V P CI c loc k ou tput s, generating tim ing requirem ents fo r Pent ium II

15,28,29,31,32,

34,35,37,38

SDRAM 12,

SDRA M (7:0)

Output SDRAM c lock outputs . F requency is s elected by S D-Sel latched input.

SDRA M 11 Output SDRAM c lock outputs . F requency is s elected by S D-Sel latched input.

CPU_S TOP # Input

As y nc h ronous ac tive low input pin us ed to stop the CP UCL K in low s tat e,

all other c loc k s will continue t o run. T he CP UCL K will h av e a " T urnon" lat enc y

of at least 3 CP U cloc k s.

SDRA M 10 Output SDRAM c lock outputs . F requency is s elected by S D-SE L latched input.

PCI-STOP# Input

Sy nc hronous ac tiv e low input us ed to s top t he P CICL K in a low st ate. It will not

effec t P CI CLK _F or any othe r outputs .

19 V DDS D/ C Pow er 3.3 V pow er for SDRA M out puts and c ore

SDRA M 9 Output SDRAM c lock outputs . F requency is s elected by S D-Sel latched input.

SDRAM_STOP# Input

As y nc h ronous ac tiv e low inpu t us ed to s t op t he S D RA M in a low s t ate.

It will no t ef fec t any ot her out puts .

SDRA M 8 Output SDRAM c lock outputs . F requency is s elected by S D-Sel latched input.

PD# Input

As y nc hronous ac tiv e low input pin us ed to pow er down the dev ic e into a low

power stat e. T he internal c loc k s are dis abled and t he V CO and the c rys t al are

st opped. Th e latenc y of t he pow er down will n ot b e greater than 3m s .

23 SDAT A Input

Data input for I

2

C serial input.

24 SC LK Input

Clock in put of I

2

C input

SEL24_14# Input

This input pin c ont rols th e frequenc y of the S I O. If logic 0 at power on

SI O= 14. 318 M Hz . If logic 1 at powe r-on SIO = 24M Hz .

SI O Out put Su per I/O ou tput . 24 or 14.318 M Hz . Se lect able at pow er-up by S E L24_14M Hz

FS0 Input Logic input frequency select bit. Input latched at power-on.

48 MH z Outpu t

3.3 V 48 M Hz c lock out put, fix ed frequenc y c loc k t ypic ally us ed wit h

USB devices

30,36 VDD S DR Pow er 3.3 V pow er for SDRA M out puts

40,41,4 3 CP UC LK (3:1) 0utput 2.5 V CP U and Hos t cloc k outpu ts

42 VD DLCP U P ower 2. 5 V po wer for CPU

RE F2 Outpu t 3.3V , 14.3 18 M Hz reference c loc k outpu t.

CP U3. 3#_2. 5 Input

This pin s elec ts the operat ing vo ltage for the CP U. If logic 0 at powe r on

CPU= 3.3 V and if logic 1 at power on CPU=2.5 V operating voltage.

45 GNDL Power 2.5 V Ground for the IOAPIC or CPU

RE F1 Outpu t 3.3V , 14.3 18 M Hz reference c loc k outpu t.

SD_ SE L # Input T his input pin c ont rols t he frequenc y of t he S DRA M .

47 IOA P IC Out put 2.5V fix ed 14.3 18 M Hz IO AP I C c loc k out puts

48 VDDLAPIC Power 2.5 V power for IOAP IC

2

1,2

8

1,2

26

1,2

7

1,2

46

1,2

44

1,2

17

1

20

1

18

1

21

1

25

1,2

3

ICS9248-128

Third party brands and names are the property of their respective owners.

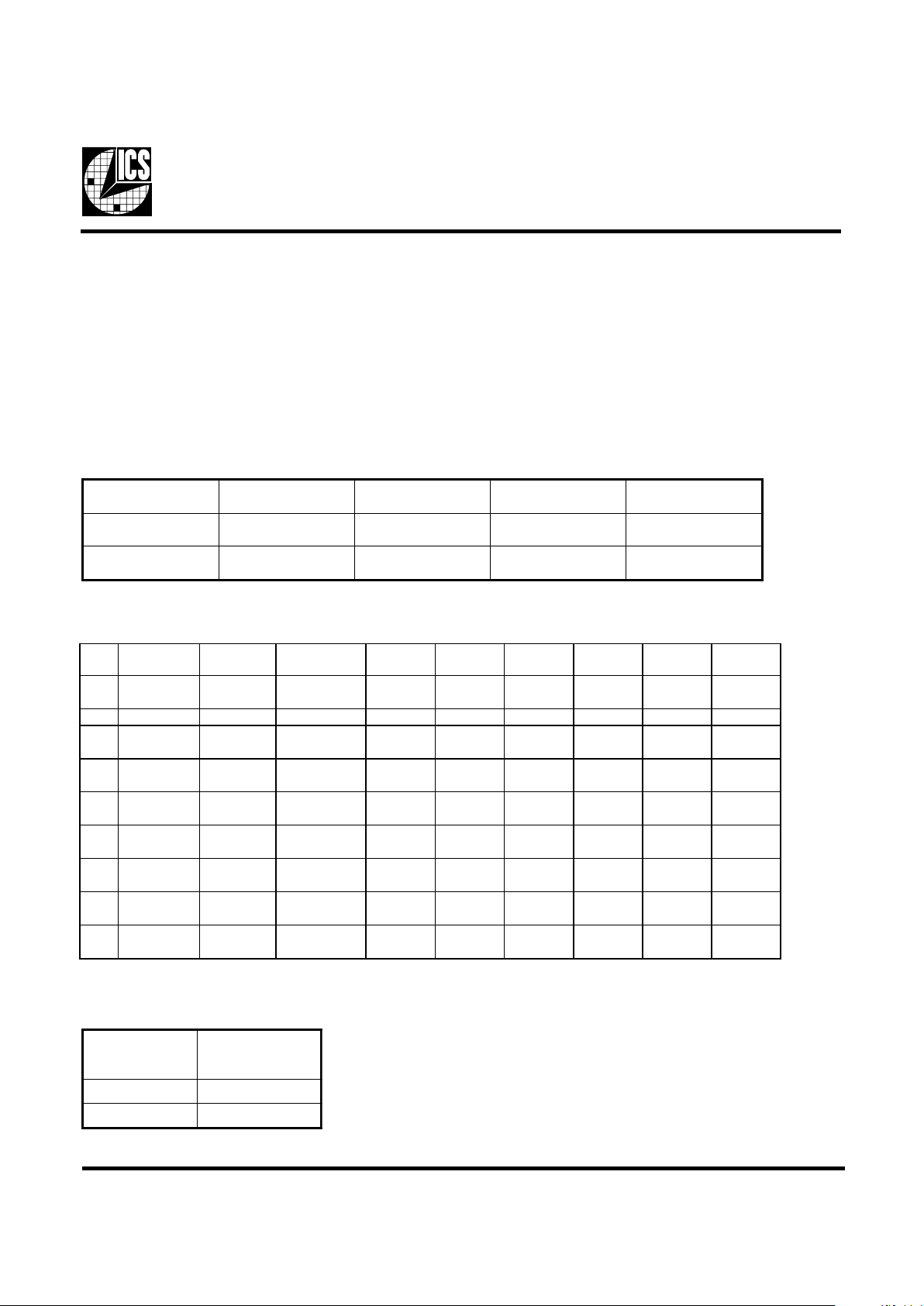

Power Management Functionality

Mode Pin - Power Management Input Control

CPU 3.3#_2.5V Buffer selector for CPUCLK drivers.

PD# CPU _ STOP# PCI_STOP# SDRA M_STOP

PCICLK

(0:4)

SDRAM

(0:12)

PCICLK_F CPUCLK

Crystal

OSC

VCO

0X X X

Stopped

Low

Stopped

Low

Stopped

Low

Stopped

Low

Stopped

Low

Stopped

Low

1 1 1 1 Running Running Running Running Running Running

1 1 1 0 Running

Stopped

Low

Running Running Running Running

11 0 1

Stopped

Low

Running Running Running Running Running

11 0 0

Stopped

Low

Stopped

Low

Running Running Running Running

1 0 1 1 Running Running Running

Stopped

Low

Running Running

1 0 1 0 Running

Stopped

Low

Running

Stopped

Low

Running Running

10 0 1

Stopped

Low

Running Running

Stopped

Low

Running Running

10 0 0

Stopped

Low

Stopped

Low

Running

Stopped

Low

Running Running

2niP,EDOM

)tupnIdehctaL(

71niP81niP02niP12niP

0

#POTS_UPC

)TUPNI(

#POTS_ICP

)TUPNI(

#POTS_MARDS

)TUPNI(

#DP

)TUPNI(

1

11MARDS

)TUPTUO(

01MARDS

)TUPTUO(

9MARDS

)TUPTUO(

8MARDS

)TUPTUO(

5.2_#3.3UPC

leveltupnI

)ataDdehctaL(

detceleSreffuB

:tanoitareporof

1DDVV5.2

0DDVV3.3

The ICS9248-128 is the single chip clock solution for Desktop/Notebook designs using the SIS style chipset. It provides all

necessary clock signals for such a system.

Spread spectrum may be enabled through I

2

C programming. Spread spectrum typically reduces system EMI by 8dB to 10dB.

This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9248-128 employs a

proprietary closed loop design, which tightly controls the percentage of spreading over process and temperature variations.

Serial programming I

2

C interface allows changing functions, stop clock programming and frequency selection. The SD_SEL

latched input allows the SDRAM frequency to follow the CPUCLK frequency(SD_SEL=1) or other clock frequencies

(SD_SEL=0)

General Description

4

ICS9248-128

Third party brands and names are the property of their respective owners.

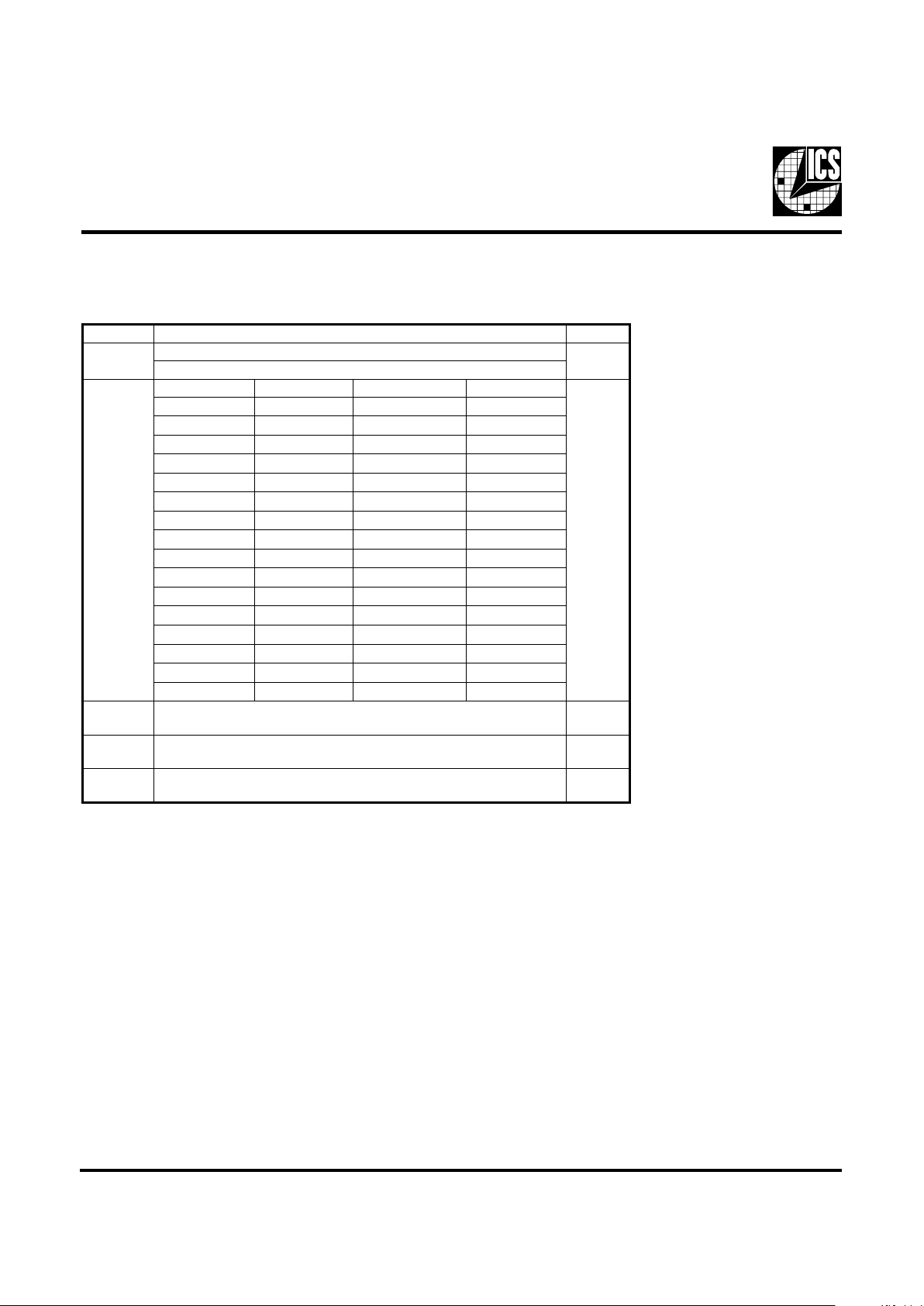

Byte 0: Functionality and frequency select register (Default = 0)

Serial Configuration Command Bitmap

Note 1: Default at power-up will be for latched logic inputs to define frequency .

I2C readback of the power up default indicates the revision ID code in bit 2, 6:4 as shown.

tiB

noitpircseD

DWP

7tiB

murtcepSdaerpSretneC%52.0±-0

1

murtcepSdaerpSnwoD%5.0-ot0-1

tiB

)4:6,2(

)4:6,2(tiBKLCUPCMARDSKLCICP

100,0

1etoN

000000.09

00.09

00.03

100007.66

50.001

53.33

010000.59

33.36

66.13

110000.001

66.66

33.33

001000.001

00.57

00.03

101000.211

66.47

33.73

011000.421

66.28

00.13

111000.79

00.79

33.23

000107.66

07.66

53.33

100100.57

00.57

00.03

010103.38

03.38

23.33

110100.59

00.59

66.13

001100.001

00.001

33.33

101100.211

00.211

33.73

011100.421

00.421

00.13

111103.331

03.331

33.33

3tiB

stupnidehctal,tceleserawdrahybdetcelessiycneuqerF-0

4:6,2tiBybdetcelessiycneuqerF-1

0

1tiB

lamroN-0

delbanemurtcepsdaerpS-1

1

0tiB

gninnuR-0

stuptuollaetatsirT-1

0

5

ICS9248-128

Third party brands and names are the property of their respective owners.

Byte 1: CPU, Active/Inactive Register

(1 = enable, 0 = disable)

Byte 2: PCI Active/Inactive Register

(1 = enable, 0 = disable)

Byte 3: SDRAM Active/Inactive Register

(1 = enable, 0 = disable)

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

Byte 4: SDRAM Active/Inactive Register

(1 = enable, 0 = disable)

Byte 5: Peripheral Active/Inactive Register

(1 = enable, 0 = disable)

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

tiB#niPDWPnoitpircseD

7tiB-1 )devreseR(

6tiB-1 )devreseR(

5tiB-1 )devreseR(

4tiB-1 )devreseR(

3tiB041 3KLCUPC

2tiB141 2KLCUPC

1tiB341 1KLCUPC

0tiB-X#0SF

tiB#niPDWPnoitpircseD

7tiB-X#1SF

6tiB71 F_KLCICP

5tiB-1 )devreseR(

4tiB311 4KLCICP

3tiB211 3KLCICP

2tiB111 2KLCICP

1tiB011 1KLCICP

0tiB81 0KLCICP

tiB#niPDWPnoitpircseD

7tiB821 7MARDS

6tiB921 6MARDS

5tiB131 5MARDS

4tiB231 4MARDS

3tiB431 3MARDS

2tiB531 2MARDS

1tiB731 1MARDS

0tiB831 0MARDS

tiB#niPDWPnoitpircseD

7tiB-1 )devreseR(

6tiB-X#2SF

5tiB-1 )devreseR(

4tiB741 CIPAOI

3tiB-X #LES_DS

2tiB4412FER

1tiB6411FER

0tiB210FER

tiB#niPDWPnoitpircseD

7tiB-1 )devreseR(

6tiB521 zHM41/42

5tiB621 zHM84

4tiB511 21MARDS

3tiB711 11MARDS

2tiB811 01MARDS

1tiB021 9MARDS

0tiB121 8MARDS

Loading...

Loading...