Integrated

Circuit

Systems, Inc.

General Description Features

ICS9179-03

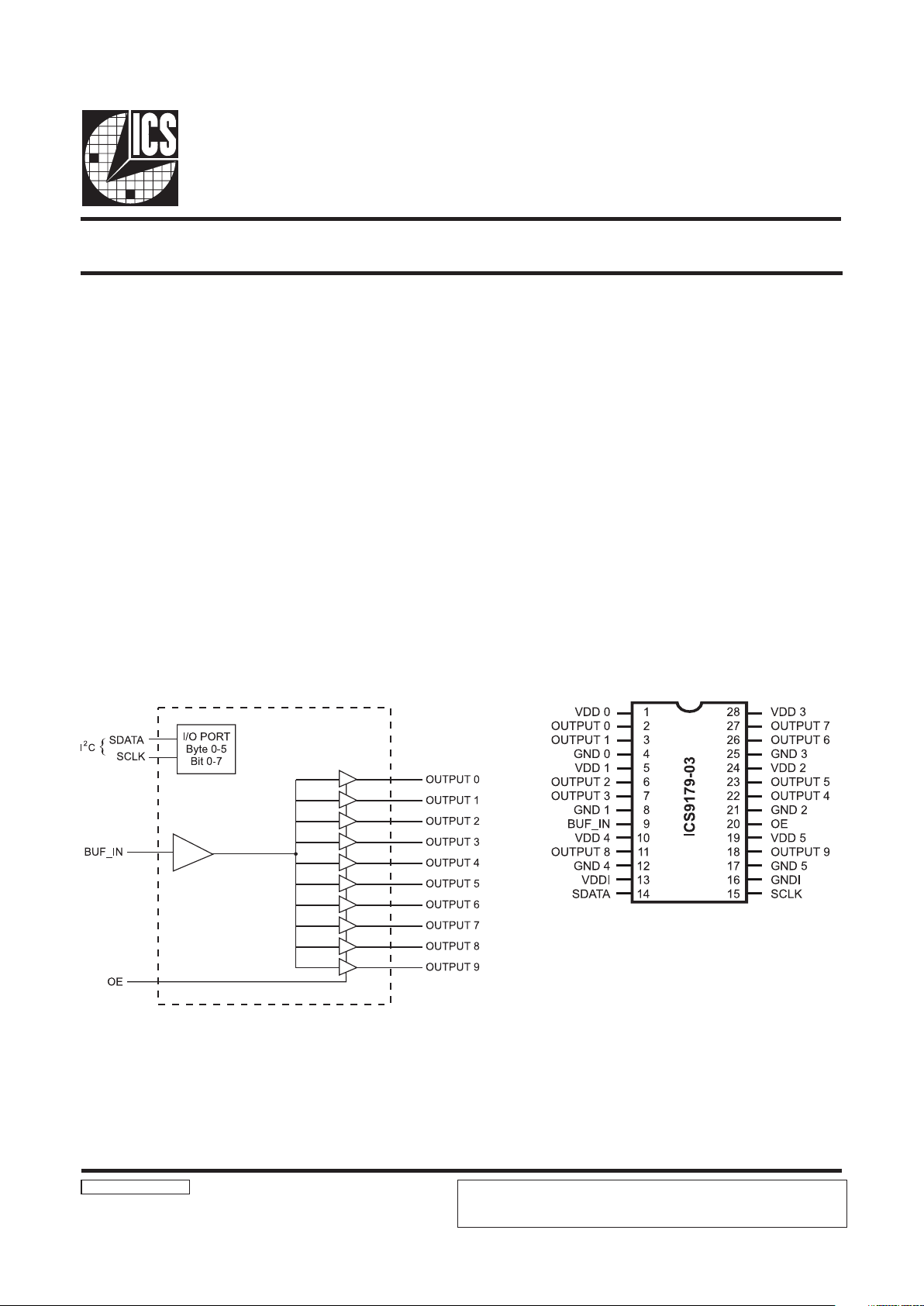

Block Diagram

PentiumPro is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

Low Skew Fan Out Buffers

9179-03 Rev H 10/16/00

Pin Configuration

The ICS9179-03 generates low skew clock buffers required

for high speed RISC or CISC microprocessor systems such as

Intel PentiumPro. Outputs will handle up to 133MHz clocks.

An output enable is provided for testability.

The device is a buffer with low output to output skew. This is

a Fanout buffer device, not using an internal PLL. This buffer

can also be a feedback to an external PLL stage for phase

synchronization to a master clock. There are a total of ten

outputs, sufficient for feedback to a PLL source and to drive

four small outline DIMM modules (S.O. DIMM) at 2 clocks

each. Or a total of ten outputs as a Fanout buffer from a

common clock source.

The individual clock outputs are addressable through I

2

C to

be enabled, or stopped in a low state for reduced EMI when

the lines are not needed.

Ten High speed, low noise non-inverting buffers for (to

133MHz), clock buffer applications.

Output slew rate faster than 1.5V/ns into 20pF

Supports up to four small outline DIMMS (S.O. DIMM).

Synchronous clocks skew matched to 250ps window on

OUTPUTs (0:9).

I

2

C Serial Configuration interface to allow individual

OUTPUTs to be stopped low.

Multiple VDD, VSS pins for noise reduction

Tri-state pin for testing

3.0V 3.7V supply range

28-pin (209 mil) SSOP and (6.1mm) TSSOP package

28-Pin SSOP & TSSOP

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

2

ICS9179-03

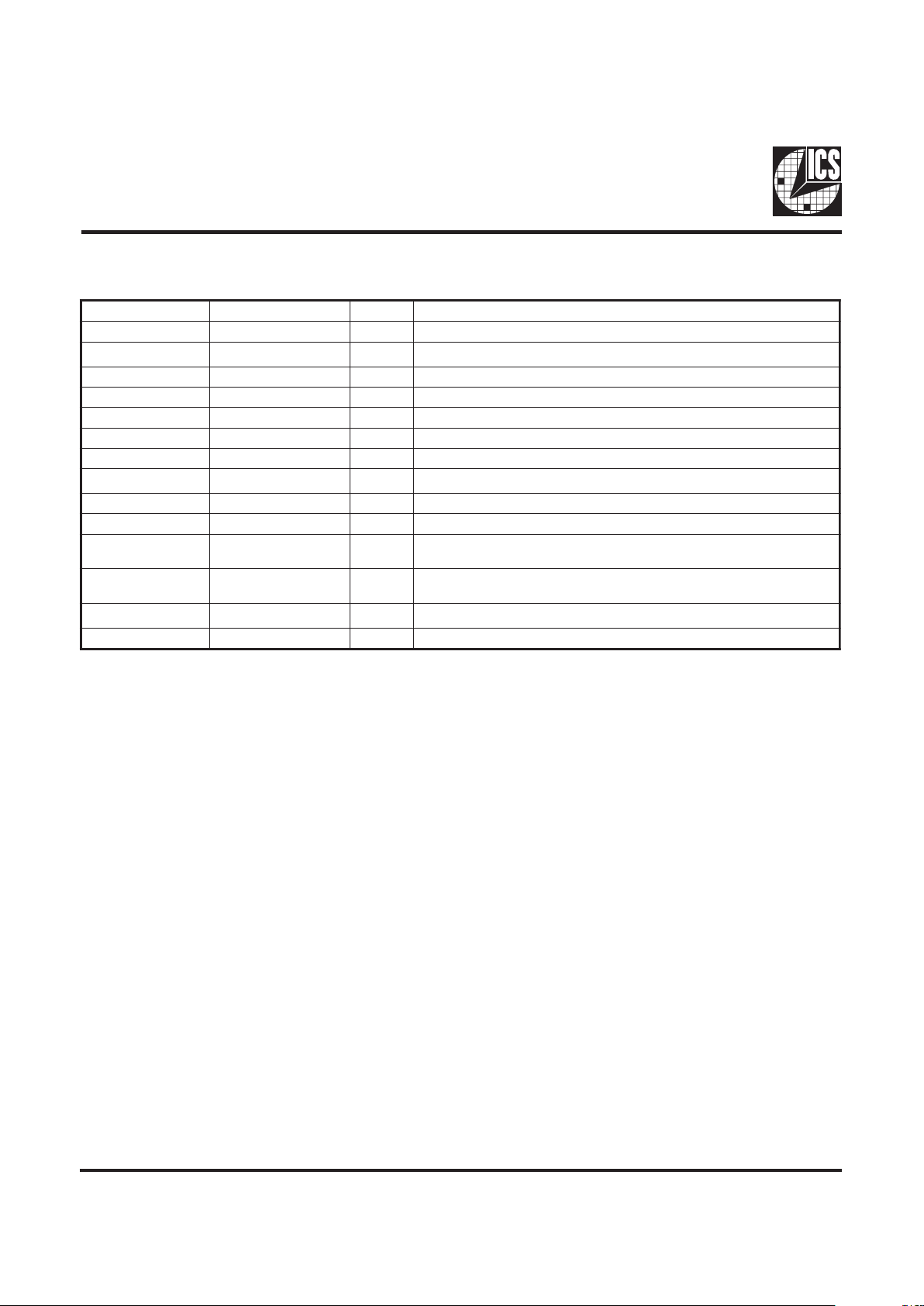

Pin Descriptions

Power Groups

VDD (0:5), GND (0:5) = Power supply for OUTPUT buffer

VDDI, GNDI = Power supply for I2C circuitry

REBMUNNIPEMANNIPEPYTNOITPIRCSED

3,2)1:0(TUPTUOTUOstuptuokcolC

1

0DNG,0DDVsesu,

7,6)3:2(TUPTUOTUOstuptuokcolC

1

1DNG,1DDVsesu,

32,22)5:4(TUPTUOTUOstuptuokcolC

1

2DNG,2DDVsesu

72,62)7:6(TUPTUOTUOtuptuokcolC

1

3DNG,3DDVsesu

118TUPTUOTUOtuptuokcolC

1

4DNG,4DDVsesu

819TUPTUOTUOtuptuokcolC

1

5DNG,5DDVsesu

9NI_FUBNIsreffubroftupnI

02EONI.pu-lluplanretnisaH.WOLdlehnehwstuptuollasetats-irT

2

41ATADSO/IIrofnipataD

2

yrtiucricC

3

51KLCSO/IIrofnipkcolC

2

yrtiucricC

3

,01,5,1

82,42,91

)5:0(DDVRWPsreffubTUPTUOrofylppusrewoPV3.3

,21,8,4

52,12,71,61

)5:0(DNGRWPsreffubTUPTUOrofdnuorG

31IDDVRWPIrofylppusrewoPV3.3

2

cigollanretnidnayrtiucricC

61IDNGRWPIrofdnuorG

2

cigollanretnidnayrtiucricC

Notes:

1. At power up all ten OUTPUTs are enabled and active.

2. OE has a 100K Ohm internal pull-up resistor to keep all outputs active.

3. The SDATA and SCLK inputs both also have internal pull-up resistors with values above 100K Ohms as well for

complete platform flexibility.

3

ICS9179-03

VDD

This is the power supply to the internal core logic of the

device as well as the clock output buffers for OUTPUT (0:9).

This pin operates at 3.3V volts. Clocks from the listed buffers

that it supplies will have a voltage swing from Ground to this

level. For the actual guaranteed high and low voltage levels

for the Clocks, please consult the DC parameter table in this

data sheet.

GND

This is the power supply ground (common or negative) return

pin for the internal core logic and all the output buffers.

OUTPUT (0:9)

These Output Clocks are use to drive Dynamic RAMs and

are low skew copies of the CPU Clocks. The voltage swing of

the OUTPUTs output is controlled by the supply voltage

that is applied to VDD of the device, operates at 3.3 volts.

I

2

C

The SDATA and SCLOCK Inputs are use to program the

device. The clock generator is a slave-receiver device in the

I2C protocol. It will allow read-back of the registers. See

configuration map for register functions. The I2C specification

in Philips I2C Peripherals Data Handbook (1996) should be

followed.

BUF_IN

Input for Fanout buffers (OUTPUT 0:9).

OE

OE tristates all outputs when held low.

VDD1

This is the power supply to I2C circuitry.

Technical Pin Function Descriptions

Loading...

Loading...