Integrated

Circuit

Systems, Inc.

General Description Features

ICS9179-06

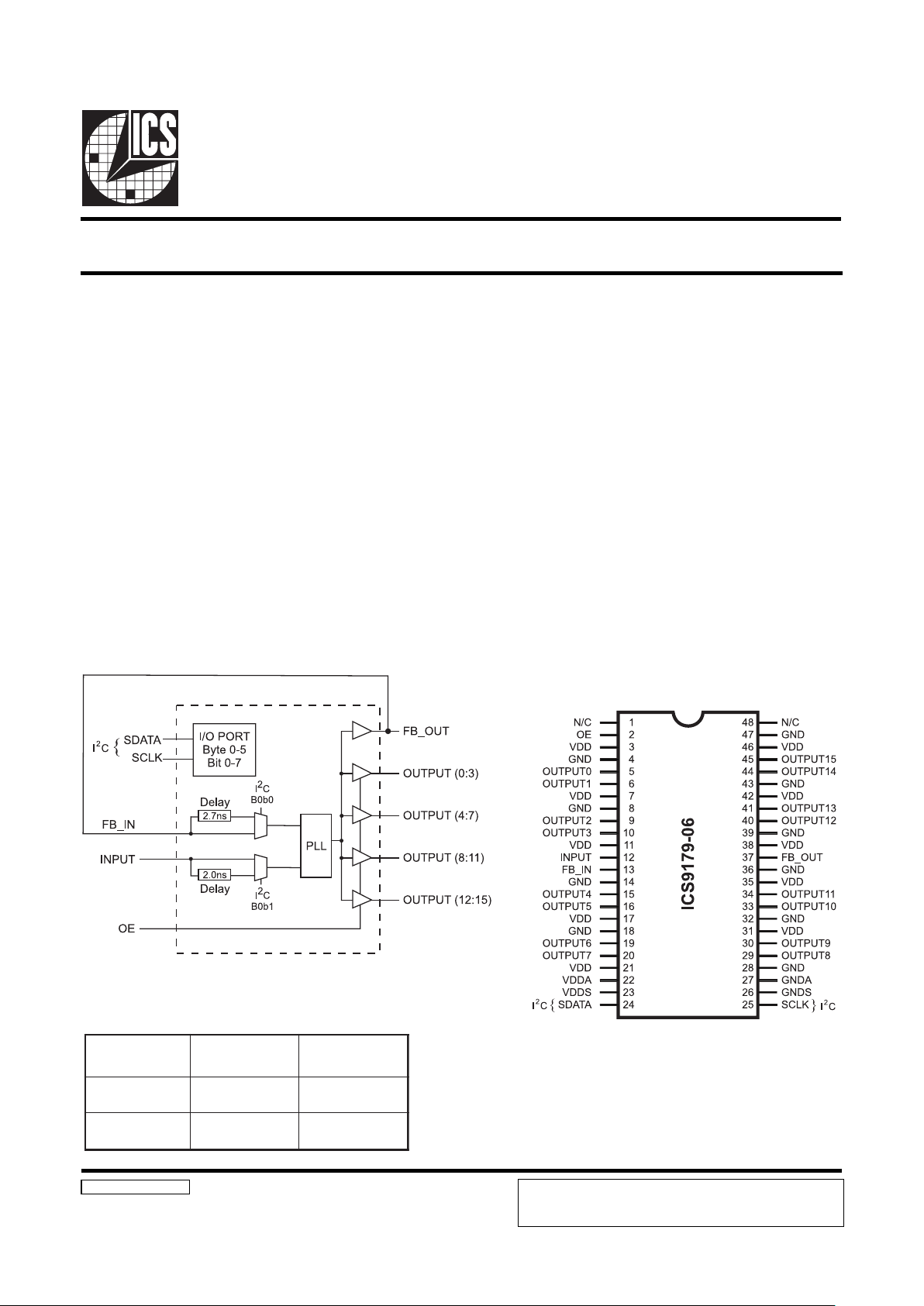

Block Diagram

PentiumPro is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

Zero Delay Buffers

9179-06 Rev F 6/22/99

Pin Configuration

The ICS9179-06 generates low skew clock buffers required

for high speed RISC or CISC microprocessor systems such as

Intel PentiumPro. An output enable is provided for testability.

The device is a buffer with low output to output skew. This is

a zero delay buffer device, using an internal PLL. This buffer

can be used for phase synchronization to a master clock. With

the wide PLL loop BW, this buffer is compatible to Spread

Spectrum input clocks from clock generator products such as

the ICS9148-27.

The individual clock outputs are addressable through I2C to be

enabled, or stopped in a low state for reduced EMI when the

lines are not needed. The device defaults to zero-delay mode,

but can be programmed with I2C for selectable delays -2.7,

+2.0, -0.7 ns (nominal target values).

Zero delay buffer, 16 outputs

Supports up to four SDRAM DIMMS

Wide PLL loop bandwidth makes this part ideal in

Spread Spectrum applications.

Skew Input to FB_IN ±250ps default, with selectable

skew -2.7, +2.0, -0.7ns nominal.

Synchronous clocks skew matched to 250ps window on

output.

33 to 133MHz input or output frequency.

I

2

C Serial Configuration interface to allow individual

clocks to be stopped, or selectable delays.

Multiple VDD, VSS pins for noise reduction

Slew rate 1.5V/ns into 30pF.

VDD = 3.3 ±5%, 0 to 70°C

All outputs (0:15) tristate with OE low

(FB_OUT stays running).

48-Pin SSOP package

48-Pin SSOP

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

Functionality

#EO

TUPTUO

)51:0(

TUO_BF

0Z-iHTUPNIX1

1TUPNIX1TUPNIX1

2

ICS9179-06

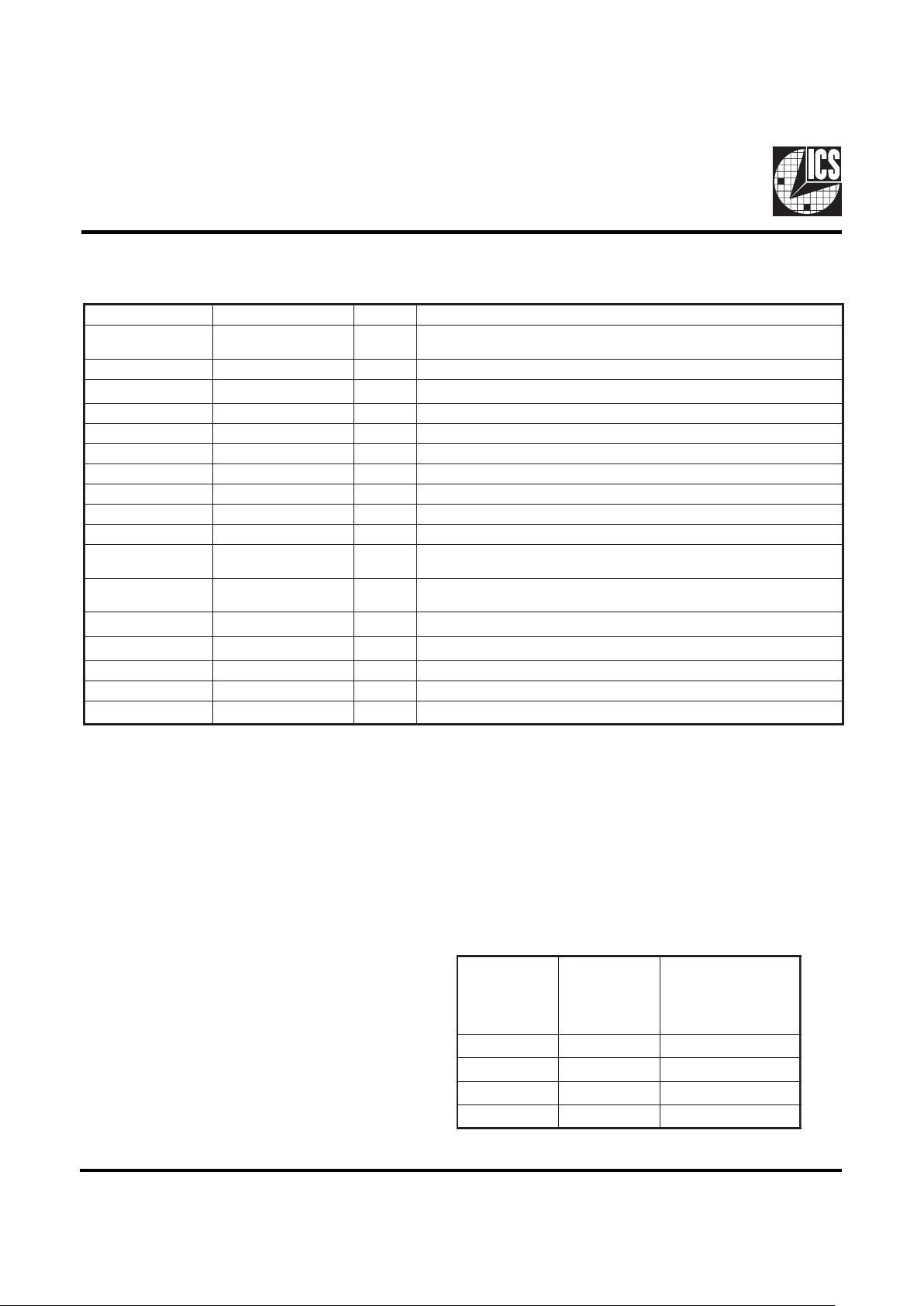

Pin Descriptions

Power Groups

VDD = Power supply for OUTPUT buffers

VDDS = Power supply for I2C circuitry

VDDA = Power supply for Analog PLL circuitry

Notes:

1. At power up all sixteen outputs are enabled and active.

2. OE has a 100K Ohm internal pull-up resistor to keep all outputs active.

3. The SDATA and SCLK inputs both also have internal pull-up resistors with values above 100K Ohms as well for

complete platform flexibility.

4. I2C Byte0, bits 0 & 1 used to select delay. Default* values at power up is 0

5. Subject to design engineering verification of target value.

REBMUNNIPEMANNIPEPYTNOITPIRCSED

2EONI

lanretnisaH.WOLdlehnehwTUO_BFtpecxestuptuollasetats-irT

.pu-llup

2

01,9,6,5)3:0(TUPTUOTUOstuptuokcolc0etyBMARDS

1

02,91,61,51)7:4(TUPTUOTUOstuptuokcolc1etyBMARDS

1

43,33,03,92)11:8(TUPTUOTUOstuptuokcolc2etyBMARDS

1

54,44,14,04)51:21(TUPTUOTUOstuptuokcolc3etyBMARDS

1

21TUPNINI.kcolcecnereferroftupnI

31NI_BFNI.tupnikcabdeeF

42ATADSO/IIrofnipataD

2

yrtiucricC

3

52KLCSO/IIrofnipkcolC

2

yrtiucricC

3

73TUO_BFTUO.NI_BFtupniottuptuokcabdeeF

,13,12,71,11,7,3

64,24,83,53

DDVRWPsreffubtuptuorofylppusrewoPV3.3

,23,82,81,41,8,4

74,34,93,63

DNGRWPsreffubtuptuorofdnuorG

22ADDVRWPsegatsLLPgolanArofylppusrewoPV3.3

32SDDVRWPIrofylppusrewoPV3.3

2

yrtiucricC

62SDNGRWPIrofdnuorG

2

yrtiucricC

72ADNGRWPsegatsLLPgolanArofdnuorG

84,1C/N- detcennocyllanretnitonerasniP

Ground Groups

GND = Ground supply for OUTPUT buffer

GNDS = Ground supply for I2C circuitry

GNDA = Ground supply for Analog PLL circuitry

Delay Selection Table

4

TUPNI

lortnoC

1tib0etyB

NI_BF

lortnoC

0tib0etyB

tegraTlanimoN

5

otTUPNI,yaleD

.snipNI_BF

*0*0sn0

01 sn7.2-

10 sn0.2+

11 sn7.0-

3

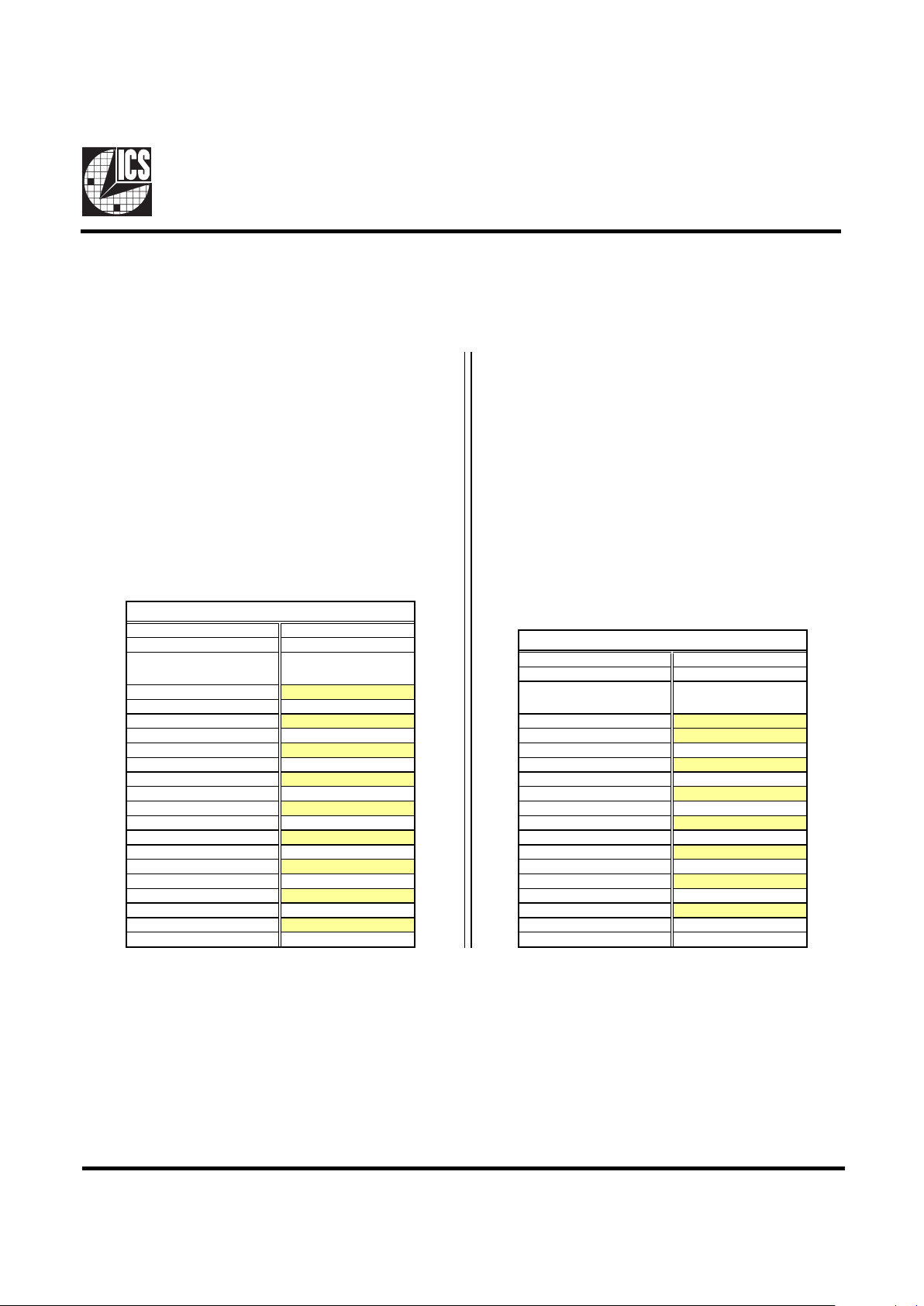

ICS9179-06

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for verification.

Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I2C interface, the protocol is set to use only "Block-Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I2C programming application note.

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

(H)

ICS clock will acknowledge

Controller (host) sends a dummy command code

ICS clock will acknowledge

Controller (host) sends a dummy byte count

ICS clock will acknowledge

Controller (host) starts sending first byte (Byte 0)

through byte 5

ICS clock will acknowledge each byte one at a time.

Controller (host) sends a Stop bit

How to Read:

Controller (host) will send start bit.

Controler (host) sends the read address D3

(H)

ICS clock will acknowledge

ICS clock will send the byte count

Controller (host) acknowledges

ICS clock sends first byte (Byte 0) through byte 5

Controller (host) will need to acknowledge each byte

Controller (host) will send a stop bit

Notes:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

AC

K

Byte Count

ACK

Byte

0

ACK

Byte 1

ACK

Byte

2

ACK

Byte

3

ACK

Byte 4

ACK

Byte

5

ACK

Stop Bit

How to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

AC

K

Dummy Command Code

AC

K

Dummy Byte Count

AC

K

Byte 0

AC

K

Byte 1

AC

K

Byte 2

ACK

Byte 3

AC

K

Byte 4

AC

K

Byte 5

AC

K

Stop Bit

How to Write:

Loading...

Loading...