ICST AV9159C-02CW28, GSP9159C-02CW28, ICS9159C-02CW28 Datasheet

Integrated

Circuit

Systems, Inc.

General Description

Features

ICS9159C-02

The ICS9159C-02 generates all clocks required for high

speed RISC or CISC microprocessor systems such as 486,

Pentium, PowerPC, etc. Four different reference frequency

multiplying factors are externally selectable with smooth

frequency transitions. These multiplying factors can be

customized for specific applications. A test mode is provided

to drive all clocks directly.

High drive BCLK outputs provide typically greater than

1V/ns slew rate into 30pF loads. PCLK outputs provide

typically better than 1V/ns slew rate into 20pF loads while

maintaining +/−5% duty cycle.

Generates up to four processor and six bus clocks, plus

disk, keyboard and reference clocks

Synchronous clocks skew matched to 250ps window on

PCLKs and 500ps window on BCLKs

Test clock mode eases system design

Custom configurations available:

Output frequency ranges to 100 MHz on options

Selectable multiplying and processor/bus ratios

Stop clock control stops clock glitch-free; available as

mask option

3.0V - 5.5V supply range

28-pin SOIC package

Applications

Ideal for high-speed RISC or CISC systems such as

486, Pentium, PowerPC, etc.

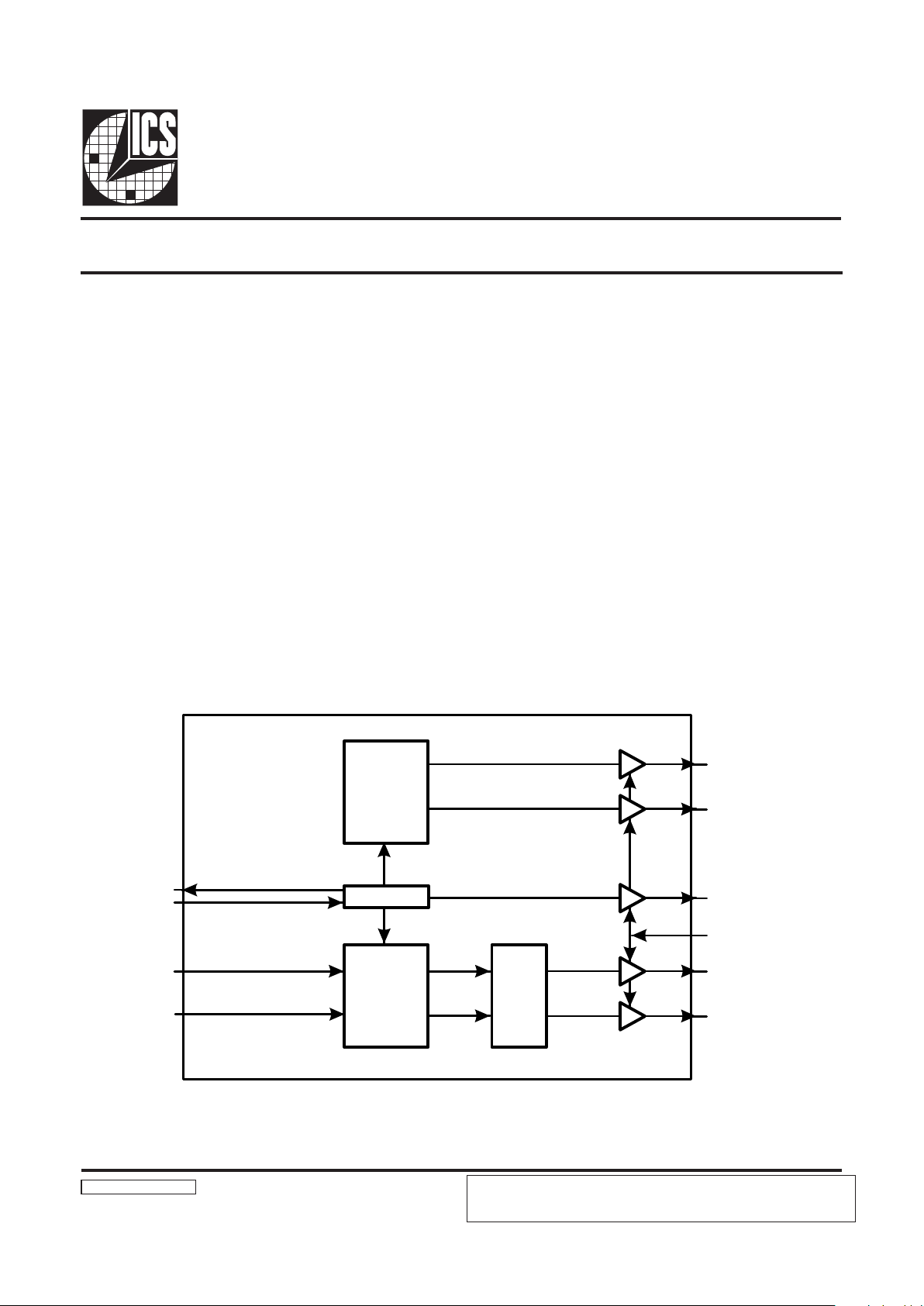

XTAL OSC

BCLK(0:5)

PCLK(0:3)

OEN

REF(0:1)

KEYBD

DISK

SYNC

REG

PLL

CLOCK

GEN

PLL

CLOCK

GEN

X2

X1

FS0

FS1

9159-02 Rev D 062397

Block Diagram

Pentium is a trademark of Intel Corporation

PowerPC is a trademark of Motorola Corporation

Frequency Generator and Integrated Buffer for PENTIUM

TM

ICS reserves the right to make changes in the device data identified in this publication

without further notice. ICS advises its customers to obtain the latest version of all

device data to verify that any information being relied upon by the customer is current

and accurate.

2

ICS9159C-02

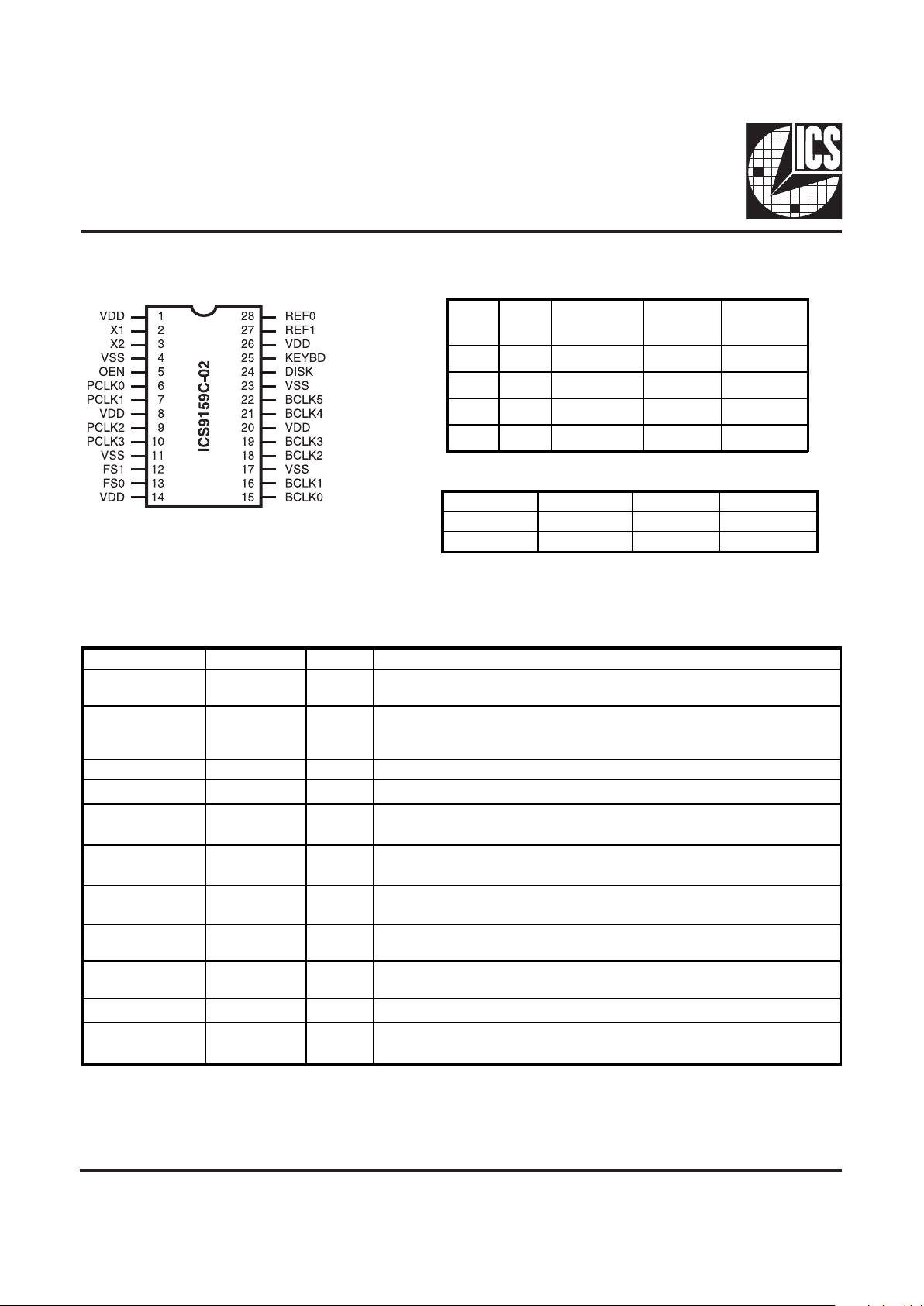

Pin Configuration

Pin Descriptions

Functionality

*VCO range is limited from 60 - 200 MHz

PCLK(0,3) BCLK(0,5) DISK KEYBD

VCO/2 PCLK/2 24 MHz 12 MHz

TCLK/2 TCLK/4 TCLK/4 TCLK/8

PIN NUMBER PIN NAME TYPE DESCRIPTION

1, 8, 14,

20, 26

VDD PWR Power for logic, PCLK and fixe d frequency output buf fers.

2X1IN

XTAL or external refer ence frequency input . This input i ncludes

XTAL load capacitance and feedback bias for a 1 2 - 16 MHz

crystal, no minally 14.31818 MHz.

3 X2 OUT XTAL output which incl udes XTAL load capacitance.

4, 11, 17, 23 VSS PWR Ground for logic, PCLK and fixed f requency output buf fers.

6, 7, 9, 10 PCLK(0:3) OUT

Processor clock outputs which are a mul tiple of the in put reference

frequency as shown in the table above.

13, 12 FS(0:1) IN

Frequency multipl ier select pins. See table above. These inputs have

internal pul l-up devices.

15, 16, 18 19,

21, 22

BCLK(0:5) OUT Bus clock output s are fixed at one ha lf the PCLK frequency.

5OENIN

OEN tristates al l outputs when l ow. This input has an i nternal pullup device.

24 DISK OUT

The DISK controller clock is fixed at 24 MHz

(with 14.318 MHz inpu t).

25 KEYBD OUT The KEYBD clock is fixed at 12 MHz (with 14.318 MHz input ).

28, 27 REF(0:1) OUT

REF is a buffered cop y of the crystal oscillator or r eference input

clock nominally 14.31818 MHz.

Note: BCLK buffers cannot be supplied with 5 volts (pins 14 and 20) if CPU and fixed frequencies (pins 1, 8, and 26) are being

supplied with 3.3 volts

28-Pin SOIC

FS1 FS0 *VCO

X1, REF

(MHz)

CPU

(MHz)

0 0 118/17xX1 14.318 50(49.7)

0 1 65/7xX1 14.318 66.6(66.5)

1 0 92/11xX1 14.318 60(59.9)

1 1 Test mode TCLK TCLK/2

3

ICS9159C-02

Absolute Maximum Ratings

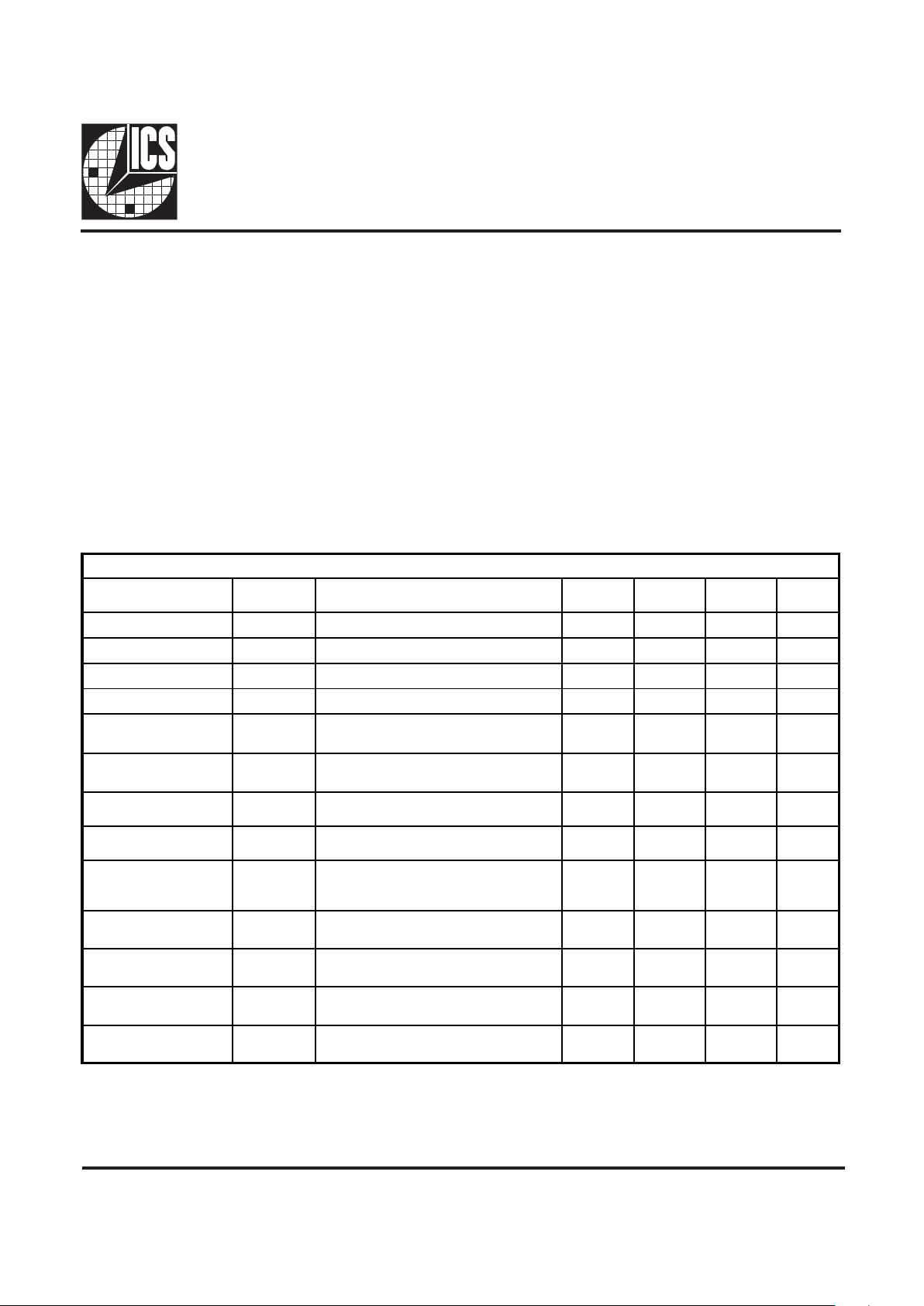

Electrical Characteristics at 3.3 V

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are

stess specifications only and functional operation of the device at these or any other conditions above those listed in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods

may affect product reliability.

Supply Voltage ......................................................................................... 7.0 V

Logic Inputs ..................................................... GND - 0.5 V to VDD + 0.5 V

Ambient .................................................... Operating Temperature0 to +70 C

Storage Temperature .................................................................. 65 to +150 C

VDD = 3.0 - 3.7 V, TA = 0 - 70oC unless otherwise stated

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

DC Characteristics

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Input Low Volta ge V

IL - -0.2VDD V

Input High Volt age V

IH 0.7VDD - - V

Input Low Current I

IL VIN=0V -28.0 -1 0.5 - mA

Input High Curre nt I

IH VIN=VDD -5.0 - 5.0 mA

Output Low Current

1

IOL VOL=0.8V for PCLKS & BCLKS 30.0 47.0 - mA

Output High Curre nt

1

IOH VOL=2.0V for PCLKS & BCLKS - -66. 0 -42.0 mA

Output Low Current

1

IOL VOL=0.8V for fixed CLKs 25.0 38.0 - mA

Output High Curre nt

1

IOH VOL=2.0V for fi xed CLKs - -47.0 -30.0 mA

Output Low Voltage

1

VOL IOL=15mA for PCLKS & BCLKS - 0.3 0.4 V

Output High

Voltage

1

VOH IOH=-30mA for PCLKS & BCLKS 2.4 2.8 - V

Output Low Voltage

1

VOL IOL=12.5mA for fixed CLKs - 0.3 0.4 V

Output High

Voltage

1

VOH IOH=-20mA for fix ed CLKs 2.4 2.8 - V

Supply Curren t I

DD @66.5 MHz all outputs unloaded - 55 110 mA

Loading...

Loading...