ICST AV9158-07M, ICS9158-07M Datasheet

Integrated

Circuit

Systems, Inc.

General DescriptionFeatures

ICS9158-07

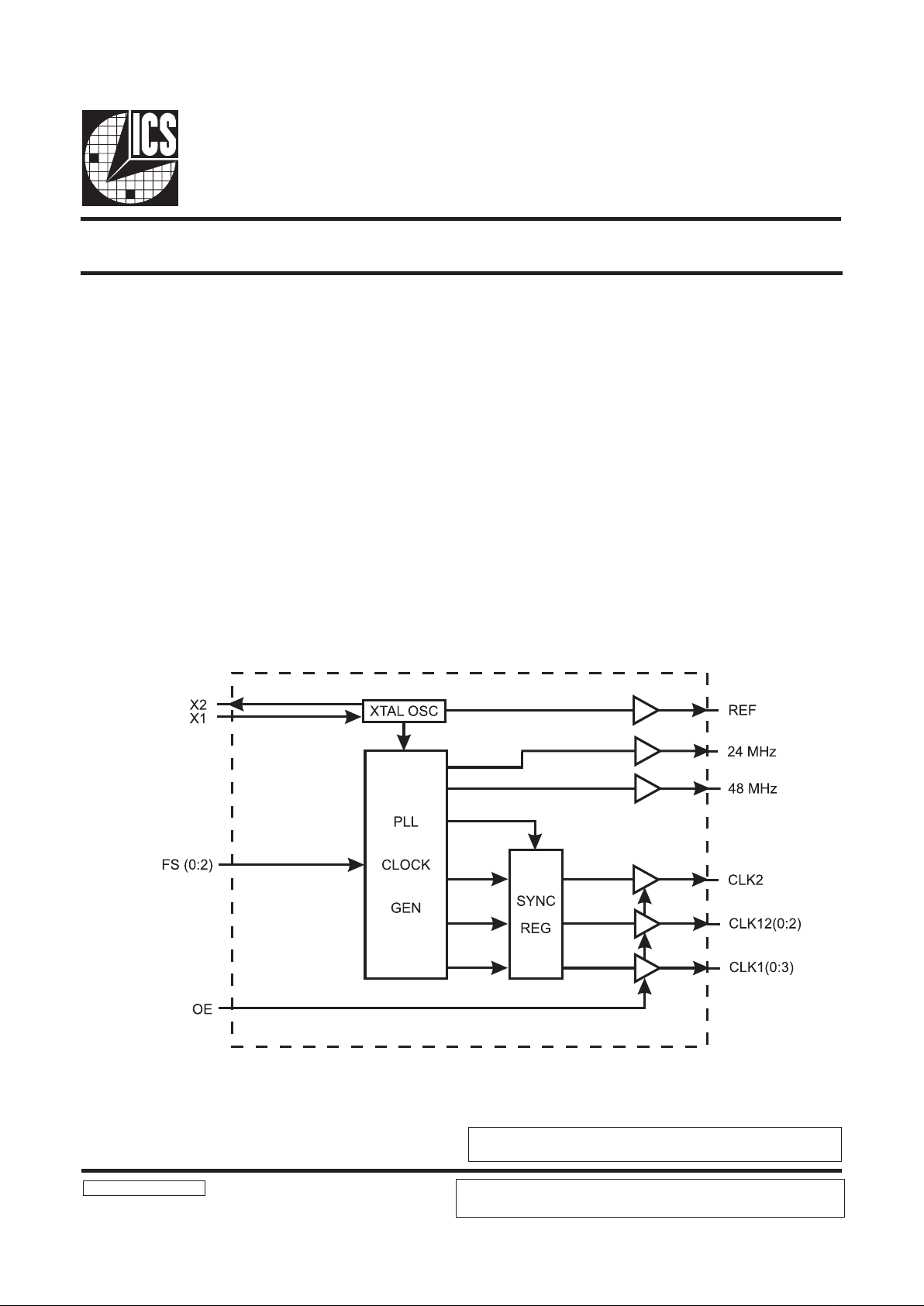

Block Diagram

9158-07 Rev B 053197

Applications

Frequency Generator and Integrated Buffer

The ICS9158-07 is a low-cost frequency generator designed

specifically for desktop and notebook PC applications. Four

copies of the CPU clock are available and four copies of

the BUS clock are available, elimating the need for an

external buffer.

Each high drive (25mA) output is capable of driving a 30pF

load and has a typical duty cycle of 50/50. The clock outputs

are skew-controlled to within ±250ps.

The ICS9158-07 makes a gradual transition between frequencies, so that it meets the Intel cycle-to-cycle timing specification for 486 and Pentium systems.

•8 skew-free, high drive CPU/BUS clocks

•Reference, floppy and keyboard clocks

•±250ps skew between all outputs

•Less than ±250ps absolute jitter

•Outputs can drive up to 30pF load at 1.5V/ns

•50±10% duty cycle

•Compatible with 486 and Pentium CPUs

•On-chip loop filter components

•3.0V - 5.5V supply range

•24-pin SOIC package

Ideal for RISC or CISC systems such as 486, Pentium,™

PowerPC,™ etc., requiring multiple CPU and BUS clocks.

Pentium is a trademark of Intel Corporation.

PowerPC is a trademark of Motorola Corporation.

NOTE: THIS DATA SHEET, ICS9158-07, IS AN ADDENDUM TO THE EXISTING

ICS9158 DATA SHEET. ALL INFORMATION IN THIS DATA SHEET SUPERSEDES

THE DATA FOUND IN THE ORIGINAL ICS9158 DATA SHEET.

ICS reserves the right to make changes in the device data identified in this publication

without further notice. ICS advises its customers to obtain the latest version of all

device data to verify that any

2

ICS9158-07

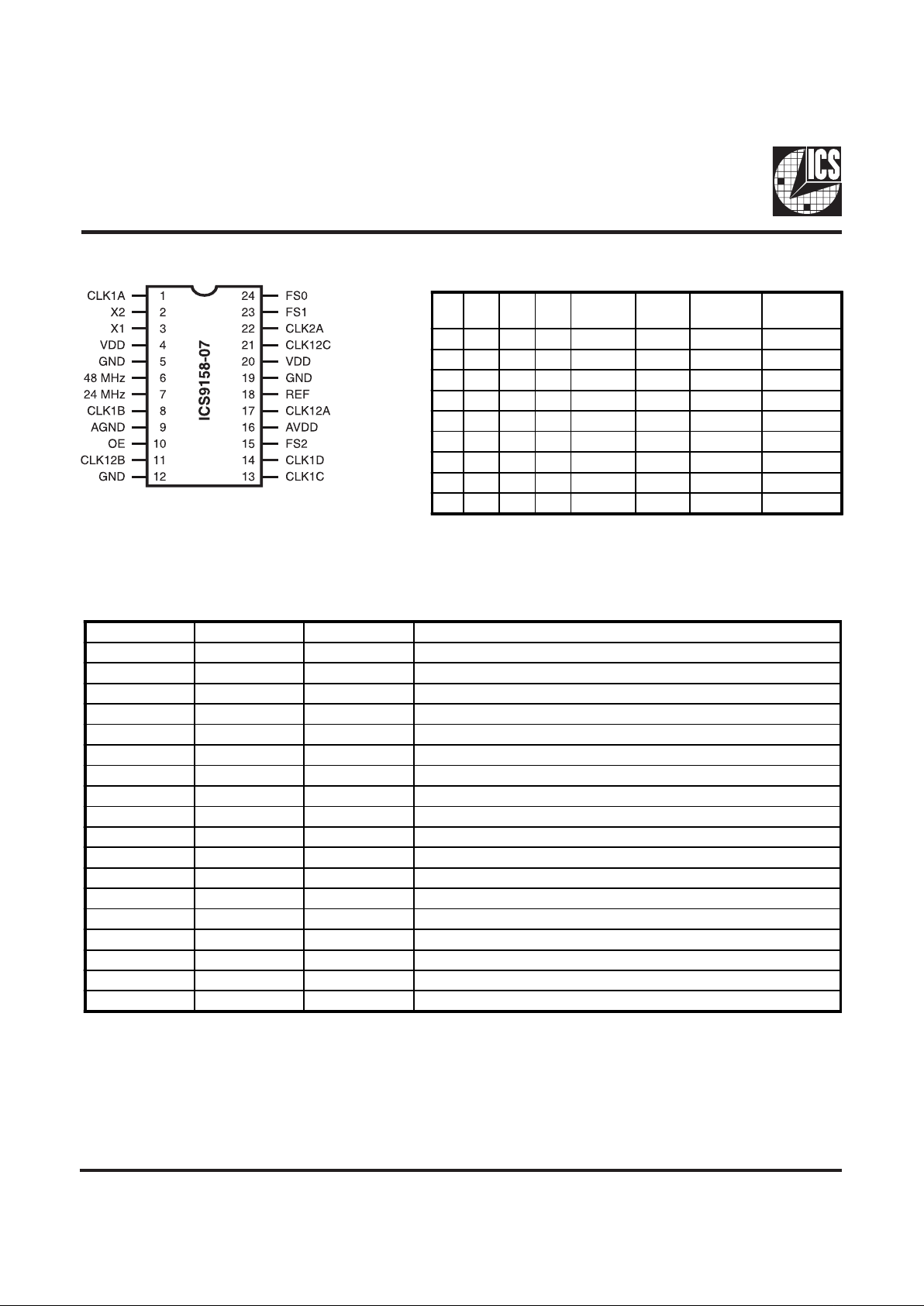

Pin Configuration

Pin Descriptions

24-Pin SOIC

Functionality

VDD=5±10% or 3.3V±10%, TEMP=0-70°C

Note 1: All frequencies in MHz, assuming 14.31818 MHz reference frequency.

Note 2: OE equals Low , tristates CLK2, CLK12(0:2), CLK1(0:3), the REF, 24 MHz

and 48 MHz clocks keep running.

PIN NUMBER PIN NAME TYPE DESCRIPTION

1, 8, 13, 14 CLK1A OUT CPU clock 1 outputs.

2 X2 OUT Crystal connection.

3 X1 IN Crystal connection.

4 VDD PWR Digital POWER SUPPLY (+5V).

5, 12 GND PWR Digital GROUND/

6 48 MHz OUT 48 MHz clock output.

7 24 MHz OUT 24 MHz floppy disk/combination I/O clock output.

9 AGND PWR ANALOG GROUND.

10 OE IN OUTPUT ENABLE. Tristates all cloc k outputs when low.

11, 17, 21, 22 CLK12 OUT CPU clock 12 outputs.

15 FS2 IN CPU clock frequency select 2.

16 AVDD PWR ANALOG power supply (+5V).

18 REF OUT 14.318 MHz reference clock output.

19 GND PWR Digital GROUND.

20 VDD PWR Digital POWER SUPPLY (+5V).

22 CLK2 OUT CPU clock 2 outputs.

23 FS1 IN CPU clock frequency select #1.

24 FS0 IN CPU clock frequency select #0.

OE FS2 FS1 FS0

CLK2

Ratio

CLK2

(Mhz)

CLK1(0:3)

(Mhz)

CLK12(0:2)

(MHz)

1 0 0 0 29/13 X1 31.9 16 31.9

1 0 0 1 29/13 X1 31.9 16 31.9

1 0 1 0 29/13 X1 31.9 16 31.9

1 0 1 1 29/13 X1 31.9 16 31.9

1 1 0 0 14/3 X1 66.8 33.4 66.8

1 1 0 1 7/2 X1 50.1 25 50.1

1 1 1 0 14/3 X1 66.8 33.4 66.8

1 1 1 1 21/5 X1 60.1 30 60.1

0 X X X -- Tristate Tristate Tristate

Loading...

Loading...