Integrated

Circuit

Systems, Inc.

General Description Features

ICS9148-53

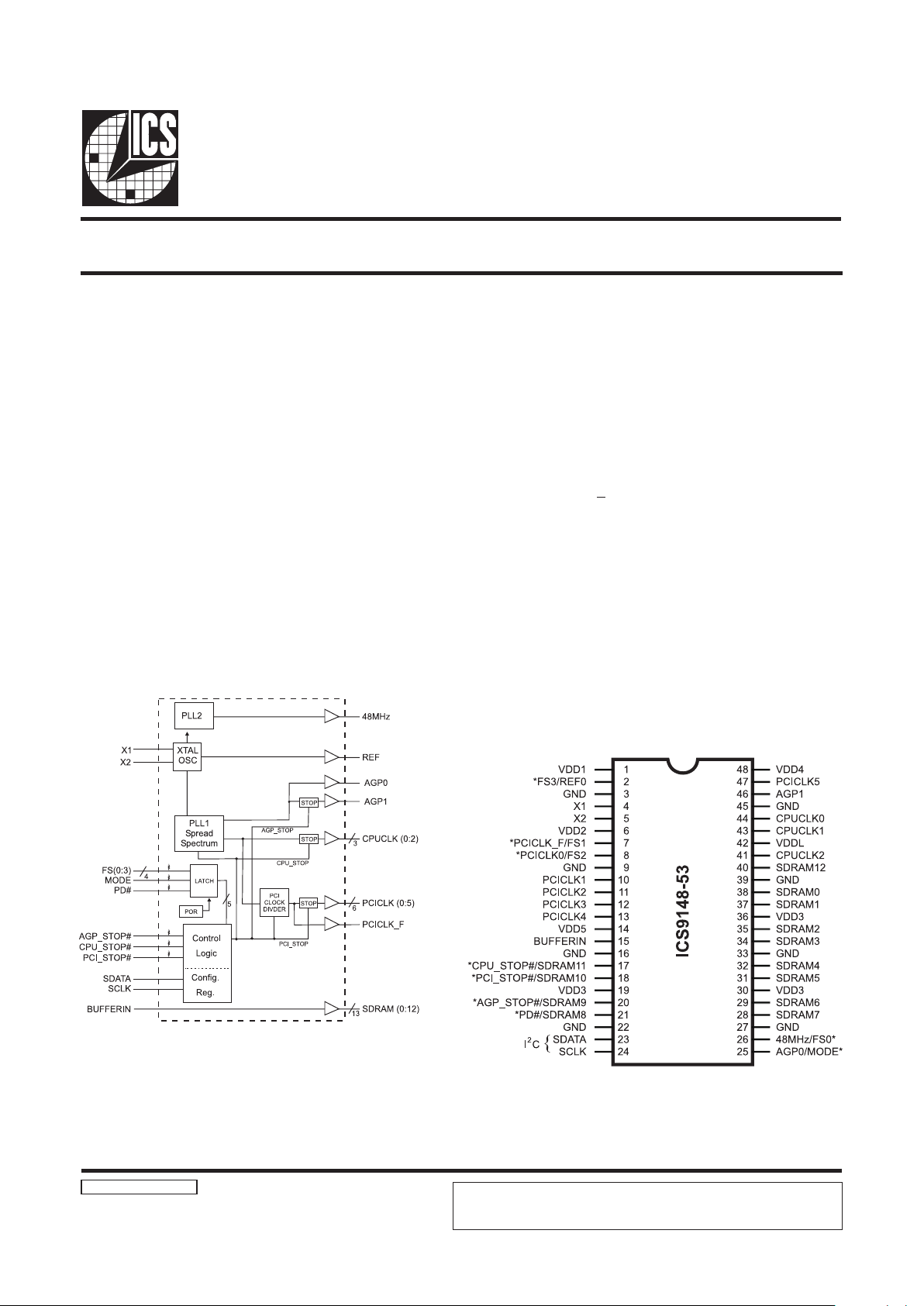

Block Diagram

Pentium is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

Frequency Generator & Integrated Buffers for Mother Boards

9148-53 Rev C 08/14/98

Pin Configuration

48-Pin SSOP

Power Groups

VDD1 = REF (0:1), X1, X2

VDD2 = PCICLK_F, PCICLK(0:5)

VDD3 = SDRAM (0:12), supply for PLL core

VDD4 = AGP (1:2)

VDD5 = Fixed PLL, 48MHz , AGP0

VDDL = CPUCLK (0:3)

* Internal Pull-up Resistor of

240K to 3.3V on indicated inputs

The ICS9148-53 generates all clocks required for high speed

RISC or CISC microprocessor systems such as Intel

PentiumPro, AMD or Cyrix. Sixteen different reference

frequency multiplying factors are externally selectable with

smooth frequency transitions.

Spread spectrum may be enabled through I2C programming.

Spread spectrum typically reduces system EMI by 8dB to

10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9148-53

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

Serial programming I2C interface allows changing functions,

stop clock programming and frequency selection. The

SDRAM12 output may be used as a feed back into an off chip

PLL.

Generates the following system clocks:

- 3 CPU(2.5V/3.3V) up to 150MHz.

- 7 PCI(3.3V) (including one free

running PCICLK)

- 2AGP(3.3V) @ 2 x PCI

- 13 SDRAMs(3.3V) up to 150MHz

- 1 REF (3.3V) @ 14.318MHz

- 1 Fixed clock 3.3V @ 48MHz

Skew characteristics:

- CPU CPU<250ps

- CPU(early) PCI : 1-4ns

Supports Spread Spectrum modulation & I2C

programming for Power Management, Frequency Select

Efficient Power management scheme through power

down CPU, PCI, AGP and CPU_STOP clocks.

Uses external 14.318MHz crystal

48 pin 300mil SSOP.

Read back of FS pin values from I2C

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

2

ICS9148-53

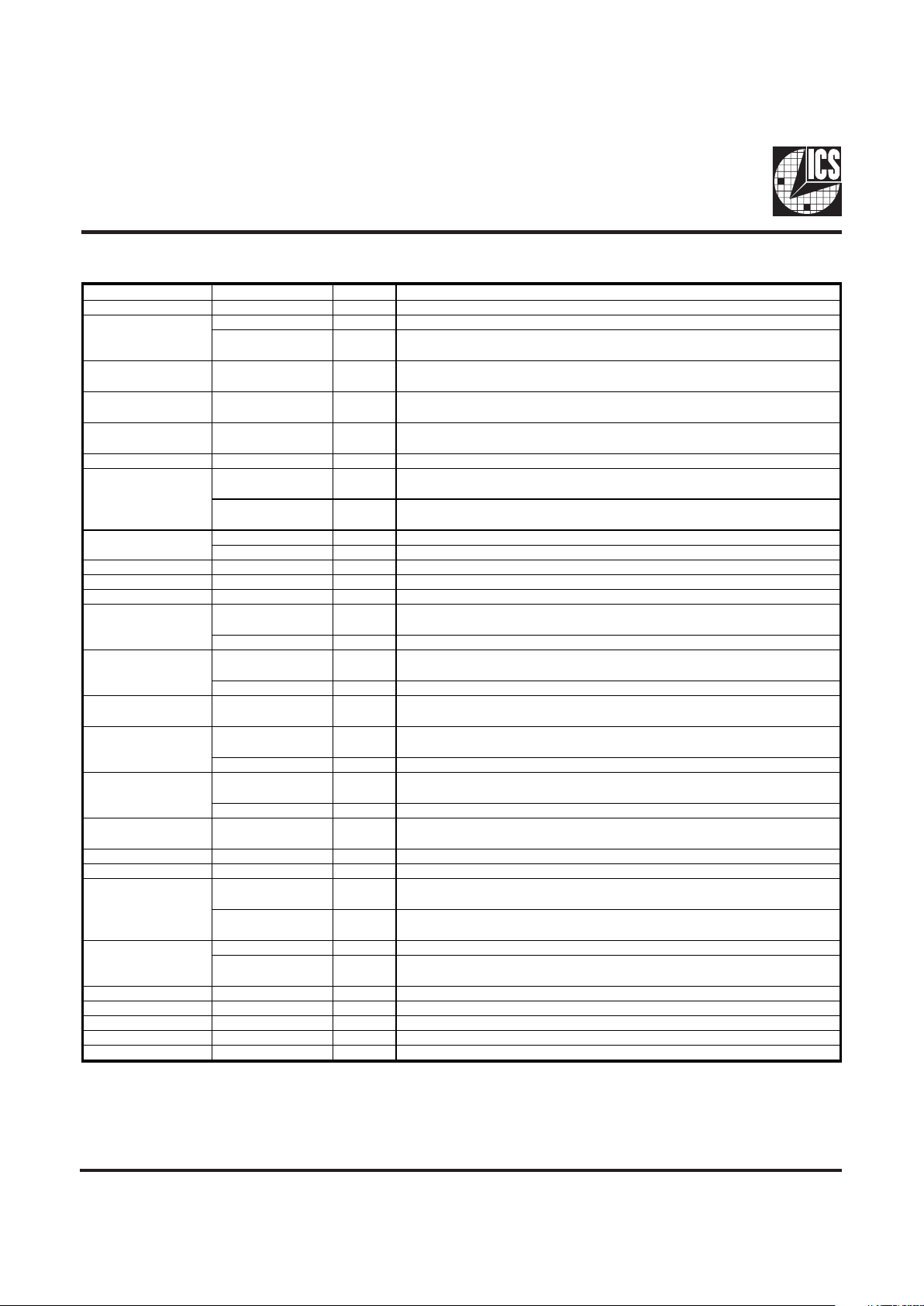

Pin Descriptions

Notes:

1: Internal Pull-up Resistor of 240K to 3.3V on indicated inputs

2: Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor to

program logic Hi to VDD or GND for logic low.

PIN NUMBER PIN NAME TYPE DESCRIPTION

1 VDD 1 PW R Ref (0:2), X TAL power supply, nominal 3.3V

2

REF0 OUT 14.318 MHz reference clock.

FS3 IN

Frequency select pin. Latched Input. Along with other FS pins determins the

CPU, SDRAM, PCI & AGP frewuencies.

3,9,16,22,27,

33,39,45

GND PWR Ground

4X1 IN

Crystal input, has internal load cap (33pF) and feedback

resistor from X2

5 X2 OUT

Crystal output, nominally 14.318MHz. Has internal load

cap (33pF)

6 VDD2 PW R Supply for PCICLK_F and PCICLK (0:5), nom inal 3.3V

7

PCICLK_F OUT

Free running PCI clock output. Synchronous with CPUCLKs with 1-4ns skew

(CPU early) This is not affected by PC I_STOP#

FS1

1, 2

IN

Frequency select pin. Latched Input. Along with other FS pins determins the

CPU, SDRAM, PCI & AGP frewuencies.

8

PCICLK0 OU T P CI clock o utputs. Synchrou nous CP UCLKs w ith 1-4ns s kew (CPU early)

FS2

1, 2

IN Frequency select pin. Latched Input

10, 11, 12, 13, 47 PCICLK(1:5) OU T P CI clock o utputs. Synchrou nous CP UCLKs w ith 1-4ns s kew (CPU early)

14 VDD5 PW R Supply for fixed PLL, 48MHz, AGP0

15 BUFFERIN IN Input pin for SDRAM buffers.

17

CPU_STOP# IN

Halts CPUCLK (0:3 ) clocks at log ic 0 level, when input low (in Mobile

Mode, MODE=0)

SDRAM 11 OU T SDRA M clock output

18

PCI_STOP#

1

IN

Halts PCICLK(0:5) clocks at logic 0 level, when input low (In mobile mode,

MODE=0)

SDRAM 10 OU T SDRA M clock output

28, 29, 31, 32, 34,

35,37,38

SDRAM (0:9) OU T SDRAM clock outputs.

20

AGP _STOP #

1

IN

This asynchronous input halts AGP(1:2) clocks at log ic "0" level when input

low (in Mobile Mode, MODE=0) Does not affect AGP0

SDRAM9 OU T SDRAM clock output

21

PD#

1

IN

This asyncheronous Power Down input S tops the V CO, crystal & internal

clocks when active, Low. (In Mobile Mode, MODE =0)

SDRAM8 OU T SDRAM clock output

19,30,36 VDD3 PW R

Supply for SDRAM (0:11), C PU Core, 4 8MHz cloc ks,

nominal 3.3V.

23 SDATA IN Data input for I

2

C serial input.

24 SCLK IN Clock input of I

2

C input

25

AGP0 OUT

Advanced Graphic Port output, powered by VDD4. Not affected by

AGP_S TO P #

MODE

1, 2

IN

Pin 17, 18, 20 & 21 function select pin, 1=Desk top Mode, 0=Mo bile Mode.

Latched Input.

26

48MHz OU T 48MHz output clock for USB timing.

FS0

1, 2

IN

Frequency select pin. Latched Input. Along with other FS pins determins the

CPU, SDRAM, PCI & AGP frewuencies.

41, 43, 44 CPUCLK(0:3) OU T CPU cloc k outputs, powered by VDDL 2. Low if CPU_STOP#=Low

40 SDR AM12 OU T Fe edback SDR AM clock outpu t.

42 VDDL PWR Supply for CPU (0:3), either 2.5V or 3.3V nominal

46 AGP1 OUT Advanced Graphic Port output powered by VDD4.

48 V D D 4 PW R Sup ply for AGP (0:2 )

3

ICS9148-53

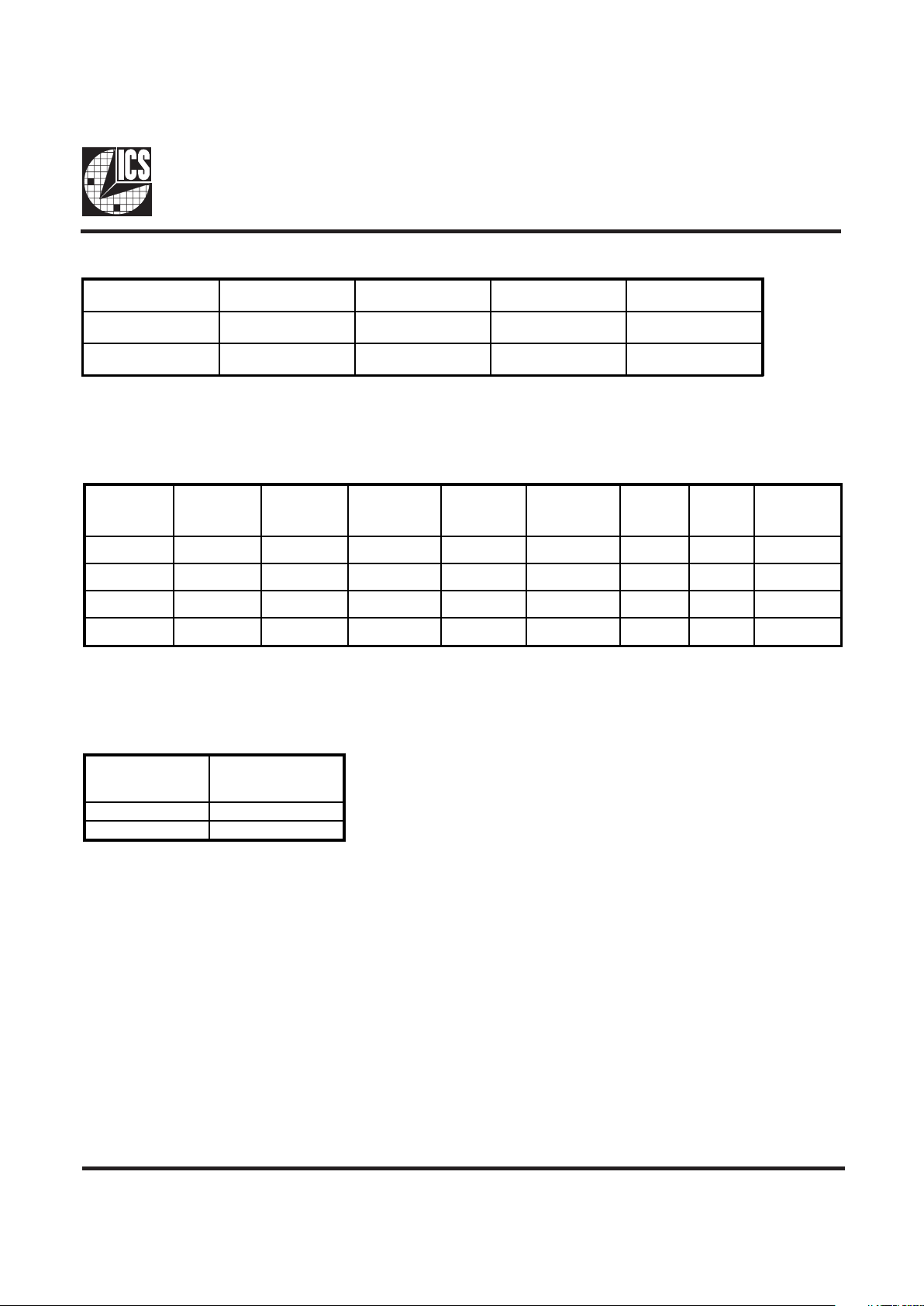

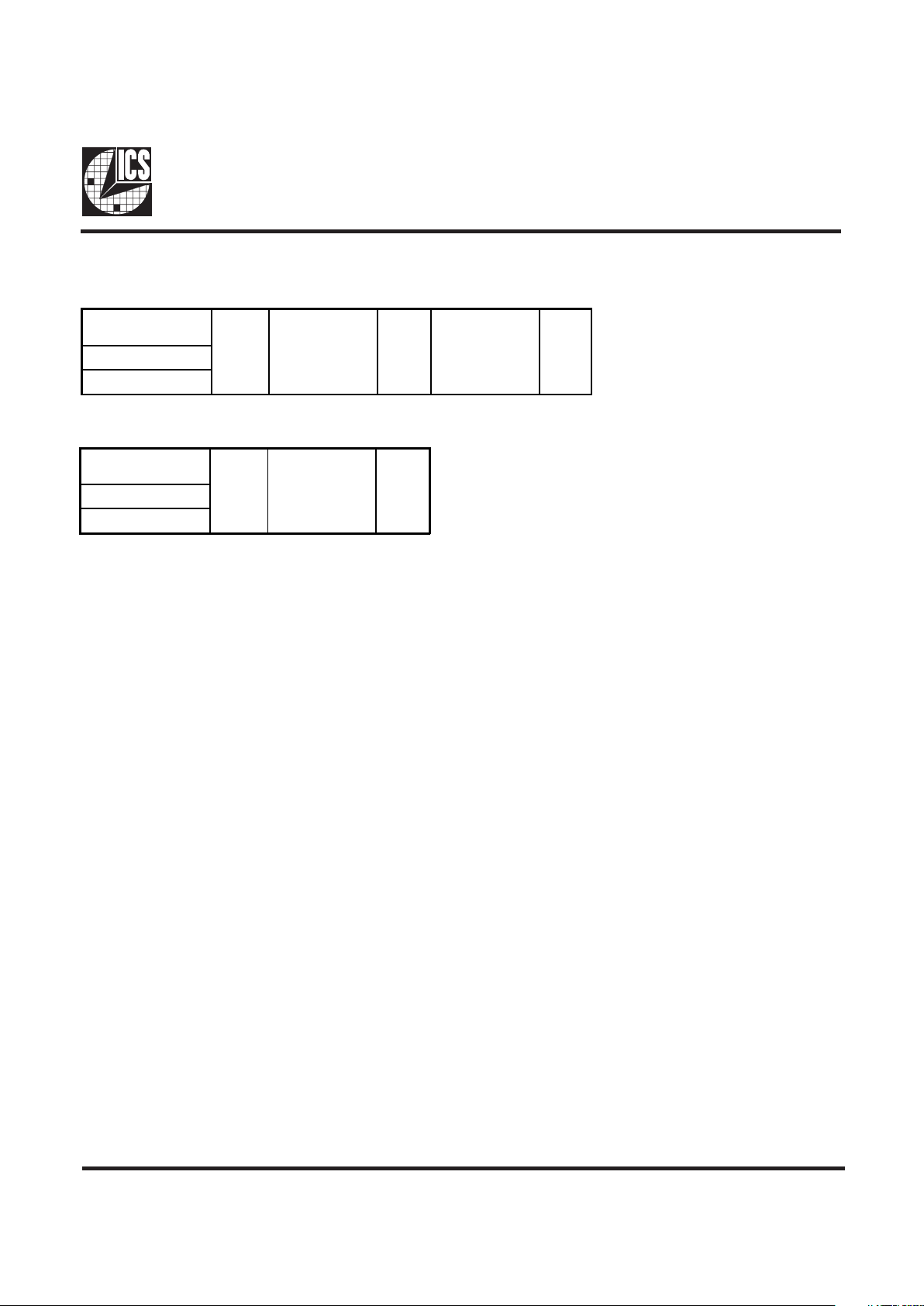

CPU3.3#_2.5

Input level

(Latch ed Data )

Buffer Selected for

operation at:

12.5V VDD

03.3V VDD

CPU 3.3#_2.5V Buffer selector for CPUCLK drivers.

Power Management Functionality

Mode Pin - Power Management Input Control

MODE, Pin 25

(Latched Input)

Pin 17 Pin 18 Pin 20 Pin 21

0

CPU_STOP#

(INPUT)

PCI_STOP#

(INPUT)

AGP_STOP#

(INPUT)

PD#

(INPUT)

1

SDRAM 11

(OUTPUT)

SDRAM 10

(OUTPUT)

SDRAM 9

(OUTPUT)

SDRAM 8

(OUTPUT)

AGP_STOP# CPU_STOP# PCI_STOP#

AGP,

CPUCLK

Outputs

PCICLK

(0:5)

PCICLK_F,

REF, 48MHz

and SDRAM

Crystal

OSC

VCO AGP(1:2)

1 0 1 Stopped Low Running Running Running Running Running

1 1 1 Running Running Running Running Running Running

1 1 0 Running Stopped Low Running Running Running Running

0 1 1 Running Running Running Running Running Stopped Low

4

ICS9148-53

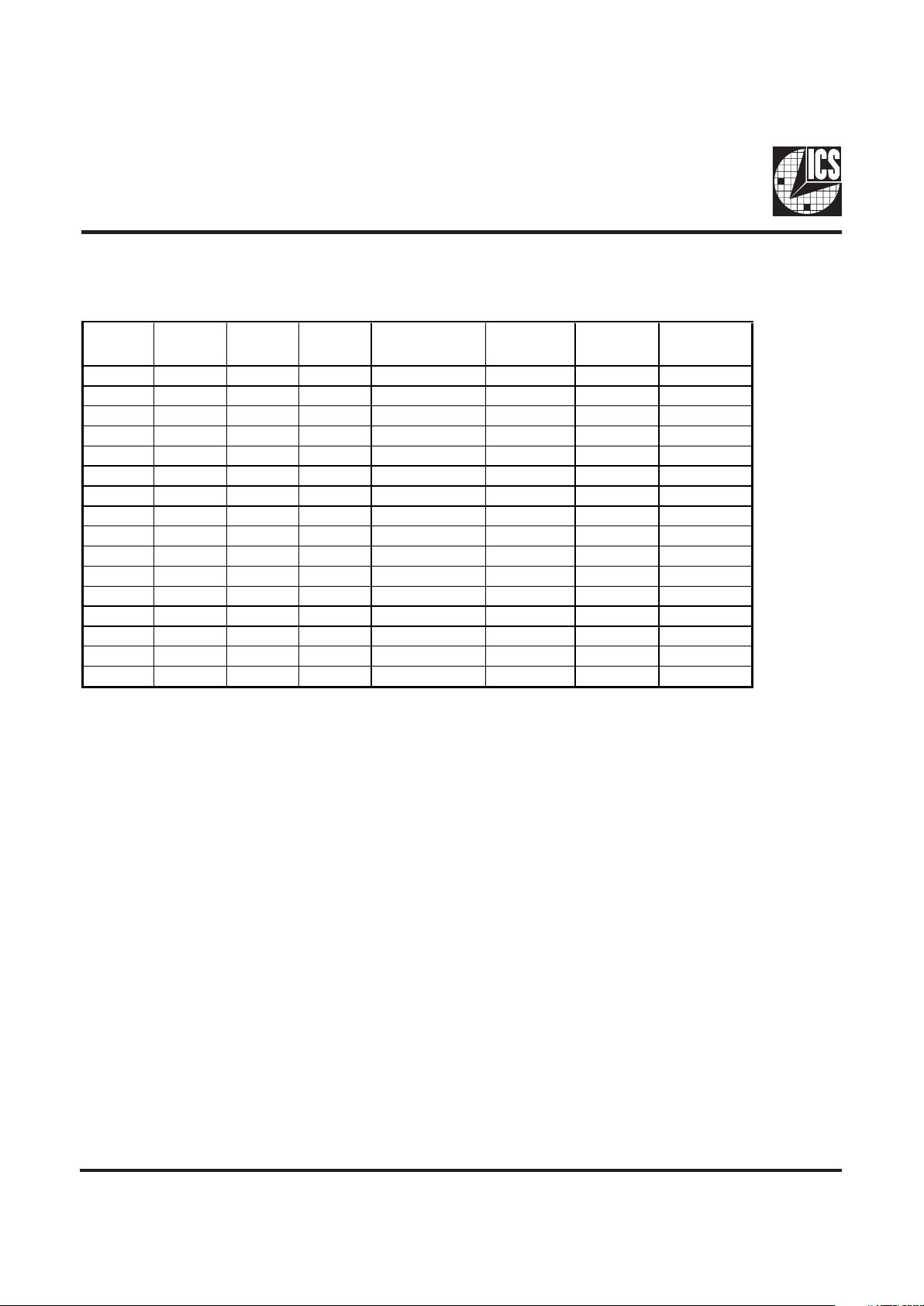

Functionality

VDD1, 2, 3, 4 = 3.3V±5%, TA= 0 to 70°C

Crystal (X1, X2) = 14.31818MHz

FS3 FS2 FS1 FS0

CPU,SDRAM

(MHZ) PCI (MHZ) AGP (M HZ)

REF, IOAPIC

(MHZ)

1111 133 44.3388.6714.318

1110 124 41.3382.6714.318

1101 150 5010014.318

1100 140 46.6793.3314.318

1011 105 35 7014.318

1010 112 37.3374.6714.318

1001 115 38.3376.6614.318

1000 120 40 8014.318

0111 100 33.366.614.318

0110 95.2531.7563.514.318

0101 83.3 33.366.614.318

0100 75 30 6014.318

0011 75 37.57514.318

0010 68.5 34.2568.514.318

0001 66.8 33.466.814.318

0000

60 30 60 14. 318

5

ICS9148-53

General I2C serial interface information

A. For the clock generator to be addressed by an I2C controller, the following address must be sent as a start sequence, with

an acknoledge bit between each byte.

B. The clock generator is a slave/receiver I2C component. It can read back the data stored in the latches for verification. (set

R/W# to 1 above) Read-Back will support Intel PIIX4 "Block-Read" protocol, with a "Byte count" following the

address with R/W#=1, then proceding to Byte 0, 1, 2, ...until STOP.

C. The data transfer rate supported by this clock generator is 100K bits/sec (standard mode)

D. The input is operating at 3.3V logic levels.

E. The data byte format is 8 bit bytes.

F. To simplify the clock generator I2C interface, the protocol is set to use only "Block Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

G. The Fixed clocks 48MHz and 24MHz are not addressable in the registers for Stopping. These output are always running,

except in Tristate Mode.

H. At power-on, all registers are set to a default condition. Byte 0 defaults to a 0, Bytes 1 through 5 default to a 1

(Enabled output state).

Then Byte 0, 1, 2, etc in

sequence until STOP.

Clock Generator

Address (7 bits)

ACK

+ 8 bits dummy

command code

ACK

+ 8 bits dummy

Byte count

ACK

A(6:0) & R/W#

D2

(H)

Then Byte 0, 1, 2, etc. in

sequence until STOP.

Clock Generat or

Address (7 bits)

ACK

Byte Count

Readback

ACK

A(6:0) & R/W#

D3

(H)

6

ICS9148-53

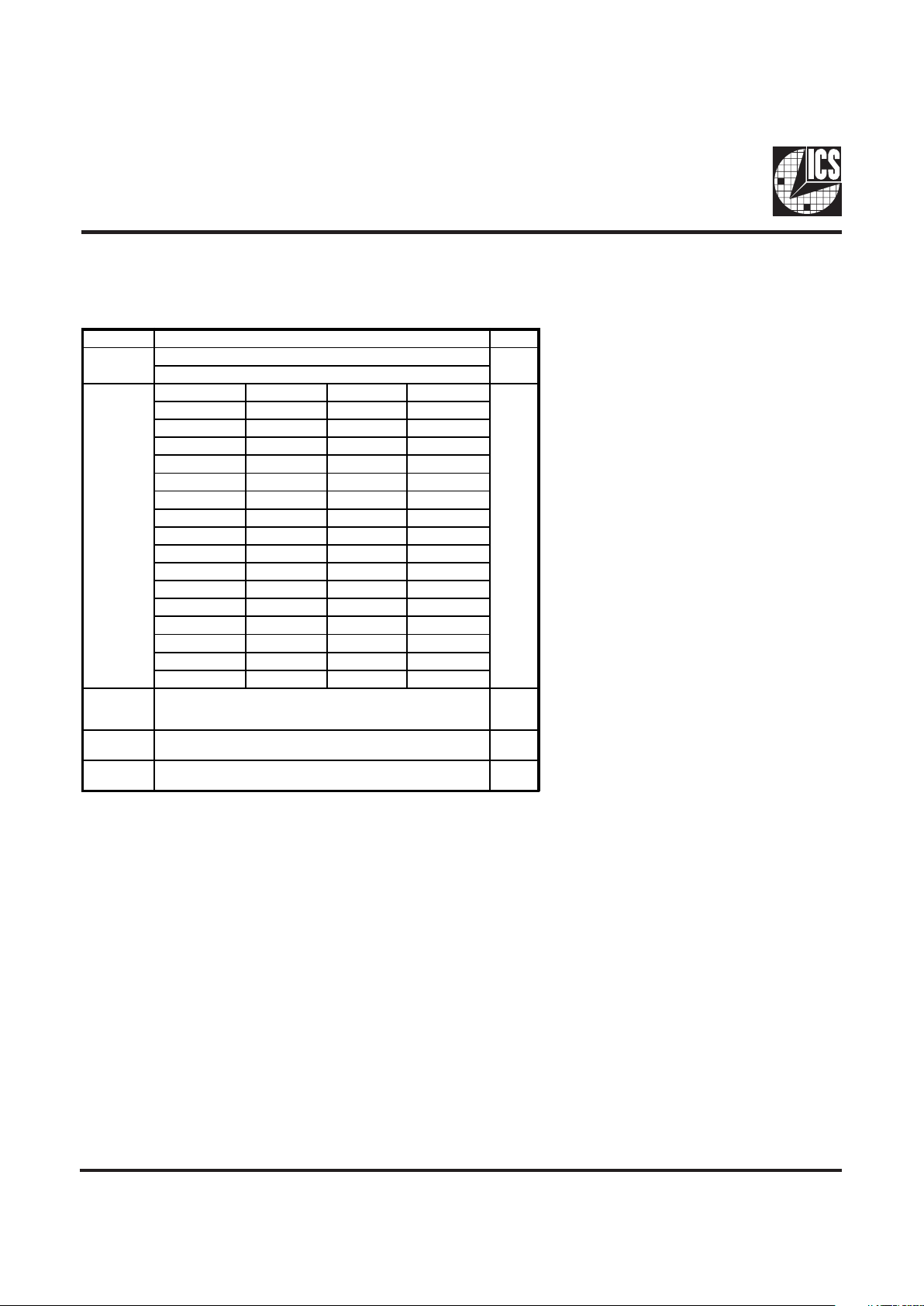

Byte0: Functionality and Frequency Select Register (default = 0)

Serial Configuration Command Bitmap

I2C is a trademark of Philips Corporation

Note 1: Default at power-up will be for latched logic inputs to define frequency;

Bits 2, 6:4 are default to 000

Note: PWD = Power-Up Default

Bit Description PWD

Bit 7

0 - ±0.25% Spread Spectrum Modulation

0

1 - ±0.6% Spread Spectrum Modulation

Bit

(2, 6:4)

Bit (2, 6:4) CPU CLKs PC I CLKs AGP CLKs

Note1

1111 133 44.33 88.67

1110 124 41.33 82.67

1101 150 50 1 00

1100 140 46.67 93.33

1011 105 35 70

1010 112 37.33 74.67

1001 115 38.33 76.66

1000 120 40 80

0111 100 33.33 66.60

0110 9 5.25 3 1.75 63.50

0101 83.3 33.30 66.60

0100 75 30.00 60.00

0011 75 37.50 75.00

0010 68.5 34.25 68.50

0001 66.8 33.40 66.80

0000 60 30.00 60.00

Bit 3

0 - Frequency is selected by hardware select,

Latched Inputs

1 - Frequency is selected by Bit 6:4 (above)

0

Bit 1

0 - Normal

1 - Spread Spectrum Enabled (center spread)

0

Bit 0

0 - Running

1- Tristate all outputs

0

Loading...

Loading...