Integrated

Circuit

Systems, Inc.

General Description Features

ICS9148-10

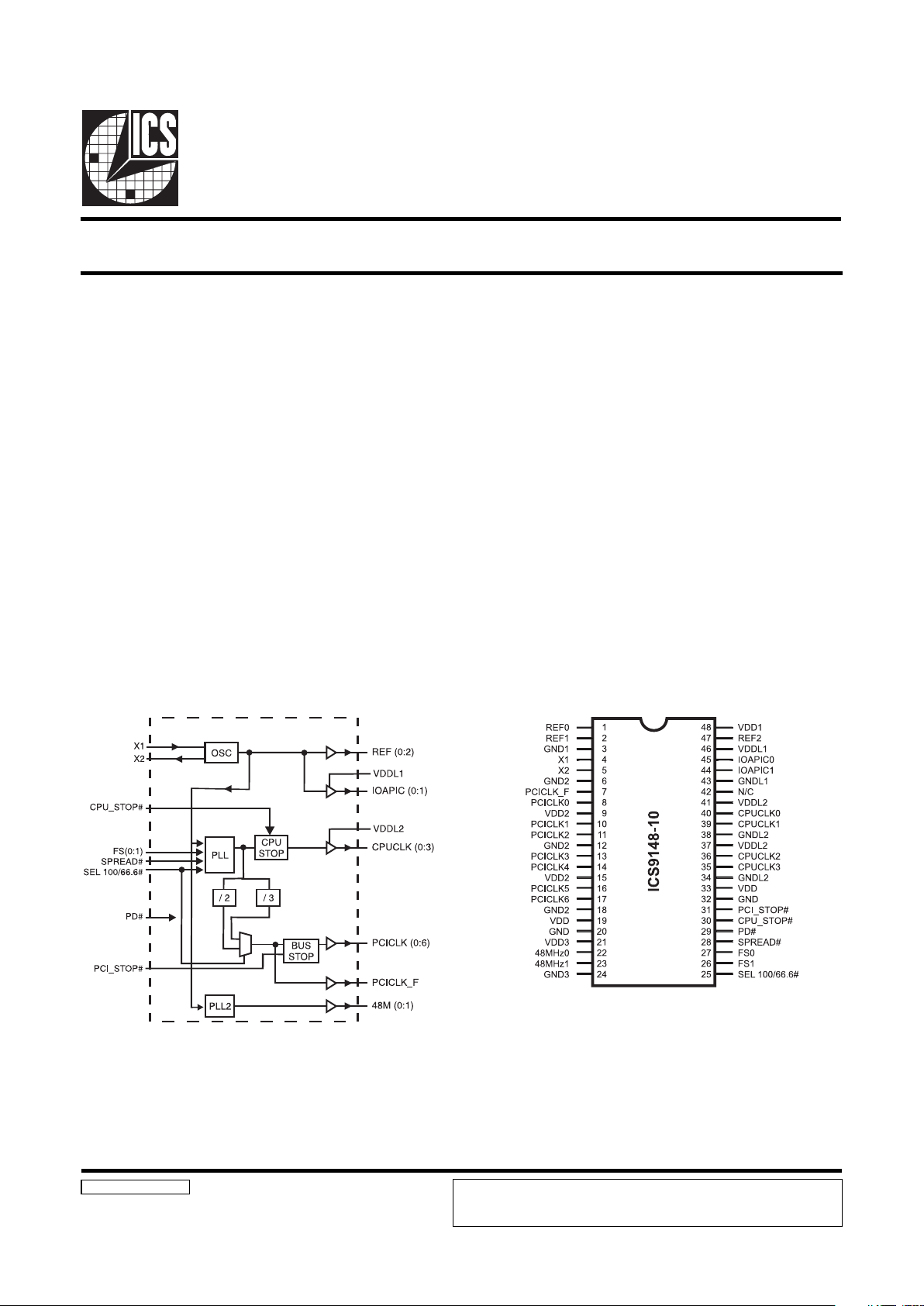

Block Diagram

Pentium/ProTM System Clock Chip

9148-10 Rev D 9/27/99

Pin Configuration

48-Pin SSOP

Pentium is a trademark on Intel Corporation.

Generates system clocks for CPU, IOAPIC, PCI, plus

14.314 MHz REF (0:2), USB, and Super I/O

Supports single or dual processor systems

Supports Spread Spectrum modulation for CPU & PCI

clocks, down spread -1%

Skew from CPU (earlier) to PCI clock (rising edges for

100/33.3MHz) 1.5 to 4ns

Two fixed outputs at 48MHz.

Separate 2.5V and 3.3V supply pins

2.5V or 3.3V output: CPU, IOAPIC

3.3V outputs: PCI, REF, 48MHz

No power supply sequence requirements

Uses external 14.318MHz crystal, no external load cap

required for CL=18pF crystal

48 pin 300 mil SSOP

The ICS9148-10 is a Clock Synthesizer chip for Pentium and

PentiumPro CPU based Desktop/Notebook systems that will

provide all necessary clock timing.

Features include four CPU and eight PCI clocks. Three

reference outputs are available equal to the crystal frequency.

Additionally, the device meets the Pentium power-up

stabilization requirement, assuring that CPU and PCI clocks

are stable within 2ms after power-up.

PD# pin enables low power mode by stopping crystal OSC

and PLL stages. Other power management features include

CPU_STOP#, which stops CPU (0:3) clocks, and PCI_STOP#,

which stops PCICLK (0:6) clocks.

High drive CPUCLK outputs typically provide greater than 1

V/ns slew rate into 20pF loads. PCICLK outputs typically

provide better than 1V/ns slew rate into 30pF loads while

maintaining 50±5% duty cycle. The REF clock outputs

typically provide better than 0.5V/ns slew rates.

The ICS9148-10 accepts a 14.318MHz reference crystal or

clock as its input and runs on a 3.3V core supply.

Power Groups

VDD = Supply for PLL core

VDD1 = REF (0:2), X1, X2

VDD2 = PCICLK_F, PCICLK (0:6)

VDD3 = 48MHz0, 48MHz1

VDDL1 = IOAPIC (0:1)

VDDL2 = CPUCLK (0:3)

Ground Groups

GND = Ground for PLL core

GND1 = REF (0:2), X1, X2

GND2 = PCICLK_F, PCICLK (0:6)

GND3 = 48MHz0, 48MHz1

GNDL1 = IOAPIC (0:1)

GNDL2 = CPUCLK (0:3)

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

2

ICS9148-10

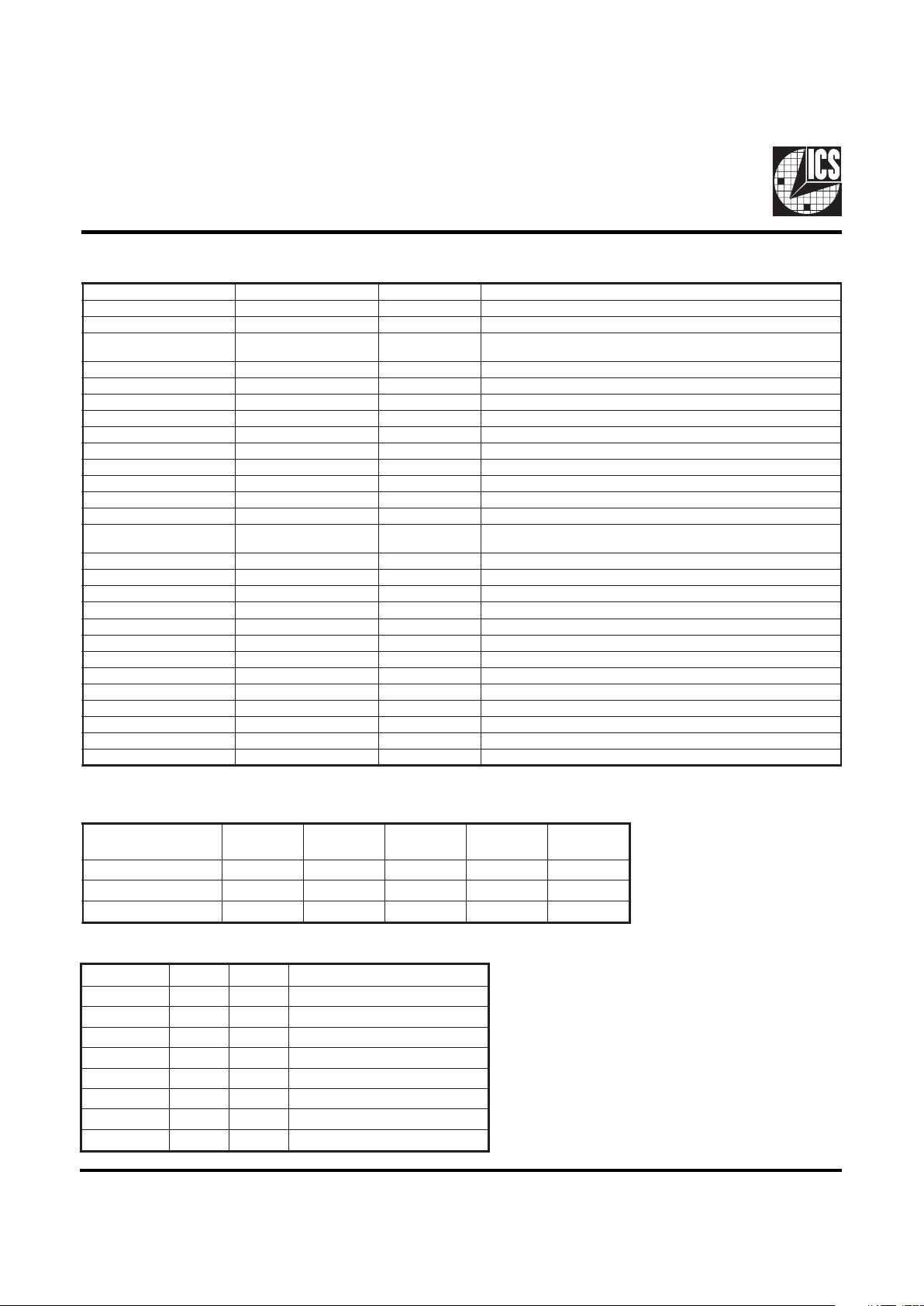

Pin Descriptions

Select Functions

Notes:

1. TCLK is a test clock driven on the X1 (crystal in

pin) input during test mode.

2. -1% modulation down spread from the selected

frequency.

3. Performance not guaranteed

ytilanoitcnuFUPC

,ICP

F_ICP

FERCIPAOI

zHM84

noitceleS

etatsirTZ-IHZ-IHZ-IHZ-IHZ-IH

edomtseT2/KLCT

1

6/KLCT

1

KLCT

1

KLCT

1

2/KLCT

1

murtcepSdaerpSdetaludoM

2

detaludoM

2

zHM813.41zHM813.41zHM0.84

#66/001LES1SF0SFnoitcnuF

000 etatS-irT

001 7.95

3

010 6.47

3

011 ICP3.33,UPCzHM6.66evitcA

100 edoMtseT

101 3.331

3

110 9.28

3

111 ICP3.33,UPCzHM001evitcA

REBMUNNIPEMANNIPEPYTNOITPIRCSED

74,2,1)2:0(FERTUOtuptuokcolczHM813.41

31DNGRWPstuptuoFERrofdnuorG

41XNI

daolFp33lanretnisah,tupnilatsyrCzHM813.41NI_LATX

2Xmorfrotsiserkcabdeefdnapac

52XTUOFp33pacdaollanretnisah,tuptuolatsyrCTUO_LATX

81,21,62DNGRWPstuptuoICProfdnuorG

7F_KLCICPTUOtuptuoICPgninnuReerF

71,61,41,31,11,01,8)6:0(KLCICPTUOV3.3elbitapmocLTT.stuptuokcolcICP

51,92DDVRWPV3.3yllanimon,stuptuoKLCICProfrewoP

33,91DDVRWPV3.3yllanimon,erocrofrewopdetalosI

23,02DNGRWPerocrofdnuorgdetalosI

123DDVRWPV3.3yllanimon,stuptuozHM84rofrewoP

32,22)1:0(zHM84TUOstuptuozHM84

423DNGRWPstuptuozHM84rofdnuorG

52#6.66/001LESNI

zHM6.66rozHM001gnilbanerofniptceleS

)zHM3.33suonorhcnyssyawlaICP(zHM6.66=L,zHM001=H

72,62)1:0(SFNIsniptceleSycneuqerF

82#DAERPSNIWOLnehwerutaefmurtcepSdaerpSselbanE

92#DPNIwolevitca,pihcnwodsrewoP

03#POTS_UPCNIwolnehwlevel"0"cigoltaskcolcUPCstlaH

13#POTS_ICPNIwolnehwlevel"0"cigoltasuBICPstlaH

14,732LDDVRWPV5.2yllanimon,stuptuoUPCrofrewoP

83,432LDNGRWP.stuptuoUPCrofdnuorG

04,93,63,53)0:3(KLCUPCTUOV5.2@stuptuokcolctsoHdnaUPC

24C/N- detcennocyllanretnitoN

341LDNGRWPstuptuoCIPAOIrofdnuorG

54,44)1:0(CIPAOITUOV5.2@)zHM813.41(stuptuoCIPAOI

641LDDVRWPV5.2yllanimon,stuptuoCIPAOIrofrewoP

841DDVRWPV3.3lanimon,2X,1X,)2:0(FERrofylppuS

3

ICS9148-10

T echnical Pin Function Descriptions

VDD(1,2,3)

This is the power supply to the internal core logic of the

device as well as the clock output buffers for REF(0:2),

PCICLK_F, PCICLK (0:6), 48MHz0, 48MHz1.

This pin operates at 3.3V volts. Clocks from the listed buffers

that it supplies will have a voltage swing from Ground to this

level. For the actual guaranteed high and low voltage levels

for the Clocks, please consult the DC parameter table in this

data sheet.

VDDL1,2

This is the power supply for the CPUCLK (0:3) and IOAPIC

output buffers. The voltage level for these outputs may be

2.5 or 3.3volts. Clocks from the buffers that each supplies will

have a voltage swing from Ground to this level. For the actual

Guaranteed high and low voltage levels of these Clocks,

please consult the DC parameter table in this Data Sheet.

GND (1,2,3)

This is the ground to the internal core logic of the device as

well as the clock output buffers for REF(0:2), PCICLK_F,

PCICLK (0:6), 48MHz 0, 48MHz1.

GNDL (1,2)

This is the ground for the CPUCLK (0:3) and IOAPIC output

buffers.

X1

This input pin serves one of two functions. When the device

is used with a Crystal, X1 acts as the input pin for the

reference signal that comes from the discrete crystal. When

the device is driven by an external clock signal, X1 is the

device input pin for that reference clock. This pin also

implements an internal Crystal loading capacitor that is

connected to ground. With a nominal value of 33pF no

external load cap is needed for a CL=17 to 18pF crystal.

X2

This Output pin is used only when the device uses a Crystal

as the reference frequency source. In this mode of operation,

X2 is an output signal that drives (or excites) the discrete

Crystal. The X2 pin will also implement an internal Crystal

loading capacitor nominally 33pF.

CPUCLK (0:3)

These Output pins are the Clock Outputs that drive processor

and other CPU related circuitry that requires clocks which are

in tight skew tolerance with the CPU clock. The voltage

swing of these Clocks is controlled by the Voltage level

applied to the VDDL2 pin of the device. See the Functionality

Table for a list of the specific frequencies that are available

for these Clocks and the selection codes to produce them.

48MHz (0:1)

This is a fixed frequency Clock output that is typically used

to drive Super I/O devices. Outputs 0 and 1 are defined as

48MHz.

IOAPIC (0:1)

This Output is a fixed frequency Output Clock that runs at

the Reference Input (typically 14.31818MHz) . Its voltage

level swing is controlled by VDDL1 and may operate at 2.5 or

3.3volts.

REF(0:2)

The REF Outputs are fixed frequency Clocks that run at the

same frequency as the Input Reference Clock X1 or the

Crystal (typically 14.31818MHz) attached across X1 and X2.

PCICLK_F

This Output is equal to PCICLK(0:6) and is FREE RUNNING,

and will not be stopped by PCI_STOP#.

PCICLK (0:6)

These Output Clocks generate all the PCI timing requirements

for a Pentium/Pro based system. They conform to the current

PCI specification. They run at 33.3 MHz.

SELECT 100/66.6MHz#

This Input pin controls the frequency of the Clocks at the

CPUCLK, PCICLK and SDRAM output pins. If a logic 1

value is present on this pin, the 100MHz Clock will be selected.

If a logic 0 is used, the 66.6MHz frequency will be selected.

The PCI clock is multiplexed to be 33.3MHz for both select

cases. PCI is synchronous at the rising edge of PCI to the

CPU rising edge (with the skew making CPU early).

PWR_DWN#

This is an asynchronous active Low Input pin used to Power

Down the device into a Low Power state by not removing the

power supply. The internal Clocks are disabled and the VCO

and Crystal are stopped. Powered Down will also place all

the Outputs in a low state at the end of their current cycle.

The latency of Power Down will not be greater than 3ms.

CPU_STOP#

This is a synchronous active Low Input pin used to stop the

CPUCLK clocks in an active low state. All other Clocks

including SDRAM clocks will continue to run while this

function is enabled. The CPUCLKs will have a turn ON

latency of at least 3 CPU clocks.

PCI_STOP#

This is a synchronous active Low Input pin used to stop the

PCICLK clocks in an active low state. It will not affect

PCICLK_F nor any other outputs.

4

ICS9148-10

Power Management

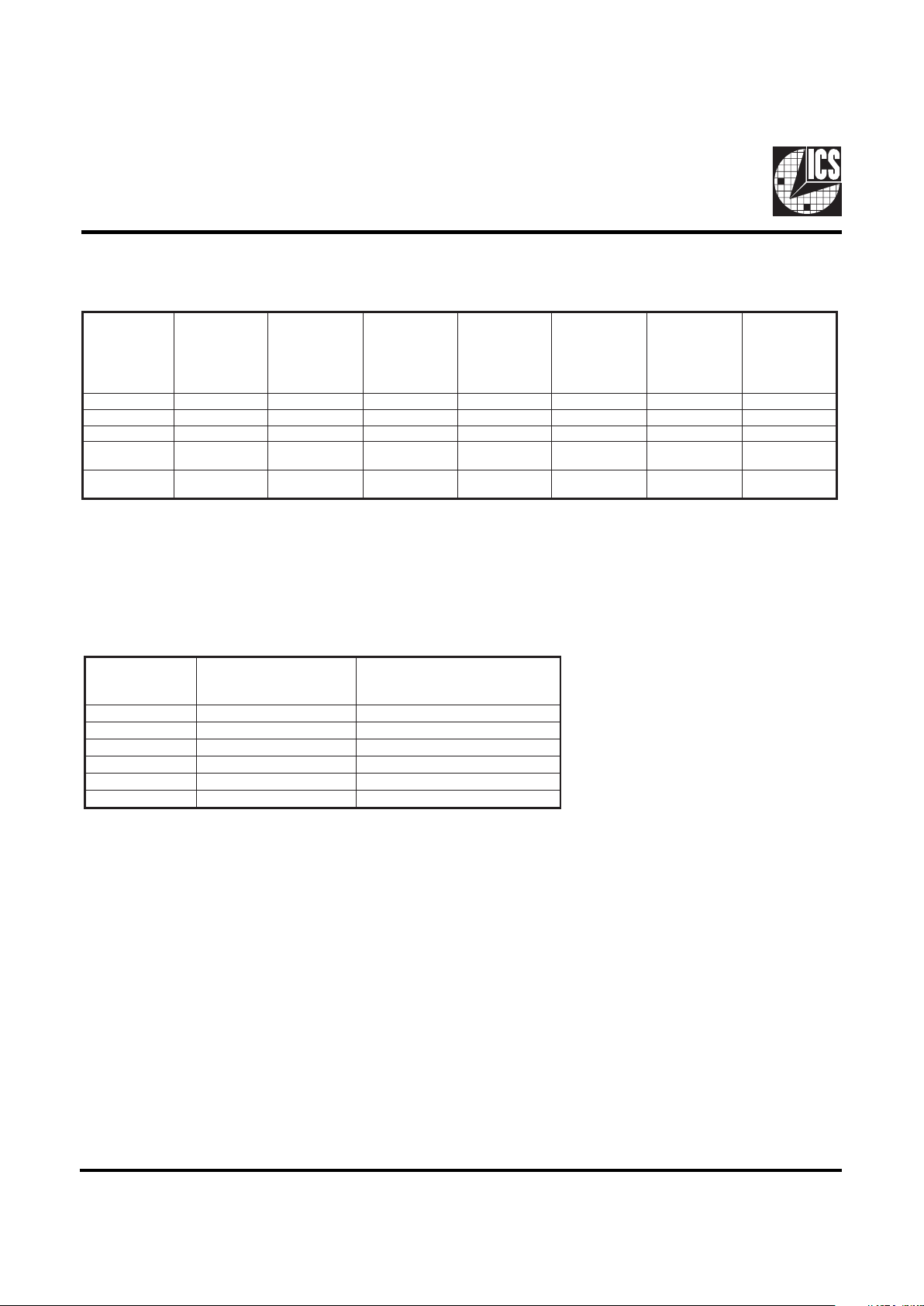

ICS9148-10 Power Management Requirements

Clock Enable Configuration

Full clock cycle timing is guaranteed at all times after the system has initially powered up except where noted. During power

up and power down operations using the PD# select pin will not cause clocks of a shorter or longer pulse than that of the

running clock. The first clock pulse coming out of a stopped clock condition may be slightly distorted due to clock network

charging circuitry. Board routing and signal loading may have a large impact on the initial clock distortion also.

Notes.

1. Clock on latency is defined from when the clock enable goes active to when the first valid clock comes out of the device.

2. Clock off latency is defined from when the clock enable goes inactive to when the last clock is driven low out of the device.

3. Power up latency is when PD# goes inactive (high) to when the first valid clocks are output by the device.

4. Power down has controlled clock counts applicable to CPUCLK, PCICLK only.

The REF and IOAPIC will be stopped independent of these.

LANGISETATSLANGIS

ycnetaL

eerffosegdegnisirfo.oN

KLCICPgninnur

#POTS_UPC)delbasiD(0

2

1

)delbanE(1

1

1

#POTS_ICP)delbasiD(0

2

1

)delbanE(1

1

1

#DP)noitarepOlamroN(1

3

sm3

)nwoDrewoP(0

4

xam2

-OTS_UPC

#P

#POTS_ICP

-NWD_RWP

#

KLCUPCKLCICP

rehtO

,skcolC

,FER

,sCIPAOI

0zHM84

1zHM84

latsyrCsOCV

XX 0 woLwoLdeppotSffOffO

00 1 woLwoLgninnuRgninnuRgninnuR

011 woLzHM3.33gninnuRgninnuRgninnuR

10 1

-HM6.66/001

z

woLgninnuRgninnuRgninnuR

111

-HM6.66/001

z

zHM3.33gninnuRgninnuRgninnuR

Loading...

Loading...