Integrated

Circuit

Systems, Inc.

General Description Features

ICS9147-09

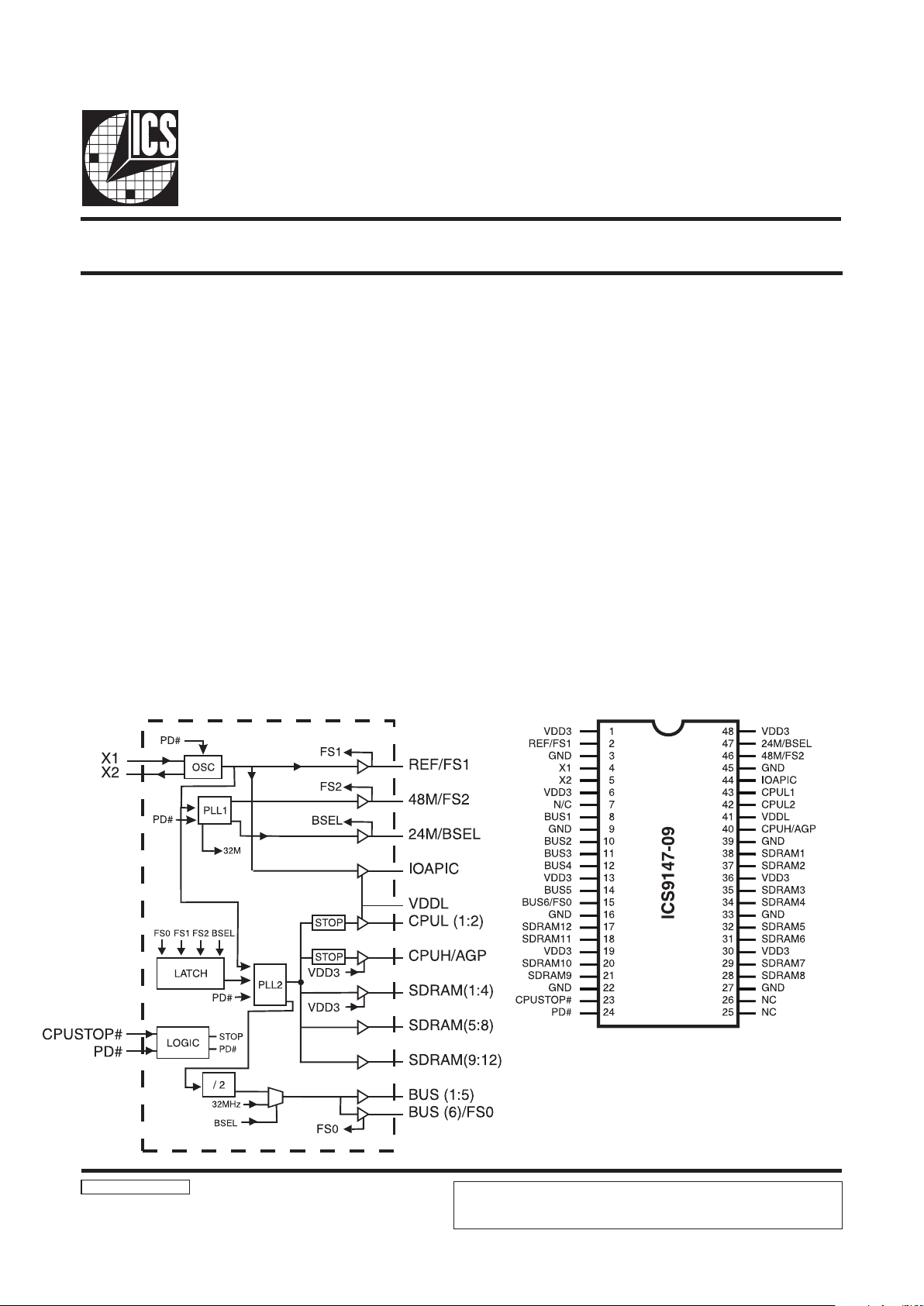

Block Diagram

Pentium is a trademark of Intel Corporation

Frequency Generator & Integrated Buffers for 686 Series CPUs

9147-09 Rev A 10/2897P

Pin Configuration

The ICS9147-09 generates all clocks required for high

speed RISC or CISC microprocessor systems such as Intel

PentiumPro, AMD or Cyrix processors. Four bidirectional I/O

pins (FS0, FS1, FS2, BSEL) are latched at power-on to the

functionality table. The Six BUS clocks can be selected as

either synchronous at 1/2 CPU speed or asynchronous at

32MHz selected by BSEL latched input.The inputs provide

for tristate and test mode conditions to aid in system level

testing.These multiplying factors can be customized for

specific applications. Glitch-free stop clock controls

provided for CPU.

High drive BUS and SDRAM outputs typically provide

greater than 1 V/ns slew rate into 30 pF loads. CPU outputs

typically provide better than 1V/ns slew rate into 20pF

loads while maintaining 50±5% duty cycle. The REF clock

outputs typically provide better than 0.5V/ns slew rates.

Seperate buffer supply pin VDDL allows for nominal 3.3V

voltage or reduced voltage swing (from 2.9 to 2.5V) for

CPUL (1:2) and IOAPIC outputs.

Total of 15 CPU speed clocks:

- Two copies of CPU clock with VDDL (2.5 to 3.3V)

- Twelve (12) SDRAM (3.3v) plus one

CPUH/AGP (3.3V) clocks

Six copies of BUS clock (synchronous with CPU clock/2 or

asynchronous 32 MHz)

250ps output skew window for CPU andSDRAM clocks

and 500ps window BUS clocks. CPU clocks to

BUSclocks skew 1-4ns (CPU early)

Two copies of Ref. clock @14.31818 MHz (One driven

by VDDL as IOAPIC)

One 48 MHz (3.3 V TTL) for USB support and single

24 MHz.

Separate VDDL for CPUL (1:2) clock buffers and

IOAPIC to allow 2.5V output (or Std. Vdd)

3.0V 3.7V supply range w/2.5V compatible outputs

48-pin SSOP package

48-Pin SSOP

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

2

ICS9147-09

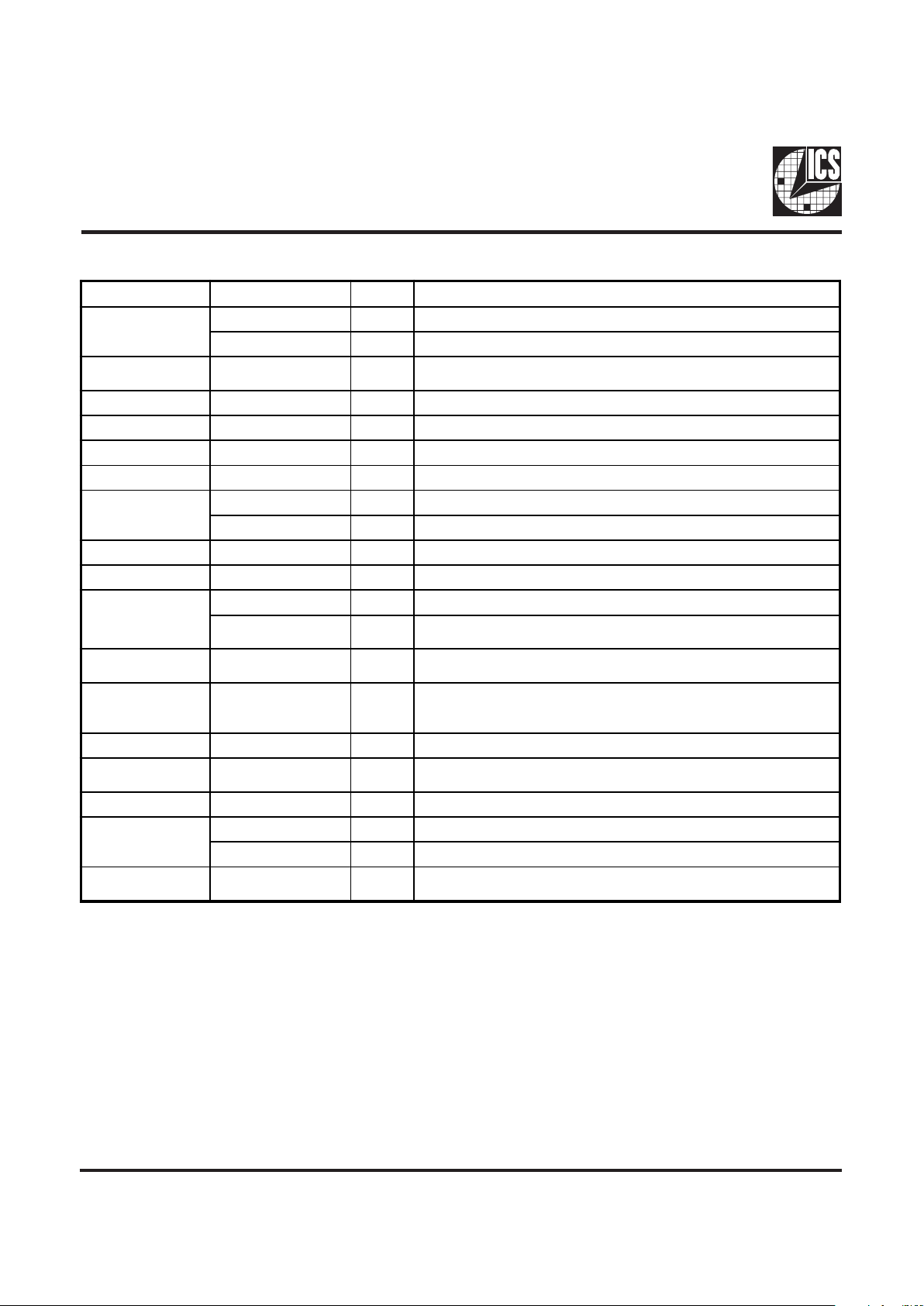

Pin Descriptions

* Bidirectional input/output pins, input logic level determined at internal power-on-reset are latched. Use 10Kohm resistor to

program logic Hi to VDD or GND for logic low.

PIN NUMBER PIN NAME TYPE DESCRIPTION

2

RE F OUT R eference clock output*

FS 1 IN Logic input frequency select Bit1*. Input latched at Poweron.

3, 9, 16, 22,

27, 33, 39, 45

GND PWR Ground.

4 X1 IN Crystal input. Nominally 14.318 MHz. Has internal load cap

5 X2 OUT Crystal output. Has internal load cap and feedack resistor to X1

41 VDDL PWR 2.5 or 3.3V buffer power for CPUL and IOAPIC output buffers.

8, 10, 11, 12, 14, BUS (1:5) OUT B US clock outputs. see select table for frequency

15

BUS6 OUT BUS clock output. See select table for frequency.*

FS0 IN Logic input frequency select Bit0.*. Input latched at Poweron.

23 CPU_STOP# IN Halts CPU Clocks at Logic "0" level when low. Internal Pull-up

24 PD# IN Powers down chip, active low. Internal Pull-up

47

24M O UT 24MHz fixed clock.*

BSEL I N

Logic input* for selecting synchronous or asynchronous BUS

frequency- see table above. Input latched at Poweron.*

1, 6, 13, 19,

30, 36, 48

VDD3 PWR 3.3 volt core logic and buffer power

17, 18, 20, 21, 28,

29, 31, 32, 34,

35, 37, 38

SDRAM (1:12) OUT S DRAM clocks at CPU speed. See select table for frequency.

40 CPUH/AGP OUT CPU clock operates at SDRAM VDD level (3.3V nom), for AGP etc.

42, 43 CPUL (1:2) OU T

CPU clocks .See select table for frequency. Operates at down to

2.5V controlled by VDDL pin.

7, 25, 26 N/C — Pins not internally connected.

46

48 M OUT 48 MHz fixed clock output*.

FS 2 IN Logic input frequency select Bit 2*. Input latched at Poweron.

44 IOAPIC OUT

Reference clock (14.318MHz) powered by VDDL,

operating 2.5 to 3.3V.

3

ICS9147-09

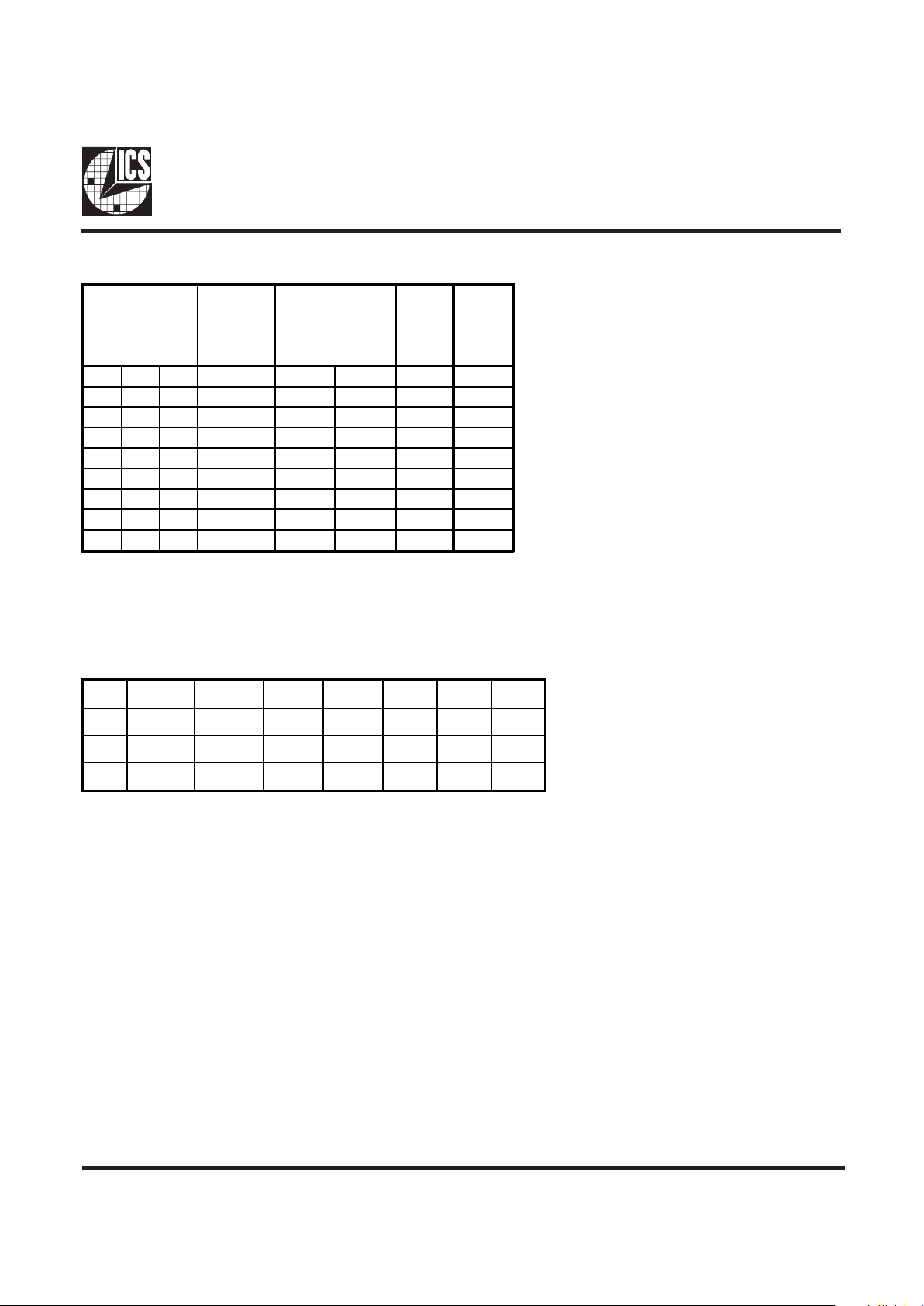

Functionality with (14.31818 MHz input)

Clock Enable Configuration

**Test: is the frequency applied to the X1 input. Can be crystal or tester generated clock overriding crystal at X1 pin.

Address Select

CPUL

(1:2)

CPUH

SDRAM

(1:12)

BUS (1:6)

(MHz)

24M

(MHz)

48M

(MHz)

FS2 FS1 FS0 (MHz) BSEL=1 BSEL=0 (MHz) (MHz)

000 60 30 32 24 48

001 66.8 33.4 32 24 48

010 50 25 32 24 48

011 55 27.5 32 24 48

100 75 37.5 32 24 48

101 68.5 34.3 32 24 48

1 1 0 83.3 41.65 32 24 48

1 1 1 Tristate Tristate Tristate Tristate Tristate

PD# CPUSTOP#

CPUL (1:2)

CPUH

SDRAM

(1:12)

BUS (1:6) 24MHz 48MHz REF

1 1 Running Running Running Running Running Running

1 0 Stop Low Running Running Running Running Running

0 X Stop Low Stop Low Stop Low Stop Low Stop Low Stop Low

Loading...

Loading...