Integrated

Circuit

Systems, Inc.

General Description Features

ICS9112-26

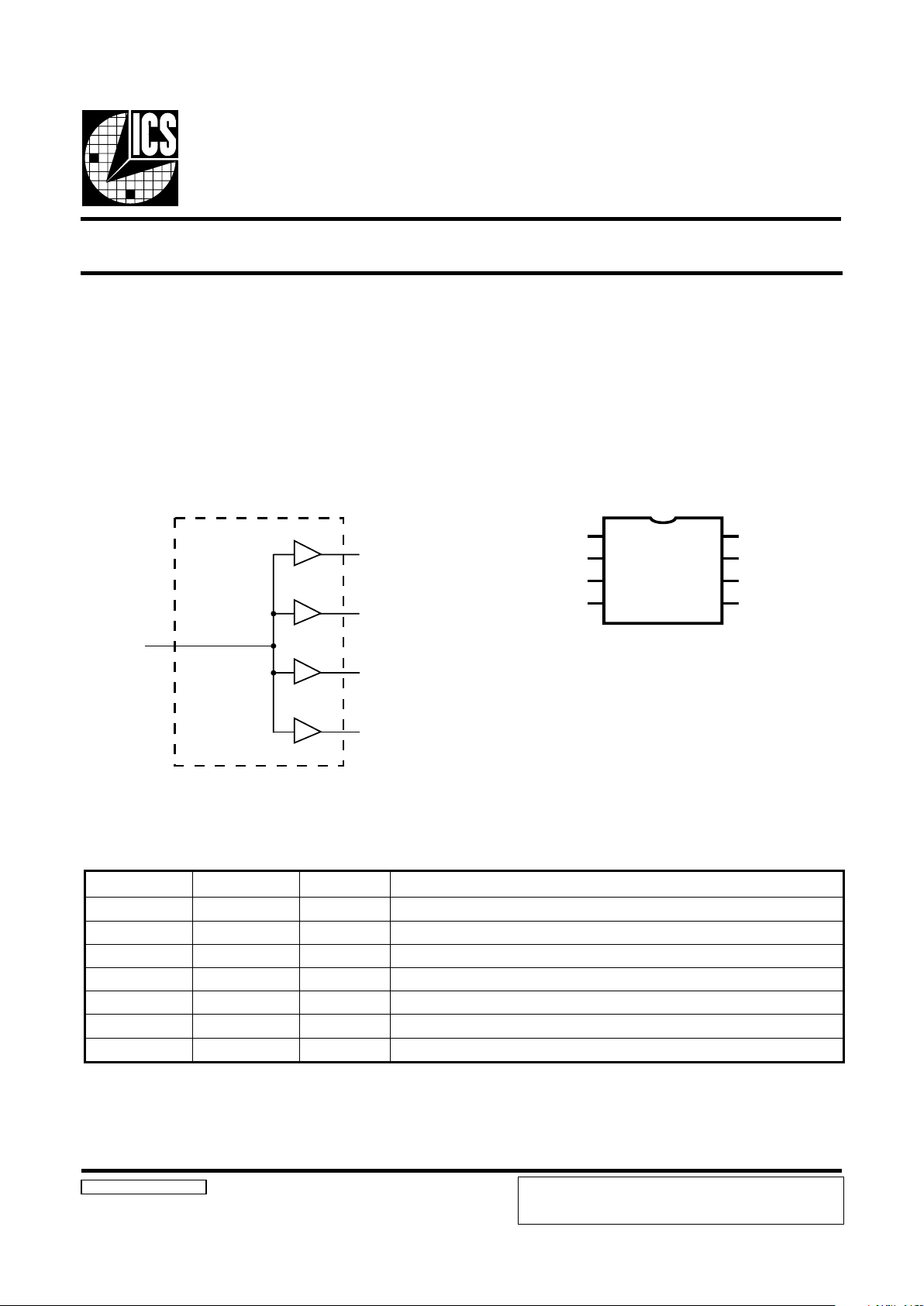

Block Diagram

Low Skew Output Buffer

9112-26 Rev B- 07/16/01

Pin Configuration

• Frequency range 0 - 133 MHz (3.3V)

• Less than 200 ps Jitter between outputs

• Skew controlled outputs

• Skew less than 250 ps between outputs

• Available in 8 pin 150 mil SOIC &

173 mil TSSOP packages.

• 3.3V ±10% operation

The ICS9112-26 is a high performance, low skew, low jitter

clock driver. It is designed to distribute high speed clocks in

PC systems operating at speeds from 0 to 133 MHz.

The ICS9112-26 comes in an eight pin 150 mil SOIC package.

It has four output clocks.

8 pin SOIC & TSSOP

CLK0

VDD

GND

CLK1

CLK_IN

CLK3

VDD

CLK2

ICS9112-26

1

2

3

4

8

7

6

5

CLK_IN

CLK0

CLK1

CLK2

CLK3

Pin Descriptions

Notes:

1. Weak pull-down on all outputs

REBMUNNIPEMANNIPEPYTNOITPIRCSED

10KLC

1

TUOtuptuokcolcdereffuB

6,2DDVRWP)V3.3(ylppuSrewoP

3DNGRWPdnuorG

41KLC

1

TUOtuptuokcolcdereffuB

52KLC

1

TUOtuptuokcolcdereffuB

73KLC

1

TUOtuptuokcolcdereffuB

8NI_KLCNI.ycneuqerfecnerefertupnI

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9112-26

Notes:

1. Guaranteed by design and characterization. Not subject to 100% test.

2. CLK_IN input has a threshold voltage of 1.4V

3. All parameters expected with loaded outputs

Absolute Maximum Ratings

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . 7.0 V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND –0.5 V to VDD +0.5 V

Ambient Operating Temperature . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are

stress specifications only and functional operation of the device at these or any other conditions above those listed in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect product reliability.

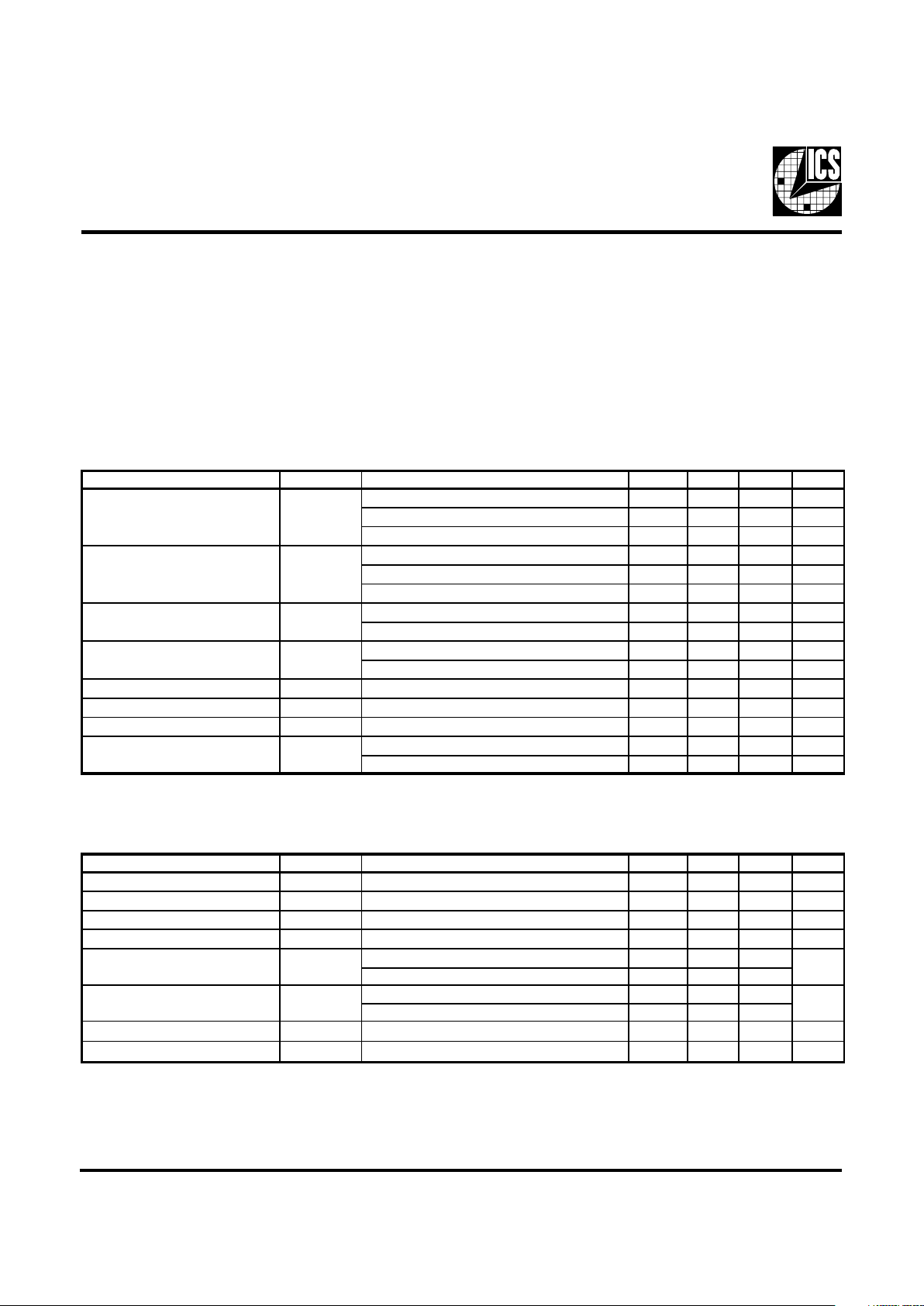

Electrical Characteristics at 3.3V

TA = 0 - 70C; Supply Voltage VDD = 3.3 V +/-5% (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

V

DD

= min to max, IOH = -1 mA VDD - 0.2

3.3 V

V

DD

= 3V, IOH = -24 mA

2 2.9 V

V

DD

= 3V, IOH = 12 mA

2.4 3.1 V

V

DD

= min to max, IOH = 1 mA

0.0055 0.2 V

V

DD

= 3V, IOH = 24 mA

0.28 0.8 V

V

DD

= 3V, IOH = 12 mA

0.14 0.55 V

V

DD

= 3V, VO = 1V

-61 -50

V

DD

= 3.3V, VO = 1.65V

-77

V

DD

= 3V, VO = 2V

60 103

V

DD

= 3.3V, VO = 1.65V

111

Input Current

I

I

V = VO or V

DD

-5 5

µA

In

p

ut Capacitance

1

C

I

VDD = 3.3V, VI = 0V or 3.3V

3pF

Out

p

ut Capacitance

1

CO

V

DD

= 3.3V, VI = 0V or 3.3V

3.2 pF

REF = 0 MHz 22 50 µ

A

Unloaded outputs at 66.67 MHz 25 40 mA

1. Guaranteed by design, not 100% tested in production.

High-level Input Current

I

OH

High-level Output Voltage

V

OH

Low-level Output Voltage

V

OL

Low-level Input Current

I

OL

Supply current

I

DD

Switching Characteristics at 3.3V

TA = 0 - 70C; Supply Voltage VDD = 3.3 V +/-5% (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Low-to-hi

g

h Propagation Dela

y

1

t

PLH

VO = VDD/2

45.67ns

Hi

g

h-to-low Propagation Dela

y

1

t

PHL

VO = VDD/2

45.27ns

Out

p

ut Skew Window

1

T

s

k

(O) VO = VDD/2

50 100 ps

Process Skew

1

Tsk(PR) VO = VDD/2

0.5 ps

66 MHz 6

133 MHz 3

66 MHz 6

133 MHz 3

Output Rise Slew Rate

1

T

r

0.3 to 0.6 V

DD

23.65V/ns

Output Rise Slew Rate

1

T

f

0.3 to 0.6 V

DD

23.25V/ns

1. Guaranteed by design, not 100% tested in production.

CLKIN Low Time

1

T

low

ns

ns

CLKIN High Time

1

T

high

Loading...

Loading...