Page 1

Integrated

ICS9248-99

Circuit

Systems, Inc.

Preliminary Product Preview

Frequency Generator & Integrated Buffers for Celeron & PII/III™

Recommended Application:

810/810E style chipset

Output Features:

• 2- CPUs @2.5V @ 150MHz (up to 200MHz. achievable

through I

• 9 - SDRAM @ 3.3V @ 150MHz (up to 200MHz.

achievable through I

2

C)

2

C)

• 8 - PCICLK @ 3.3V

• 1 - IOAPIC @ 2.5V,

• 2 - 3V66MHz @ 3.3V

• 2- 48MHz, @ 3.3V fixed.

• 1- 24/48MHz, @ 3.3V

• 1- REF @3.3V, 14.318MHz.

Features:

• Up to 200.4MHz frequency support

• Support FS0-FS3 trapping status bit for I

• Support power management: Power down Mode form I

2

C read back.

2

programming.

• Spread spectrum for EMI control ( ± 0.25% center).

• FS0, FS1, FS2, FS3 must have a internal 120K pull-Down

to GND.

• Uses external 14.318MHz crystal

Skew Specifications:

• CPU – CPU: <175ps

• SDRAM - SDRAM: < 250ps

• 3V66 – 3V66: <175ps

• PCI – PCI: <500ps

• For group skew specifications, please refer to group

timing relationship table.

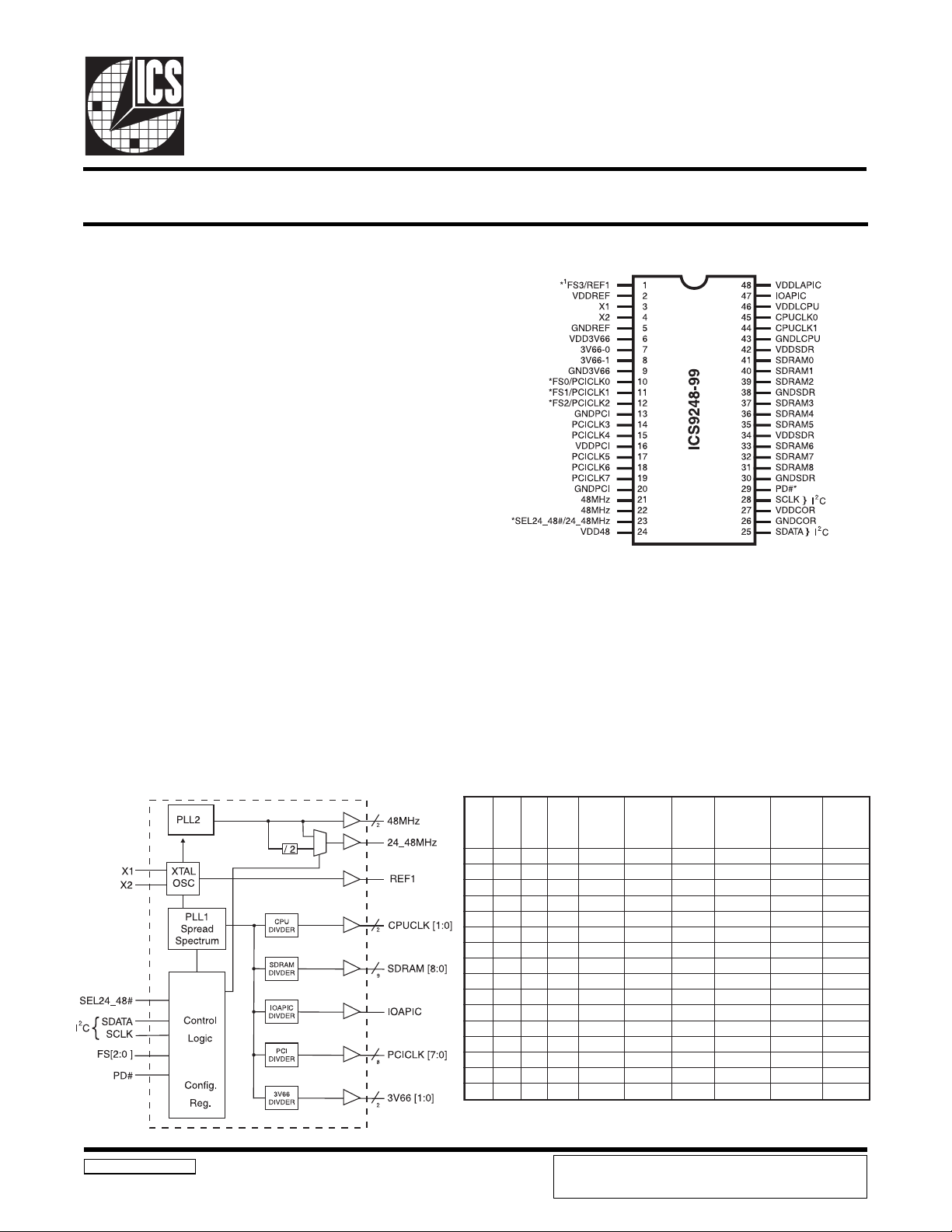

Pin Configuration

C

48-Pin 300mil SSOP

* These inputs have a 120K pull down to GND.

1 These are double strength.

Block Diagram

9248- 99 Rev A 8/27/99

Third party brands and names are the property of their respective owners.

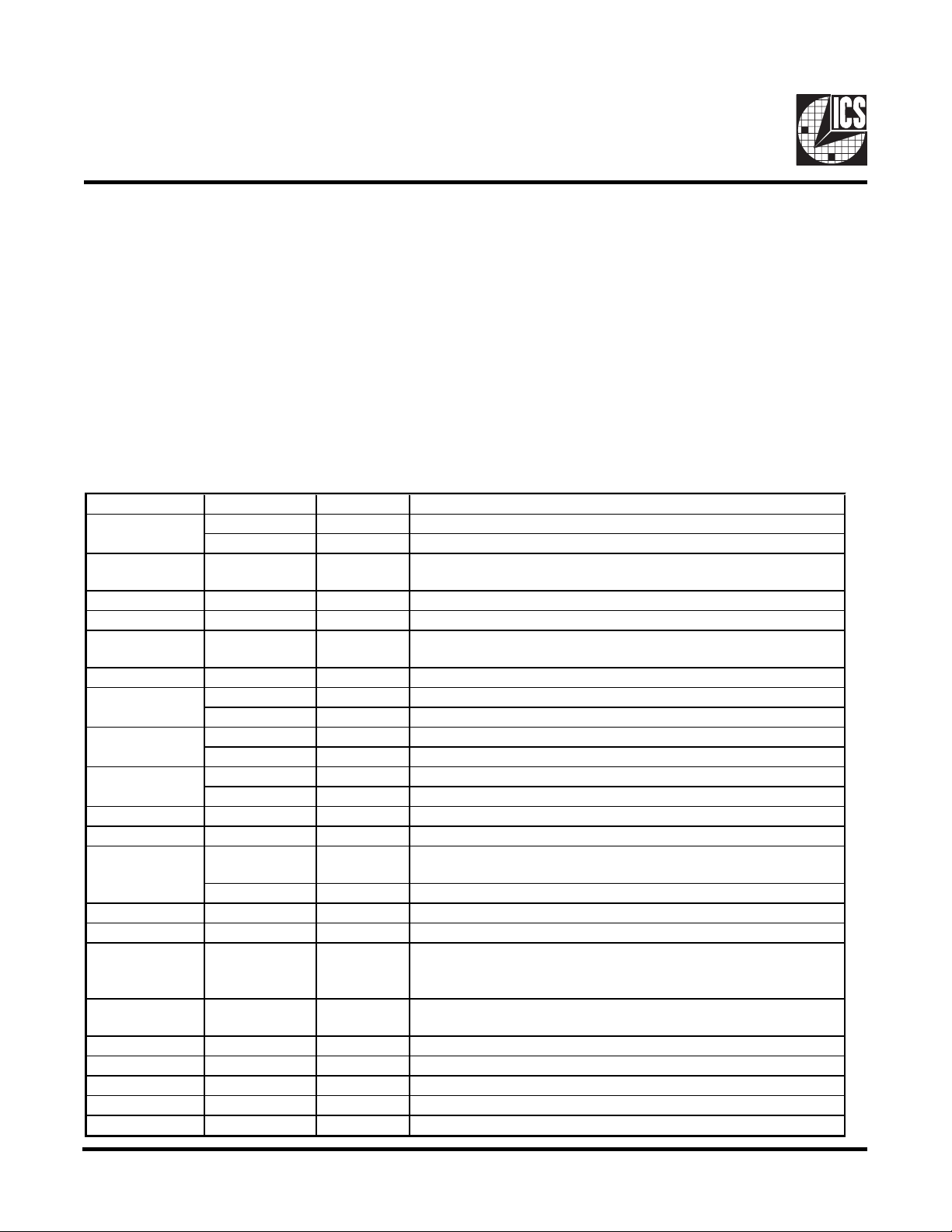

Functionality

3SF2SF1SF0SF

0000

0001

0010

0011

0100

0101

0110

0111

100 0

100 1

1010

1011

1100

110 1

1110

1111

PRODUCT PREVIEW documents contain information on new

products in the sampling or preproduction phase of development.

Characteristic data and other specifications are subject to change

without notice.

UPC

MARDS

)zHM(

33.5700.31133.5776.7338.8176.73

00.52100.52133.3876.1438.0276.14

00.92100.92100.6800.3405.1200.34

92.05100.31133.5776.7338.8176.73

00.05100.05100.00100.0500.5200.05

00.21100.21176.4733.7376.8133.73

00.54100.54176.6933.8471.4233.84

46.34100.80100.2700.6300.8100.63

03.8605.20133.8671.4380.7171.43

00.50100.50100.0700.5305.7100.53

00.83100.83100.2900.6400.3200.64

00.04100.50100.0700.5305.7100.53

76.6600.00176.6633.3376.6133.33

00.00100.00176.6633.3376.6133.33

06.33106.33170.9835.4472.2235.44

33.33100.00176.6633.3376.6133.33

66V3

)zHM(

)zHM(

KLCICP

*66V3(

)2/1

)zHM(

CIPAOI

*ICP(

)2/1

)zHM(

CIPAOI

)ICP(

)zHM(

Page 2

ICS9248-99

p

pp

Preliminary Product Preview

General Description

The ICS9248-99 is the single chip clock solution for Desktop

designs using 810/810/E style chipset. It provides all necessary

clock signals for such a system.

Spread spectrum may be enabled through I

Spread spectrum typically reduces system EMI by 8dB to

10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9248-99

2

C programming.

Power Groups

GNDREF, VDDREF = REF1, X1, X2

GNDPCI , VDDPCI = PCICLK [7:0]

GNDSDR, VDDSDR = SDRAM [8:0]

GNDCOR, VDDCOR = supply for PLL core

GND3V66 , VDD3V66 = 3V66

VDD48 = 48MHz, 24_48MHz,

VDDLAPIC = IOAPIC

GNDLCPU , VDDLCPU = CPUCLK [1:0]

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

2

Serial programming I

C interface allows changing functions,

stop clock programming and frequency selection.

Pin Configuration

PIN NUMBER PIN NAME TYPE DESCRIPTION

1

2, 6, 16, 24, 27 , 34,

42

3 X1 IN Crystal input,nominally 14.318MHz.

4 X2 OUT Crystal output, nominally 14.318MHz.

5, 9, 13, 20, 26, 30,

38

8, 7 3V66 [1:0] OU T 3.3V clock outputs

10

11

12

19, 18, 17, 15, 14 PCICLK [7:3] OUT PCI clock outputs.

21, 22 48MHz OUT 48MHz output clocks

23

25 SDATA IN Data input for I2C serial input, 5V tolerant input

28 SCLK IN Clock input of I2C input, 5V tolerant input

29 PD# IN

31, 32, 33, 35, 36,

37, 39, 40, 41

43 GNDLCPU PWR Ground pin for the CPU clocks.

44, 45 CPUCLK [1:0] OUT CPU clock outputs.

46 VDDLCPU PWR Power pin for the CPUCLKs. 2.5V

47 IOAPIC OUT 2.5V clock output.

48 VDDLAPIC PWR Power pin for the IOAPIC. 2.5V

REF1 OU T 14.318 MHz reference clock.

FS3 IN Frequency select pin.

VDD PWR

GND PWR Ground pin for 3V outputs.

FS0 IN Frequency select pin.

PCICLK0 OUT PCI clock output.

FS1 IN Frequency select pin.

PCICLK1 OUT PCI clock output.

FS2 IN Frequency select pin.

PCICLK2 OUT PCI clock output.

SEL24_48# IN

24_48MHz OUT Clock output for super I/O/US B

SDRAM [8:0] OUT SDRAM clock outputs

3.3V Power s upply for SD RAM output buffers, PCI output buffers,

reference out

Select pin for enabling 24MHz or 48MHz

H=24MHz L=48MHz

Asynchronous active low input pin used to power down the device into a low

power state. The internal clocks are disabled and the VC O and the crystal are

ed. The latency of the power down will not be greater than 3ms.

sto

ut buffers and 48MHz output

Third party brands and names are the property of their respective owners.

2

Page 3

Preliminary Product Preview

K

0

2

3

5

K

K

K

K

K

K

K

K

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I

2

C programming application note.

ICS92 48-99

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

ICS clock will acknowledge

Controller (host) sends a dummy command code

ICS clock will acknowledge

Controller (host) sends a dummy byte count

ICS clock will acknowledge

Controller (host) starts sending first byte (Byte 0)

through byte 5

ICS clock will acknowledge each byte one at a time.

Controller (host) sends a Stop bit

How to Write:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

Dummy Command Code

Dummy Byte Count

Byte 0

Byte 1

Byte 2

Byte 3

Byte 4

Byte 5

Stop Bit

(H)

AC

AC

AC

AC

ACK

AC

AC

AC

AC

How to Read:

Controller (host) will send start bit.

Controller (host) sends the read address D3

ICS clock will acknowledge

ICS clock will send the byte count

Controller (host) acknowledges

ICS clock sends first byte (Byte 0) through byte 5

Controller (host) will need to acknowledge each byte

Controller (host) will send a stop bit

How to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

ACK

ACK

ACK

ACK

ACK

ACK

ACK

Stop Bit

AC

Byte Count

Byte

Byte 1

Byte

Byte

Byte 4

Byte

(H)

Notes:

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for

verification. Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

Third party brands and names are the property of their respective owners.

2

C interface, the protocol is set to use only "Block-Writes" from the controller. The

3

Page 4

ICS9248-99

Preliminary Product Preview

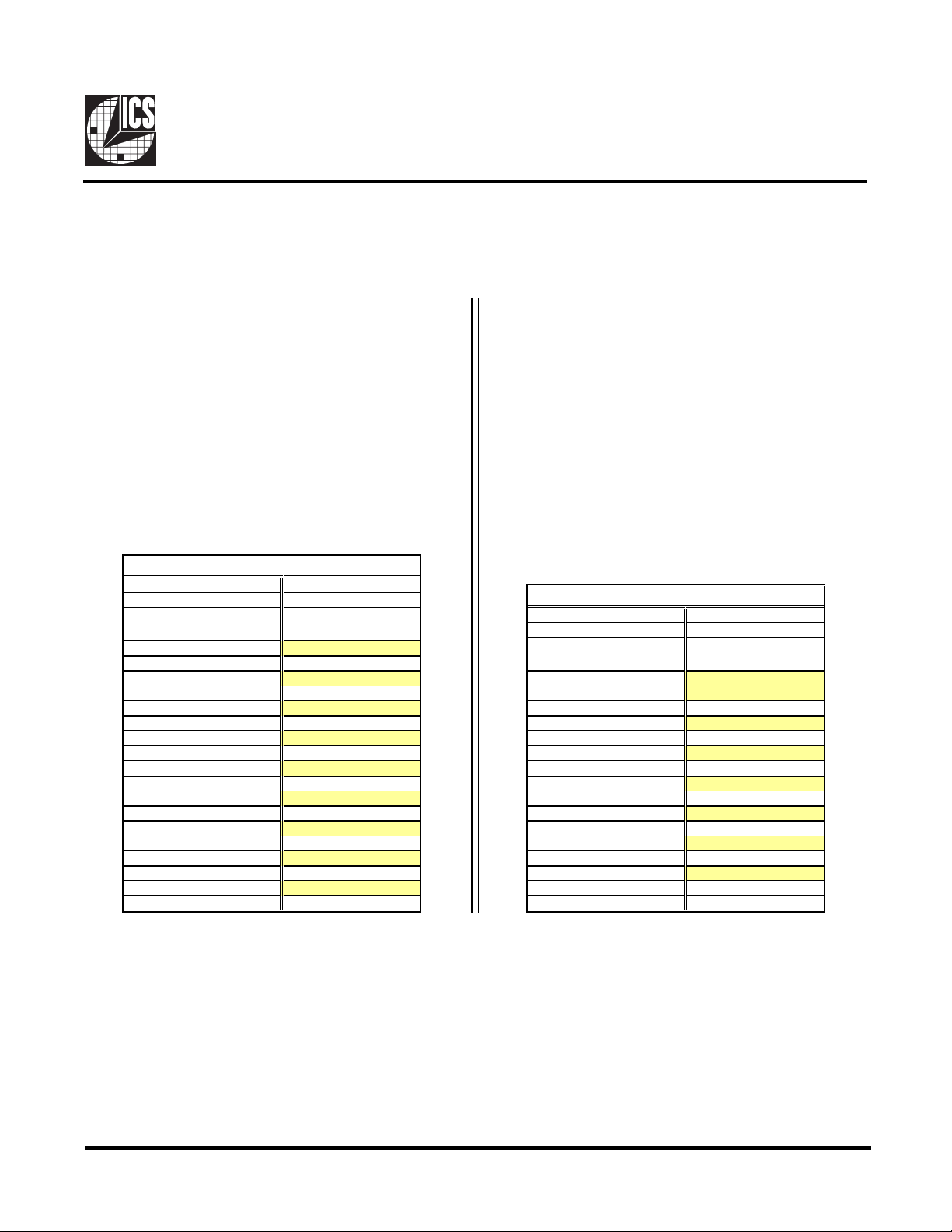

Serial Configuration Command Bitmap

Byte4: Functionality and Frequency Select Register (default = 0)

tiBnoitpircseDDWP

)4:7,2(tiB

00000 33.5700.31133.5776.7338.8176.73

00001 00.52100.52133.3876.1438.0276.14

00010 00.92100.92100.6800.3405.1200.34

00011 92.05100.31133.5776.7338.8176.73

00100 00.05100.05100.00100.0500.5200.05

00101 00.21100.21176.4733.7376.8133.73

00110 00.54100.54176.6933.8471.4233.84

00111 46.34100.80100.2700.6300.8100.63

01000 03.8605.20133.8671.4380.7171.43

01001 00.50100.50100.0700.5305.7100.53

01010 00.83100.83100.2900.6400.3200.64

01011 00.04100.50100.0700.5305.7100.53

01100 76.6600.00176.6633.3376.6133.33

01101 00.00100.00176.6633.3376.6133.33

,2tiB

01110 06.33106.33170.9835.4472.2235.44

4:7tiB

01111 33.33100.00176.6633.3376.6133.33

10000 49.65100.81176.8733.9376.9133.93

10001 00.06100.02100.0800.0400.0200.04

10010 03.64100.01133.3776.6333.8176.63

10011 00.72152.5905.3657.1388.5157.13

10100 00.72100.72176.4833.2471.1233.24

1010 1 00.12100.12176.0833.0471.0233.04

10110 00.71100.71100.8700.9305.9100.93

10111 00.41100.41100.6700.8300.9100.83

11000 00.0800.02100.0800.0400.0200.04

11001 00.8700.71100.8700.9305.9100.93

11010 00.00200.00233.33176.6633.3376.66

11011 00.08100.08100.02100.0600.0300.06

11100 00.66100.66176.01133.5576.7233.55

11101 00.01100.01133.3776.6333.8176.63

11110 00.70100.70133.1776.5338.7176.53

11111 00.0900.0900.0600.0300.5100.03

3tiB

1tiB

0tiB

lamroN-0

gninnuR-0

stuptuollaetatsirT-1

KLCUPC

)zHM(

4:7,2tiBybdetcelessiycneuqerF-1

MARDS

)zHM(

66V3

)zHM(

stupnIdehctaL,tceleserawdrahybdetcelessiycneuqerF-0

daerpSretneC%52.0±delbanEmurtcepSdaerpS-1

KLCICP

zHM(

CIPAOI

)zHM(

2/ICP=ICP=

11000

1etoN

0

1

0

Note 1: Default at power-up will be for latched logic inputs to define frequency, as displayed by Bit 3.

1) The IOAPIC Frequency change from IOAPIC=PCICLK/2 to IOAPIC=PCICLK is controlled by

IOAPC_Freq control in I2C Byte 3 Bit 1

2) The I2C readback of the power up default indicate the revision ID in bits 2, 7:4

I2C is a trademark of Philips Corporation

Third party brands and names are the property of their respective owners.

4

Page 5

ICS92 48-99

Preliminary Product Preview

Byte 0: CPU, Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-0 devreseR

6tiB-0 devreseR

5tiB-0 devreseR

4tiB-0 devreseR

3tiB-0 devreseR

2tiB321 zHM84/42

1tiB22,121 zHM84

0tiB-0 devreseR

Byte 2: PCI, Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB911 7KLCICP

6tiB811 6KLCICP

5tiB711 5KLCICP

4tiB511 4KLCICP

3tiB411 3KLCICP

2tiB211 2KLCICP

1tiB111 1KLCICP

0tiB011 0KLCICP

Byte 1: SDRAM, Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB231 7MARDS

6tiB331 6MARDS

5tiB531 5MARDS

4tiB631 4MARDS

3tiB731 3MARDS

2tiB931 2MARDS

1tiB041 1MARDS

0tiB141 0MARDS

Byte 3: Reserved , Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-0 devreseR

6tiB-X#2SF

5tiB-X#1SF

4tiB-X#0SF

3tiB741 CIPAOI

2tiB-X #)#84_42LES(

CIPAOI_QERF

1tiB-1

0tiB-X#3SF

2/KLCICP=CIPAOI>=1=

>=0=CIPAOI_QERF

KLCICP=CIPAOI

Byte 5: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-0 devreseR

6tiB-0 devreseR

5tiB-0 devreseR

4tiB-0 devreseR

3tiB-0 devreseR

2tiB-0 devreseR

1tiB-0 devreseR

0tiB-0 devreseR

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

2. Latched Frequency Selects (FS#) will be inferted logic

load of the input frequency select pin conditions.

Third party brands and names are the property of their respective owners.

Byte 6: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-0 )etoN(devreseR

6tiB-0 )etoN(devreseR

5tiB-0 )etoN(devreseR

4tiB-0 )etoN(devreseR

3tiB-0 )etoN(devreseR

2tiB-1 )etoN(devreseR

1tiB-1 )etoN(devreseR

0tiB-0 )etoN(devreseR

Note: Dont write into this register, writing into this

register can cause malfunction

5

Page 6

ICS9248-99

Preliminary Product Preview

Shared Pin Operation Input/Output Pins

The I/O pins designated by (input/output) on the ICS924899 serve as dual signal functions to the device. During initial

power-up, they act as input pins. The logic level (voltage)

that is present on these pins at this time is read and stored

into a 4-bit internal data latch. At the end of Power-On reset,

(see AC characteristics for timing values), the device changes

the mode of operations for these pins to an output function.

In this mode the pins produce the specified buffered clocks

to external loads.

To program (load) the internal configuration register for these

pins, a resistor is connected to either the VDD (logic 1)

power supply or the GND (logic 0) voltage potential. A 10

Kilohm(10K) resistor is used to provide both the solid CMOS

programming voltage needed during the power-up

programming period and to provide an insignificant load on

the output clock during the subsequent operating period.

Figs. 1 and 2 show the recommended means of implementing

this function. In Fig. 1 either one of the resistors is loaded

onto the board (selective stuffing) to configure the devices

internal logic. Figs. 2a and b provide a single resistor loading

option where either solder spot tabs or a physical jumper

header may be used.

These figures illustrate the optimal PCB physical layout

options. These configuration resistors are of such a large

ohmic value that they do not effect the low impedance clock

signals. The layouts have been optimized to provide as little

impedance transition to the clock signal as possible, as it

passes through the programming resistor pad(s).

Third party brands and names are the property of their respective owners.

Fig. 1

6

Page 7

ICS92 48-99

Preliminary Product Preview

Fig. 2a

Fig. 2b

Third party brands and names are the property of their respective owners.

7

Page 8

ICS9248-99

Preliminary Product Preview

PD# Timing Diagram

The power down selection is used to put the part into a very low power state without turning off the power to the part. PD# is

an asynchronous active low input. This signal needs to be synchronized internal to the device prior to powering down the clock

synthesizer.

Internal clocks are not running after the device is put in power down. When PD# is active low all clocks need to be driven to a

low value and held prior to turning off the VCOs and crystal. The power up latency needs to be less than 3 mS. The power down

latency should be as short as possible but conforming to the sequence requirements shown below. PCI_STOP# and

CPU_STOP# are considered to be don't cares during the power down operations. The REF and 48MHz clocks are expected to

be stopped in the LOW state as soon as possible. Due to the state of the internal logic, stopping and holding the REF clock

outputs in the LOW state may require more than one clock cycle to complete.

Notes:

1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248-99 device).

2. As shown, the outputs Stop Low on the next falling edge after PD# goes low.

3. PD# is an asynchronous input and metastable conditions may exist. This signal is synchronized inside this part.

4. The shaded sections on the VCO and the Crystal signals indicate an active clock.

5. Diagrams shown with respect to 133MHz. Similar operation when CPU is 100MHz.

Third party brands and names are the property of their respective owners.

8

Page 9

ICS92 48-99

Preliminary Product Preview

Absolute Maximum Ratings

Core Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . 4.6 V

I/O Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . 3.6V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND 0.5 V to V

Ambient Operating Temperature . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . 65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are

stress specifications only and functional operation of the device at these or any other conditions above those listed in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods

may affect product reliability.

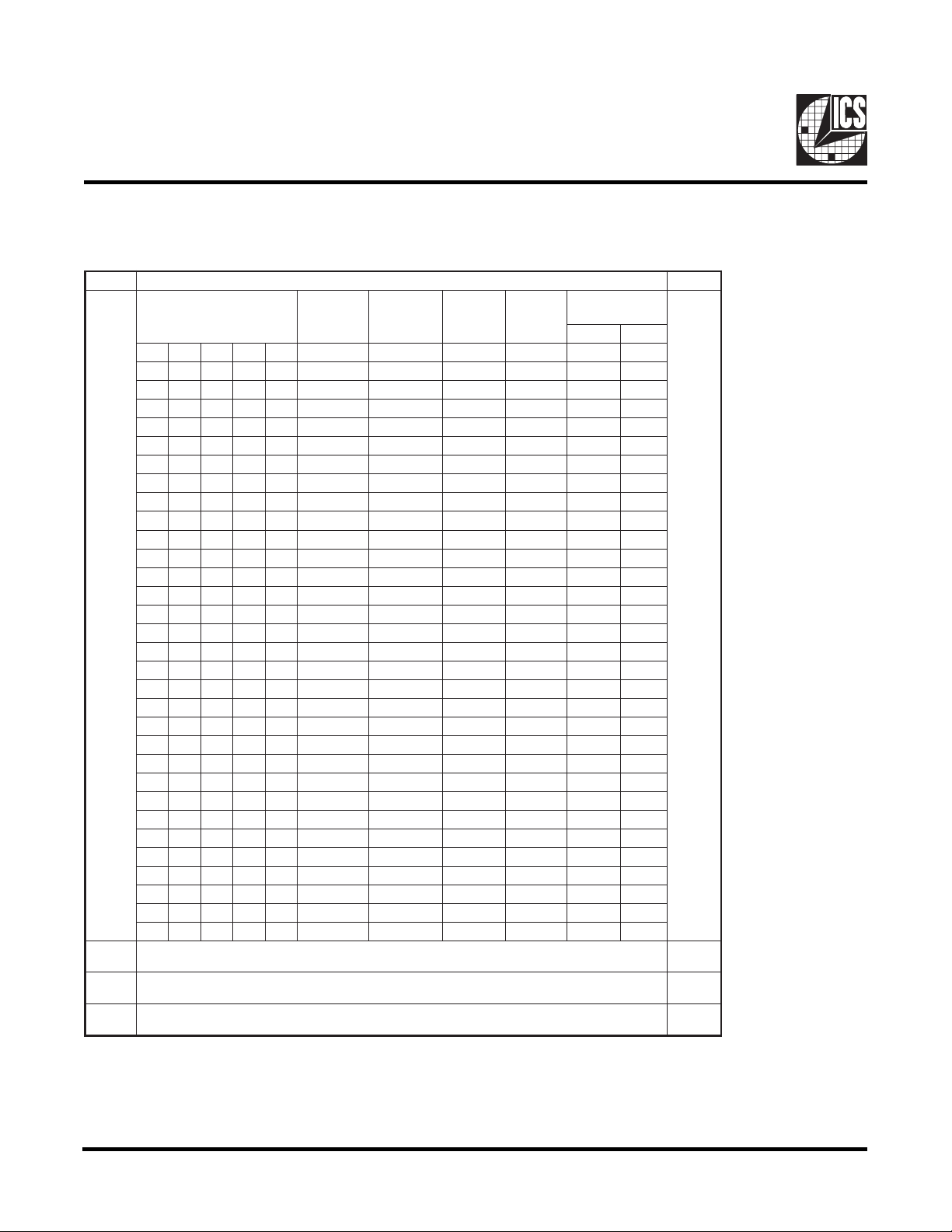

Group Timing Relationship Table

DD

+0.5 V

puorG

zHM66UPCzHM001UPCzHM331UPC

tesffOecnareloTtesffOecnareloTtesffOecnareloT

MARDSotUPCsn5.2sp005sn0.5sp005sn0.0sp005

66V3otUPCsn5.7sp005sn0.5sp005sn0.0sp005

66V3otMARDSsn0.0sp005sn0.0sp005sn0.0sp005

ICPot66V3sn5.3-5.1sp005sn5.3-5.1sp005sn5.3-5.1sp005

ICPotICPsn0.0sn0.1sn0.0sn0.1sn0.0sn0.1

TOD&BSUhcnysAA/NhcnysAA/NhcnysAA/N

Electrical Chara cteristics - Inpu t/Supply/Common Outpu t Parameters

TA = 0 - 70C; Supp ly Voltage VDD = 3. 3 V +5%, VDDL=2.5 V+ 5%(unless other wise s t a te d)

PARAMETER

Inpu t High Vo lta g e

Input Low Voltage

Input High Current

Input Low Current

Input Low Current

Operat i ng

Suppl y C urre nt

Power Down

Suppl y C urre nt

Input freq ue nc y

Pin Inductance

Inpu t C a pa c it a nc e

Transition Time

Settling Time

Clk Stabilization

Delay

1

G ua rentee d by de s i gn , not 100% tes t e d i n production.

SYMBOL CONDITIONS MIN TYP MAX UNITS

V

IH

V

IL

IH

pin

IN

out

INX

VIN = V

DD

VIN = 0 V; Inputs with no pull-up resistors -5 2.0

VIN = 0 V; Inputs with pull-up resis tors -200 -100

CL = 0 pF; Select @ 66M 60 100 mA

CL = 0 pF; With i nput a dd ress to Vdd or GND 400 600

VDD = 3.3 V; 14.318 MH z

i

Logic Inputs 5 pF

O ut put pi n c a pa c it a nc e 6 pF

X 1 & X2 pins 27 45 pF

To 1st crossing of target Fr e q. 3 mS

From 1s t c ross ing t o 1% ta rget F req. 3 mS

s

From VDD = 3.3 V to 1% ta rget F req. 3 mS

output e nable delay (all output s) 1 10 nS

output disable dela y (all output s) 1 10 nS

I

I

IL1

I

IL2

I

DD3.3OP

I

DD3.3PD

F

L

C

1

C

C

1

1

1

T

trans

T

T

STAB

t

PZH,tPZH

t

PLZ,tPZH

2V

VSS-0.3 0.8 V

-5 5

+0.3 V

DD

A

µ

A

µ

A

µ

A

µ

7nH

Third party brands and names are the property of their respective owners.

9

Page 10

ICS9248-99

jcy

Preliminary Product Preview

Electrical Characteristics - CPU

TA = 0 - 70C, V

PARA METER SYMBOL COND ITIO N S MIN TYP MAX UNI TS

O utp ut Imped a nc e R

O utp ut Imped a nc e R

Output High Voltage V

Output Low Voltage V

O utput High Cur rent I

Ou tput L o w Cur rent I

Rise Time t

Fa ll T ime t

Duty Cycle

Skew t

Jitter

1

G ua renteed by d e sign, not 100% tested in production.

= 2.5 V +/-5%; CL = 1 0 - 20 pF (unless other wise stated)

DDL

1

DSP2B

DSN2B

OH2B

OL2B

OH2B

OL2B

r2B

f2B

d

t2B

d

t2B

d

t2B

sk2B

t

c-cyc

t

jcyc-cyc

VO = VDD*(0.5) 13.5 45

1

VO = VDD*(0.5) 13.5 45

IOH = -1 mA 2 V

IOL = 1 mA 0.4 V

V

V

1

VOL = 0.4 V, VOH = 2 .0 V 0.4 1.1 1.6 ns

1

VOH = 0.4 V, VOL = 2 .0 V 0.4 1.1 1.6 ns

1

VT = 1.25 V CPUM Hz <133 45 49 55 %

1

VT = 1.25 V CPUM Hz =133 40 44 50 %

1

VT = 1.25 V CPUM Hz >133 45 51 55 %

1

VT = 1.25 V 30 175 ps

1

VT = 1.25 V CPUMHz = SDRAMMHz 120 250 ps

1

VT = 1.25 V CPUMHz = SDRAMMHz

OH @MIN

OL @MIN

= 1.0V , V

= 1.2V , V

OH@ MAX

OL@ MAX

= 2 .375V -27 -27 mA

= 0.3V 27 30 mA

330 350 ps

Ω

Ω

Elect r i cal C har acteristics - 3V 66

TA = 0 - 70C; VDD = 3.3 V +/-5% ; CL = 1 0-30 pF ( u nless other wise s ta ted)

PARA METER SYMBOL COND ITIO NS MIN TYP MAX U NITS

1

O utput Impe danc e R

O utput Impe danc e R

O utput High Voltage V

O utput L ow Volta ge V

O utput High Current I

O utput Low C urrent I

Rise Time t

Fall Time t

Duty Cycle d

Skew t

Jitte r

1

G ua renteed by design, not 100% te s te d in production.

DSP1

DSN1

OH1

OL1

OH1

OL1

r1

f1

t1

sk1

t

jcyc-cyc

VO = VDD*(0.5) 12 55

1

VO = VDD*(0.5) 12 55

IOH = -1 mA 2.4 V

IOL = 1 mA 0.55 V

VOH@ MIN = 1.0 V, VOH@ MAX = 3.135 V-33 -33 mA

VOL@ MIN = 1.95 V, VOL@ MAX= 0.4 30 38 mA

1

VOL = 0. 4 V, VOH = 2 . 4 V 0.4 1.4 1.9 ns

1

VOH = 2.4 V, VOL = 0 . 4 V 0.4 1.3 1.6 ns

1

VT = 1.5 V 454855%

1

VT = 1.5 V 30 175 ps

VT = 1.5 V

270 500 ps

Ω

Ω

Third party brands and names are the property of their respective owners.

10

Page 11

ICS92 48-99

Preliminary Product Preview

Electrical Characteristics - IOAPIC

TA = 0 - 70C;V

PARA METER SYMBOL COND ITIO N S MIN TYP MAX UNITS

O utput Impe danc e R

O utput Impe danc e R

Output High Voltage V

Output Low Voltage V

O utput High Current I

O utput Low Cu rrent I

Rise Time t

F all Time t

Duty Cycle d

Jitter t

Skew

1

G ua renteed by design, not 100% te sted in produc tion.

= 2. 5 V +/-5%; CL = 10 - 20 pF (unless oth erwise stated)

DDL

1

DSP4B

DSN4B

OH4\ BIOH

OL4B

OH4B

OL4B

r4B

f4B

t4B

jcyc-cyc

T

ska

VO = VDD*(0.5) 9 30

1

VO = VDD*(0.5) 9 30

= -5.5 mA 2 V

IOL = 9.0 mA 0.4 V

V

V

1

VOL = 0.4 V, VOH = 2 .0 V 0.4 0.9 1.6 ns

1

VOH = 2.0 V, VOL = 0 .4 V 0.4 1.5 1.9 ns

1

VT = 1.25 V 455055%

OH@ min

OL@ MIN

= 1.4 V, V

= 1.0 V, V

OH@ MAX

OL@ MAX=

= 2 .5 V -36 -21 m A

0.2 36 31 mA

VT = 1.25 V 120 250 ps

1

250 ps

Ω

Ω

Electrical Characteristics - SDRAM

TA = 0 - 70C; VDD = V

PARA METER SYMBOL COND ITIO NS MIN TYP MAX UN ITS

O utp ut Impeda nc e R

O utp ut Impeda nc e R

Output High Voltage V

Output Low Voltage V

O utput High Current I

O utput L ow Current I

Rise Time T

F all Time T

Duty Cycle D

Skew T

Jitte r

1

G ua renteed by de s ign, not 100% tested in pr oduc tion.

= 3.3 V +/-5%; CL = 20 - 30 pF (unles s othe r wise s tate d)

DDL

1

DSP3

DSN3

OH3

OL3

OH3

OL3

r3

f3

t3

sk3

cyc-cyc VT = 1.5 V

t

j

VO = VDD*(0.5) 10 24

1

VO = VDD*(0.5) 10 24

IOH = -1 mA 2.4 V

IOL = 1 mA 0.4 V

V

V

1

VOL = 0.4 V, VOH = 2 .4 V 0.4 1.0 1.6 ns

1

VOH = 2.4 V, VOL = 0 .4 V 0.4 1.0 1.6 ns

1

VT = 1.5 V 455055%

1

VT = 1.5 V 50 250 ps

OH @MIN

OL@ MIN

= 2.0 V, V

= 1.0 V, V

OH@ MAX

OL@ MAX

=3.135 V - 54 -46 mA

=0.4 V 54 53 mA

140 250 ps

Ω

Ω

Third party brands and names are the property of their respective owners.

11

Page 12

ICS9248-99

Preliminary Product Preview

Elect r i cal C har acteristics - P CI

TA = 0 - 70C; VDD = 3.3 V +/-5% ; CL = 1 0-30 pF ( u nless other wise s ta ted)

PARA METER SYMBOL COND ITIO NS MIN TYP MAX U NITS

1

O utput Impe danc e R

O utput Impe danc e R

O utput High Voltage V

O utput L ow Volta ge V

O utput High Current I

O utput Low C urrent I

Rise Time t

Fall Time t

Duty Cycle d

Skew t

Jitte r

1

G ua renteed by design, not 100% te s te d in production.

DSP1

DSN1

OH1

OL1

OH1

OL1

r1

f1

t1

sk1

t

jcyc-cyc

VO = VDD*(0.5) 12 55

1

VO = VDD*(0.5) 12 55

IOH = -1 mA 2.4 V

IOL = 1 mA 0.55 V

VOH@ MIN = 1.0 V, VOH@ MAX = 3.135 V-33 -33 mA

VOL@ MIN = 1.95 V, VOL@ MAX= 0.4 30 38 mA

1

VOL = 0. 4 V, VOH = 2 . 4 V 0.5 2.0 2.5 ns

1

VOH = 2.4 V, VOL = 0 . 4 V 0.5 1.9 2.3 ns

1

VT = 1.5 V 455055%

1

VT = 1.5 V 390 500 ps

VT = 1.5 V

110 500 ps

Ω

Ω

Electrica l Ch ara cteri stics - REF1, 48MH z

TA = 0 - 70C; VDD = V

PARA METER SYMBO L CO ND ITIO NS MIN TYP MAX U NITS

O utput Impe danc e R

O utput Impe danc e R

Output High Voltage V

Output Low Voltage V

O utput High Current I

O utput Low C urrent I

Rise Time t

F all Time t

Duty Cycle d

Jitte r t

Skew

1

G ua r e nte e d by de s ign, not 100% tested in produc tion.

= 3. 3 V +/- 5% ; CL = 10 -20 pF (unless othe rwis e s ta ted)

DDL

1

DSP5

DSN5

OH5

OH5

OL5

r5

f5

jcyc- c yc

t

jcyc-cyc

T

OL5

t5

VO = VDD*(0.5) 20 60

1

VO = VDD*(0.5) 20 60

IOH = 1 mA 2.4 V

IOL = -1 mA 0.4 V

V

V

1

VOL = 0. 4 V, VOH = 2 . 4 V 4 nS

1

VOH = 2. 4 V, VOL = 0 . 4 V 4 nS

1

VT = 1. 5 V 45 55 %

1

VT = 1.5 V; Fixed Clocks 500 ps

1

VT = 1.5 V; R ef Clocks 1000 ps

VT = 1. 5 V

sk

OH @MIN

OL@MIN

=1 V, V

OH@MAX

=1.95 V , V

= 3.135 V -29 -23 mA

=0.4 V 29 27 mA

OL@MIN

250 ps

Ω

Ω

Third party brands and names are the property of their respective owners.

12

Page 13

ICS92 48-99

Preliminary Product Preview

LOBMYS SNOISNEMIDNOMMOC SNOITAIRAV D N

A590.101.011.CA026.526.036.84

1A800.210.610.DA027.527.037.65

2A880.090.290.

B800.010.5310.

C500.- 010.

DsnoitairaVeeS

E292.692.992.

eCSB520.0

H004.604.014.

h010.310.610.

L420.230.040.

NsnoitairaVeeS

µ

X580.390.001.

.NIM.MON.XAM.NIM.MON.XAM

°0°5°8

Ordering Information

ICS9248yF-99

Example:

ICS XXXX y F - PPP

Pattern Number (2 or 3 digit number for parts with ROM code patterns)

Package Type

F=SSOP

Revision Designator (will not correlate with datasheet revision)

Device Type (consists of 3 or 4 digit numbers)

Prefix

ICS, AV = Standard Device

SSOP Package

Third party brands and names are the property of their respective owners.

13

PRODUCT PREVIEW documents contain information on new

products in the sampling or preproduction phase of development.

Characteristic data and other specifications are subject to change

without notice.

Loading...

Loading...