Page 1

ICOP-602X

Embedded 386SX CPU ISA Half Size SBC

User’s Manual

Page 2

ii

Copyright Notice

This document is copyrighted, 2000 by ICOP Technology Inc.

All rights are reserved. The information in the manual is

subject to change without notice in order to improving products.

No part of this manual may be reproduced, copied, translated

or transmitted in any form or by any means without the prior

written permission of the manufacturer.

ICOP Technology Inc. assumes no responsibility for any

inaccuracies that may be contained in this document. ICOP

Technology Inc. makes no commitment to update or to keep

current the information contained in this manual.

Copyright 2000 by ICOP Technology Inc.

All rights reserved. Ver.2.0 2000,

Printed in Taiwan

Trademarks Acknowledgments

All brand names and trademarks are the properties and

registered brands of their respective owners.

Page 3

iii

T a b l e o f C o n t e n t s

Chapter 0 Startup

0.1 Packing List ........................................ 1

0.2 Specifications ...................................... 4

0.3 Board Layout ....................................... 7

0.4 Mechanical Drawing ............................... 8

Chapter 1 Introduction

1.1 Features ............................................ 9

1.2 Specifications .....................................10

1.3 VGA Interface .....................................12

1.4 DiskOnChip .........................................13

Chapter 2 Installation

2.1 Jumper Settings ...................................14

2.1.1 ICOP-6025/V ..................................14

2.1.2 ICOP-6024/V ..................................14

2.1.3 ICOP-6022....................................15

2.1.4 ICOP-6020....................................15

2.2 Connectors ........................................16

2.2.1 ICOP-6025/V ..................................16

2.2.2 ICOP-6024/V ..................................16

2.2.3 ICOP-6022....................................17

2.2.4 ICOP-6020....................................18

2.3 DiskOnChip/EPROM/Flash ROM Disk .............19

2.3.1 Setting Up a DiskOnChip 2000 Flah Disk 19

2.3.2 Setting Up a Flash Disk ...................20

2.3.3 Setting Up an EPROM Disk .................21

2.4 Watchdog Tomer ...................................23

2.5 General Purpose I/O ..............................30

Chapter 3 AMI BIOS Setup

3.1 Standard CMOS Setup ............................33

3.2 Advanced CMOS Setup ............................36

3.3 Advanced Chipset Setup ..........................38

3.4 Peripheral Setup ..................................39

Page 4

iv

3.5 Auto-Detect Hard Disks ..........................39

3.6 Change Supervisor Password ....................42

3.7 Auto Configuration with Optimal Settings ....43

3.8 Auto Configuration with Fail Safe Settings ..43

3.9 Save Settings and Exit ...........................43

3.10 Exit Without Saving ...............................43

Chapter 4 SGVA Setup

4.1 Introduction.......................................44

4.1.1 Chipset .......................................44

4.1.2 Display Memory .............................44

4.2 Flat Panel BIOS and Wiring .....................44

Chapter A Pin Assignments

A.1 IDE Interface Connector .........................53

A.2 VGA/Flat Panel Interface Connectors .........54

A.3 Floppy Disk Connector ...........................56

A.4 Parallel Port Interface .........................57

A.5 Serial Port Interface ............................58

A.6 Keyboard and PS/2 Mouse Connector ...........59

A.7 PC/104 Connector ................................. 60

A.8 16-bit General Purpose I/O ......................62

Chapter B System Assignments

B.1 System I/O ports...................................63

B.2 DMA channel assignments .......................63

B.3 Interrupt Assignments ...........................65

B.4 1st MB memory map................................66

Chapter C POST Error Codes

C.1 Beep Error Messages .............................68

C.2 Other AMI BIOS POST Codes ......................69

C.3 Troubleshooting ..................................70

C.4 Screen Error Messages ..........................71

C.5 POST Card Codes ..................................73

Warranty

Page 5

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 1

C h a p t e r 0

Startup

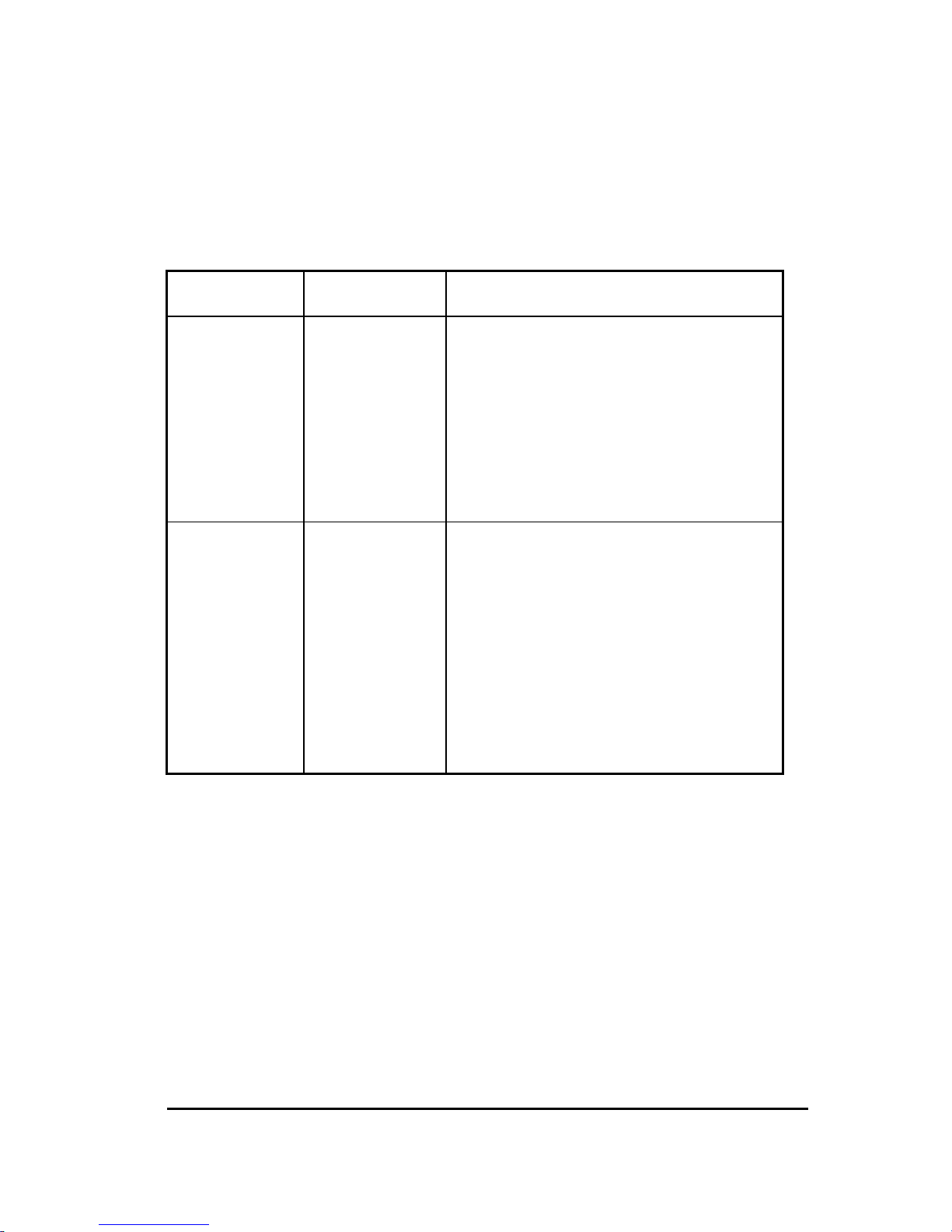

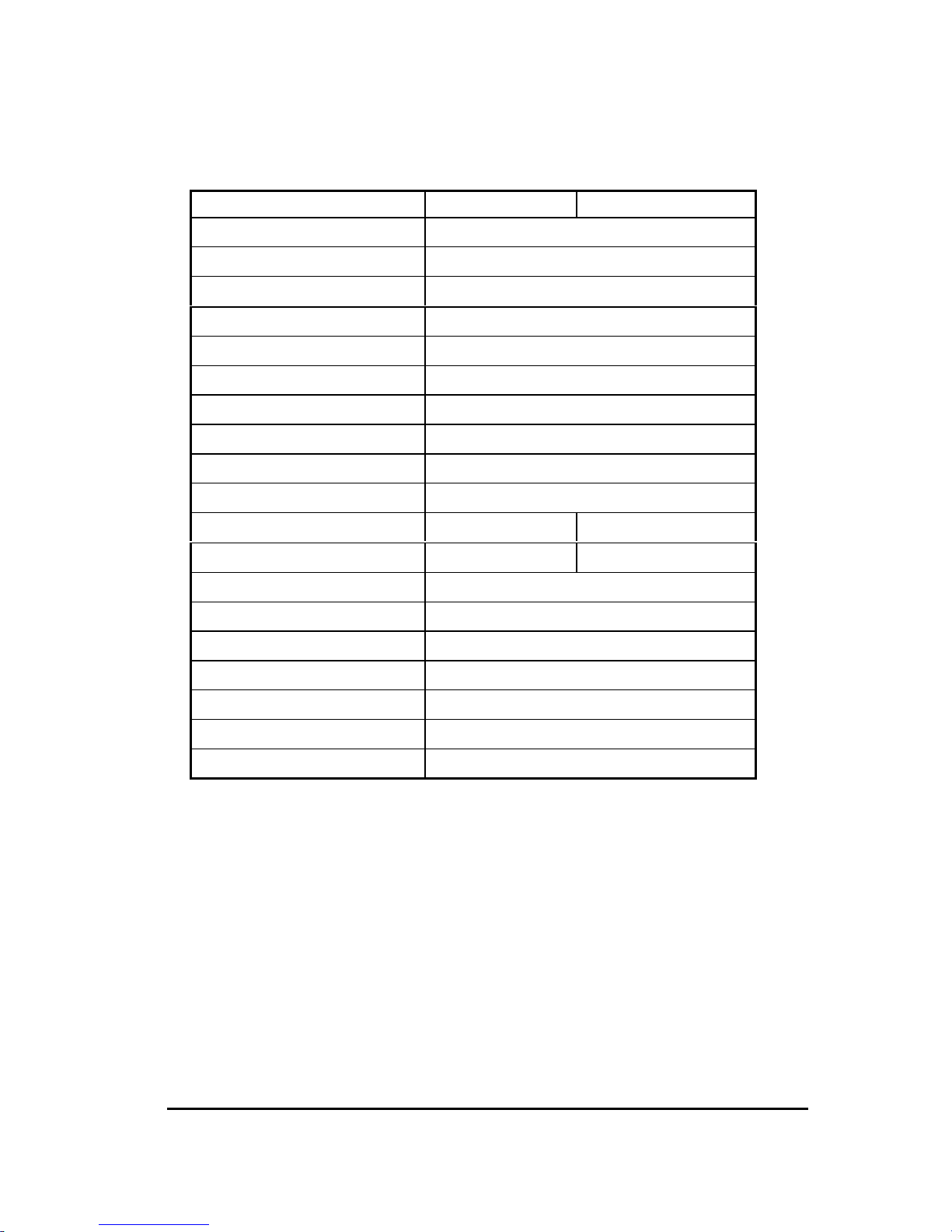

0.1 Packing List

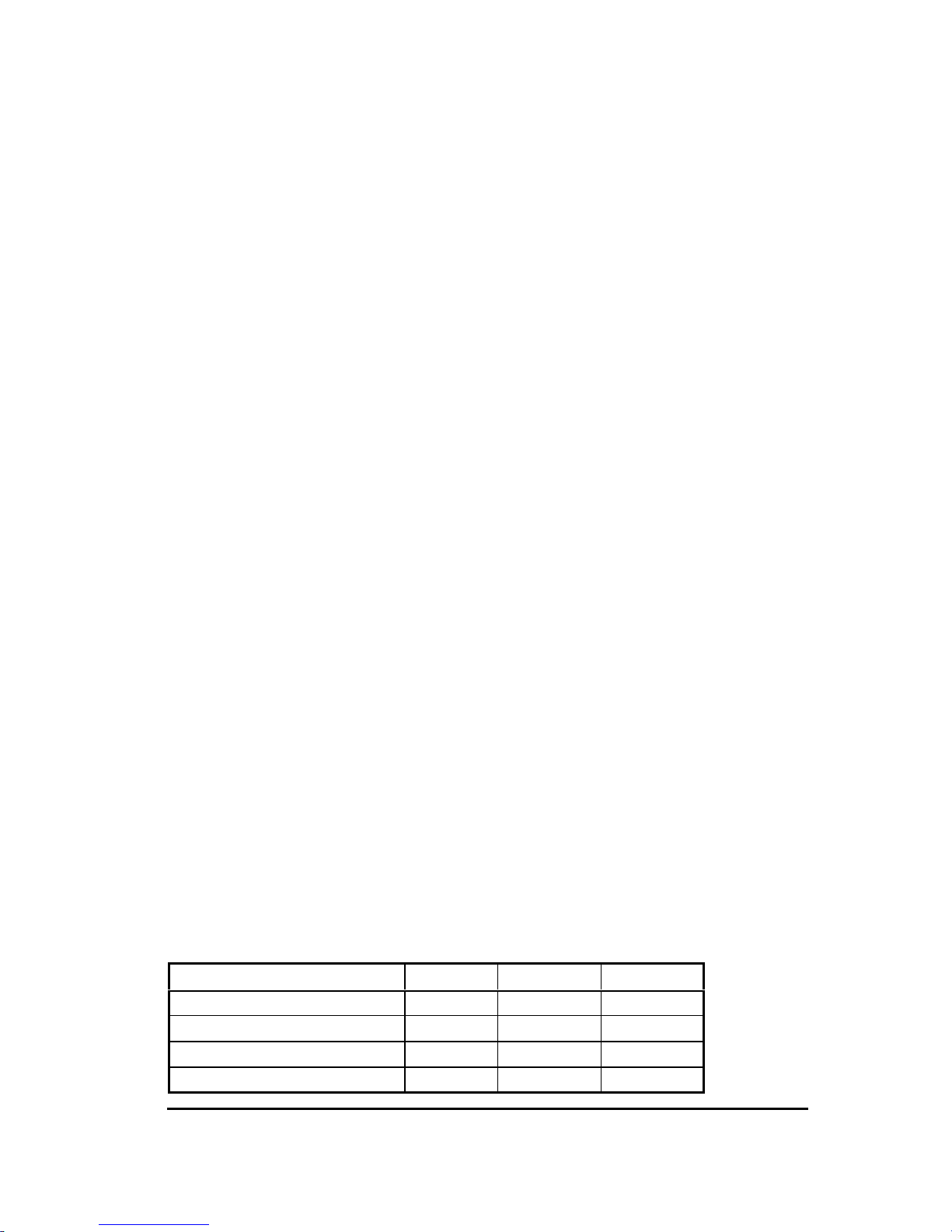

Product

Name

Function Package

ICOP-6025

Embedded

386SX Half Size

All-in-One SBC

l ICOP-6025 Embedded 386SX CPU SBC

l User’s Manual x 1

l Utility and Drivers Diskette x 1

l FDD cable x 1

l HDD cable x 1

l RS232 cable x 3

l Printer cable with bracket x 1

l AT KB / PS2 Mouse Y-cable x 1

ICOP-6025V

Embedded

386SX Half Size

All-in-One SBC

with VGA/LCD

l ICOP-6025V Embedded 386SX CPU

SBC

l User’s Manual x 1

l Utility and Drivers Diskette x 1

l FDD cable x 1

l HDD cable x 1

l RS232 cable x 3

l Printer cable with bracket x 1

l AT KB / PS2 Mous Y-cable x 1

l VGA cable x 1

Page 6

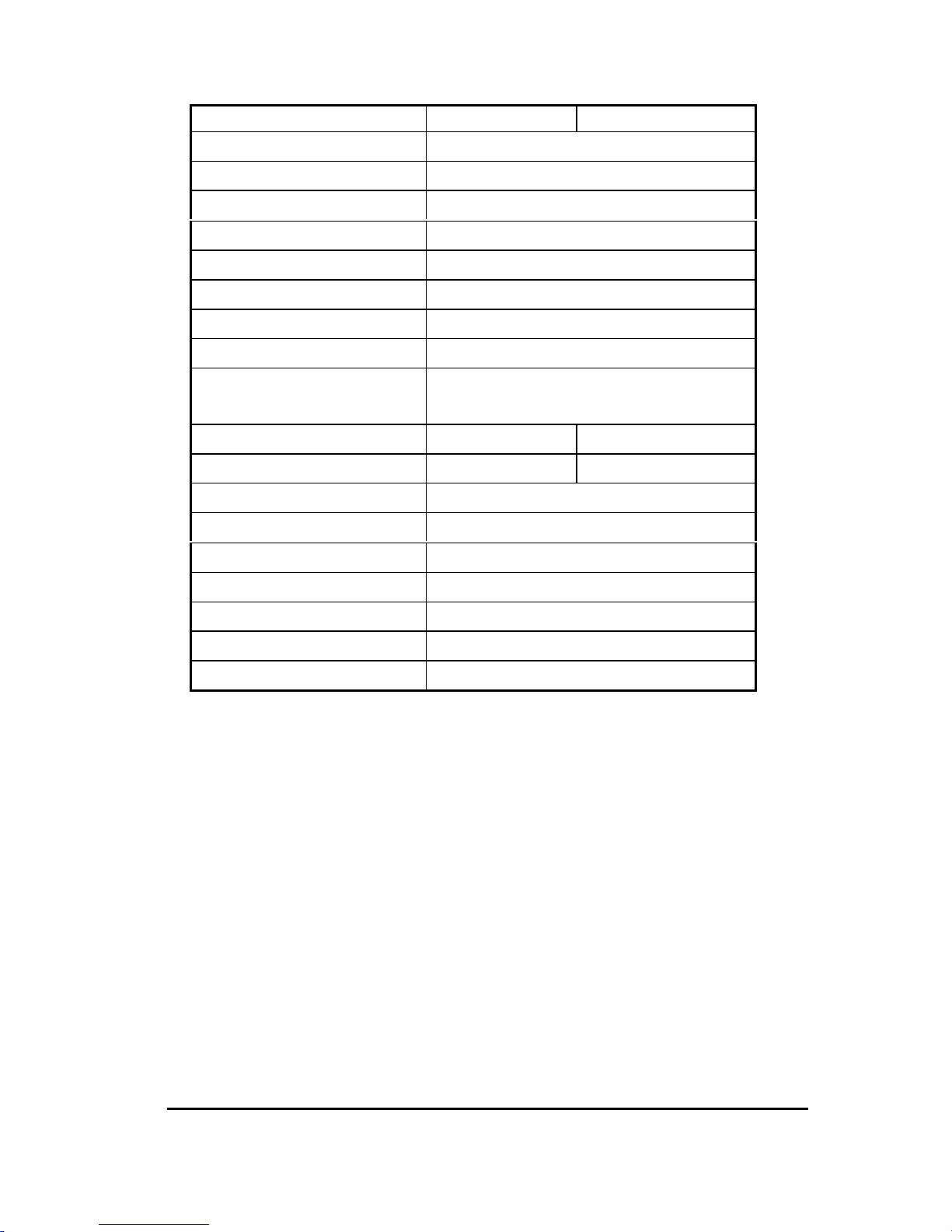

2 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

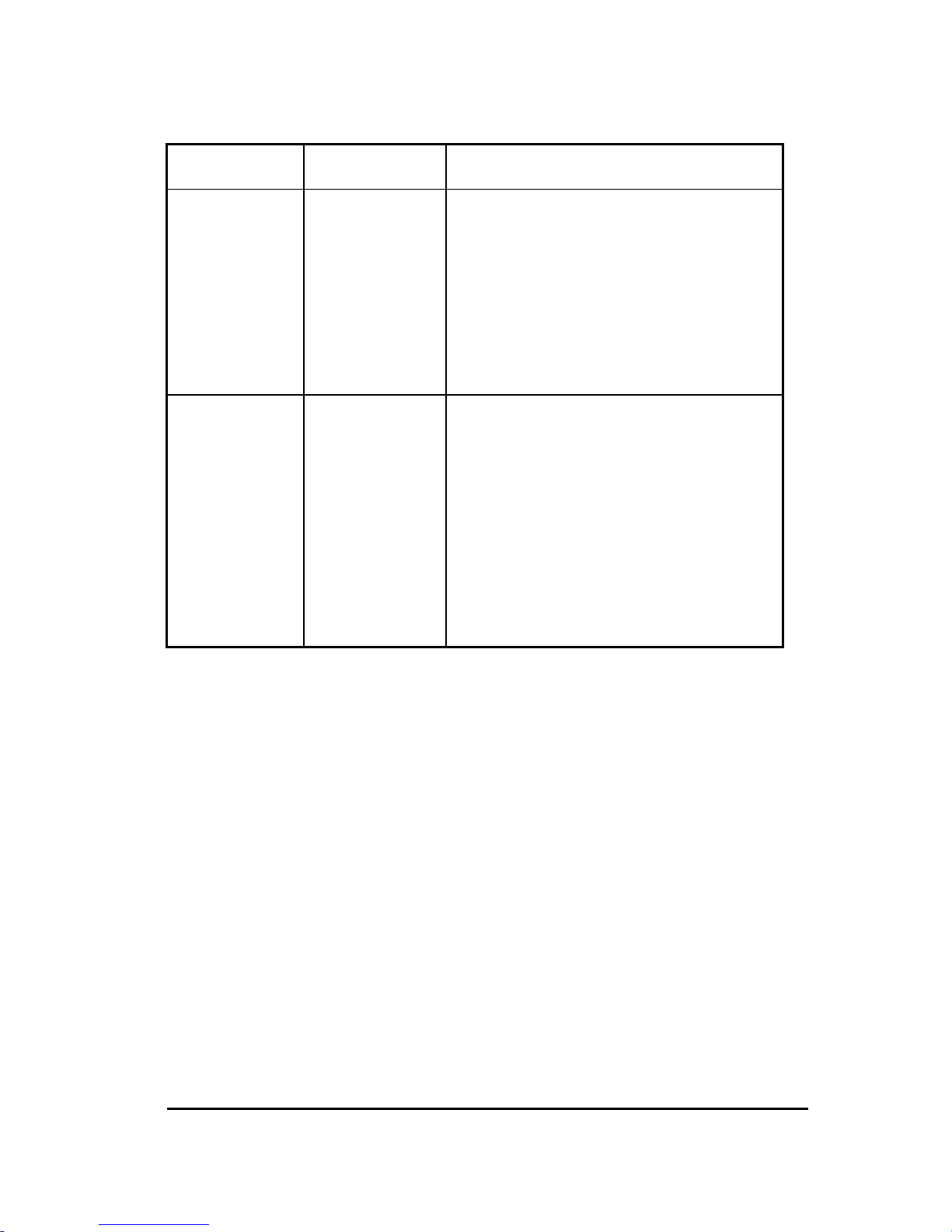

Product

Name

Function Package

ICOP-6024

Embedded

386SX Half Size

All-in-One SBC

l ICOP-6024 Embedded 386SX CPU SBC

l User’s Manual x 1

l Utility and Drivers Diskette x 1

l FDD cable x 1

l HDD cable x 1

l RS232 cable x 1

l Printer cable with bracket x 1

l AT KB / PS2 Mouse Y-cable x 1

ICOP-6024V

Embedded

386SX Half Size

All-in-One SBC

with VGA/LCD

l ICOP-6024V Embedded 386SX CPU

SBC

l User’s Manual x 1

l Utility and Drivers Diskette x 1

l FDD cable x 1

l HDD cable x 1

l RS232 cable x 1

l Printer cable with bracket x 1

l AT KB / PS2 Mous Y-cable x 1

l VGA cable x 1

Page 7

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 3

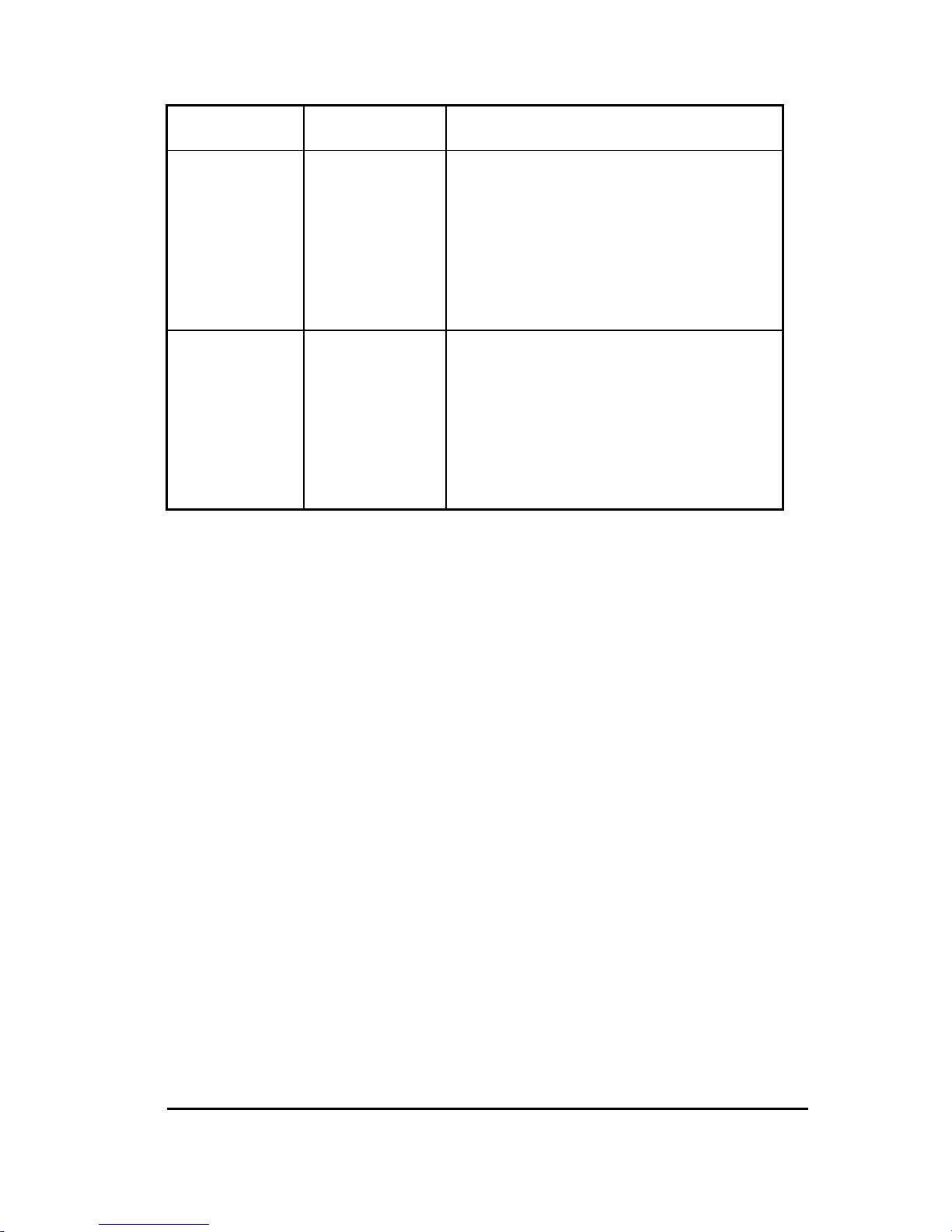

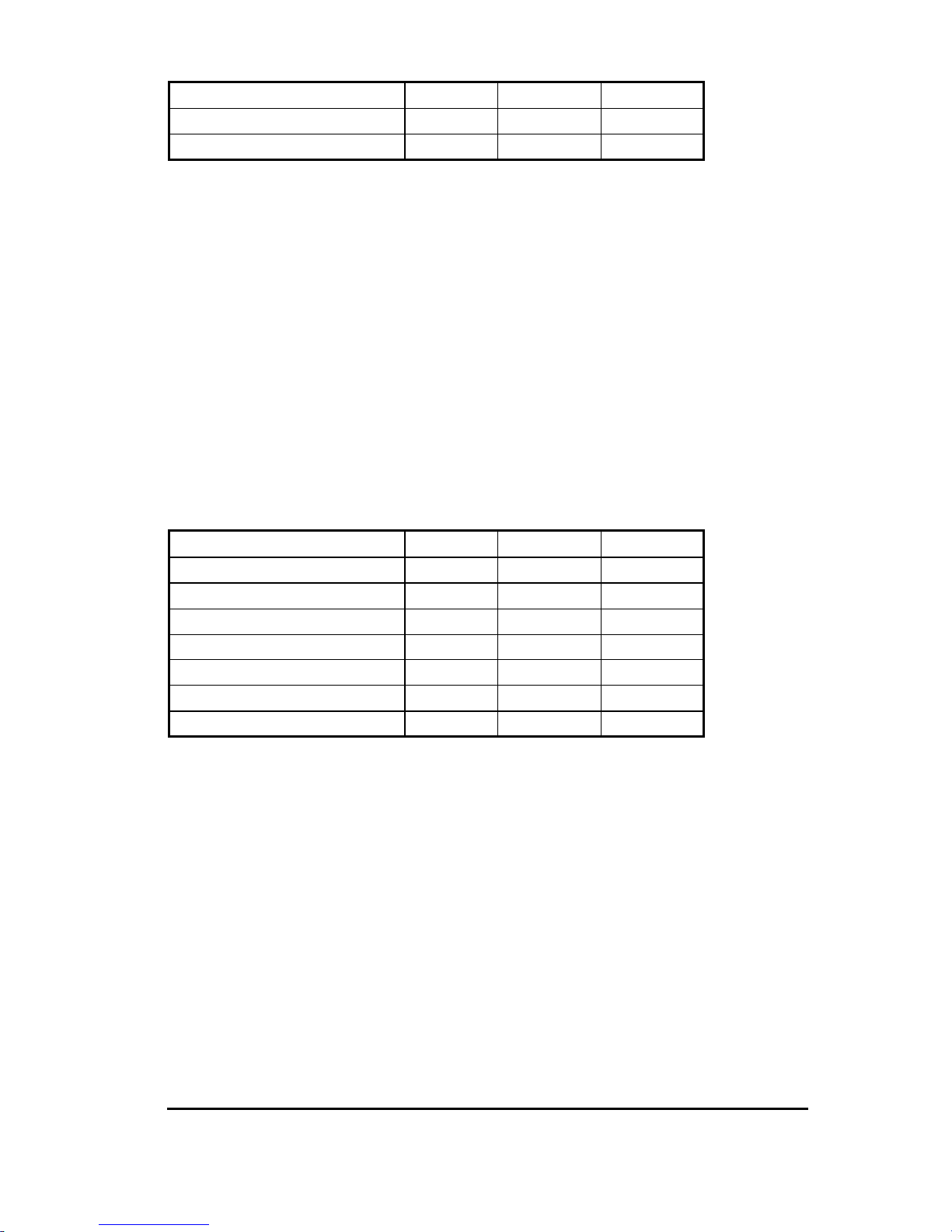

Product

Name

Function Package

ICOP-6020

Embedded

386SX Half Size

All-in-One SBC

l ICOP-6020 Embedded 386SX CPU SBC

l User’s Manual x 1

l Utility and Drivers Diskette x 1

l FDD cable x 1

l HDD cable x 1

l Printer cable with bracket x 1

l AT KB / PS2 Mouse Y-cable x 1

ICOP-6022

Embedded

386SX Half Size

All-in-One SBC

l ICOP-6022 Embedded 386SX CPU SBC

l User’s Manual x 1

l Utility and Drivers Diskette x 1

l FDD cable x 1

l HDD cable x 1

l Printer cable with bracket x 1

l AT KB / PS2 Mous Y-cable x 1

Page 8

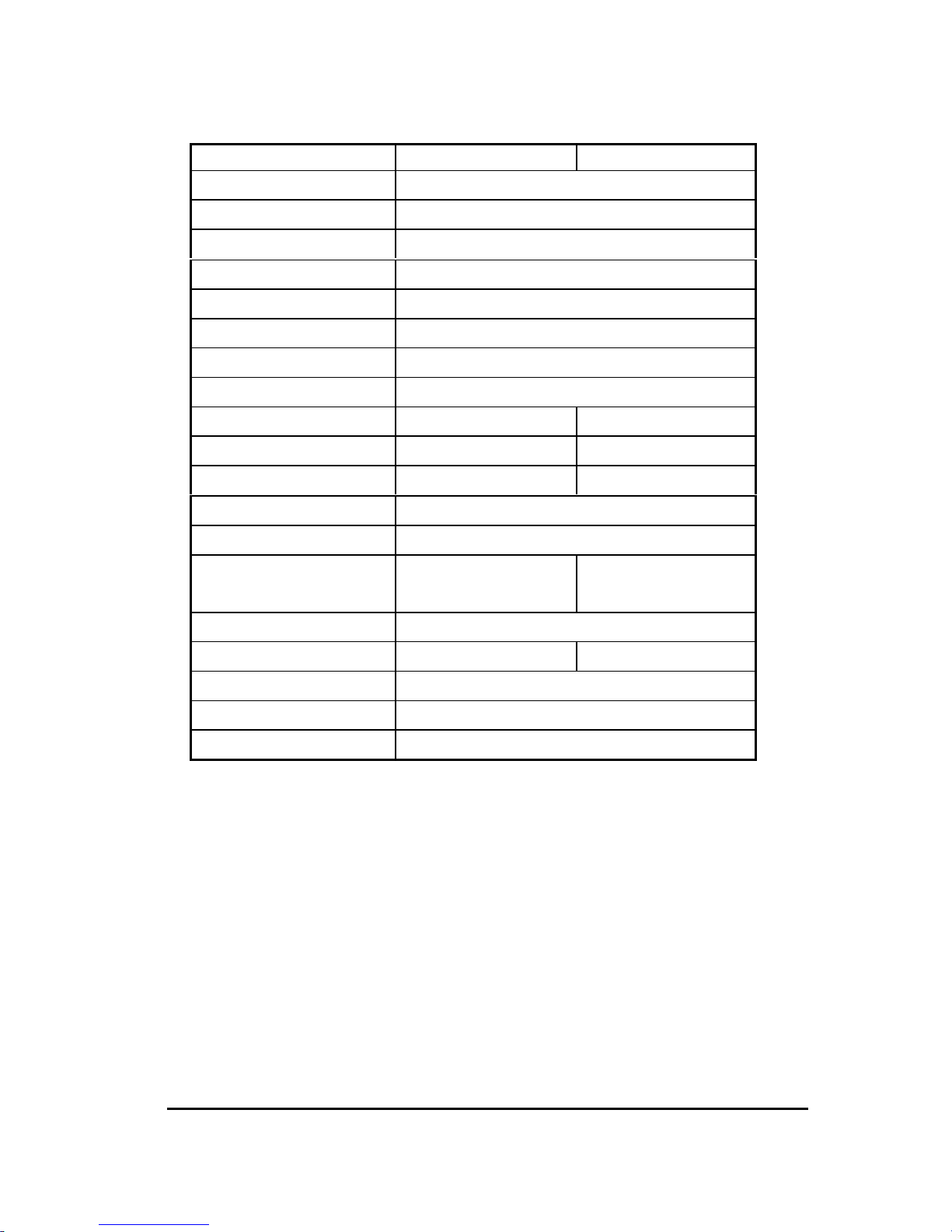

4 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

0.2 Specifications

Features ICOP-6025 ICOP-6025V

Processor

DM&P(Ali) M6117D

Chipset

DM&P(Ali) M6117D

Multi I/O Chip

Ali 5113

BIOS

AMI BIOS

Watchdog Timer From 30.5ìs to 512 seconds

Bus Interface ISA and PC/104 standard compliant

Memory 4MB On-Board up to 20MB

Memory Sockets 1

DiskOnChip Sockets

1

Digital I/O

16 Bit

DISPLAY

X VGA/LCD

VGA CRT/LCD Chip

X HMC HM86508

Enhanced IDE Port 1

Serial Port RS232 X 4 or RS232 X 3,RS485 X 1

Parallel Port 1

Power Requirement +5V @0.8A

Board Weight

240g

Board Size

185mm X 122 mm

Operating Temperature

-20 ~ +60°C

Page 9

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 5

Features ICOP-6024 ICOP-6024V

Processor

DM&P(Ali) M6117D

Chipset

DM&P(Ali) M6117D

Multi I/O Chip

Ali 5113

BIOS

AMI BIOS

Watchdog Timer From 30.5ìs to 512 seconds

Bus Interface ISA and PC/104 standard compliant

Memory 4MB On-Board up to 20MB

Memory Sockets 1

DiskOnChip

Flah Disk Sockets

2

DISPLAY X VGA/LCD

VGA CRT/LCD Chip

X HMC HM86508

Enhanced IDE Port

1

Serial Port

RS232 X 2 or RS232,RS485

Parallel Port

1

Power Requirement +5V @0.8A

Board Weight 240g

Board Size 185mm X 122 mm

Operating Temperature -20 ~ +60°C

Page 10

6 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

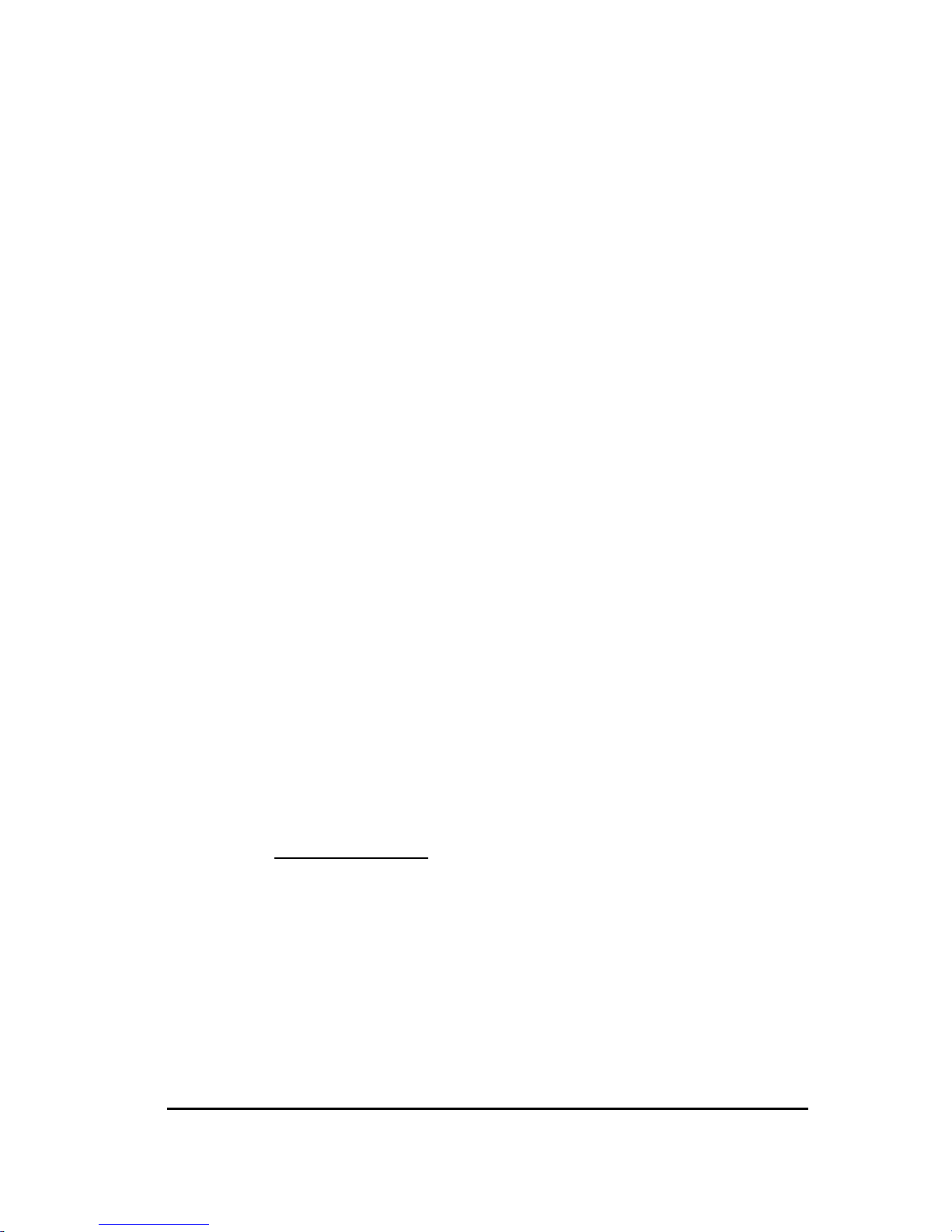

Features ICOP-6020 ICOP-6022

Processor

DM&P(Ali) M6117D

Chipset

DM&P(Ali) M6117D

Multi I/O Chip

Ali 5113

BIOS

AMI BIOS

Watchdog Timer From 30.5ìs to 512 seconds

Bus Interface ISA and PC/104 standard compliant

Memory up to 32MB

Memory Sockets SIMM 72 pin X 2

DiskOnChip Sockets

1 2

Flash Disk/ EPROM

X 2

Digital I/O

16 bit X

DISPLAY

X

Enhanced IDE Port 1

Serial Port RS232 X 2 RS232 X 2 or

RS232/485

Parallel Port 1

Power Requirement +12V,-12V,+5V @0.8A +5V @0.8A

Board Weight 240g

Board Size

185mm X 122 mm

Operating Tempture

-20 ~ +60°C

Page 11

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 7

0.3 Board Layout

ICOP-6025 (photo A), ICOP-6025V (photo B)

ICOP-6024 (photo C), ICOP-6024V (photo D)

ICOP-6020 (photo E), ICOP-6022 (photo F)

Page 12

8 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

0.4 Mechanical Drawing

ICOP-6025 (placement A), ICOP-6025V (placement B)

ICOP-6024 (placement C), ICOP-6024V (placement D)

ICOP-6020 (placement E), ICOP-6022 (placement F)

Page 13

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 9

C h a p t e r 1

Introduction

1.1 Features

The ICOP-602X contains all standard motherboard features such as :

386SX-40 compatible CPU, CRT and Flat Panel SVGA controller, serial and

parallel ports, floppy and EIDE disk controller.

The modules SSD socket can accommodate a DiskOnChip ® 2000, a new

generation of high performance single-chip Flash Disks of up to 144 MB.

The ICOP-602X is a core module for high performance control applications

in demanding embedded applications. Because the module implements all

key functions of a full PC/AT compatible system any standard PC compiler

or debugger can be used, resultng in a significantly reduced software

develop-ment cycle.

Enhanced IDE, High Speed I/O

In addition, the ICOP-602X has one PS/2 mouse port, serial ports (RS-232

or RS485), one bidirectional printer port that supports SPP, ECP andEPP

modes, an enhanced IDE HDD interface that supports PIO mode 4, and a

floppy disk controller.

Flash/EPROM Disk or DiskOnChip

The onboard socket can accept up to 2 MB EPROM or 1 MB Flash memory.

Both sockets can by jumper setting be assigned to hold a DiskOnChip.

There areno combinations possible of devices, it is either Flash, EPROM or

DiskOn-Chip.

Watchdog Timer

The watchdog timer optionally monitors system operation and can invoke

asystem reset when your application loses control over the system. The

timing of the watchdog timer is programmable by software.

Page 14

10 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

1.2 Specifications

• Embedded CPU : DM&P(Ali) M6117D is an implementation of an INTEL

compatible 386SX-40 CPU, Realtime clock, a watchdog timer and ALi’s

M1217B chipset

• BIOS : Y2K compliant AMI system BIOS

• DRAM Memory: 4MB EDO DRAM onboard

• Bus Interface : ISA and PC/104

• Data Bus : 16-bit

• Bus Speeds : PC/104 - 8 MHz

(above values are defaults, bus speeds are programmable up to 16 MHz)

• DMA Channels : 7

• Interrupt Levels : 15

• Enhanced IDE : supports one port and up to two hard drives or Enhanced

IDE devices of PIO mode 4. BIOS enabled/disabled

• Watchdog Timer : generates either a RESET, NMI or an IRQ when your

application loses control over the system. Optionally the watchdog can

trigger a user specified interrupt. The watchdog is configurable from 30.5ì s

to 512 seconds (in 30.5ì s segments)

• Real-time Clock : included in M6117D with onboard lithium battery backup

for 10 years of data retention. CMOS data backup of BIOS setup and BIOS

default.

• Keyboard and Mouse Connectors:

Supports different tpye connectors of AT Keyboard and PS/2-mouse

High Speed Multi I/O

• Chipset : ALi 5113 or SMS CFDC37C669

• Serial ports: Supports high speed RS-232 port, high speed RS-232/485

port (jumper selectable). Both with 16C550 UART and 16 byte FIFO. BIOS

enabled/ disabled

• Floppy Disk Drive Interface: supports up to two floppy drives, 5¼“ (360

KB or 1.2 MB) and 3½ “ (720 KB, 1.44 MB). BIOS enabled / disabled

• Bi-directional Parallel Port : supports SPP, EPP and ECP mode. BIOS

Page 15

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 11

enabled/disabled

Environmental and Power

• Power Requirements:

single voltage +5 V

+12V,-12V (ICOP-6020)

• Board Dimensions : 185 (L) x 122 (W) mm.

• Board Weight : 240 g

• Extended Operating Temperature: -20~+60 °C

Page 16

12 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

1.3 VGA Interface

(ICOP-6025V ,ICOP-6024V)

• Chipset : HMC HM86508

• Memory : 1 MB onboard

• System Bus : 16-bit ISA bus

• Panel Data Bus : 24-bit

• Display : CRT and Flat Panel Mono/TFT/DSTN/EL

• Supported Flat Panels :

NEC NL-6448AC30-10 TFT 9.4" 640X480

NEC NL-6448AC30-03 TFT 9.4" 640X480

NEC NL-6448AC33-10 TFT 10.4" 640X480

NEC NL-6448AC33-13 TFT 10.4" 640X480

NEC NL-6448AC33-18 TFT 10.4" 640X480

NEC NL-8060BC31-09 TFT 12’1 800X600

NEC NL-8060AC31-02 TFT 10.4" 800X600

NEC NL-8060AC31-01 TFT 10.4" 800X600

SHARP LQ10D42 TFT 10.4" 640X480

SHARP LQ10D421 TFT 10.4" 640X480

SHARP LQ12531 TFT 12.1" 800x600

SHARP LM64C35P MONO 10.4" 640X480

Planar EL640.480-AA1 EL color 10.4" 640X480

Check for other displays.

• Compatibility : IBM VGA hardware

Page 17

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 13

1.4 DiskOnChip 2000 Flash Disk

Flash Disk DiskOnChip ® 2000

• Package : Single Chip FlashDisk in 32-pin DIP JEDEC

• Capacity : 1-144 MByte capacity

• Data Reliability : ECC/EDC error correction

• Memory Window : 8 KByte

Page 18

14 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

C h a p t e r 2

Installation

2.1 Jumper Settings

2.1.1 ICOP-6025/V

JP1 RESET connector

JP2 Power LED connector

JP3 RS-232/485 selection for COM2

1-2 -> RS-232 mode (CONT11 active)

2-3 -> RS-485 mode (CONT8 active)

JP6 IDE LED connector

JP7 VGA IRQ9 operation (ICOP-6025V)

open -> VGA operation without IRQ9

closed -> VGA operation with IRQ9

2.1.2 ICOP-6024/V

JP1 RESET connector

JP2 Multi I/O Ali M5113 Enable/disable

1-2 -> Enabled

2-3 -> Disabled

JP3 RS-232/485 selection for COM2

1-2 -> RS-232 mode (JP4 active)

2-3 -> RS-485 mode (CONT9 active)

CONT13 DiskOnChip/EPROM Disk/Flash Disk address select

DOC address 1-2 3-4 5-6

C800H & CA00H (default)

Close Close Close

CA00H & CE00H Close Close Open

D800H & DA00H Close Open Close

DC00H & DE00H

Close Open Open

Page 19

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 15

Disabled

Open Close Open

Both EPROM

Open Open Close

Both Flash

Open Open Open

2.1.3 ICOP-6022

JP1 RESET connector

JP2 Multi I/O Ali M5113 Enable/disable

1-2 -> Enabled

2-3 -> Disabled

JP3 RS-232/485 selection for COM2

1-2 -> RS-232 mode (JP4 active)

2-3 -> RS-485 mode (CONT9 active)

JP4 internal COM2 RS-232 mode

CONT13 DiskOnChip/EPROM Disk/Flash Disk address select

DOC address 1-2 3-4 5-6

C800H & CA00H (default) Close Close Close

CA00H & CE00H Close Close Open

D800H & DA00H

Close Open Close

DC00H & DE00H

Close Open Open

Disabled Open Close Open

Both EPROM Open Open Close

Both Flash Open Open Open

2.1.4 ICOP-6020

CONT8

1-2 -> RESET connector

3-4 -> Power LED

5-6 -> IDE LED

Page 20

16 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

2.2 Connectors

2.2.1 ICOP-6025/V

CON1 External female 15-pin D-type CRT Display connector (ICOP6025V)

CON2 Internal 44-pin Flat Panel Display connector (ICOP-6025V)

CONT1 Internal 20-pin box header for 16-bit GPIO (digital I/O)

CONT2 PC/104 bus 64-pin

CONT3 PC/104 bus 40-pin

CONT4 External PS/2 and AT keyboard connector

CONT5 Speaker connector

CONT6 Power connector

CONT7 Internal AT-keyboard connector

CONT8 Internal COM2 RS-485

CONT9 FDD connector

COM1 External 9-pin male D-type connector for COM1

CONT11 Internal 10-pin boxheader connector for COM2

CONT12 IDE connector

CONT13 Internal 10-pin boxheader connector for COM3

CONT14 Internal 10-pin boxheader connector for COM4

P1 Parralel Port

SIM1 not available replaced by 4 MB onboard EDO memory

SIM2 Memory bank 1, SIMM for EDO

2.2.2 ICOP-6024/V

JP4 Internal COM2 RS-232 connector

CON1 External female 15-pin Dtype CRT Display connector (ICOP-6024V)

CON2 Internal 44-pin Flat Panel Display connector (ICOP-6024V)

CONT1 PC/104 bus 64-pin

Page 21

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 17

CONT2 PC/104 bus 40-pin

CONT3 Internal AT-keyboard connector

CONT4 External PS/2 and AT keyboard connector

CONT5 Internal PS/2 mouse connector

CONT6 External speaker connector

CONT7 Power LED connector

CONT9 Internal COM2 RS-485

CONT10 FDD controller

CONT11 IDE LED connector

CONT12 IDE connector

P1 Parralel Port

COM1 External COM1

SIM1 not available replaced by 4 MB onboard EDO memory

SIM2 Memory bank 1 (FP DRAM or EDO)

LED1 Power-on LED

2.2.3 ICOP-6022

CON2 Internal 44-pin Flat Panel Display connector

CONT1 PC/104 bus 64-pin

CONT2 PC/104 bus 40-pin

CONT3 Internal AT-keyboard connector

CONT4 External PS/2 and AT keyboard connector

CONT5 Internal PS/2 mouse connector

CONT6 External speaker connector

CONT7 Power LED connector

CONT9 Internal COM2 RS-485

CONT10 FDD controller

CONT11 IDE LED connector

Page 22

18 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

CONT12 IDE connector

P1 Parralel Port

COM1 External COM1

SIM1 not available replaced by 4 MB onboard EDO memory

SIM2 Memory bank 1 (FP DRAM or EDO)

LED1 Power-on LED

2.2.4 ICOP-6020

CONT1 Internal 20-pin box header for 16-bit GPIO (digital I/O)

CONT2 PC/104 bus 64-pin

CONT3 PC/104 bus 40-pin

CONT4 External PS/2 and AT keyboard connector

CONT5 Speaker connector

CONT6 Power connector

SIM1 Memory bank 0 (FP DRAM or EDO)

SIM2 Memory bank 1 (FP DRAM or EDO)

Page 23

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 19

2.3 DiskOnChip/EPROM/Flash ROM Disk

2.3.1 Setup a DiskOnChip ® 2000 Flash Disk

Installation Instructions

1. Make sure the ICOP-602X is powered OFF

2. Plug the DiskOnChip 2000 device(s) into its socket. Verify the direction is

correct (pin 1 of the DiskOnChip 2000 is aligned with pin 1 of the socket)

3. Set address for both DiskOnChip devices (note that the last two settings

are for normal EPROM or Flash devices)

4. Power up the system

5. During power up you may observe the messages displayed by the

DiskOnChip 2000 when its drivers are automatically loaded into system’s

memory

6. At this stage the DiskOnChip 2000 can be accessed as any disk in the

system

7. If the DiskOnChip 2000 is the only disk in the system, it will appear as the

first disk (drive C: in DOS)

8. If there are more disks besides the DiskOnChip 2000, the DiskOnChip

2000 will appear by default as the last drive, unless it was programmed as

first drive. (please refer to the DiskOnChip 2000 utilities user manual)

9. If you want the DiskOnChip 2000 to be bootable: a - copy the operating

system files into the DiskOnChip by using the standard DOS command (for

example: sys d:) b - The DiskOnChip should be the only disk in the systems

or should be configured as the first disk in the system (c : ) using the

DUPDATE utility

For more information on DiskOnChip2000 technology, visit M-Systems Web

site http:// www.m-sys.com where you can find Utilities Manual, Data

Sheets and Application Notes. In addition, you can find the lasted

DiskOnChip 2000 S/W Utilities.

Page 24

20 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

2.3.2 Setting up a Flash Disk

Before you can use the ICOP-602X’s Flash disk you will have to initialize it

using a software utility called “PC104.EXE”. This program can be found on

the utility disk in the subdirectory “ A:\FLASH”

- Connect a keyboard and floppy disk ICOP-602X to the PC/104 bus and

boot-up your system.

- run PC104.EXE (this is a DOS command line utility)

ICOP-602X FLASH disk initialize program V1.0

FLASH manufacturer : (1)ATMEL (2)SST

Input manufacturer number (1,2) : 1

Input quantity of FLASH (1,2) : 2

Simulation disk:

(1)DISK-A (2)DISK-B (3)DISK-C (4)DISK-D

Input manufacturer number (1,2,3,4) : 1

FLASH-DISK initialize finish.

(Text in bold should be entered by user)

- After running the PC104.EXE configuration program reboot the system,

while holding down the left “ CRTL” key. This will bring you to the “Flash Disk

Utility”

- “CHANGE CURRENT DISK NUMBER” lets you select the drive you want to

assign to the disk, either A, B, C or D

- “CHANGE FLASH DISK SIZE” lets you select the amount of Flash EPROM

chips that are onboard.

- make selections and reboot the system after closing the program

Your disk can now be formatted and setup with normal DOS commands such

as

FORMAT, FDISK, COPY, SYS etc.

Note : when assigning the solid state disk as either C or D, you first have to

run FDISK before formatting the drive !

Page 25

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 21

2.3.3 Setting up an EPROM disk

EPROMs should be inserted starting from Socket. All modules have to be of

the same type.

To create a ROM disk you will need the following:

- EPROM devices

- EPROM programmer

- ROM files

The ROM files are hacked-up portions of your system and program files that

should have the same size as your EPROM devices.

On the utility disk you will find a program called: ROMIMAGE.EXE that will

assist you in creating these files. Before using the program there are some

files you will have to prepare first:

1. The system files, for example MSDOS.SYS, I/O.SYS, COMMAND.COM

The program can pick these files up automatically from your boot deviceor

from a bootable floppy.

2. Your application files and other necessary DOS files. Make a subdirectory

that only contains these additional files. With “other DOS files” are meant

files such as AUTOEXEC.BAT, CONFIG.SYS, EMM386.EXE etc

3. Prepare a directory that can temporarily hold the generated ROM files

Once you prepared all the above, start the ROMIMAGE.EXE programSystem

driver :

location of system files (see 1)

Source path: location of program files (see 2)

Destination path: this is where the ROM files go (see 3)

EPROM-size: depends on your choice

Simulation-disk: set this to the drive letter the ROM disk should emulate

After you have set all the right directories, use the Analysis file function to

let the program determine how many files of what size it should generate.

After using the Analysis function go to Create image , and generate the

ROM files. Than exit the program. In the directory that was assigned to hold

the ROM files you will find your ROM images:

For example: ROM010.01 ROM010.02

Use an EPROM programmer to write the files to their EPROMs.

Page 26

22 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

Beware to keep track of their sequence when inserting the EPROM’s

PRESS ESC KEY QUIT THIS PROGRAM

Page 27

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 23

2.4 Watchdog Timer

The watchdog timer uses a 32.768 KHz frequency source with a 24-bit

counter. Its time range stretches from 30.5 ms to 512 sec. with a resolution

of 30.5 ms. When the watchdog times out a System RESET, NMI or IRQ can

be invoked. Watchdog timer control and the 24-bit counter itself occupy 6

consecutive 8-bit address locations.

When functioning properly the system resets the watchdog timer periodically

to prohibit that it times out. If the watchdog timer times out, it will RESET

the system, or generate and NMI or IRQ, depending on its configuration.

Watchdog or System Timer

Another great application is to generate a periodic IRQ signal. Under DOS

environment, the 8254, system timer 0, will generate IRQ0 every 54.9 ms.

The watchdog is like system timer 0. It can be programmed to periodically

generate a configurable IRQ. It may be clear that the selected IRQ, will be

no longer available to the system.

Configuring the Watchdog Timer in the BIOS

The M6117D watchdog configuration register can be controlled by software

or can be setup in the BIOS. To do so go to BIOS Setup’s “ Advanched

Chipset Setup”

Watchdog Function = Enable/Disable

Watchdog Signal = RESET, NMI or IRQ 3/4/5/6/7/9/10/11/12/14/15

Watchdog Timer = 1/2/4/8/16/32/64/128/256/512 Seconds

The BIOS setup only offers a limited amount of time-out values. More a

hiher resolution of timeout values refer to the next paragraph “ Configuring

the Watchdog Timer by Software” Note that in case of using the BIOS setup,

the watchdog starts counting the moment it passes the BIOS setup. This

means that if you set the time-out period to 1 second, the system will keep

rebooting before being able to load operating system or software !

After you have finnished configuring you watchdog timer read “Timeout

Status & Reset - INDEX 3CH” on page 12 and look at the example on page

15 to find out how to priodically reseting the timeout status to prevent the

watchdog timer from invoking a RESET, NMI or IRQ.

Configuring the Watchdog Timer by Software

Chipset configuration registers

The M6117D configuration register INDEX 37H, 38H, 39H, 3AH, 3BH, 3Ch

Page 28

24 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

are used to control the watchdog functions and/or display its current status.

Enable/Disable watchdog - INDEX 37H

Bit Value Action

7 reserved Do not modify the value of these bits!

6 0

1

Disable watchdog timer

Enable watchdog timer

5-0 Other function Do not modify the value of these bits!

Watchdog time out action - INDEX 38H

Bit Value Action

7-4 0000 No output signal

0001 IRQ3

0010 IRQ4

0011 IRQ5

0100 IRQ6

0101 IRQ7

0110 IRQ9

0111 IRQ10

1000 IRQ11

1001 IRQ12

1010 IRQ14

1011 IRQ15

1100 NMI

1101 System RESET

1110 No output signal

1111 No output signal

3-0 Other function Do not modify the value of these bits!

Watchdog timer - INDEX 39H, 3AH, 3BH

Page 29

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 25

Index 3Bh 3Ah 39h

Bits D7……D0 D7……D0 D7……D0

counter [VSB……………. …………………... ………..LSB]

For example

Index 3Bh 3Ah 39h Time out

00h 00h 01h 30.5ì s

00h 00h 02h 61ì s

00h 01h 00h 7.8 ms

00h 02h 00h 15.6 ms

01h 00h 00h 2 s

02h 00h 00h 4 s

FFh FFh FFh 512 s

Timeout Status & Reset - INDEX 3CH

Bit Value Action

7 0

1

Timeout has not occurred

Timeout has occured

6

5 1

0

Reset timer

Has no meaning

4-0

Other function, do not modify these bits

Programming the watchdog

To perform any operation on the M6117D configuration registers you always

have to unlock first and lock the registers afterwards

Unlock configuration register Lock configuration register

mov al, 013h mov al, 013h

out 22h, al out 22h, al

nop nop

Page 30

26 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

nop nop

mov al, 0c5h mov al, 000h

out 23h, al out 23h, al

nop nop

nop nop

Read the value of a configuration register

For example, read INDEX 3Ch :

Unlock configuration register

mov al, 03ch

out 22h, al

nop

nop

in al, 23h

nop

nop

push ax

Lock configuration register

pop ax ;AL - result

Write data to configuration register

For example, write 0FFh to INDEX 3Bh :

Unlock configuration register

mov al, 03bh

out 22h, al

nop

nop

mov al, 0ffh

out 23h, al

nop

Page 31

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 27

nop

Lock configuration register

Watchdog Program Example

We use the following sequence to initialize the watchdog timer:

(1) Unlock configuration register.

(2) Disable watchdog timer by setting INDEX 37H Bit 6 to ‘0’.

(3) Set the expected counter value to INDEX 3BH, 3AH, 39H.

(4) Select timeout action from INDEX 38H Bit 7-4.

(5) Enable watchdog timer by setting INDEX 37H Bit 6 to ‘1’.

(6) Lock configuration register.

Example: Set timeout to 128 sec to generate a system RESET.

; Please use MASM to compiler the following program

; Execute under DOS environment

dosseg

. model small

. stack 100h

.code

main proc

mov ax, 0c513h ; Unlock config. register

call writechip

mov ax, 03737h ; Disable watchdog timer

call readchip

and al, 10111111b

xchg ah, al

call writechip

mov ax, 0403bh ; Set the expected counter

; value

call writechip ; to [400000h]

mov ax, 0003ah ; 30.5*sec*400000h= 128 sec

Page 32

28 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

call writechip

mov ax, 00039h

call writechip

mov ax, 03838h ; Select “system reset” as

; timeout action

call readchip

and al, 00001111b

or al, 11010000b

xchg ah, al

call writechip

mov ax, 03737h ; Enable watchdog timer

call readchip

or al, 01000000b

xchg ah, al

call writechip

mov ax, 00013h ; Lock config. register

call writechip

mov ax, 04c00h

int 21h

main endp

readchip proc

out 22h, al

nop

nop

in al, 23h

nop

nop

ret

Page 33

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 29

readchip endp

writechip proc

out 22h, al

nop

nop

xchg ah, al

out 23h, al

nop

nop

xchg ah, al

ret

writechip endp

end main

Reset watchdog timer

Resets the watchdog timer periodically to prevent timeout.

mov ax, 0c513h ; Unlock configuration

; register

call writechip

mov ax, 03C3Ch ; Reset watchdog timer

; counter

call readchip

or al, 00100000b ; The counter is reset at

xchg ah, al ; out 23h, al

call writechip

mov ax, 00013h ; Lock configuration

; register

call writechip

(the above code uses readchip and writechip procedures)

Page 34

30 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

2.5 General Purpose I/O

M6117D supports 16 independent GPOs and GPIs. This group of GPOs

does not need external 74LS373 to latch as generate purpose output. Also

this group of GPIs do not share signals with the ISA data bus, so no external

74LS245 is required either.

At boot time the state of the GPIO ports can be set in the BIOS.

Go to BIOS Setup’s “Advanched Chipset Setup”

GPIO Sample Program

; Please use TASM to compiler the following program.

; Execute under DOS environment.

;

.286

.model small

.code

mov al,13 ; Unlock configuration register.

out 22,al ;

mov al,c5 ;

out 23,al ;

mov al,4e ; Enable GPIO[7-0] is output pin.

out 22,al ;

mov al,ff ; If AL fill “ 00”,

; GPIO[7-0] set input pin.

mov 23,al ; User can be set logic “1 ”

; of OUT direction.

mov al,4f ; Enable GPIO[15-8] is input pin

out 22,al ;

mov al,00 ; If AL fill “ FF”,

; GPIO[15-8] set output pin.

Page 35

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 31

out 23,al ; User can be set logic “0 ”

; of IN direction.

mov al,47 ; Output data port.

out 22,al ;

mov al,55 ; Example data out value is 55,

; to output pin

out 23,al ; GPIO[7-0]. So user can

; repeat this loop.

mov al,46 ; If GPIO[7-0] is set input direction, then data

out 22,al ; input port is 46.

in al,23 ; Example data input value

; from data input GPIO[7-0]

mov al,4c ; Input data port

out 22,al ;

in al,23 ; Read data from GPIO[15-8]

; into AL register.

mov al,4d ; If GPIO[15-8] is set output

; direction, then data

out 22,al ; output port is 4d.

mov al,55 ; output data value is 55.

out 23,al ; Example data output value

; to data input GPIO[15-8]

....... continue program

end

Page 36

32 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

C h a p t e r 3

AMI BIOS Setup

When the system is powered on, the BIOS will perform diagnostics

and initialize system components, including the video system. (This is

self-evident when the screen first flicks before the Video Card header

is displayed). This is commonly referred as POST (Power-On Self

Test). Afterwards, the computer will proceed its final boot-up stage by

calling the operating system. Just before that, the user may interrupt

to have access to SETUP.

The AMI BIOS is entered by pressing the <DEL> key after resetting (CTRLALT-DEL) or powering up the computer. You can bypass the extended

CMOS settings by holding the <INS> key down during boot-up. This is really

helpful, especially if you bend the CMOS settings right out of shape and the

computer won’t boot properly anymore. The following pages are meant to

give you a better insight into the options you have to setup your system.

Many options depend on the choice of type of memory, memory speed,

peripherals and the programs that you will be running. The effect of many of

these settings are related to system perfor-mance that can destabilize

operation. We urge you to proceed with caution.

Page 37

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 33

3.1 Standard CMOS Setup

Date

The BIOS determines the day of the week from the other date information;

this field is for information only.

Time

The time format is based on the 24-hour military-time clock. For example, 1

p.m. is 13:00:00. Press the « or ( key to move to the desired field . Press the

PgUp or PgDn key to increment the setting, or type the desired value into

the field.

Floppy Drive A, B

Select the correct specifications for the diskette drive(s) installed in the

computer.

None: No diskette drive installed

360K : 5.25 in5-1/4 inch PC-type standard drive

1.2M : 5.25 in5-1/4 inch AT-type high-density drive

720K : 3.5 in3-1/2 inch double-sided drive

1.44M : 3.5 in3-1/2 inch double-sided drive

Hard Disks

The BIOS supports up to four IDE drives. This section does not show

information about other IDE devices, such as a CD-ROM drive, or about

other hard drive types, such as SCSI drives.

NOTE : recommend that you select type AUTO for all drives.

The BIOS can automatically detect the specifications and optimal operating

mode of almost all IDE hard drives. When you select type AUTO for a hard

drive, the BIOS detects its specifications during POST, every time the

system boots. If you do not want to select drive type AUTO, other methods

of selecting the drive type are available:

1. Match the specifications of your installed IDE hard drive(s) with the

preprogrammed values for drive types 1 through 45.

2. Select USER and enter values into each drive parameter field.

3. Use the IDE HDD AUTO DETECTION function in Setup.

Here is a brief explanation of drive specifications:

Page 38

34 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

Type: The BIOS contains a table of predefined drive types. Each defined

drive type has a specified number of cylinders, number of heads, write

precompensation factor, landing zone, and number of sectors. Drives whose

specifications do not accommodate any predefined type are classified as

type USER.

Size: Disk drive capacity (approximate). Note that this size is usually slightly

greater than the size of a formatted disk given by a disk-checking program.

Cyln: Number of cylinders

Head: Number of heads

WPcom: Write Precompensation. Older HDD’s have the same number of

sectors per track at the innermost tracks as at the outermost tracks. This

means that the data density at the innermost tracks is higher and thus the

bits are lying closer together. Areas having the same direction tend to float

away from each other and areas having opposite direction tend to float

towards each other making the data less reliable after some time. To avoid

this, starting from the WP cylinder, bits are written on the surface making

your data last longer. Starting with this Cylnumber until the end of

Cylnumber the writing starts earlier on the disk. In modern HDs (all ATBUS

and SCSI, Small Computer Systems Interface) this entry is useless.

Sec: Number of sectors

LBA Mode Logical Block Addressing Mode enables support for IDE drives

with capacities greater than 528 MB (On/Off)

Block Mode Support IDE drives that use Block Mode. (On/Off)

32Bit Mode Support IDE drives that permit 32-bit accesses. (On/Off)

PIO Mode IDE Programmed I/O mode. PIO programming also

works with ATAPI CD-ROM drives. The settings are Auto, 0, 1, 2, 3, 4, or 5.

Click on Auto to allow AMIBIOS to automatically find the PIO mode that the

IDE drive being configured uses. If you select 0-5 you must make absolutely

certain that you are selecting the PIO mode supported by the IDE drive

being configured.

BootSector Virus Protection

It is not exactly a virus protection. All it does is whenever your boot sector is

accessed for writing, it gives a warning to the screen allowing you to disable

the access or to continue. Extremely annoying if you use something like

OS/2 Boot Manager that needs to write to it. It is completely useless for

SCSI or ESDI (Enhanced Small Device Interface) drives as they use their

Page 39

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 35

own BIOS on the controller. Disabled recommended. If you want virus

protection, use a TSR (Terminate and Stay Resident) virus detection (Norton,

Central Point, etc ...). Scan by Macfee is also a good idea. Available on most

FTP servers, it is shareware.

Page 40

36 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

3.2 Advanced CMOS Setup

1st Boot Device

Specifies the first device for which to look and use for booting the system.

Options are : Disabled 1st IDE-HDD, 2nd IDE-HDD, 3rd IDE-HDD, 4th IDEHDD, Floppy, ARMD-FDD, ARMD-HDD, ATAPI CDROM, SCSI or NETWORK.

ARMD (FDD/HDD) means “ATAPI Removeable Media Device”.

2nd Boot Device

Specifies the second device for which to look and use for booting the system.

Options are : Disabled 1st IDE-HDD, 2nd IDE-HDD, 3rd IDE-HDD, 4th IDEHDD, Floppy, ARMD-FDD, ARMD-HDD, ATAPI CDROM, SCSI or NETWORK.

Floppy Drive Swap

This field is effective only in systems with two floppy drives. Selecting

Enabled assigns physical drive B to logical drive A, and physical drive A to

logical drive B.

PS/2 Mouse Support

This setting is specially for those users who whish to connect a PS/2 mouse.

Enabling reserves IRQ 12 for the PS/2 mouse. Disabling releases the IRQ

12 for use by another system component.

System Keyboard

“Present”. If “ Absent” is selected this option sets the BIOS to pass the

keyboard test in the POST, allowing to reset a PC without a keyboard (file

server, printer server, etc.), without the BIOS producing a keyboard error.

Primary display

The type of display standard you are using. The most frequent is

VGA/PGA/EGA. Modern computers have VGA (Video Graphics Array). If you

have an older black/ white display select Mono. If you want to use the board

without display controller set this value to “ Absent”. This option sets the

BIOS to pass the display controller test in the POST, allowing to boot a PC

without a display controller. Even if set to “ Absent” the board will still try to

initialize a display card if present.

Password Check

If you have set a password, select whether the password is required every

time the System boots, or only when you enter the BIOS Setup.

Page 41

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 37

Always The system will not boot and access to Setup will be denied if the

correct password is not entered at the prompt.

Setup The system will boot, but access to Setup will be denied if the

correct password is not entered at the prompt.

C8000, 16 K Shadow

Specifies whether the specified area of ROM is to be shadowed and if

shadowed, whether it should be written to or read from cache memory. The

fail-safe default is Disabled.

Caution: Some option ROMs do not operate properly when shadowed.

CC000, 16 K Shadow

D0000, 16 K Shadow

D4000, 16 K Shadow

D8000, 16 K Shadow

DC000, 16 K Shadow

Page 42

38 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

3.3 Advanced Chips et CMOS Setup

VGA Frame Buffer Size

The STPC implements a single memory subsystem for both the system as

well as the frame buffer memory. In other words, the size of the DRAM

available to the system is reduced by the size of the DRAM allocated to the

frame buffer. The lower range of the DRAM, starting from the DRAM address

00h, is allocated to frame buffer. The rest of the memory is used by the

system.

ISACLK

Set the speed of the ISA bus here. The settings are tied to the speed of the

PCI bus. If the PCI bus operates at 33 MHz, a setting of PCICLK/4 (default)

would yield an ISA bus speed of approximately 8 MHz, the standard speed

of the ISA bus. While most devices operate at higher ISA bus speeds, try a

slower bus speed if your ISA device does not function properly.

Memory Hole

You can reserve this area of system memory for ISA adapter ROM. When

this area is reserved, it cannot be cached. The user information of

peripherals that need to use this area of system memory usually discusses

their memory requirements.

The memory hole can be configured as 1 MB (15-14MB), 2 MB (15-13MB), 4

MB (15-11MB), 8 MB (15-7MB) or disabled.

Page 43

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 39

3.4 Peripheral Setup

Onboard FDC

Enable/disable or Auto detect FDD Controller

Onboard Serial Port1 Disable or enable wtih I/O address 3E8h, 3F8h as

COM1 or 2E8h or 2F8h as COM2

Onboard Serial Port1 Disable or enable wtih I/O address 3E8h, 3F8h as

COM1 or 2E8h or 2F8h as COM2

Onboard Parallel Port

This option specifies the parallel port mode. ECP and EPP are both

bidirectional data transfer schemes that adhere to the IEEE P1284

specifications. The settings are 378h, 278h, or Disabled.

Normal The normal parallel port mode is used.

Bi-Dir Supports bidirectional transfers on the parallel port.

EPP The parallel port can be used with devices that adhere to the Enhanced

Parallel Port (EPP) specification. EPP uses the existing parallel port signals

to provide asymmetric bidirectional data transfer driven by the host device.

ECP The parallel port can be used with devices that adhere to the Extended

Capabilities Port (ECP) specification. ECP uses the DMA protocol to achieve

transfer rates of approximately 2.5 Mbs. ECP provides symmetric

bidirectional communications.

Parallel Port DMA

This option is only available if the setting for the Parallel Port Mode option is

ECP. The settings are Disabled, DMA CH (channel) 0, DMA CH 1, or DMA

CH 3.

The default setting is Disabled.

Onboard SIP1 PCI IDE

Enables or disables the onboard Primary IDE controller

These settings provide the best performance characteristics.

3.5 Auto-Detect Hard Disks

The Enhance IDE feature is included in all AMI BIOS. The following is

a brief description of this feature.

1. Setup Changes

Page 44

40 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

<I> Auto-detection

BIOS setup will display all possible modes supported by the

HDD including NORMAL, LBA & LARGE. If HDD does not

support LBA modes, no ’ LBA’ option will be shown. Users

can select a mode that is appropriate for them.

<II> Standard CMOS Setup

CYLS Heads Precomp Landzone Sector Mode

Drive C :User(516MB) 1120 16 65535 1119 59 NORMAL

Drive D :None (203MB) 684 16 65535 685 38 ----------

When HDD type is in ‘ user’ type, the ”MODE” option will be

open for user to select the HDD mode.

2. HDD Modes

The Award BIOS supports 3 HDD modes: NORMAL, LBA & LARGE.

n NORMAL mode

A generic access mode wherein neither the BIOS nor the IDE

controller will make any transformations during accessing.

The maximum number of cylinders, head & sectors for NORMAL mode

are 1024, 16 & 63.

no. Cylinder ( 1024)

x no. Head ( 16)

x no. Sector ( 63)

x no. per sector ( 512)

528 Megabytes

I f user sets his HDD to NORMAL mode, the maximum accessible HDD

size will be 528MB even though its physical size may be greater than

that!

n LBA (Logical Block Addressing) mode

A new HDD accessing method to overcome the 528MB bottleneck.

The number of cylinders, heads & sectors shown in setup may not be

the number physically contained in the HDD.

During HDD accessing, the IDE controller will transform the logical

address described by sector, head & cylinder number into its own

physical address inside the HDD.

The maximum HDD size supported by LBA mode is 8.4GB which is

obtained by the following formula:

no. Cylinder ( 1024)

x no. Head ( 255)

Page 45

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 41

x no. Sector ( 63)

x bytes per sector ( 512)

814 Gigabytes

n LARGE mode

Extended HDD access mode supported by Award Software.

Some IDE HDDs contain more than 1024 cylinder without LBA support

(in some cases, user does not want LBA). The Award BIOS provides

another alternative to support these kinds of HDD!

Example of LARGE mode:

CYLS HEADS SECTOR MODE

1120 16 59 NORMAL

560 32 59 LARGE

BIOS tricks DOS (or other OS) that the number of cylinders is less than

1024 by dividing it by 2. At the same time, the number of heads is

multiplied by 2. A reverse transformation process will be made inside

INT13h in order to access the right HDD address!

Maximum HDD size:

no. Cylinder ( 1024)

x no. Head ( 32)

x no. Sector ( 63)

x bytes per sector ( 512)

1 Gigabytes

Page 46

42 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

3.6 Change Supervisor Password

When you select this function, the following message will appear at

the center of the screen to assist you in creating a password.

ENTER PASSWORD:

Type the password, up to eight characters, and press <Enter>. The

password typed now will clear any previously entered password from

CMOS memory. You will be asked to confirm the password. Type the

password again and press <Enter>. You may also press <Esc> to

abort the selection and not enter a password.

To disable password, just press <Enter> when you are prompted to

enter password. A message will confirm the password being disabled.

Once the password is di sabled, the system will boot and you can

enter Setup freely.

PASSWORD DISABLED.

If you select System at Security Option of BIOS Features Setup Menu,

you will be prompted for the password every time the system is

rebooted or any time you try to enter Setup. If you select Setup at

Security Option of BIOS Features Setup Menu, you will be prompted

only when you try to enter Setup.

Page 47

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 43

3.7 Auto Configuration with Optimal Setting

This option allows you to load the default values to your system

configuration. These default settings are optimal and enable all high

performance features.

3.8 Auto Configuration with Fail Safe Setting

This option allows you to load the troubleshooting default values

permanently stored in the BIOS ROM. These default settings are nonoptimal and disable all high-performance features.

3.9 Save Settings and Exit

This option allows you to determine whether to accept the

modifications or not. If you type “ Y”, you will quit the setup utility and

save all changes into the CMOS memory. If you type “ N”, you will

return to Setup utility.

3.10 Exit Without Saving

Select this option to exit the Setup utility without saving the changes

you have made in this session. Typing “ Y” will quit the Setup utility

without saving the modifications. Typing “ N” will return you to Setup

utility.

Page 48

44 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

C h a p t e r 4

SVGA Setup

4.1 Introduction

The ICOP-602XV has an on-board VGA interface. The specifications

and features are described as follows:

4.1.1 Chipset

The ICOP-602XV uses a HMC HM86508 for its SVGA controller,

which supports conventional analog CRT monitor or flat panel. In

addition, it also supports interlaced and non-interlaced analog

monitors (color and monochrome VGA) in high-resolution modes

while maintaining complete IBM VGA compatibility. Multiple

frequency (multisync) monitors are handled as if they were analog

monitors.

4.1.2 Display memory

With 1 MB memory, the VGA controller can drive CRT displays or

color panel displays with resolutions up to 1024 x 768 at 256 colors.

4.2 Flat Panel BIOS and Wiring

Below is a list of optional Flat Panel SVGA BIOS. The VGA BIOS is

combined with the system BIOS in a single. To change to another BIOS

please contact your local dealer.

MLCD.dat - Data File for MONO DSTN640*480 (Default)

example : (1) HOSIDEN HLM6667

(2) HITACHI LMG5160XUFC

(3) CASIO MD650TS00-01

(4) OPTREX DMF_50260NFU-FW-8

DSTN.dat - Data file for Color DSTN640*480

example : (1) Sanyo LCM-5331-22NTK

(2) SHARP LM64C35P

Page 49

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 45

TFT_S1.dat - Data File for TFT640*480-Sync (16 BIT)

TFT_S2.dat - Data File for TFT640*480-Sync (18/24 BIT)

example : (1) HITACHI TX26D60/TX24D55

(2) TOSHIBA LTM09C015A

(3) SHARP LQ10D321

TFT_LP1.dat - Data File For TFT640*480-LP (16 BIT)

TFT_LP2.dat - Data File For TFT640*480-LP (18/24 BIT)

example : (1) Toshiba LTM09c015A)

TFT86_S1.dat - Data File for TFT800*600_sync (16 BIT)

TFT86_S2.dat Data File for TFT800*600_sync (18/24 BIT)

example : (1) NEC NL8060AC26-05

(2) NEC NL8060AC26-04

(3) NEC NL8060BC31-02

EL.dat - Data File for EL640*480

example : (1) PLANAR EL640.480-A

PLASMA.dat - Data File for PLASMA640*480

example : (1) PANASONIC S817

CRT/Flat Panel Mode

All the above BIOS support either CRT only, Flat Panel only or CRT/Flat

Panel simultaneously. To set the mode a Panel Switching Utility is used.

USAGE:

At DOS prompt type >SW508 then Screen will show

1. CRT Only

2. Panel Only

3. CRT/Panel Simutaneous

NEC NL6448AC33-18 wiring

NEC NL6448AC33-18 ICOP-602XV CON1

Pin Pin Name Pin Pin Name

CN1-1 GND 3 GND

Page 50

46 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

CN1-2 CLK 35 SHFCLK

CN1-3 Hsync 38 LP

CN1-4 Vsync 36 FLM

CN1-5 GND 4 CN1-6 R0 27 P18

CN1-7 R1 28 P19

CN1-8 R2 29 P20

CN1-9 R3 30 P21

CN1-10 R4 31 P22

CN1-11 R5 32 P23

CN1-12 GND 33 CN1-13 G0 19 P10

CN1-14 G1 20 P11

CN1-15 G2 21 P12

CN1-16 G3 22 P13

CN1-17 G4 23 P14

CN1-18 G5 24 P15

CN1-19 GND 34 CN1-20 B0 11 P2

CN1-21 B1 12 P3

CN1-22 B2 13 P4

CN1-23 B3 14 P5

CN1-24 B4 15 P6

CN1-25 B5 16 P7

CN1-26 GND 39 CN1-27 ENAB 37 MDE

Page 51

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 47

CN1-28 Vcc 43 Vcc

CN1-29 Vcc 44 Vcc

CN1-30 NC - CN1-31 NC - -

NEC NL6448AC30-10 wiring

NEC NL6448AC30-10 ICOP-602XV CON1

Pin Pin Name Pin Pin Name

CN1-1 CLK 42 SHFCLK

CN1-2 Hsync 38 LP

CN1-3 Vsync 36 FLM

CN1-4 DE 37 MDE

CN1-5 - - P0

CN1-6 B0 10 P1

CN1-7 B1 11 P2

CN1-8 B2 12 P3

CN1-9 B3 13 P4

CN1-10 - 14 P5

CN1-11 - 15 P6

CN1-12 G0 16 P7

CN1-13 G1 17 P8

CN1-14 G2 18 P9

CN1-15 G3 19 P10

CN1-16 - 20 P11

CN1-17 R0 21 P12

CN1-18 R1 22 P13

Page 52

48 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

CN1-19 R2 23 P14

CN1-20 R3 24 P15

CN1-21 - - P16

CN1-22 - - P17

CN1-23 - 27 P18

CN1-24 - 28 P19

CN1-25 - 29 P20

CN1-26 - 30 P21

CN1-27 - 31 P22

CN1-28 - 32 P23

CN1-29 PVcc 5 LCD Vdd

CN1-30 Vcc 43 Vcc

CN1-31 MODE 44 Vcc

CN1-32 GND 3 GND

CN1-33 GND 4 GND

CN1-34 Vdd +12 1 +12

CN1-35 ENABKL 40 ENABKL

CN1-36 GND 39 GND

LJ32H028 wiring

LJ32H028 ICOP-602XV CON1

Pin Pin Name Pin Pin Name

CN1-1 D1 11 P2

CN1-2 D0 12 P3

CN1-3 D3 9 P0

CN1-4 D2 10 P1

Page 53

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 49

CN1-5 CP2 35 SHF_CLK

CN1-6 GND 3,4 GND

CN1-7 CP1 38 LP

CN1-8 GND 33,34 GND

CN1-9 S 36 FLM

CN1-10 - - CN1-11 - - CN1-12 - - CN1-13 +5V 43,44 +5V(Vdd)

CN1-14 - - CN1-15 +12V 1,2 +12V

SHARP LQ10D42 wiring

(640 X 480 TFT Color)

SHARP LQ10D42 ICOP-602XV CON1

Pin Pin Name Pin Pin Name

CN1-1 GND 3,4 GND

CN1-2 CLK 42 SHFCLK

CN1-3 Hsync 38 LP

CN1-4 Vsync 36 FLM

CN1-5 GND 3,4 GND

CN1-6 R0 21 P12

CN1-7 R1 22 P13

CN1-8 R2 23 P14

CN1-9 R3 24 P15

CN1-10 R4 25 P16

CN1-11 R5 26 P17

Page 54

50 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

CN1-12 GND 3,4 GND

CN1-13 G0 15 P6

CN1-14 G1 16 P7

CN1-15 G2 17 P8

CN1-16 G3 18 P9

CN1-17 G4 19 P10

CN1-18 G5 20 P11

CN1-19 GND 3,4 GND

CN1-20 B0 9 P0

CN1-21 B1 10 P1

CN1-22 B2 11 P2

CN1-23 B3 12 P3

CN1-24 B4 13 P4

CN1-25 B5 14 P5

CN1-26 GND 3,4 GND

CN1-27 ENAB 40 M

CN1-28 Vcc 43,44 Vcc +5V

CN1-29 Vcc 43,44 Vcc +5V

CN1-30 R/L - CN1-31 U/D - -

SHARP LQ12S31 wiring

(800 X 600 TFT Color)

SHARP LQ12S31 ICOP-602XV CON1

Pin Pin Name Pin Pin Name

Page 55

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 51

CN1-1 GND 3 GND

CN1-2 CLK 35 SHFCLK

CN1-3 GND 4 GND

CN1-4 Hsync 38 LP

CN1-5 Vsync 36 FLM

CN1-6 GND 8 GND

CN1-7 GND 8 GND

CN1-8 GND 8 GND

CN1-9 R0 27 P18

CN1-10 R1 28 P19

CN1-11 R2 29 P20

CN1-12 GND 8 GND

CN1-13 R3 30 P21

CN1-14 R4 31 P22

CN1-15 R5 32 P23

CN1-16 GND 39 GND

CN1-17 GND 39 GND

CN1-18 GND 39 GND

CN1-19 G0 19 P10

CN1-20 G1 20 P11

CN1-21 G2 21 P12

CN1-22 GND 39

CN1-23 G3 22 P13

CN1-24 G4 23 P14

CN1-25 G5 24 P15

CN1-26 GND 41 GND

CN1-27 GND 41 GND

Page 56

52 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

CN1-28 GND 41 GND

CN1-29 B0 11 P2

CN1-30 B1 12 P3

CN1-31 B2 13 P4

CN1-32 GND 41 GND

CN1-33 B3 14 P5

CN1-34 B4 15 P6

CN1-35 B5 16 P7

CN1-36 GND 41 GND

CN1-37 ENAR 37 M

CN1-38 TST - CN1-39 Vcc 43 +5Vcc

CN1-40 Vcc 44 +5Vcc

CN1-41 TST - -

Page 57

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 53

C h a p t e r A

Pin Assignments

A.1 IDE Interface Connector

Pin Description Pin Description

1

Reset

2

GND

3 Data 7 4 Data 8

5 Data 6 6 Data 9

7

Data 5

8

Data 10

9

Data 4

10

Data 11

11

Data 3

12

Data 12

13 Data 2 14 Data 13

15 Data 1 16 Data 14

17

Data 0

18

Data 16

19

GND

20

N/C

21 N/C 22 GND

23 IOW # 24 GND

25 IOR # 26 GND

27

N/C

28

BALE-Default

29

N/C

30

GND-Default

31 Interrupt 32 IOCS16-Default

33 SA1 34 N/C

35 SA0 36 SA2

37

HDC CS0

38

HDC CSI #

39

HDD Active

40

GND

Page 58

54 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

A.2 VGA/Flat Panel Connectors

CRT/VGA Connector Pin Assignment

Pin Description Pin Description

1 Red 2 GND

3 Green 4 GND

5 Blue 6 GND

7 HSYNC 8 GND

9 VSYNC 10 GND

Flat Panel Connector Pin Assignment

Pin Description Pin Description

1 -12V 2 +12V

3 GND 4 GND

5 PVcc 6 PVcc

7 FPVee 8 GND

9 P0 10 P1

11 P2 12 P3

13 P4 14 P5

15 P6 16 P7

17 P8 18 P9

19 P10 20 P11

21 P12 22 P13

23 P14 24 P15

25 P16 26 P17

27 P18 28 P19

29 P20 30 P21

31 P22 32 P23

33 GND 34 GND

35 SHFCLK 36 FLM

37 M 38 LP

39 GND 40 ENABKL

41 GND 42 ASHFCLK

43 Vcc 44 Vcc

Page 59

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 55

Flat Panel Connector Pin Description

Name Description

P0~P23 Flat panel data output

ENABKL Activity Indicator and Enable Backlight outputs

SHFCLK Shift clock. Pixel clock for flat panel data

M M signal for panel AC drive control

LP Latch pulse. Flat panel equivalent of HSYNC

FLM First line marker. Flat panel equivalent of VSYNC

+12V +12V power from PC power supply

ENAVEE Power sequencing controls for panel LCD bias volt

– SHFCLK the inverter signal of SHFCLK

VDDM 3.3V or 5V selected by JP6

Page 60

56 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

A.3 Floppy Disk Connector

Pin Description Pin Description

1 GND 2 Drive Enable Select

3 GND 4 N/C

5 GND 6 N/C

7 GND 8 Index #

9 GND 10 Drive select 0

11 GND 12 Drive select 1

13 GND 14 Drive select 2

15 GND 16 Motor enable

17 GND 18 Direction #

19 GND 20 STEP #

21 GND 22 Write data #

23 GND 24 Write gate #

25 GND 26 Track 0 #

27 GND 28 Write protect #

29 GND 30 Read data #

31 GND 32 Side 1 select #

33 GND 34 Disk change #

Page 61

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 57

A.4 Parallel Port Interface

Pin Description Pin Description

1 Strobe 2 Data 0

3 Data 1 4 Data 2

5 Data 3 6 Data 4

7 Data 5 8 Data 6

9 Data 7 10 Acknowledge #

11 Busy 12 Paper Empty #

13 Printer Select 14 Auto Form Feed #

15 Error # 16 Initialize #

17 Printer Select In # 18 GND

19 GND 20 GND

21 GND 22 GND

23 GND 24 GND

25 GND 26 NC

Page 62

58 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

A.5 Serial Port Interface

10- Pin D-Type

Description

1 1

Data Carrier Detect (DCD)/5V/12V

6 2

Data Set Ready (DSR)

2 3 Receive Data (RXD)

7 4 Request to Send (RTS)

3 5

Transmit Data (TXD )

8 6

Clear to Send (CTS)

4 7 Data Terminal Ready (DTR)

9 8 Ring Indicator (RI)/5V/12V

5 9 Ground (GND)

X 10

GND

123456789

10

Page 63

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 59

A.6 Keyboard and PS/2 Mouse Connector

Clock

Data

No Connection

GND

Power

1

2

5

4

3

Page 64

60 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

A.7 PC/104 Connectors

64-Pin

PIN No. PIN Name PIN No. PIN Name

1 IOCHCHK * 2 0V

3 SD7 4 RESETDRV

5

SD6

6

+5V

7

SD5

8

IRQ9

9 SD4 10 -5V

11 SD3 12 DRQ2

13

SD2

14

-12V

15

SD1

16

ENDXFR *

17

SD0

18

+12V

19 IOCHRDY 20 (KEY)

21 AEN 22 SMEMW *

23

SA19

24

SMEMR *

25

SA18

26

IOW *

27 SA17 28 IOR *

29 SA16 30 DACK3 *

31 SA15 32 DRQ3

33

SA14

34

DACK1 *

35

SA13

36

DRQ1

37 SA12 38 REFRESH *

39 SA11 40 SYSCLK

41 SA10 42 IRQ7

43

SA9

44

IRQ6

45

SA8

46

IRQ5

47 SA7 48 IRQ4

49 SA6 50 IRQ3

51

SA5

52

DACK2 *

53 SA4 54 TC

55

SA3

56

SALE

57

SA2

58

+5V

59 SA1 60 OSC

61 SA0 62 0V

63

0V

64

0V

40-Pin

Page 65

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 61

PIN No. PIN Name PIN No. PIN Name

1 0V 2 0V

3 MEMCS16 * 4 SBHE *

5

IOCS16 *

6

LA23

7

IRQ10

8

LA22

9 IRQ11 10 LA21

11 IRQ12 12 LA20

13

IRQ15

14

LA19

15

IRQ14

16

LA18

17

DACK0 *

18

LA17

19 DRQ0 20 MEMR *

21 DACK5 * 22 MEMW *

23

DRQ5

24

SD8

25

DACK6 *

26

SD9

27 DRQ6 28 SD10

29 DACK7 * 30 SD11

31 DRQ7 32 SD12

33

+5V

34

SD13

35

MASTER *

36

SD14

37 0V 38 SD15

39 0V 40 (KEY)

Page 66

62 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

A.8 16-bit General Purpose I/O

Pin Description Pin Description

1 GND 2 Vcc

3 GP0 4 GP8

5 GP1 6 GP9

7 GP2 8 GP10

9 GP3 10 GP11

11 GP4 12 GP12

13 GP5 14 GP13

15 GP6 16 GP14

17 GP7 18 GP15

19 Vcc 20 GND

Page 67

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 63

C h a p t e r B

System Assignments

B.1 System I/O Ports

The 5x86 CPU communicates via I/O ports. It has a total of 1KB port

addresses able to be assigned to other devices via I/O expansion

cards.

Address Devices

000-01F

DMA controller #1

020-03F Interrupt controller #1

040-05F Timer

060-06F

Keyboard controller

070-07F

Real time clock, NMI

080-09F

DMA page register

0A0-0BF Interrupt controller #2

0C0-0DF DMA controller #2

0F0

Clear math co-processor busy signal

0F1

Reset math co-processor

0F8-0FF Math processor

10C-10E RAM/ROM disk program port address

120-123 Watch-dog timer operation

1F0-1F8

Fixed disk controller

200-207

Game port

300-31F Prototype card

360-36F Reserved

378-37F Parallel port #1

3F0-3F7

Floppy disk controller

3F8-3FF

Serial port #1(COM1)

2F8-2FF Serial port #2(COM2)

370 Onboard I/O (SMC37C669) Configuration Register

B.2 DMA Channel Assignments

Channel Function

0 Available

1 Available

Page 68

64 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

2

Floppy disk (8-bit transfer)

3

Available

4 Cascade for DMA controller 1

5 Available

6

Available

7

Available

Page 69

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 65

B.3 Interrupt Assignments

The ICOP-602X Series is a fully PC compatible control board. It

consists of 16 ISA interrupt request lines and 4 of the 16 can be

either ISA or PCI. The mapping list of the 16 interrupt request lines is

shown below;

NMI Parity check error

IRQ0 System timer output

IRQ1 Keyboard

IRQ2

Interrupt rerouting from IRQ8 through IRQ15

IRQ3

Serial port #2

IRQ4 Serial port #1

IRQ5 Selectable for Parallel port

IRQ6

Floppy disk controller

IRQ7

Parallel port #1

IRQ8

Real time clock

IRQ9 Reserved

IRQ10 Reserved

IRQ11

Reserved

IRQ12

PS/2 mouse

IRQ13 Math co-processor

IRQ14 Primary IDE channel

IRQ15 Reserved

Page 70

66 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

B.4 1st MB Memory Map

Address Size Description

00000000h-0009FFFFh 640K Host access map to the main memory

000A0000h-000BFFFFh 128K Video frame buffer

000C0000h-000C3FFFh 16K Reserved for Shadow VGA BIOS

000C4000h-000C7FFFh 16K Reserved for Shadow VGA BIOS

000C8000h-000CBFFFh 16K Reserved for Shadow ROM device

000CC000h-000CFFFFh 16K Reserved for Shadow ROM device

000D0000h-000DFFFFh 64K Reserved for Shadow ROM device

Page 71

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 67

C h a p t e r C

POST Error Codes

These settings are more likely to configure a workable computer

when something is wrong. If you cannot boot the computer

successfully, select the Fail-Safe Setup options and try to diagnose

the problem after the computer boots. These settings do not provide

optimal performance.

During the POST routines, which are performed each time the system

is powered on, errors may occur. Non-fatal errors are those which, in

most cases, allow the system to continue the boot process. Error

messages would normally appear on the screen. Fatal errors are

those which will not allow the system to continue the boot procedure.

If a fatal error occurs, you should consult your system manufac-turer

or dealer for possible solutions or repairs. These fatal errors are

usually communicated through a series of audible beeps. All errors

listed, with the exception of 8 beeps, are fatal errors. All errors found

by the BIOS will be forwarded to the I/O port 80h.

Page 72

68 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

C.1 Beep Error Messages

·1 beep DRAM refresh failure. The memory refresh circuitry on the

motherboard is faulty.

2 beeps Parity Circuit failure. A parity error was detected in the base

memory (first 64k Block) of the system.

3 beeps Base 64K RAM failure. A memory failure occurred within the first

64k of memory.

4 beeps System Timer failure. Timer #1 on the system board has failed to

function properly.

5 beeps Processor failure. The CPU on the system board has generated an

error.

6 beeps Keyboard Controller 8042-Gate A20 error. The keyboard controller

(8042) contains the gate A20 switch which allows the computer to operate in

virtual mode. This error message means that the BIOS is not able to switch

the CPU into protected mode.

7 beeps Virtual Mode (processor) Exception error. The CPU on the

motherboard has generated an Interrupt Failure exception interrupt.

8 beeps Display Memory R/W Test failure. The system video adapter is

either missing or Read/Write Error its memory is faulty. This is not a fatal

error.

9 beeps ROM-BIOS Checksum failure. The ROM checksum value does not

match the value encoded in the BIOS. This is good indication that the BIOS

ROMs went bad.

10 beeps CMOS Shutdown Register. The shutdown register for the CMOS

memory Read/Write Error has failed.

11 beeps Cache Error / External Cache Bad. The external cache is faulty.

Page 73

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 69

C.2 Other AMI BIOS POST Codes

·2 short beeps POST failed. This is caused by a failure of one of the

hardware testing procedures.

·1 long & 2 short beeps Video failure. This is caused by one of two possible

hardware faults. 1) Video BIOS ROM failure, checksum error encountered. 2)

The video adapter installed has a horizontal retrace failure.

·1 long & 3 short beeps: Video failure. This is caused by one of three

possible hardware problems. 1) The video DAC has failed. 2) the monitor

detection process has failed. 3) The video RAM has failed.

·1 long beep: POST successful. This indicates that all hardware tests were

completed without encountering errors.

Page 74

70 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

C.3 Troubleshooting

1 beep, 2 beeps, or 3 beeps

try reseating the memory first. If the error still occurs, replace the memory

with known good chips.

4 beeps, 5 beeps, 6 beeps, 7 beeps, or 10 beeps

the system board must be sent in for repair.

8 beeps

indicates a memory error on the video adapter. Replace the video card or

the memory on the video card.

9 beeps

indicates faulty BIOS chip(s). It is not likely that this error can be corrected

by reseating the chips. Consult the motherboard supplier for replacement

part(s).

No beeps, No boot

If no beeps are heard and no display is on the screen, The first thing to

check is the power supply. Connect a LED to the POWER LED connection

on the motherboard. If this LED lights and the drive(s) spin up then the

power supply will usually be good.

Next, inspect the motherboard for loose components. A loose or missing

CPU, BIOS chip, Crystal Oscillator, or Chipset chip will cause the

motherboard not to function. Next, eliminate the possibility of interference by

a bad or improperly set up I/O card by removing all card except the video

adapter. The system should at leastpower up and wait for a drive time-out.

Insert the cards back into the system one at a time until the problem

happens again. When the system does nothing, the problem will be with the

last expansion card that was put in.

If the above suggestions fail to cause any change in the disfunction of the

system, the motherboard must be returned for repair.

Page 75

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 71

C.4 Screen Error Messages

8042 Gate A20 Error :

Gate A20 on the keyboard controller (8042) is not working.

Address Line Short! :

Error in the address decoding circuitry.

Cache Memory Bad, Do Not Enable Cache! :

Cache memory is defective.

CH2 Timer Error :

There is an error in timer 2. Several systems have two timers.

CMOS Battery State Low :

The battery power is getting low. It would be a good idea to replace the

battery.

CMOS Checksum Failure :

After CMOS RAM values are saved, a checksum value is generated for error

checking. The previous value is different from the current value.

CMOS System Options Not Set :

The values stored in CMOS RAM are either corrupt or nonexistent.

CMOS Display Type Mismatch :

The video type in CMOS RAM is not the one detected by the BIOS.

CMOS Memory Size Mismatch :

The physical amount of memory on the motherboard is different than the

amount in CMOS RAM.

CMOS Time and Date Not Set :

Self evident.

Diskette Boot Failure :

The boot disk in floppy drive A: is corrupt (virus?). Is an operating system

present?

Display Switch Not Proper :

A video switch on the motherboard must be set to either color or monochrome.

Page 76

72 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

DMA Error :

Error in the DMA controller.

DMA number 1 Error :

Error in the first DMA channel.

DMA number 2 Error :

Error in the second DMA channel.

FDD Controller Failure :

The BIOS cannot communicate with the floppy disk drive controller.

HDD Controller Failure :

The BIOS cannot communicate with the hard disk drive controller.

INTR number 1 Error :

Interrupt channel 1 failed POST.

INTR number 2 Error :

Interrupt channel 2 failed POST.

Keyboard Error :

There is a timing problem with the keyboard.

KB/Interface Error :

There is an error in the keyboard connector.

Parity Error ???? :

Parity error is in system memory at an unknown address.

Memory Parity Error at xxxxx :

Memory failed at the xxxxx address.

I/O Card Parity Error at xxxxx :

An expansion card failed at the xxxxx address.

DMA Bus Timeout : A device has used the bus signal for more than

allocated time (around 8 microseconds).

Page 77

ICOP Embedede 386SX CPU ISA Half Size SBC User's Manual 73

C.5 POST Card Codes

The following codes are not displayed on the screen. They can only be

viewed on the LED display of a so called POST card. The codes are listed in

the same order as the according functions are executed at PC startup. If you

have access to a POST Card reader, you can watch the system perform

each test by the value that’s displayed. If the system hangs (if there’s a

problem) the last value displayed will give you a good idea where and what

went wrong, or what’s bad on the system board.

CHECK DESCRIPTION OF CHECK

01 Processor register test about to start, and NMI to be disabled.

02 NMI is Disabled. Power on delay starting.

03 Power on delay

complete. Any initialization before keyboard BAT is in progress.

04 Any initialization before keyboard BAT is complete. Reading keyboard

SYS bit, to check soft reset/ power-on.

05 Soft reset/ power-on determined. Going to enable ROM. i.e. disable

shadow RAM/Cache if any.

06 ROM is enabled. Calculating ROM BIOS checksum, and waiting for KB

controller input buffer to be free.

07 ROM BIOS checksum passed, KB controller I/B free. Going to issue the

BAT command to keyboard controller.

08 BAT command to keyboard controller is issued. Going to verify the BAT

command.

09 Keyboard controller BAT result verified. Keyboard command byte to be

written next.

0A Keyboard command byte code is issued. Going to write command byte

data.

0B Keyboard controller command byte is written. Going to issue Pin-23,24

blocking/unblocking command.

0C Pin-23,24 of keyboard controller is blocked/ unblocked. NOP command

of keyboard controller to be issued next.

0D NOP command processing is done. CMOS shutdown register test to be

done next.

0E CMOS shutdown register R/W test passed. Going to calculate CMOS

checksum, and update DIAG byte.

Page 78

74 ICOP Embedded 386SX CPU ISA Half Size SBC User's Manual

0F CMOS checksum calculation is done, DIAG byte written. CMOS init. To