IC+ TC9208M DATA SHEET

TC9208M

Preliminary Dat

8

-

P

o

r

t

10/100/1000 S

m

a

r

t

E

t

h

e

r

n

e

t

S

w

i

t

c

h

a

Sheet

Features

Stand Alone Switch On A Chip

8 Ethernet 10/100/1000 ports

MII/GMII interface for all ports

Trunk group support

s of Service (CoS) sele

Four Cl

each port and/or checked via IP Header and

802.1Q VLAN Tag

Eight port-based VLANs

Maximum throughp

blocking architecture

Em

8K MAC address table

Each

100 full/half duplex and 1000 full duplex mode

Flow-control ability is able to set for both full

and half duplex mode

Broadcast throttling

Port Mirroring

S

MDIO master for PHY configuration / polling

0.18 micron technology

2V and 3.3V dual voltage power supply

Packaged in PBGA 292

27 MHz crystal input only

asse

ut, non hea

bedded SSRAM packet

configurable to

s

port i

rial EEPROM Interface, EEPROM is optional

e

ctab

d-o

buffer/address

10 full/half d

le for

-line

f

table

uplex,

General Description

,

whi

00

c

h

rt 10/100/10

a

cket buf

fer

s for each

.

ted 8 po

be

ds p

a fully integra

08M is

TC92

smart Ethernet switch controller designed for low

cost and high performance solutions. The chip

embeds necessary SSRAM for packet buffering

and MAC address table. It provides MII / GMII

interface for all port

A store-and-forward switching method using a

non-blocking architecture is implemented within

TC9208M to improve the availability and

band

wi

d

t

h. The chip em

s no

it suppo

transmission port.

TC9208M provides evolved CoS with four levels

of priority. The priority can be checked via layer 2

(802.1Q VLAN Tagging) and/or layer 3 (IP Header

TOS bits) packets. Port based priority is also

provided to ensure transmission with precedence

for all packets incoming from selected port(s).

rt

s

rmal and priority queue

This feature allows improved support for

c to im

8K add

an

earnin

nfig

ram

plement flow

ss-loo

re

, and a

g

cellent add

x

nterface

uration i

configuration

s

ng. A virtua

mi

terface in the

s for

control for

rol for full

table

kup

tic agi

a

tom

u

ress sp

compri

ses 40

n

terface, the

l internal

abse

ng,

ace

n

ce

multimedia applications.

s IEEE 802.3 MAC function

cessa

handle

n

chi

r

nfiguration i

c

e to

bed

y logi

r

s

g, self-l

ed and e

spe

pin co

rog

mming in

The chip em

each port and these functions support full and half

duplex modes for both 10 and 100 Mbits/s data

rates and full duplex for 1000 Mbit/s. Each port

includes dedicated receive and transmit FIFOs

with ne

both full and half duplex modes. TC9208M uses

IEEE 802.3x frame based flow cont

duplex and backpressure for half duplex.

08M

TC92

with sea

at very high

coverage. Forwarding rules are implemented

according to IEEE 802.1D specifications. Filtering

capabilities for bad packets and packets with

Reserved Group Address DA are also provided.

Increased interconnection bandwidth can be

achieved by using TC9208M’s trunking

capabilities. Several load-balancing schemes are

provided through pin and EEPROM configuration.

A port mirror feature, which it includes bad frames

optionally, can be used for debugging network

problems.

The pin co

configurations, which are shared with GMII output

pins by latching the configuration data during

reset. An external EEPROM device can also be

used to configure the TC9208M at power-up. With

referen

EEPROM extends the chip’

capability with new features and enables a

jumper-less configuration mode using a parallel

interface for rep

EEPROM mode is also provided to enable the

use of the progra

of external EEPROM. TC9208M can make

effective use by most of its features using only the

pin configuration interface.

TC9208M includes a physical layer configuration /

polling entity, which it is use to configure the phy

functions and to monitor the physical layer

transceiver’s speed, duplex mode, link status and

full duplex flow control ability for each port. The

chip provides four modes for phy configurations,

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

1/53

August 1, 2003

which these modes include auto-negotiation

disable procedure for 10/100 speed modes. The

phy configuration information is stored in

EEPROM setting.

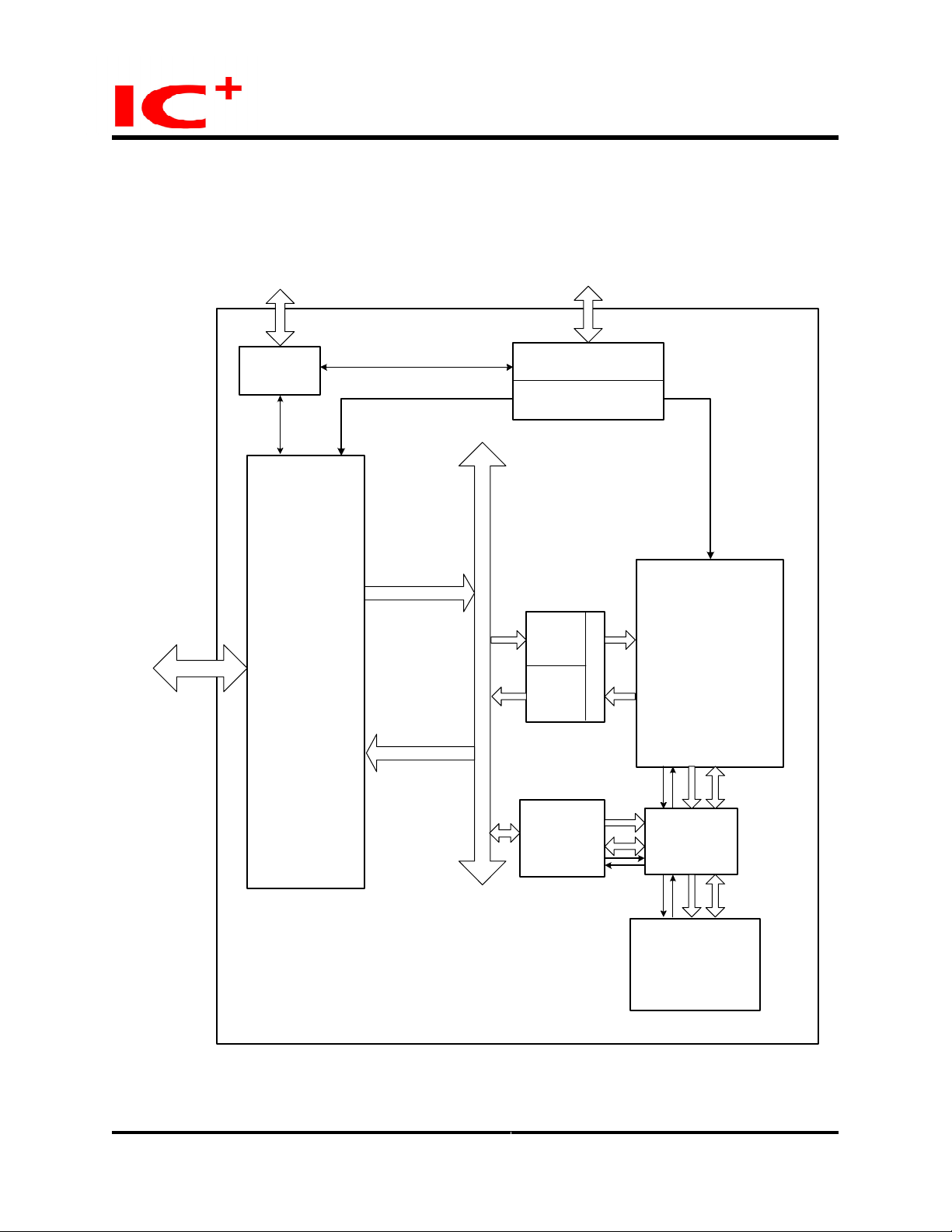

Block Diagram

TC9208M

Preliminary Data Sheet

The chip requires 27 MHz system clock, dual 2V

and 3.3V power supply and is packaged in PBGA

292.

External PHY's

MDIO

interface

8 GM II/MII

RX/TX MAC's

Fro m RX MAC

To TX MA C

EEprom Interface

Configuration

Register

Rx FIFO

Control

Tx FIFO

Address

LoockUp

&

Reso lution

Unit

Queue

Management

Memory

Inte rface

&

Arbiter

Inte rna l

TC9208M

SSRAM

Buffer

Block Diagram

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

2/53

August 1, 2003

TC9208M

Preliminary Data Sheet

Table Of Contents

Features ..............................................................................................................................................................1

General Description ............................................................................................................................................ 1

Block Diagram.....................................................................................................................................................2

Table Of Contents...............................................................................................................................................3

Revision History .................................................................................................................................................. 4

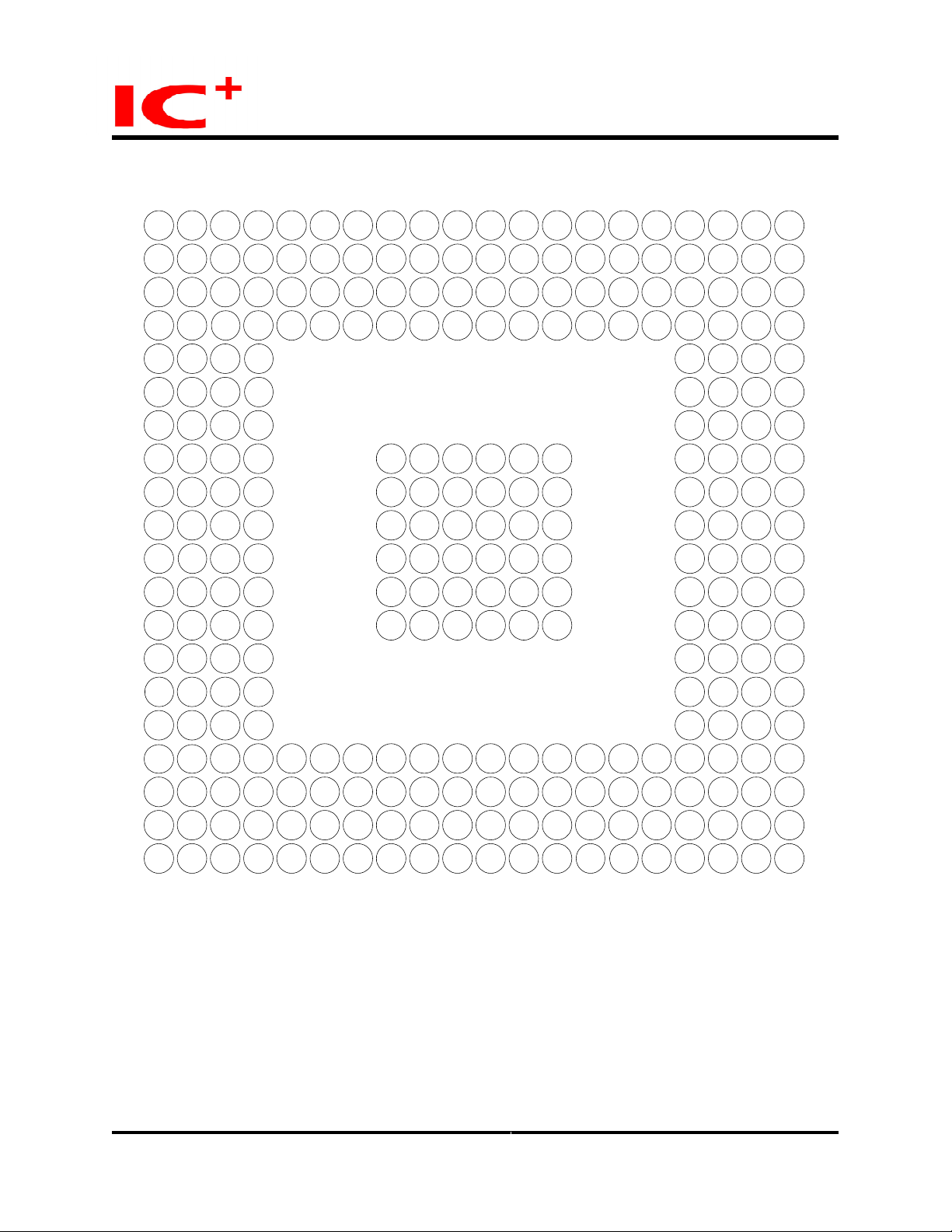

Pins Placement...................................................................................................................................................5

Pin Listing (PBGA 292)...............................................................................................................................6

1

2 Ethernet Media Access Controller ............................................................................................................17

2.1 Receive MAC .....................................................................................................................17

2.2

Transmit MAC ....................................................................................................................18

3 MAC Address Handling.............................................................................................................................19

4 Queue Management.................................................................................................................................19

5

Classes of Service ....................................................................................................................................20

Trunk Configuration...................................................................................................................................22

6

7

Flow Control ..............................................................................................................................................22

8 Broadcast Throttling ..................................................................................................................................24

9 Port Mirroring.............................................................................................................................................24

10 Physical Layer Configuration / Polling......................................................................................................25

11 EEPROM Interface ...................................................................................................................................26

11.1 Reprogramming the EEPROM for reconfiguration ............................................................ 26

11.2 EEPROM Address Map ..................................................................................................... 27

11.3 Register Description........................................................................................................... 29

11.3.1 Validation Register ................................................................................................ 29

11.3.2 Port [X] Configuration Register ............................................................................. 31

11.3.3 Port [X] IFG Configuration Register ...................................................................... 33

11.3.4 Flow Control Register ........................................................................................... 34

11.3.5 Backpressure Time Value Register....................................................................... 35

11.3.6 Flow Control Port Base Address Register ............................................................ 36

11.3.7 Trunk Configuration Register................................................................................ 36

11.3.8 Broadcast Configuration Register......................................................................... 37

11.3.9 IP Priority Mapping Register ................................................................................. 38

11.3.10 VLAN Priority Mapping Register ........................................................................... 39

11.3.11

11.3.12

11.3.13

11.3.14

11.3.15

11.3.16

11.3.17

11.4 Writing / Reading PHY management registers via EEPROM interface............................. 46

11.4.1 Data Write Register............................................................................................... 46

11.4.2

11.4.3 Physical Layer’s Register Address Register ......................................................... 47

11.4.4 IO Status Control Register.................................................................................... 47

11.4.5

12 Timing Requirements................................................................................................................................49

12.1 GMII / MII Receive Timing Requirements.......................................................................... 49

12.2

GMII / MII Transmit Timing................................................................................................. 49

12.3 PHY Management (MDIO) Timing ..................................................................................... 50

12.4 EEPROM Timing................................................................................................................ 51

13

Electrical Specifications ............................................................................................................................52

CoS Bandwidth Register....................................................................................... 40

Reserved Register ................................................................................................ 40

CoS Configuration Register .................................................................................. 41

Port Mirroring Register.......................................................................................... 42

General Configuration Register ............................................................................ 43

Port VLAN Enable Register .................................................................................. 44

VLAN [Y] Register................................................................................................. 45

Physical Layer Device Address Register .............................................................. 46

Data Read Register .............................................................................................. 48

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

3/53

August 1, 2003

TC9208M

Preliminary Data Sheet

13.1

ABSOLUTE MAXIMUM RATINGS..................................................................................... 52

13.2

RECOMMENDED OPERATING CONDITIONS ................................................................ 52

13.3 DC CHARACTERISTICS................................................................................................... 52

Package Detail ..........................................................................................................................................53

14

Revision History

Revision # Change Description

TC9208-DS-R05

TC9208-DS-R06 1. Modify The “Pin Latched” field in Class of Service section and the “Pin Latched”

field in Trunk Configuration.

2. Correct the register map of “Broadcast Configuration Register”

3. Correct the junction temperature limit.

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

4/53

August 1, 2003

Pins Placement

TC9208M

Preliminary Data Sheet

1234

RXD00 CRS0 COL0 TXD76 TXD73 TXD70 RXDV7 RXER7 RXD74 RXD73 RXD70 TXER6 TXD66 TXD63 TXD60 RXER6 RXD65 RXD64 RXD63 RXD62

A

RXD03 RXD02 RXD01 TXD77 TXD74 TXD71 RXD75 RX D72 CRS7 TXEN6 TXD65 TXD62 RXD66 RXD61 RXD60 CRS6

B

RXD06 RXD05 RXD04 TXER7 TXD75 TXD72 RXD77 RXD76 RXD71 COL7 TXD67 TXD64 TXD61 RXDV6 RXD67 COL6 SDA

C

RXDV0 RXD07 RXER0 T XEN7 VSS2.0 VDD3.3 VDD2.0 VSS2.0 VSS3.3 VSS3.3 VSS2.0 V DD2.0 VDD3.3 VSS3.3 VSS3.3 VSS2.0 SCL MDIO MDC

D

TXD00 VSS3.3 TXER5 TXEN5 TXD57 TXD56

E

TXD03 TXD02 TXD01 VSS3.3 VSS2.0 TXD55 TXD54 TXD53

F

TXD06 TXD05 TXD04 VDD3.3 VDD3.3 TXD50 TXD51 TXD52

G

TXER0 TXEN0 TXD07 VDD2.0 VDD2.0 RXER5 RXDV5

H

RXD10 CRS1 COL1 VDD3.3 RXD57 RXD56

J

RXD13 RXD12 RXD11 VSS2.0 VDD3.3 RXD55 RXD54 RXD53

K

RXD17 RXD16 RXD15 RXD14 VSS3.3 RXD52 RXD51 RXD50

L

RXDV1 VDD3.3 VDD3.3 TXEN4 COL5 CRS5

M

RXER1 TXD10 VDD2.0 VDD2.0 TXD46 TXD47 TXER4

N

RXCLK0

GTXCLK0TXCLK0

GTXCLK1RXCLK1

TXCLK1

5

7891011

6

RXCLK7

GTXCLK7

TXCLK7

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

12

13

14 15 16 17 18 19

RXCLK6TXCLK6

GTXCLK6

TXCLK5

GTXCLK5RXCLK5

TESTINT

20

A

B

C

D

E

F

G

H

J

K

L

M

N

TXD11 TXD12 TXD13 VDD3.3 VDD3.3 TXD43 TXD44 TXD45

P

TXD16 TXD15 TXD14 VSS3.3 VSS2.0 TXD40 TXD41 TXD42

R

TXD17 TXER1 TXEN1 VSS2.0 RXDV4

T

SELSCK

GTXCK RESET

U

VDD18PLL

V

CRS2 RXD20 COL2 RXD25 RXDV2 TXD21 TXD24 TXD27 CRS3 RXD31 RXD34 RXD37 TXD30 TXD33 TXD36 TXEN3 RXD40 RXD43

W

RXD21 RXD22 RXD23 RXD26 RXER2 TXD20 TXD25 TXD26 TXER2 RXD32 RXD33 RXDV3 RXER3 TXD34 TXD37 T XER3 RXD41 RXD42

Y

SYSCK VSS3.3 VSS3.3 VDD3.3 VDD2.0 VDD3.3 VSS3.3 VSS3.3 VDD3.3 VDD2.0 VDD3.3 VSS3.3 VSS2.0 RXD45 RXD46 RXD47 RXER4

D

D

E

E

L

L

T

S

C

B

RXD24 RX D27 TXD22 TXD23 T XEN2 COL3 RXD30 RXD35 RXD36 TXD31 TXD32 TXD35 COL4 CRS4 RXD44

N

U

V

O

RXCLK2

TXCLK2

RXCLK3

TXCLK3GTXCLK2

GTXCLK3

RXCLK4

12345678910111213141516171819

Top View

GTXCLK4

TXCLK4

20

P

R

T

U

V

W

Y

Confidential.

5/53

August 1, 2003

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

1 Pin Listing (PBGA 292)

TC9208M

Preliminary Data Sheet

I ⇒ digital input

I

⇒ schmitt trigger digital input

s

⇒ digital input with internal pull down

I

pd

I/O ⇒ digital bi-directional

⇒ digital bi-directional with internal pull up

I/O

pu

O ⇒ digital output

P ⇒ power

G ⇒ ground

I/Opd ⇒ digital bi-directional with internal pull down

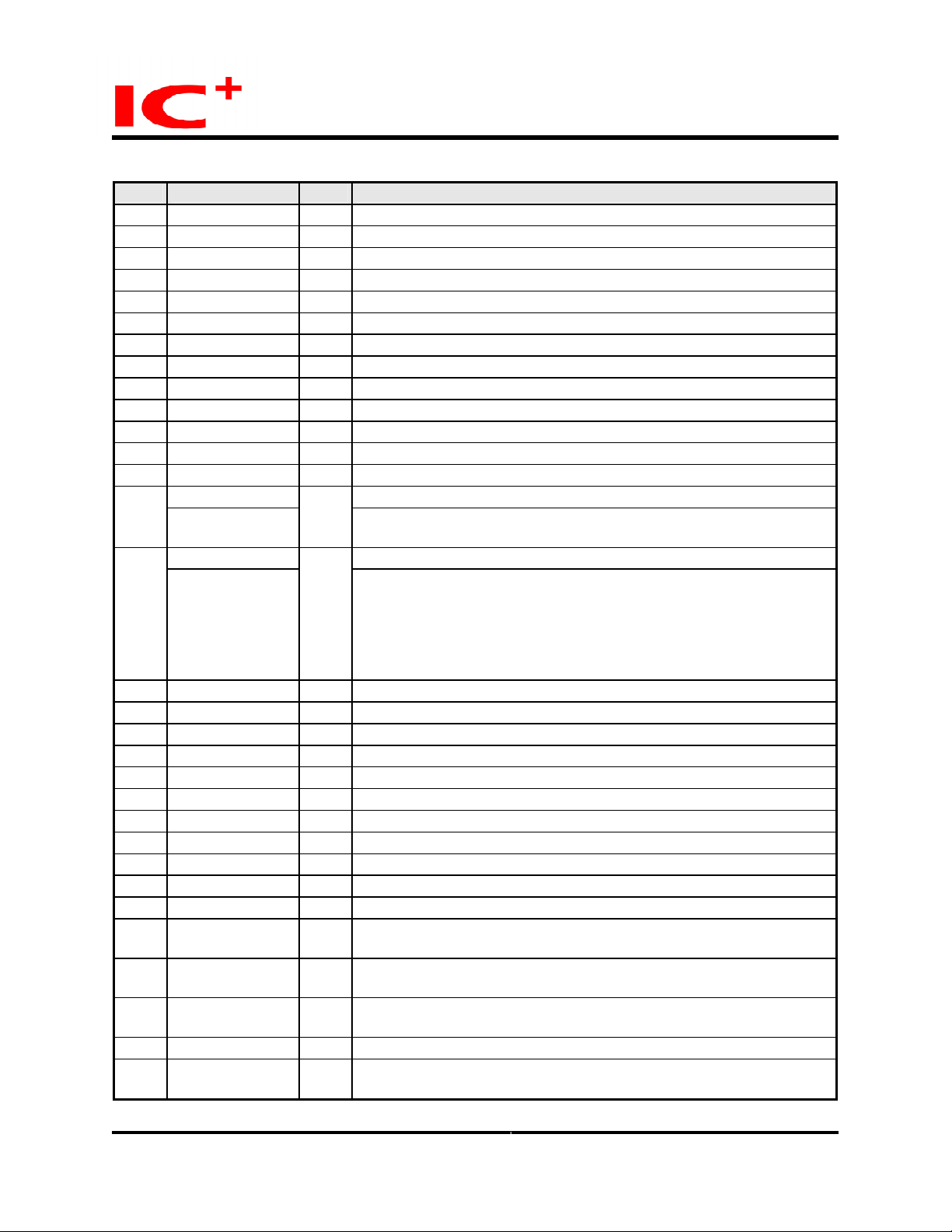

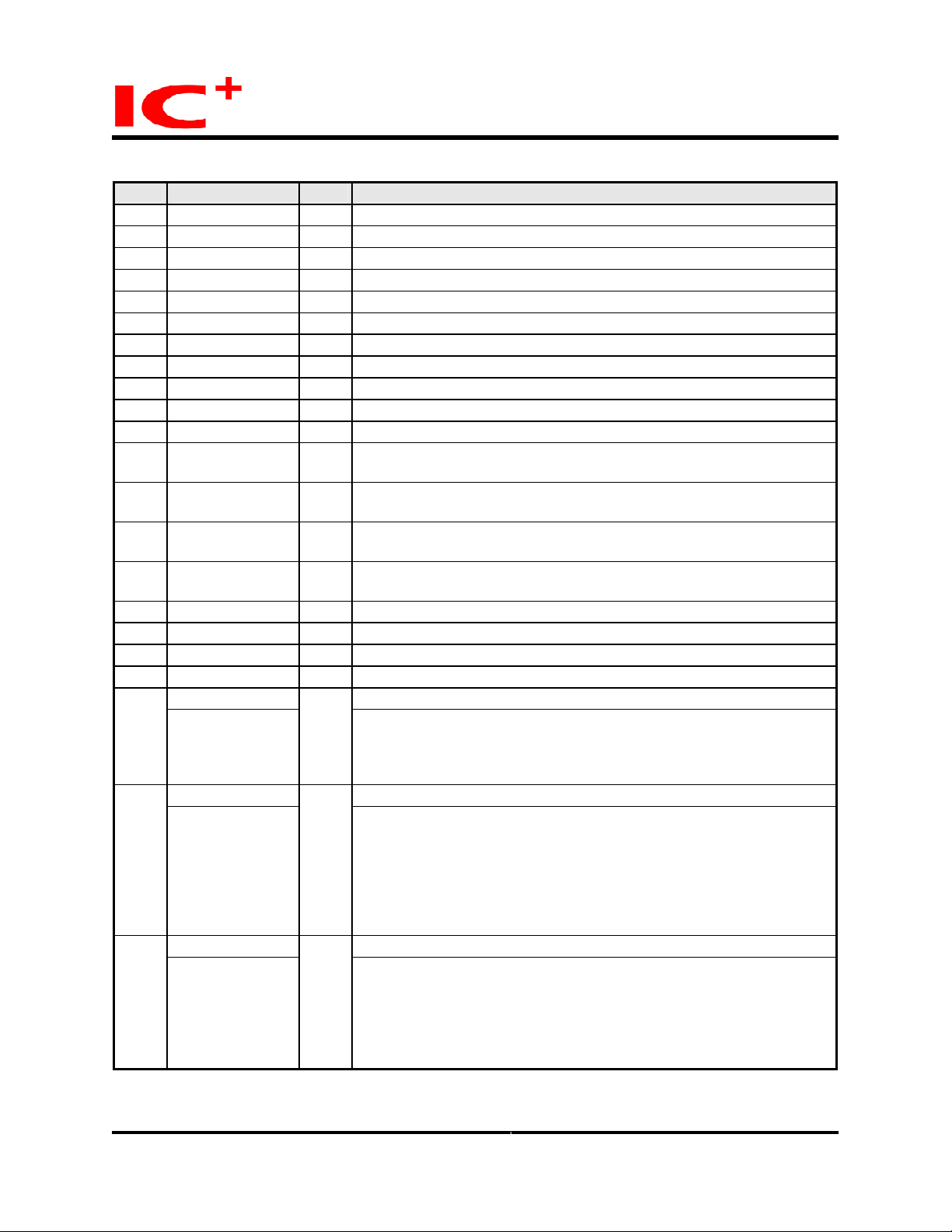

No. Pin label Typ e Description

G4 Vdd 3.3 P Digital +3.3V power supply for I/O

C12 TxData6_7 O GMII transmit data - bits 7

A13 TxData6_6 O GMII transmit data - bits 6

B13 TxData6_5 O GMII transmit data - bits 5

E4 Vss 3.3 G Digital ground for I/O

C13 TxData6_4 O GMII transmit data - bits 4

A14 TxData6_3 O GMII/MII transmit data - bits 3

B14 TxData6_2 O GMII/MII transmit data - bits 2

J4 Vdd 3.3 P Digital +3.3V power supply for I/O

TxData6_1 GMII/MII transmit data - bit 1 C14

PriClass6_1

TxData6_0 GMII/MII transmit data - least significant bit A15

Priclass6_0

I/Opd

Priority class - most significant bit.

I/Opu

Priority class - least significant bit. Sets priority level per port basis.

PriClass[6] - '00' - port 6 low priority

PriClass[6] - '01' - port 6 has normal priority

PriClass[6] - '10' - port 6 has high priority

PriClass[6] - '11' - port 6 has very high priority

PriClass[6] is latched on reset

B12 TxEn6 O GMII/MII transmit enable

C15 GTxClk6 O GMII transmit clock

F4 Vss 3.3 G Digital ground for I/O

A12 TxEr6 TxEr6 I/Opd Transmit Error

B15 TxClk6 I MII transmit clock

B20 Crs6 Is MII carrier sense indication

C18 Col6 Is MII collision indication

A16 RxEr6 Is Receive Error

H4 Vdd 2.0 P Digital +2.0V power supply for core

B16 RxClk6 I MII receive clock

C16 RxDv6 Is GMII/MII data valid

B19 RxData6_0 Is GMII receive data - least significant nibble.

MII receive data

B18 RxData6_1 Is GMII receive data - least significant nibble.

MII receive data

A20 RxData6_2 Is GMII receive data - least significant nibble.

MII receive data

K4 Vss 2.0 G Digital ground for core

A19 RxData6_3 Is GMII receive data - least significant nibble.

MII receive data

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

6/53

August 1, 2003

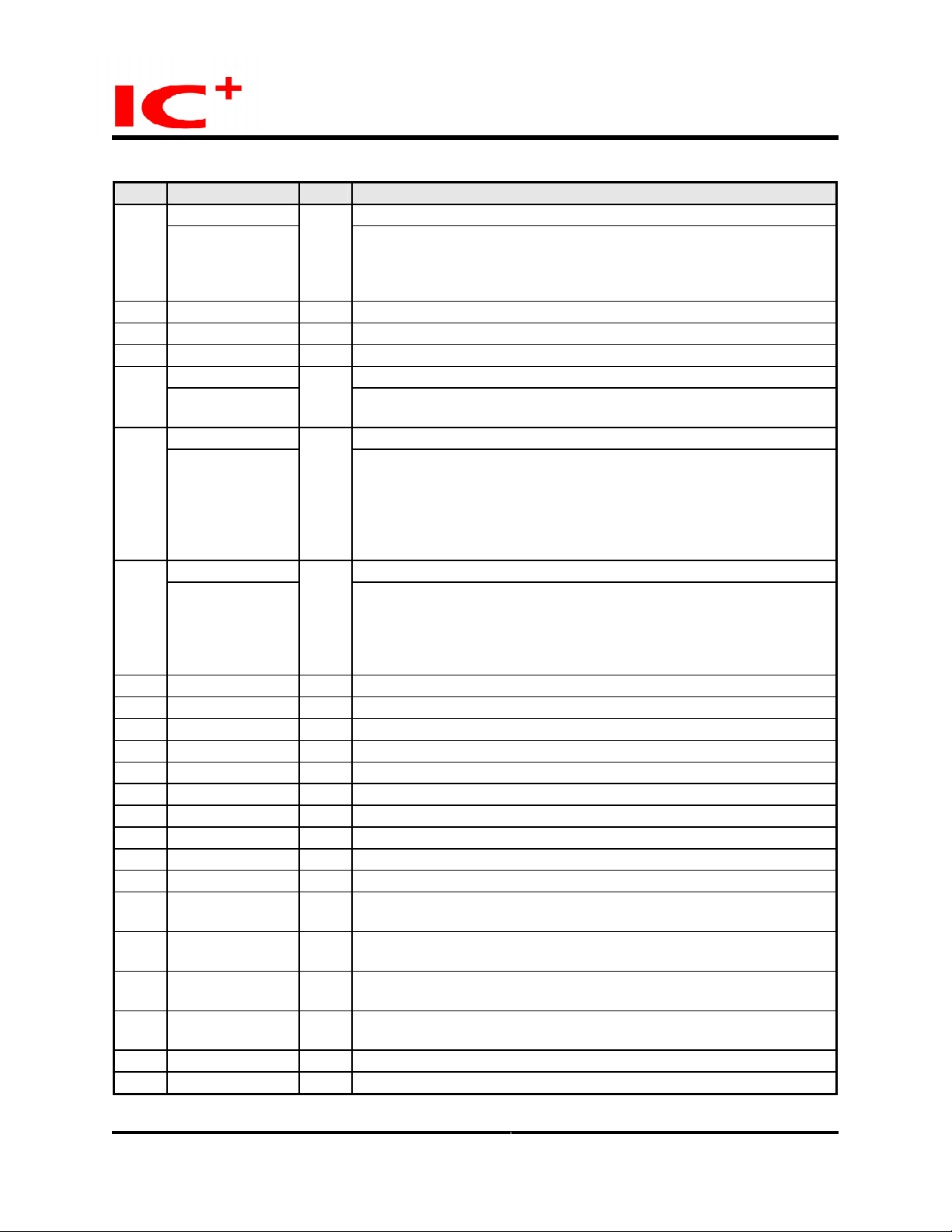

Pin Listing (continued)

No. Pin label Typ e Description

A18 RxData6_4 Is GMII receive data - most significant nibble

A17 RxData6_5 Is GMII receive data - most significant nibble

B17 RxData6_6 Is GMII receive data - most significant nibble

C17 RxData6_7 Is GMII receive data - most significant nibble

M4 Vdd 3.3 P Digital +3.3V power supply for I/O

R4 Vss 3.3 G Digital ground for I/O

B4 TxData7_7 O GMII transmit data – bits 7

A4 TxData7_6 O GMII transmit data – bits 6

C5 TxData7_5 O GMII transmit data – bits 5

N4 Vdd 2.0 P Digital +2.0V power supply for core

B5 TxData7_4 O GMII transmit data – bits 4

A5 TxData7_3 O GMII/MII transmit data - bits 3

C6 TxData7_2 O GMII/MII transmit data - bits 2

T4 Vss 2.0 G Digital ground for core

TxData7_1 GMII/MII transmit data - bit 1 B6

PriClass7_1

TxData7_0 GMII/MII transmit data - least significant bit A6

PriClass7_0

D5 TxEn7 O GMII/MII transmit enable

B7 GTxClk7 O GMII transmit clock

P4 Vdd 3.3 P Digital +3.3V power supply for I/O

C4 TxEr7 I/Opd Transmit Error

C7 TxClk7 I MII transmit clock

B11 Crs7 Is MII carrier sense indication

C11 Col7 Is MII collision indication

A8 RxEr7 Is Receiver Error

U5 Vss 3.3 G Digital ground for I/O

B8 RxClk7 I MII receive clock

A7 RxDv7 Is GMII/MII data valid

A11 RxData7_0 Is GMII receive data - least significant nibble.

C10 RxData7_1 Is GMII receive data - least significant nibble.

B10 RxData7_2 Is GMII receive data - least significant nibble.

U7 Vdd 3.3 P Digital +3.3V power supply for I/O

A10 RxData7_3 Is GMII receive data - least significant nibble.

A9 RxData7_4 Is GMII receive data - most significant nibble

I/Opd

Priority class - most significant bit.

I/Opu

Priority class - least significant bit. Sets priority level per port basis.

PriClass[7] - '00' - port 7 low priority

PriClass[7] - '01' - port 7 has normal priority

PriClass[7] - '10' - port 7 has high priority

PriClass[7] - '11' - port 7 has very high priority

PriClass[7] is latched on reset

MII receive data

MII receive data

MII receive data

MII receive data

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

7/53

August 1, 2003

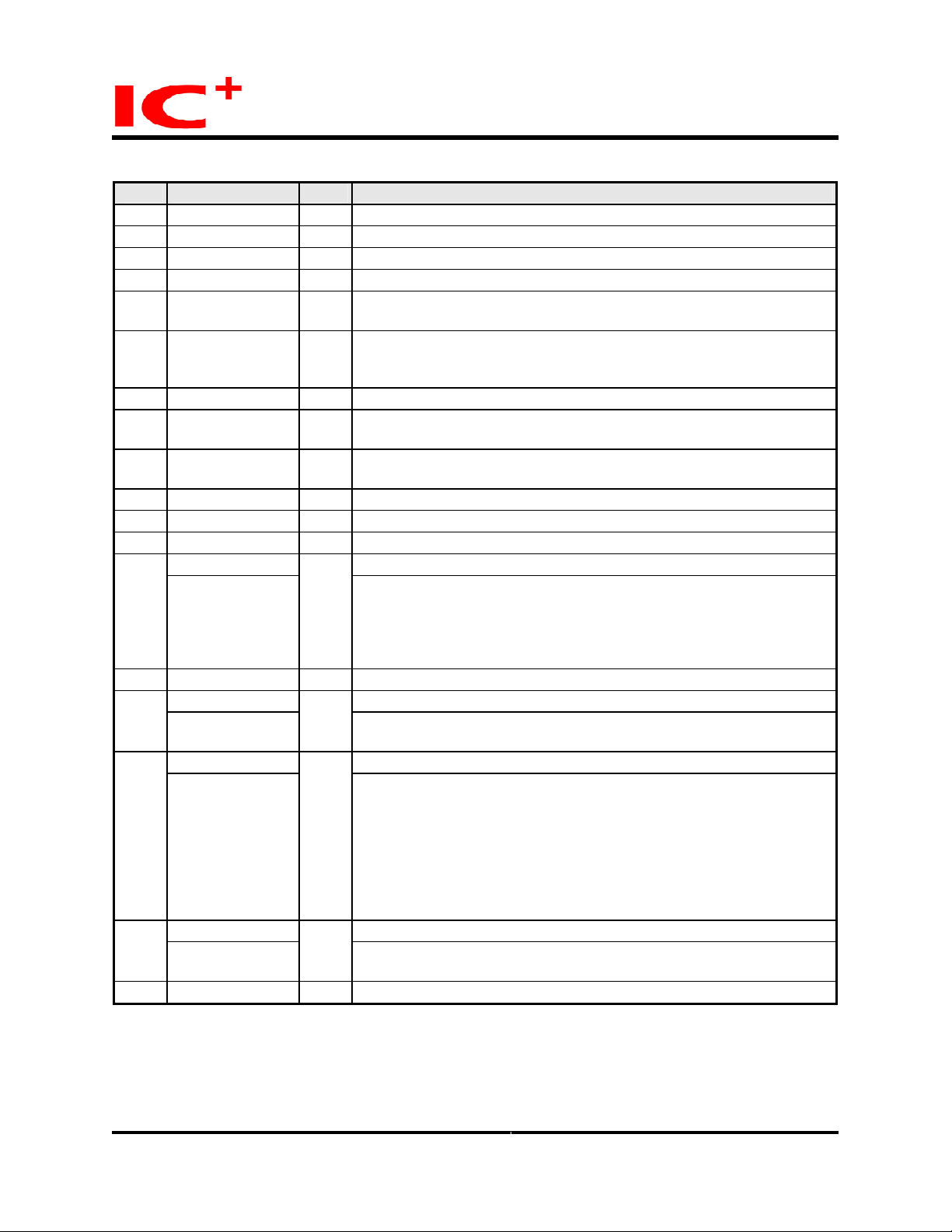

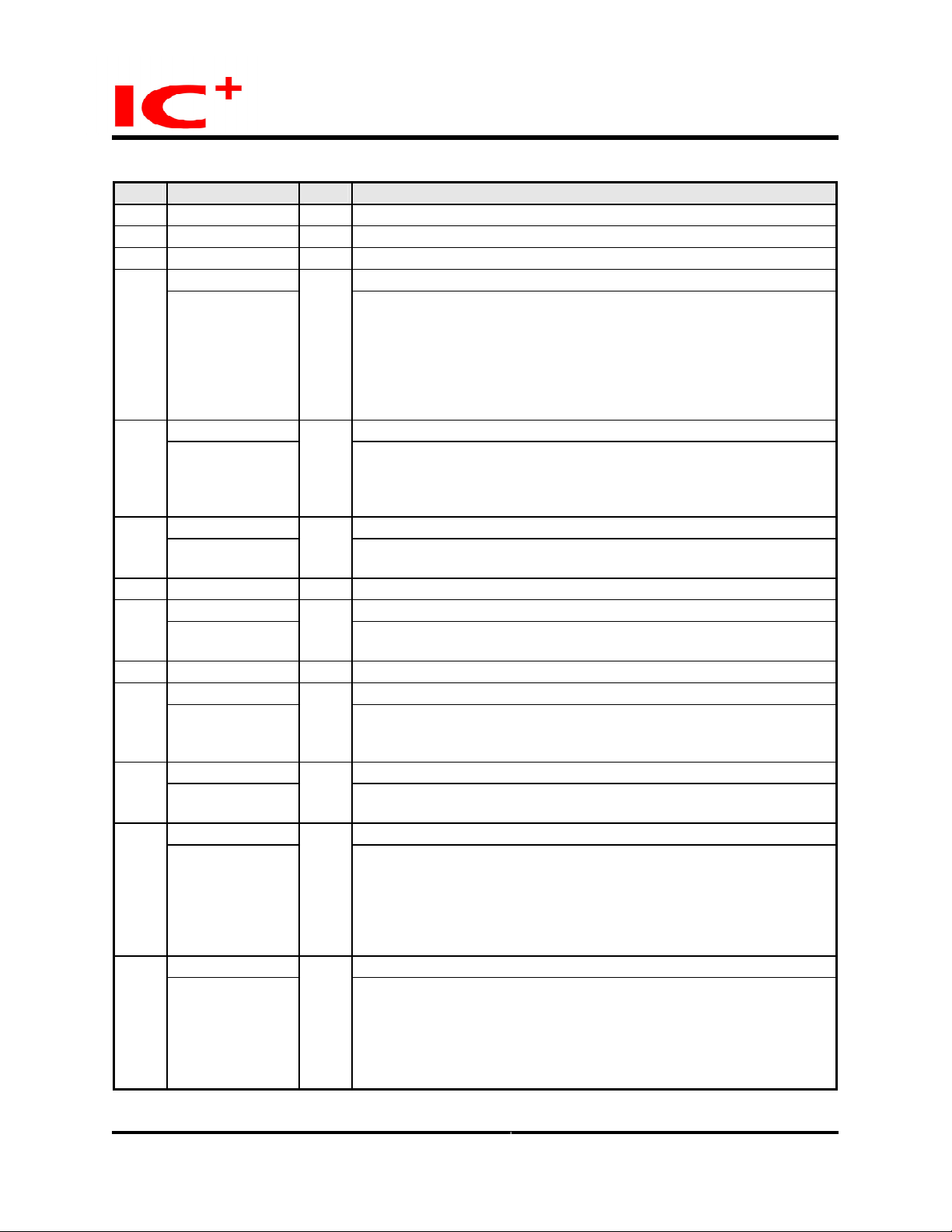

Pin Listing (continued)

No. Pin label Typ e Description

B9 RxData7_5 Is GMII receive data - most significant nibble

C9 RxData7_6 Is GMII receive data - most significant nibble

C8 RxData7_7 Is GMII receive data - most significant nibble

U6 Vss 3.3 G Digital ground for I/O

U9 Vdd 3.3 P Digital +3.3V power supply for I/O

H3 TxData0_7 O GMII transmit data - bits 7

G1 TxData0_6 O GMII transmit data - bits 6

G2 TxData0_5 O GMII transmit data - bits 5

U10 Vss 3.3 G Digital ground for I/O

G3 TxData0_4 O GMII transmit data - bits 4

F1 TxData0_3 O GMII/MII transmit data - bits 3

F2 TxData0_2 O GMII/MII transmit data - bits 2

U12 Vdd 3.3 P Digital +3.3V power supply for I/O

TxData0_1 GMII/MII transmit data - bit 1 F3

PriClass0_1

TxData0_0 GMII/MII transmit data - least significant bit E1

PriClass0_0

H2 TxEn0 O GMII/MII transmit enable

E3 GTxClk0 O GMII transmit clock

U11 Vss 3.3 G Digital ground for I/O

H1 TxEr0 I/Opd Transmit Error

E2 TxClk0 I MII transmit clock

A2 Crs0 Is MII carrier sense indication

A3 Col0 Is MII collision indication

D4 RxEr0 Is Receive Error

U8 Vdd 2.0 P Digital +2.0V power supply for core

D3 RxClk0 I MII receive clock

D1 RxDv0 Is GMII/MII data valid

A1 RxData0_0 Is GMII receive data - least significant nibble.

B3 RxData0_1 Is GMII receive data - least significant nibble.

B2 RxData0_2 Is GMII receive data - least significant nibble.

U16 Vss 2.0 G Digital ground for core

B1 RxData0_3 Is GMII receive data - least significant nibble.

C3 RxData0_4 Is GMII receive data - most significant nibble

I/Opd

Priority class - most significant bit.

I/Opu

Priority class - least significant bit. Sets priority level per port basis.

PriClass[0] - '00' - port 0 has low priority

PriClass[0] - '01' - port 0 has normal priority

PriClass[0] - '10' - port 0 has high priority

PriClass[0] - '11' - port 0 has very high priority

PriClass[0] is latched on reset

MII receive data

MII receive data

MII receive data

MII receive data

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

8/53

August 1, 2003

Pin Listing (continued)

No. Pin label Typ e Description

C2 RxData0_5 Is GMII receive data - most significant nibble

C1 RxData0_6 Is GMII receive data - most significant nibble

D2 RxData0_7 Is GMII receive data - most significant nibble

U14 Vdd 3.3 P Digital +3.3V power supply for I/O

U15 Vss 3.3 G Digital ground for I/O

T1 TxData1_7 O GMII transmit data - bits 7

R1 TxData1_6 O GMII transmit data - bits 6

R2 TxData1_5 O GMII transmit data - bits 5

U13 Vdd 2.0 P Digital +2.0V power supply for core

R3 TxData1_4 O GMII transmit data - bits 4

P3 TxData1_3 O GMII/MII transmit data - bits 3

P2 TxData1_2 O GMII/MII transmit data - bits 2

R17 Vss 2.0 G Digital ground for core

TxData1_1 GMII/MII transmit data - bit 1 P1

Priclass1_1

TxData1_0 GMII/MII transmit data - least significant bit N3

PriClass1_0

T3 TxEn1 O GMII/MII transmit enable

M3 GTxClk1 O GMII transmit clock

P17 Vdd 3.3 P Digital +3.3V power supply for I/O

T2 TxEr1 I/Opd Transmit Error

N2 TxClk1 I MII transmit clock

J2 Crs1 Is MII carrier sense indication

J3 Col1 Is MII collision indication

N1 RxEr1 Is Receive Error

L17 Vss 3.3 G Digital ground for I/O

M2 RxClk1 I MII receive clock

M1 RxDv1 Is GMII/MII data valid

J1 RxData1_0 Is GMII receive data - least significant nibble.

K3 RxData1_1 Is GMII receive data - least significant nibble.

K2 RxData1_2 Is GMII receive data - least significant nibble.

M17 Vdd 3.3 P Digital +3.3V power supply for I/O

K1 RxData1_3 Is GMII receive data - least significant nibble.

I/Opd

Priority class - most significant bit.

PriClass[1] is latched on reset

I/Opu

Priority class - least significant bit. Sets priority level per port basis.

PriClass[1] - '00' - port 1 low priority

PriClass[1] - '01' - port 1 has normal priority

PriClass[1] - '10' - port 1 has high priority

PriClass[1] - '11' - port 1 has very high priority

PriClass[1] is latched on reset

MII receive data

MII receive data

MII receive data

MII receive data

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

9/53

August 1, 2003

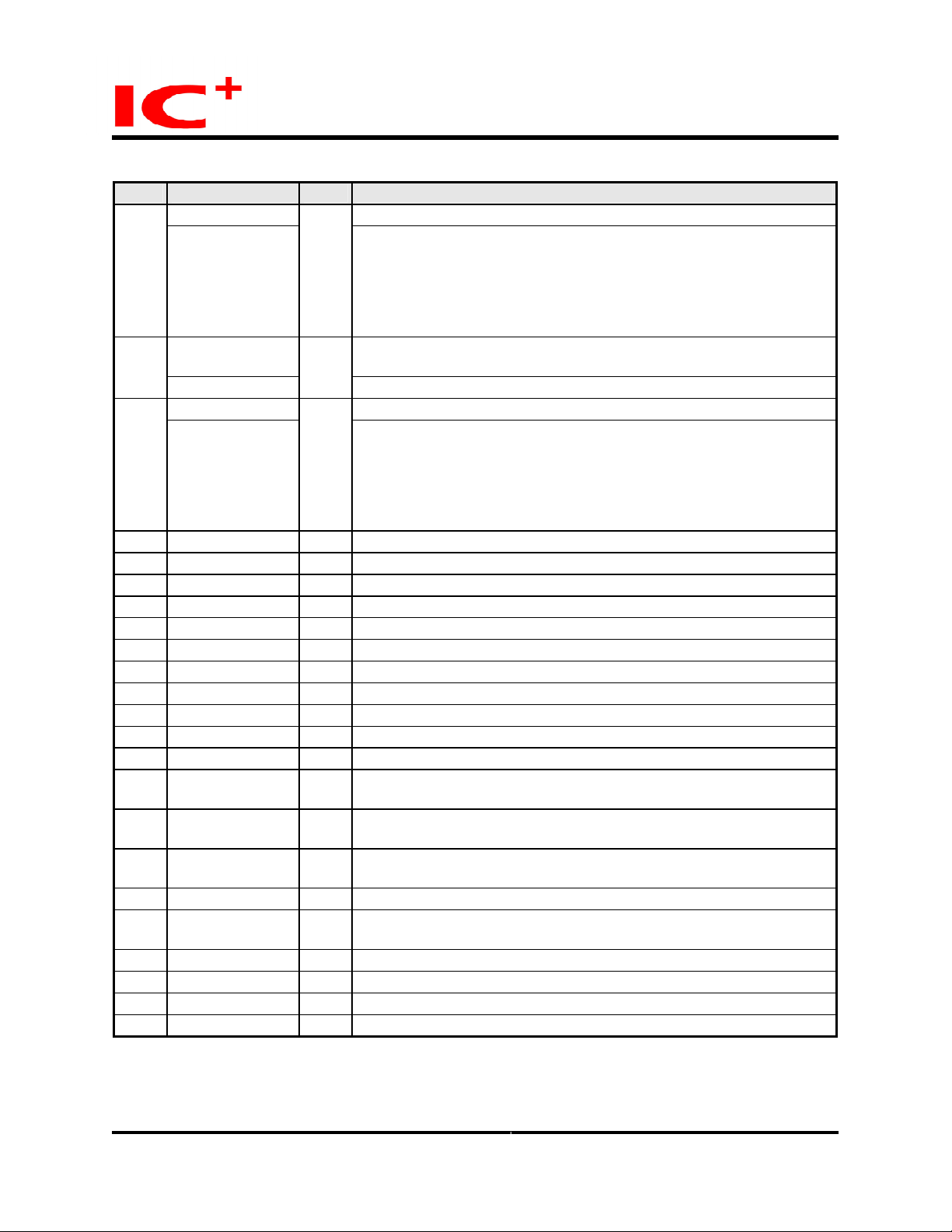

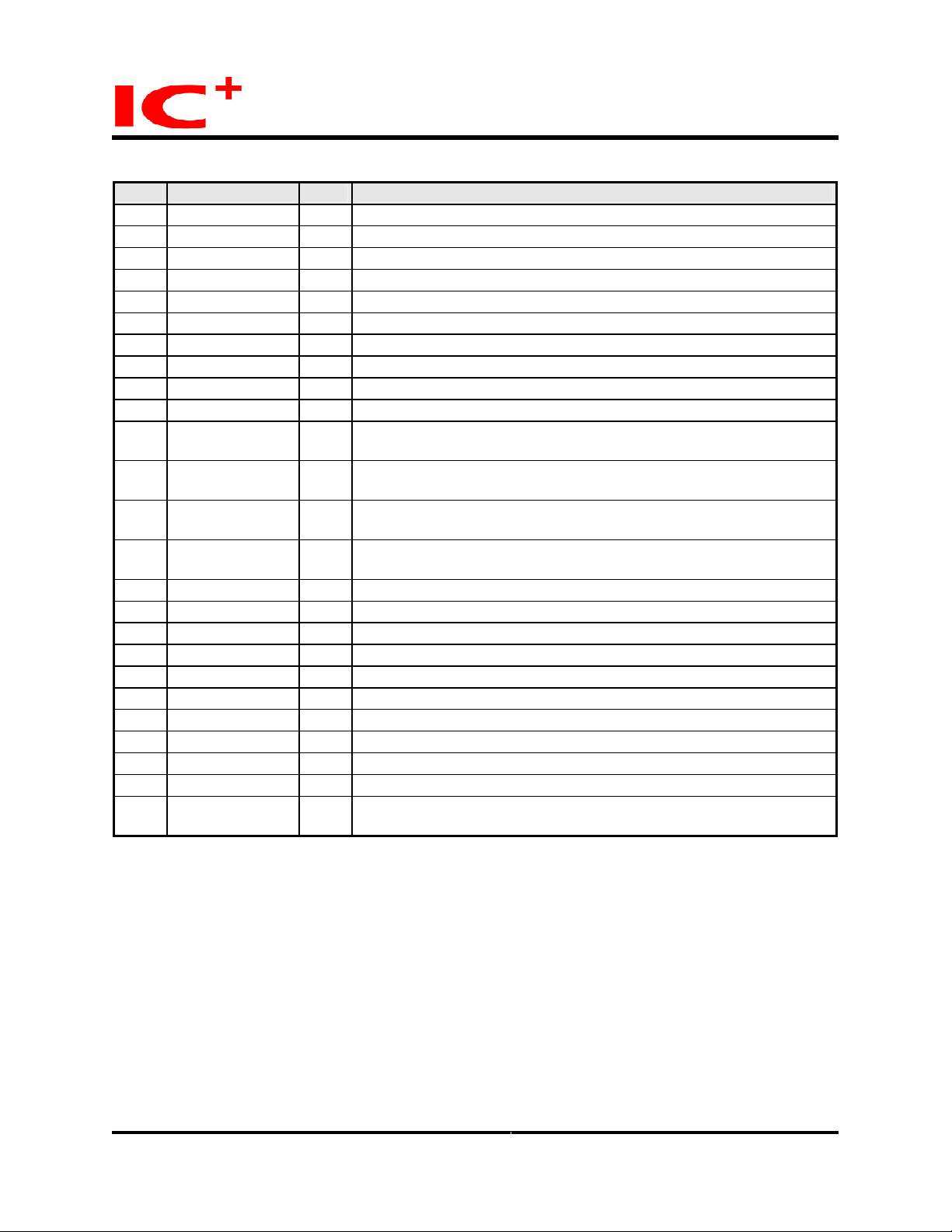

TC9208M

Preliminary Data Sheet

Pin Listing (continued)

No. Pin label Typ e Description

L4 RxData1_4 Is GMII receive data - most significant nibble

L3 RxData1_5 Is GMII receive data - most significant nibble

L2 RxData1_6 Is GMII receive data - most significant nibble

L1 RxData1_7 Is GMII receive data - most significant nibble

U4 selsck Is Selects the source for the system clock.

selsck - ‘1’ - sysck is driven by a 27Mhz external clock.

U1 Gtxck I The 125Mhz reference clock for 1000Mbps operating mode. This

clock is used as a reference clock for the GMII transmission clock for

every port.

V1 Vdd 2.0 P Digital +2.0V power supply for core

V2 BcstLED I/Opd The led can signal filtering of broadcast frames Also the led remains

lit if the POST test fails, which indicates a faulty chip.

V3 OvUnLED O The led is lit whenever a unicast packets overflow condition is reached

and some frames are dropped by the buffer management engine.

D9 Vss 2.0 G Digital ground for core

U3 sysck I The 27Mhz system clock.

U2 reset I

TxData2_7 GMII transmit data - most significant bit W9

TrunkA

Y9 TxData2_6 I/Opd GMII transmit data - bit 6

TxData2_5 GMII transmit data - bit 5 Y8

TnkMod1

TxData2_4 GMII transmit data - bit 4 W8

TnkMod0

TxData2_3 GMII/MII transmit data - bit 3 V8

PriBndw1

N17 Vdd 2.0 P Digital +2.0V power supply for core

General reset.

pus

I/Opd

Trunk channel A configuration pin.

TrunkA - '0' - trunk channel A disabled

TrunkA - '1' - trunk channel A enabled

Trunk channel A is comprised from ports 0 and 1.

TrunkA is latched on reset

I/Opd

Trunk Balance Mode Select

TnkMod(1) is latched on reset

I/Opd

Trunk Balance Mode Select

TnkMod - '00' - Only the source port is used to select the transmission

TnkMod(0) is latched on reset

I/Opd

Priority bandwidth configuration pins.

PriBndw(1)is latched on reset

port inside the trunk.

- '01' -Transmission port is selected using the source address.

- '10' -Transmission port is selected using the source and

destination addresses

- '11'- not used

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

10/53

August 1, 2003

Pin Listing (continued)

No. Pin label Typ e Description

TxData2_2 GMII/MII transmit data - bit 2 V7

PriBndw0

TxData2_1 GMII/MII transmit data - bit 1

W7

PriClass2_1

TxData2_0 GMII/MII transmit data - least significant bit Y7

PriClass0_0

V9 TxEn2 O GMII/MII transmit enable

W6 GTxClk2 O GMII transmit clock

F17 Vss 2.0 G Digital ground for core

Y10 TxEr2 I/Opd Transmit Error

Y6 TxClk2 I MII transmit clock

W1 Crs2 Is MII carrier sense indication

W3 Col2 Is MII collision indication

Y5 RxEr2 Is Receive Error

K17 Vdd 3.3 P Digital +3.3V power supply for I/O

V6 RxClk2 I MII receive clock

W5 RxDv2 Is GMII/MII data valid

W2 RxData2_0 Is GMII receive data - least significant nibble.

Y1 RxData2_1 Is GMII receive data - least significant nibble.

Y2 RxData2_2 Is GMII receive data - least significant nibble.

D16 Vss 3.3 G Digital ground for I/O

Y3 RxData2_3 Is GMII receive data - least significant nibble.

V4 RxData2_4 Is GMII receive data - most significant nibble

W4 RxData2_5 Is GMII receive data - most significant nibble

Y4 RxData2_6 Is GMII receive data - most significant nibble

V5 RxData2_7 Is GMII receive data - most significant nibble

I/Opu

Priority bandwidth configuration pins. These configuration pins allow

the bandwidth percentage assigned to a priority packet queue to be

modified to certain hardwired levels. PriBndw chooses between 4

hardwired spreading percentage schemes among the 4 priority

queues of each port.

PriBndw(0)is latched on reset

I/Opd

PriClass[2] is latched on reset

Priority class - most significant bit.

I/Opu

Priority class - least significant bit. Sets priority level per port basis.

PriClass[2] - '00' - port 2 low priority

PriClass[2] - '01' - port 2 has normal priority

PriClass[2] - '10' - port 2 has high priority

PriClass[2] - '11' - port 2 has very high priority

PriClass[2] is latched on reset

MII receive data

MII receive data

MII receive data

MII receive data

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

11/53

August 1, 2003

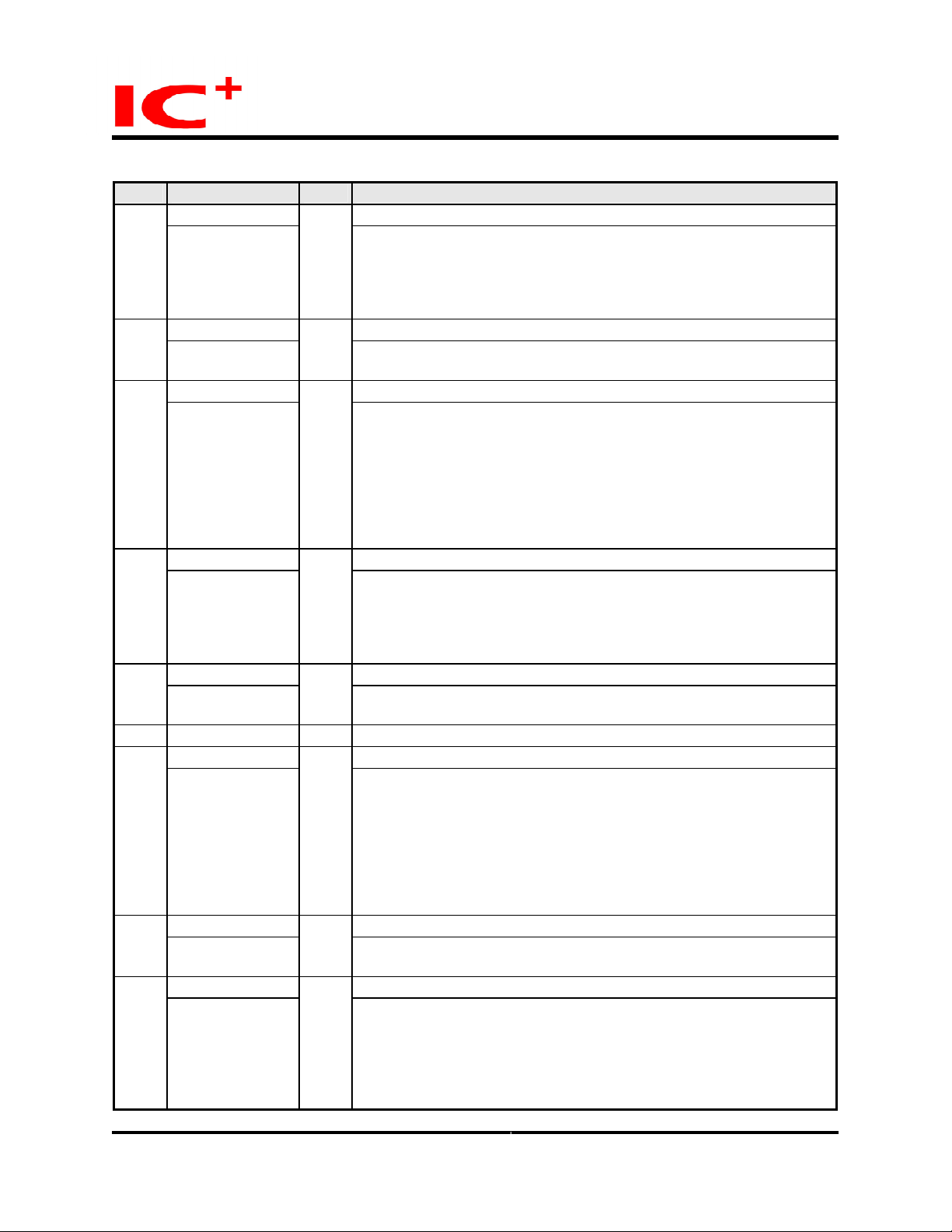

TC9208M

Preliminary Data Sheet

Pin Listing (continued)

No. Pin label Typ e Description

TxData3_7 GMII transmit data - bit 7 Y17

EnIPPr

TxData3_6 GMII transmit data - bit 6 W17

IPTosMap1

TxData3_5 GMII transmit data - bit 5 V17

IPTosMap0

TxData3_4 GMII/MII transmit data - bit 4 Y16

EnVLANPr

TxData3_3 GMII/MII transmit data - bit 3 W16

VLANPrMap1

G17 Vdd 3.3 P Digital +3.3V power supply for I/O

TxData3_2 GMII/MII transmit data - bit 2 V16

VLANPrMap0

TxData3_1 GMII/MII transmit data - bit 1 V15

PriClass3_1

TxData3_0 GMII/MII transmit data - least significant bit W15

PriClass3_0

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

I/Opd

I/Opd

I/Opu

I/Opu

I/Opd

I/Opu

I/Opd

I/Opu

Enables IP prioritization. CoS resolution will consider TOS

Precedence bits from IP Header.

‘1’ – IP priority will be taken into consideration

‘0’ – IP priority will be neglected

EnIPPr is latched on reset

IP type of service mapping - the most significant bit

IPTosMap(1) is latched on reset

IP type of service mapping - the least significant bit. This

configuration chooses between 4 hard-wired mapping schemes for

the associations of IP priority within the received packet and one of

the 4 priority level set by PriClass.

In case the receiving port already has a priority level assigned by

PriClass configuration, or the VLAN prioritization is also active, a

resolution function is used for the final priority class.

IPTosMap(0) is latched on reset.

Enables VLAN prioritization. CoS resolution will consider user priority

bits (TCI field) from 802.1Q VLAN Tag Header.

‘1’ – VLAN priority will be taken into consideration

‘0’ – VLAN priority will be neglected

EnVLANPr is latched on reset

VLAN priority mapping

VLANPrMap(1)is latched on reset.

VLAN priority mapping

This configuration chooses between 4 hard-wired mapping schemes

for the associations of VLAN priority within the received packet and

one of the 4 priority levels set by PriClass.

In case the receiving port already has a priority level assigned by

PriClass configuration, or the IP prioritization is also active, a

resolution function is used for the final priority class.

VLANPrMap(0)is latched on reset.

Priority class - most significant bit.

PriClass[3] is latched on reset

Priority class - least significant bit. Sets priority level per port basis.

PriClass[3] - '00' - port 3 low priority

PriClass[3] - '01' - port 3 has normal priority

PriClass[3] - '10' - port 3 has high priority

PriClass[3] - '11' - port 3 has very high priority

PriClass[3] is latched on reset

12/53

August 1, 2003

Pin Listing (continued)

No. Pin label Typ e Description

W18 TxEn3 O GMII/MII transmit enable

Y14 GTxClk3 O GMII transmit clock

D15 Vss 3.3 G Digital ground for I/O

Y18 TxEr3 I/Opd Transmit Error

W14 TxClk3 I MII transmit clock

W10 Crs3 Is MII carrier sense indication

V10 Col3 Is MII collision indication

Y15 RxEr3 Is Receive Error

H17 Vdd 2.0 P Digital +2.0V power supply for core

V14 RxClk3 I MII receive clock

Y13 RxDv3 Is GMII/MII data valid

V11 RxData3_0 Is GMII receive data - least significant nibble.

MII receive data

W11 RxData3_1 Is GMII receive data - least significant nibble.

MII receive data

Y11 RxData3_2 Is GMII receive data - least significant nibble.

MII receive data

Y12 RxData3_3 Is GMII receive data - least significant nibble.

MII receive data

W12 RxData3_4 Is GMII receive data - most significant nibble

V12 RxData3_5 Is GMII receive data - most significant nibble

V13 RxData3_6 Is GMII receive data - most significant nibble

W13 RxData3_7 Is GMII receive data - most significant nibble

TxData4_7 GMII transmit data - bit 7 N19

BcstThrot

TxData4_6 GMII transmit data - bit 6 N18

OBMTest

TxData4_5 GMII transmit data - bit 5 P20

FcBcstMode

I/Opd

Enables broadcast throttling.

'1' – Enable

'0' – Disable

BcstThrot is latched on reset.

I/Opd

Sets the switch into a special test mode. This test mode require

crossover loopbacks cables to be placed on the pair ports: 1 & 2,2 &

3, 3 & 4, 4 & 5,5 & 6 while ports 0 and 7 will be accessible to the test

machine.

'1' – enabled

'0' – disabled

OBMTest is latched on reset.

I/Opd

Changes the way flow control threshold is handled while in broadcast

situations.

'1' – only the flow control threshold on the broadcast queue is considered

'0' – flow control thresholds associated to each source port originating

the broadcast frames are considered

FCBcstMode is latched on reset.

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

13/53

August 1, 2003

Pin Listing (continued)

No. Pin label Typ e Description

TxData4_4 GMII transmit data - bit 4 P19

FcBcstEn

P18 TxData4_3 I/Opd GMII/MII transmit data - bit 3

D17 Vss 2.0 G Digital ground for core

R20 TxData4_2 I/Opd GMII/MII transmit data - bit 2

TxData4_1 GMII/MII transmit data - bit 1 R19

PriClass4_1

TxData4_0 GMII/MII transmit data - least significant bit R18

PriClass4_0

TxEn4 GMII/MII transmit enable M18

RejRDA

T19 GTxClk4 O GMII transmit clock

D7 Vdd 3.3 P Digital +3.3V power supply for I/O

N20 TxEr4 I/Opd Transmit Error

T20 TxClk4 I MII transmit clock

V19 Crs4 Is MII carrier sense indication

V18 Col4 Is MII collision indication

U20 RxEr4 Is Receive Error

D11 Vss 3.3 G Digital ground for I/O

T17 RxClk4 I MII receive clock

T18 RxDv4 Is GMII/MII data valid

W19 RxData4_0 Is GMII receive data - least significant nibble.

Y19 RxData4_1 Is GMII receive data - least significant nibble.

Y20 RxData4_2 Is GMII receive data - least significant nibble.

W20 RxData4_3 Is GMII receive data - least significant nibble.

V20 RxData4_4 Is GMII receive data - most significant nibble

U17 RxData4_5 Is GMII receive data - most significant nibble

I/Opd

Enables/disables flow control for broadcast packets.

'1' – enabled

'0' – disabled

FcBcstEn is latched on reset.

I/Opd

Priority class - most significant bit.

PriClass[4] is latched on reset.

I/Opu

Priority class - least significant bit. Sets priority level per port basis.

PriClass[4] - '00' - port 4 low priority

PriClass[4] - '01' - port 4 has normal priority

PriClass[4] - '10' - port 4 has high priority

PriClass[4] - '11' - port 4 has very high priority

PriClass[4] is latched on reset

I/Opd

If this pin is set to '1' then all frames with 802.1D Reserved Group

Address or 802.3x Full Duplex PAUSE operation DA will be filtered

out. This setting is provided for testing purposes only and it is

recommended to be set high in normal operation.

RejRDA is latched on reset.

MII receive data

MII receive data

MII receive data

MII receive data

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

14/53

August 1, 2003

Pin Listing (continued)

No. Pin label Typ e Description

U18 RxData4_6 Is GMII receive data - most significant nibble

U19 RxData4_7 Is GMII receive data - most significant nibble

D14 Vdd 3.3 P Digital +3.3V power supply for I/O

TxData5_7 GMII transmit data - bit 7 E19

FullBp

TxData5_6 GMII transmit data - bit 6 E20

CarrBp

TxData5_5 GMII transmit data - bit 5 F18

DisBkPr

F19 TxData5_4 I/Opd GMII transmit data - bit 4

TxData5_3 GMII/MII transmit data - bit 3 F20

FrcFdFc

D10 Vss 3.3 G Digital ground for I/O

TxData5_2 GMII/MII transmit data - bit 2 G20

DisFdFc

TxData5_1 GMII/MII transmit data - bit 1 G19

PriClass5_1

TxData5_0 GMII/MII transmit data - least significant bit G18

PriClass5_0

TxEn5 GMII/MII transmit enable E18

DisBPBk

I/Opd

In normal operation the backpressure process is executed until flow

control condition disappears or until the time limit for backpressure is

reached. This limit is based on EEPROM’s BPTimeValue register.

When this configuration is ‘0’ the backpressure process will be also

limited from exceeding 28 consecutive collisions. The default value

(28) can be changed by EEPROM settings.

FullBp is latched on reset

I/Opu

Enable / disable carrier based backpressure for half -duplex mode.

'1' – Carrier based backpressure

‘0' – Collision based backpressure.

CarrBp is latched on reset

I/Opd

Setting this pin to ‘1’ will disable backpressure procedure for all half

duplex ports. DisBkPr is latched on reset.

I/Opd

Setting this bit to ‘1’ will force flow control execution for 10/100Mbps,

no matter the auto negotiation result. FrcFdFc is latched on reset.

I/Opd

Setting this bit to '1' will disable flow-control for full-duplex mode

(transmission of pause frames).

DisFdFc is latched on reset.

I/Opd

Priority class - most significant bit.

PriClass[5] is latched on reset

I/Opu

Priority class - least significant bit. Sets priority level per port basis.

PriClass[5] - '00' - port 5 low priority

PriClass[5] - '01' - port 5 has normal priority

PriClass[5] - '10' - port 5 has high priority

PriClass[5] - '11' - port 5 has very high priority

PriClass[5] is latched on reset

I/Opd

Enable / disable backoff during backpressure.

'1' – No backoff executed. Another collision will be forced again after

one minimum IFG time following previous collision if carrier

sense is observed.

'0' – The MAC randomly chooses between 0 and 1 slot times of

backoff. DisBkBp is latched on reset.

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

15/53

August 1, 2003

Pin Listing (continued)

No. Pin label Typ e Description

J18 GTxClk5 O GMII transmit clock

D13 Vdd 2.0 P Digital +2.0V power supply for core

E17 TxEr5 I/Opd Transmit Error

H18 TxClk5 I MII transmit clock

M20 Crs5 Is MII carrier sense indication

M19 Col5 Is MII collision indication

H19 RxEr5 Is Receive Error

D12 Vss 2.0 G Digital ground for core

J17 RxClk5 I MII receive clock

H20 RxDv5 Is GMII/MII data valid

L20 RxData5_0 Is GMII receive data - least significant nibble.

MII receive data

L19 RxData5_1 Is GMII receive data - least significant nibble.

MII receive data

L18 RxData5_2 Is GMII receive data - least significant nibble.

MII receive data

K20 RxData5_3 Is GMII receive data - least significant nibble.

MII receive data

K19 RxData5_4 Is GMII receive data - most significant nibble

K18 RxData5_5 Is GMII receive data - most significant nibble

J20 RxData5_6 Is GMII receive data - most significant nibble

J19 RxData5_7 Is GMII receive data - most significant nibble

D8 Vdd 2.0 P Digital +2.0V power supply for core

D20 MDC O MDIO Clock.

D19 MDIO I/Opu MDIO Data.

D6 Vss 2.0 G Digital ground for core

D18 SCL I/Opu EEPROM's serial clock.

C20 SDA I/Opu EEPROM's serial data.

C19 TestInt Ipd TestInt - '0' - switch normal mode(default)

TestInt -'1' - internal memory test mode.

TC9208M

Preliminary Data Sheet

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

16/53

August 1, 2003

TC9208M

Preliminary Data Sheet

2 Ethernet Media Access Controller

The TC9208M’s Ethernet Media Access Controller (MAC) contains IEEE 802.3 MAC functions for 8 ports.

It is able to operate in 10/100/1000 full duplex and 10/100 half duplex modes for all ports. Each port has

its dedicated receive and transmit FIFO with necessary logic to implement flow control for both duplex

modes. The MAC functions are specially designed for high speed and flexible interfacing.

2.1 Receive MAC

When a frame is received from the Ethernet media through the MII interface, it is stored first in a

dedicated receive FIFO. This FIFO acts as a temporary buffer between the Receive MAC section and

switch core interface.

The Receive MAC layer extracts the valid ethernet information by stripping off the preamble sequence

and SFD of the received frame, which the frame was acquired from the PHY layer via either GMII or MII

interface. The Receive MAC then sends packets with valid information to the receive FIFO.

TC9208M determines the validity of each received packet by checking the CRC and packet length. The

bad packets will be dropped either by the MAC or by the queue manager. Oversized packets are

truncated to 1536 bytes and marked as erroneous packets. Undersized packets are removed from the

receive FIFO without being reported to the switch interface. Therefore the FIFO space held by

undersized packets will be removed automatically.

In Full Duplex mode the Receive MAC can identify any received frame as a flow control frame having a

valid CRC. It will load its internal pause counter with the ‘pause quanta’ value extracted from the

incoming frame. The flow control frame will be rejected after the pausing period has been acquired. After

the pausing period has obtained from the flow control frame, the flow control mechanism inside

TC9208M will set a decremental timer in the pause counter according to the value of the pausing period.

A non-zero value sets in the pause counter will issue the Receive MAC to XOFF (Transmit Stop) the

Transmit MAC. The pause counter will decrement the ‘pause quanta’ value after each slot time until it

reaches zero. If the pause quanta value is equal to zero the flow control mechanism will XON (Transmit

Enable) the Transmit MAC.

If a frame transmission is in progress when the PAUSE frame is received, the transmission is allowed to

complete for the current transmitting frame but the transmission for the next frame(s) will hold until the

Receive MAC generates an XON command. The pause time will begin at the end of current transmission

or start immediately if no transmission is in the medium when the PAUSE frame is received. If a pause

command is received while the transmitter is already in pause, the new pause time indicated by the new

Flow Control frame will be loaded into the pause register.

The MAC is also able to reject frames containing IEEE 802.1D Reserved Group Destination Addresses

and frames with Mac Control Type (Type 88-08) if selected through configuration settings.

When the receive FIFO is full and additional data are still incoming from the MAC, then the overrun

condition occurs and the frame is dropped. If the system clock frequency is not lower than the

recommended value this condition will never occur.

Confidential.

Copyright © 2003, IC Plus Corp. TC9208M-DS-R06

17/53

August 1, 2003

Loading...

Loading...