IC+ IP178C, IP178C LF, IP178CH, IP178CH LF DATA SHEET

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

8 Port 10/100 Ethernet Integrated Switch

Features General Description

Support 1k MAC address

512k bits packet buffer memory

Support auto-polarity for 10 Mbps

Support filter/ forward special DA option

Support broadcast storm protection

Auto MDI-MDIX option

Support port security option to lock the first

MAC address

Support one MII/RMII port, which works at 100

Mbps full duplex for router application

Support port base VLAN & tag VLAN

Support CoS

Support SMART MAC function

Support spanning tree protocol

Support max forwarding packet length 1552/

1536 bytes option

Support 8-level bandwidth control

Support SCA

Support two fiber ports with far end fault

function for IP178CH only

Built in linear regulator control circuit

Support Lead Free package (Please refer to

the Order Information)

Note – some features need CPU support, please

refer to the detail description inside this data sheet

IP178C/IP178CH integrates a 9-port switch

controller, SSRAM, and 8 10/100 Ethernet

transceivers. Each of the transceivers complies

with the IEEE802.3, IEEE802.3u, and IEEE802.3x

specifications. The transceivers are designed in

DSP approach in 0.18um technology; they have

high noise immunity and robust performance.

IP178C/IP178CH operates in store and forward

mode. It supports flow control, auto MDI/MDI-X,

CoS, port base VLAN, bandwidth control, DiffServ,

SMART MAC and LED functions, etc. Each port

can be configured as auto-negotiation or forced 10

Mbps/100 Mbps, full/half duplex mode. Using an

EEPROM or pull up/down resistors on specific

pins can configure the desired options.

Besides an 8-port switch application,

IP178C/IP178CH supports one MII/RMII ports for

router application, which supports 7 LAN port s and

one WAN port. The external MAC can monitor or

configure IP178C/IP178CH by accessing MII

registers through SMI.

MII/RMII port also can be configured to be MAC

mode. It is used to interface an external PHY to

work as an 8+1 switch.

IP178CH supports two fiber ports with far end fault

function.

1/93

June 21, 2007

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

Table Of Contents

Features ...................................................................................................................................................1

General Description..................................................................................................................................1

Table Of Content s.....................................................................................................................................2

Revision History........................................................................................................................................3

Pin diagram (IP178C).............................................................................................................................10

1 Pin description.................................................................................................................................15

Pin description (continued).....................................................................................................................16

Pin description (continued).....................................................................................................................18

Pin description (continued).....................................................................................................................19

Pin description (continued).....................................................................................................................20

Pin description (continued).....................................................................................................................21

Pin description (continued).....................................................................................................................22

Pin description (continued).....................................................................................................................24

Pin description (continued).....................................................................................................................25

Pin description (continued).....................................................................................................................26

Pin description (continued).....................................................................................................................27

Pin description (continued).....................................................................................................................28

2 Functional Description.....................................................................................................................29

2.1 Flow control.........................................................................................................................32

2.2 Broadcast storm protection.................................................................................................33

2.3 Port locking.........................................................................................................................34

2.4 Port base VLAN..................................................................................................................35

2.5 Tag VLAN/ Tag and un-tag function....................................................................................36

2.6 Tag VLAN............................................................................................................................36

2.7 Tag VLAN in router application ...........................................................................................37

2.8 Smart MAC .........................................................................................................................38

2.9 CoS.....................................................................................................................................42

2.9.1 Port base priority....................................................................................................42

2.9.2 Frame base priority................................................................................................42

2.10 Spanning tree......................................................................................................................44

2.11 Static MAC address table....................................................................................................46

2.12 Serial management interface..............................................................................................47

2.13 SCA.....................................................................................................................................48

2.14 Bandwidth control ...............................................................................................................48

2.15 Register descriptions ..........................................................................................................49

3 Electrical Characteristics.................................................................................................................86

3.1 Absolute Maximum Rating..................................................................................................86

3.2 DC Characteristic................................................................................................................86

3.3 AC Timing ...........................................................................................................................87

3.3.1 PHY Mode MII Timing............................................................................................87

3.3.2 MAC Mode MII Timing...........................................................................................88

3.3.3 RMII Timing............................................................................................................89

3.3.4 SMI Timing.............................................................................................................90

3.3.5 EEPROM Timing....................................................................................................91

3.4 Thermal Data......................................................................................................................91

4 Order information ............................................................................................................................92

5 Package Detail................................................................................................................................93

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

2/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

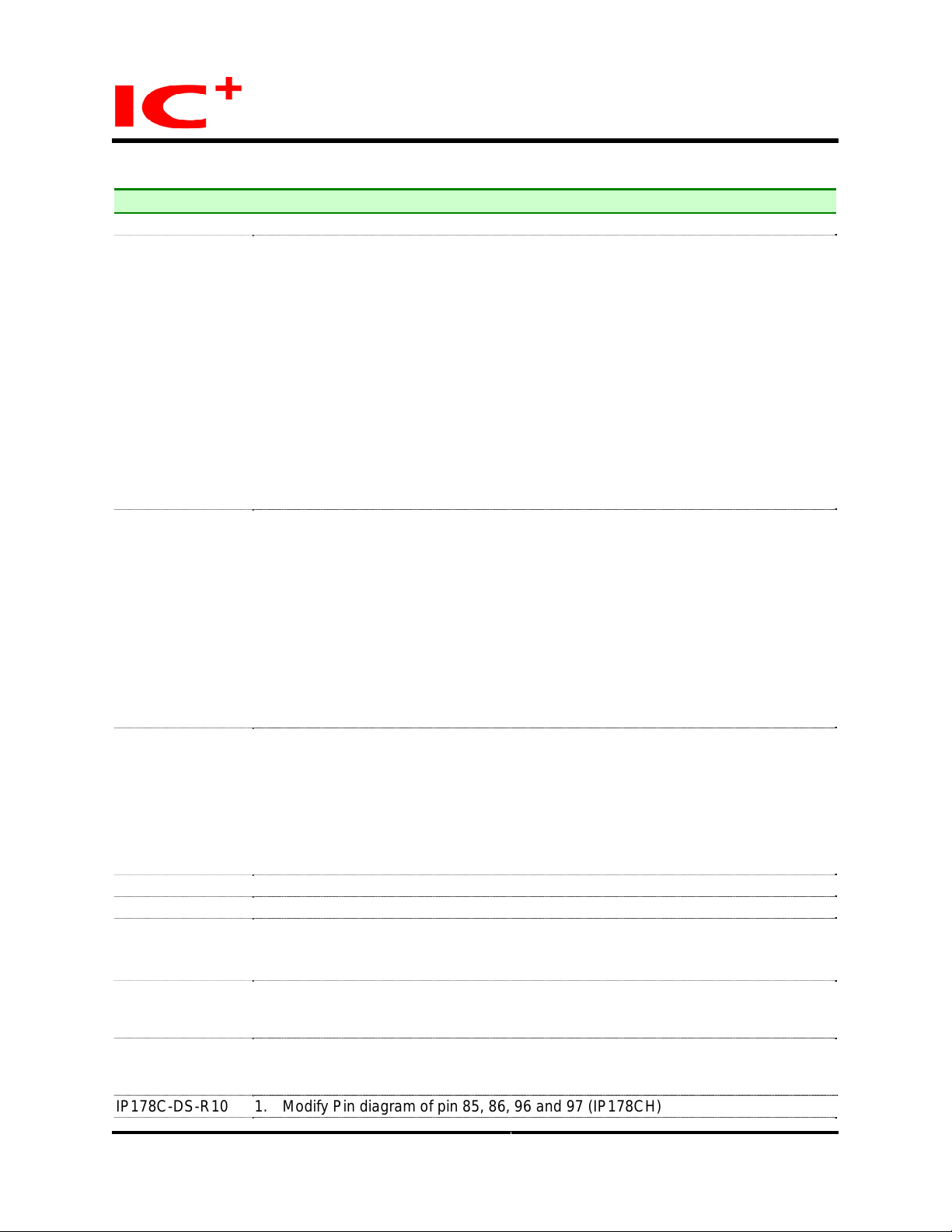

Revision History

Revision # Change Description

IP178C-DS-R01 Initial release.

IP178C-DS-R02 1. Modify Pin diagram in page 9, pin_89 from HASH_MODE[1]/LINK_LED7 to

MLT3_DET/LINK_LED7,pin 84 from LOW_10M_DIS to SCA_DIS, pin_36 from

SCA to NC, VCTRL to REG_OUT

2. Replace VCTRL with REG_OUT

3. Modify HASH_MODE [1] to MLT3_DET in page 17, 54 & 55

4. Modify pin 84 from LOW_10M_DIS to SCA_DIS, pin_36 from SCA to NC

5. Change BF_STM_THR_SEL [1:0] from 01: 128 frames to 126 frames in page 74

6. Modify EXT MII Pin description in page 21, 22, 23

7. "100M" change to "100 Mbps" and "10M" change to "10 Mbps".

8. Modify PHY mode for only support one MIICLK on page 25

9. Add in Thermal Data on page 85

10. Add in power consumption on page 80

11. P.54 PHY30.1[12] Default value=0, P.56 PHY30.2[7] Default value=0, P.56

PHY30.2[0] 為 FORCE_MODE -> BI_COLOR

12. 1.8V change 1.95V

IP178C-DS-R03 1. Modify FILTER_DA, 01-80-c2-00-00-00 to 01-80-c2-00-00-02 on page 19

2. Modify VLAN_ON function when Pin 53EXTMII_EN=1 on page 18

3. Modify long packet enable function description on page 55

4. Modify Backpressure type selection on page 54

5. Modify RESETB CKT on page 14

6. Modify HASH_MODE [0] to LDPS_DIS on page 17, 54

7. Modify Pin type description on page 13

8. Modify Pin 84 from SCA_DIS to LOW_10M_DIS or SCA_DIS on page 14

9. Modify Pin 73 from LINK_Q to SEL_SCA on p age 18

10. Modify Pin diagram on page 9, pin_87 from HASH_MODE [0] to LDPS_DIS,pin

84 from SCA_DIS to LOW_10M_DIS or SCA_DIS, pin_73 from LINK_Q to

SEL_SCA

IP178C-DS-R04 1. Modify broadcast storm protection function on page 18, page 30, page 75

2. Add BW control value setting on page 81

3. Add BW control description on page 45

4. Rearrange Index

5. Add special_add_forward description on page 81

6. Add “The function is valid only if pin 53 EXTMII_EN is pulled low.” To pin 75, 76,

77, 78, 85, 86, 87

7. Add Note on page 1 for CPU support

IP178C-DS-R05 1. Add the order information for lead free package

IP178C-DS-R06 1. Add IP178C.RX_DV connect to MAC.RX_DV and MAC.CRS on page 27

IP178C-DS-R07 1. All ports unlink on page 84 for VCC

2. Modify VCC min form 1.85V to 1.80V on page 84

3. Modify regulator description on page 1 & 13

IP178C-DS-R08 1. Revise the pin description.

2. Modify Pin diagram of pin 85, 86, 96 and 97.

3. Modify application diagram on page 10.

IP178C-DS-R09 1. Add FXSD7 on page 26 FXSD6 on page 15

2. Add

3.

fiber application for order information on page 90

Add IP178CH Pin diagram on page 10

IP178C-DS-R10 1. Modify Pin diagram of pin 85, 86, 96 and 97 (IP178CH)

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

3/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

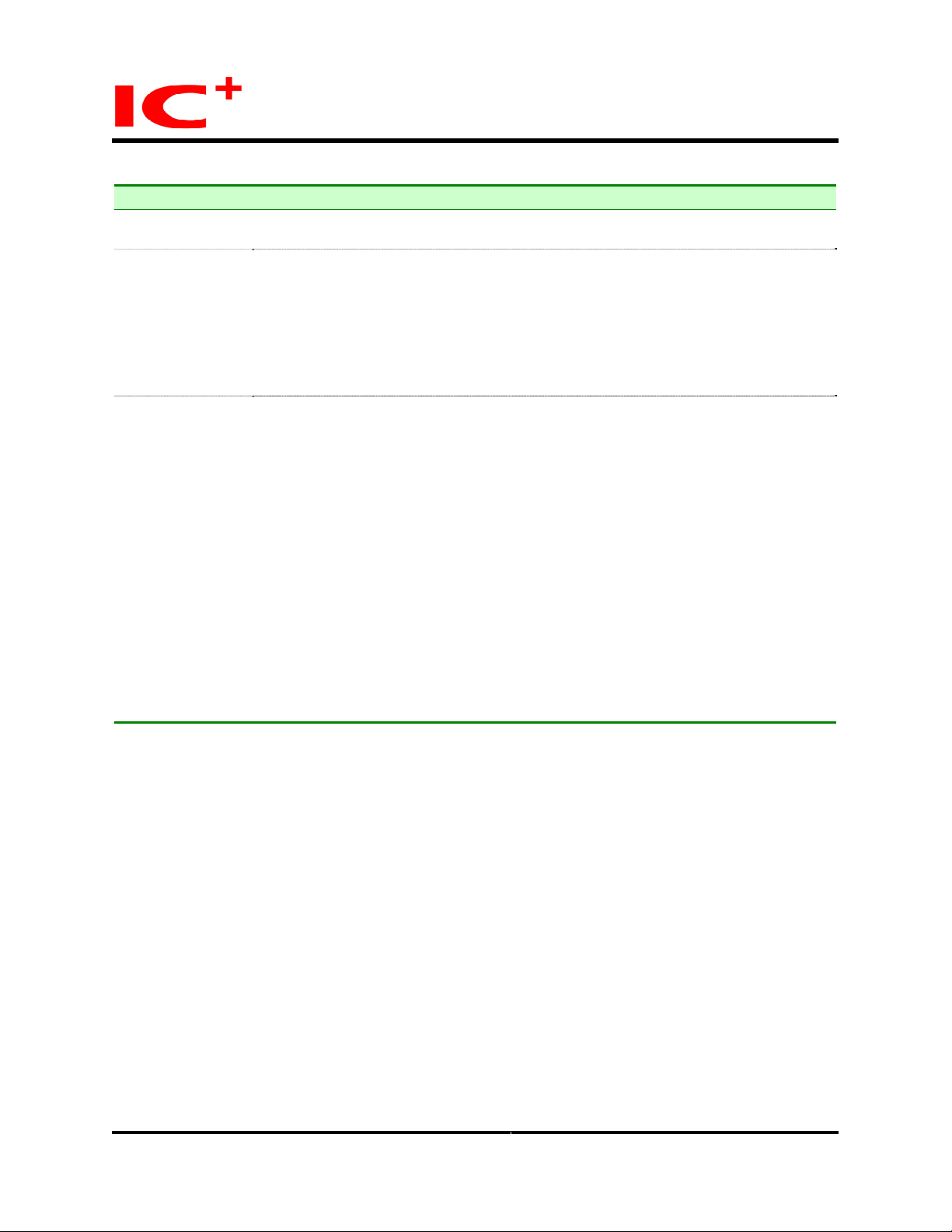

Revision History

Revision # Change Description

2. Modify Pin description on page 21 for (IP178CH)

3. Modify initial setting on page 5 for (IP178CH)

IP178Cx-DS-R11 1. Modify SCA Table on page 48

2. Replace with new SCA register table

3. Replace IP178C with IP178C/IP178CH

4. Modify the difference of the definition in pin 36 and 57 between IP178B and

IP178C/IP178CH on page 5 and 6

5. Modify application blocks on page 12, 13 and 14

6. Add “IP178CH support two fiber “ to feature list and general description on page

1

IP178Cx-DS-R12 1. Modify from “register 0” to “register 5” on page 74

2. Modify flow control description on page 32

3. Modify IPL/IPH description on page 15

4. Add 2.5V VCC_O DC description on page 86

5. Modify Bi-color LED definition on page 19

6. Replace PHY0 register 1.1 IP113A to IP178C/IP178CH & add RO/LH on page

51

7. Modify OP0 OP1 to FX enable/half on page 60

8. Add FXSDx DC on page 86

9. Modify LED Flash behavior on page 31

10. Add X1 VIL & X1 VIH on page 86

11. Add 512k bits packet buffer memory on page 1

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

4/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

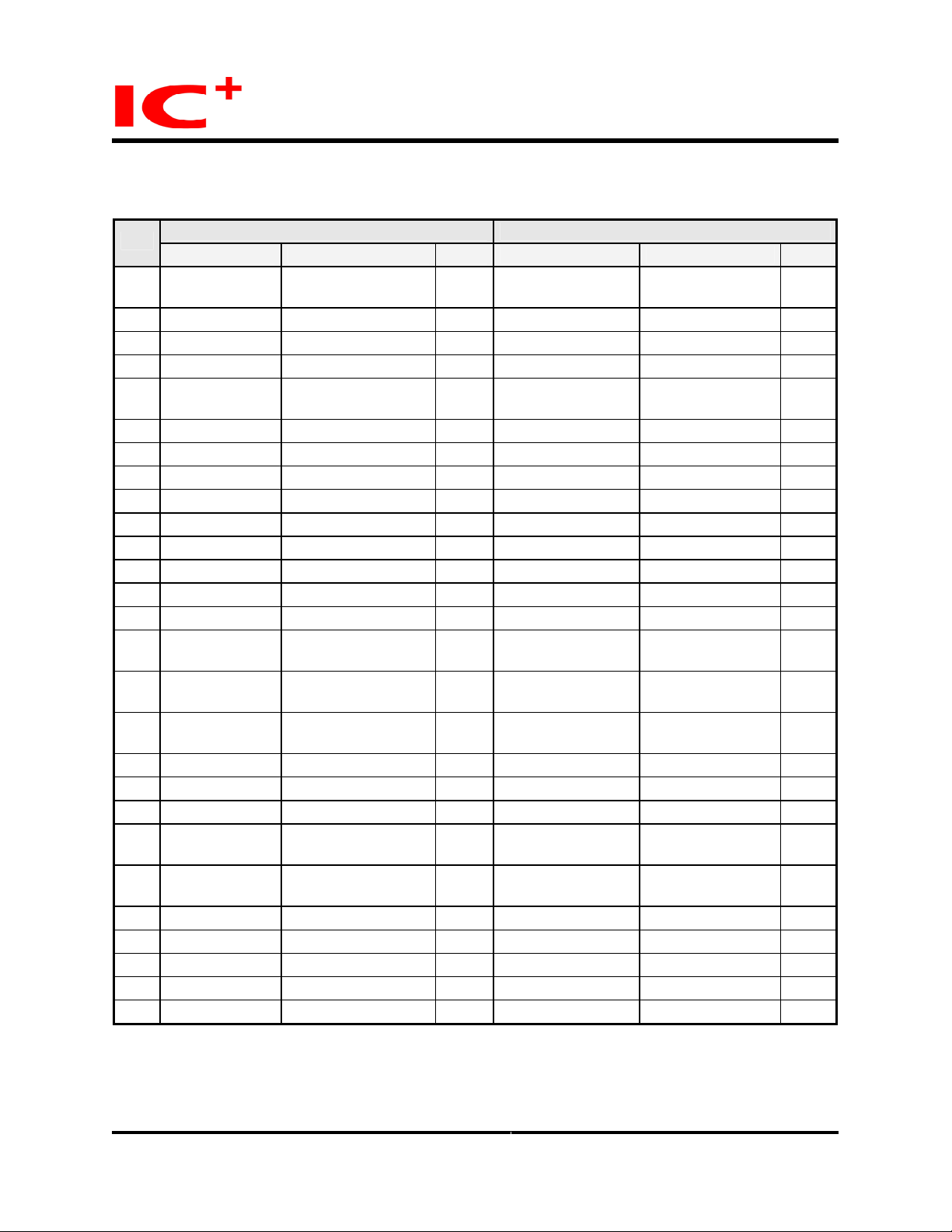

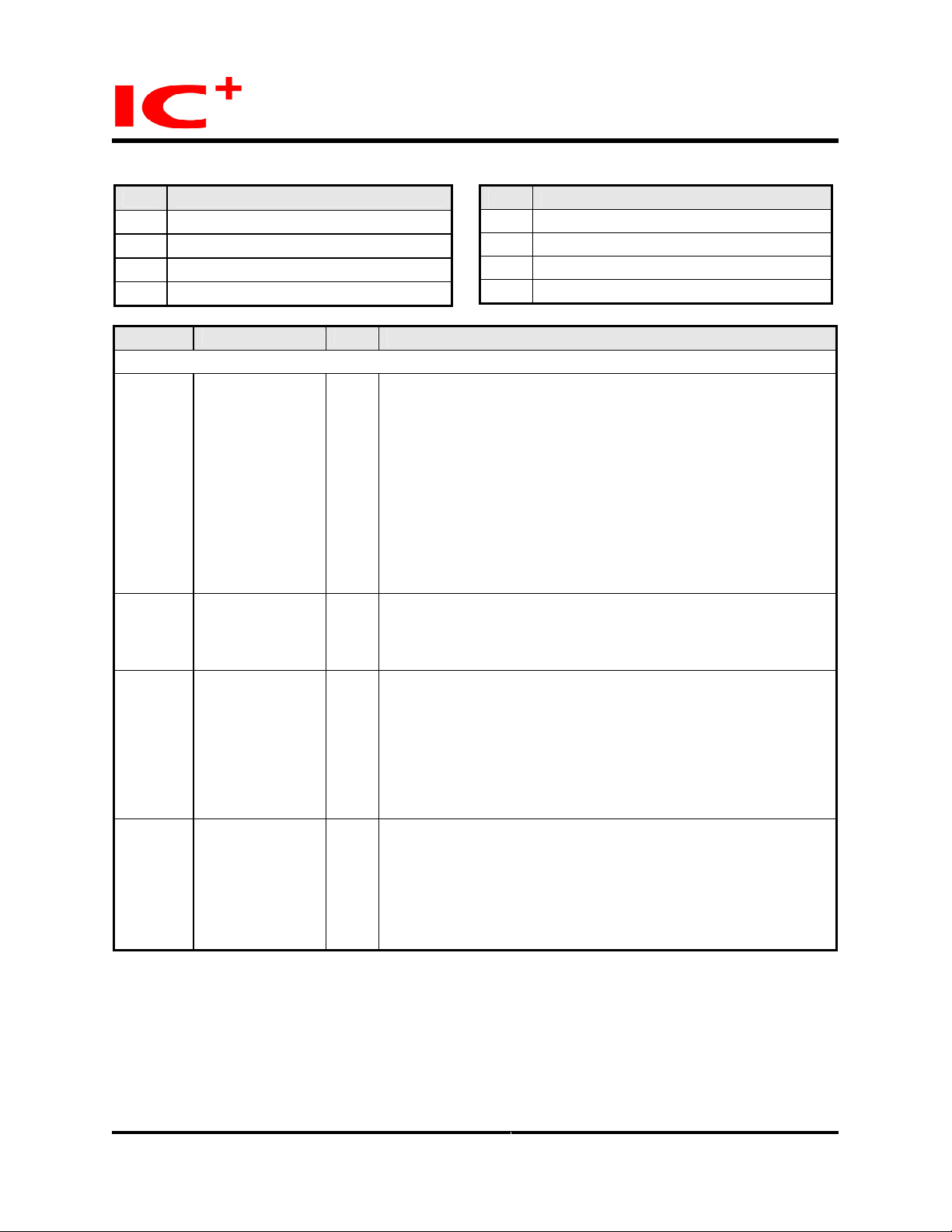

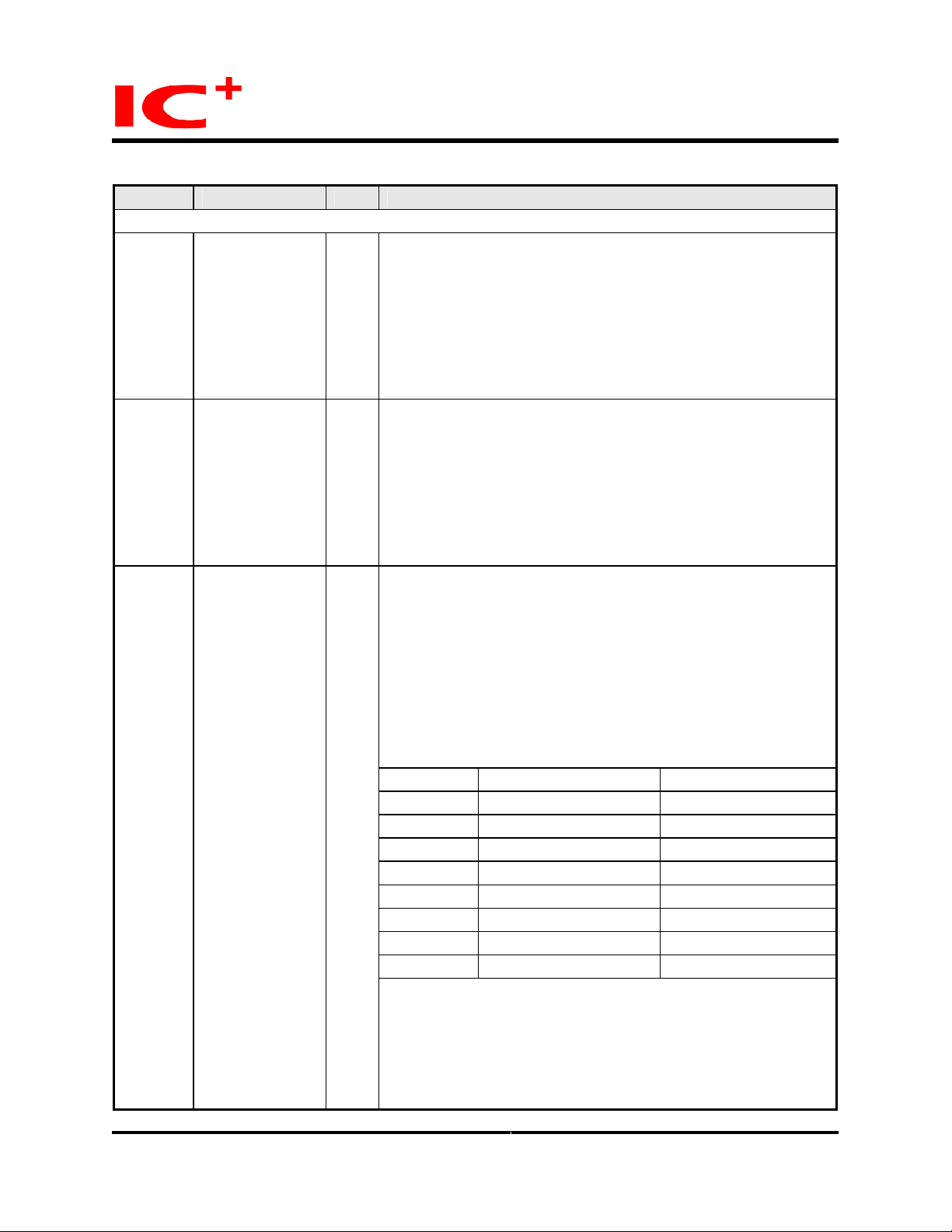

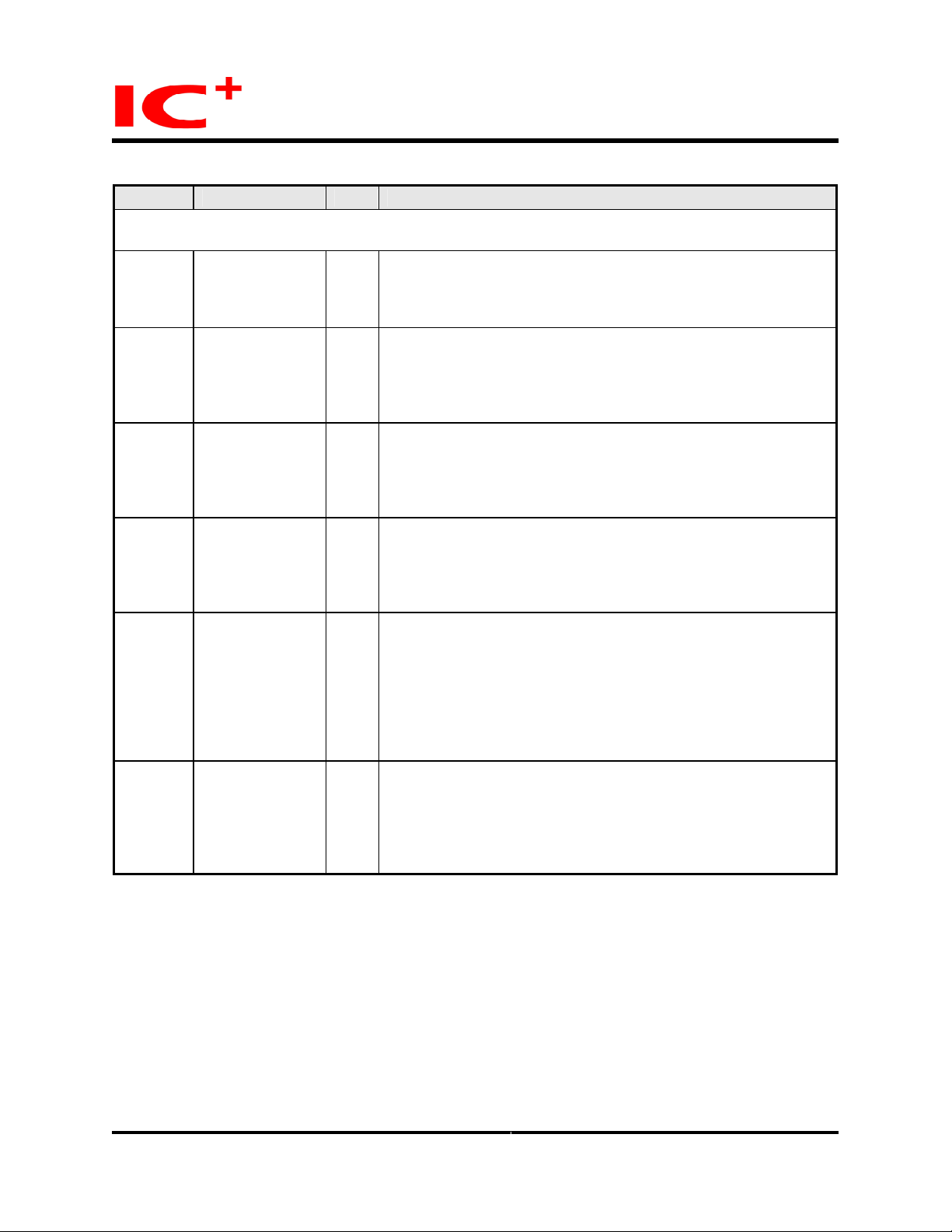

The difference in pin definition between IP178B and IP178C/IP178CH (MII port disabled:

EXTMII_EN=0)

Pin

Function Configure Type Function Configure Type

36 NC I NC(IP178C)

52 REG_OUT I REG_OUT O

53 OSCGND -- EXTMII_EN=0 IPL

56 OSCVCC -- RXCLK IPH

57 GND GND(IP178C)

72 SPEED_LED1 DIRECT_LED IPL SPEED_LED1 IPL

73 SPEED_LED0 SPEED_LED0 SEL_SCA IPL

75 FDX_LED7 FDX_LED7 X_EN IPH

76 FDX_LED6 FDX_LED6 AGING IPH

77 FDX_LED5 FDX_LED5 BCSTF IPL

78 FDX_LED4 FDX_LED4 FILTER_DA IPL

79 FDX_LED3 VLAN_ON IPL FDX_LED3 VLAN_ON IPL

80 LED_SEL [1] IPH LED_SEL [1] IPH

81 LED_SEL [0] IPH LED_SEL [0] IPH

84 AGING IPH LOW_10M_DIS/

85 FDX_LED2 OP1 [1] IPL FDX_LED2 FX7_EN

86 FDX_LED1 OP1 [0] IPL FDX_LED1 FX7_HALF

87 FDX_LED0 HASH_MODE [0] IPL FDX_LED0 LDPS_DIS IPL

90 MID_MDIX_EN IPL MID_MDIX_EN IPH

95 FORCE_MODE IPL BI_COLOR IPL

96 LINK_LED3 OP0 [0] IPL LINK_LED3 FX6_EN

97 LINK_LED2 OP0 [1] IPL LINK_LED2 FX6_HALF

101 UPDATE_R4_EN IPH TXCLK LONG_PKT_DIS IPH

102 EEDI IPL MDIO IPH

103 EEDO IPL MDC IPL

104 EECS IPL SCL IPL

105 EESK IPL SDA IPH

IP178B IP178C/IP178CH

IPL

FXSD6(IP178CH)

FXSD7(IP178CH)

IPH

SCA_DIS

IPL

(for IP178CH only)

IPL

(for IP178CH only)

IPL

(for IP178CH only)

IPL

(for IP178CH only)

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

5/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

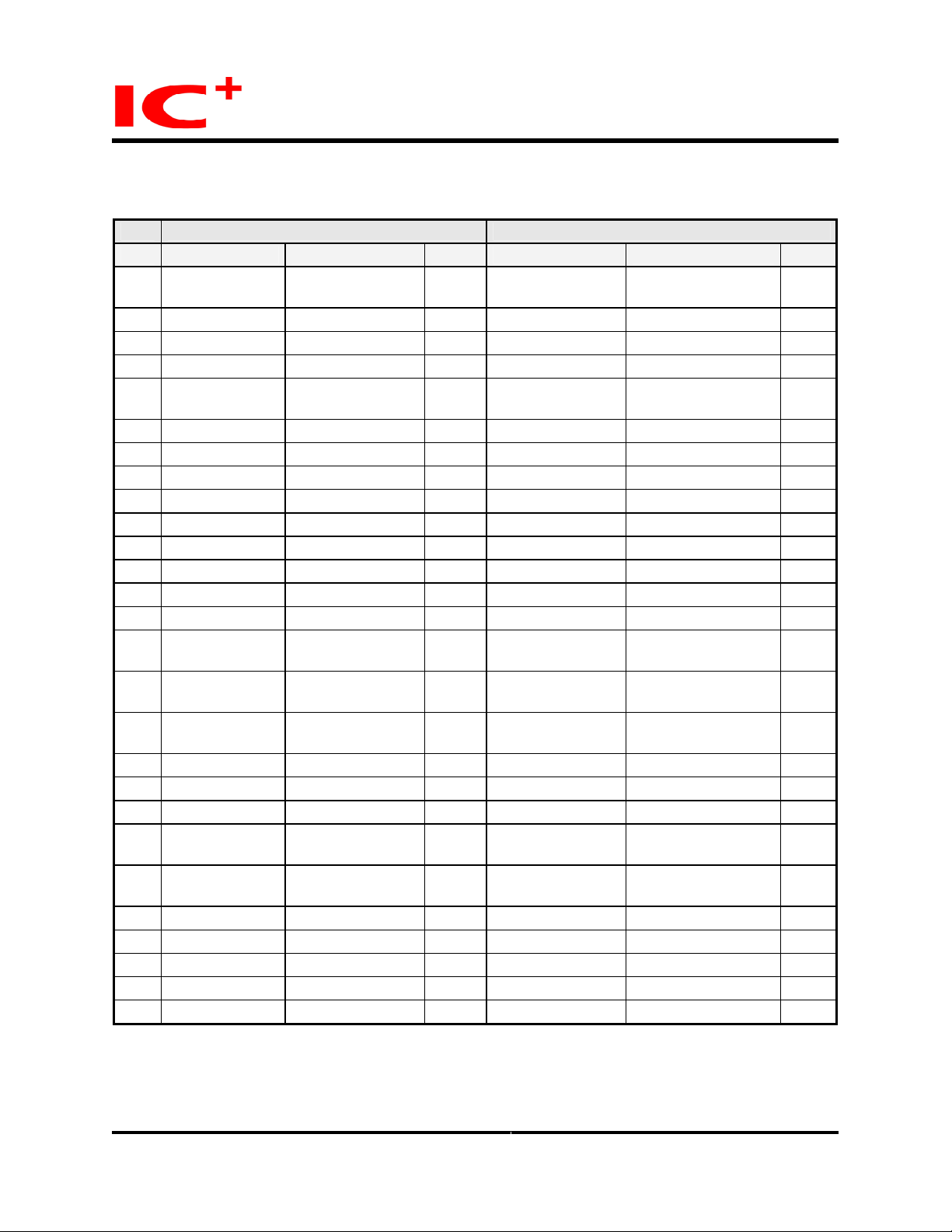

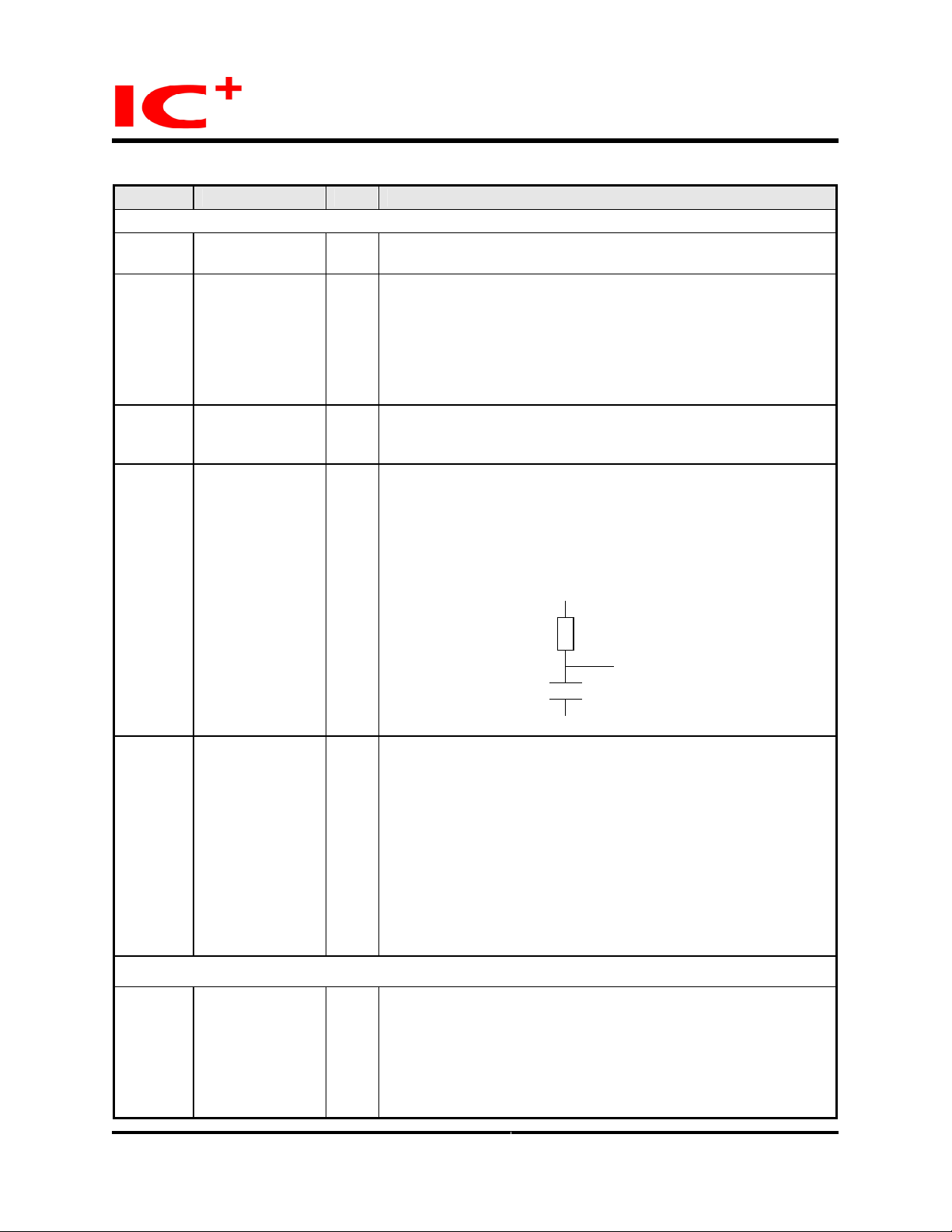

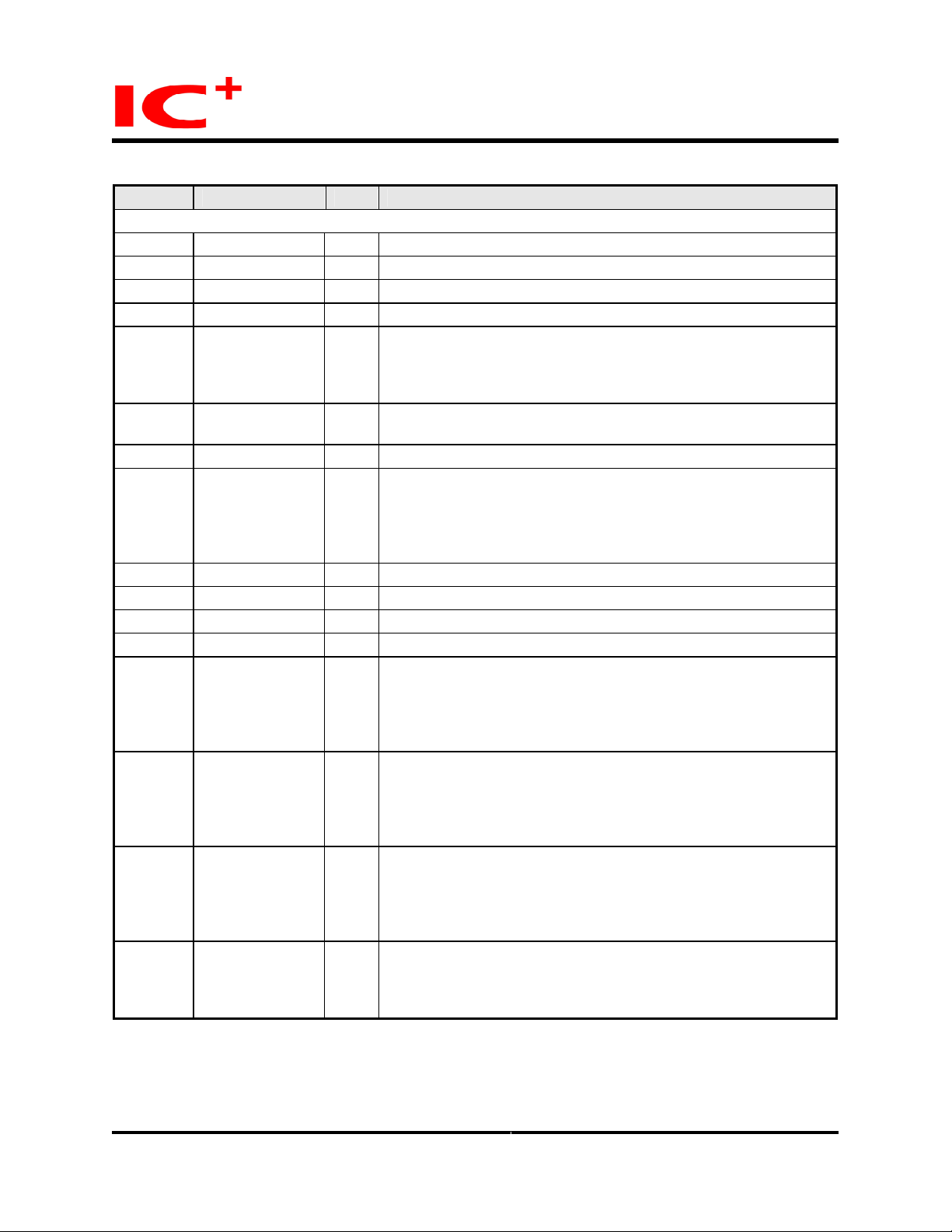

The difference in pin definition between IP178B and IP178C/IP178CH (MII port enabled:

EXTMII_EN=1)

Pin IP178B IP178C/IP178CH

Function Configure Type Function Configure Type

36 NC I NC(IP178C)

FXSD6(IP178CH)

52 REG_OUT I REG_OUT O

53 OSCGND -- EXTMII_EN=1 IPL

56 OSCVCC -- RMII_CLK_IN IPH

57 GND GND(IP178C)

FXSD7(IP178CH)

72 SPEED_LED1 DIRECT_LED IPL SPEED_LED1 RMII_ MII IPL

73 SPEED_LED0 SPEED_LED0 SEL_SCA IPL

75 FDX_LED7 RXDV X_EN IPH

76 FDX_LED6 RMII_CLK_OUT AGING IPH

77 FDX_LED5 RXD2 BCSTF IPL

78 FDX_LED4 RXD1 FILTER_DA IPL

79 FDX_LED3 VLAN_ON IPL RXD0 VLAN_ON IPL

80 LED_SEL [1] IPH TXEN LED_SEL [1] IPH

81 LED_SEL [0] IPH TXD3 LED_SEL [0] IPH

84 AGING IPH LOW_10M_DIS/

85 FDX_LED2 OP1 [1] IPL TXD2 (note1)

86 FDX_LED1 OP1 [0] IPL TXD1 (note1)

87 FDX_LED0 HASH_MODE [0] IPL TXD0 LDPS_DIS IPL

90 MID_MDIX_EN IPL MID_MDIX_EN IPH

95 FORCE_MODE IPL BI_COLOR IPL

96 LINK_LED3 OP0 [0] IPL LINK_LED3 FX6_EN

97 LINK_LED2 OP0 [1] IPL LINK_LED2 FX6_HALF

101 UPDATE_R4_EN IPH TXCLK LONG_PKT_DIS IPH

102 EEDI IPL MDIO IPH

103 EEDO IPL MDC IPL

104 EECS IPL SCL MII_MAC IPL

105 EESK IPL SDA IPH

Note1: FX7_EN & FX7_HALH only can be updated by EEPORM or MDC/MDIO when EXTMII_EN = 1

IPL

IPH

SCA_DIS

IPL

(for IP178CH only)

IPL

(for IP178CH only)

IPL

(for IP178CH only)

IPL

(for IP178CH only)

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

6/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

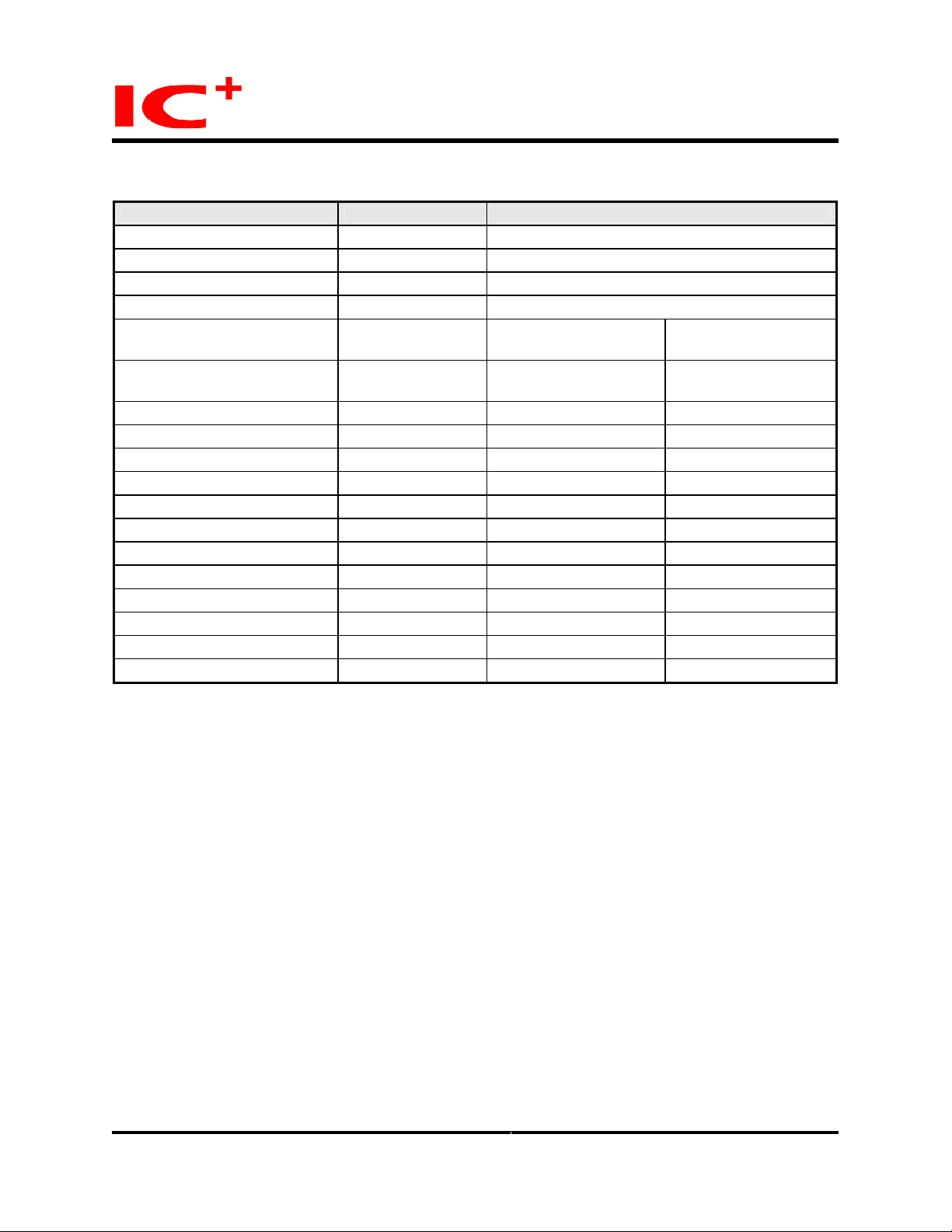

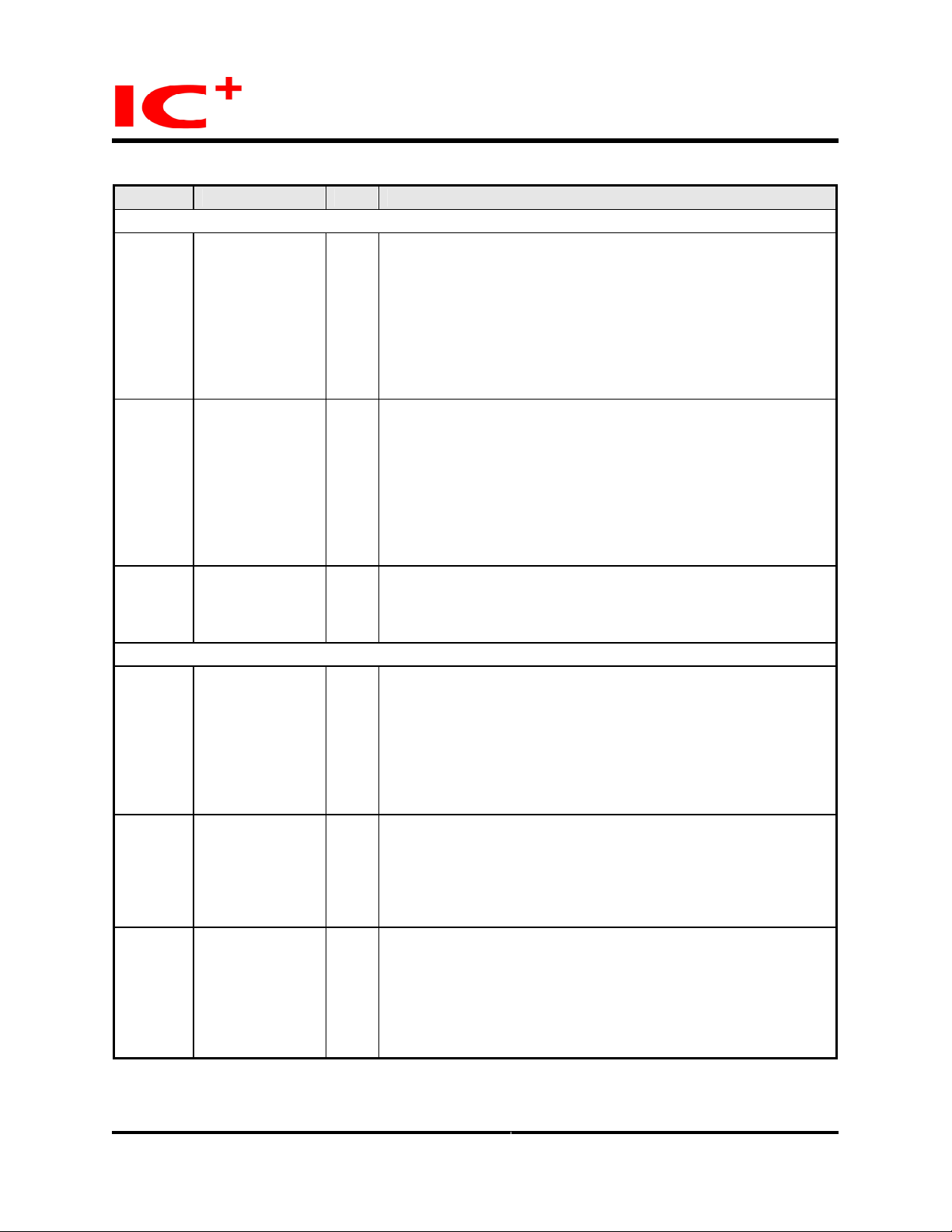

Features comparison between IP178B and IP178C/IP178CH

Function IP178B IP178C/IP178CH

EEPROM 93C46 24C01A

SCA (Smart Cable Analysis) X O

UPDATE_R4_EN O X

8 TP + 1* MII (9 port switch) 8 TP 8 TP + 1* MII (9 port switch)

Disable MII port

(pin 53 EXTMII_EN=0)

LED pins Link, Speed,

Duplex

Link quality LED X Pin 73 Default on (note1)

VLAN_ON Pin 79 Pin 79 Default off (note1)

Filter reserved address option Fixed on Pin 78 Default off (note1)

Broadcast frame option X Pin 77 Default off (note1)

Aging option Pin 84 Pin 76 Default on (note1)

Flow control option Fixed on Pin 75 Default on (note1)

Max packet length option X Pin 101 Default off (note1)

MII port speed/ duplex X X Fixed 100 Mbps full

RMII/MII option X X Pin 72

MII MAC mode/ PHY mode X X Pin 104

MII register, MDC/MDIO X X O

Built in regulator X 2.5v Æ 1.95V 3.3V Æ 1.95V

Note1: The default value can be updated by EEPORM or MDC/MDIO.

Note2: It is UPDATE_R4_EN in IP178B.

Link, Speed, Duplex Link, Speed

Enable MII port

(pin 53 EXTMII_EN=1)

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

7/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

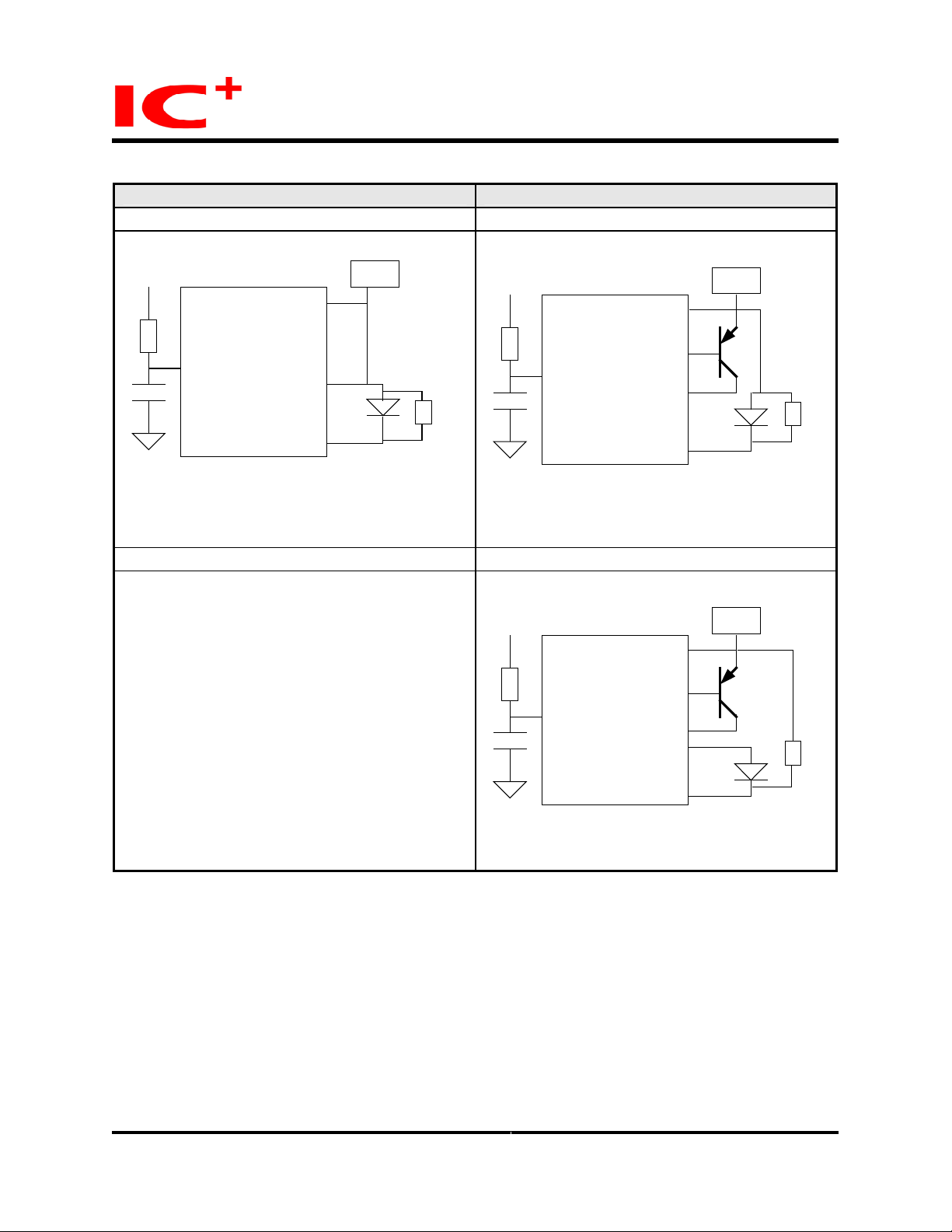

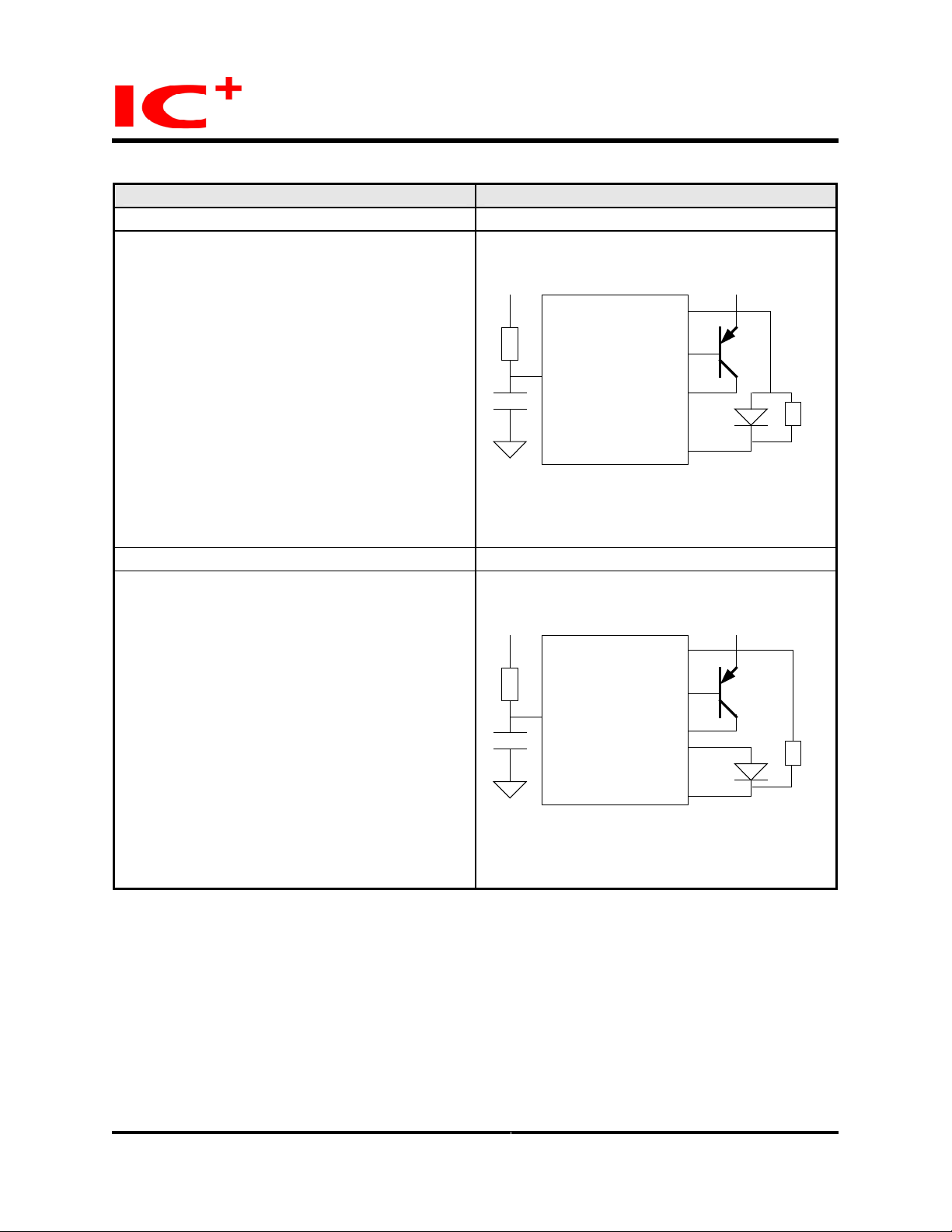

The differences in application circuit between IP178B and IP178C/IP178CH

IP178B IP178C/IP178CH

A. Dumb switch A. Dumb switch (EXTMII_EN=0, BI_COLOR=0)

2.3v

VCC_O

REGOUT

RESETB

AVCC=DVCC

LED178B

34063

2.3v

2.5v

VCC_O

REGOUT

RESETB

AVCC=DVCC

R

LED178C

34063

2.5v

PNP

1.8v

R

Note: R is a pull up resistor for configuration. It

should be connected to VCC_O.

B. Dumb switch (EXTMII_EN=0, BI_COLOR=1)

2.5v

VCC_O

34063

2.5v

NA

RESETB

REGOUT

AVCC=DVCC

LED

PNP

1.8v

R

LED178C

Note: R is a pull up resistor for configuration. It

should be connected to VCC_O.

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

8/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

The differences in application circuit between IP178B and IP178C/IP178CH (continued)

IP178B IP178C/IP178CH

C. Router (EXTMII_EN=1, BI_COLOR=0)

NA

D. Router (EXTMII_EN=1, BI_COLOR=1)

NA

3.3v

VCC_O

REGOUT

RESETB

AVCC=DVCC

LED178C

Note: R is a pull up resistor for configuration. It

should be connected to VCC_O.

3.3v

VCC_O

REGOUT

RESETB

AVCC=DVCC

LED

Datasheet

3.3v

PNP

1.8v

R

3.3v

PNP

1.8v

R

LED178C

Note: R is a pull up resistor for configuration. It

should be connected to VCC_O.

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

9/93

June 21, 2007

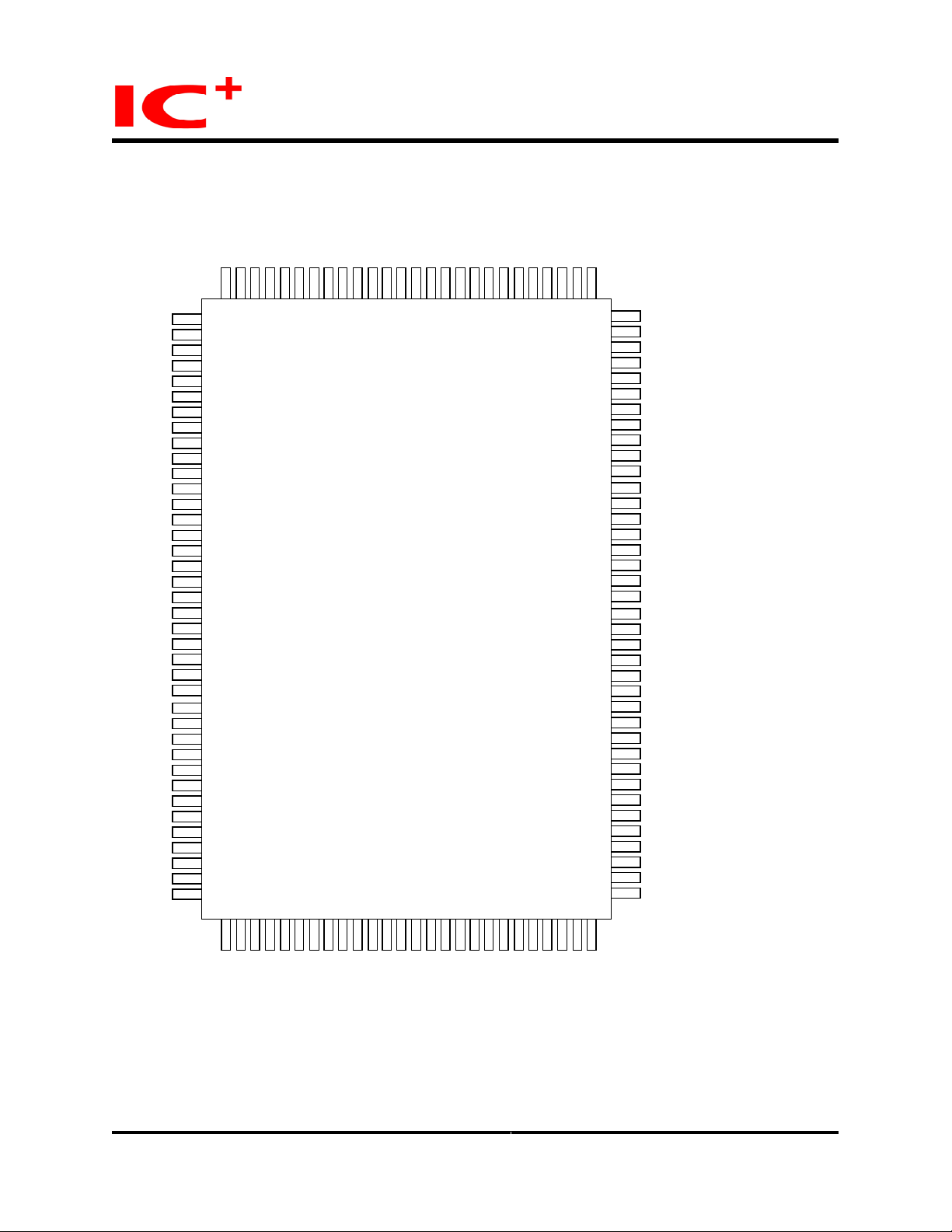

Pin diagram (IP178C)

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

RXVCC2

RXIP2

RXIM2

RXGND2

TXGND2

TXOP2

TXOM2

TXVCC23

TXOM3

TXOP3

TXGND3

RXGND3

RXIM3

RXIP3

RXVCC3

BGVCC

BGRES

BGGND

PLLGND

PLLVCC

RXVCC4

RXIP4

RXIM4

RXGND4

TXGND4

TXOP4

TXOM4

TXVCC45

TXOM5

TXOP5

TXGND5

RXGND5

RXIM5

RXIP5

RXVCC5

RXVCC6

RXIP6

RXVCC1

RXGND1

RXIM1

RXIP1

128

125

126

127

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

NC

37

38

TXVCC01

TXGND1

TXOP1

TXOM1

TXOM0

TXOP0

TXGND0

RXGND0

RXIP0

RXIM0

121

124

123

122

120

119

118

117

115

116

IP178C

GND

RXVCC0

GND

GND

GND

VCC

VCC

VCC

SCL / MII_MAC

SDA

MDC

VCC

111

114

113

112

110

109

108

107

104

105

103

106

102

MDIO

101

TXCLK / LONG_PKT_DIS

100

P6_7_HIGH / LINK_LED0

99

COS_EN / LINK_LED1

98

VCC_SRAM

97

LINK_LED2

96

LINK_LED3

95

BI_COLOR

94

GND_SRAM

93

MODBCK / LI NK_LED4

92

VCC_O

91

BF_STM_EN / LINK_LED5

90

MDI_MDIX_EN / L INK_LED6

89

MLT3_DET / LINK_LED7

88

GND_O

87

TXD0 / LDPS_DIS / FDX_LED0

86

TXD1 / FDX_LED1

85

TXD2 / FDX_LED2

84

LOW_10M_DIS or SCA_DIS

83

VCC_O

82

GND_O

81

TXD3 / LED_SEL[0]

80

TXEN / LED_SEL[1]

79

RXD0 / VLAN_ON / FDX_LED3

78

RXD1/ FILTER_DA/ FDX_LED4

77

RXD2/ BCSTF / FDX_LED5

76

RXD3/ RMII_CLK_OUT / AGING / FDX_LED6

75

RXDV / X_EN / FDX_LED7

74

VCC_SRAM

73

SEL_SCA / SPEED_LED0

72

RMII_MII / SP EED_LED1

71

SPEED_LED2

70

SPEED_LED3

69

SPEED_LED4

68

SPEED_LED5

67

SPEED_LED6

66

SPEED_LED7

65

GND_SRAM

39

RXIM6

TXOP6

TXGND6

RXGND6

June 21, 2007

434244

TXOM6

TXVCC67

46

454147

TXOP7

TXOM7

484049

50

RXIP7

RXIM7

TXGND7

RXVCC7

RXGND7

REG_OUT

535254

OSCI

EXTMII_EN

56

5551575859

X2

GND

GND

RXCLK / RMII_CLK_IN

GND

6063626461

GND

VCC

VCC

VCC

RESETB

10/93

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

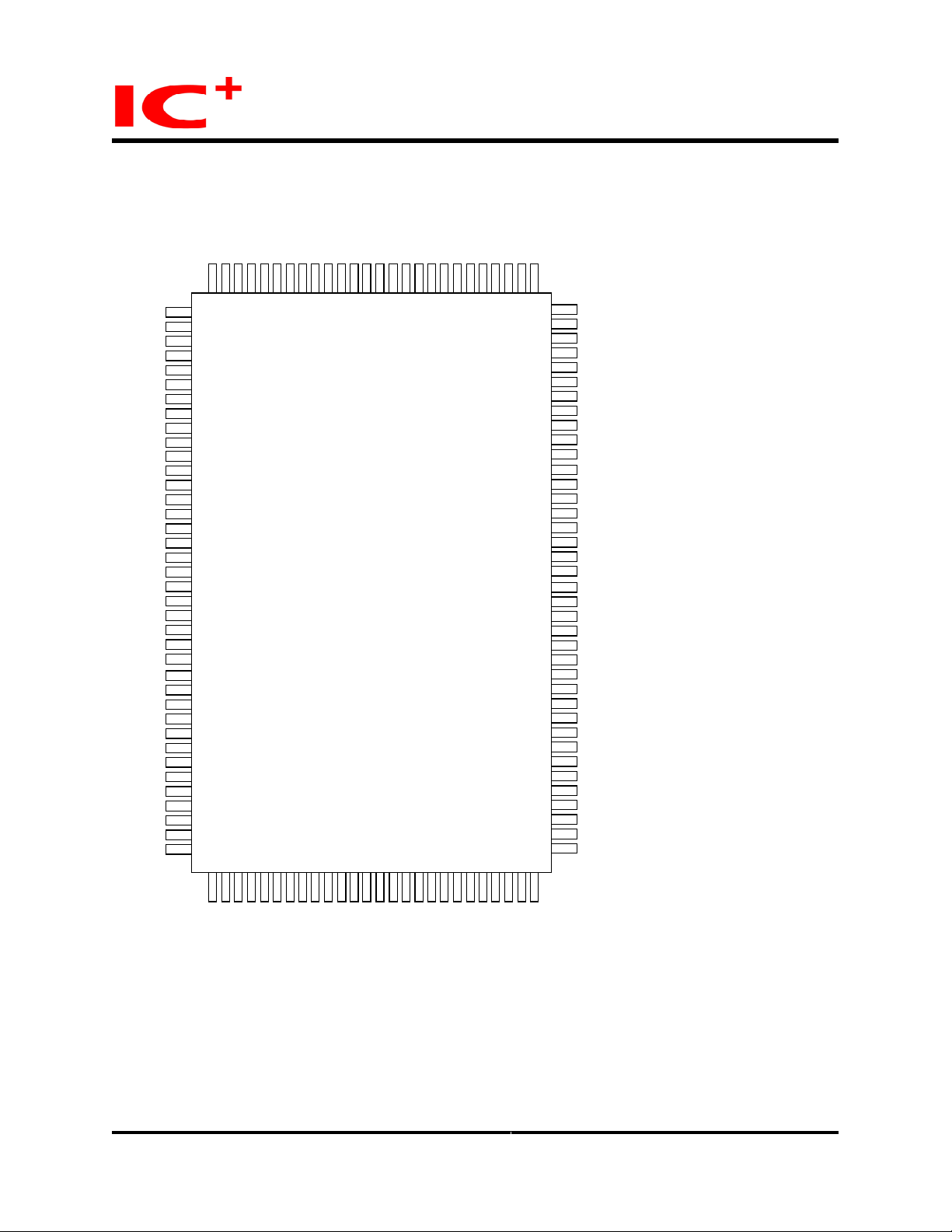

Pin diagram (IP178CH)

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

RXVCC2

RXIP2

RXIM2

RXGND2

TXGND2

TXOP2

TXOM2

TXVCC23

TXOM3

TXOP3

TXGND3

RXGND3

RXIM3

RXIP3

RXVCC3

BGVCC

BGRES

BGGND

PLLGND

PLLVCC

RXVCC4

RXIP4

RXIM4

RXGND4

TXGND4

TXOP4

TXOM4

TXVCC45

TXOM5

TXOP5

TXGND5

RXGND5

RXIM5

RXIP5

RXVCC5

FXSD6

RXVCC6

RXIP6

RXVCC1

RXGND1

RXIM1

RXIP1

128

125

126

127

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

TXVCC01

TXGND1

TXOP1

TXOM1

TXOM0

TXOP0

TXGND0

RXGND0

RXIP0

RXIM0

121

124

123

122

120

119

118

117

115

116

IP178CH

GND

RXVCC0

GND

GND

GND

VCC

VCC

VCC

SCL / MII_MAC

SDA

MDC

VCC

111

114

113

112

110

109

108

107

104

105

103

106

102

MDIO

101

TXCLK / LONG_PKT_DIS

100

P6_7_HIGH / LINK_LED0

99

COS_EN / LINK_LED1

98

VCC_SRAM

97

FX6_EN / LINK_L ED 2

96

FX6_HALF / LINK_LED3

95

BI_COLOR

94

GND_SRAM

93

MODBCK / LINK_LED4

92

VCC_O

91

BF_STM_EN / LINK_LED5

90

MDI_MDIX_EN / LINK_LED6

89

MLT3_DET / LINK_LED7

88

GND_O

87

TXD0 / LDPS_DIS / FDX_LED0

86

TXD1 / FX7_HALH / FDX_LED1

85

TXD 2 / FX7_ EN / FDX_LED2

84

LOW_10M_DIS or SCA_DIS

83

VCC_O

82

GND_O

81

TXD3 / LED_SEL[0]

80

TXEN / LED_SEL[1]

79

RXD0 / VLAN_ON / FDX_LED3

78

RXD1/ FILTER_DA/ FDX_LED 4

77

RXD2/ BCSTF / FDX_LED5

76

RXD 3/ RMII_C L K _ OUT / AGING / F DX_LED6

75

RXDV / X_EN / FDX_LED7

74

VCC_SRAM

73

SEL_SCA / SPEED_LED0

72

RM II_ MII / SPEED _ LED 1

71

SPEED_LED2

70

SPEED_LED3

69

SPEED_LED4

68

SPEED_LED5

67

SPEED_LED6

66

SPEED_LED7

65

GND_SRAM

39

RXIM6

TXOP6

TXGND6

RXGND6

June 21, 2007

434244

TXOM6

TXVCC67

46

454147

TXOP7

TXOM7

TXGND7

484049

RXGND7

RXIM7

5056535254

RXIP7

RXVCC7

REG_OUT

EXTMII_EN

5551575859

X2

OSCI

RXCLK / RMII_CLK_IN

FXSD7

6063626461

GND

GND

GND

1 1 /93

VCC

VCC

VCC

RESETB

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

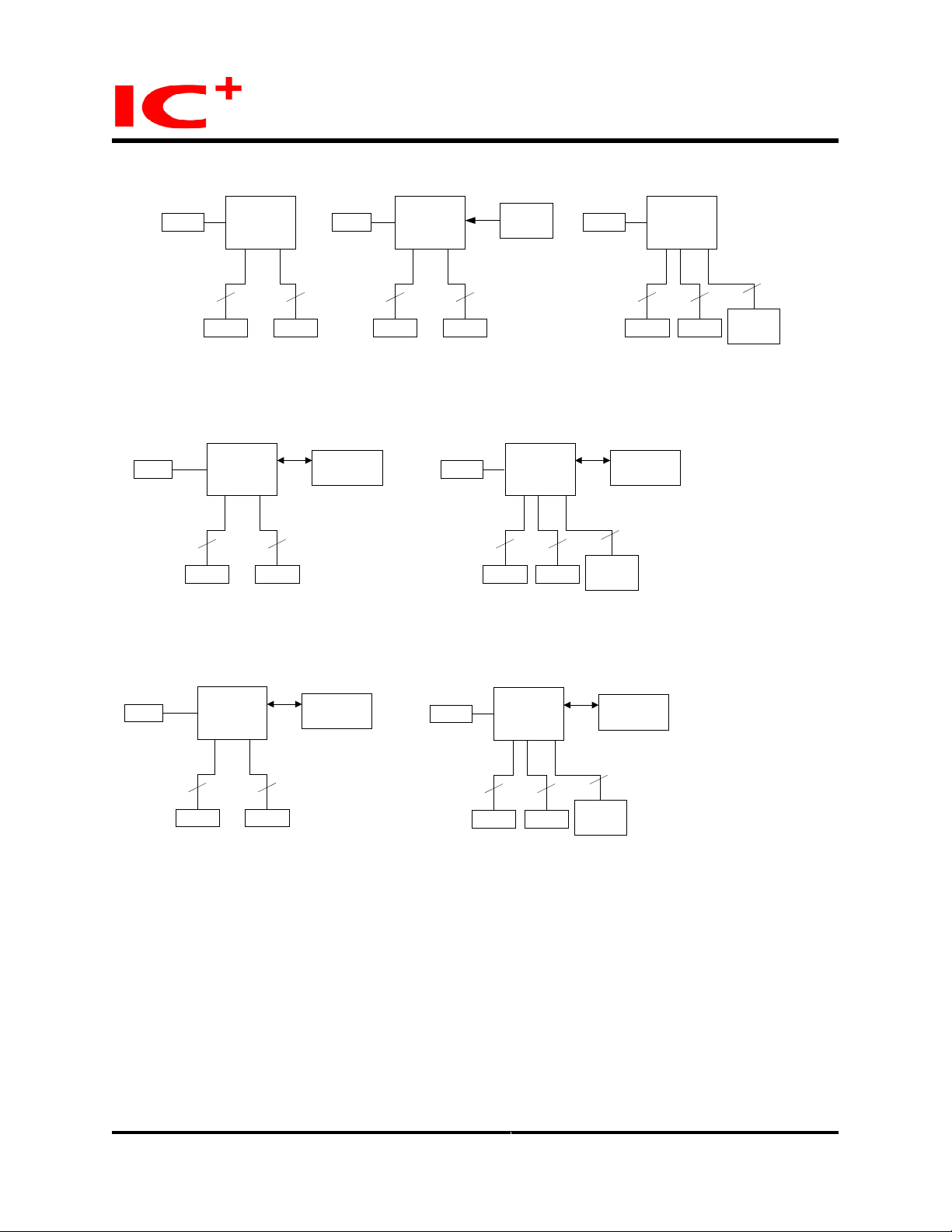

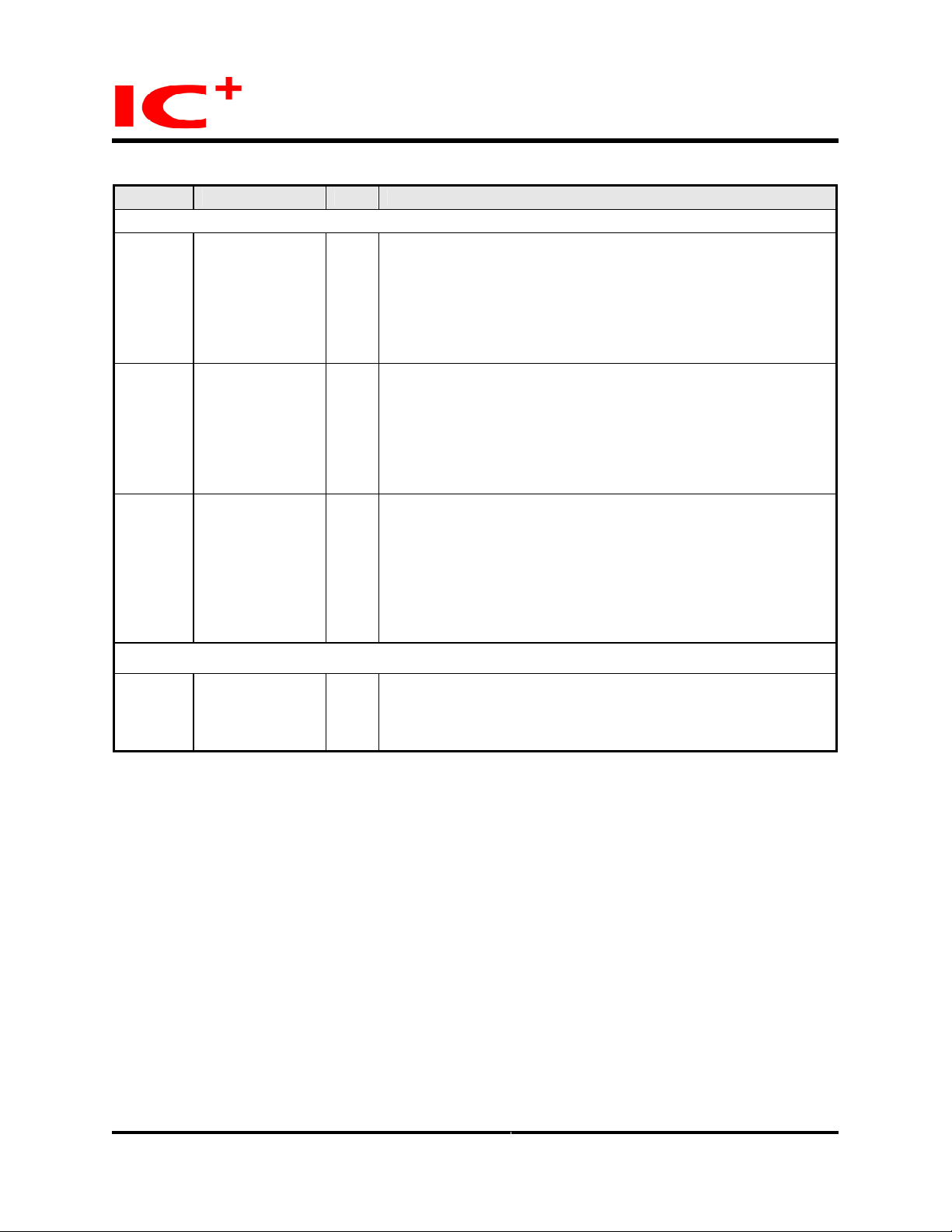

An 8-port switch

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

OSC

Xfm Xfm

A 9-port switch

OSC IP178C

Xfm Xfm

An 8-port router

IP178C

/IP178CH

MII/

RMII

44

OSC

44

IP178C

/IP178CH

Xfm Xfm

24C01

44

OSC IP178CH

24

Xfm Xfm

2

FIBER

MAU

MII/

PHY

OSC IP178CH

Xfm Xfm

RMII

PHY

2

24

FIBER

MAU

OSC

IP178C

/IP178CH

Xfm Xfm

MII/

RMII

June 21, 2007

UP

44

OSC IP178CH

24

Xfm Xfm

MII/

RMII

2

FIBER

MAU

UP

12/93

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

IP178C/IP178CH applications: (continued)

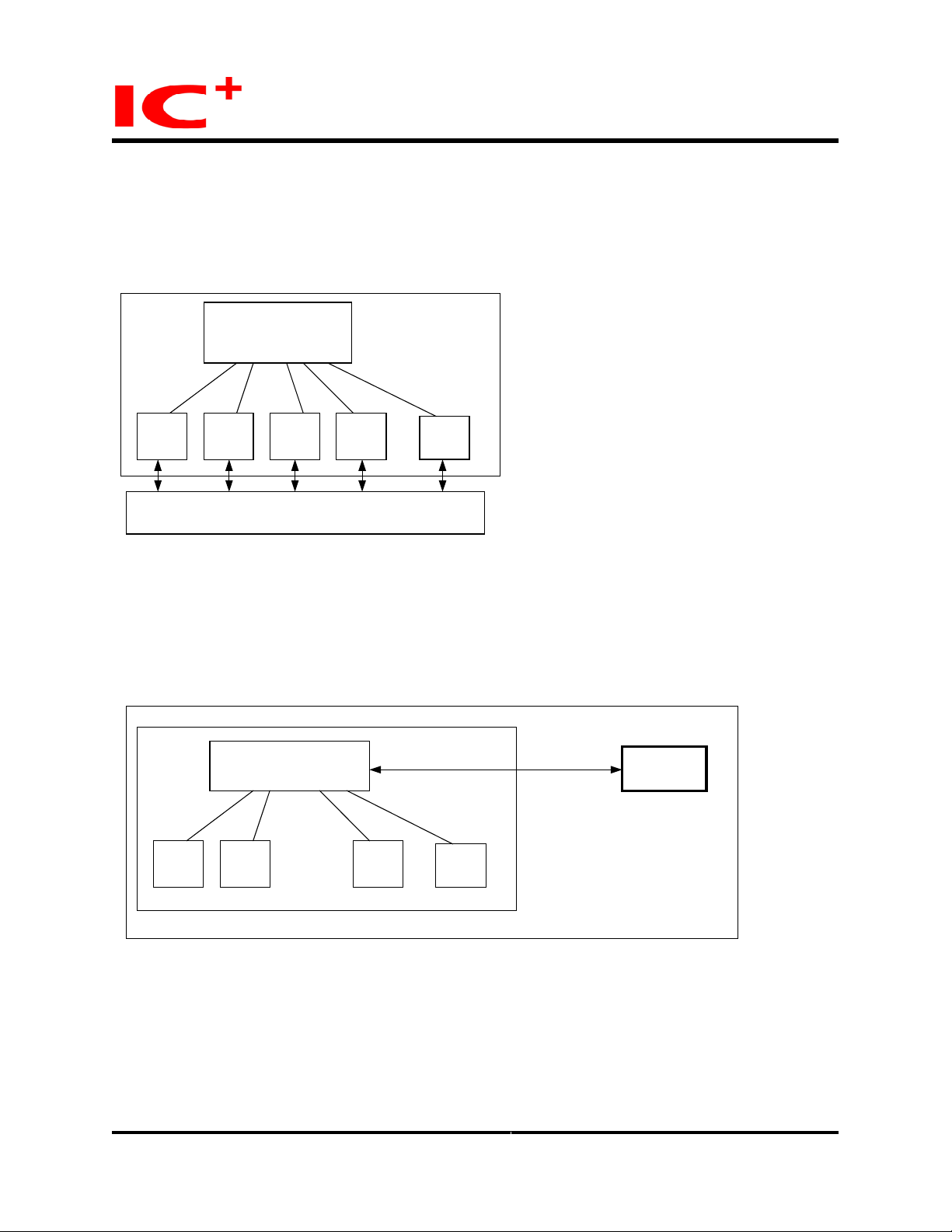

An 8-port switch application

If pin 53 EXTMII_EN is pulled low, then MII/ RMII interface is disabled. IP178C/IP178CH is not

connected to a CPU and works as an 8-port switch. The ninth switch port MAC8 is unused in this

application.

IP178C/

178CH

PHY

0

switch engine

MAC0

PHY

1

.....

PHY

2

TP

MAC8

MAC7

(MAC8 is unused)

PHY

3

PHY

7

A 9-port switch application

If pin 53 EXTMII_EN is pulled high, then MII/ RMII interface is enabled. The ninth switch port MAC8 is

connected to a PHY through the MII/RMII interface. IP178C/IP178CH works as a 9-port switch. Because

IP178C/IP178CH doesn’t access the MII register of the external PHY through SMI, MII/RMII interface

should be MAC mode and full duplex in this application.

IP178C

/178CH

switch engine

.....

MAC0 MAC7

MAC8

MII/RMII

(MAC mode)

external

PHY

PHY

0

PHY

1

.....

PHY

6

PHY

7

June 21, 2007

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

13/93

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

IP178C/IP178CH applications: (continued)

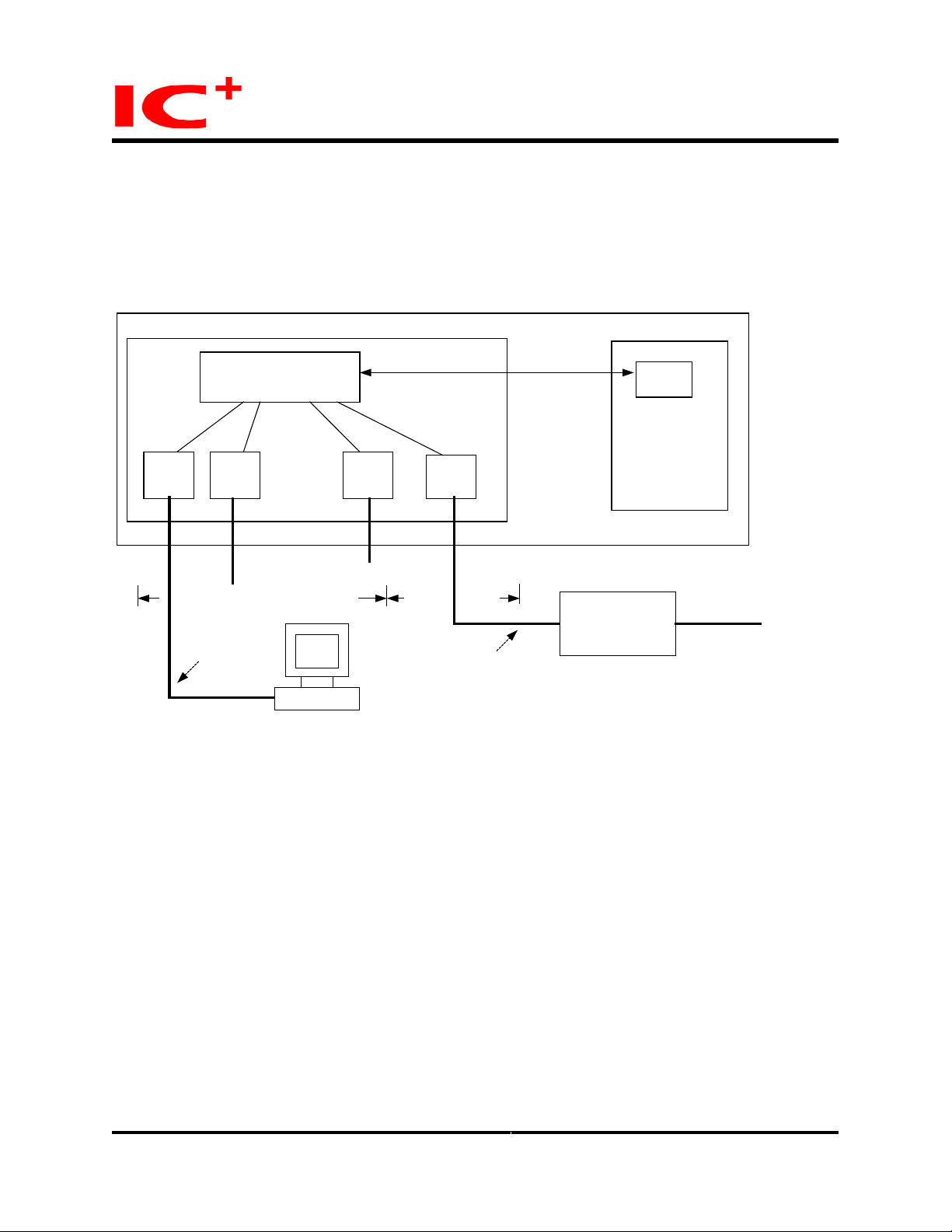

An 8-port router application

IF pin 53 EXTMII_EN is pulled high, then MII/RMII interface is enabled. IP178C/IP178CH is connected to

a CPU through MII/ RMII interface. IP178C/IP178CH works as an 8-port router. MII/RMII interface is set

to be PHY mode and 100 Mbps full duplex in this application.

Router

IP178C

/178CH

PHY

0

switch engine

.....

MAC0 MAC7

PHY

1

Ethernet

.....

MAC8

PC

PHY

6

MII/RMII

(PHY mode)

PHY

7

WAN portLAN port

Ethernet

ADSL

Cable modem

MAC

CPU

WAN to ISP

or

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

14/93

June 21, 2007

m

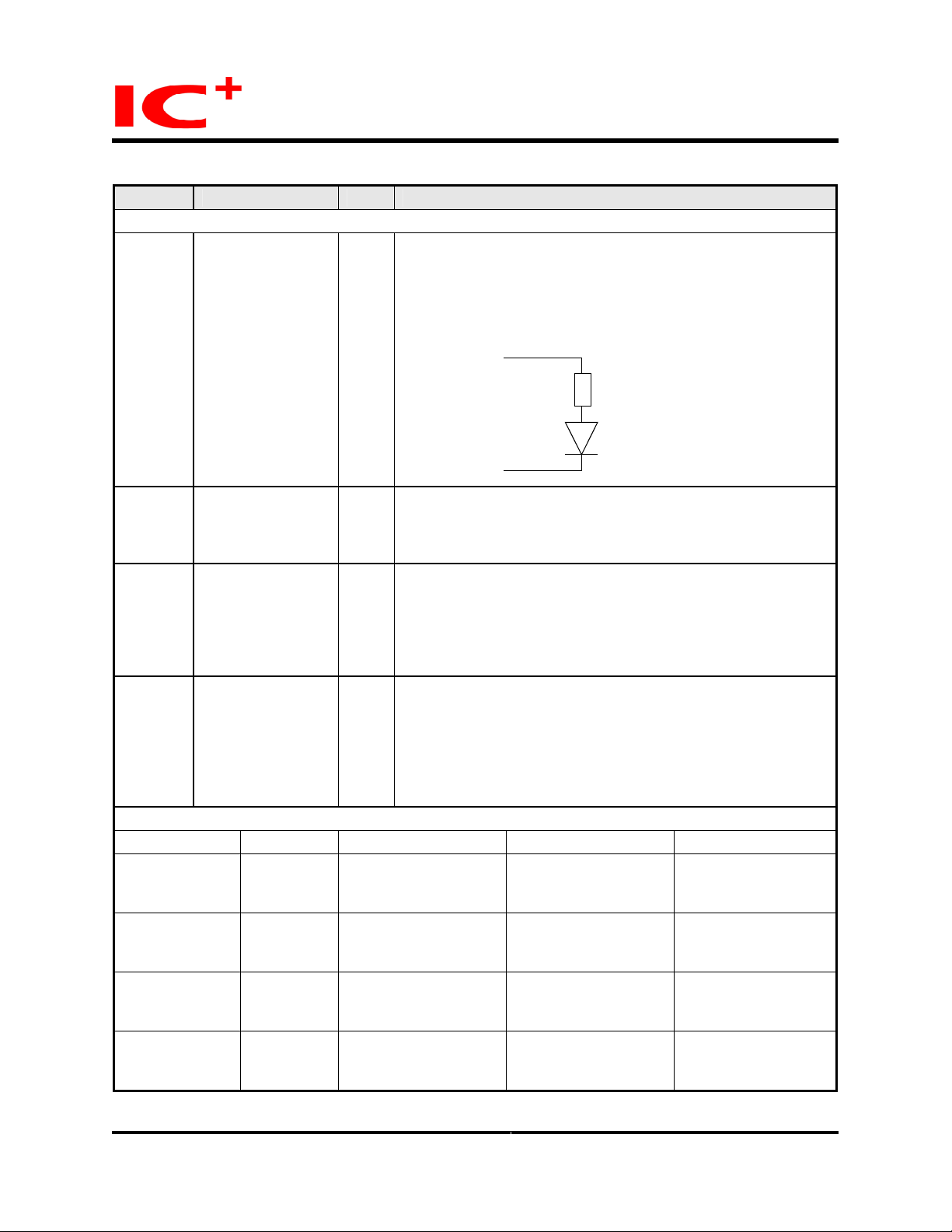

1 Pin description

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

Type Description

Input pin

I

Output pin

O

IPL

IPH Input pin with internal pull high 50M oh

Pin No. Label Type Description

Analog

52 REG_OUT O Regulator output voltage

17 BGRES I Band gap resister

1 15, 116,

127, 126,

2, 3, 14,

13, 22,

23, 34,

33, 38,

39, 50,

49

1 19, 120,

123, 122,

6, 7, 10,

9, 26, 27,

30, 29,

42, 43,

46, 45

Input pin with internal pull low 50M ohm

The internal regulator uses pin83/pin92 VCC_O as reference

voltage to control external transistor to generate a voltage

source between 1.80v ~ 2.05v..

If pin 53 EXTMII_EN is pulled high, then pin83/pin92 VCC_O

should be connected to 3.3v to generate 1.80v ~ 2.05v voltage

source.

If pin 53 EXTMII_EN is pulled low, then pin83/pin92 VCC_O

should be connected to 2.5v to generate 1.80v ~ 2.05v voltage

source.

It is connected to GND through a 6.19k (1%) resistor in

application circuit.

RXIP0~7

RXIM0~7

TXOP0~7

TXOM0~7

I TP receive

O TP transmit

Type Description

IPL1 Input pin with internal pull low 22.8k ohm

IPH1 Input pin with internal pull high 22.8k ohm

IPL2 Input pin with internal pull low 92.6k ohm

IPH2 Input pin with internal pull high 1 13.8k ohm

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

15/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin No. Label Type Description

Misc.

36 NC

(FXSD6)

54 OSCI I 25Mhz system clock

55 X2 O Crystal pin

64 RESETB I Reset

(for IP178CH only)

It is recommended to connect OSCI and X2 to a 25M crystal.

If the clock source is from another chip or oscillator, the clock

should be active at least for 1ms before pin 64 RESETB

de-asserted.

Pin 55 X2 should be left open in this application.

A 25Mhz crystal can be connected to OSCI and X2.

It is low active. It must be hold for more than 1ms. It is Schmitt

trigger input. If a R/C reset circuit is used, the capacitor should

be connected to VCC_O as shown in the figure.

VCC_O

Datasheet

84 LOW_10M_DIS

Or

SCA_DIS

EEPROM

104 SCL IPL2

IPH2 LOW_10M_DIS or SCA_DIS

/O

R

RESETB

C

GND

If pin 73 SEL_SCA is pull low, then pin 84 is LOW_10M_DIS.

If pin 73 SEL_SCA is pull high, then pin 84 is SCA_DIS.

For LOW_10M_DIS

1: disable power saving mode, the 10M transmit amplitude is

depressed in this mode. (default)

0: enable power saving mode

For SCA_DIS

1: Disable smart cable analysis function (default).

0: Enable smart cable analysis function.

Clock of EEPROM

After reset, it is used as clock pin SCL of EEPROM. After

reading EEPROM, this pin becomes an input pin. Its period is

longer than 10us.

IP178C/IP178CH stops reading the rest data in EEPROM if the

first two bytes in EEPROM aren’t 55AA.

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

16/93

June 21, 2007

105 SDA IPH2

IP178C/IP178C LF/IP178CH/IP178CH LF

Datasheet

Data of EEPROM

/O

After reset, it is used as data pin SDA of EEPROM. After reading

EEPROM, this pin becomes an input pin.

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

17/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

LED.

89, 90,

91, 93,

96, 97,

99, 100

LINK_LED [7:0] O LINK LED

The detail functions are illustrated in the following table. It

should be connected to VCC_O through a LED and a resistor.

Application circuit

VCC_O

Datasheet

R

LINK_LED

66, 67,

68, 69,

70, 71,

72, 73

75, 76,

77, 78,

79, 85,

86, 87

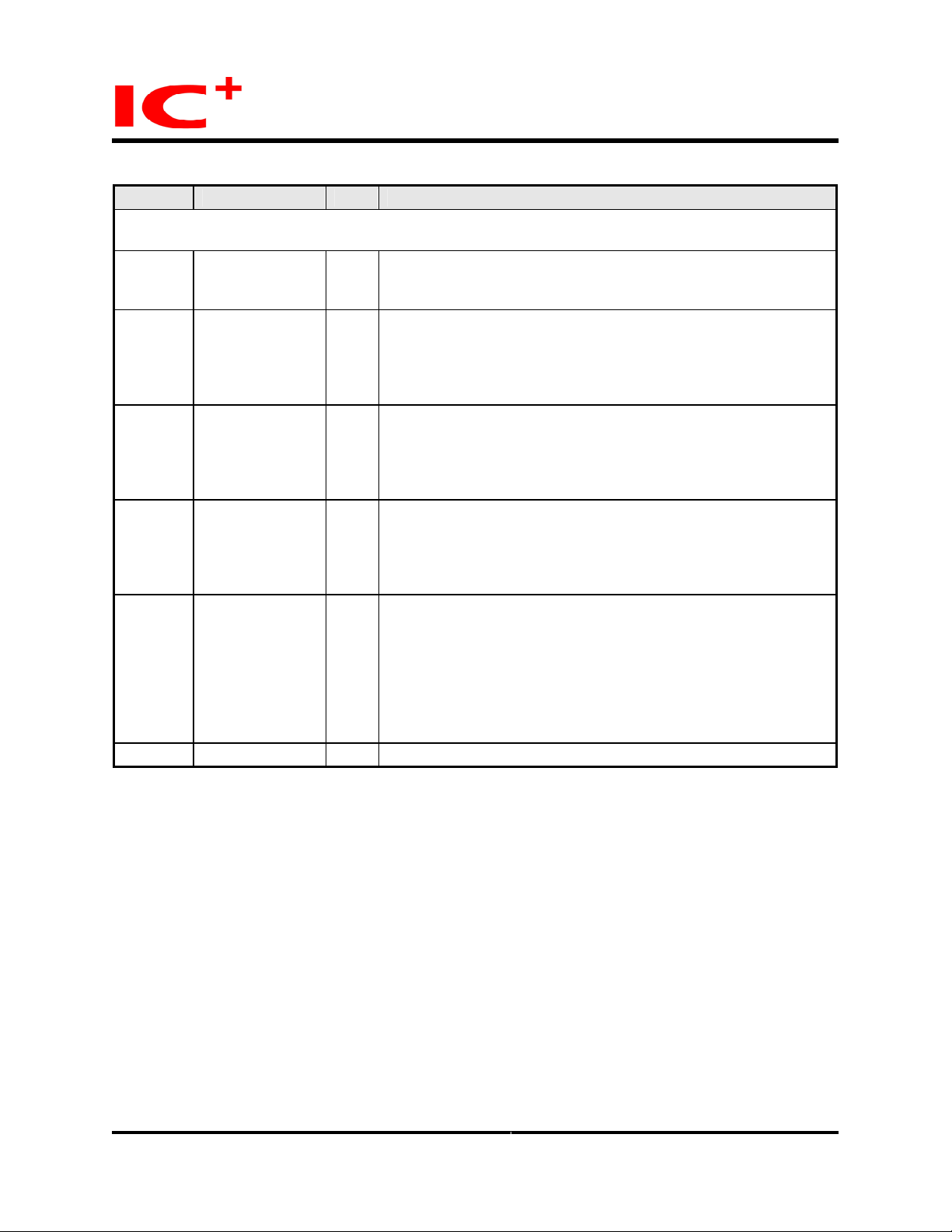

80, 81 LED_SEL [1:0] IPH2 LED function selection

LED_SEL [1:0] LED mode LINK_LED [7:0] SPEED_LED [7:0] FDX_LED [7:0]

00 Mode 0 Off: link fail

01 Mode 1 Off: link fail

10 Mode 2 Off: link fail

11 (default) Mode 3 Off: link fail

SPEED_LED [7:0] O SPEED LED

The detail functions are illustrated in the following table. It

should be connected to VCC_O through a LED and a resistor.

FDX_LED [7:0] O FDX LED

The detail functions are illustrated in the following table. It

should be connected to VCC_O through a LED and a resistor.

The function is valid only if pin 53 EXTMII_EN is pulled low.

The data on these pins are latched at the end of reset to

select LED modes. The default value is mode 3. The detail

functions are illustrated in the following table.

After reset, these two pins becomes MII interface TXEN and

TXD3 if pin 53 EXTMII_EN is pulled high.

On: 10 Mbps link ok

Flash: Tx/Rx

On: link ok

Flash: Rx

On: 10 Mbps link ok

Flash: Tx/Rx

On: link ok

Flash: Tx/Rx

Off: link fail

On: 100 Mbps link ok

Flash: Tx/Rx

Off: 10 Mbps

On: 100 Mbps

Off: link fail

On: 100 Mbps link ok

Flash: Tx/Rx

Off: 10 Mbps

On: 100 Mbps

Off: half duplex

On: full duplex

Off: half duplex

On: full duplex

Flash: collision

Off: half duplex

On: full duplex

Flash: collision

Off: half duplex

On: full duplex

Flash: collision

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

18/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

LED.

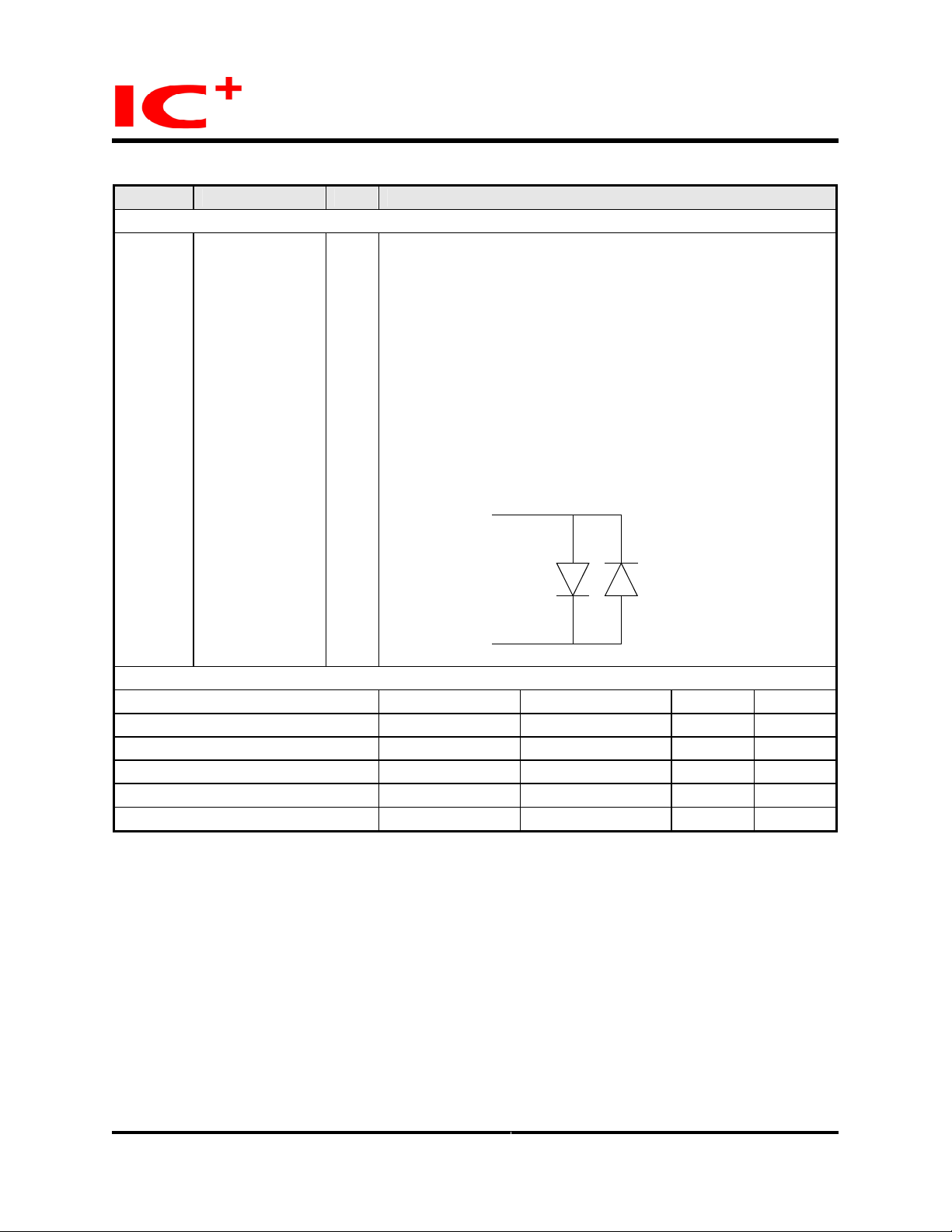

95 BI_COLOR IPL2 Bi-color LED mode enable

1: Bi-color mode LED enabled. LED_LINK [7:0] and

LED_SPEED [7:0] are used to drive dual color LED. The

functions are defined in the following table. The behavior of

FDX_LED [7:0] is the same as that in mode3 on the previous

page.

0: Bi-color mode LED disabled. Please refer to pin description of

LED_SEL [1:0] for LED functions.

This pin takes precedence of LED_SEL [1:0].

Application circuit

Datasheet

LINK_LED

LED 1 LED 2

100M link/act

SPEED_LED

Bi-color LED definition

Status LINK_LED [7:0] SPEED_LED [7:0] LED 1 LED 2

Link off 1 1 Off Off

100 Mbps link ok 1 0 On Off

100 Mbps link ok/ activity 1 Clock Flash Off

10 Mbps link ok 0 1 Off On

10 Mbps link ok/ activity Clock 1 Off Flash

10M link/act

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

19/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

Basic operation parameter setting of switch

87 LDPS_DIS IPL1 Disable link down power saving mode

0: enable link down power saving mode (default)

1: disable link down power saving mode

LDPS_DI S is full duplex LED of port 0 after reset.

The function is valid only if pin 53 EXTMII_EN is pulled low.

89 MLT 3_DET IPL1 Ability for detecting MLT3 (for 10 Mbps switch to 100 Mbps)

0: disable MLT3 detection ability (default)

1: enable MLT3 detection ability

MLT3_DET is link LED of port 7 after reset.

91 BF_STM_EN IPL1 Broadcast storm enable

1: enable, 0: disable (default)

A port begins to drop packets if it receives broadcast packets

more than the threshold defined in MII register 31.9[15:14]

bq_stm_thr_sel [1:0] or EEPROM register 83[7:6].

93 MODBCK IPH1

76 AGING IPH1 Aging enable

73 SEL_SCA IPL1 Select SCA function

75 X_EN IPH1

Aggressive back off enable

/ O

IP178C/IP178CH adopts modified (aggressive) back off

algorithm if this function is enabled. The maximum back off

period is limited to 8-slot time. It makes IP178C/IP178CH have

higher transmission priority in a collision event.

1: aggressive mode enable (default),

0: standard back off

It is link LED of port 4 after reset.

1: enable 300s aging timer (default)

0: disable aging function

The function is valid only if pin 53 EXTMII_EN is pulled low.

Function selection for PIN_84

0: PIN_84 is LOW_10M_DIS (default)

1: PIN_84 is SCA_DIS

Flow control enable

/O

1: enable IEEE802.3x & back pressure (default),

0: disable IEEE802.3x & back pressure

The function is valid only if pin 53 EXTMII_EN is pulled low.

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

20/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

Advance operation parameter setting of switch engine

100 P6_7_HIGH IPL1

99 COS_EN IPL1

79 VLAN_ON IPL1

Port6 port7 are set to be high priority port

/O

Packets received from port6 or port7 are handled a s high p riority

packets if the function is enabled.

1: enable,

0: disabled (default)

It is an input signal during reset and its value is latched at the

end of reset. It acts as a link LED of port 0 after reset.

Class of service enable

/O

Packets with high priority tag are handled as high priority

packets if the function is enabled.

1: enable,

0: disabled (default)

It is an input signal during reset and its value is latched at the

end of reset. It acts as a link LED of port 1 after reset.

Turn on VLAN

/O

Enable a specific configuration of port base VLAN.

0: disabled (default),

1: enable

IP178C/IP178CH are separated into 7 VLANs if this function is

enabled and MII port is disabled.

The VLAN group is as follows.

Pin 53 EXTMII_EN=0 Pin 53EXTMII_EN=1

VLAN 1 port 0, port 7 port 0~7 & MII port

VLAN 2 port 1, port 7 port 0~7 & MII port

VLAN 3 port 2, port 7 port 0~7 & MII port

VLAN 4 port 3, port 7 port 0~7 & MII port

VLAN 5 port 4, port 7 port 0~7 & MII port

VLAN 6 port 5, port 7 port 0~7 & MII port

VLAN 7 port 6, port 7 port 0~7 & MII port

VLAN 8 NA port 0~7 & MII port

It is an input signal during reset and its value is latched at the

end of reset. It acts as a full duplex LED of port 3 after reset.

The configuration can be updated by programming EEPROM

register. Please refer to EEPROM register 66~78 for detail

information.

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

21/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

Advance operation parameter setting of switch engine

77 BCSTF IPL1 Broadcast frame option

1: Packets with DA equal to FFFFFFFF are handled as

broadcast frame in broadcast protection function,

0: Packets with DA equal to FFFFFFFF or multi-cast frames are

handled as broadcast frame in broadcast protection function.

The function is valid only if pin 53 EXTMII_EN is pulled low.

Programming MII register 31.30.12 will overwrite the setting.

78 FILTER_DA IPL1 Reserved address forward option

Filter packets with specific DA from 01-80-c2-00-00-02 to

01-80-c2-00-00-0f. Packets with specific DA equal to

01-80-c2-00-00-01 are always filtered regardless the setting of

this pin.

1: filter, 0: forward (default)

The function is valid only if pin 53 EXTMII_EN is pulled low.

101 LONG_PKT_DIS IPH2 Max packet size option

1: Drop packets with length longer than 1536 bytes

0: Drop packets with length longer than 1552 bytes

TP/ Fiber setting

90 MDI_MDIX_EN IPH1

85 FX7_EN IPL1 Port 7 mode selection (for IP178CH only)

86 FX7_HALF IPL1 Port7 fiber port half duplex (for IP178CH only)

MDI/MDI-X enable

/O

MDI/MDI-X auto cross over

1: enable (default), 0:disable

It is an input signal during reset and its value is latched at the

end of reset to set auto MDI/MDIX function. It is link LED of port

6 after reset.

1: port7 is a fiber port,

0: port7 is a TP port

The function is valid only if pin 53 EXTMII_EN is pulled low.

1: port7 is half duplex,

0: port7 is full duplex

It is valid only if pin 85 FX7_EN is pulled high.

The function is valid only if pin 53 EXTMII_EN is pulled low.

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

22/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

97 FX6_EN IPL1 Port 6 mode selection (for IP178CH only)

1: port6 is a fiber port,

0: port6 is a TP port

96 FX6_HALF IPL1 Port6 fiber port half duplex (for IP178CH only)

1: port6 is half duplex,

0: port6 is full duplex

It is valid only if pin 97 FX6_EN is pulled high.

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

23/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

MII configuration pins

53 EXTMII_EN IPL2 MII port enable

1: enable MII port,

0: disable MII port

This pin53 also determines the regulator output voltage. Please

see pin 52 REG_OUT for detail information.

104 MII_MAC IPL2

72 RMII_MII IPL1

SMI

MII mode selection

/O

It is latched as MII MAC/ PHY mode selection at the end of

reset. It should be pull high if pin 72 RMII_MII is pulled high.

1: MAC mode,

0: PHY mode

After reset, it is used as clock pin SCL of EEPROM

MII RMII selection

/O

It is latched as RMII_MII selection at the end of reset. It is valid

only if pin 53 EXTMII_EN is pulled high. Pin 104 MII_MAC

should be pull high RMII is enabled.

1: RMII,

0:MII

After reset, it is used as SPPED_LED1.

Datasheet

103, 102 MDC, MDIO IPL2

IPH2

SMI

,

The external MAC device uses the interface to access the

registers of IP178C/IP178CH. IP178C/IP178CH doesn’t access

/O

the MII registers of external PHY.

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

24/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

MII interface/ PHY mode

(Pin 53 EXTMII_EN =1, pin104 MII_MAC=0 and Pin72 RMII_MII =0)

101 MIICLK IPL2/O MII transmit & receive clock

It is an output signal when MII works at PHY mode. It should be

connected to MII TXCLK & RXCLK of an external MAC device.

87,86,85

,81

80 TXEN IPH2 MII transmit enable

75 RXDV IPH1/O MII receive data valid

79, 78,

77, 76

56 NC IPH2 This pin should be left open

TXD0~TXD3 IPL1

IPL1

IPL1

IPH2

RXD0~RXD4 IPL1/

IPL1/

IPL1/

IPH1/

MII transmit data

They are input signals when MII works at PHY mode. They are

sampled at the rising edge of MIICLK. They should be

connected to MII TXD of an external MAC device.

It is an input signal when MII works at PHY mode. It is used to

frame TXD [3:0]. It is sampled at the rising edge of MIICLK. It

should be connected to MII TXEN of an external MAC device.

It is an output signal when MII works at PHY mode. It is used to

frame RXD [3:0]. It is sent out at the falling edge of MIICLK. It

should be connected to MII RXDV of an external MAC device.

MII receive data

O,

They are output signals when MII works at PHY mode. They are

O,

sent out at the falling edge of MIICLK. They should be

connected to MII RXD of an external MAC device.

O,

O

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

25/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

MII interface/ MAC mode

(Pin 53 EXTMII_EN =1, pin104 MII_MAC=1 and Pin72 RMII_MII =0)

101 TXCLK IPL2 MII transmit clock

It is an input signal when MII works at MAC mode. It should be

connected to MII RXCLK of an external PHY.

87,86,85

,81

80 TXEN IPH2 MII transmit enable

75 RXDV IPH1/O MII receive data valid

79, 78,

77, 76

56 RXCLK IPH2 MII receive clock

TXD0~TXD3 IPL1

IPL1

IPL1

IPH2

RXD0~RXD4 IPL1/

IPL1/

IPL1/

IPH1/

MII transmit data

They are input signals when MII works at MAC mode. They are

sampled at the rising edge of TXCLK. They should be connected

to MII RXD of an external PHY.

It is an input signal when MII works at MAC mode. It is used to

frame TXD [3:0]. It is sampled at the rising edge of TXCLK. It

should be connected to MII RXDV of an external PHY.

It is an output signal when MII works at MAC mode. It is used to

frame RXD [3:0]. It is sent out at the falling edge of RXCLK. It

should be connected to MII TXEN of an external PHY.

MII receive data

O,

They are output signals when MII works at MAC mode. They are

O,

sent out at the falling edge of RXCLK. They should be

connected to MII TXD of an external PHY.

O,

O

It is an input signal when MII works at MAC mode. It should be

connected to MII TXCLK of an external PHY.

This pin should be left open when MII/RMII is disabled.

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

26/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

RMII interface

(Pin 53 EXTMII_EN =1, pin104 MII_MAC=0 and Pin72 RMII_MII =1)

76 RMII_CLK_OUT O RMII reference clock source

56 RMII_CLK_IN IPH2 RMII reference clock input

87,86 TXD0, TXD1 IPL1 RMII transmit data

It is sampled at the rising edge of RMII_CLK_IN.

80 TXEN IPH2 RMII transmit enable

It is used to frame TXD [1:0]. It is sampled at the rising edge of

RMII_CLK_IN.

75 RXDV IPH1/O RMII receive data valid

It is used to frame RXD [1:0]. It is sent out at the rising edge of

RMII_CLK_IN.

79, 78 RXD0, RXD1 IPL1/O RMII receive data

It is sent out at the rising edge of RMII_CLK_IN.

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

27/93

June 21, 2007

IP178C/IP178C LF/IP178CH/IP178CH LF

Pin description (continued)

Pin no. Label Type Description

Power

16 BGVCC I Power of band gap circuit

18 BGGND I Power of band gap circuit

19 PLLGND I Ground of PLL circuit

20 PLLVCC I Power of PLL circuit

59, 60,

110, 111,

112,

113,

57 GND

58 GND

61, 62,

63, 106,

107,

108,

109,

65, 94, GND_SRAM I Ground of internal SRAM

74, 98, VCC_SRAM I Power of internal SRAM

82, 88, GND_O I Ground for LED, MII and EEPROM

83, 92, VCC_O I Power for LED, MII and EEPROM

114,

128, 1,

15, 21,

35, 37,

51

117,

125, 4,

12, 24,

32, 40,

48,

118,

124, 5,

11, 25,

31, 41,

47,

121,

8,

28,

44,

GND I Ground of internal logic

(FXSD7)

VCC I Power of internal logic

RXVCC0~7 I Power of analog receive block

RXGND0~7 I Ground of analog receive block

TXGND0~7 I Ground of analog transmit buffer

TXVCC01

TXVCC23

TXVCC45

TXVCC67

( for IP178CH only )

I Power of analog transmit buffer

Datasheet

Copyright © 2004, IC Plus Corp. IP178Cx-DS-R12

28/93

June 21, 2007

Loading...

Loading...