Page 1

Front cover

IBM xSeries

450 Planning and

Installation Guide

Describes the technical details of

the new 64-bit server

Covers Windows Server 2003 and

SuSE Linux Enterprise Server

Helps you prepare for and

perform an installation

ibm.com/redbooks

David Watts

Gerry McGettigan

Michael L. Nelson

Lubos Nikolini

Jose Rodriguez Ruibal

Page 2

Page 3

International Technical Support Organization

IBM ^ xSeries 450 Planning and Installation

Guide

July 2003

Page 4

Note: Before using this information and the product it supports, read the information in

“Notices” on page vii.

First Edition (July 2003)

This edition applies to the IBM ^ xSeries 450, machine type 8688.

This document was updated on July 1, 2003.

© Copyright International Business Machines Corporation 2003. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP

Schedule Contract with IBM Corp.

Page 5

Contents

Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . viii

Preface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

The team that wrote this redbook. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ix

Become a published author . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xii

Comments welcome. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xii

Chapter 1. Technical description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 The x450 product line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.2 IBM XA-64 chipset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.3 Extensible Firmware Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.3.1 GUID Partition Table disk . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.3.2 EFI System Partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3.3 EFI and legacy-free concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.4 Intel Itanium 2 processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.5 System assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.5.1 Memory-board assembly. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.5.2 Processor-board assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.6 IBM XceL4 Server Accelerator Cache. . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.7 System memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.8 PCI subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.9 Redundancy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.10 Light path diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.11 Remote Supervisor Adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

1.12 Operating system support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Chapter 2. Positioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.1 x450 application solutions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.1.1 Database applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.1.2 Business logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.1.3 e-business and security transactions . . . . . . . . . . . . . . . . . . . . . . . . 33

2.1.4 In-house developed compute-intensive applications . . . . . . . . . . . . 34

2.1.5 Science and technology industries . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.2 Why choose x450? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Chapter 3. Planning. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.1 System hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.1.1 Processors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

© Copyright IBM Corp. 2003. All rights reserved. iii

Page 6

3.1.2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.1.3 PCI slot configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.1.4 Broadcom Gigabit Ethernet controller . . . . . . . . . . . . . . . . . . . . . . . . 47

3.2 Cabling and connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.2.1 Remote Supervisor Adapter connectivity . . . . . . . . . . . . . . . . . . . . . 50

3.2.2 Remote Expansion Enclosure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.2.3 Serial connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.3 Storage considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

3.3.1 xSeries storage solutions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

3.3.2 Tape backup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.4 Rack installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.5 Power considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.6 Solution Assurance Review. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Chapter 4. Installation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

4.1 Using the Extensible Firmware Interface. . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.1.1 The EFI shell. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.1.2 Flash update . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.1.3 Configuration and Setup utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.1.4 Diagnostic utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4.1.5 Boot maintenance menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

4.2 Installing Windows Server 2003 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

4.2.1 Overall process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4.2.2 Microsoft Reserved Partition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.2.3 Windows installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

4.2.4 Pre-installation phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

4.2.5 Starting the installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.2.6 Text-mode setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4.2.7 GUI setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.2.8 Post-setup phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.3 Installing SuSE Linux Enterprise Server . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.3.1 Background . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

4.3.2 Linux IA-64 kernel overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

4.3.3 Choosing a Linux distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

4.3.4 Installing SuSE Linux Enterprise Server . . . . . . . . . . . . . . . . . . . . . 103

4.3.5 Linux boot process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

4.3.6 Information about the installed system . . . . . . . . . . . . . . . . . . . . . . 108

4.3.7 Using the serial port for the Linux console . . . . . . . . . . . . . . . . . . . 112

4.3.8 RXE-100 Expansion Enclosure. . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

4.3.9 Upgrading drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Chapter 5. Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

5.1 The Remote Supervisor Adapter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

iv IBM ^ xSeries 450 Planning and Installation Guide

Page 7

5.1.1 The Remote Supervisor Adapter. . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.1.2 Connecting via a Web browser . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.1.3 Configuring a static IP address . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

5.1.4 Connecting via the ASM interconnect . . . . . . . . . . . . . . . . . . . . . . . 124

5.1.5 Installing the device driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.1.6 Configuring the remote control password . . . . . . . . . . . . . . . . . . . . 125

5.2 Management using the Remote Supervisor Adapter . . . . . . . . . . . . . . . 126

5.2.1 Configuring which alerts to monitor. . . . . . . . . . . . . . . . . . . . . . . . . 126

5.2.2 Configuring SNMP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.2.3 Sending alerts directly to IBM Director . . . . . . . . . . . . . . . . . . . . . . 128

5.2.4 Creating a test event action plan in IBM Director . . . . . . . . . . . . . . 130

Related publications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

IBM Redbooks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Referenced Web sites . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

How to get IBM Redbooks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

IBM Redbooks collections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Contents v

Page 8

vi IBM ^ xSeries 450 Planning and Installation Guide

Page 9

Notices

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult

your local IBM representative for information on the products and services currently available in your area.

Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM

product, program, or service may be used. Any functionally equivalent product, program, or service that

does not infringe any IBM intellectual property right may be used instead. However, it is the user's

responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document.

The furnishing of this document does not give you any license to these patents. You can send license

inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such

provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION

PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR

IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT,

MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer

of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made

to the information herein; these changes will be incorporated in new editions of the publication. IBM may

make improvements and/or changes in the product(s) and/or the program(s) described in this publication at

any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any

manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the

materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without

incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published

announcements or other publicly available sources. IBM has not tested those products and cannot confirm

the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on

the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them

as completely as possible, the examples include the names of individuals, companies, brands, and products.

All of these names are fictitious and any similarity to the names and addresses used by an actual business

enterprise is entirely coincidental.

COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming

techniques on various operating platforms. You may copy, modify, and distribute these sample programs in

any form without payment to IBM, for the purposes of developing, using, marketing or distributing application

programs conforming to the application programming interface for the operating platform for which the

sample programs are written. These examples have not been thoroughly tested under all conditions. IBM,

therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy,

modify, and distribute these sample programs in any form without payment to IBM for the purposes of

developing, using, marketing, or distributing application programs conforming to IBM's application

programming interfaces.

© Copyright IBM Corp. 2003. All rights reserved. vii

Page 10

Trademarks

The following terms are trademarks of the International Business Machines Corporation in the United States,

other countries, or both:

Redbooks (logo)™

iSeries™

pSeries™

xSeries™

zSeries™

Chipkill™

DB2 Universal Database™

DB2®

Enterprise Storage Server™

eServer™

The following terms are trademarks of other companies:

Intel, Intel Inside (logos), MMX, and Pentium are trademarks of Intel Corporation in the United States, other

countries, or both.

Microsoft, Windows, Windows NT, and the Windows logo are trademarks of Microsoft Corporation in the

United States, other countries, or both.

Java and all Java-based trademarks and logos are trademarks or registered trademarks of Sun

Microsystems, Inc. in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries.

SET, SET Secure Electronic Transaction, and the SET Logo are trademarks owned by SET Secure

Electronic Transaction LLC.

Other company, product, and service names may be trademarks or service marks of others.

^™

ESCON®

FlashCopy®

FICON™

IBM®

Lotus®

Netfinity®

Predictive Failure Analysis®

PS/2®

™

Redbooks™

ServerProven®

ServeRAID™

Summit®

ThinkPad®

Tivoli®

TotalStorage™

Wake on LAN®

X-Architecture™

viii IBM ^ xSeries 450 Planning and Installation Guide

Page 11

Preface

The IBM ^ xSeries™ 450 is IBM®’s new 64-bit Itanium Processor Family

(IPF) Architecture server and is the first implementation of the 64-bit IBM XA-64

chipset, as part of the Enterprise X-Architecture™ strategy. This IBM Redbook is

a comprehensive resource on the technical aspects of the server, and is divided

into five key subject areas:

Chapter 1, “Technical description” introduces the server and its subsystems

Chapter 2, “Positioning” examines the types of applications that would be

Chapter 3, “Planning” describes the considerations when planning to

Chapter 4, “Installation” covers the process of installing Windows Server

Chapter 5, “Management” describes how to use the Remote Supervisor

and describes the key features and how they work. This includes the new

Extensible Firmware Interface, which provides a powerful replacement to the

BIOS facility found on the IA-32 platform.

used on a server such as the x450.

purchase and planning to install the x450. It covers such topics as

configuration, operating system specifics, scalability, and physical site

planning.

2003, Enterprise Edition and SuSE Linux Enterprise Server on the x450.

Adapter to send alerts to an IBM Director management environment.

The team that wrote this redbook

This redbook was produced by a team of specialists from around the world

working at the International Technical Support Organization, Raleigh Center.

David Watts is a Consulting IT Specialist at the International Technical Support

Organization in Raleigh. He manages residencies and produces IBM

Redbooks™ on hardware and software topics related to IBM xSeries systems

and associated client platforms. He has authored over 20 Redbooks; his most

recent books include the

Guide

. He has a Bachelor of Engineering degree from the University of

Queensland (Australia) and has worked for IBM for over 14 years. He is an

IBM ^ Certified Specialist for xSeries and an IBM Certified IT

Specialist.

© Copyright IBM Corp. 2003. All rights reserved. ix

IBM

^

xSeries 440 Planning and Installation

Page 12

Gerry McGettigan is an Advanced Technical Support engineer in EMEA working

in Greenock, Scotland. Before joining ATS in the summer of 2002, he provided

pre-sale and post-sale technical training on high-end xSeries systems and

solutions as part of the xSeries Academy. He holds a Bachelor of Science in

Multimedia Technology from Glasgow Caledonian University and has been with

IBM for over five years. His area of expertise is xSeries systems and hardware.

Michael L. Nelson is a Performance Consultant in IBM ^ Solutions

Engineering working in Raleigh. He was previously an architect for many of the

xSeries Web-based sizing tools. He is a Microsoft Certified Systems Engineer on

both Windows NT 4.0 and 2000, a Lotus® Certified Professional, a Cisco

Certified Network Associate, a Citrix Certified Administrator, and an

IBM ^ Certified Expert for xSeries. He also holds a Bachelor of Arts

degree from Whittier College. He has five years of experience with Intel-based

server hardware, and has worked for IBM for six years. His areas of expertise

include xSeries hardware, Microsoft Windows, and Citrix.

Lubos Nikolini is a Systems Engineer working for HT Computers a.s. in

Bratislava, Slovak Republic. He has six years of experience with Microsoft

operating systems, Intel-based hardware (including IBM xSeries and Netfinity®),

networking, and storage technologies. He is a Microsoft MCSE, Citrix CCEA and

a Compaq Proliant ASE. His areas of expertise include Active Directory

deployments, thin-client technology, and groupware solutions.

Jose Rodriguez Ruibal is a Linux Specialist in the Advanced Technical Support

(ATS) Products and Solutions Support Center (PSSC) for EMEA in Montpellier,

France. Prior to joining the ATS team, he worked for Red Hat in Spain and for the

INRIA (National French Institute for Research in Computing and Robotics) in

Linux-related activities. He has four years of experience in Linux and UNIX-like

network operating systems. He holds a Bachelor’s degree with Honors in

Computer Science from the Universidad Antonio de Nebrija in Madrid, Spain,

and he is also Red Hat Certified Engineer. His areas of expertise include xSeries

hardware and storage, and Linux. He has also authored a white paper about

Oracle 9i RAC installation under Linux on xSeries x360 and x440 machines.

x IBM ^ xSeries 450 Planning and Installation Guide

Page 13

The redbook team (l-r): David, Jose, Gerry, Mike, Lubos

Thanks to the following IBM employees for their contributions to this project:

Henry Artner, Service Education Curriculum Manager, Raleigh

Charlotte Brooks, ITSO Project Leader for Tivoli® Storage, San Jose

Pat Byers, Program Director, Linux xSeries Alliances & Marketing

Alex Candelaria, IBM Center for Microsoft Technologies, Seattle

Zeynep Dayar, xSeries Systems Management, Raleigh

Peter Figueroa, Technical Project Manager, Software Development, Raleigh

Amy Freeman, Manager Brand Communications, Linux on xSeries, Raleigh

Maynard Ferguson, x450 Product Development Team Lead, Raleigh

Mauro Gatti, EMEA xSeries Solution Architects, Italy

Barney Hallman, Server Development, Austin

Jim Hanna, xSeries Server Development, Austin

Roger Hellman, xSeries Global Product Manager, Raleigh

William L. Jones, IBM xSeries Preloads, Raleigh

Michael S Lee, IBM Center for Microsoft Technologies, Seattle

Grace Lennil, IBM Center for Microsoft Technologies, Seattle

Cecil Lockett, Senior Engineer, Engineering Software, Raleigh

John McAbel, Datacenter/Cluster Product Manager, Beaverton

Chris McDermott, Linux Technology Center, IA-64 Enablement, Beaverton

Willie Nathan, Systems Management Firmware Development, Raleigh

Charles Perkins, Course Developer, Service and Support Education, Raleigh

David Pfeffer, Global Service Planner, Beaverton

Steve Powell, Technical Advisor, Service & Support Education Team, Raleigh

Ajit Ravani, Firmware Project Manager, Austin

Mike Schiskey, Technical Support, x450 Development, Raleigh

Al Thomason, Senior Product Marketing Manager, Beaverton

Damon A. West, IBM ^ Technology Enablement Center

Bob Zuber, x450 World Wide Product Manager, Raleigh

Preface xi

Page 14

Also, thanks to the following people from Intel:

Scott Diaz

Tim Farrell

Dave Myron

John F Stewart

Become a published author

Join us for a two- to six-week residency program! Help write an IBM Redbook

dealing with specific products or solutions, while getting hands-on experience

with leading-edge technologies. You'll team with IBM technical professionals,

Business Partners and/or customers.

Your efforts will help increase product acceptance and customer satisfaction. As

a bonus, you'll develop a network of contacts in IBM development labs, and

increase your productivity and marketability.

Find out more about the residency program, browse the residency index, and

apply online at:

ibm.com/redbooks/residencies.html

Comments welcome

Your comments are important to us!

We want our Redbooks to be as helpful as possible. Send us your comments

about this or other Redbooks in one of the following ways:

Use the online Contact us review redbook form found at:

ibm.com/redbooks

Send your comments in an Internet note to:

redbook@us.ibm.com

Mail your comments to:

IBM Corporation, International Technical Support Organization

Dept. HZ8 Building 662

P.O. Box 12195

Research Triangle Park, NC 27709-2195

xii IBM ^ xSeries 450 Planning and Installation Guide

Page 15

Chapter 1. Technical description

The IBM ^ xSeries 450 is the latest IBM top-of-the-line server and is the

first full implementation of the 64-bit IBM XA-64 chipset, code named “Summit”,

as part of the Enterprise X-Architecture strategy. The x450 completes the

xSeries product family, leveraging the proven Enterprise X-Architecture used in

the x440 to deliver commercially viable 64-bit systems.

The following are the key features of the x450:

One or two-way Intel Itanium 2 models, upgradable to four-way

1

4U rack-dense design

64 MB XceL4 Server Accelerator Cache providing an extra level of cache

1 GB or 2 GB RAM standard, up to 40 GB total using 512 MB, 1 GB, and

2 GB ECC SDRAM DIMMs

Memory enhancement such as memory mirroring, Chipkill™, and Memory

ProteXion

Six Active PCI-X slots: two 64-bit 133 MHz, two 64-bit 100 MHz, two 64-bit

66 MHz

Connectivity to an RXE-100 external PCI-X enclosure for an additional 12

PCI-X slots

Integrated dual-channel Ultra 320 SCSI controller

Two hot-swap 1” drive bays

© Copyright IBM Corp. 2003. All rights reserved. 1

Page 16

Support for major storage subsystems, including Fibre Channel and

ServeRAID™

Light path diagnostics and the Remote Supervisor Adapter for systems

management

Integrated dual 10/100/1000 Mbps Ethernet controller

1.1 The x450 product line

Powered by XA-64 Enterprise X-Architecture and 64-bit Itanium 2 “Madison”

processors, xSeries 450 servers bring the future of 64-bit processing and

production-level reliability to your data centers today. Featuring

mainframe-inspired, advanced mission-critical function, you can depend on these

four-way-capable enterprise servers to run your complex business applications

around the clock.

The models of the x450 that will be available on July 1 are listed in Table 1-1.

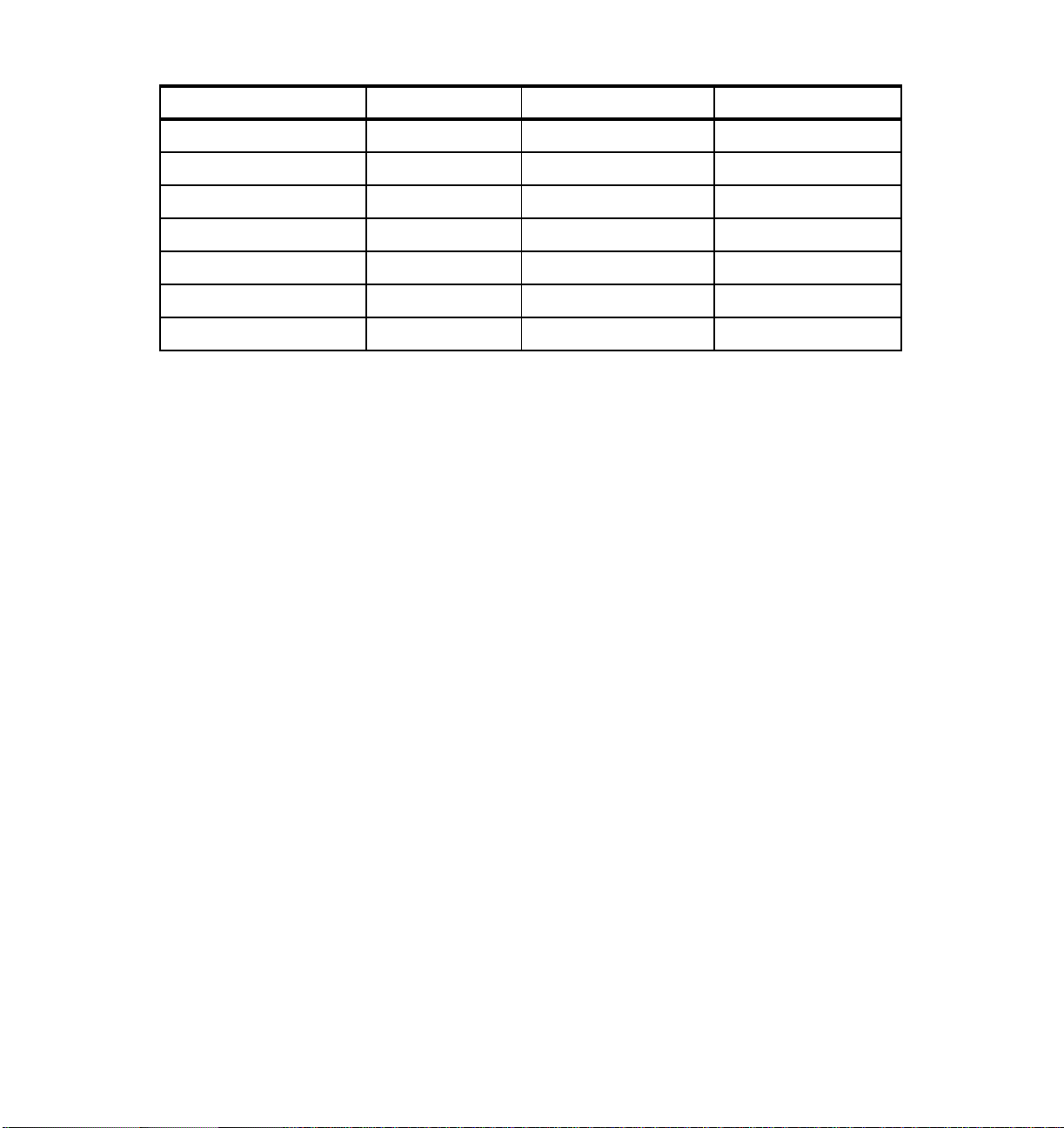

Table 1-1 Initial x450 models

Model Standard processors Max SMP L2 cache L3 cache Std memory

8688-4RX 1x 1.3 GHz Intel Itanium 2 4-way 256 KB 3 MB 1 GB (2x 512 MB)

8688-5RX 1x 1.4 GHz Intel Itanium 2 4-way 256 KB 4 MB 2 GB (4x 512 MB)

8688-6RX 1x 1.5 GHz Intel Itanium 2 4-way 256 KB 6 MB 2 GB (4x 512 MB)

IBM had ealier announced models that were based on the Itanium 2 “McKinley”

processor, but these have been withdrawn due to a bug in these processors.

These models are listed in Table 1-2.

Table 1-2 Withdrawn “McKinley” processor-based models

Model Standard processors Max SMP L2 cache L3 cache Std memory

8688-1RX 1x 900 MHz Intel Itanium 2 4-way 256 KB 1.5 MB 1 GB (2x 512 MB)

8688-2RX 2x 1.0 GHz Intel Itanium 2 4-way 256 KB 1.5 MB 2 GB (4x 512 MB)

8688-3RX 2x 1.0 GHz Intel Itanium 2 4-way 256 KB 3 MB 2 GB (4x 512 MB)

The x450 models support one, two, three, and four processors.

The attachment of a single RXE-100 Remote Expansion Enclosure is also

supported using either a single or two remote I/O cables. The RXE-100 has six

PCI-X slots standard, upgradable to 12 PCI-X slots, giving the customer up to a

total of 12 PCI-X or 18 PCI-X slots respectively.

2 IBM ^ xSeries 450 Planning and Installation Guide

Page 17

1.2 IBM XA-64 chipset

The IBM XA-64 chipset is the product name describing the chipset developed

under the code name “Summit” and implemented on the IA-64 platform. A

product of the IBM Microelectronics Division, the XA-64 chipset leverages the

proven Enterprise X-Architecture chipset used in the x440 and applies those

same technologies to the IA-64 architecture. The XA-64 chipset is composed of

the following components:

Memory controller: a single memory controller, code named “Cyclone”,

located within the memory-board assembly.

Processor/cache controller: a single processor and cache controller, code

named “Tornado”, located within the processor-board assembly.

PCI bridges: two PCI bridges, code named “Winnipeg”, per x450 located on

the PCI-X board and the I/O board that control both the PCI-X and Remote

I/O.

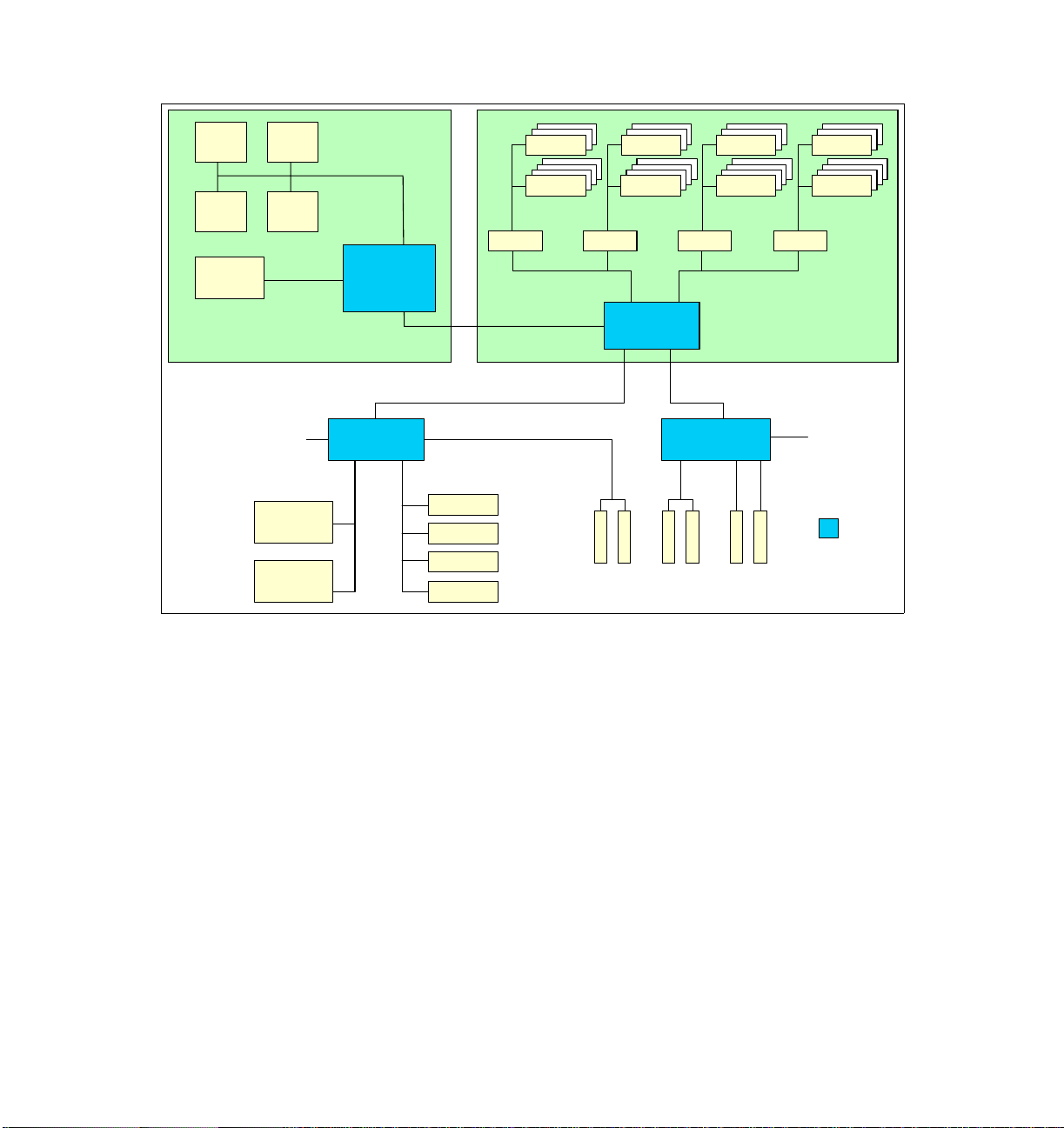

Figure 1-1 on page 4 shows the various IBM XA-64 components in an x450

configuration.

Chapter 1. Technical description 3

Page 18

CPU 1 CPU 2

6.4 GBps

CPU 3 CPU 4

400 MHz

64 MB

L4 cache

Processor-board assembly Memory-board assembly

6.4 GBps

RXE

Expansion

Port A

(1 GBps)

Processor &

cache

controller

PCI bridge PCI bridge

33 MHz66 MHz

SDRAM

SDRAM

SMI-E

3.2 GBps

SDRAM

SDRAM

SMI-E SMI-E SMI-E

Port 1

3.2 GBps

Memory

controller

Bus A66 MHz

B-100

Port 2

3.2 GBps

1 GBps1 GBps

SDRAM

SDRAM

SDRAM

SDRAM

200 MHz

2-way or 4-way

interleaved DDR

RXE

Expansion

Port B

(1 GBps)

D-133C-133

Ultra320

SCSI

Gigabit

Ethernet

Video

3x USB

Serial

RSA

Figure 1-1 xSeries 450 system block diagram

What was called the SMP Expansion module in the x440 has been divided into

two components in the x450. The component that contains the CPUs,

processor/cache controller, and cache is called the

The component that contains the memory controller and memory is called the

memory-board assembly.

The CPUs are connected together with a 200 MHz frontside bus, but supply data

at an effective rate of 400 MHz using the “dual-pump” design of the Intel

Itanium 2 architecture as described in 1.4, “Intel Itanium 2 processor” on

page 10. To ensure the processors are optimally used, the x450 has a 64 MB

XceL4 Server Accelerator Cache, comprised of 200 MHz DDR memory. This L4

system cache services all CPUs.

64-bit

66 MHz

IBM XA-64

64-bit

100 MHz

64-bit

133 MHz

("Summit")

core chipset

processor-board assembly.

4 IBM ^ xSeries 450 Planning and Installation Guide

Page 19

Memory used in the x450 is standard PC2100 ECC DDR SDRAM DIMMs. With

g

2 GB DIMMs, up to 40 GB can be installed using 20 of the 28 DIMM sockets. The

memory is two-way interleaved; however, four-way interleaving is also supported

in order to ensure that the memory subsystem can supply data fast enough to

match the throughput of the CPUs. Two-way interleaving means that DIMMs

must be installed in matched pairs and in specific DIMM sockets (see 3.1.2,

“Memory” on page 41)

The two PCI bridges in the XA-64 chipset provide support for 33, 66, 100, and

133 MHz devices using four PCI-X buses (labeled A-D in Figure 1-1 on page 4).

This is discussed further in 1.8, “PCI subsystem” on page 21.

The PCI bridge also has two 1 GBps bi-directional Remote Expansion I/O (RXE)

ports for connectivity to the RXE-100 enclosure. The RXE-100 provides up to an

additional 12 PCI-X slots and can be connected by a single cable to port A.

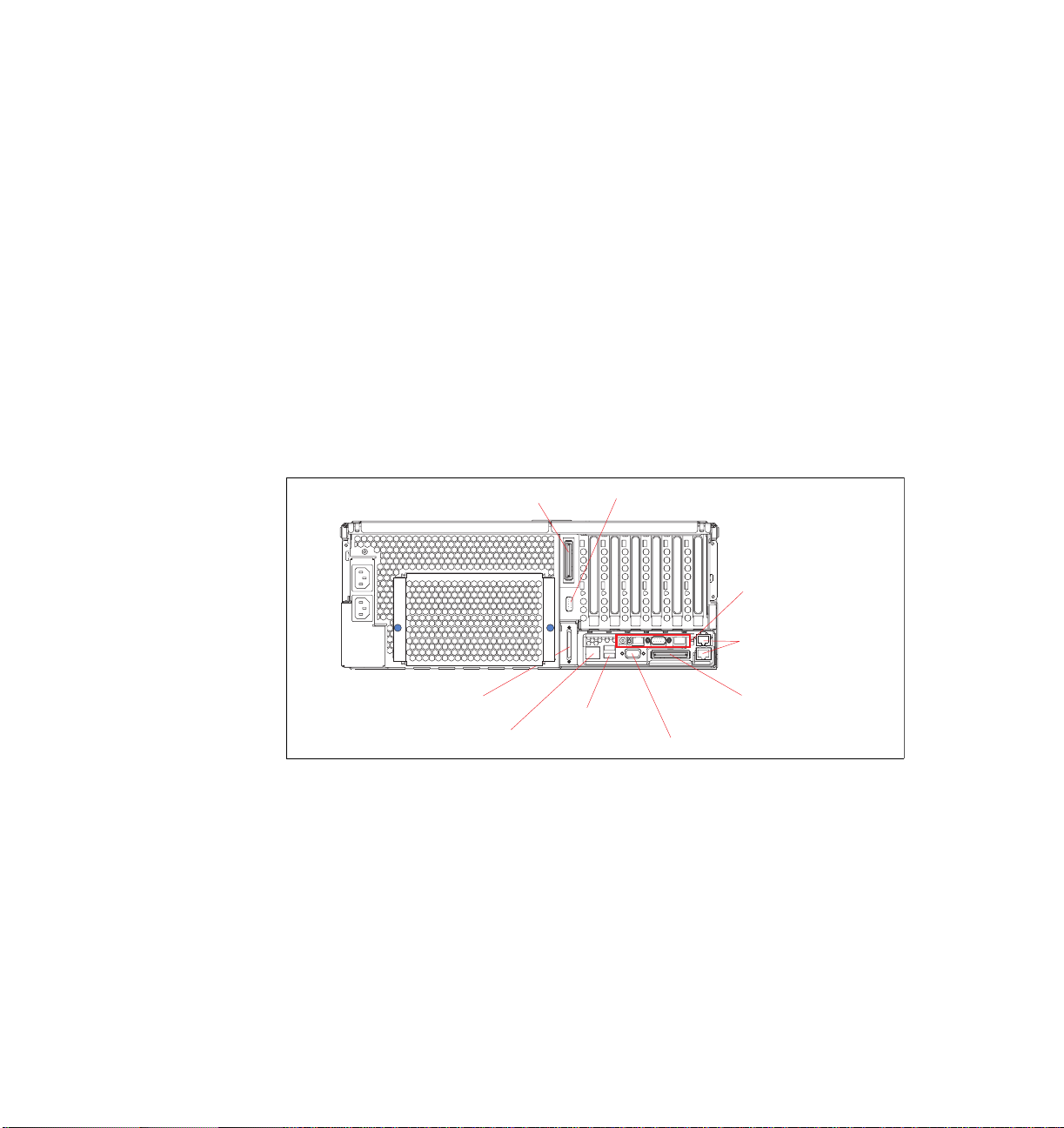

The rear panel of the x450, indicating the location of the RXE Expansion Ports, is

shown in Figure 1-2.

RXE Expansion Port (B)

connector

SCSI connector

USB ports

RXE Mana

Figure 1-2 Rear view of the x450

ement Port

1.3 Extensible Firmware Interface

The Extensible Firmware Interface (EFI) specification describes an interface

between the operating system and platform firmware as shown in Figure 1-3 on

page 6. The interface offers platform-related information to the operating system

as well as boot and runtime service calls that are available to the operating

system and OS loader. Together, these makes a well-defined environment for

booting the operating system and running pre-boot applications, such as

diagnostics and system setup.

Serial connector

Remote Supervisor

Adapter connectors

Gigabit Ethernet

connectors

RXE Expansion

Port (A) connector

Video connector

Chapter 1. Technical description 5

Page 20

In comparison to a BIOS-based, legacy system, the EFI is an additional layer

between the operating system and the firmware. In a legacy system, the OS

loader calls BIOS functions directly. Consequently, to provide a stable boot

environment, changes in the OS loader and the platform firmware must go

hand-in-hand.

Note: All operating systems supported on x450 are EFI-aware. The OS loader

communicates with the firmware and hardware through the EFI interface.

The primary goal of this specification is to provide an abstract model both for

operating system and hardware developers. With such a model in a place, OS

loader customizations are not required if there are changes in the platform

hardware or firmware (added new boot or input devices for instance). The EFI

breaks up a tight dependency between the operating system and the firmware,

thus speeding up the process of releasing the new products and introducing the

new features and functionality (both operating system and hardware).

Operating system

Legacy OS

loader

Platform-specific firm ware (BIOS)

Platform hardware

Figure 1-3 The EFI concept

EFI OS loader

EFI

Consider, for example, the situation where a new type of boot device, for example

a USB key, is to be implemented. First the BIOS would have to offer an option to

choose this new device for booting, then new USB key-specific functions would

have to be added to the firmware to support booting from a USB device, and

finally, the OS loader would have to be modified to use these functions.

6 IBM ^ xSeries 450 Planning and Installation Guide

Page 21

The same situation with the EFI would be dramatically simplified. The OS loader

calls unified (not vendor-specific) EFI API functions for booting. These functions

are not dependent on the boot device used, so when a new boot device type is

added to the platform and the firmware is modified to recognize it, the operating

system can immediately boot.

The EFI architecture is modular, extensible and offers backward compatibility for

the older systems by default. This means there is a way for non-EFI-aware

operating systems to communicate directly with system BIOS as shown in

Figure 1-3 on page 6.

Note: The EFI concept was originally introduced with Itanium

Architecture-based computers, but is not restricted to 64-bit platforms. There

is a gradual transition from BIOS to the EFI expected on the IA-32 platform as

well.

1.3.1 GUID Partition Table disk

The GUID Partition Table (GPT) was introduced as part of the EFI initiative.

Every disk is assigned a global unique identifier (GUID) to allow self-identification

of the disks. GPT replaces the older Master Boot Record (MBR) partitioning

scheme that has been common to PCs.

There are several reasons for introducing a new partitioning scheme:

MBR disks support only four partition table entries. If more partitions are

wanted, a secondary structure — an extended partition — is necessary.

Extended partitions are then subdivided into one or more logical disks. On

any given drive, only one extended partition can be present.

In theory, a GPT disk can have an unlimited number of partitions. The number

of partitions is limited only by the amount of space reserved for making

partition entries.

GPT disks use primary and backup partition tables for redundancy and

CRC32 fields for improved partition data structure integrity.

GPT disks can grow to a very large size. In theory, a GPT disk can be up to

64

2

logical blocks in length (logical blocks are typically 512 bytes). In practice,

the maximum is less. For example, Windows Server 2003 supports GPT disks

up to approximately 18 Exabytes in size.

For backward compatibility with legacy MBR disk tools, all GPT disks contain a

protective MBR. The protective MBR, beginning in sector 0, precedes the GUID

Partition Table on the disk and contains only one partition that appears to span

the disk. The legacy tools are not aware of GPT and do not know how to properly

access a GPT disk. The benefit of protective MBR is that these tools will view a

Chapter 1. Technical description 7

Page 22

GPT disk as having a single encompassing (possibly unrecognized) partition,

rather than mistaking the disk for one that is unpartitioned. That is why

GPT-partitioned disk appears to have MBR.

Note: GPT disks can be converted to MBR disks and vice versa only if all

existing partitioning is first deleted, with associated loss of data.

In general, the structure of any GPT disk is as shown in Figure 1-4. The

protective MBR is followed by a theoretically unlimited number of data partitions.

Protective

MBR

Figure 1-4 General GPT disk structure

Note: Currently, only 64-bit operating systems have the ability to read, write,

and boot from GPT disks. 32-bit operating systems do not have built-in

support for GPT disks.

The specification for GPT disk partitioning can be found in Chapter 16 of the

Extensible Firmware Interface (EFI) specification. This document is available at:

http://developer.intel.com/technology/efi/download.htm

1.3.2 EFI System Partition

A special partition on the GPT disk is EFI System Partition (ESP). It contains the

OS loader files of all installed operating systems. These files are stored in the

EFI directory. The ESP may also contain other files necessary to boot the

system, such as drivers.

Data partition(s)

Note: The EFI System Partition is shareable among all installed operating

systems. To support multiple operating system installations, create multiple

data partitions.

8 IBM ^ xSeries 450 Planning and Installation Guide

Page 23

An example directory structure for an EFI System Partition present on a hard disk

with SuSE and Windows Server 2003 installed is as follows:

\EFI

\Microsoft

\WINNT50

\EFIDrivers

\SuSE

\MSUtils

There can be only one ESP on a single disk. The size of the ESP is determined

using the following algorithm:

ESP = max(100 MB, min(1% of physical disk, 1GB))

In other words, the size of the ESP must be the larger of these two numbers, 100

MB or 1% of the physical disk size (up to 1 GB). For example, for an 18 GB disk,

the size of the ESP is 184 MB. The value 1% of the physical disk is calculated at

the time that the ESP is created and does not change if the disk is extended later

(for example, via RAID).

Note: Each bootable GPT disk must contain an EFI System Partition.

The ESP should be the first partition on the disk, right after protective MBR as

shown in Figure 1-5.

EFI

Protective

MBR

Figure 1-5 Boot GPT disk structure

System

Partition

(ESP)

Data partition(s)

The EFI specification supports only FAT or FAT32 on the ESP partition.

Note: The ESP is not visible to the operating systems users by default but can

be accessed for read/write operations from within the operating system by

special commands. For Windows-specific information, see “Accessing EFI

System Partition from Windows” on page 96. For SuSE information, see

“Partitions on IA-64 Linux” on page 111.

Chapter 1. Technical description 9

Page 24

1.3.3 EFI and legacy-free concept

The EFI complements legacy-free concept of PCs. Legacy-free refers to PC

system designs that eliminate certain hardware and firmware elements of the

original PC architecture while advancing the PC's stability and usability.

Specifically, we are talking about a set of I/O options that have been part of the

PC architecture for a very long time, for example parallel, serial and game port,

ISA slots or devices, floppy disk controller (FDC), PS/2® mouse, and keyboard.

BIOS interfaces require the OS loader to have a specific knowledge of the

workings of hardware devices. The EFI abstract concept makes it possible to

build code that works on a range of hardware devices without having explicit

knowledge of the specifics of these devices. This EFI feature allows a

replacement of legacy devices and adding new boot devices. The legacy devices

are replaced by USB devices in x450.

Tip: One key interface that is no longer supported is INT 13, disk I/O.

For more information about the EFI specification, see the following:

http://www.intel.com/technology/efi/index.htm

http://www.microsoft.com/hwdev/platform/firmware/EFI/default.asp

1.4 Intel Itanium 2 processor

The Itanium 2 processor used in the x450 (code named “Madison”) uses a ZIF

socket design, although the socket is designed differently from the one on the

x440, for example. This small form factor is what permits the x450 to have up to

four processors in a 4U node.

Table 1-3 outlines some of the differences between the Itanium and Itanium 2

processors (both the “Madison” and the earlier “McKinley” processor):

Table 1-3 Itanium vs Itanium 2 processors

Feature Itanium Itanium 2 “McKinley” Itanium 2 “Madison”

Processor core speed 733 or 800 MHz 900 MHz or 1.0 GHz 1.3, 1.4 or 1.5 GHz

L3 Cache 2 or 4 MB 1.5 or 3 MB 3, 4 or 6 MB

Frontside bus 266 MHz 400 MHz, 128 bit 400 MHz, 128 bit

Frontside bus bandwidth 2.1 GBps 6.4 GBps 6.4 GBps

Pipeline stages 10 8 8

10 IBM ^ xSeries 450 Planning and Installation Guide

Page 25

Feature Itanium Itanium 2 “McKinley” Itanium 2 “Madison”

Issue ports 9 11 11

on-board registers 328 328 328

Integer units 3 6 6

Branch units 3 3 3

Floating point units 2 2 2

SIMD units 2 1 1

Load and store units 2 (total) 2 load and 2 store 2 load and 2 store

The Itanium 2 processor has three levels of cache, all of which are on the

processor die:

Level 3 cache is equivalent to L2 cache on the Pentium III Xeon, or the L3

cache on the Pentium Xeon MP processor. Itanium 2 processors in the x450

models contain either 3, 4 or 6 MB of L3 cache. Unlike the design of the

original Itanium processor, this L3 cache is now on the processor die, greatly

improving performance, up or 2 times greater than that of the original Itanium.

Level 2 cache is equivalent to L1 cache on the Pentium III Xeon and is 256 KB

in size.

A new level 1 cache, 32 KB in size, is “closest” to the processor and is used to

store micro-operations (that is, decoded executable machine instructions) and

serves those to the processor at rated speed. This additional level of cache

saves decode time on cache hits.

The x450 also implements a Level 4 cache as described in 1.6, “IBM XceL4

Server Accelerator Cache” on page 17.

Intel has also introduced a number of features associated with its Itanium

micro-architecture. These are available in the x450, including:

400 MHz frontside bus

The Pentium III Xeon processor had a 100 MHz frontside bus that equated to

a burst throughput of 800 MBps. With protocols such as TCP/IP, this had been

shown to be a bottleneck in high-throughput situations. The Itanium 2

processor improves on this by using a single 200 MHz clock and using both

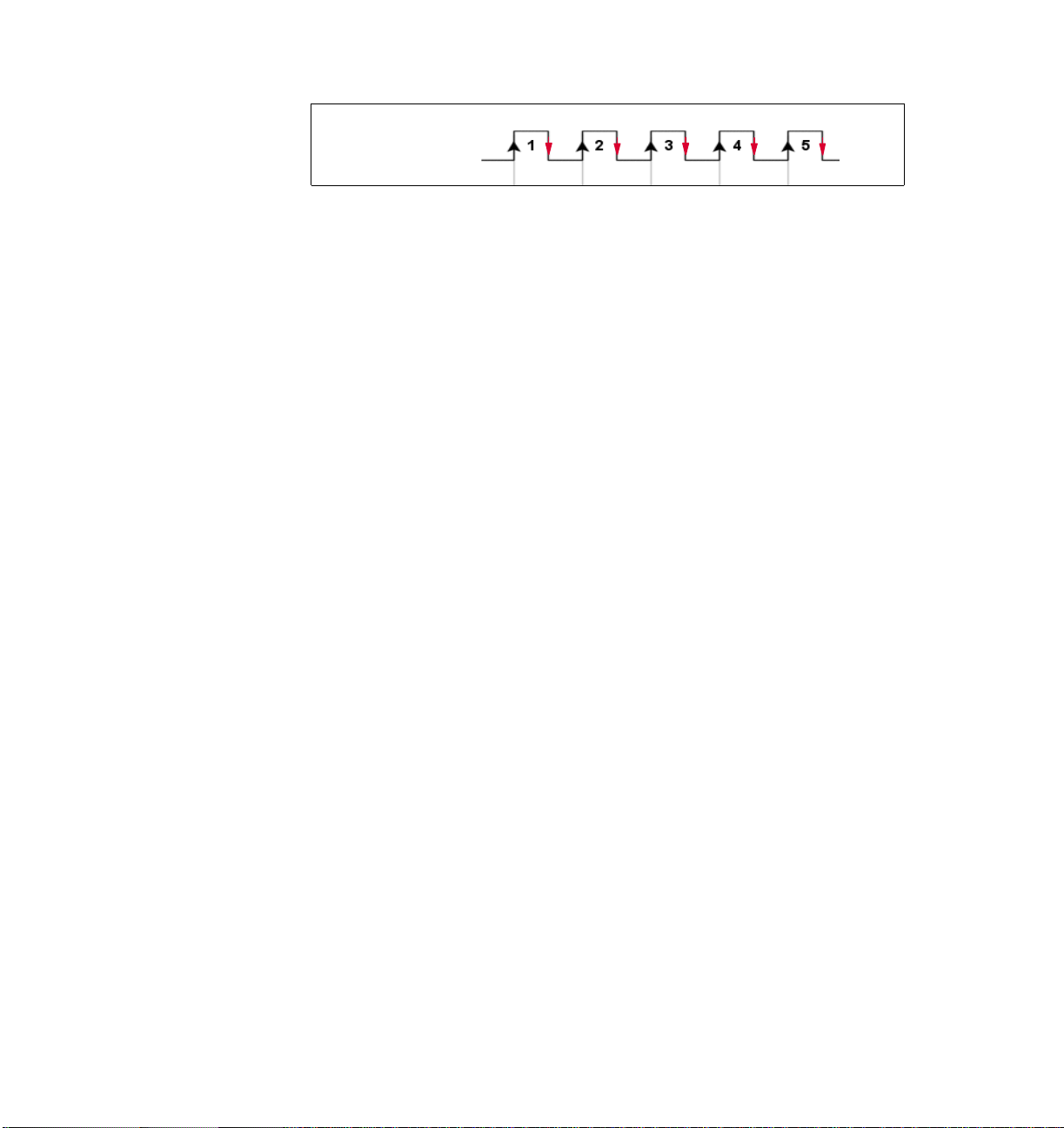

edges of each clock to transmit data. This is shown in Figure 1-6 on page 12.

Chapter 1. Technical description 11

Page 26

200 MHz clock

Figure 1-6 Dual-pumped frontside bus

This increases the performance of the frontside bus. The end result is an

effective burst throughput of 6.4 GBps (128-bit wide data path running at 400

MHz), which can have a substantial impact, especially on TCP/IP-based LAN

traffic. This is opposed to the Itanium processor, which had a burst throughput

of only 2.1 GBps (64-bit wide data path running at 266 MHz).

Explicitly Parallel Instruction Computing (EPIC)

EPIC technology, developed by Intel and HP, leads to more efficient, faster

processors because it eliminates numerous processing inefficiencies in

current processors and attacks the perennial data bottleneck problems by

increasing parallelism, rather than simply boosting the raw “clock” speed of

the processor.

Specifically, in today's 32-bit processors, much of the instruction

scheduling--the order in which computing instructions are executed--is done

on the chip itself, leading to a great deal of overhead and slowing down overall

processor performance. Moreover, today's processors are plagued by

instruction flow problems since the processor often has to stop what it's doing

and reconstruct the instruction flow due to inherent inefficiencies in instruction

handling.

EPIC makes the instruction scheduling more intelligent and handles much of

the scheduling off-chip, in the compiler program, before feeding “parallelized”

instructions to the Itanium 2 processor for execution. The parallelized

instructions allow the chip to process a number of instructions simultaneously,

increasing performance. A compiler prepares instructions for execution on the

processor.

The Itanium 2 architecture is based on EPIC technology and has the following

features:

– Provides faster online transaction processing

– Has the capability to execute multiple instructions simultaneously,

processing more data and allowing more users

– Enables faster calculations and data analysis

– Allows for faster storage and movement of large models (CAD, CAE)

– Speeds up simulation and rendering times

12 IBM ^ xSeries 450 Planning and Installation Guide

Page 27

For more information about the features of the Itanium 2 processor, go to:

http://www.intel.com/design/itanium2

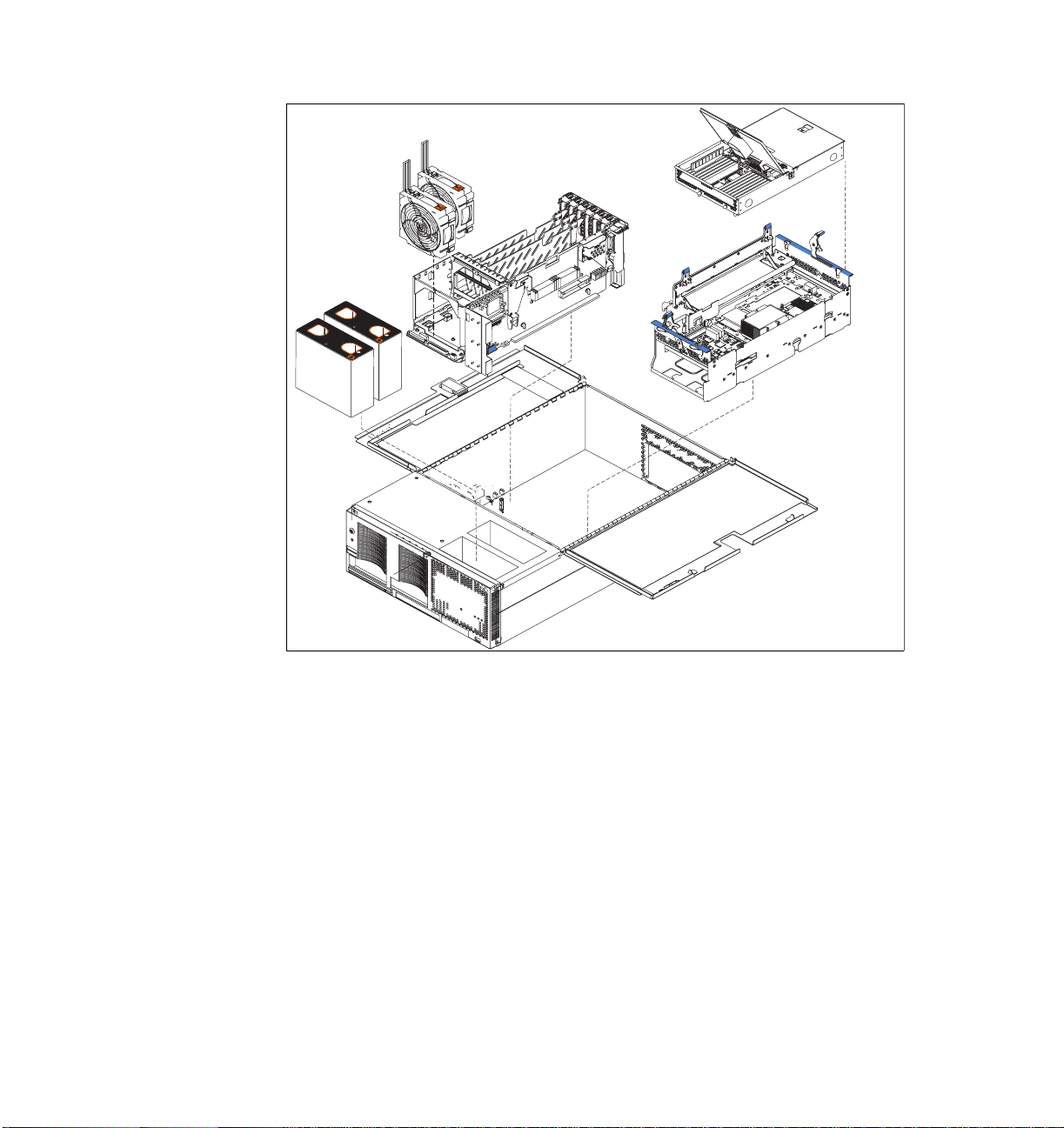

1.5 System assembly

Unlike the x440, then x450 does not use a single SMP Expansion Module, which

contains the processors, memory, XceL4 Server Accelerator Cache, and

respective controller. Instead, there are now two separate assemblies:

A single memory-board assembly, located at the top of the system, which

contains the physical DIMM’s as well as the memory and I/O controller

A single processor-board assembly, located at the bottom of the system,

which contains the processors, XceL4 Server Accelerator Cache, and L4

Cache/Scalability Controller

See Figure 1-7 on page 14 for the location of the memory-board and

processor-board assemblies.

Tip: Be careful when removing or installing either the memory-board

assembly or the processor-board assembly, because it is possible to damage

the midplane.

Chapter 1. Technical description 13

Page 28

Memory-board

assembly

PCI-X

slots

N

O

T

E

:

F

O

R

P

R

O

P

E

R

A

IR

F

L

O

W, R

E

P

L

A

N

O

T

E

:

F

C

E

F

A

F

N

R

F

O

R

P

R

O

R

O

N

T

O

F

W

O

I

N

T

T

H

O

IN

F

2

B

P

E

R

A

I

R

F

B

O

X

M

O

IN

X

U

T

E

L

O

W, R

E

S

P

L

A

C

E

F

A

N

W

I

T

H

IN

2

M

I

N

U

T

E

S

Processor-board

assembly

Figure 1-7 Memory-board and processor-board assembly locations

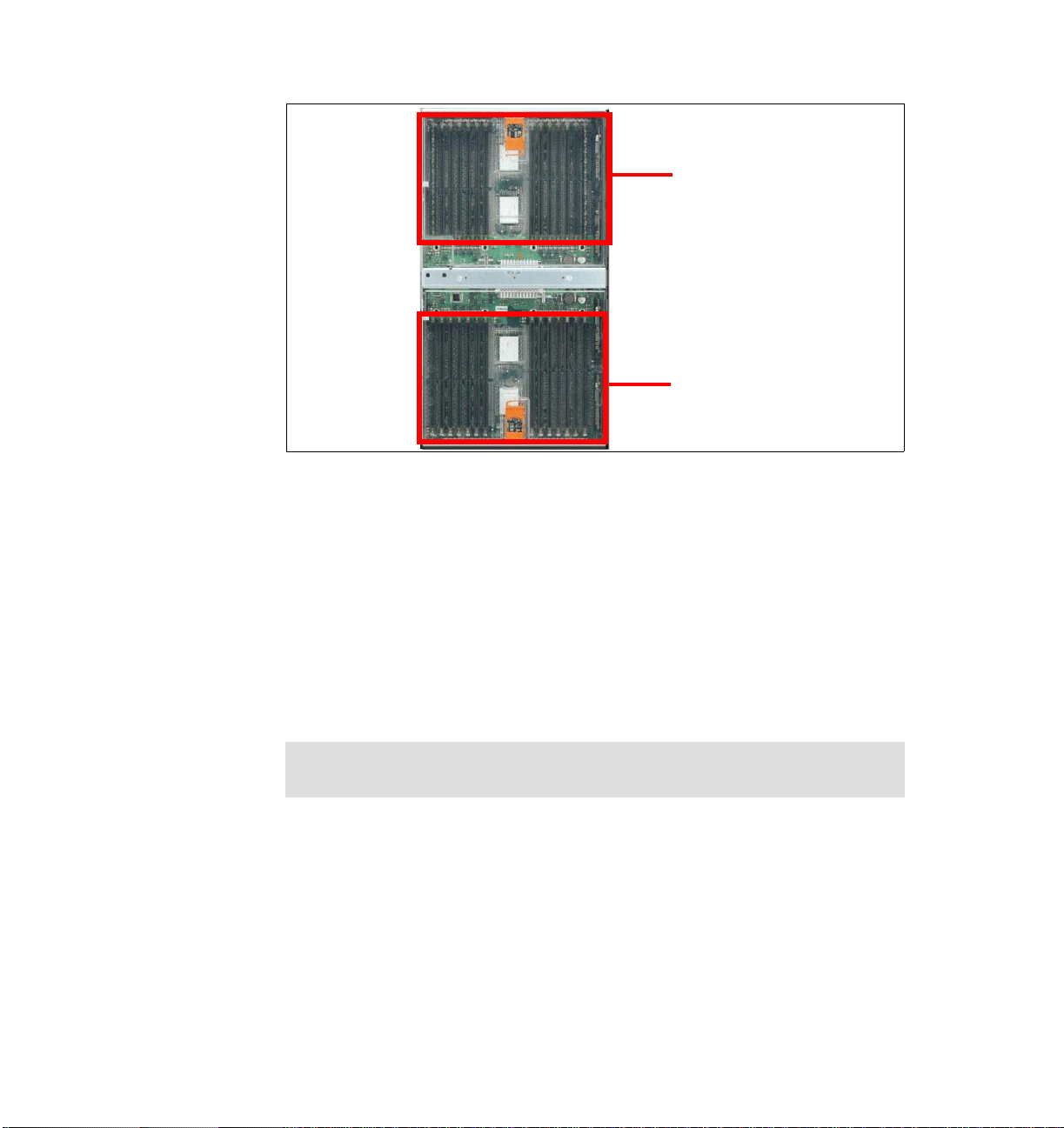

1.5.1 Memory-board assembly

The x450 memory-board assembly is installed from the top of the server and

mounts to the side of the midplane using two levers on the top. This location

allows for easy access to all memory DIMMs without having to remove any

components from the system.

14 IBM ^ xSeries 450 Planning and Installation Guide

Page 29

Memory Port 1

There are 14 DIMM slots in each

of the two ports, for a total of 28

DIMMs.

Memory Port 2

Figure 1-8 Memory-board assembly, showing the two memory ports

The memory-board assembly contains 28 DIMM slots. All DIMM slots can be

used when 512 MB or 1 GB DIMMs are used. If 2 GB DIMMs are used, up to 20

DIMMs slots can be used. The maximum installable memory is 40 GB (using 2

GB DIMMs).

The memory-board assembly is also equipped with LEDs for light path

diagnostics for each DIMM. In addition, the assembly is equipped with LEDs for

the following:

Power to memory port 1

Power to memory port 2

Hot-plug memory enabled

Restriction: The ability to hot-add or hot-replace memory is not available in

the x450.

For information about installing memory in the memory-board assembly, see

3.1.2, “Memory” on page 41.

1.5.2 Processor-board assembly

The x450 processor-board assembly is located under the memory-board

assembly, as shown in Figure 1-7 on page 14. It is installed from the top of the

server and mounts to the side of the midplane using two levers on the side, as

shown in Figure 1-9 on page 16.

Chapter 1. Technical description 15

Page 30

Tip: Be careful when removing or installing either the memory-board

assembly or the processor-board assembly, since it is possible to damage the

midplane.

Processors 1 & 3

(processors 2 &

4 are on the

underside of the

circuit board)

Power modules

(“pods”) for each

processor

Figure 1-9 Processor-board assembly

x450 models have either one or two processors installed. The unused CPU

sockets will hold metal air baffles. The power pods shown in Figure 1-9 supply

power to the processors and are equivalent to VRMs in other systems.

Important: While processors should be installed in the order listed in

Figure 1-9, the bootstrap processor (BSP) may not necessarily be the

processor located in Processor Socket 1. The Intel Itanium Architecture

processors are initialized and tested in parallel. The first processor to

complete initialization becomes the BSP.

The processor-board assembly is also equipped with LEDs for light path

diagnostics for the following components:

Each processor

Each power module (“pod”)

In addition, a “remind” button is located on the upper side of the processor-board

assembly. Pressing this button while the processor-board assembly is not

attached to AC power will illuminate any light path LEDs that had been lit while

the system was under power for a total of 10 seconds.

16 IBM ^ xSeries 450 Planning and Installation Guide

Page 31

1.6 IBM XceL4 Server Accelerator Cache

Integrated into the processor-board assembly is 64 MB of Level 4 cache, which is

shown in Figure 1-1 on page 4. This XceL4 Server Accelerator Cache provides

the necessary extra level of cache to maximize CPU throughput by reducing the

need for main memory access under demanding workloads, resulting in an

overall enhancement to system performance.

Cache memory is two-way interleaved 200 MHz DDR memory and is faster than

the main memory because it is directly connected to the memory controller and

does not have additional latency associated with the large fan-out necessary to

support the 28 DIMM slots. Since the data interface to the controller is 400 MHz,

peak bandwidth for the XceL4 cache is 6.4 GBps.

1.7 System memory

The x450 has 1 GB or 2 GB of RAM standard, depending on the model. Memory

packaging is PC2100 ECC DDR SDRAM DIMMs, and standard memory is either

two or four 512 MB DIMMs. Memory options are 512 MB, 1 GB, or 2 GB DIMMs.

There are a total of 28 DIMM sockets (two ports of 14). All 28 DIMM sockets can

be used to install DIMMs, with the exception of the 2 GB DIMM option. If 2 GB

DIMMs are installed, the total number of DIMM sockets that can be used is

limited to 20. A maximum of 40 GB of system memory is supported by populating

20 DIMM sockets each with a 2 GB DIMM.

DIMMs must be installed in matched pairs, since the DIMMs are two-way

interleaved. However, if memory is installed in matched fours (a matched pair in

each port), the system automatically detects this and will enable four-way

interleaving. With this, memory access is performed simultaneously from both

ports (two separate paths into the memory controller as shown in Figure 1-1 on

page 4), leading to improved memory performance.

See 3.1.2, “Memory” on page 41 for a further discussion of how memory is

implemented in the x450 and what you should consider before an x450

installation.

There are a number of advanced features implemented in the x450 memory

subsystem, collectively known as

Restriction: The ability to hot-add or hot-replace memory is not available in

the x450.

Active Memory:

Chapter 1. Technical description 17

Page 32

Memory ProteXion

Memory ProteXion, also known as “redundant bit steering”, is the technology

behind using redundant bits in a data packet to provide backup in the event of

a DIMM failure.

Currently, other industry-standard servers use 8 bits of the 72-bit data packets

for ECC functions and the remaining 64 bits for data. However, the x450 uses

an advanced ECC algorithm that is based not on bits but on memory symbols.

Symbols are groups of multiple bits, and in the case of the x450, each symbol

is 4 bits wide. With two-way interleaved memory, the algorithm needs only

three symbols to perform the same ECC functions, thus leaving one symbol

free (2 bits on each DIMM). See Figure 1-10.

C0S1 S2

C0S1 S2

C0S1 S2

C1

C1

C2

C2

C2

C1

K1

K1

K1

S0

S0

S0

S16

S16

S16

S17 S18

S17 S18

S17 S18

S3 S4

S3 S4

S3 S4

S19 S20

S19 S20

S19 S20

S5 S6

S5 S6

S5 S6

S21 S22

S21 S22

S21 S22

S7

S7

S7

S23

S23

S23

S8

S8

S8

S24

S24

S24

S9

S9

S9

S25

S25

S25

S10

S10

S10

S26

S26

S26

S11

S11

S11

S27

S27

S27

S12

S12

S12

S28

S28

S28

S13

S13

S13

S29

S29

S29

S14

S14

S14

S30

S30

S30

S15

S15

S15

S31

S31

S31

S32C3S33 S34

S32C3S33 S34

S32C3S33 S34

S49 S50

S49 S50

S49 S50

S48

S48

S48

S35 S36

S35 S36

S35 S36

S51 S52

S51 S52

S51 S52

S37 S38

S37 S38

S37 S38

S53 S54

S53 S54

S53 S54

S39

S39

S39

S55

S55

S55

S40

S40

S40

S56

S56

S56

S41

S41

S41

S57

S57

S57

S42

S42

S42

S58

S58

S58

S43

S43

S43

S59

S59

S59

S44

S44

S44

S60

S60

S60

S45

S45

S45

S61

S61

S61

S46

S46

S46

S62

S62

S62

S47

S47

S47

S63

S63

S63

C4

C4

C4

C5

C5

C5

K2

K2

K2

Figure 1-10 Memory ProteXion

In the event that a chip failure on the DIMM is detected by memory scrubbing,

the memory controller can re-route data around that failed chip through the

spare symbol (similar to the hot-spare drive of RAID array). It can do this

automatically without issuing a Predictive Failure Analysis® (PFA) or light

path diagnostics alert to the administrator. After the second DIMM failure, PFA

and light path diagnostics alerts would occur on that DIMM as normal.

Memory scrubbing

Memory scrubbing is an automatic daily test of all the system memory that

detects and reports memory errors that might be developing before they

cause a server outage.

Memory scrubbing and Memory ProteXion work in conjunction with each

other, but they do not require memory mirroring (as described below) to be

enabled to work properly.

When a bit error is detected, memory scrubbing determines if the error is

recoverable or not. If it is recoverable, Memory ProteXion is enabled and the

data that was stored in the damaged locations is rewritten to a new location.

The error is then reported so that preventative maintenance can be

performed.

As long as there are enough good locations to allow the proper operation of

the server, no further action is taken other than recording the error in the error

18 IBM ^ xSeries 450 Planning and Installation Guide

Page 33

logs. Errors from scrubbing are not reported unless bit steering has already

been invoked.

If the error is not recoverable, then memory scrubbing sends an error

message to the light path diagnostics, which then turns on the proper lights

and LEDs to guide you to the defective DIMM. If memory mirroring is enabled,

then the mirrored copy of the data in the damaged DIMM is used until the

system is powered down and the DIMM replaced.

Memory mirroring

Memory mirroring is roughly equivalent to RAID-1 in disk arrays, in that

memory is divided in two ports and one port is mirrored to the other half (see

Figure 1-11). If 8 GB is installed, then the operating system sees 4 GB once

memory mirroring is enabled (it is disabled in BIOS by default). All mirroring

activities are handled by the hardware without any additional support required

from the operating system.

Por t 1 Port 2

Front of server

Figure 1-11 Memory DIMMs are divided into two ports

When memory mirroring is enabled (see “Enabling memory mirroring” on

page 83), the data that is written to memory is stored in two locations. One

copy is kept in the port 1 DIMMs, while a second copy is kept in the port 2

DIMMs.

During the execution of the read command, the data is read simultaneously

from both ports, and error-free data from either port is forwarded. This

Chapter 1. Technical description 19

Page 34

provides an extra level of error recovery capability. (In the x440, the read

command is read from the DIMM with the least amount of reported memory

errors through memory scrubbing).

If memory scrubbing determines the DIMM is damaged beyond use, read and

write operations are redirected to the partner DIMM in the other port. Memory

scrubbing then reports the damaged DIMM and the light path diagnostics

display the error. If memory mirroring is enabled, then the mirrored copy of the

data in the damaged DIMM is used until the system is powered down and the

DIMM replaced.

Certain restrictions exist with respect to placement and size of memory

DIMMs when memory mirroring is enabled. These are discussed in “Memory

mirroring” on page 42.

Chipkill memory

Chipkill is integrated into the XA-64 chipset and does not require special

Chipkill DIMMs. Chipkill corrects multiple single-bit errors to keep a DIMM

from failing. When combining Chipkill with Memory ProteXion and Active

Memory, the x450 provides very high reliability in the memory subsystem.

Chipkill memory is approximately 100 times more effective than ECC

technology, providing correction for up to 4 bits per DIMM, whether on a single

chip or multiple chips.

If a memory chip error does occur, Chipkill is designed to automatically take

the inoperative memory chip offline while the server keeps running. The

memory controller provides memory protection similar in concept to disk array

striping with parity, writing the memory bits across multiple memory chips on

the DIMM. The controller is able to reconstruct the “missing” bit from the failed

chip and continue working as usual.

Chipkill support is provided in the memory controller and implemented using

standard DIMMs, so it is transparent to the operating system.

In addition, to maintain the highest levels of system availability, if a memory error

is detected during POST or memory configuration, the server can automatically

disable the failing memory bank and continue operating with reduced memory

capacity. You can manually re-enable the memory bank after the problem is

corrected via the Setup menu in BIOS.

20 IBM ^ xSeries 450 Planning and Installation Guide

Page 35

Memory mirroring, Chipkill, and Memory ProteXion provide multiple levels of

redundancy to the memory subsystem. Combining Chipkill with Memory

ProteXion enables up to two memory chip failures per memory port (14 DIMMs)

on the x450. An x450 with its two memory ports could sustain up to four memory

chip failures. Memory mirroring provides additional protection with the ability to

continue operations with memory module failures.

1. The first failure detected by the Chipkill algorithm on each port doesn’t

generate a light path diagnostics error, since Memory ProteXion recovers

from the problem automatically.

2. Each memory port could then sustain a second chip failure without shutting

down.

3. Provided that memory mirroring is enabled, the third chip failure on that port

would send the alert and take the DIMM offline, but keep the system running

out of the redundant memory bank.

1.8 PCI subsystem

As shown in Figure 1-12 on page 22, there are six PCI-X slots internal to the

x450:

Two 133 MHz slots, which accept 32-bit or 64-bit, 3.3 V, PCI or PCI-X

adapters, from 33-133 MHz

Two 100 MHz slots, which accept 32-bit or 64-bit, 3.3 V, PCI or PCI-X

adapters, from 33-100 MHz

Two 66 MHz slots, which accept 32-bit or 64-bit, 3.3 V, 33 or 66 MHz, PCI or

PCI-X adapters

Chapter 1. Technical description 21

Page 36

PCI-X slot 3

(100 )MHz

PCI-X slot 2

(66 )MHz

PCI-X slot 1

(66 )MHz

PCI-X slot 5

(133 )MHz

PCI-X slot 6

(133 MHz)

Bus: D B AC

Figure 1-12 PCI slot information

PCI-X slot 4

(100 )MHz

Back of server

See 3.1.3, “PCI slot configuration” on page 44 for details on what adapters are

supported and in what combinations.

The PCI subsystem also supplies these I/O devices:

Two Wide Ultra320 SCSI ports, one internal and one external (LSI

LSI53C1030 chipset). This SCSI controller supports both single disks and

RAID-1 mirrored pairs of disks.

Dual Gigabit Ethernet ports (Broadcom 5704 chipset).

The x450 includes a dual-port Broadcom BCM5704 10/100/1000 Base-T

MAC (Media Access Controller) on a PCI 64-bit 66 MHz bus.

The BCM5704 supports full and half-duplex performance at all speeds

(10/100/1000 Mbps, auto-negotiated) and includes integrated on-chip

memory for buffering data transmissions to ensure the highest network

performance and dual onboard RISC processors for advanced packet parsing

and backwards compatibility with today's 10/100 network. The Broadcom

controller also includes software support for failover, layer-3 load balancing,

and comprehensive diagnostics.

Category 5 or better Ethernet cabling is required with RJ-45 connectors. If

you plan to implement a Gigabit Ethernet connection, ensure your network

infrastructure is capable of the necessary throughput to match the server’s I/O

capacity.

SVGA with 8 MB video memory (ATI RageXL chipset).

22 IBM ^ xSeries 450 Planning and Installation Guide

Page 37

Three USB ports (one on the front panel, two on the rear). All USB ports are

2.0 compliant.

One RS-232 serial port, located on the rear of the machine.

Remote Supervisor Adapter (RS-485 ASM interconnect bus, 10/100 Ethernet

and serial ports).

Note: There are no PS/2 keyboard or mouse ports on the x450. USB

keyboard and mice are supported, as well as serial connections via the

integrated serial port.

If you require KVM support the 1.5 M USB Conversion Option (UCO) (part

number 73P5832) enables the x450 to be attached to one of the Advanced

Connectivity Technology (ACT) switches for common management within the

rack. This smart cable is plugged into the USB and video ports on the server.

It converts KVM signals to CAT5 signals for transmission over a CAT5 cable to

either a Remote Console Manager (RCM) or Local Console Manager (LCM).

USB servers can be managed on the same set of switches as legacy

PS/2-based or C2T-based KVM servers.

With the addition of an RXE-100 Remote Expansion Enclosure, you can connect

an additional six or 12 PCI-X adapters to the x450. See 3.2.2, “Remote

Expansion Enclosure” on page 51 for details.

Note: Currently, only one RXE-100 can be connected to an x450 configuration.

1.9 Redundancy

The x450 has the following redundancy features to maintain high availability:

Four hot-swap multi-speed fans

With four hot-swap redundant fans, the x450 has adequate cooling for each of

its major component areas. There are two fans located at the front of the

server that direct air through the memory-board assembly and

processor-board assembly. These fans are accessible from the top of the

server without having to open the system panels. In the event of a fan failure,

the other fan will speed up to continue to provide adequate cooling until the

fan can be hot-swapped by the IT administrator.

The other two fans are located just behind the power supplies and provide

cooling for the I/O devices. Similar to the SMP Expansion Module fans, these

fans will speed up in the event that one should fail to compensate for the

reduction in air flow. In general, failed fans should be replaced within 24 hours

following failure.

Chapter 1. Technical description 23

Page 38

The four fans are shown in Figure 1-7 on page 14.

Important: Due to airflow requirements, fans should not be removed for

longer than two minutes. The fan compartments need to be fully populated

even if the fan is defective. Therefore, remove a defective fan only when a

new fan is available for immediate replacement.

Two hot-swap power supplies with separate power cords.

Note: For large configurations, redundancy is achieved only when connected

to a 220 V power supply. See 3.5, “Power considerations” on page 63 for

details.

Note: To ensure adequate power, a UPS with a rating of RMB 5000 or

more is recommended.

Two hot-swap hard disk drive bays. Using the onboard LSI chipset, these

drives can be configured to form a RAID-1 disk array for the operating system.

The memory subsystem has a number of redundancy features, including

memory mirroring, as described in 1.7, “System memory” on page 17.

The layout of the front panel of the x450, showing the location of the drive bays,

power supplies and fans, is shown in Figure 1-13.

Power-on light

Power button

Reset button

Hot swap

power supplies

Hot swap

drive bays

Blank media

bay

DVD/CD-RW drive

Light Path Diagnostics

panel (pulls out)

Figure 1-13 Front panel of the xSeries 450

24 IBM ^ xSeries 450 Planning and Installation Guide

Hot-swap fans

USB port

System-error light (amber)

Information light (amber)

SCSI activity light (green)

Locator light (blue)

Page 39

1.10 Light path diagnostics

CPU

VRM

M

E

M

O

R

Y

DASD

NMI

BOAR

D

EVENT LOG

FAN

POWER

SUPPLY

PC

I B

US

2

1

NON RED

OVER SPE

C

TE

MP

RE

MIND

To limit the need to slide the server out of the rack to diagnose problems, a light

path diagnostics panel has been incorporated in the front of the x450, as shown

in Figure 1-14. This panel can be ejected from the server to view all light path

diagnostics-monitored server subsystems. In the event that maintenance is then

required, the customer can slide the server out from the rack and, using the

LEDs, find the failed or failing component.

As illustrated in Figure 1-14, light path diagnostics is able to monitor and report

on the health of CPUs, main memory, hard disk drives, PCI-X and PCI slots, fans,

power supplies, VRMs, and the internal system temperature.

i

!

CPU

MEMORY

DASD

PCI-X BUS

FAN

1

POWER

SUPPLY

2

TEMP

Light Path

Diagnostics™

NMI

BOARD

EVENT LOG

VRM

NON REDUND

OVER SPEC

REMIND

Figure 1-14 Light path diagnostics panel on the x450

Important: If a light path diagnostics LED has been illuminated and system

power is removed, there is no way to redisplay the LEDs on the system tray

without re-applying AC power. If the fault has not been rectified when power is

restored, the LED will re-light.

The light path diagnostics on the x450 has four levels:

1. The first level is the front panel fault LED.

2. Level 2 is the pop-out panel as shown in Figure 1-14.

3. For further investigation, there are light path diagnostics LEDs visible through

the top of the server. This requires the server to be slid out of the rack.

Chapter 1. Technical description 25

Page 40

4. For the fourth level of diagnostics, LEDs on major system components

indicate the component causing the error.

As the processor-board assembly is not visible during normal operation, a light

path diagnostics button has been incorporated into it to assist with diagnosing

errors. You can light up the LEDs for a maximum of 2 minutes. After that time, the

circuit that powers the lights is exhausted.

The pop-out panel (Figure 1-14 on page 25) also has a remind button. This

places the front panel system-error LED into remind mode, which means it

flashes briefly every 2 seconds. By pressing the button, you acknowledge the

failure but indicate that you will not take immediate action. If a new failure occurs,

the system-error LED will turn on again and no longer blink. The system-error

LED remains in the remind mode until one of the following situations occurs:

All known problems are resolved

The system is restarted

A new problem occurs, at which time it then is illuminated continuously

Tip: The remind button on the pop-out LPD panel does not function when AC

power has been removed from the system. The button is just used to

acknowledge a system error as described above.

1.11 Remote Supervisor Adapter

The x450 includes a Remote Supervisor Adapter (RSA), which is positioned

horizontally in a dedicated PCI slot beneath the PCI-X adapter area of the

system.

Rear of x450

External power

supply

Error LED

(amber)

Figure 1-15 Remote Supervisor Adapter connectors

26 IBM ^ xSeries 450 Planning and Installation Guide

ASM interconnect

(RS-485) port

Power LED

(green)

10/100

Ethernet port

Management

COM port

Page 41

The Remote Supervisor Adapter offers the following capabilities:

In-band and out-of-band remote server access and alerting through IBM

Director

Full Web browser support with no other software required

Enhanced security features

Graphics/text console redirection for remote control

Dedicated 10/100 Ethernet access port

ASM interconnect bus for connection to other service processors

Serial dial in/out

E-mail, pager and SNMP alerting

Event log

Predictive Failure Analysis on memory, power, hard drives, and CPUs

Temperature and voltage monitoring with settable threshold

Light path diagnostics

Automatic Server Restart (ASR) for operating system and POST

Wake on LAN®

Remote firmware update

LAN access

Alert forwarding

See the IBM Redbook

Director

, SG24-6188 for more information on the Remote Supervisor Adapter.

Implementing Systems Management Solutions using IBM

1.12 Operating system support

In line with the overall message of providing application flexibility to meet the

varying needs of our enterprise customers, the x450 is optimized for several

operating system and application solutions. Table 1-4 lists the supported

operating systems for the x450. For the latest operating system support

information, go to:

http://www.pc.ibm.com/us/compat/nos/matrix.shtml

Note: Hyper-Threading is not available on systems with the Itanium 2

processor.

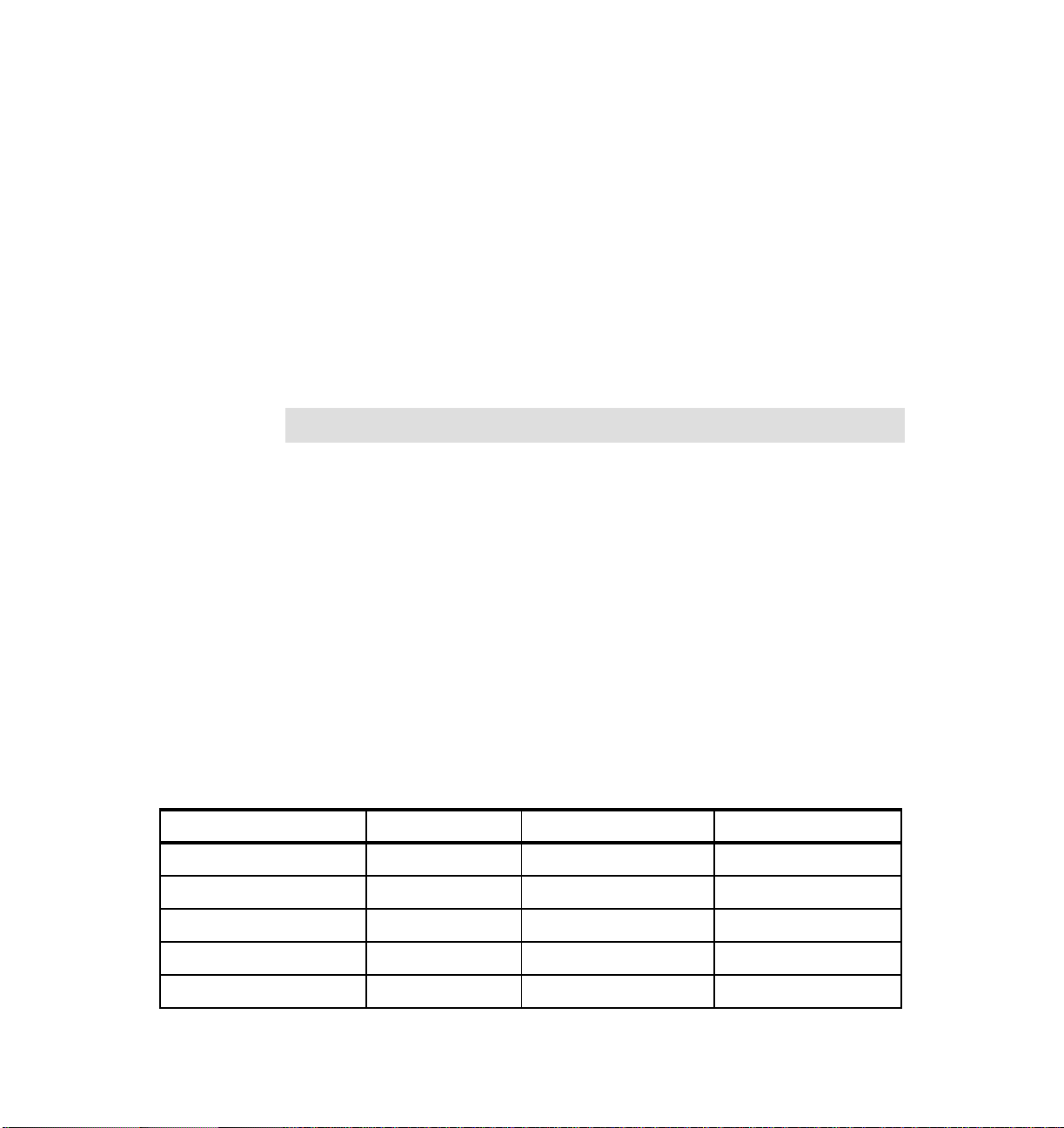

Table 1-4 x450 operating system support

Description Release SMP support

Windows Server 2003 Enterprise (64-bit) Supports up to four-way

SuSE Linux Enterprise Server 8.x Supports up to four-way

Chapter 1. Technical description 27

Page 42

Note: While operating systems may support large systems, scalability is a

function of both the operating system and the application/workload. Few

applications are designed to take advantage of larger SMP systems.

28 IBM ^ xSeries 450 Planning and Installation Guide

Page 43

Chapter 2. Positioning

In this chapter we discuss topics that help you to understand how the x450 can

be useful for your business. The topics covered are:

x450 application solutions

Why choose x450?

2

© Copyright IBM Corp. 2003. All rights reserved. 29

Page 44

2.1 x450 application solutions

With the x450 in the IA-64 environment, you are ready to deploy even larger

implementations of enterprise solutions.

As companies' performance demands grow, 64-bit technology becomes an

increasingly attractive option, due to increased memory addressability and true

parallel architecture. There are a number of ways the x450 can be deployed in

specific application solution environments. These include:

Database applications

Business logic

e-business and security transactions

In-house developed compute-intensive applications

Science and technology

Solutions

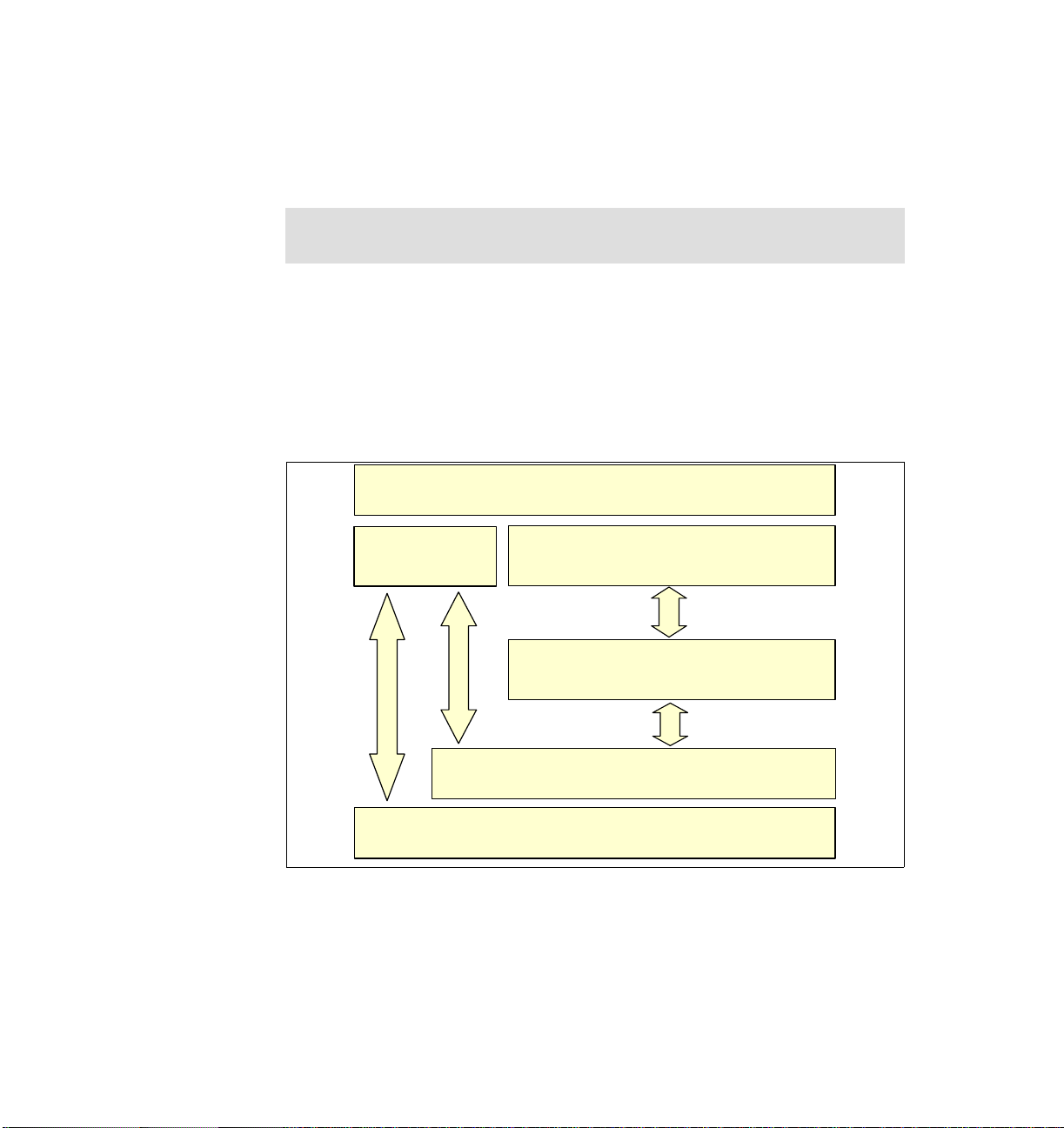

e-Business

Database applications

Figure 2-1 xSeries 450-based solutions

BI/ERP/SCM/CRM

Operating system

xSeries 450

2.1.1 Database applications

Four-way x450 configurations can be used as database servers and application

servers providing a highly available platform. These configurations require an

external storage enclosure or SAN, depending on the size of the database that is

driven by the number of users.

30 IBM ^ xSeries 450 Planning and Installation Guide

applications

In-house developed

technology

Science and

Page 45

Database applications with memory-sensitive workloads that require working

data sets larger than 4 GB to be loaded in memory will benefit from the larger

memory support of the 64-bit platform.

The following is an example from the field. Microsoft SQL Server Enterprise

Edition uses AWE memory only for the buffer pool. The AWE (Advanced

Windowing Extensions) API allows applications that are written to use the AWE

API to access more than 4 GB of RAM (basically anything between 4 GB and 64