Page 1

PPC750FX Evaluation Board

User’s Manual

SA14-2720-00

Title Page

Preliminary

June 10, 2003

Page 2

®

© Copyright International Business Machines Corporation 2002, 2003

All Rights Reserved

Printed in the United States of America June 2003

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or

both:

IBM PowerPC Architecture PPC750FX

IBM logo PowerPC Embedded Controllers RISCTrace

PowerPC PowerPC logo RISCWatch

Other company, product, and service names may be trademarks or service marks of others.

The information contained in this document is subject to change or withdrawal at any time without notice and is

being provided on an "AS IS" basis without warranty or indemnity of any kind, whether express or implied,

including without limitation, the implied warranties of non-infringement, merchantability, or fitness for a

particular purpose. Any products, services, or programs discussed in this document are sold or licensed under

IBM's standard terms and conditions, copies of which may be obtained from your local IBM representative.

Nothing in this document shall operate as an express or implied license or indemnity under the intellectual

property rights of IBM or third parties.

Without limiting the generality of the foregoing, any performance data contained in this document was

determined in a specific or controlled environment and not submitted to any formal IBM test. Therefore, the

results obtained in other operating environments may vary significantly. Under no circumstances will IBM be

liable for any damages whatsoever arising out of or resulting from any use of the document or the information

contained herein.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be

relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

Note: This document contains information on products in the sampling and/or initial production phases of

development. This information is subject to change without notice. Verify with your IBM field applications

engineer that you have the latest version of this document before finalizing a design.

IBM Microelectronics Division

1580 Route 52, Bldg. 504

Hopewell Junction, NY 12533-6351

The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.ibm.com/chips

750FXebm_title.fm

June 10, 2003

Page 3

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

Contents

Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

About This Book . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.1 PowerPC 750FX RISC Microprocessor Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.2 Board Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2. Board Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.1 Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2 Board Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.3 Internal Processor Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.4 System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.5 SDRAM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.6 PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.7 Ethernet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.8 Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.9 NVRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.10 SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.11 Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.12 Logic Analyzer Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.13 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.13.1 PCI Voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.13.2 System Controller Voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.13.3 PPC750FX Voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.13.4 SDRAM Voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.14 Form Factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3. Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.1 CPLD Register Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4. Programming the System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.1 DDR SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.1.1 SDRAM Controller Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.2 Device Controller Bank Register Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.2.1 Device Bank 0 Parameters (32-bit Flash) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.2.2 Device Bank 1 Parameters (CPLD registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

750FXebmTOC.fm

June 10, 2003

Contents

Page 3 of 115

Page 4

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

4.2.3 Device Bank 2 Parameters (UARTs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.2.4 Device Bank 3 Parameters (FRAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.2.5 Boot Device Parameters (8 bit flash and SRAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5. Reset and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.1 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6. Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.1 Reset Pushbutton . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.2 ATX Power-on Pushbutton . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

6.3 CPU 0 PLL Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

6.4 CPU 1 PLL Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.5 System Controller Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7. Fuses, Batteries, Regulators, and Fans . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.1 On-Board Current Monitoring and Variable Voltage Testing . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.1.1 1.45V Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.1.2 2.5V Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.2 Fan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

8. Displays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9. Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

9.1 Write-Protect 32-Bit Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.2 Ignore Fan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.3 PCI Interrupt Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

10. Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

10.1 Auxiliary Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

10.2 Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

10.3 Fan Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

10.4 RISCWatch JTAG Debugger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

10.5 Ethernet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

10.6 PCI Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

10.7 CPLD JTAG Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

10.8 Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

10.9 System Controller Device Address Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.10 Memory Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

10.11 External Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

10.12 Test Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Contents

Page 4 of 115

750FXebmTOC.fm

June 10, 2003

Page 5

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

11. CPLD Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

11.1 Programming—Registers and Control Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

11.1.1 I/O Pin List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

11.1.2 CPLD Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

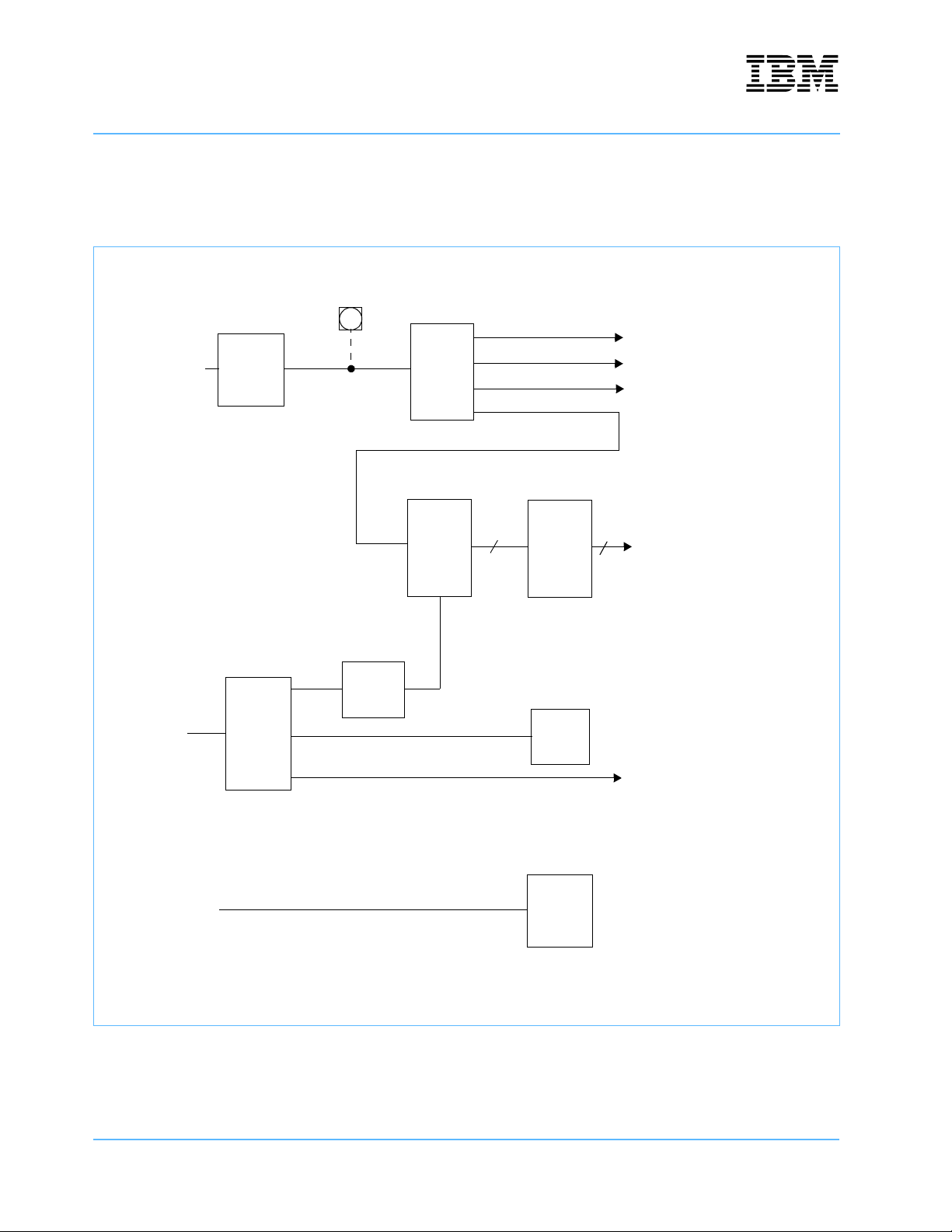

11.1.2.1 Top Level Block Diagram 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

11.1.2.2 Top Level Block Diagram 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

11.1.2.3 framcs Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

11.1.2.4 decode_block Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

11.1.2.5 registers2 Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

11.1.2.6 reset_block Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

11.1.2.7 misc Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

11.2 Timing—Registers and Control Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

11.2.1 Maximum Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

11.2.2 Clock-to-Output Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

11.2.3 Pin-to-Pin Signal Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

11.2.4 Setup and Hold Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

12. Bills of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

12.1 Component Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

12.2 Debugging Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

12.3 Auxiliary Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

12.4 Board Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Revision Log . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

750FXebmTOC.fm

June 10, 2003

Contents

Page 5 of 115

Page 6

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Contents

Page 6 of 115

750FXebmTOC.fm

June 10, 2003

Page 7

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

Tables

Table 2-1. Ethernet Ports ........................................................................................................................ 21

Table 2-2. Switch Settings ....................................................................................................................... 23

Table 2-3. Flash Configurations .............................................................................................................. 23

Table 3-1. Board Address Space Usage ................................................................................................. 27

Table 3-2. Register0 ................................................................................................................................ 27

Table 3-3. Register1 ................................................................................................................................ 28

Table 3-4. Register2 ................................................................................................................................ 28

Table 3-5. Register3 ................................................................................................................................ 29

Table 3-6. Register4 ................................................................................................................................ 29

Table 4-1. DDR SDRAM Characteristics ................................................................................................. 31

Table 4-2. Device Bank 0 Parameters = 0x85A492BF ........................................................................... 32

Table 4-3. Device Bank 1 Parameters = 0x8004921A ............................................................................ 33

Table 4-4. Device Bank 2 Parameters = 0x8C002BD6 ........................................................................... 34

Table 4-5. Device Bank 3 Parameters = 0x8D891445 ............................................................................ 35

Table 4-6. Boot Device Bank Parameters = 0x8185D09E ...................................................................... 36

Table 5-1. External Interrupts .................................................................................................................. 38

Table 6-1. Switches ................................................................................................................................. 39

Table 6-2. Reset Pushbutton—U5 .......................................................................................................... 39

Table 6-3. Reset Pushbutton—U53 ........................................................................................................ 40

Table 6-4. CPU 0 PLL Configuration—U30 ............................................................................................. 40

Table 6-5. CPU 1 PLL Configuration Switches—U35 ............................................................................. 41

Table 6-6. System Controller Initilization—U17 ....................................................................................... 42

Table 6-7. System Controller Initilization—U24 ....................................................................................... 43

Table 7-1. Current Measurement of the1.4V Supplies ............................................................................ 45

Table 7-2. Current Measurement of the 2.5V Supply ............................................................................. 46

Table 8-1. Displays ................................................................................................................................. 47

Table 9-1. Jumpers ................................................................................................................................. 49

Table 9-2. Write-Protect 32-bit Flash Memory—J8 ................................................................................. 50

Table 9-3. Ignore Fans—J16 ................................................................................................................... 50

Table 9-4. PCI Interrupt Selection—J22 .................................................................................................. 51

Table 10-1. Connectors ............................................................................................................................. 53

Table 10-2. ATX Power Signals—J34 ....................................................................................................... 55

Table 10-3. Ground Connectors —J1, J2, J7, J9, J10, J12, J17, J18, J23, J24 ....................................... 56

Table 10-4. Fan Power Signals—J4, ......................................................................................................... 56

Table 10-5. RISCWatch Signals—J11 ...................................................................................................... 57

Table 10-6. Ethernet UTP Signals—J20, both sockets ............................................................................. 58

750FXebmLOT.fm

June 10, 2003

Tables

Page 7 of 115

Page 8

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Table 10-7. PCI Connector Signals—J25 ..................................................................................................59

Table 10-8. CPLD JTAG Connector—J26 .................................................................................................62

Table 10-9. Serial Port Connector Signals—J13, both ports .....................................................................63

Table 10-10. System Controller Device Address Signals—J14 ...................................................................64

Table 10-11. Memory Control Signals—J15 ................................................................................................66

Table 10-12. External Clock Input Signal—U39 ..........................................................................................68

Table 10-13. Test Connections ....................................................................................................................69

Table 11-1. Section Contents ....................................................................................................................73

Table 11-2. CPLD I/O Pin List ...................................................................................................................73

Table 11-3. CPLD Logic Descriptions ........................................................................................................76

Table 11-4. Maximum Clock Frequency ....................................................................................................94

Table 11-5. Clock-to-Output Time .............................................................................................................94

Table 11-6. Pin-to-Pin Signal Delay ...........................................................................................................96

Table 11-7. Setup and Hold Time ............................................................................................................100

Table 12-1. Section Contents ..................................................................................................................101

Table 12-2. Component Placement Data Description .............................................................................102

Table 12-3. Debugging Tools ..................................................................................................................104

Table 12-4. Auxiliary Materials in Kit .......................................................................................................104

Table 12-5. Evaluation Board Bill of Materials .........................................................................................106

Tables

Page 8 of 115

750FXebmLOT.fm

June 10, 2003

Page 9

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

Figures

Figure 1-1. PPC750FX Block Diagram ..................................................................................................... 14

Figure 2-1. PPC750FX Board Architecture .............................................................................................. 19

Figure 2-2. Clock Distribution on the PPC750FX Board ........................................................................... 20

Figure 2-3. Board Ethernet Architecture ................................................................................................... 22

Figure 2-4. Board Serial Port Architecture ................................................................................................ 24

Figure 5-1. Interrupt Architecture .............................................................................................................. 37

Figure 6-1. Switch Location Diagram ....................................................................................................... 39

Figure 7-1. Resistor Location Diagram ..................................................................................................... 45

Figure 7-2. Fan and Heatsink Location Diagram ...................................................................................... 46

Figure 8-1. Display Location Diagram ...................................................................................................... 47

Figure 9-1. Jumper Location Diagram ...................................................................................................... 49

Figure 9-2. Write-Protect 32-bit Flash Memory Jumper—J8 .................................................................... 50

Figure 9-3. Ignore Fan Jumper—J16 ....................................................................................................... 50

Figure 9-4. PCI Interrupt Selection Jumper—J22 ..................................................................................... 51

Figure 10-1. Connector Location Diagram, Top Side ................................................................................. 54

Figure 10-2. ATX Power Supply Connector—J34 ......................................................................................55

Figure 10-3. Ground Connectors—J1, J2, J7, J9, J10, J12, J17, J18, J23, J24 ........................................ 56

Figure 10-4. Fan Power Connector—J4 ..................................................................................................... 56

Figure 10-5. RISCWatch JTAG Connector—J11 ....................................................................................... 57

Figure 10-6. Ethernet Connector—One of two RJ45 Sockets in J20 ......................................................... 58

Figure 10-7. PCI Connector—J25 ............................................................................................................. 59

Figure 10-8. CPLD JTAG Connector—J26 ................................................................................................ 62

Figure 10-9. Serial Port Connector—J13, one of two RJ11/12 sockets ..................................................... 63

Figure 10-10. System Controller Device Address Connector—J14 ............................................................. 64

Figure 10-11. Memory Control Connector—J15 ........................................................................................... 66

Figure 10-12. External Clock Input Connector—U39 ................................................................................... 68

Figure 10-13. Test Connection Locations ..................................................................................................... 71

Figure 12-1. Example of a Component Placement List in the Schematics ............................................... 102

Figure 12-2. Board Location Grid—Top View ........................................................................................... 103

Figure 12-3. Board Location Grid—Bottom View .....................................................................................103

750FXebmLOF.fm

June 10, 2003

Figures

Page 9 of 115

Page 10

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Figures

Page 10 of 115

750FXebmLOF.fm

June 10, 2003

Page 11

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

About This Book

This manual describes an evaluation platform for the PPC750FX chip.

Who Should Use This Book

This book is written to aid programmers and other technical personnel in the use of the PPC750FX

Evaluation Board. In order to use the board and this document, the reader shouldbe familiar with the

following:

• PowerPC Architecture™

• PCI bus

• Embedded microprocessor hardware

• IBM RISCWatch™ debugger

How to Use This Book

This book describes the features and interfaces of the IBM PPC750FX Evaluation Board. This book contains

the following sections:

• Overview provides a brief overview of the processor chip. Some chip aspects important to understanding

the board design are discussed in greater detail.

• Board Design describes the architecture of the evaluation board.

• Memory Map describes the address space usage of the board. Tables are provided which define the

access methods for all memory-mapped registers on the board.

• Programming the System Controller outlines the required programming to configure the MV64360

system controller for the board memory and peripherals.

• Reset and Interrupts lists the sources of resets and interrupts on the board, and provides information

required to program the PPC750FX amd MV64360 interrupt controllers.

• Switches locates and describes the function of all switches on the board, and indicates their default

settings.

• Fuses, Batteries, Regulators, and Fans locates and describes the function of fuses, batteries, and

voltage regulator adjustments on the board.

• Displays locates and describes all displays on the board.

• Jumpers locates and describes all jumpers on the board, and indicates their default settings.

• Connectors locates and describes all connectors on the board, and identifies the pin usage.

• CPLD Programming provides the source code and timing information for the CPLDs on the board.

• Bills of Materials provides lists of materials and parts that are assembled on the board, parts shipped with

the board but not assembled on the board, and other tools that are useful while using the board.

750FXebm_preface.fm

June 10, 2003

About This Book

Page 11 of 115

Page 12

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Related Publications

The following publications contain related information:

• PowerPC 750FX RISC Microprocessor Embedded Controller Data Sheet

• PowerPC 750FX RISC Microprocessor Embedded Controller Functional Specification

• PowerPC 750FX RISC Microprocessor Embedded Controller User’s Manual

• PowerPC 750FX RISC Microprocessor Evaluation Design Kit User’s Manual

• PowerPC 750FX RISC Microprocessor Evaluation Board Schematics

• PowerPC Architecture

• PowerPC Microprocessor Family: The Programming Environments, MPRPPCFPE-01

• PowerPC Embedded Processor Solutions, SC09-3032, a CDROM which includes the RISCWatch

Debugger User’s Guide

• PowerPC CoreConnect Bus (PLB) Specification

• PCI Local Bus Specification

•Marvell

MV64360/1/2 Data Sheet

About This Book

Page 12 of 115

750FXebm_preface.fm

June 10, 2003

Page 13

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

1. Overview

The PowerPC 750FX Evaluation Board is an evaluation platform intended to support the needs of

prospective users of the IBM PowerPC 750FX processor. The form factor of the board is a full-length PCI

card. This board is suitable for software development, for benchmarking, and for detailed study of the

hardware. This board contains two PPC750FX processors. A memory control and PCI bridge function

provided on the board coordinates the operations of the two processors. The two processors may be used

together or independently under program control. Both processors share the available memory and the PCI

interface. The board can appear to the PCI interface as either a 64-bit adapter or a 64-bit host.

Please be aware that the circuitry on this board is sometimes more complex than would be required for a

board design limited to a particular application. A customer who is developing his own design using this board

design as a guide should simplify the design wherever his application allows.

Warning: IBM is not responsible for use of the circuit designs on this board or use of the design of the

board itself in any other applications. Any functional, reliability, or safety issues resulting from the use of

any part of this board design, including copying the board, are the responsibility of the user.

The following sections will highlight the PPC750FX processor, and will then briefly discuss the features

available on the board.

1.1 PowerPC 750FX RISC Microprocessor Features

The IBM PowerPC 750FX RISC Microprocessor is a 32-bit implementation of the IBM PowerPC family of

reduced instruction set computer (RISC) microprocessors. The PPC750FX is targeted for high performance,

low power systems using a 60x bus. The 750FX also includes an internal 512KB L2 cache with on-board

Error Correction Circuitry (ECC). A block diagram of the processor chip is provided in Figure 1- 1.

750FXebm_ch1.fm

June 10, 2003

Overview

Page 13 of 115

Page 14

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Figure 1-1. PPC750FX Block Diagram

FXU1

32KB D-Cache

with parity

Completion

System

Unit

FXU2

Instruction Fetch

Branch Unit

Dispatch

GPRs

Rename

Buffers

Control Unit

BHT/BTIC

LSU FPU

L2 Tags

FPRs

Rename

Buffers

512KB

L2 Cache

with ECC

32KB I-Cache

with parity

Enhanced

60X

BIU

The PPC750FX processor has the following features:

• Branch processing unit

- Four instructions fetched per clock.

- One branch processed per cycle (plus resolving two speculations).

- Up to one speculative stream in execution, one additional speculative stream in fetch.

- 512-entry branch history table (BHT) for dynamic prediction.

- 64-entry, 4-way set associative branch target instruction cache (BTIC) for eliminating branch delay

slots.

• Dispatch unit

- Full hardware detection of dependencies (resolved in the execution units).

- Dispatch two instructions to six independent units (system, branch, load/store, fixed-point unit 1

(FXU1), fixed-point unit 2 (FXU2), or floating-point).

- Four-stage pipeline: fetch, dispatch, execute, and complete.

- Serialization control (predispatch, postdispatch, execution, serialization).

Overview

Page 14 of 115

750FXebm_ch1.fm

June 10, 2003

Page 15

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

• Decode

- Register file access.

- Forwarding control.

- Partial instruction decode.

• Load/Store unit

- One cycle load or store cache access (byte, half word, word, double word).

- Effective address generation.

- Hits under misses (one outstanding miss).

- Single-cycle misaligned access within double word boundary.

- Alignment, zero padding, sign extend for integer register file.

- Floating-point internal format conversion (alignment, normalization).

- Sequencing for load/store multiples and string operations.

- Store gathering.

- Cache and translation look-aside buffer (TLB) instructions.

- Big and little-endian byte addressing supported.

- Misaligned little-endian support in hardware.

• Fixed-point units

- FXU1: multiply, divide, shift, rotate, arithmetic, logical.

- FXU2: shift, rotate, arithmetic, logical.

- Single-cycle arithmetic, shift, rotate, logical.

- Multiply and divide support (multi-cycle).

- Early out multiply.

- Thirty-two, 32-bit general purpose registers.

• Floating-point unit

- Support for IEEE-754 standard single- and double-precision floating-point arithmetic.

- Optimized for single-precision multiply/add.

- Thirty-two, 64-bit floating point registers.

- Enhanced reciprocal estimates.

- Three-cycle latency, one-cycle throughput, single-precision multiply-add.

- Three-cycle latency, one-cycle throughput, double-precision add.

- Four-cycle latency, two-cycle throughput, double-precision multiply-add.

- Hardware support for divide.

- Hardware support for denormalized numbers.

- Time deterministic non-IEEE mode.

• System unit

- Executes CR logical instructions and miscellaneous system instructions.

- Special register transfer instructions.

• Level 1 (L1) Cache structure

- 32KB, 32-byte line, 8-way set associative instruction cache.

- 32KB, 32-byte line, 8-way set associative data cache.

- Single-cycle cache access.

750FXebm_ch1.fm

June 10, 2003

Overview

Page 15 of 115

Page 16

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

- Pseudo-LRU replacement.

- Copy-back or write-through data cache (on a page per page basis).

- Parity on L1 tags and arrays.

- Three-state (MEI) memory coherency.

- Hardware support for data coherency.

- Non-blocking instruction cache (one outstanding miss).

- Non-blocking data cache (two outstanding misses).

- No snooping of instruction cache.

• Memory management unit

- 64-entry, 2-way set associative instruction TLB (total 128).

- 64-entry, 2-way set associative data TLB (total 128).

- Hardware reload for TLB's.

- Eight instruction BAT's and eight data BATs.

52

- Virtual memory support for up to 4PB (2

- Real memory support for up to 4GB (2

) virtual memory.

32

) of physical memory.

- Support for big/little-endian addressing.

• Dual PLLs

- Allows seamless frequency switching.

• Level 2 (L2) cache

- Internal L2 cache controller and 4K-entry tags; 512KB data SRAMs.

- Two-way set associative, supports locking by way.

- Copy-back or write-through data cache on a page basis, or for all L2.

- 64-byte sectored line size.

- L2 frequency at core speed.

- ECC protection on SRAM array.

- Parity on L2 tags.

- Supports up to 2 outstanding misses (1 data and 1 instruction or 2 data).

• Bus interface

- 32-bit address bus.

- 64-bit data bus (can be operated in 32-bit mode).

- Core-to-bus frequency multipliers of 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x, 7.5x, 8x, 8.5x, 9x, 9.5x, 10x,

11x, 12x, 13x, 14x, 15x, 16x, 17x, 18x, 19x, and 20x supported.

- Supports 1.8V, 2.5V, or 3.3V I/O modes.

•Power

- Low power consumption with low voltage.

- Dynamic power management.

- Three static power saving modes: doze, nap, and sleep.

- Thermal Assist Unit (TAU).

Overview

Page 16 of 115

750FXebm_ch1.fm

June 10, 2003

Page 17

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

• Reliability and Serviceability

- Parity checking on 60x busses.

- ECC checking on L2 cache.

- Parity on the L1 arrays.

- Parity on the L1 and L2 tags.

• Testability

- Level-sensitive scan design (LSSD).

- Powerful diagnostic and test interface through Common On-Chip Processor (COP) and IEEE 1149.1

(JTAG) interface.

1.2 Board Features

The features of the PPC750FX evaluation board are summarized briefly below. More detail may be found in

Section 2 Board Design on page 19.

• PCI adapter form factor

• Two IBM PowerPC 750FX processors

•Marvell

• 256MB DDR SDRAM with ECC

• 1MB 8-bit wide socketed Flash (2 - 512KB devices)

• 1MB 8-bit wide SRAM

• 32MB 32-bit wide Flash

• 32KB Ferroelectric Nonvolatile RAM (FRAM)

• Two 100BASE-TX Ethernet ports

• Two 16550 compatible serial ports

• Two 64kb IIC Serial EEPROMs

• Single RISCWatch header for both processors

• Powered either externally or from PCI slot

• External system clock input

• External input for programming the on-board CPLD (FPGA)

MV64360 System Controller

750FXebm_ch1.fm

June 10, 2003

Overview

Page 17 of 115

Page 18

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Overview

Page 18 of 115

750FXebm_ch1.fm

June 10, 2003

Page 19

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

2. Board Design

Figure 2-1 illustrates the architecture of the PPC750FX evaluation board. Subsequent sections discuss

aspects of Figure 2-1 in more detail.

Figure 2-1. PPC750FX Board Architecture

PCI

Connector

ATX

Power

Connector

100/10

Fast

Ethernet

x2

System

PCI

Memory

Bus

Controller

and PCI

Bridge

Board Power

DDR

SDRAM

60x Bus

CPU 0

JTAG/RISCWatch

CPU 1

Interrupts

Boot

SEEPROM

CPLD

SEEPROM

Flash/SRAM

NVRAM

Serial Port

x2

4-Pin

2.1 Processor

The PPC750FX evaluation board is based upon the PPC750FX processor. See Section 1.1 PowerPC 750FX

RISC Microprocessor Features on page 13 for details. There are two PPC750FX processors on this board.

750FXebm_ch2.fm

June 10, 2003

Board Design

Page 19 of 115

Page 20

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

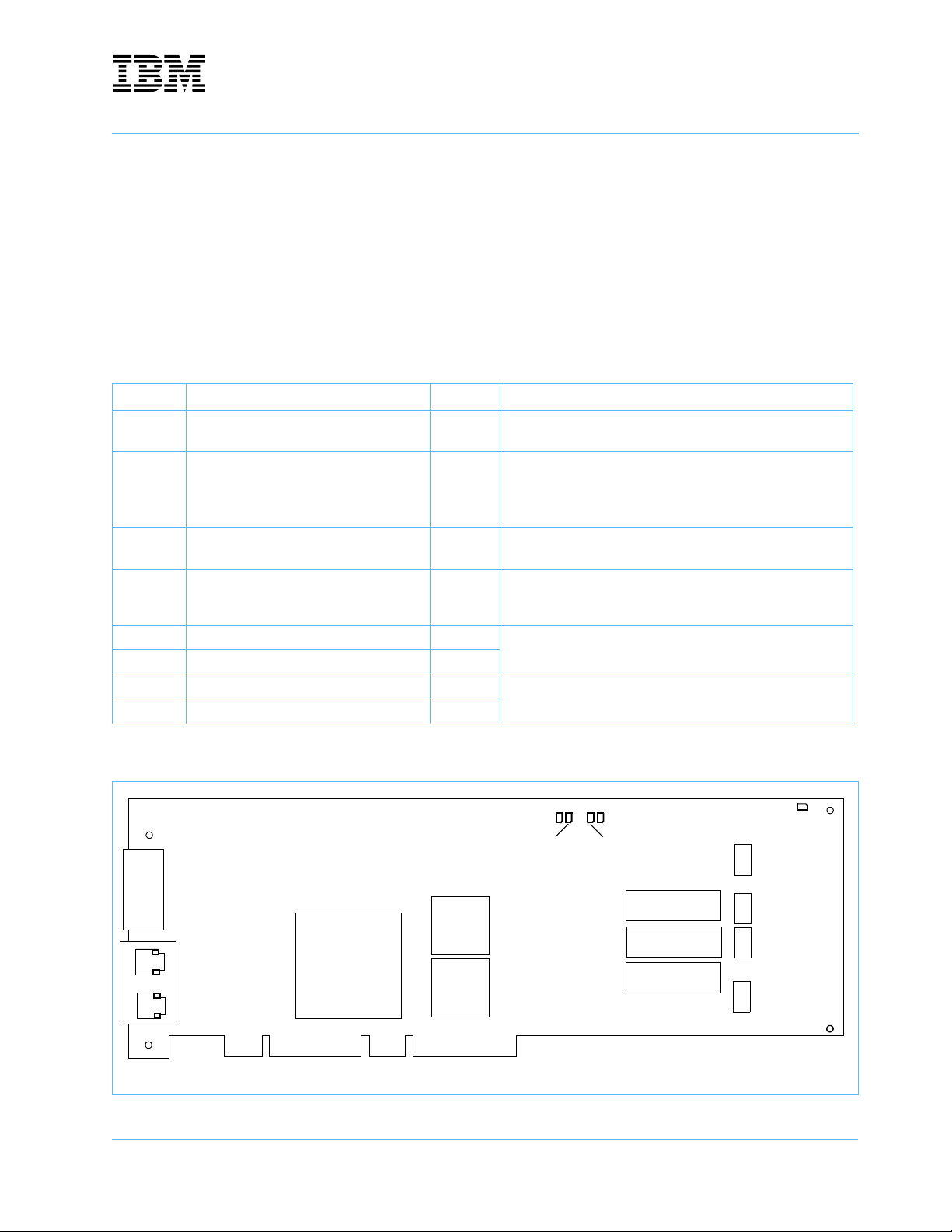

2.2 Board Clocking

The clock architecture of the PPC750FX board is illustrated in Figure 2-2.

Figure 2-2. Clock Distribution on the PPC750FX Board

External clock

(see Note)

MK74CB218

Clock

Driver

133MHz @ 2.5V

133MHz @ 2.5V

133MHz @ 3.3V

133MHz @ 3.3V

CPU 0

CPU 1

CPLD

33.33MHz Osc

C9531AT

Clock

Generator

133MHz

25MHz Osc

3.6864MHz Osc

Clock

Buffer

25MHz

25MHz

25MHz

Clock

Multiplier

MV64360

System

Controller

125MHz

2

ICS93V857

Clock

Driver

BCM5222

Dual

Ethernet

PHY

STI6C2552

Dual

UART

10

DDR SDRAM

CPLD

Board Design

Page 20 of 115

Note : Rework to the board is required to use the external oscillator input.

750FXebm_ch2.fm

June 10, 2003

Page 21

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

2.3 Internal Processor Clocking

The PPC750FX requires a single system clock input SYSCLK. The frequency of this input determines the

frequency of the PPC750FX bus interface. Internally, the PPC750FX uses a phase-lock loop (PLL) circuit to

generate a master core clock that is frequency-multiplied and phase-locked to the SYSCLK input. The PLL in

the PPC750FX is configured using seven pins PLL_CFG(0:4) and PLL_RANGE(0:1). On the PPC750FX

evaluation board, the configuration of these pins is controlled by switch settings (see Section 6 Switches on

page 39).

2.4 System Controller

The board contains a Marvell MV64360 system controller that connects to the 60x bus of the PPC750FX, and

provides an interface to DDR SDRAM, the PCI bus, the integrated Ethernet MACs, the integrated SRAM, an

interrupt controller, DMA engines, and an interface to attach external devices. Hereafter, in this document,

this component is referred to as the system controller.

2.5 SDRAM Interface

This board provides 256MB of permanently mounted DDR SDRAM operating at 133.33MHz. The interface to

the SDRAM is through the system controller, and is accessed using DRAM chip selects CS0 and CS1. The

SDRAM on the board is 72 bits wide and allows the use of the SDRAM Error Checking and Correction (ECC)

feature in the system controller if desired.

2.6 PCI Bus

This PPC750FX evaluation board is a full-length PCI card and is intended to be operated while plugged into a

PCI slot in a personal computer or a PCI backplane. However, because an ATX power connector is provided,

it can be operated without being plugged into a PCI slot. If this external mode of operation is used, the PCI

bus will not be available.

2.7 Ethernet

The board provides two 100BASE-TX Ethernet interfaces. The physical layer for both Ethernet ports is

provided by the BCM5222 which contains two medium-independent interface (MII) PHYs. The five address

pins of the BCM5222 are tied to ground making the addresses of the two PHYs 0 and 1. Tab le 2- 1 shows the

relationship between the two Ethernet ports being used in the MV64360, the PHY to which each port is

connected in the BCM5222, the address of each PHY, and finally the RJ45 connectors for each port (see J20

in Figure 10-1 on page 54).

Table 2-1. Ethernet Ports

MV64360 Ethernet Port No. BCM522 PHY No.

0211

1102

750FXebm_ch2.fm

June 10, 2003

Serial Manangement Interface

PHY Address

RJ45 Connector

Board Design

Page 21 of 115

Page 22

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Figure 2-3. Board Ethernet Architecture

MV64360

System

Controller

Ethernet

Ports

0

1

MDIO/MDC

MII

MII

Dual PHY

2

1

2

BCM5222

SMI 1

SMI 0

J8064D628A

2

1

1

2

RJ45 Sockets

w/ Magnetics and LEDs

The supported media is Category 5A Unshielded Twisted Pair cable (UTP), accessed via two RJ45

connectors on the board. The two RJ45 connectors are in a common housing with integrated magnetics and

LEDS.

2.8 Flash Memory

The following describes how to access Flash memory directly on the board.

Eight-bit Flash memory is used on the PPC750FX board. No benchmarking impact is expected from the use

of a narrow rather than a wide Flash array. For performance work, one should expect to replace the initial

firmware support provided in the Flash with more optimized routines residing in DRAM.

The PPC750FX board contains 1MB of 8-bit wide Flash memory provided by two socketed 8b x 0.5Mb

modules, and 32MB of 32-bit wide Flash memory provided by two 16b x 16Mb module (+3.3V only) for data

or code storage. Additionally, 1MB of SRAM, provided as two 512 KB modules, can be used in this memory

space.

The board can be set to boot from 8-bit wide Flash with SRAM below it in memory or, alternatively, it can boot

from the SRAM with the 8-bit wide Flash below it in memory. This setup uses system controller chip select

BootCS.

When set up to use BootCS to boot from 8-bit wide Flash or from SRAM, the system controller chip select

CS0 is used to select the 32-bit wide Flash. If desired, these chip selects can be swapped so that the board

will boot from the 32-bit wide Flash using BootCS, then CS0 selects the 8-bit wide Flash/SRAM combination.

There are two switches used to control where the system controller chip selects are directed. See System

Controller Initialization on page 42 for details on U17 switch 6 and U24 switch 7.

Board Design

Page 22 of 115

750FXebm_ch2.fm

June 10, 2003

Page 23

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

The 8-bit wide Flash is installed at the top of the address space. Immediately below that Flash in the address

space is the SRAM. Switch #7 on switch U24 allows the exchange of the two blocks in the address space.

The intent of this SRAM is to aid in the debug of ROM boot code, not for speed enhancement. Flash contents

will be copied to SRAM, then SRAM will be placed at the top of the address space. ROM code can then be

debugged from SRAM, allowing the placement of unlimited software break points.

Note 1: A jumper at J8 can be installed to prevent any 32-bit Flash write operations.

Note 2: Caching the 8- or 32-bit Flash memories is not supported.

Tab le 2-2 and Tab le 2- 3 describe the switch settings and the resulting configurations.

Table 2-2. Switch Settings

Configuration U17 SW6 U24 SW 7 Description

1 ON ON 8-bit boot, Flash at higher address

2 ON OFF 8-bit boot, SRAM at higher address

3 OFF ON 32-bit boot, Flash at higher address

4 OFF OFF 32-bit boot, SRAM at higher address

Table 2-3. Flash Configurations

Configuration Address Range Module(s) selected

0xFFF00000 to 0xFFFFFFFF 8-bit Flash controlled by BootCS

1

2

3

4

Notes: 1. The reset vector of the PPC750FX is 0xFFF00100.

2. The base addresses of peripherals attached to the MV64360 system controller device are software dependent. The values

0xFFE00000 to 0xFFEFFFFF 8-bit SRAM controlled by BootCS

0xFC000000 to 0xFDFFFFFF 32-bit Flash controlled by DevCS0

0xFFF00000 to 0xFFFFFFFF 8-bit SRAM controlled by BootCS

0xFFE00000 to 0xFFEFFFFF 8-bit Flash controlled by BootCS

0xFC000000 to 0xFDFFFFFF 32-bit Flash controlled by DevCS0

0xFE000000 to 0xFFFFFFFF 32-bit Flash controlled by BootCS

0xFC100000 to 0xFC1FFFFF 8-bit Flash controlled by DevCS0

8-bit SRAM controlled by DevCS0.

0xFC000000 to 0xFC0FFFFF

0xFE000000 to 0xFFFFFFFF 32-bit Flash controlled by BootCS

0xFC100000 to 0xFC1FFFFF 8-bit SRAM controlled by DevCS0

0xFC000000 to 0xFC0FFFFF

in the table above are used by the PPC750FX Evaluation Kit Software. Other software environments may use different

values for the peripheral base addresses.

Note: In configuration 3, SRAM is at the beginning of the DevCS0 memory

range followed by 8-bit wide Flash.

8-bit Flash controlled by DevCS0.

Note: In configuration 4, 8-bit wide Flash is at the beginning of the DevCS0

memory range followed by SRAM.

750FXebm_ch2.fm

June 10, 2003

Board Design

Page 23 of 115

Page 24

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

2.9 NVRAM

The board provides 32KB of non-volatile RAM. This memory is attached to the system controller device

interface, and is accessed using chip select DevCS3. This particular type of non-volatile ram uses magnetic

core technology and is referred to in the board schematics as FRAM. It does not require any battery power to

maintain its contents.

2.10 SRAM

The PPC750FX evaluation board provides 1MB of permanently mounted SRAM. This memory interfaces to

the system controller. Access to this memory by the processors is through the system controller. Address

space for SRAM is shared with Flash memory. See Flash Memory on page 22 for details on how the address

space can be configured.

In addition to the SRAM on the board, there are 256KB of addressible SRAM integrated in the system

controller module.

2.11 Serial Ports

The board utilizes an Exar ST16C2552 DUART to provide two 16550 compatible UARTs. The DUART is

attached to the device interface of the system controller, and is accessed using chip select DevCS2. Each

UART provides four interface signals (Tx, Rx, DSR, DTR) and is connected to an RJ11/12 connector.

Both serial ports are clocked by the same 3.68MHz oscillator provided on the board.

The Multi-Protocol Serial Controllers in the system controller are not supported on the PPC750FX evaluation

board.

Figure 2-4. Board Serial Port Architecture

ST16C2552

Dual UART

1 (A)

2 (B)

RJ11/12 Sockets

1 (Right)

2 (Left)

Board Design

Page 24 of 115

750FXebm_ch2.fm

June 10, 2003

Page 25

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

2.12 Logic Analyzer Connections

The system controller device bus is attached to Mictor logic analyzer connectors.

HP Logic analyzer connection to the PCI bus is accomplished using a FuturePlus PCI Local Bus Passive

Analysis Probe, vendor part number FS2005. The customer may purchase this probe from the manufacturer.

Probe hardware does not ship with the board.

2.13 Power Supply

The PPC750FX evaluation board obtains its power from the PCI slot connector into which it is plugged or

from the on-board ATX power connector.

2.13.1 PCI Voltages

The voltages provided through the PCI slot connector are:

•+5V

•+3.3V

All of the voltages described in the following sections are developed from the +3.3V PCI voltage.

2.13.2 System Controller Voltages

The system controller requires four voltages:

• System controller I/O—+3.3V

• DRAM —+2.5V

• CPU I/O—+2.5V

• System controller logic and Ethernet—+1.8V

Note: There are no external connection points for the +1.8V or +2.5V supplies. As a result variable

voltage testing and current measurement capability for these supplies are not available.

2.13.3 PPC750FX Voltages

The PPC750FX chip requires two voltages:

• Logic and PLL analog circuits— +1.45V

• 60x bus I/O circuits— +2.5V

Both voltages are generated by on-board regulators from the +3.3V voltage. Current measurement points are

available for both voltages. These measurement points can also be used to connect external voltage

supplies.

Note: The 60x bus voltage supply to the PPC750FX can be +1.8V, +2.5V, or +3.3V. To use any voltage

other than the +2.5V supplied by the board, the voltage must be supplied externally, and the 60x voltage

selection signals to the PPC750FX must be programmed accordingly.

750FXebm_ch2.fm

June 10, 2003

Board Design

Page 25 of 115

Page 26

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

2.13.4 SDRAM Voltages

An on-board regulator supplies +2.5V to the DDR SDRAM. This voltage is also the supply for the DRAM

interface in the system controller.There is also a +1.25V reference voltage provided to the SDRAM. There is

no current measurement point provided for this voltage.

2.14 Form Factor

The PPC750FX board is a full-length PCI card intended to be plugged into and operated in a standard PCI

slot on a personal computer or a PCI backplane. If a personal computer or PCI backplane are not available, it

can operate stand-alone with an external ATX power supply connected at J34.

Board Design

Page 26 of 115

750FXebm_ch2.fm

June 10, 2003

Page 27

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

3. Memory Map

Table 3-1 provides a summary of the board address space usage. For details about address space usage

relating to the processor registers, refer to the PPC750FX Embedded Processor User’s Manual.

Table 3-1. Board Address Space Usage

Peripheral Start Address End Address Chip Select Size

DDR SDRAM 0x00000000 0x0FFFFFFF SDRAM CS0 and CS1 256MB

MV64360 Integrated SRAM 0x42000000 0x4203FFFF n/a 256KB

FRAM 0xEF500000 0xEF507FFF DevCS3 32KB

ST16C2552 UART Channel B 0xEF600000 0xEF600007 DevCS2 8B

ST16C2552 UART Channel A 0xEF600008 0xEF60000F DevCS2 8B

CPLD Registers 0xEF700000 0xEF700004 DevCS1 5B

MV64360 Registers 0xF1000000 0xF100FFFF n/a 64KB

32-bit Flash 0xFC000000 0xFDFFFFFF DevCS0 32MB

SRAM 0xFFE00000 0xFFEFFFFF BootCS 1MB

8-bit Flash 0xFFF00000 0xFFFFFFFF BootCS 1MB

Note: The base addresses of peripherals attached to the MV64360 system controller device are software dependent. The values in the

table above are used by the PPC750FX Evaluation Kit Software. Other software environments may use different values for the

peripheral base addresses.

3.1 CPLD Register Definitions

This section provides description by bit for each of the CPLD registers.

Each CPLD register is 8 bits wide. In the tables below, the most significant bit is bit 0, and the least significant

bit is bit 7. The CPLD source code uses the reverse bit ordering.

Table 3-2. Register0

Bit Name R/W Description

0:7 CPLD Revision R Revision level of CPLD code

750FXebm_ch3.fm

June 10, 2003

Memory Map

Page 27 of 115

Page 28

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Table 3-3. Register1

Note: This register should be written before reading in order to latch the most current status. Any value can be written to the register.

Bit Name R/W Description

0 (msb) na na Unused

1 na na Unused

2 ATX or PCI Power R

3 Spare Switch B R

4 Spare Switch A R

5 PCI Adapter/Host select R

6 8-bit Flash/SRAM swap select R

7 (lsb) BootFlash select R

0 = Using an ATX power supply

1 = Power obtained from a PCI slot

0 = U35 Switch 8 is ON

1 = U35 Switch 8 is OFF

0 = U30 Switch 8 is ON

1 = U30 Switch 8 is OFF

0 = PCI Host mode U24 Switch 6 is ON

1 = PCI Adapter mode U24 Switch 6 is OFF

0 = 8-bit Flash is at a higher address in memory, U24 Switch 6 is ON

1 = 8-bit SRAM is at a higher address in memory, U24 Switch 6 is ON

0 = Booted from 8-bit flash or SRAM U17 Switch 6 is ON

1 = Booted from 32-bit flash U17 Switch 6 is OFF

Table 3-4. Register2

Bit Name R/W Description

0 (msb) CPU1 MCP control R/W

1 CPU0 MCP control R/W

2 CPU TBEN control R/W

3 CPU1 SMI control R/W

4 CPU0 SMI control R/W

5 DS4 LED control R/W

6 DS2 LED control R/W

7 (lsb) DS1 LED control R/W

Asserts the Machine Check Pin (MCP) signal on CPU1

0 = CPU1 MCP signal not asserted

1 = CPU1 MCP signal asserted

Asserts the Machine Check Pin (MCP) signal on CPU0

0 = CPU0 MCP signal not asserted

1 = CPU0 MCP signal asserted

Controls the state of the timebase enable (TBEN) signal of both CPUs

0 = timebase runs freely on both CPUs

1 = timebase frozen on both CPUs

Asserts the System Management Interrupt signal on CPU1

0 = CPU1 SMI signal not asserted

1 = CPU1 SMI signal asserted

Asserts the System Management Interrupt signal on CPU0

0 = CPU0 SMI signal not asserted

1 = CPU0 SMI signal asserted

0 = DS4 LED is ON

1 = DS4 LED is OFF

0 = DS2 LED is ON

1 = DS2 LED is OFF

0 = DS1 LED is ON

1 = DS1 LED is OFF

Memory Map

Page 28 of 115

750FXebm_ch3.fm

June 10, 2003

Page 29

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

Table 3-5. Register3

Bit Name R/W Description

Five MPP/GPP pins on the system controller can be used to control

the SRESET and HRESET of pins of the processors, and an entire

board reset. To give software a chance to configure the MPP/GPP

0 (msb) Block MPP resets R/W

1:7 unused

pins 7, 8, 11, 12, and 24 properly, the signals are blocked by the

CPLD until this bit is set to 1.

0 = MPP resets are blocked

1 = MPP resets are not blocked

Table 3-6. Register4

Bit Name R/W Description

0:7 Board Revision R

Board revision level in binary (for example, 0x00000010 = Revision

level 2).

750FXebm_ch3.fm

June 10, 2003

Memory Map

Page 29 of 115

Page 30

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

Memory Map

Page 30 of 115

750FXebm_ch3.fm

June 10, 2003

Page 31

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

4. Programming the System Controller

This section provides guidance on programming the system controller to agree with the board design.

4.1 DDR SDRAM

The following are the characteristics of the DDR SDRAM memory on the PPC750FX evaluation board:

Table 4-1. DDR SDRAM Characteristics

Memory Type DDR SDRAM

Number of Row Addresses 13

Number of Column Addresses 9

Number of Module Banks 2

SDRAM Width, Primary 16 bits

Error Checking SDRAM Width 8 bits

Data Width 72 bits

Number of SDRAM Banks 4

4.1.1 SDRAM Controller Initialization

See Marvell MV64360/1/2 data sheet.

4.2 Device Controller Bank Register Settings

The following sections define the settings for the device controller bank registers in the system controller.

750FXebm_ch4.fm

June 10, 2003

Programming the System Controller

Page 31 of 115

Page 32

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

4.2.1 Device Bank 0 Parameters (32-bit Flash)

Table 4-2. Device Bank 0 Parameters = 0x85A492BF

Field Value (bin) Comment

TurnOff 111

Acc2First 0111

Acc2Next 0101

ALE2Wr 010 Number of Sysclk cycles from ALE de-assertion to the assertion of Wr[0]

WrLow 010 Number of Sysclk cycles that Wr[0] is active

WrHigh 010

DevWidth 10 Device width of 32 bits

TurnOffExt 0 TurnOff extension (most significant bit)

Acc2FirstExt 1 Acc2First extension (most significant bit)

Acc2NextExt 1 Acc2Next extension (most significant bit)

ALE2WrExt 0 ALE2Wr extension (most significant bit)

WrLowExt 1 WrLow extension (most significant bit)

WrHighExt 0 WrHigh extension (most significant bit)

BadrSkew 00 Number of Sysclk cycles from when BAdr changes to the read of the data

DPEn 0 Parity Disabled

Reserved 1

Number of Sysclk cycles that the system controller does not drive the

address/data bus after completion of a device read

Number of Sysclk cycles from the de-assertion of ALE to the cycle that the

first read data is sampled

Number of Sysclk cycles in a burst read access between the cycle that

samples data N to the cycle that samples data N+1

Number of Sysclk cycles between data beats of a burst write that Wr[0] is

held in-active. BAdr and data are held valid for WrHigh-1 cycles

Programming the System Controller

Page 32 of 115

750FXebm_ch4.fm

June 10, 2003

Page 33

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

4.2.2 Device Bank 1 Parameters (CPLD registers)

Table 4-3. Device Bank 1 Parameters = 0x8004921A

Field Value (bin) Comment

TurnOff 010

Acc2First 0011

Acc2Next 0100

ALE2Wr 010 Number of Sysclk cycles from ALE de-assertion to the assertion of Wr[0]

WrLow 010 Number of Sysclk cycles that Wr[0] is active

WrHigh 010

DevWidth 00 Device width of 8 bits

TurnOffExt 0 TurnOff extension (most significant bit)

Acc2FirstExt 0 Acc2First extension (most significant bit)

Acc2NextExt 0 Acc2Next extension (most significant bit)

ALE2WrExt 0 ALE2Wr extension (most significant bit)

WrLowExt 0 WrLow extension (most significant bit)

WrHighExt 0 WrHigh extension (most significant bit)

BadrSkew 00 Number of Sysclk cycles from when BAdr changes to the read of the data

DPEn 0 Parity Disabled

Reserved 1

Number of Sysclk cycles that the system controller does not drive the

address/data bus after completion of a device read

Number of Sysclk cycles from the de-assertion of ALE to the cycle that the

first read data is sampled

Number of Sysclk cycles in a burst read access between the cycle that

samples data N to the cycle that samples data N+1

Number of Sysclk cycles between data beats of a burst write that Wr[0] is

held in-active. BAdr and data are held valid for WrHigh-1 cycles

750FXebm_ch4.fm

June 10, 2003

Programming the System Controller

Page 33 of 115

Page 34

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

4.2.3 Device Bank 2 Parameters (UARTs)

Table 4-4. Device Bank 2 Parameters = 0x8C002BD6

Field Value (bin) Comment

TurnOff 110

Acc2First 1010

Acc2Next 0111

ALE2Wr 101 Number of Sysclk cycles from ALE de-assertion to the assertion of Wr[0]

WrLow 000 Number of Sysclk cycles that Wr[0] is active

WrHigh 000

DevWidth 00 Device width of 8 bits

TurnOffExt 0 TurnOff extension (most significant bit)

Acc2FirstExt 0 Acc2First extension (most significant bit)

Acc2NextExt 0 Acc2Next extension (most significant bit)

ALE2WrExt 0 ALE2Wr extension (most significant bit)

WrLowExt 1 WrLow extension (most significant bit)

WrHighExt 1 WrHigh extension (most significant bit)

BadrSkew 00 Number of Sysclk cycles from when BAdr changes to the read of the data

DPEn 0 Parity Disabled

Reserved 1

Number of Sysclk cycles that the system controller does not drive the

address/data bus after completion of a device read

Number of Sysclk cycles from the de-assertion of ALE to the cycle that the

first read data is sampled

Number of Sysclk cycles in a burst read access between the cycle that

samples data N to the cycle that samples data N+1

Number of Sysclk cycles between data beats of a burst write that Wr[0] is

held in-active. BAdr and data are held valid for WrHigh-1 cycles

Programming the System Controller

Page 34 of 115

750FXebm_ch4.fm

June 10, 2003

Page 35

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

4.2.4 Device Bank 3 Parameters (FRAM)

Table 4-5. Device Bank 3 Parameters = 0x8D891445

Field Value (bin) Comment

TurnOff 101

Acc2First 1000

Acc2Next 010

ALE2Wr 010 Number of Sysclk cycles from ALE de-assertion to the assertion of Wr[0]

WrLow 100 Number of Sysclk cycles that Wr[0] is active

WrHigh 100

DevWidth 00 Device width of 8 bits

TurnOffExt 0 TurnOff extension (most significant bit)

Acc2FirstExt 1 Acc2First extension (most significant bit)

Acc2NextExt 1 Acc2Next extension (most significant bit)

ALE2WrExt 0 ALE2Wr extension (most significant bit)

WrLowExt 1 WrLow extension (most significant bit)

WrHighExt 1 WrHigh extension (most significant bit)

BadrSkew 00 Number of Sysclk cycles from when BAdr changes to the read of the data

DPEn 0 Parity Disabled

Reserved 1

Number of Sysclk cycles that the system controller does not drive the

address/data bus after completion of a device read

Number of Sysclk cycles from the de-assertion of ALE to the cycle that the

first read data is sampled

Number of Sysclk cycles in a burst read access between the cycle that

samples data N to the cycle that samples data N+1

Number of Sysclk cycles between data beats of a burst write that Wr[0] is

held in-active. BAdr and data are held valid for WrHigh-1 cycles

750FXebm_ch4.fm

June 10, 2003

Programming the System Controller

Page 35 of 115

Page 36

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

4.2.5 Boot Device Parameters (8 bit flash and SRAM)

If booting from the 8-bit Flash or SRAM, the default value of the Boot Device Parameters register in the

system controller is 0x8FCFFFFF. To improve the access time to the Flash contents, the register can be

changed to the following:

Table 4-6. Boot Device Bank Parameters = 0x8185D09E

Field Value (bin) Comment

TurnOff 110

Acc2First 0011

Acc2Next 010

ALE2Wr 010 Number of Sysclk cycles from ALE de-assertion to the assertion of Wr[0]

WrLow 111 Number of Sysclk cycles that Wr[0] is active

WrHigh 010

DevWidth 00 Device width of 8 bits

TurnOffExt 0 TurnOff extension (most significant bit)

Acc2FirstExt 1 Acc2First extension (most significant bit)

Acc2NextExt 1 Acc2Next extension (most significant bit)

ALE2WrExt 0 ALE2Wr extension (most significant bit)

WrLowExt 0 WrLow extension (most significant bit)

WrHighExt 0 WrHigh extension (most significant bit)

BadrSkew 00 Number of Sysclk cycles from when BAdr changes to the read of the data

DPEn 0 Parity Disabled

Reserved 1

Number of Sysclk cycles that the system controller does not drive the

address/data bus after completion of a device read

Number of Sysclk cycles from the de-assertion of ALE to the cycle that the

first read data is sampled

Number of Sysclk cycles in a burst read access between the cycle that

samples data N to the cycle that samples data N+1

Number of Sysclk cycles between data beats of a burst write that Wr[0] is

held in-active. BAdr and data are held valid for WrHigh-1 cycles

Programming the System Controller

Page 36 of 115

750FXebm_ch4.fm

June 10, 2003

Page 37

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

5. Reset and Interrupts

The following sections provide details regarding the reset and interrupt operation of the board.

5.1 Resets

Reset to the PPC750FX is generated at power-on, by the reset pushbutton, by system-reset from the

PPC750FX (usually in response to a command from the RISCWatch debugger), or by undervoltage on the

+3.3V supply.

Under software control, using registers in the CPLD, each processor can be reset individually, or the entire

board can be reset.

5.2 Interrupts

The system controller contains an interrupt controller that handles interrupts from peripherals inside the

system controller as well as external peripherals.

There are three external interrupt inputs to the PPC750FX (INT, MCP, and SMI). See Table 5-1 for more

detail.

Figure 5-1. Interrupt Architecture

MV64360

CPU 0

INT

MCP

SMI

CPU 1

SMI

MCP

INT

UART A

UART B

Ethernet PHY

PCI Intr A

PCI Intr B

PCI Intr C

PCI Intr D

System Controller

CPLD

Register2

750FXebm_ch5.fm

June 10, 2003

Reset and Interrupts

Page 37 of 115

Page 38

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

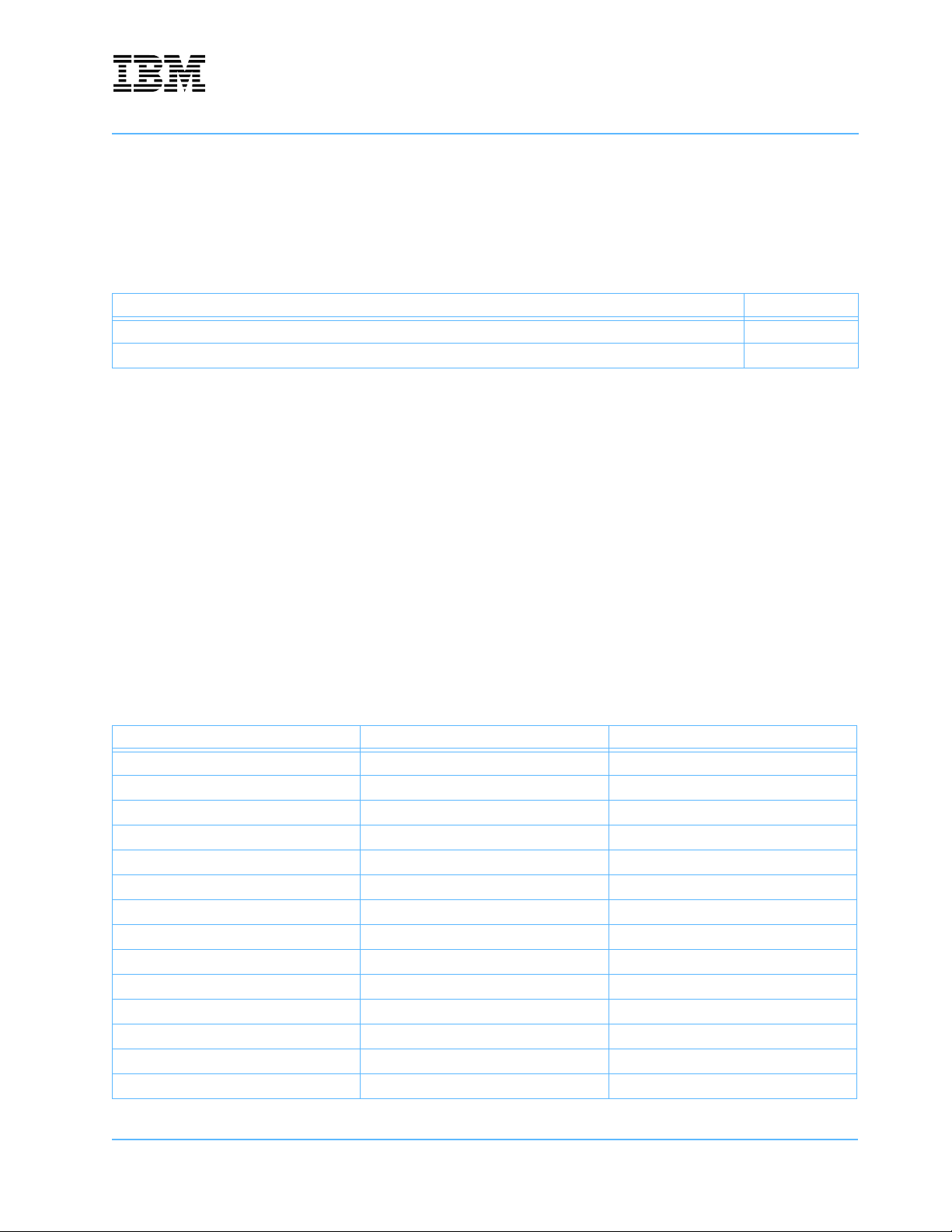

Table 5-1. External Interrupts

MPP Controller Pin +/- Active Sensitivity Description

25 + level UART Channel A

26 + level UART Channel B

27 – level Ethernet PHY

28 – level PCI Intr A

29 – level PCI Intr B

30 – level PCI Intr C

31 – level PCI Intr D

Note: The PCI interrupts are inputs when the board is operating as a PCI host. If operating as a PCI adapter, these pins should be

configured as outputs.

Reset and Interrupts

Page 38 of 115

750FXebm_ch5.fm

June 10, 2003

Page 39

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

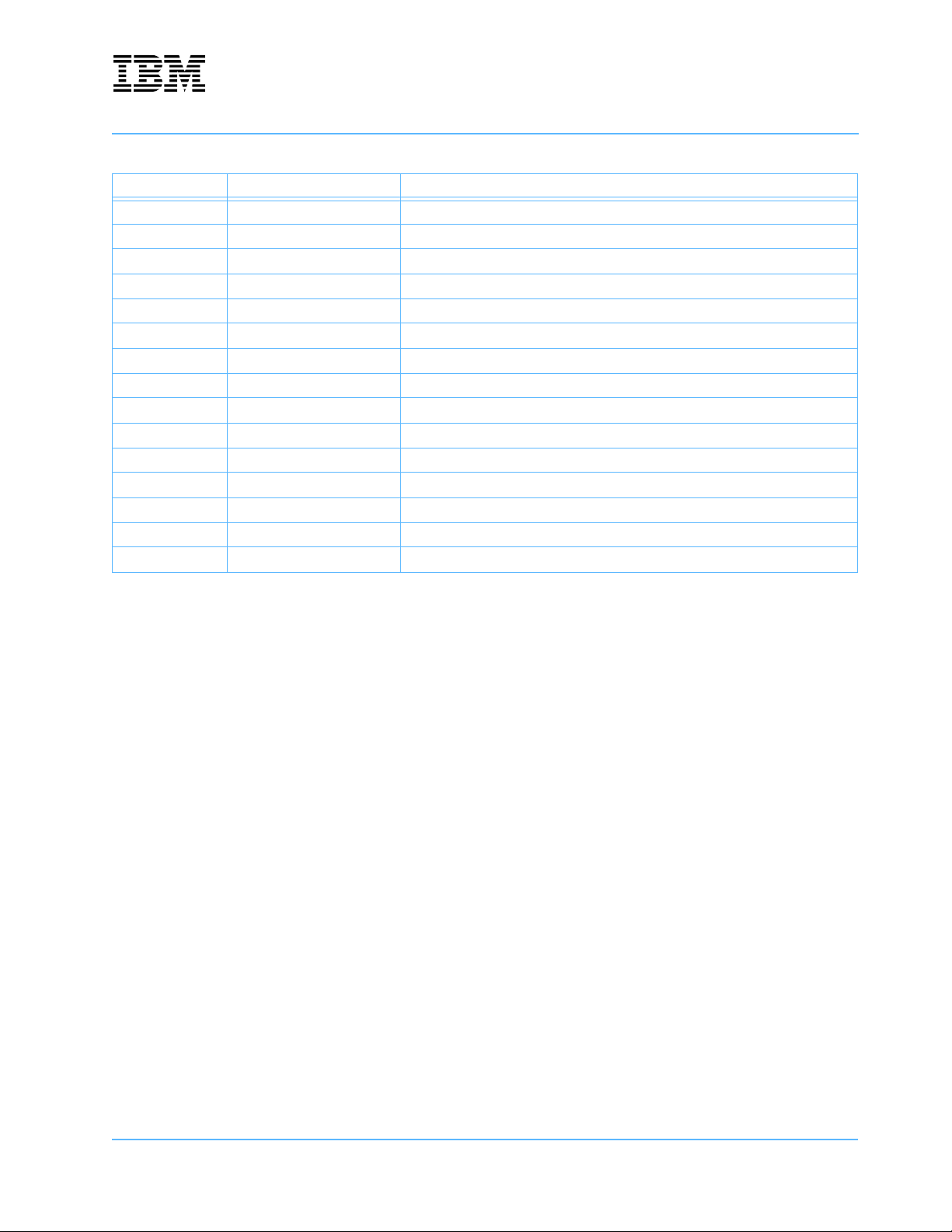

6. Switches

This section shows the location of all the switches on the board, and explains the function of each switch.

Table 6-1. Switches

Location Function Page

U5 Reset pushbutton 39

U17, U24 System controller initialization 42

U30 CPU 0 PLL configuration 40

U35 CPU 1 PLL configuration 41

U53 External ATX power 40

Figure 6-1. Switch Location Diagram

U5

On

U53

ATX Power

Off

Off

Off

1

8

1

8

1

8

1

8

Reset

U17

On

U24

U30

On

U35

6.1 Reset Pushbutton

When pressed, the pushbutton switch at U5 pulls the PWRGD signal to ground, causing a reset of the board.

Table 6-2. Reset Pushbutton—U5

Signal Description (0 = ON = close)

Pulls down PWRGD. Main board reset.

750FXebm_ch6.fm

June 10, 2003

Switches

Page 39 of 115

Page 40

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

6.2 ATX Power-on Pushbutton

When pressed, the pushbutton switch at U53 generates a power-on signal to the external ATX power supply

connected to J34. This pushbutton must be pressed after the ATX power supply is connected to J34 in order

to activate the power supply

Note: If the board is plugged into a PCI slot, the external ATX power supply will not activate under any

conditions, and pressing U53 will have no effect.

Table 6-3. Reset Pushbutton—U53

Signal Description (0 = ON = close)

PS_ON Generates power-on signal to the external ATX power connector.

6.3 CPU 0 PLL Configuration

An 8-position DIP switch at location U30 configures the PLL for the first PPC750FX processor (U1).

Table 6-4. CPU 0 PLL Configuration—U30

Switch No. Signal Default Setting Description (0 = ON = closed, 1 = OFF = open)

1 PLL_CONFIG0 ON

2 PLL_CONFIG1 OFF

3 PLL_CONFIG2 ON

4 PLL_CONFIG3 OFF

5 PLL_CONFIG4 OFF

6 PLL_RANGE0 ON

7 PLL_RANGE1 ON

8 SPARESWITCH1 ON

Refer to the latest version of the PowerPC 750FX

RISC Microprocessor Data Sheet for details on the bit

settings for PLL_CONFIG and PLL_RANGE.

Input to CPLD F2 pin with pull-up to +3.3V. See CPLD

Register1.

Switches

Page 40 of 115

750FXebm_ch6.fm

June 10, 2003

Page 41

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

6.4 CPU 1 PLL Configuration

An 8-position DIP switch at location U35 configures PLL for the second PPC750FX processor (U2).

Table 6-5. CPU 1 PLL Configuration Switches—U35

Switch No. Signal Default Setting Description (0 = ON = closed, 1= OFF = open)

1 PLL_CONFIG0 ON

2 PLL_CONFIG1 OFF

3 PLL_CONFIG2 ON

4 PLL_CONFIG3 OFF

5 PLL_CONFIG4 OFF

6 PLL_RANGE0 ON

7 PLL_RANGE1 ON

8 SPARESWITCH2 ON Connected to +3.3V pull-up. See CPLD Register1.

Refer to the latest version of the PowerPC 750FX

RISC Microprocessor Data Sheet for details on the bit

settings for PLL_CONFIG and PLL_RANGE.

750FXebm_ch6.fm

June 10, 2003

Switches

Page 41 of 115

Page 42

Evaluation Board Manual

PPC750FX Evaluation Board Preliminary

6.5 System Controller Initialization

Two 8-position DIP switches at location U17 and U24 provide initilization settings for the system controller.

Table 6-6. System Controller Initilization—U17

Switch No. Signal Default Setting Description (0 = ON = closed, 1 = OFF = open)

1DEV_AD0 ON

2:3 DEV_AD2:DEV_AD3 ON:ON

4DEV_AD5 OFF

5DEV_AD8 OFF

6DEV_AD15 ON

7DEV_AD16 OFF

8DEV_AD18 OFF

ON = MV64360 Serial ROM initialization disabled

OFF = MV64360 Serial ROM initialization enabled

Specifies the two least significant bits of the 7 bit IIC address of the Serial

ROM the MV64360 can use for initialization.

ON:ON = address 0b1010000 (Serial EEPROM U36)

ON:OFF = reserved

OFF:ON = address 0b1010001 (Serial EEPROM U55)

OFF:OFF = reserved

ON = MV64360 register base address is 0x14000000

OFF = MV64360 register base address is 0xF1000000

ON = MV64360 CPU Pads Calibration Disabled

OFF = MV64360 CPU Pads Calibration Enabled

ON = boot from 8 bit socketed Flash BOOTSMALL_N

OFF = boot from 32 bit Flash

ON = MV64360 PCI retry disabled

OFF = MV64360 PCI retry enabled

ON = DDR-SDRAM clock is running at a higher frequency than the

MV64360 core clock

OFF = DDR-SDRAM clock is running at the same frequency as the

MV64360 core clock

Switches

Page 42 of 115

750FXebm_ch6.fm

June 10, 2003

Page 43

Evaluation Board Manual

Preliminary PPC750FX Evaluation Board

Table 6-7. System Controller Initilization—U24

Switch No. Signal Default Setting Description (0 = ON = closed, 1 = OFF = open)

ON = DDR SDRAM address/control signals toggle on falling edge of

1DEV_AD19 OFF

2DEV_AD21 ON

3DEV_AD22 ON

4DEV_AD23 ON

5DEV_AD24 ON

6

7 FLASH_N/SRAM_SEL ON

8DEV_AD14 ON

PCIMODE_TARGET/

HOST_N

OFF

DRAM clock.

OFF = DDR SDRAM address/control signals toggle on rising edge of

DRAM clock.

ON = DDR SDRAM two pipe stages (up to 133MHz SDRAM clock)

OFF = DDR SDRAM three pipe stages (up to 183MHz SDRAM clock)

ON = DDR SDRAM read data is synchronized to the MV64360 core clock.

OFF = DDR SDRAM read data is synchronized to the MV64360 FBClkIn

clock signal.

DDR SDRAM Read Control Logic Delay

ON = Disabled

OFF = Enabled

DDR SDRAM Read Data Delay

ON = Disabled

OFF = Enabled

ON = board operates as a PCI Host

OFF = board operates as a PCI Adapter

ON = 8-bit Flash resides at a higher address than the 8-bit SRAM

OFF = 8-bit SRAM resides at a higher address than the 8-bit Flash

Note: This switch can be useful for putting SRAM at the CPU reset vector

during boot ROM code development.