Page 1

POWER7

Technology Insight

Wayne Huang

Fang Shu Xin

IBM CONFIDENTIAL – FOR IBM AND BP USE ONLY – NOT FOR DISCLOSURE TO CUSTOMERS

© 2010 IBM Corporation

Page 2

IBM Power Systems

Agenda….

POWER7 Product Family

POWER7 Processor

Active Memory Expansion

POWER7 TPMD

OS Support on POWER7

POWER7 Servers

Power 750

Power 755

Power 770

Power 780

RAS Update

I/O Update

Summary

Power your planet

© 2010 IBM Corporation

Page 3

IBM Power Systems

0

100

200

300

400

500

600

700

JS23 JS43 520 550 750 560 570/16 570/32 770 780 595

POWER7 System Highlights

Balance System Design

Cache, Memory, and IO

POWER7 Processor Technology

6thImplementation of multi-core design

On chip L2 & L3 caches

POWER7 System Architecture

Blades to High End offerings

Enhances memory implementation

PCIe, SAS / SATA

Built in Virtualizatio n

Memory Expansion

VM Control

Green Technologies

Processor Nap & Sleep Mode

Memory Power Down support

Aggressive Power Save / Capping Modes

Availability

Processor Instruction Retry

Alternate Process Recovery

Concurrent Add & Services

Power your planet

© 2010 IBM Corporation

Page 4

IBM Power Systems

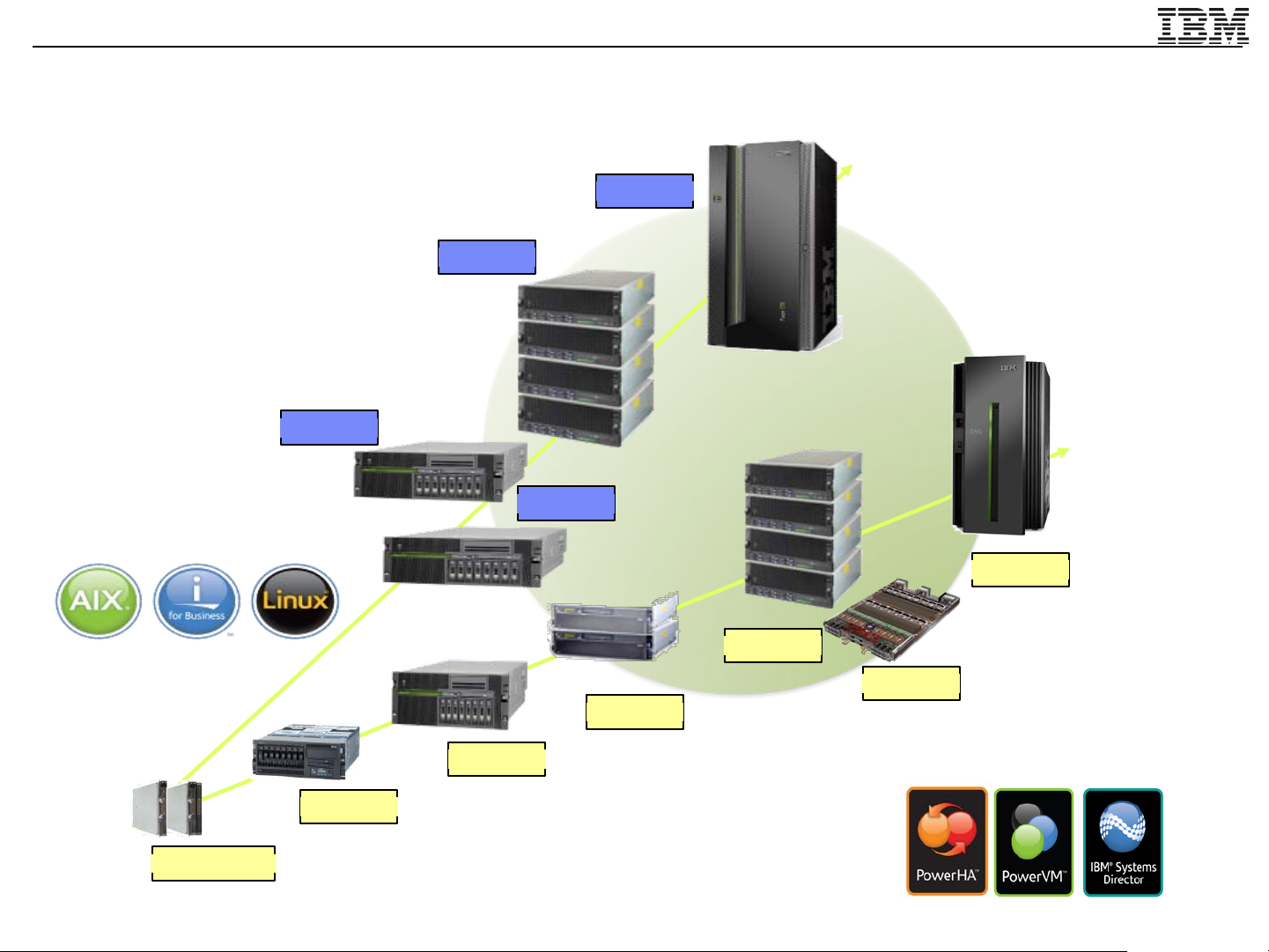

Power 2010 全新产品线

全新发布的Power7产品线

Pow er 750 (8, 16,32 C ore)

Pow er 755 ( 32 C or e) for HPC

Pow er 770 (12, 24,36,48 C ore)

Pow er 780 (16, 32,48,64 C ore)

POWER6产品线2010年继续支持

Pow er 520, Bl ades

Pow er 550

Pow er 560

Pow er 570

Pow er 575

Pow er 595

Power 750

Power 770

Power 755

Power 780

Power 7 Systems

Power 6 Systems

Power 520

Power Blades

Power your planet

Power 595

Power 570

Power 575

Power 560

Power 550

© 2010 IBM Corporation

Page 5

IBM Power Systems

POWER7 Processor

POWER7

Pushing the

Limits

Power your planet

© 2010 IBM Corporation

Page 6

IBM Power Systems

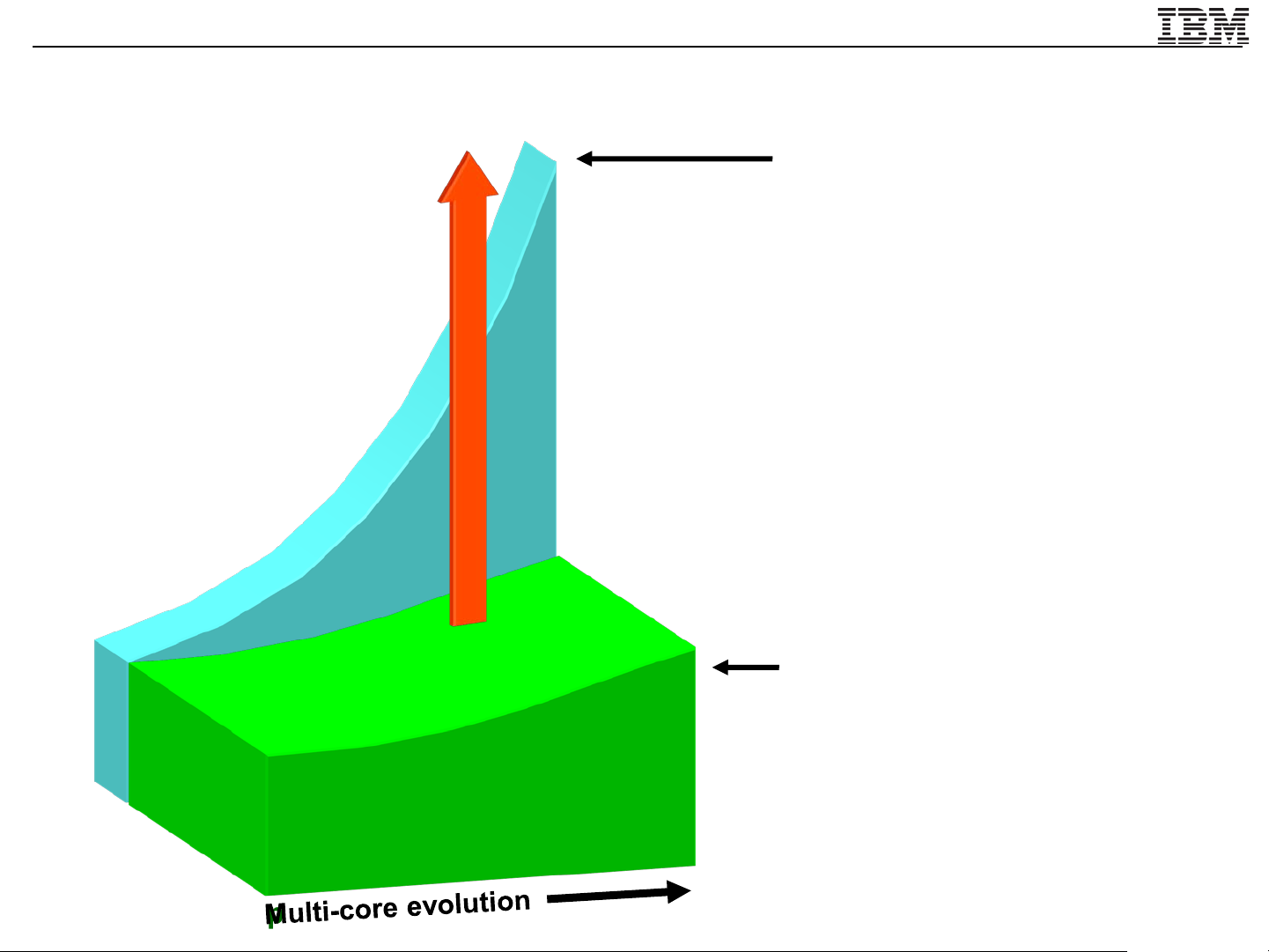

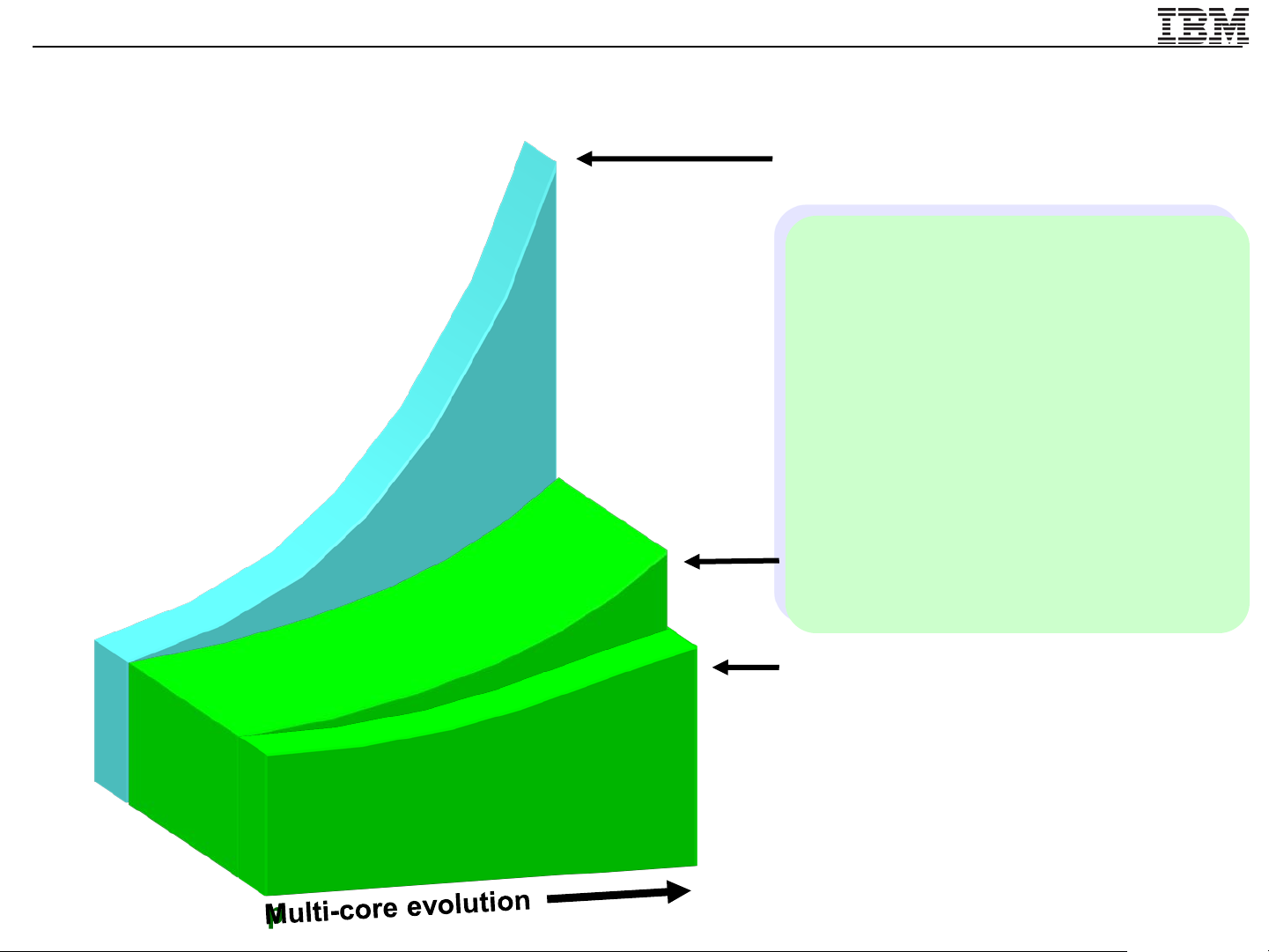

Challenge: Beating Physics to Realize Multi-core Potential

Need to Amplify Effective

Socket Throughput

to Close Gap and

Achieve Potential

Compute Throughput Potential

Socket Throughput Limitation

Power your planet

(Physical signal economics)

© 2010 IBM Corporation

Page 7

IBM Power Systems

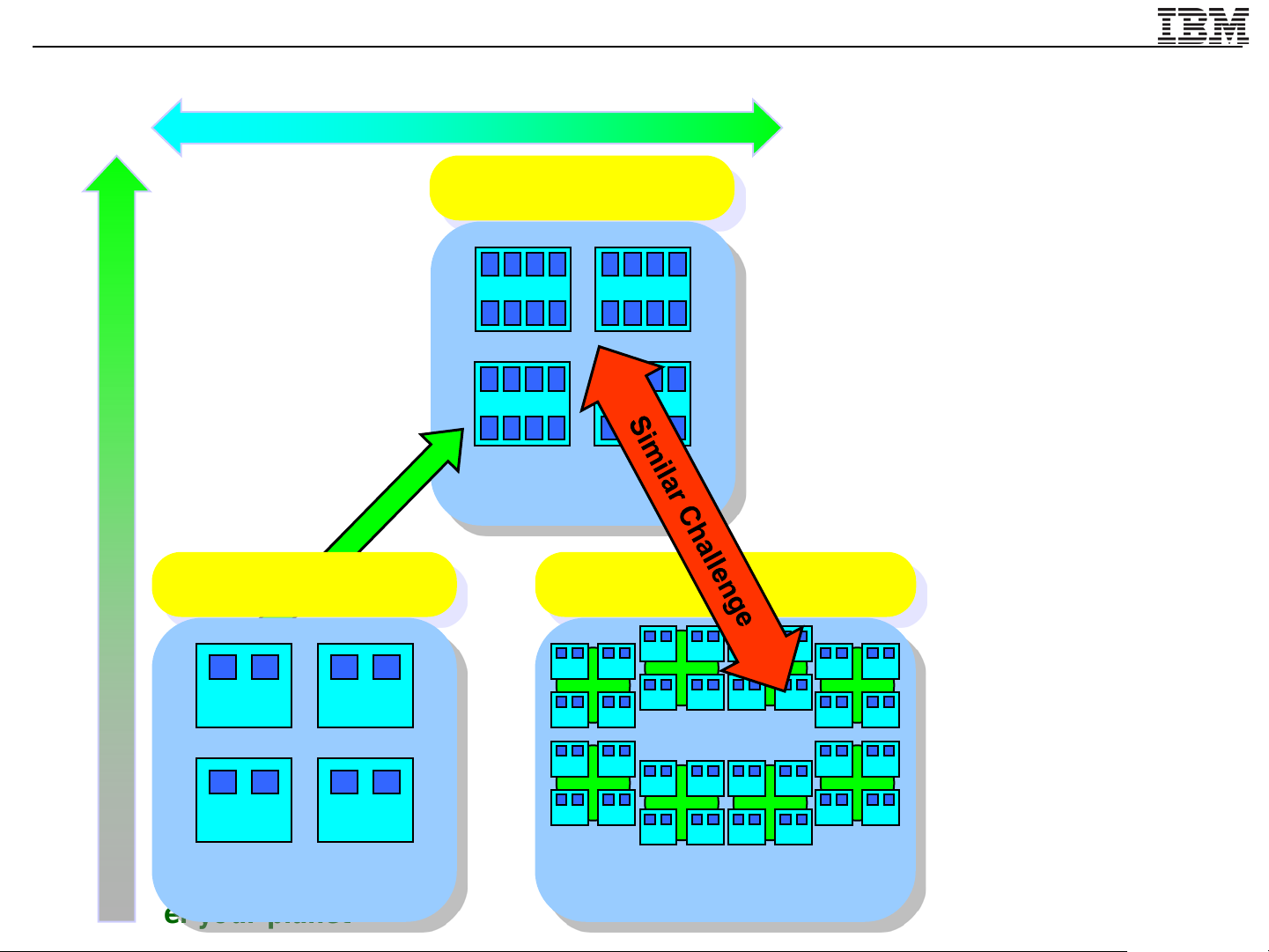

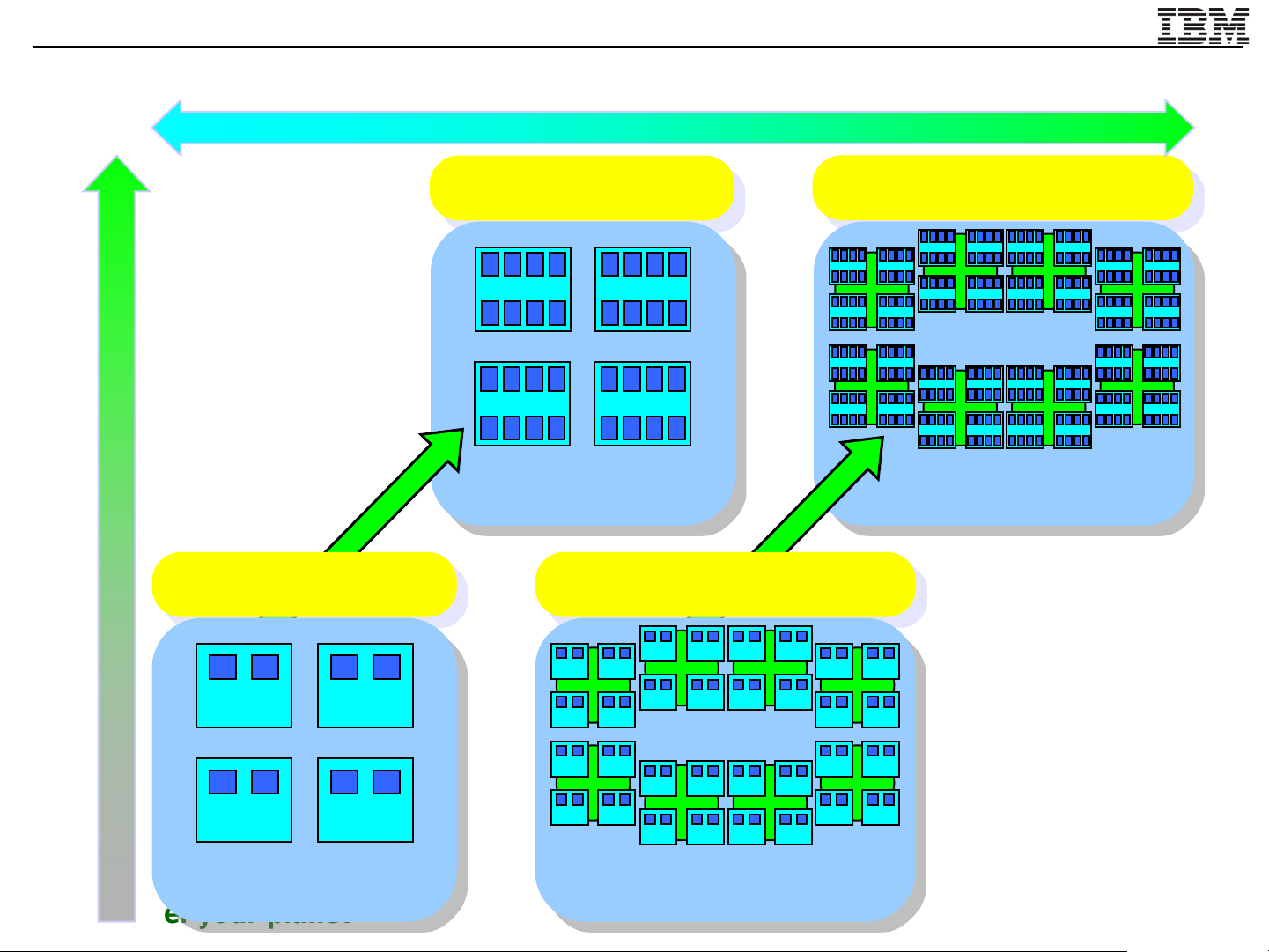

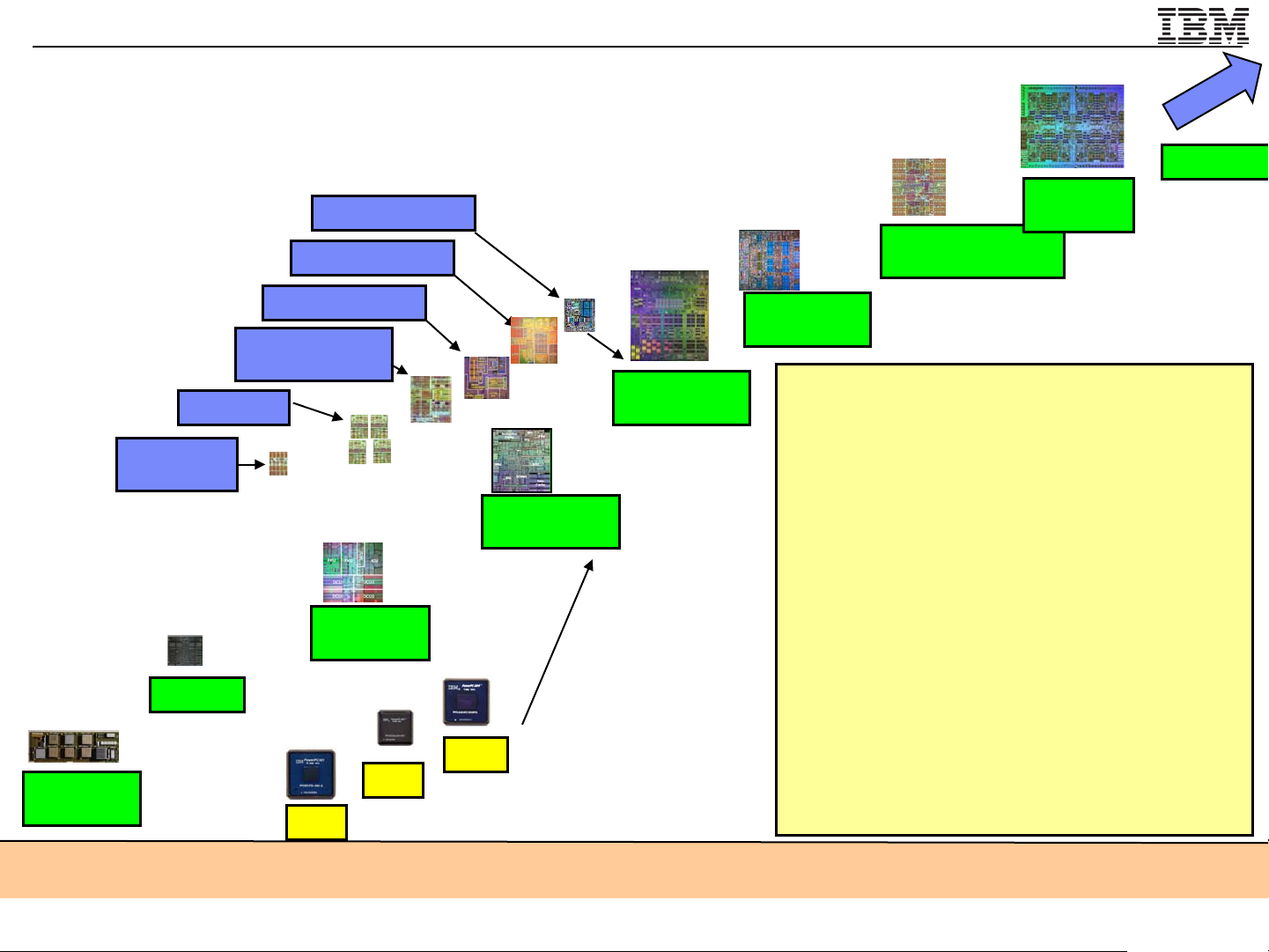

Single Image Virtualized/Cloud

Trends in Server Evolution

Emerging Entry Server

Virtualiz ed/Cloud Platform

- A simple matter of riding

the multi-core trend?

- Ad d more core s to the die,

Enabled by:

8-core

8-core

- Technology

- Innovation

Driven by:

8-core

8-core

- IT Evolution

- Economics

Time

Traditi onal Entry Server

Single Image Platform

16 to 32-way SMP Server

2 to 4 socket

Traditional High-End Server

Virtualiz ed Consolidation Platform

beef up some interfaces,

and scale to a large SMP?

2-core 2-core

2-core 2-core

2 to 4 socket

4 to 8-way SMP Server

Power your planet

8 to 32 socket

16 to 64-way SMP Server

* Statements regarding SMP servers

do not imply that IBM will introduce

a system with this capability.

© 2010 IBM Corporation

Page 8

IBM Power Systems

Single Image Virtualized/Cloud

Trends in Server Evolution

Emerging Entry Server

Virtualiz ed/Cloud Platform

- A simple matter of riding

the multi-core trend?

- Ad d more core s to the die,

Enabled by:

- Technology

- Innovation

8-core

8-core

beef up some interfaces,

and scale to a large SMP?

Not so simple:

Driven by:

8-core

- IT Evolution

- Economics

Time

Traditi onal Entry Server

Single Image Platform

16 to 32-way SMP Server

2 to 4 socket

8-core

- Emerging entry servers

have characteristics similar

to traditional high-end

large SMP servers

Traditional High-End Server

Virtualiz ed Consolidation Platform

Achieving solid virtual

machine performance

2-core 2-core

requires a Balanced

2-core 2-core

2 to 4 socket

4 to 8-way SMP Server

Power your planet

8 to 32 socket

16 to 64-way SMP Server

System Structure.

* Statements regarding SMP servers

do not imply that IBM will introduce

a system with this capability.

© 2010 IBM Corporation

Page 9

IBM Power Systems

Single Image Virtualized/Cloud UltraScale Cloud

Trends in Server Evolution

Enabled by:

Emerging Entry Server

Virtualiz ed/Cloud Platform

8-core

8-core

Emerging High-End Server

UltraScale Cloud Platform

- Technology

- Innovation

Driven by:

8-core

8-core

- IT Evolution

- Economics

Time

Traditi onal Entry Server

Single Image Platform

16 to 32-way SMP Server

2 to 4 socket

Traditional High-End Server

Virtualiz ed Consolidation Platform

8 to 32 socket

64 to 256-way SMP Server

Same enablers and

driving factors apply

at larger scale

2-core 2-core

2-core 2-core

2 to 4 socket

4 to 8-way SMP Server

Power your planet

8 to 32 socket

16 to 64-way SMP Server

* Statements regarding SMP servers

do not imply that IBM will introduce

a system with this capability.

© 2010 IBM Corporation

Page 10

IBM Power Systems

Challenge: How does POWER7 mai ntain the Bal ance?

Need to Amplify Effective

Socket Throughput

to Close Gap and

Achieve Potential

Compute Throughput Potential

Cache Hierarchy Technology

and Innovation

Socket Throughput Limitation

Power your planet

(Physical signal economics)

© 2010 IBM Corporation

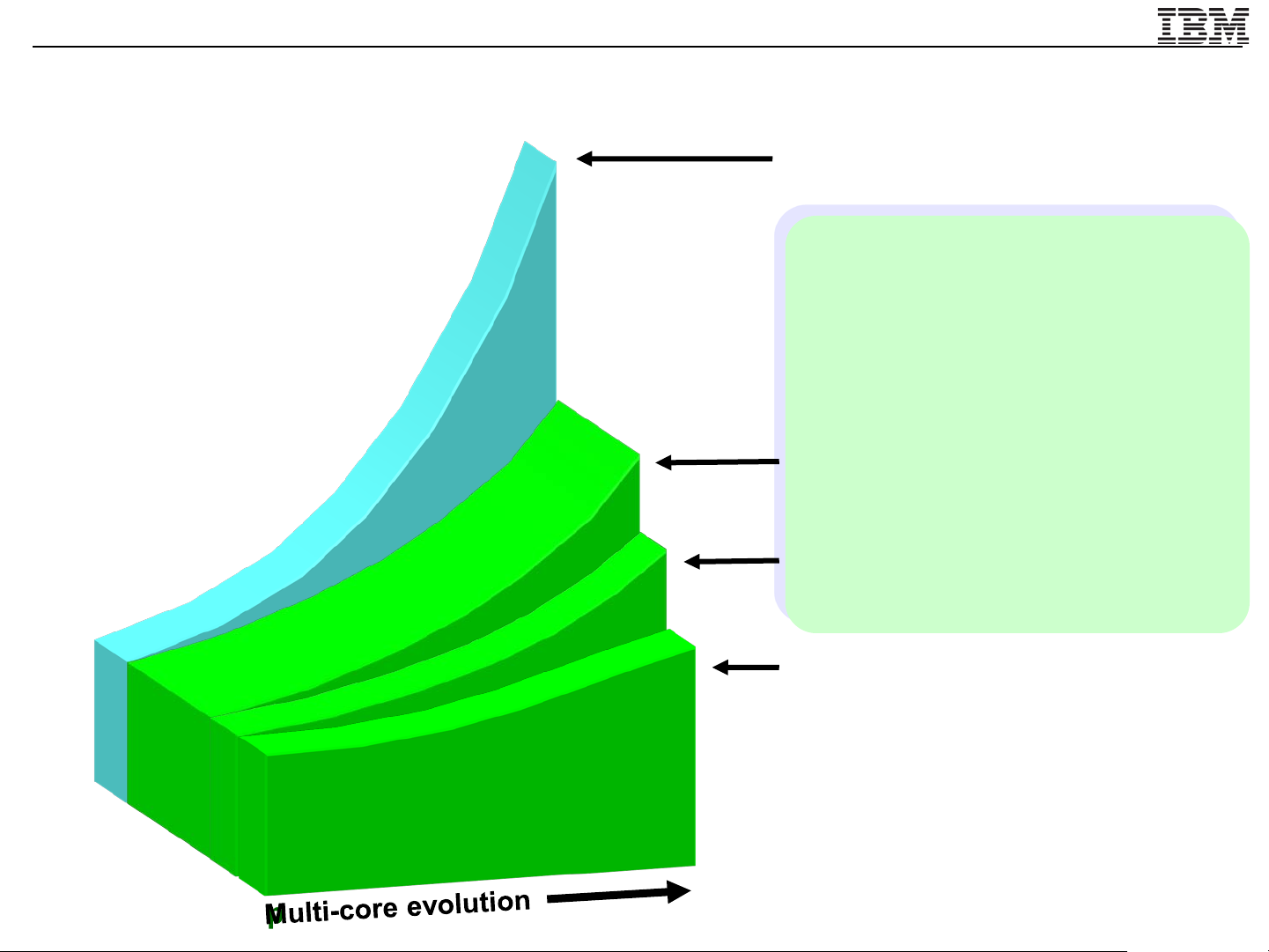

Page 11

IBM Power Systems

Challenge: How does POWER7 mai ntain the Bal ance?

Need to Amplify Effective

Socket Throughput

to Close Gap and

Achieve Potential

Compute Throughput Potential

Advances in Memory Subsystem

Cache Hierarchy Technology

and Innovation

Socket Throughput Limitation

Power your planet

(Physical signal economics)

© 2010 IBM Corporation

Page 12

IBM Power Systems

Challenge: How does POWER7 mai ntain the Bal ance?

Need to Amplify Effective

Socket Throughput

to Close Gap and

Achieve Potential

Compute Throughput Potential

Advances in Off-Chip Signaling

Technology

Advances in Memory Subsystem

Cache Hierarchy Technology

and Innovation

Socket Throughput Limitation

Power your planet

(Physical signal economics)

© 2010 IBM Corporation

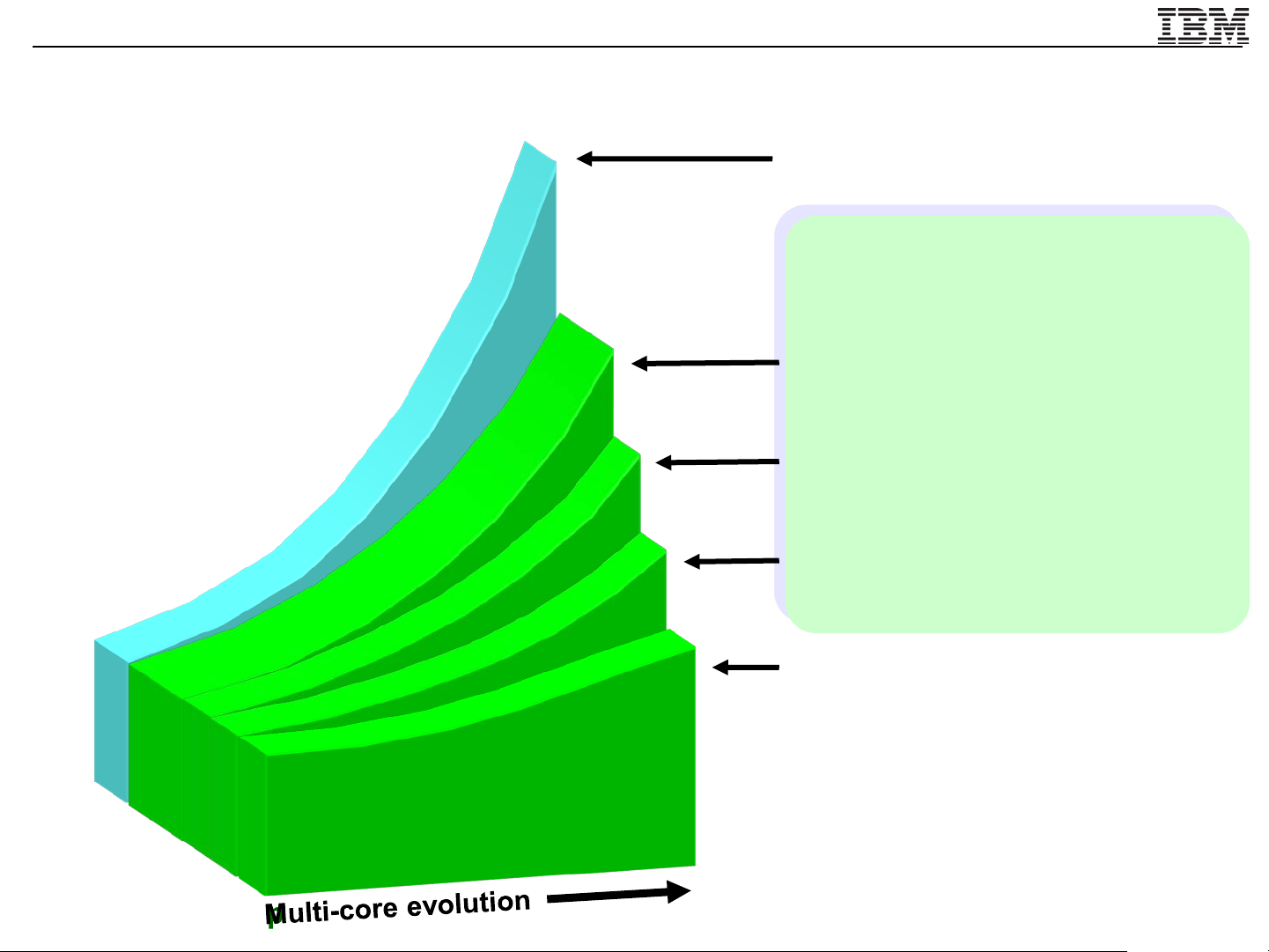

Page 13

IBM Power Systems

Challenge: How does POWER7 mai ntain the Bal ance?

Need to Amplify Effective

Socket Throughput

to Close Gap and

Achieve Potential

Compute Throughput Potential

Exploit Long Ter m Investmen t

in Coherence Innovation

Advances in Off-Chip Signaling

Technology

Advances in Memory Subsystem

Cache Hierarchy Technology

and Innovation

Socket Throughput Limitation

Power your planet

(Physical signal economics)

© 2010 IBM Corporation

Page 14

IBM Power Systems

POWER7 Processor

POWER7

Processor

Power your planet

© 2010 IBM Corporation

Page 15

IBM Power Systems

20+ Years of POWER Processors

45nm

1.0um

POWER1

-AMERICA’s

Muskie A35

-Cobra A10

-64 bit

.72um

RSC

RS64IV Sstar

RS64III Pulsar

RS64II North Star

RS64I Apache

BiCMOS

.5um

.35um

POWER2

P2SC

.6um

-601

.5um

.35um

TM

-603

.5um

.35um

.25um

604e

.25um

.22um

POWER3

-630

.18um

TM

180nm

POWER4

-Dual Core

TM

65nm

130nm

TM

POWER5

-SMT

POWER6

-Ultra High Frequency

TM

Major POWER® Innovation

-1990 RISC Architecture

-1994 SMP

-1995 Out of Order Execution

-1996 64 Bit Enterprise Architecture

-1997 Hardware Multi-Threading

-2001 Dual Core Processors

-2001 Large System Scaling

-2001 Shared Caches

-2003 On Chip Memory Control

-2003 SMT

-2006 Ultra High Frequency

-2006 Dual Scope Coherence Mgmt

-2006 Decimal Float/VSX

-2006 Processor Recovery/Sparing

-2009 Balanced Multi-core Pr ocesso r

-2009 On Chip EDRAM

Next Gen.

POWER7

-Multi-core

1990 1995 2000 2005 2010

Power your planet

* Dates represent approximate proc essor power-on dates, not sys tem availability

© 2010 IBM Corporation

Page 16

IBM Power Systems

IBM risc processors have many innovations..

pSeries p640,

64bit

P2,P3,P4

64bit

32bit

RS64

Apache

125

Power3

200+

RS64-II

Northstar

262.5

604e

332 / 375

1998

RS64-II

Northstar

340

1999 2000

p610

Power3-II

333 / 375 / 450

RS64-III

Pulsar

450

pSeries p620, p660, & p680

POWER4

1.1+GHz

RS64-IV

Sstar

600+ / 750

2001

POWER4

1.5GHz

Regatta

7450

800MHz/1.0GHz

2002

POWER4

1.8GHz

2003

Copper =

Power your planet

& SOI =

& low-k =

Σ

© 2010 IBM Corporation

Page 17

IBM Power Systems

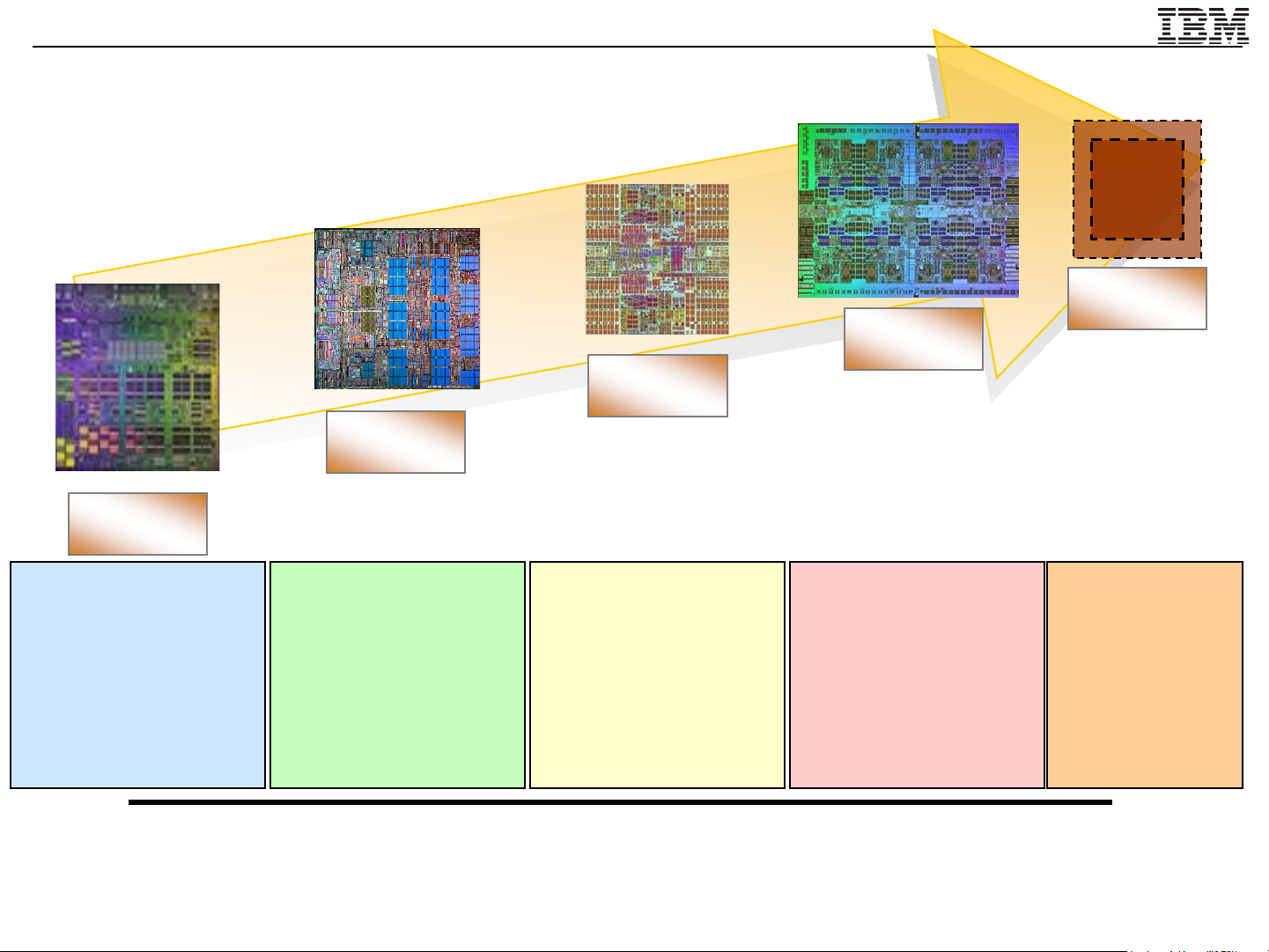

Processor Technology Roadmap

POWER6

65 nm

POWER5

130 nm

POWER4

180 nm

POWER8

POWER7

45 nm

Dual Core

Chip Multi Processing

Distributed Switch

Shared L2

Dynamic LPARs (32)

2001

Power your planet

Dual Core

Enhanced Scaling

SMT

Distributed Switch +

Core Parallelism +

FP Performance +

Memory bandwidth +

Virtualization

2004

Dual Core

High Frequencies

Virtualization +

Memory Subsystem +

Altivec

Instruction Retry

Dyn Energy Mgmt

SMT +

Protection Keys

2007

Multi Core

On-Chip eDRAM

Power Optimized Cores

Mem Subsystem ++

SMT++

Reliability +

VSM & VSX (AltiVec)

Protection Keys+

2010

Concept Phase

© 2010 IBM Corporation

Page 18

IBM Power Systems

Processor Designs contrast: 0.278nm H2O

POWER5 POWER5+ POWER6 POWER7

Technology 130 nm 90 nm 60 nm 45 nm

Size 389 mm

2

245 mm

2

341 mm

2

567 mm

Transistors 276 M 276 M 790 M 1.2 B

Cores 2 2 2 4 / 6 / 8

Frequencies 1.65 GHz 1.9 GHz 3-5 GHz 3-4 GHz

L2 Cache 1.9 MB Shared 1.9 MB Shared 4 MB / Core 256 KB / Core

L3 Cache 36 MB 36 MB 32 MB 4 MB / Core

Memory Cntrl 1 1 2 / 1 2

LPAR 10 / Core 10 / Core 10 / Core 10 / Core

Power your planet

© 2010 IBM Corporation

2

Page 19

IBM Power Systems

POWER6 / POWER7

POWER6

M

E

M

O

R

Y

L3

Mem

Ctrl

Alti

Vec

L3

Dir

SMT

Core

4MB

SMT

Core

4MB

L2

Bus Fabric Controller

GX Bus Cntrl

GX+ Bridge

Chip

to Chip

L2

to Chip

Alti

Vec

Chip

L3

Dir

Mem

Ctrl

L3

M

E

M

O

R

Y

Power your planet

© 2010 IBM Corporation

Page 20

IBM Power Systems

POWER6 / POWER7

POWER7

POWER6

M

L3

E

M

O

R

Y

Power your planet

Mem

Ctrl

Alti

Vec

SMT

Core

SMT

Core

Alti

Vec

L3 Cache

L3

Dir

4MB

L2

Bus Fabric Controller

GX Bus Cntrl

GX+ Bridge

Chip

to Chip

eDRAM (Embedded D y namic RAM )

L3 — 6:1 latency improvement (vs. external L3) and 2x BW improvements

Capacitor vs transister

1/3 space (vs 6Trn SRAM cell), 1/5 standby power of standard SRAM

Soft error rated 250x lower than SRAM

Savings of ~ 1.5B transistors over other RAM

4MB

L2

Chip

to Chip

L3

Dir

Mem

Ctrl

L3

M

E

M

O

R

Y

© 2010 IBM Corporation

Page 21

IBM Power Systems

POWER6 / POWER7

POWER7

M

E

M

O

R

Y

P

O

W

E

R

G

X

B

U

S

Mem

Ctrl

SMT

Core

Alti

L2 L2 L2 L2

L2 L2 L2 L2

Vec

L3

Dir

4MB

L2 L2 L2 L2

L2 L2 L2 L2

SMT

Core

Bus Fabric Controller

Bus Fabric Controller

SMT

Core

SMT

Core

L3 Cache

L2

SMT

Core

SMT

Core

SMT

Core

4MB

L2

SMT

Core

Alti

Vec

SMT

Core

L3

SMT

Dir

Core

Mem

Ctrl

GX Bus Cntrl

GX+ Bridge

Chip

to Chip

Footprints of working set:

Private footprints automatically migrates to fast local r eg i on 4m/cor e

Shared data automatically cloned to multiple private regions

Chip

to Chip

M

E

M

O

R

Y

Power your planet

© 2010 IBM Corporation

Page 22

IBM Power Systems

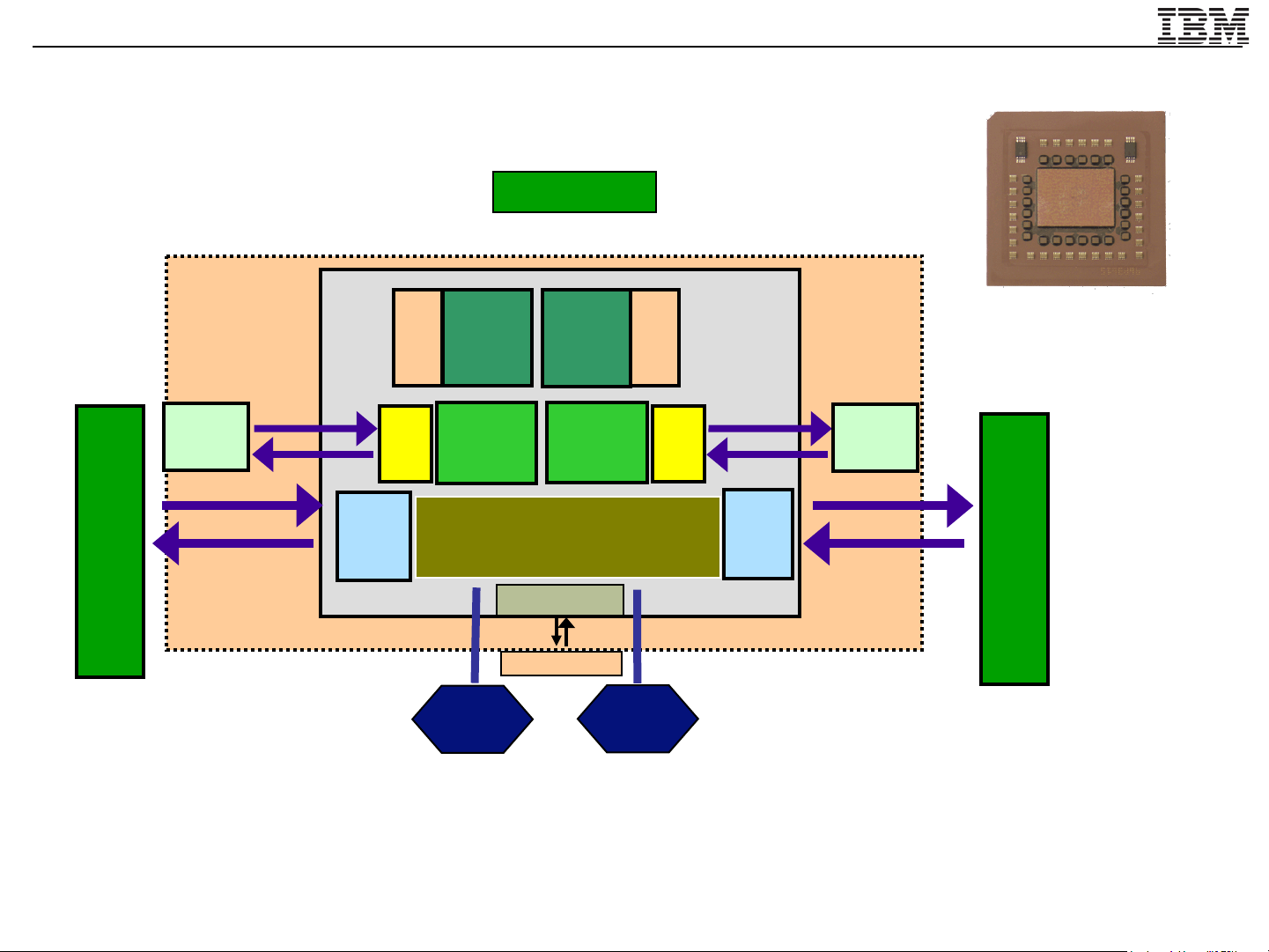

POWER7 Processor Chip

Cores : 8 ( 4 / 6 core options )

Local SMP Links

POWER7

CORE

L2 Cache

L2 Cache

POWER7

CORE

POWER7

F

CORE

A

S

T

L2 Cache

L3 REGION

L3 Cache and

Chip Interconnect

L2 Cache

POWER7

CORE

Remote SMP & I/O Links

POWER7

CORE

L2 Cache

L2 Cache

POWER7

CORE

Binary Compatibility with

POWER6

POWER7

CORE

L2 Cache

L2 Cache

POWER7

CORE

567mm

2

Technology:

45nm li’thography, Cu, SOI, eDRAM

Transistors: 1.2 B

Equivalent function of 2.7B

eDRAM efficiency

Eight processor cores

MC1MC0

12 execution units per core

4 Way SMT per core – up to 4 threads per core

32 Threads per chip

L1: 32 KB I Cache / 32 KB D Cache

L2: 256 KB per core

L3: Shared 32MB on chip eDRAM

Dual DDR3 Memory Controllers

90 GB/s Memory bandwidth per chip

Scalability up to 32 Sockets

360 GB/s SMP bandwidth/chip

20,000 coherent operations in flight

Power your planet

4th Generation SMP Fabric Bus

3rd Generation Multi-Threading

Energy Optimized Desig n

Enhanced GX System Buses

DDR3 memory

On-chip eDRAM L3

© 2010 IBM Corporation

Page 23

IBM Power Systems

Cache Hierarchy Technology a nd Innovat ion

Local SMP Links Remote SMP + I/O Links

Core

L2 Cache

Mem Ctrl Mem Ctrl

L2 Cache

Core

L3 Cache and Chip Interconnect

Core

L2 Cache

L2 Cache

Core

Core

L2 Cache

L2 Cache

Core

Core

L2 Cache

L2 Cache

Core

Power your planet

© 2010 IBM Corporation

Page 24

IBM Power Systems

Cache Hierarchy Technology a nd Innovat ion

Local SMP Links Remote SMP + I/O Links

Core

L2 Cache

Mem Ctrl Mem Ctrl

L3 Cache and Chip Interconnect

L2 Cache

Core

Core

L2 Cache

Fast Local

L3 Region

L2 Cache

Core

Core

L2 Cache

L2 Cache

Core

Core

L2 Cache

L2 Cache

Core

Power your planet

© 2010 IBM Corporation

Page 25

IBM Power Systems

POWER7 Core

64-bit PowerPC architecture v2.07

Execution Unit s

• 2 Fixed Point Units

• 2 Load Store Units

• 4 Double Precision Float ing Point Units

• 1 Branch

• 1 Condition Register

• 1 Vector Unit

• 1 Decimal Floating Point Uni t

• 6 Wide Dispatch

• Units include distributed Recovery Function

Out of Order Execution excellent for commercial load

ISU

IFU

CRU/BRU

DFU

FXU

L2 Cache

VSX

FPU

LSU

Modes: POWER6, POWER6+ and POWER7

e.g. partition mobility+

POWER7 continue s to s u pport VMX / Extends SIMD supp or t with VSX

2 VSX (Vec Scalar Ext) units that can each handle 2 Double-Precision FP instructions

8 FLOPS per cycles

VSX units can also handle 4 Single Precision instructions per cycle

VSX instruction set support for vector and scalar instructions

Power your planet

© 2010 IBM Corporation

Page 26

IBM Power Systems

Advances in Memory Subsystem

Memory Subsystem Requiremen t

for POWER Servers

Core

Need 10 to 20 GB/s

Sustained bandwidth

per Core

Need 16 to 32 GB

of Storage per Core

Challenge

for Multi-core POWER7

Socket Challenge:

4x growth in memory bandwidth

and capacity needed per socket.

System Challenge:

Packaging more memory into

similar volume with

similar energy and cooling

constraints.

Energy Constraints

Power your planet

© 2010 IBM Corporation

Page 27

IBM Power Systems

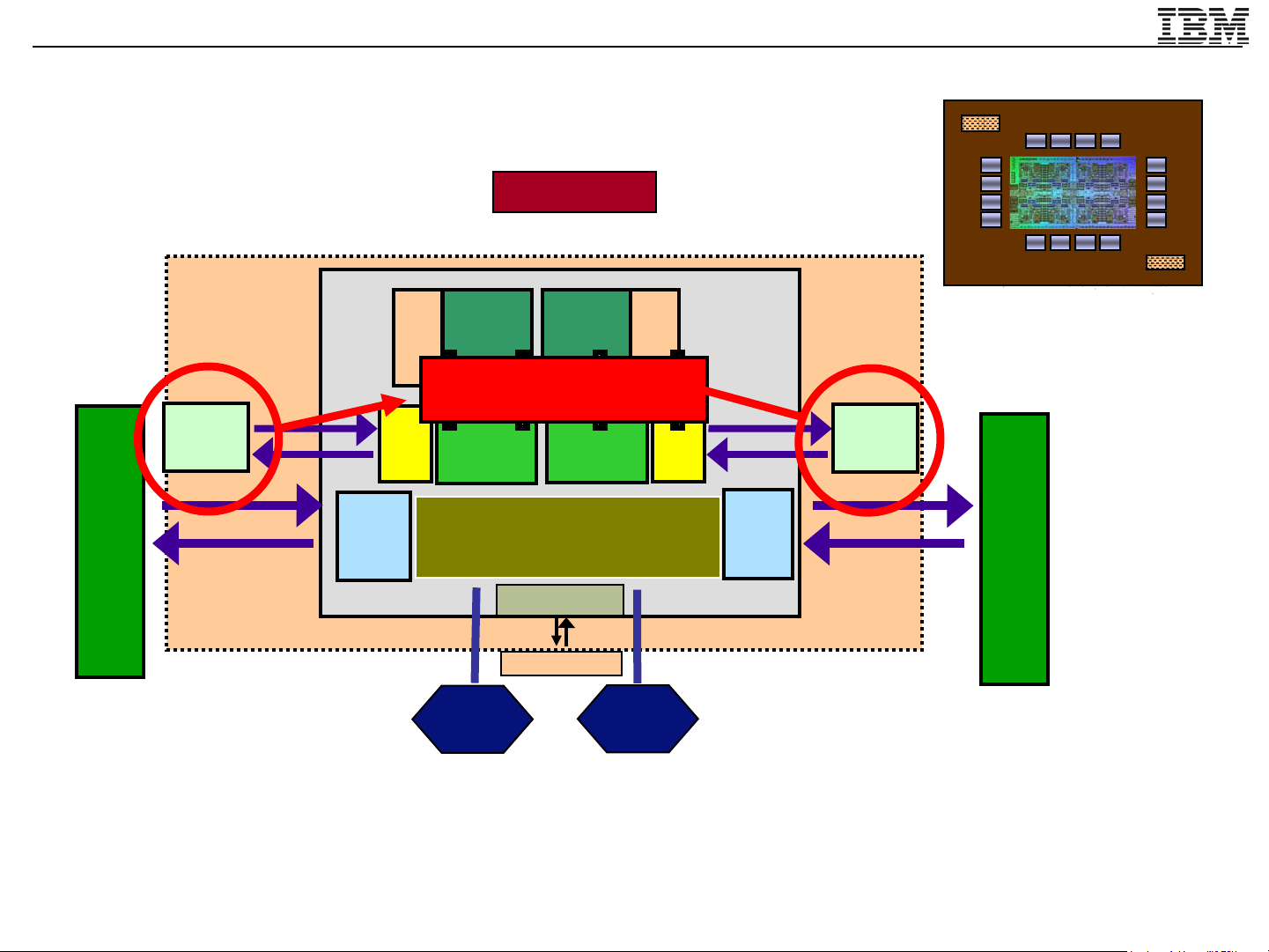

Advances in Memory Subsystem

Multi-faceted Solution

POWER7 Chip

Memory

Controller

Memory

Controller

Advanced

Buffer

Chip

1) Dual Integrated DDR3 Controllers

- Massive 16KB scheduling window

per POWER7 chip insures high

channel and DIMM utilization

- Sparse access acceleration

- Advanced Energy Management

- Numerous RAS advances

2) Eight high speed 6.4 GHz channels

- New low power differential signaling

- Sustained 100+ GB/s per socket

3) New DDR3 buffer chip architecture

- Larger capacity support (32 GB / core)

Power your planet

- Energy Management support

- RAS enablementh

4) DDR3 DRAMs

- Supports 800, 1066, 1333, and 1600

* Statements regarding memory subsystem features do not imply that IBM will introduce a system with these capabili ties.

© 2010 IBM Corporation

Page 28

IBM Power Systems

Memory Channel Bandwidth Evolution

POWER5

Memory Performance:

2x DIMM

POWER6

Memory Performance:

4x DIMM

POWER7

Memory Performance:

6x DIMM

D

D

D

D

R

R

3

3

D

D

D

D

R

R

3

3

D

D

D

D

R

R

3

3

D

D

D

R

3

D

D

D

R

R

3

3

D

D

R

3

DDR2 @ 553 MHz

Effective Bandwidth:

1.1 GB/s

Power your planet

DDR2 @ 553 / 667 MHz

Effective Bandwidth:

2.6 GB/sec

DDR3 @ 1066 MHz

Effective Bandwidth:

6.4 GB/sec

© 2010 IBM Corporation

Page 29

IBM Power Systems

Exploit Long Term Investment in Coherence Innovation

Local SMP Links Remote SMP + I/O Links

Core

L2 Cache

Mem Ctrl Mem Ctrl

L2 Cache

Core

L3 Cache and Chip Interconnect

Core

L2 Cache

L2 Cache

Core

Core

L2 Cache

L2 Cache

Core

Core

L2 Cache

L2 Cache

Core

Using local and remote SMP links, up to 32 POWER7 chips are connected

Power your planet

© 2010 IBM Corporation

Page 30

IBM Power Systems

Exploit Long Term Investment in Coherence Innovation

Up to 32 POWER7 chips form a massive SMP system.

Power your planet

* Statements regarding SMP servers

do not imply that IBM will introduce

a system with this capability.

© 2010 IBM Corporation

Page 31

IBM Power Systems

Multi-threading Evolut ion

S80 HMT

Single thread Out of Order

FX0

FX1

FP0

FP1

LS0

LS1

BRX

CRL

POWER5 2 Way SMT

FX0

FX1

FP0

FP1

LS0

LS1

BRX

CRL

S80 Hardware Multi-thread

FX0

FX1

FP0

FP1

LS0

LS1

BRX

CRL

POWER7 4 Way SMT

FX0

FX1

FP0

FP1

LS0

LS1

BRX

CRL

No Thread Executing

Thread 2

Executing

Power your planet

Thread 0

Executing

Thread 3

Executing

Thread 1

Executing

© 2010 IBM Corporation

Page 32

IBM Power Systems

0

0.5

1

1.5

2

2.5

SMT4 SMT2 Single

0

0.5

1

1.5

2

2.5

SMT4 SMT2 Single

IBM Confidential

POWER7 Multi-threading Opti ons

TurboCore option

50% of the cores active

MaxCore option

All cores active

Power your planet

Based of rPerf workload

© 2010 IBM Corporation

Page 33

IBM Power Systems

0

0.5

1

1.5

2

SMT1 SMT2 SMT4

POWER7 SMT4

Requires POWE R 7 Mode

POWER6 Mode supports SMT1 and SMT2

Operating Sy st em Support

AIX 6.1 and AIX 7.1

IBM i 6.1 and 7.1

Linux

Dynamic Runtim e SM T scheduling

Spread work among cores to execute in

Standard Cache Option

All cores active

appropriate threaded mode

Can dynamical shift between modes as required:

SMT1 / SMT2 / SMT4

LPAR-wide SMT controls

ST, SMT2, SMT4 modes

smtctl / mpstat commands

Mixed SMT mode s su pported within sam e

LPAR

Requires use of “Resource Groups”

Power your planet

© 2010 IBM Corporation

Page 34

IBM Power Systems

POWER7 TurboCore Mode

Power 780 TurboCore Chip

TurboCore Chips: 4 available cores

Aggregation of L3 Caches of unused cores.

TurboCore chips have a 2X the L3 Cache

per Chip available

4 TurboCore Chips L3 = 32 MB

Performance gain over POWER6.

Provi des up to 1.5X per core to core

Chips run at higher frequency:

Power reduction of unused cores.

With “Reboot”, System can be reconfigur ed

to 8 core mode.

ASM Menus

CoreL2Core

P

O

W

E

R

G

X

B

U

S

L2

Core

POWER7 Chip

CoreL2Core

L2

32 MB

L3 Cache

L2

Core

L2

Core

L2

L2

Core

S

M

P

F

A

B

R

I

C

TurboCores

Power your planet

Memory Interface

Unused

Core

© 2010 IBM Corporation

Page 35

IBM Power Systems

TurboCore - Example

Single Node Power 780 system (maximum throughput)

One processor feature #4982 (0 of 16)

Two POWER7 processors

64 MB internal L3 cache

16 POWER7 cores @ 3.8 GHz

Up to 16 CoD processor core activation features #5469

Best total system capacity config urat io n

Single Node Power 780 system (TurboCore mode)

One processor feature #4982 (0 of 16)

Two POWER7 processors

64 MB internal L3 cache

System is configured for TurboCore mode

8 POWER7 cores @ 4.1 GHz available

Up to 8 CoD processor core activation features #5469

Up to 22% greater performance per core

Power your planet

X

X

TurboCore

Cores

X

X

X X

X X

Unused

Core

© 2010 IBM Corporation

Page 36

IBM Power Systems

POWER7 Processor

POWER7

Active Memory

Expansion

Power your planet

© 2010 IBM Corporation

Page 37

IBM Power Systems

Active Memory Expansion

True

Memory

True

Memory

True

Memory

Expanded

Memory

Expanded

Memory

Expanded

Memory

Effectively up

to 100% more

True

Memory

True

Memory

True

Memory

Expanded

Memory

POWER7 Advantage

Expand memory beyond physical limits

More effective server consolidation

Run more application workload / users per partition

Run more partitions and more workload per server

The configuration is on a per-LPAR basis. When AME is enabled for a LPAR, the OS will compress a portion of the LPAR’s memory and leave the remaining portion of m emory

uncompressed.

This results in memory effectively being broken up into two pools – a compressed pool and an uncompressed pool.

The operating system will dynamically vary the amount of memory that is compressed based on the workload and the configuration of the LPAR.

The operating system will move data between the compressed and uncompressed mem ory pools based on the memory access patterns of apps.

When an application needs to access data that is compressed, the operating sys tem will automatically decompress the data and move it from the compressed pool to the uncompressed

pool, making it available to the appl i cation.

When the uncompressed pool is full, the operating system will compress data and move it from the uncompressed pool to the compressed pool. This compression and decompression

activity is transparent to the application.

Because Active Memory Expansion relies on memory compression, some additional CPU utilization will be consumed when Active Memory Expansion is in-use. The amount of additional

CPU utilization needed for Active Memory Expansion will vary based on the workload and the level of memory expansion being used.

Expanded

Memory

Expanded

Memory

memory

Power your planet

© 2010 IBM Corporation

Page 38

IBM Power Systems

0

5

10

15

#10

#9

#8

#7

#6

#5

#4

#3

#2

#1

Active Memory Expansion & Active Memory Sharing

Active Memory Expansion

Effectively gives more memory

capacity to the partition using

compression / decompression of

the contents in true memor y

AIX partitions only

Active Memory Sharing

Moves memory from one partition

to another

Best fit when one partition is not

busy when another partition is

busy

AIX, IBM i, and Linux partitions

Active Memory Expansion Active Memory Sharing

Supported, potentially a very nice option

Considerations

Only AIX partitions using Active Memory Expansion

Active Memory Expansion value is dependent upon com pressi bilit y of

data and available CPU resource

Power your planet

© 2010 IBM Corporation

Page 39

IBM Power Systems

Active Memory Expansion

Innovative POWER7 technology

For AIX 6.1 or later

For POWER7 servers

Uses compression/decompression to effectively expand the true physical

memory available for client workloads

Often a small amount of processor resource provides a significant incr ease in

the effective memory maximum

Processor resource part of AIX partition’s resource and licensing

Actual expansion results dependent upon how “com pressi ble” t he data being

used in the application

A SAP ERP sample workload shows up to 100% expansion,

Your results will vary

Estimator tool and free trial available

Will not compress AIX kernel

Will not compress pinned memory pages (pinned pages to see)

Will not compress File memory pages incl. code, cache & mmap (numperm to see)

Already compressed data (e.g. compress database objects) will not compress well

Computational memory good target (data:heap/stack, but not the code)

Localized memory access pattern works well with AME

Power your planet

© 2010 IBM Corporation

Page 40

IBM Power Systems

Excellent Compression Targets

Data only used on program initialization

Pages allocated but unused = full of zeros/blanks

Pages with lots of repeat data like database r eco r ds

Access Pattern

Some hot pages, some warm, some freezing

All pages equally used (HPC) – not so good

How can I work that out?

Power your planet

© 2010 IBM Corporation

Page 41

IBM Power Systems

What is your Plan?

10GB

Memory Shrinking

for supporting more lpars

or workloads

Looks like 10GB but

is actually 8GB

Memory Growing

for constrained lpar

10GB

But want 14GB to

improve performance

2GB released

for another LPAR

Power your planet

Actually still using 10 GB but

looks like 14 GB

© 2010 IBM Corporation

Page 42

IBM Power Systems

Permanent Enablement - Chargeable

One feature per server

No matter how many partitions use it

Permanent enablem ent with new server or v ia MES order

Enablement “V E T ” code applied to the VP D anchor card

Once enabled: no mechanism to move it to a different server

Power 750 & Power 755

#4792 AME E nabl em ent Feature

Power 770 & Power 780

#4791 AME E nabl em ent Feature

One-time, 60-day trial - No charge

Request via Capacity on Demand Web page

www.ibm.com/systems/power/hardware/cod/

Power your planet

© 2010 IBM Corporation

Page 43

IBM Power Systems

Active Memory Expansion – Client Deployment

1

Planning Tool

A. Part of AIX 6.1 TL4

B.

Calculates data

compressibility

estimates CPU

overhead due to

Active Memory

Expansion

C. Provides initial

recommendations

Estimated Results

&

2

60-Day Tri al

A. One-time, temporarily

enablement

B. Config LPAR based

on planning tool

C. Use AIX tools to

monitor Act Mem Exp

environment

D. Tune based on actual

results

Actual Results

3

Deploy into Product ion

A. Permanently enable

Active Memory

Expansion

B. Deploy workload

into production

C. Continue to monitor

workload using AIX

performance tools

CPU Utilization

Memory Expansion

Power your planet

CPU Utilization

Memory Expansion

App. Performance

Memory Expansion

Performance

Time

© 2010 IBM Corporation

Page 44

IBM Power Systems

Active Memory Expansion - Planning Tool

amepat -- AME Planning and Advisory Tool

Active Memory Expansion Modeled Statistics:

----------------------Modeled Expanded Memory Size : 8.00 GB

This sample partition

Expansion True Memory Modeled Memory CPU Usage

Factor Modeled Size Gain Estimate

--------- -------------- ----------------- -----------

1.21 6.75 GB 1.25 GB [ 19%] 0.00

1.31 6.25 GB 1.75 GB [ 28%] 0.20

1.41 5.75 GB 2.25 GB [ 39%] 0.35

1.51 5.50 GB 2.50 GB[ 45%] 0.58

1.61 5.00 GB 3.00 GB [ 60%] 1.46

Active Memory Expansion Recommendation:

--------------------The recommended AME configuration for this workload is to configure

the LPAR with a memory size of 5.50 GB and to configure a memory

expansion factor of 1.51. This will result in a memory expansion of

45% from the LPAR's current memory size. With this configuration,

the estimated CPU usage due to Active Memory Expansion is

approximately 0.58 physical processors, and the estimated overall

peak CPU resource required for the LPAR is 3.72 physical processors.

has fairly good

expansion potential

A nice “sweet” spot for

this partition appears

to be 45% expansion

• 2.5 GB gained memory

• Usi ng about 0.58 cores

additional CPU

resource

Tool included in AIX 6.1 TL4 SP2

Run tool in the partition of interest for memory expansion.

Input desired expanded memory size. Tool outputs different real memory

and CPU resource comb inations to achieve the desired effective memory.

Power your planet

© 2010 IBM Corporation

Page 45

IBM Power Systems

How do we switch AME on?

Power your planet

© 2010 IBM Corporation

Page 46

IBM Power Systems

Is the machine AME Capable?

Power your planet

HMC

Server Properties

Capabilities

then scroll to the bottom

© 2010 IBM Corporation

Page 47

IBM Power Systems

Activate on AME on the LPAR profi le

Hard reboot (not restart ) to

activate LPAR in AME mode

Expansion Factor:

Power your planet

1.0 = AM E on but inactive

1.2 to 1.5 = Good start point

10.0 = suicidal !

© 2010 IBM Corporation

Page 48

IBM Power Systems

Dynamically changing the Expansion Factor

Use Dynamic LP AR Memory Add/Remove

and change the Expansion Factor

Power your planet

© 2010 IBM Corporation

Page 49

IBM Power Systems

Monitoring Active Memory Expansion in use

Power your planet

© 2010 IBM Corporation

Page 50

IBM Power Systems

POWER7

TPMD

Power your planet

© 2010 IBM Corporation

Page 51

IBM Power Systems

TPMD: Thermal Power Manageme nt Device

TPMD card is part of the base hardware confi guration.

Residing on the processor planar

TPMD function is comprised of a risk processor and data acquisition

TPMD monitor power usage and temperature s in real time

Responsible for thermal protection of the processor cards

Can adjust t he processor power and performance in real time.

If the temperature ex ceeds an upper (f unctional) threshold, TPMD

actively reduces power consumption by reducing processor voltage

and frequency or throttling memory as needed.

If the t emperat ure is lower than upper (functional) threshold, TPMD

will allows POWER7 cores to “Over clock

” if workloads demands are

present.

~10% up clock speed, beneficial for cpu intensive workload

Power your planet

© 2010 IBM Corporation

Page 52

IBM Power Systems

3

3.2

3.4

3.6

3.8

4

4.2

4.4

Nominal Over Clock

POWER7 “Over Clock” Uplift

Power your planet

© 2010 IBM Corporation

Page 53

IBM Power Systems

EnergyScale

EnergyScale is IBM Trademark. It consists of a built-in Thermal Power

Management Device (TPMD) card and Power Executive software.

IBM Systems Director is also required to manage Energy-Scale functions.

EnergyScale is used to dynamically optimizes the processor performance

versus processor power and system workload.

IBM Systems Director is also required to manage AEM functions and

supports the following functions:

• Power Trending

• Thermal Reporting

• Static Energy Saver Mode

• Dynamic Energy Saver Mode

• Energy Capping

• Soft Energy Capping

• Processor Nap

• Energy Optimized Fan Control

• Altitude Input

• Processor Folding

Power your planet

© 2010 IBM Corporation

53

Page 54

IBM Power Systems

What is ENERGY STAR?

ENERGY STAR is a program developed by the U.S.

Environmental Protection Agency (EPA) to reduce

energy consumption

Voluntary labeling program designed to identify and

promote energy efficient products

Computer servers that earn EPA’s ENERGY STAR

include:

Power 750 Express

Efficient power supplies that have smaller conversion losses and

generate less waste heat,

Capabilities to measure real time power use

Advanced power management features

Power and Performance Data Sheet

Power 750 Express and Power 755 are the first RISC

or Itanium ENERGY STAR-qualified server

Power your planet

© 2010 IBM Corporation

Page 55

IBM Power Systems

Power W orkload

Optimization

Power your planet

© 2010 IBM Corporation

Page 56

IBM Power Systems

Power Workload Optimization – the new features

Power Systems offers b alanced systems desig ns

that automatically optimize workload performance

and capacity at either a system or VM level

✓ TurboCore™ for max per core performance for databases

✓ MaxCore for incredible parallelization and high capacity

✓ Intelligent Threads utilize more threads when workloads benefit

✓ Intelligent Cache technology optimizes cache utilization flowing it from core to core

✓ Intelligent Energy Optimization maximizes performance when thermal conditions allow

✓ Active Memory™ Expansion provides more memory for SAP

✓ Solid State Drives optimize high I/O access applications

Workload-Optimizing Features make POWER7

#1 in Transaction and Throughput Computing

Power your planet

© 2010 IBM Corporation

Page 57

IBM Power Systems

POWER7

OS Support

Power your planet

© 2010 IBM Corporation

Page 58

IBM Power Systems

58

Power your planet

© 2010 IBM Corporation

Page 59

IBM Power Systems

POWER7 based Systems provide two modes for each LPAR:

POWER6 & POWER6+ ,POWER7

P6 MODE (and P6+)* P7 MODE Customer Value

2-Thread SMT 4-Thread SMT

8 Storage Keys

16 Storage Keys in P6+

VMX (Vector Multimedia

Extension / AltiV ec)

Affinity OFF by Default On by Default

64-core/128-thread Scaling 32-core / 128-thread Scaling

EnergyScale CPU Idle EnergyScale CPU Idle and Folding

32 Storage Keys

VSX (Vector Scalar Extension)

3-tier Memory , MicroPartition Affinity

64-core / 256-thread Scaling

256-core / 1024-thread Scaling

with NAP and SLEEP

吐能力、CPU 利用率

RAS、数据隔离的颗粒度、提升应用

键的使用

高性能计算

提升系统性能

高可扩展、服务器整合

提升能源效率

N/A Active Memory Expansion

Power your planet

扩展内存容量

© 2010 IBM Corporation

Page 60

IBM Power Systems

OS Support on POWER7: IBM i ,AIX and Linux

Max Cores

IBM i

Release

POWER6 Mode POWER7 Mode

IBM i 6.1 32 / 64 32 / 128

Special Support 64/128 32 / 128

IBM i 7.1 32 / 64 32 / 128

Special Support 64/128 64 / 256

& Threads Supported

Linux

Max Cores

AIX

Release/TL

POWER6 Mode POWER7 Mode

AIX 5.3

(All TL9,10,11,12)

AIX 6.1 TL2, TL3 64 / 128 N/A

AIX 6.1 TL4 64 / 128 64 / 256

AIX 6.1 TL5 64 / 128 64 / 256

AIX 7.1 64 / 128 256 / 1024

& Threads Supported

64 / 128 N/A

Max Processors

& Threads Supported

POWER6 Mode POWER7 Mode

RHEL 5 ( Updates new er than U4) 64 / 128 N/A

SLES 10 SP# and newer 64 / 128 N/A

SLES 11 ( All Service Packs) 64 / 128 256 / 1024

RHEL 6 (Next major RHEL version) 64 / 128 256 / 1024

Power your planet

© 2010 IBM Corporation

Page 61

IBM Power Systems

2009 – 20 11 AIX TL Roadmap

AIX 5.3

TL8

TL9

TL9

TL10

TL10

AIX 6.1

TL1

TL2

TL2

TL3

TL3

TL11

TL11

TL4

TL4

SP

SP

04/2010 10/2010

POWER7 Hardware Support

SP

SP

TL12

TL12

SP

SP

TL5

TL5

TL6

04/2011 10/201110/2009

SP

Service Pack

POWER7 Support

Power your planet

TL7

TL8

TL0

TL1

AIX 7.1

TL2

© 2010 IBM Corporation

Page 62

IBM Power Systems

AIX support for POWER7

AIX supports Power 750, 755, 770, and 780 with P OWER7

processors offering more performance, energy

efficiency and scalab il ity

Initial AIX Levels supported

AIX 6 Technology Level 4 SP3 (GA 2/12)

AIX 5.3 Technology Level 11 SP2 (GA 3/16)

April AIX Technology Levels

AIX 6 Technology Level 5 (GA 4/23)

AIX 5.3 Technology Level 12 (GA 4/23)

Prior Technology levels

AIX 6 Technology Levels 2 and 3 (June 2010)

AIX 5.3 Technology Levels 9 and 10 (May 2010)

Power your planet

© 2010 IBM Corporation

Page 63

IBM Power Systems

POWER Virtualization Features

DLP A R Processor add/remove

DLPAR I/O adapter add/remove

DLPAR Memory add

DLPAR Memory remove

Micro Partitioning

Capacity Upgrade on Demand

Virtual I/O Server

Integrated Virtualization Manager

Virtual SCSI (VIO Server)

Virtual Ether net ( VIO Serv er )

Workload Partitions (AIX only)

Application Mobility (AIX only)

Lx86 (Statement of direction for POWER7)

Shared Dedicated Capacit y (POWER6)

AIX

5.3

Yes Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes Yes

Yes Yes Yes No No Yes

Yes Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes Yes

No Yes No No No No

No Yes No No No No

No No No Yes Yes Yes

Yes Yes Yes Yes Yes Yes

AIX

6.1

IBM i

6.1.1

RHEL

5.4

SLES

V10 SP3

SLES

V11

Multiple Processor Pools (POWER6)

Live Partition Mobility (POWER6)

N_Port ID Virtualization (POWER6)

Active Memory Expansion (POWER7)

Active Memory Sharing (POWER6)

Integrated Virtual Ethernet (POWER6)

Activ e Memory Expansion (POWER7 / AIX 6.1)

Note: Some features are supported with specific fix levels or only on specific hardware models. Check the appropriate documentation.

Power your planet

Yes Yes Yes Yes Yes Yes

Yes Yes No Yes Yes Yes

Yes Yes Yes Yes No Yes

No Yes No No No No

Yes Yes Yes No No Yes

Yes Yes Yes Yes Yes Yes

No Yes No No No No

© 2010 IBM Corporation

Page 64

IBM Power Systems

Partition Mobility

POWER6

POWER6+

POWER7

Binary Compatibility between POWER6 and POWER7

Leverage POWER6 / POWER6+ Compatibility Mode

Migrate partitions between POWER6 and POWER7 Servers

Forward and Backward

Power your planet

© 2010 IBM Corporation

Page 65

IBM Power Systems

65

Power your planet

© 2010 IBM Corporation

Loading...

Loading...