Page 1

Front cover

IBM Power 595

Technical Overview and Introduction

PowerVM virtualization technology

including Live Partition Mobility

World-class performance and

flexibility

Mainframe-inspired

continuous availability

ibm.com/redbooks

Charlie Cler

Carlo Costantini

Redpaper

Page 2

Page 3

International Technical Support Organization

IBM Power 595 Technical Overview and Introduction

August 2008

REDP-4440-00

Page 4

Note: Before using this information and the product it supports, read the information in “Notices” on

page vii.

First Edition (August 2008)

This edition applies to the IBM Power Systems 595 (9119-FHA), IBMs most powerful Power Systems offering.

© Copyright International Business Machines Corporation 2008. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule

Contract with IBM Corp.

Page 5

Contents

Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . viii

Preface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

The team that wrote this paper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

Become a published author . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .x

Comments welcome. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .x

Chapter 1. General description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Model overview and attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.2 Installation planning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2.1 Physical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2.2 Service clearances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2.3 Operating environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.2.4 Power requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.3 Minimum configuration requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.3.1 Minimum required processor card features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.3.2 Memory features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.3.3 System disks and media features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.3.4 I/O Drawers attachment (attaching using RIO-2 or 12x I/O loop adapters) . . . . . 15

1.3.5 IBM i, AIX, Linux for Power I/O considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.3.6 Hardware Management Console models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.3.7 Model conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.4 Racks power and cooling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.4.1 Door kit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

1.4.2 Rear door heat exchanger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.4.3 Power subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.5 Operating system support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

1.5.1 IBM AIX 5.3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1.5.2 IBM AIX V6.1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1.5.3 IBM i 5.4 (formerly IBM i5/OS V5R4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

1.5.4 IBM i 6.1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

1.5.5 Linux for Power Systems summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Chapter 2. Architectural and technical overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.1 System design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.1.1 Design highlights. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

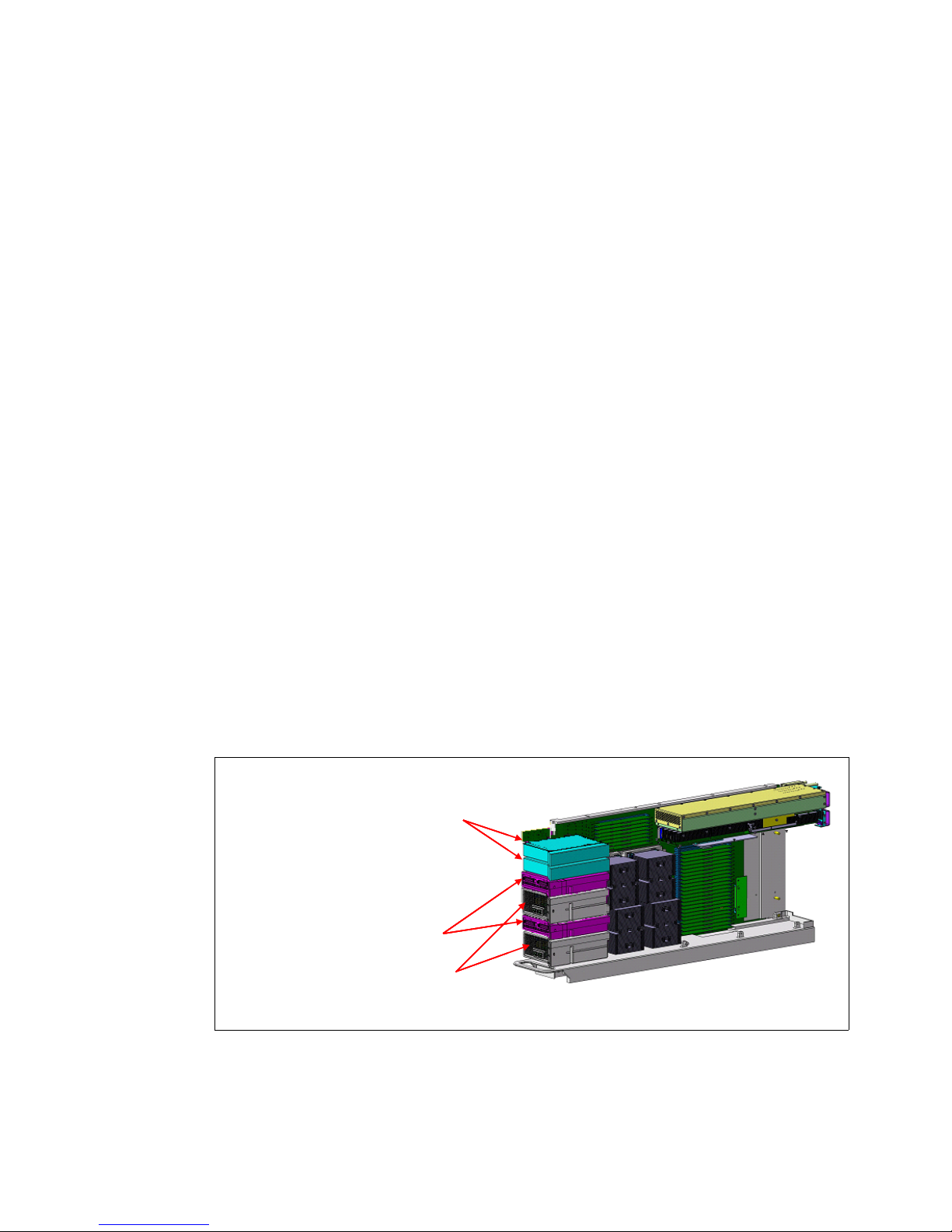

2.1.2 Center electronic complex (CEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.1.3 CEC midplane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.1.4 System control structure (SCS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.1.5 System controller (SC) card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.1.6 System VPD cards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.1.7 Oscillator card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2.1.8 Node controller card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2.1.9 DC converter assembly (DCA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.2 System buses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.2.1 System interconnects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.2.2 I/O subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

2.3 Bulk power assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

© Copyright IBM Corp. 2008. All rights reserved. iii

Page 6

2.3.1 Bulk power hub (BPH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

2.3.2 Bulk power controller (BPC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

2.3.3 Bulk power distribution (BPD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

2.3.4 Bulk power regulators (BPR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

2.3.5 Bulk power fan (BPF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

2.3.6 Integrated battery feature (IBF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.3.7 POWER6 EnergyScale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.4 System cooling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

2.5 Light strips . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

2.6 Processor books . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

2.6.1 POWER6 processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

2.6.2 Decimal floating point . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

2.6.3 AltiVec and Single Instruction, Multiple Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

2.7 Memory subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

2.7.1 Memory bandwidth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

2.7.2 Available memory features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

2.7.3 Memory configuration and placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

2.8 Internal I/O subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

2.8.1 Connection technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

2.8.2 Internal I/O drawers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

2.8.3 Internal I/O drawer attachment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

2.8.4 Single loop (full-drawer) cabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

2.8.5 Dual looped (half-drawer) cabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

2.8.6 I/O drawer to I/O hub cabling sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

2.9 PCI adapter support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

2.9.1 LAN adapters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

2.9.2 SCSI adapters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

2.9.3 iSCSI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

2.9.4 SAS adapters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

2.9.5 Fibre Channel adapters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

2.9.6 Asynchronous, WAN, and modem adapters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

2.9.7 PCI-X Cryptographic Coprocessor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

2.9.8 IOP adapter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

2.9.9 RIO-2 PCI adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

2.9.10 USB and graphics adapters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

2.10 Internal storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

2.11 Media drawers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

2.11.1 Media drawer, 19-inch (7214-1U2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

2.11.2 DVD/Tape SAS External Storage Unit (#5720). . . . . . . . . . . . . . . . . . . . . . . . . . 99

2.12 External I/O enclosures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

2.12.1 TotalStorage EXP24 Disk Dwr (#5786). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

2.12.2 PCI Expansion Drawer (#5790) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

2.12.3 EXP 12S Expansion Drawer (#5886) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

2.13 Hardware Management Console (HMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

2.13.1 Determining the HMC serial number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

2.14 Advanced System Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

2.14.1 Accessing the ASMI using a Web browser . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

2.14.2 Accessing the ASMI using an ASCII console . . . . . . . . . . . . . . . . . . . . . . . . . . 104

2.14.3 Accessing the ASMI using an HMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

2.14.4 Server firmware. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Chapter 3. Virtualization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

3.1 Virtualization feature support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

iv IBM Power 595 Technical Overview and Introduction

Page 7

3.2 PowerVM and PowerVM editions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

3.3 Capacity on Demand. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

3.3.1 Permanent activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

3.3.2 On/Off CoD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

3.3.3 Utility CoD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

3.3.4 Trial CoD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

3.3.5 Capacity Backup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

3.4 POWER Hypervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

3.5 Logical partitioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

3.5.1 Dynamic logical partitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

3.5.2 Shared processor pool partitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

3.5.3 Shared dedicated capacity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

3.5.4 Multiple shared processor pools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

3.6 Virtual Ethernet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

3.7 Virtual I/O Server. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

3.7.1 Virtual SCSI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

3.7.2 Shared Ethernet Adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

3.8 PowerVM Lx86 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

3.9 PowerVM Live Partition Mobility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

3.10 AIX 6 workload partitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

3.11 System Planning Tool . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Chapter 4. Continuous availability and manageability . . . . . . . . . . . . . . . . . . . . . . . . 131

4.1 Reliability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

4.1.1 Designed for reliability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

4.1.2 Placement of components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

4.1.3 Continuous field monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

4.2 Availability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

4.2.1 Detecting and deallocating failing components. . . . . . . . . . . . . . . . . . . . . . . . . . 134

4.2.2 Special uncorrectable error handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

4.2.3 Cache protection mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

4.2.4 The input output subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

4.2.5 Redundant components and concurrent repair update. . . . . . . . . . . . . . . . . . . . 145

4.2.6 Availability in a partitioned environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

4.2.7 Operating system availability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

4.3 Serviceability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

4.3.1 Service environments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

4.3.2 Service processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

4.3.3 Detecting errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

4.3.4 Diagnosing problems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

4.3.5 Reporting problems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

4.3.6 Notifying the appropriate contacts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

4.3.7 Locating and repairing the problem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

4.4 Operating system support for RAS features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

4.5 Manageability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

4.5.1 Service processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

4.5.2 System diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

4.5.3 Electronic Service Agent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

4.5.4 Manage serviceable events with the HMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

4.5.5 Hardware user interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

4.5.6 IBM System p firmware maintenance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

4.5.7 Management Edition for AIX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

4.5.8 IBM Director . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Contents v

Page 8

4.6 Cluster solution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Related publications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

IBM Redbooks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Other publications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Online resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

How to get Redbooks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Help from IBM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

vi IBM Power 595 Technical Overview and Introduction

Page 9

Notices

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult

your local IBM representative for information on the products and services currently available in your area. Any

reference to an IBM product, program, or service is not intended to state or imply that only that IBM product,

program, or service may be used. Any functionally equivalent product, program, or service that does not

infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to

evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The

furnishing of this document does not give you any license to these patents. You can send license inquiries, in

writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive, Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such

provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION

PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR

IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT,

MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of

express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made

to the information herein; these changes will be incorporated in new editions of the publication. IBM may make

improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time

without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any

manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the

materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring

any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published

announcements or other publicly available sources. IBM has not tested those products and cannot confirm the

accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the

capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them

as completely as possible, the examples include the names of individuals, companies, brands, and products.

All of these names are fictitious and any similarity to the names and addresses used by an actual business

enterprise is entirely coincidental.

COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrate programming

techniques on various operating platforms. You may copy, modify, and distribute these sample programs in

any form without payment to IBM, for the purposes of developing, using, marketing or distributing application

programs conforming to the application programming interface for the operating platform for which the sample

programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore,

cannot guarantee or imply reliability, serviceability, or function of these programs.

© Copyright IBM Corp. 2008. All rights reserved. vii

Page 10

Trademarks

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines

Corporation in the United States, other countries, or both. These and other IBM trademarked terms are

marked on their first occurrence in this information with the appropriate symbol (® or ™), indicating US

registered or common law trademarks owned by IBM at the time this information was published. Such

trademarks may also be registered or common law trademarks in other countries. A current list of IBM

trademarks is available on the Web at http://www.ibm.com/legal/copytrade.shtml

The following terms are trademarks of the International Business Machines Corporation in the United States,

other countries, or both:

1350™

AIX 5L™

AIX®

BladeCenter®

Chipkill™

DB2®

DS8000™

Electronic Service Agent™

EnergyScale™

eServer™

HACMP™

i5/OS®

IBM®

iSeries®

Micro-Partitioning™

OpenPower®

OS/400®

POWER™

Power Architecture®

POWER Hypervisor™

POWER4™

POWER5™

POWER5+™

POWER6™

PowerHA™

PowerPC®

PowerVM™

Predictive Failure Analysis®

pSeries®

Rational®

Redbooks®

Redbooks (logo) ®

RS/6000®

System i™

System i5™

System p™

System p5™

System Storage™

System x™

System z™

Tivoli®

TotalStorage®

WebSphere®

Workload Partitions Manager™

z/OS®

The following terms are trademarks of other companies:

AMD, the AMD Arrow logo, and combinations thereof, are trademarks of Advanced Micro Devices, Inc.

Novell, SUSE, the Novell logo, and the N logo are registered trademarks of Novell, Inc. in the United States

and other countries.

ABAP, SAP NetWeaver, SAP, and SAP logos are trademarks or registered trademarks of SAP AG in Germany

and in several other countries.

Java, JVM, Power Management, Ultra, and all Java-based trademarks are trademarks of Sun Microsystems,

Inc. in the United States, other countries, or both.

Internet Explorer, Microsoft, and the Windows logo are trademarks of Microsoft Corporation in the United

States, other countries, or both.

Intel, Intel logo, Intel Inside logo, and Intel Centrino logo are trademarks or registered trademarks of Intel

Corporation or its subsidiaries in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries.

Linux is a trademark of Linus Torvalds in the United States, other countries, or both.

Other company, product, or service names may be trademarks or service marks of others.

viii IBM Power 595 Technical Overview and Introduction

Page 11

Preface

This IBM® Redpaper is a comprehensive guide describing the IBM Power 595 (9119-FHA)

enterprise-class IBM Power Systems server. The goal of this paper is to introduce several

technical aspects of this innovative server. The major hardware offerings and prominent

functions include:

The POWER6™ processor available at frequencies of 4.2 and 5.0 GHz

Specialized POWER6 DDR2 memory that provides improved bandwidth, capacity, and

Support for AIX®, IBM i, and Linux® for Power operating systems.

EnergyScale™ technology that provides features such as power trending, power-saving,

PowerVM™ virtualization

Mainframe levels of continuous availability.

This Redpaper is intended for professionals who want to acquire a better understanding of

Power Systems products, including:

Clients

Sales and marketing professionals

Technical support professionals

reliability

thermal measurement, and processor napping.

IBM Business Partners

Independent software vendors

This Redpaper expands the current set of IBM Power Systems documentation by providing a

desktop reference that offers a detailed technical description of the 595 system.

This Redpaper does not replace the latest marketing materials, tools, and other IBM

publications available, for example, at the IBM Systems Hardware Information Center

http://publib.boulder.ibm.com/infocenter/systems/scope/hw/index.jsp. It is intended as

an additional source of information that, together with existing sources, can be used to

enhance your knowledge of IBM server solutions.

The team that wrote this paper

This paper was produced by a team of specialists from around the world working at the

International Technical Support Organization, Austin Center.

Charlie Cler is an Executive IT Specialist for IBM in the United States. He has worked with

IBM Power Systems and related server technology for over 18 years. Charlie’s primary areas

of expertise include Power Systems processor virtualization and server consolidation. He

holds a masters degree in Mechanical Engineering from Purdue University with specialization

in robotics and computer graphics.

Carlo Costantini is a Certified IT Specialist for IBM and has over 30 years of experience with

IBM and IBM Business Partners. He currently works in Italy Power Systems Platforms as

Presales Field Technical Sales Support for IBM Sales Representatives and IBM Business

© Copyright IBM Corp. 2008. All rights reserved. ix

Page 12

Partners. Carlo has broad marketing experience and his current major areas of focus are

competition, sales, and technical sales support. He is a certified specialist for Power Systems

servers. He holds a masters degree in Electronic Engineering from Rome University.

The project manager that organized the production of this material was:

Scott Vetter, (PMP) is a Certified Executive Project Manager at the International Technical

Support Organization, Austin Center. He has enjoyed 23 years of rich and diverse experience

working for IBM in a variety of challenging roles. His latest efforts are directed at providing

world-class Power Systems Redbooks®, whitepapers, and workshop collateral.

Thanks to the following people for their contributions to this project:

Terry Brennan, Tim Damron, George Gaylord, Dan Henderson, Tenley Jackson,

Warren McCracken, Patrick O’Rourke, Paul Robertson, Todd Rosedahl, Scott Smylie,

Randy Swanberg, Doug Szerdi, Dave Williams

IBM Austin

Mark Applegate

Avnet

Become a published author

Join us for a two- to six-week residency program! Help write a book dealing with specific

products or solutions, while getting hands-on experience with leading-edge technologies. You

will have the opportunity to team with IBM technical professionals, Business Partners, and

Clients.

Your efforts will help increase product acceptance and client satisfaction. As a bonus, you will

develop a network of contacts in IBM development labs, and increase your productivity and

marketability.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

Comments welcome

Your comments are important to us!

We want our papers to be as helpful as possible. Send us your comments about this paper or

other IBM Redbooks in one of the following ways:

Use the online Contact us review Redbooks form found at:

ibm.com/redbooks

Send your comments in an e-mail to:

redbooks@us.ibm.com

Mail your comments to:

IBM Corporation, International Technical Support Organization

Dept. HYTD Mail Station P099

2455 South Road

Poughkeepsie, NY 12601-5400

x IBM Power 595 Technical Overview and Introduction

Page 13

Chapter 1. General description

IBM System i™ and IBM System p™ platforms are unifying the value of their servers into a

single and powerful lineup of IBM Power Systems servers based on POWER6-processor

technology with support for the IBM i operating system (formerly known as i5/OS®), IBM AIX,

and Linux for Power operating systems. This new single portfolio of Power Systems servers

offers industry-leading technology, continued IBM innovation, and the flexibility to deploy the

operating system that your business requires.

This publication provides overview and introductory-level technical information for the

POWER6-based IBM Power 595 server with Machine Type and Model (MTM) 9119-FHA.

1

The IBM Power 595 server is designed to help enterprises deploy the most cost-effective and

flexible IT infrastructure, while achieving the best application performance and increasing the

speed of deployment of new applications and services. As the most powerful member of the

IBM Power Systems family, the Power 595 server is engineered to deliver exceptional

performance, massive scalability and energy-efficient processing for a full range of complex,

mission-critical applications with the most demanding computing requirements.

Equipped with ultra-high frequency IBM POWER6 processors in up to 64-core, symmetric

multiprocessing (SMP) configurations, the Power 595 server is designed to scale rapidly and

seamlessly to address the changing needs of today's data centers. With advanced PowerVM

virtualization, EnergyScale technology, and Capacity on Demand (CoD) options, the

Power 595 is ready to help businesses take control of their IT infrastructure and confidently

consolidate multiple UNIX®-based, IBM i, and Linux application workloads onto a single

system.

© Copyright IBM Corp. 2008. All rights reserved. 1

Page 14

1.1 Model overview and attributes

The Power 595 server (9119-FHA) offers an expandable, high-end enterprise solution for

managing the computing requirements to enable your business to become an On Demand

Business. The Power 595 is an 8- to 64-core SMP system packaged in a 20U (EIA-unit) tall

central electronics complex (CEC) cage. The CEC is 50 inches tall, and housed in a 24-inch

wide rack. Up to 4 TB of memory are supported on the Power 595 server.

The Power 595 (9119-FHA) server consists of the following major components:

A 42U-tall, 24-inch system rack that houses the CEC, Bulk Power Assemblies (BPA) that

are located at the top of the rack, and I/O drawers that are located at the bottom of the

rack. A redundant power subsystem is standard. Battery backup is an optional feature.

CEC features include:

– A 20U-tall CEC housing that features the system backplane cooling fans, system

electronic components, and mounting slots for up to eight processor books.

– One to eight POWER6 processor books. Each processor book contains eight,

dual-threaded SMP cores that are packaged on four multi-chip modules (MCMs). Each

MCM contains one dual-core POWER6 processor supported by 4 MB of on-chip L2

cache (per core) and 32 MB of shared L3 cache. Each processor book also provides:

• Thirty-two DDR2 memory DIMM slots

• Support for up to four GX based I/O hub adapter cards (RIO-2 or 12x) for

connection to system I/O drawers

• Two Node Controller (NC) service processors (primary and redundant)

One or two optional Powered Expansion Racks, each with 32U of rack space for up to

eight, 4U I/O Expansion Drawers. Redundant Bulk Power Assemblies (BPA) are located at

the top of the Powered Expansion Rack. Optional battery backup capability is available.

Each Powered Expansion Rack supports one 42U bolt-on, nonpowered Expansion Rack

for support of additional I/O drawers.

One or two nonpowered Expansion Racks, each supporting up to seven 4U I/O Expansion

Drawers.

One to 30 I/O Expansion Drawers (maximum of 12 RIO-2), each containing 20 PCI-X slots

and 16 hot-swap SCSI-3 disk bays.

In addition to the 24 inch rack-mountable I/O drawers, also available are standard, 2

meters high, 19 inch I/O racks for mounting both SCSI and SAS disk drawers. Each disk

drawer is individually powered by redundant, 220 V power supplies. The disk drawers can

be configured for either RAID or non-RAID disk storage. A maximum of 40 SCSI drawers

(each with 24 disks), and 185 SAS drawers (each with 12 disks), can be mounted in

19-inch racks. The maximum number of disks available in 19 inch racks is 960 hot-swap

SCSI disks (288 TB) and 2,220 hot-swap SAS disks (666 TB).

Note: In this publication, the main rack containing the CEC is referred to as the system

. Other IBM documents might use the terms CEC rack or Primary system rack to refer

rack

to this rack.

Table 1-1 on page 3 lists the major attributes of the Power 595 (9119-FHA) server.

2 IBM Power 595 Technical Overview and Introduction

Page 15

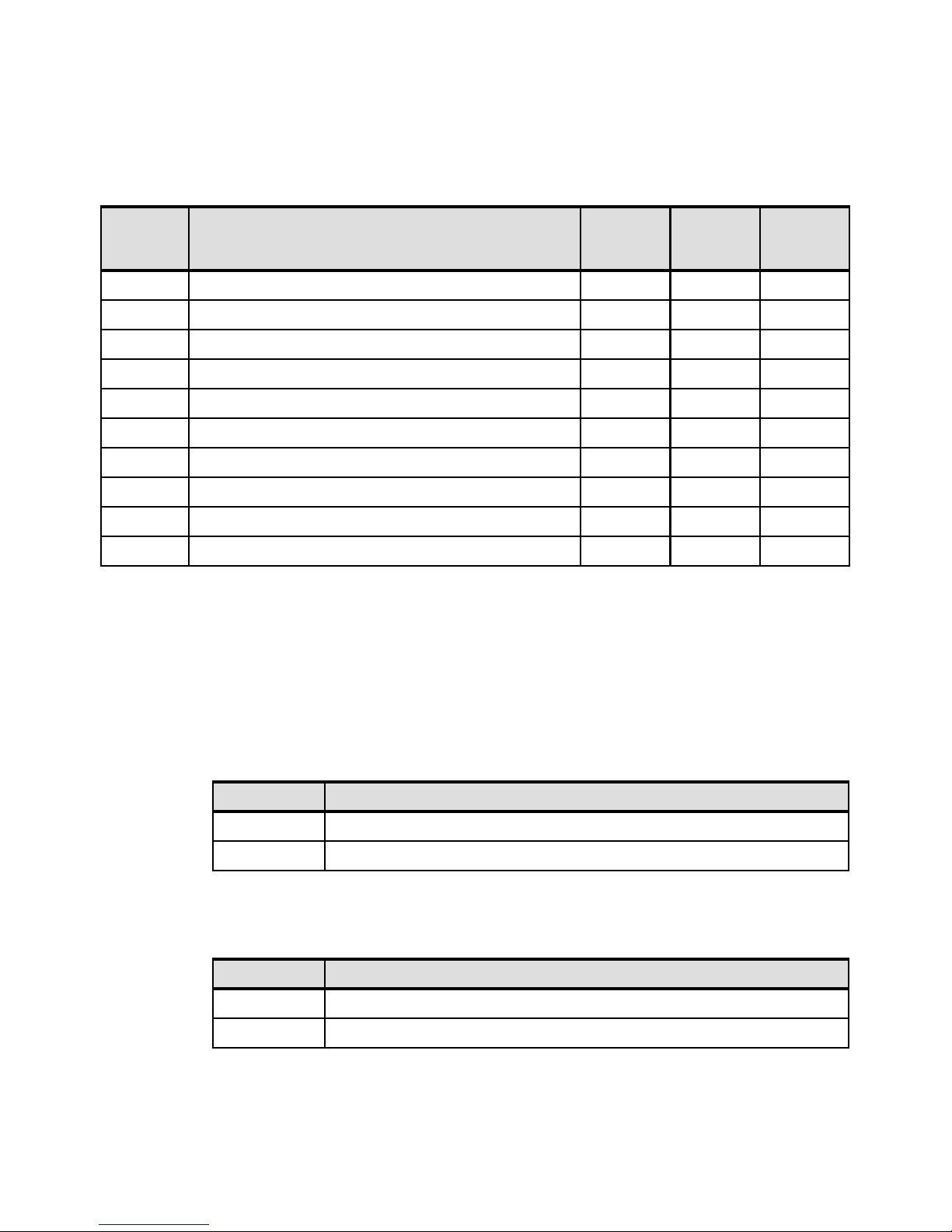

Table 1-1 Attributes of the 9119-FHA

Attribute 9119-FHA

SMP processor configurations 8- to 64 core POWER6 using 8-core processor books

8-core processor books Up to 8

POWER6 processor clock rate 4.2 GHz Standard or 5.0 GHz Turbo

L2 cache 4 MB per core

L3 cache 32 MB per POWER6 processor (shared by two cores)

RAM (memory) 16, 24, or 32 DIMMs configured per processor book

Up to 4 TB of 400 MHz DDR2

Up to 1 TB of 533 MHz DDR2

Up to 512 GB of 667 MHz DDR2

Processor packaging MCM

Maximum memory configuration 4 TB

Rack space 42U 24-inch custom rack

I/O drawers 24": 1 - 30

19" I/O drawers 0 - 96

Internal disk bays 16 maximum per 24" I/O drawer

Internal disk storage Up to 4.8 TB per 24" I/O drawer

64-bit PCI-X Adapter slots #5791 RIO-2 drawer:

20 PCI-X (133 MHz), 240 per system

#5797 or #5798 drawer:

14 PCI-X 2.0 (266 MHz), 6 PCI-X (133 MHz), 600 per system

I/O ports 4 GX+ adapter ports per processor book, 32 per system

POWER™ Hypervisor LPAR, Dynamic LPAR, Virtual LAN

PowerVM Standard Edition

(optional)

Micro-Partitioning™ with up to 10 micro-partitions per

processor (254 maximum); Multiple shared processor pools;

Virtual I/O Server; Shared Dedicated Capacity; PowerVM Lx86

PowerVM Enterprise Edition

PowerVM Standard Edition plus Live Partition Mobility

(optional)

Capacity on Demand configurations 8 to 64 processor cores in increments of one (using one to

eight processor books); 4.2 or 5.0 GHz POWER6 processor

a

cores.

Capacity on Demand (CoD)

features (optional)

Processor CoD (in increments of one processor), Memory

CoD (in increments of 1 GB), On/Off Processor CoD, On/Off

Memory CoD, Trial CoD, Utility CoD

High availability software PowerHA™ family

Chapter 1. General description 3

Page 16

Attribute 9119-FHA

RAS features Processor Instruction Retry

Alternate Processor Recovery

Selective dynamic firmware updates

IBM Chipkill™ ECC, bit-steering memory

ECC L2 cache, L3 cache

Redundant service processors with automatic failover

Redundant system clocks with dynamic failover

Hot-swappable disk bays

Hot-plug/blind-swap PCI-X slots

Hot-add I/O drawers

Hot-plug power supplies and cooling fans

Dynamic Processor Deallocation

Dynamic deallocation of logical partitions and PCI bus slots

Extended error handling on PCI-X slots

Redundant power supplies and cooling fans

Redundant battery backup (optional)

Operating systems AIX V5.3 or later

IBM i V5.4 or later

SUSE® Linux Enterprise Server 10 for POWER SP2 or later

Red Hat Enterprise Linux 4.7 and 5.2 for POWER or later

a. Minimum requirements include a single 8-core book with three cores active, and for every

8-core book, three cores must be active.

1.2 Installation planning

Complete installation instructions are shipped with each server. The Power 595 server must

be installed in a raised floor environment. Comprehensive planning information is available at

this address:

http://publib.boulder.ibm.com/infocenter/eserver/v1r3s/index.jsp

1.2.1 Physical specifications

The key specifications, such as dimensions and weights, are described in this section.

Table 1-2 lists the major Power 595 server dimensions.

Table 1-2 Power 595 server dimensions

Dimension Rack only Rack with

Height 201.4 cm

(79.3 in)

Width 74.9 cm

(29.5 in)

Depth 127.3 cm

(50.1 in)

a. Rack with slim line and side doors, one or two frames

b. Rack with slim line front door and rear door heat exchanger (RDHX), system rack only

side doors

201.4 cm

(79.3 in)

77.5 cm

(30.5 in)

Slim line Acoustic

1 Frame 2 Frames 1 Frame 2 Frames

201.4 cm

(79.3 in)

77.5 cm

(30.5 in)

148.6 cm

(58.5 in)

152.1 cm

(61.3 in)

a

b

201.4 cm

(79.3 in)

156.7 cm

(61.7 in)

201.4 cm

(79.3 in)

77.5 cm

(30.5 in)

180.6 cm

(71.1 in)

201.4 cm

(79.3 in)

156.7 cm

(61.7 in)

180.6 cm

(71.1 in)

4 IBM Power 595 Technical Overview and Introduction

Page 17

Table 1-3 lists the Power 595 server full system weights without the covers.

Table 1-3 Power 595 server full system weights (no covers)

Frame With integrated battery

backup

A Frame (system rack) 1542 kg (3400 lb) 1451 kg (3200 lb)

A Frame (powered expansion rack) 1452 kg (3200 lb) 1361 kg (3000 lb)

Z Frame (bolt-on expansion rack) N/A 1157 kg (2559 lb)

Without integrated battery

backup

Table 1-4 lists the Power 595 cover weights.

Table 1-4 Power 595 cover weights

Covers Weight

Side covers pair 50 kg (110 lb)

Slim Line doors, single 15 kg (33 lb)

Acoustic doors, single (Expansion frame) 25 kg (56 lb)

Acoustic doors, single (System rack) 20 Kg (46 lb)

Table 1-5 lists the Power 595 shipping crate dimensions.

Table 1-5 Power 595 shipping crate dimensions

Dimension Weight

Height 231 cm (91 in)

Width 94 cm (37 in)

Depth 162 cm (63.5 in)

Weight Varies by configuration. Max 1724 kg (3800 lb)

1.2.2 Service clearances

Several possible rack configurations are available for Power 595 systems. Figure 1-1 on

page 6 shows the service clearances for a two-rack configuration with acoustical doors.

Note: The Power 595 server must be installed in a raised floor environment.

Chapter 1. General description 5

Page 18

Figure 1-1 Service clearances for a two-rack system configuration with acoustic doors

Service clearances for other configurations can be found at:

http://publib.boulder.ibm.com/infocenter/eserver/v1r3s/index.jsp?topic=/iphad/serv

iceclearance.htm

Important: If the Power 595 server must pass through a doorway opening less than 2.02

meters (79.5 inches), you should order the compact handling option (#7960) which, ships

the rack in two parts.

1.2.3 Operating environment

Table 1-6 lists the operating environment specifications for the Power 595 server.

Table 1-6 Power 595 server operating environment specifications

Description Range

Recommended operating temperature

(8-core, 16-core, and 32-core configurations)

Recommended operating temperature

(48-core and 64-core configurations)

Relative humidity 20% to 80%

10 degrees to 32 degrees C

(50 degrees to 89.6 degrees F)

10 degrees to 28 degrees C

(50 degrees to 82.4 degrees F)

a

a

6 IBM Power 595 Technical Overview and Introduction

Page 19

Description Range

Maximum wet bulb 23 degrees C (73 degrees F) (operating)

Sound power Declared A-weighted sound power level, per

Sound pressure Declared A-weighted one-meter sound

a. The maximum temperatures of 32°C (90°F) and 28°C (82°F) are linearly derated above 1295

m (4250 ft).

1.2.4 Power requirements

All Power 595 configurations are designed with a fully redundant power system. To take full

advantage of the power subsystem redundancy and reliability features, each of the two power

cords should be connected to different distribution panels.

Table 1-7 lists the electrical and thermal characteristics for the Power 595 server.

Table 1-7 Power 595 electrical and thermal characteristics

Description Range

ISO 9296: 9.2 bels (with slim line doors)

Declared A-weighted sound power level, per

ISO 9296: 8.2 bels (with acoustical doors)

pressure level, per ISO 9296: 79 decibels (with

slim line doors)

Declared A-weighted one-meter sound

pressure level, per ISO 9296: 69 decibels (with

acoustical doors)

Operating voltages 3-phase V ac at 50/60 Hz): 200 to 240 V;

380 to 415 V; 480 V

Rated current (A per phase): 48 A or 63

A or 80 A; 34 A or 43 A; 24 A or 34 A

Power consumption: 27,500 watts

(maximum for full CEC, three I/O

drawers)

Power source loading: 27.7 kVA

Thermal output: 27,500 joules/sec

(93,840 Btu/hr) maximum

Inrush current 134

Power Factor 0.99

Operating frequency 50/60 plus or minus 0.5 Hz

Maximum Power (Fully configured 4.2 GHz system) 23.3 KW

Maximum Power (Fully configured 5.0 GHz system) 28.3 KW

Maximum thermal output (4.2 GHz processor) 74.4 KBTU/hr

Maximum thermal output (5.0 GHz processor) 83.6 KBTU/hr

Table 1-8 on page 8 lists the electrical characteristics for 4.2 GHz and 5.0 GHz Power 595

servers, and the Powered Expansion Rack (U.S., Canada, and Japan).

Chapter 1. General description 7

Page 20

Table 1-8 Electrical characteristics (U.S., Canada, and Japan)

Description US, Canada, Japan US high voltage

Voltage and

Frequency

4.2 GHz Server

System Rating 48 A 63 A 24 A 24 A

Plug rating 60 A 100 A 30 A 30 A

Recommended

circuit breaker

rating

Cord size 6 AWG 6 AWG 8 AWG 8 AWG

Recommended

receptacle

5.0 GHz Server

System Rating 48 A 63 A 24 A 34 A

Plug rating 60 A 100 A 30 A 60 A

Recommend

circuit breaker

rating

Cord size 6 AWG 4 AWG 8 AWG 6 AWG

200-240 V at 50-60 Hz 480 V at 50-60 Hz

60 A80 A30 A30 A

IEC60309, 60 A,

type 460R9W

60 A 100 A 30 A 60 A

IEC60309, 100 A,

type 4100R9W

IEC60309, 30 A,

type 430R7W

IEC60309, 30 A,

type 430R7W

Recommended

receptacle

Powered Expansion Rack

System rating 48 A 63 A 24 A 24 A

Plug rating 60 A 100 A 30 A 30 A

Recommend

circuit breaker

rating

Cord size 6 AWG 6 AWG 8 AWG 8 AWG

Recommended

receptacle

IEC60309, 60 A,

type 460R9W

60 A80 A30 A30 A

IEC60309, 60 A,

type 460R9W

IEC60309, 100 A,

type 4100R9W

IEC60309, 100 A,

type 4100R9W

IEC60309, 30 A,

type 430R7W

IEC60309, 30 A,

type 430R7W

IEC60309, 30 A,

type 430R7W

IEC60309, 30 A,

type 430R7W

Table 1-9 lists the electrical characteristics for 4.2 GHz and 5.0 GHz Power 595 servers, and

the Powered Expansion Rack (World Trade).

Table 1-9 Electrical characteristics (World Trade)

Description Worl d Tra d e

Voltage and

frequency

4.2 GHz server

200-240 V at 50-60 Hz 380/415 V at 50-60 Hz

System rating 48 A 63 A 34 A 34 A

Plug rating no plug no plug no plug no plug

8 IBM Power 595 Technical Overview and Introduction

Page 21

Description Worl d Tra d e

Recommend

circuit breaker

rating

Cord size 6 AWG 6 AWG 8 AWG 8 AWG

Recommended

receptacle

5.0 GHz server

System rating 48 A 80 A 34 A 43 A

Plug rating no plug no plug no plug no plug

Recommend

circuit breaker

rating

Cord size 6 AWG 4 AWG 8 AWG 6 AWG

Recommended

receptacle

Powered Expansion Rack

System rating

Powered I/O

Rack

60 A80 A40 A40 A

Not specified

Electrician

installed

60 A 100 A 40 A 63 A

Not specified

Electrician

installed

48 A63 A34 A34 A

Not specified

Electrician

installed

Not specified

Electrician

installed

Not specified

Electrician

installed

Not specified

Electrician

installed

Not specified

Electrician

installed

Not specified

Electrician

installed

Plug rating no plug no plug no plug no plug

Recommend

circuit breaker

rating

Cord size 6 AWG 6 AWG 8 AWG 8 AWG

Recommended

receptacle

60 A80 A40 A40 A

Not specified

Electrician

installed

Not specified

Electrician

installed

1.3 Minimum configuration requirements

This section discusses the minimum configuration requirements for the Power 595. Also

provided are the appropriate feature codes for each system component. The IBM

configuration tool also identifies the feature code for each component in your system

configuration. Table 1-10 on page 10 identifies the required components for a minimum

9119-FHA configuration.

Note: Throughout this chapter, all feature codes are referenced as #xxxx, where xxxx is

the appropriate feature code number of the particular item.

Not specified

Electrician

installed

Not specified

Electrician

installed

Chapter 1. General description 9

Page 22

Table 1-10 Power 595 minimum system configuration

Quantity Component description Feature code

1 Power 595 9119-FHA

1 8-core, POWER6 processor book 0-core active #4694

3 1-core, processor activations 3 x #4754

4 Four identical memory features (0/4 GB or larger) —

16 1 GB memory activations (16x #5680) #5680

1 Power Cable Group, first processor book #6961

4 Bulk power regulators #6333

2 Power distribution assemblies #6334

2 Line cords, selected depending on country and

voltage

1 Pair of doors (front/back), either slim line or acoustic —

1 Universal lift tool/shelf/stool and adapter #3759 and #3761

1 Language - specify one #93xx (country dependent)

1 HMC (7042-COx/CRx) attached with Ethernet cables —

1 RIO I/O Loop Adapter #1814

or 1 12X I/O Loop Adapter #1816

1 One I/O drawer providing PCI slots attached to the

I/O loop

or 1 As an alternative when the 12X I/O Drawer (#5798)

becomes available, located at A05 in the system rack

2 Enhanced 12X I/O Cable 2.5 M #1831

1 Enhanced 12X I/O Cable, 0.6 m (#1829) #1829

—

#5791 (AIX, Linux)

#5790 (IBM i)

#5798

Prior to the availability of 12X Expansion Drawers (#5797 or #5798), new server shipments

will use an RIO I/O Expansion Drawer model dependent on the primary operating system

selected. When 12x Expansion Drawers become available, they become the default, base I/O

Expansion Drawer for all operating systems.

If AIX or Linux for Power operating system is specified as the primary operating system, see

Table 1-11 for a list of the minimum, required features:

Table 1-11 Minimum required features when AIX or Linux for Power is the primary operating system

Quantity Component description Feature code

1 Primary Operating System Indicator for AIX or Linux

for Power

1 PCI-X 2.0 SAS Adapter (#5912 or #5900) or PCI LAN

Adapter for attachment of a device to read CD media

or attachment to a NIM server

2 15,000 RPM, 146.8 GB, SCSI Disk Drives #3279

10 IBM Power 595 Technical Overview and Introduction

#2146

#2147

#5912 (#5900 is supported)

Page 23

Quantity Component description Feature code

1 RIO-2 I/O drawer located at location U5 in the system

rack prior to the availability of #5798

2 RIO-2 I/O bus cables, 2.5 m #3168

1 Remote I/O Cable, 0.6 m #7924

1 UPIC Cable Group, BPD1 to I/O Drawer at position

U5 in the system rack

#5791

#6942

If IBM i is specified as the primary operating system, refer to Table 1-12, which lists the

minimum required features.

Table 1-12 Minimum required features when IBM i is the primary operating system

Quantity Component description Feature code

1 Primary operating system indicator for IBM i #2145

1 System console specify —

1 SAN Load Source Specify: Requires Fibre Channel

Adapter

or 1 Internal Load Source Specify: Requires disk

controller and minimum of two disk drives

1 PCI-X 2.0 SAS Adapter for attachment of a DVD drive #5912

1 PCI 2-Line WAN Adapter with Modem #6833

For example, #5749

For example, #5782, two #4327

1 RIO-attached PCI Expansion Drawer (prior to feature

5798 availability)

— Rack space in a Dual I/O Unit Enclosure #7307, #7311

1 RIO-2 Bus Adapter #6438

2 RIO-2 I/O Bus Cables, 8 m #3170

2 Power cords #6459

2 Power Control Cable, 6 m SPCN #6008

1 Media Drawer, 19-inch (prior to feature 5798/5720

availability).

One DVD drive

Power cords

SAS cable for attachment to #5912 SAS adapter

or 1 595 Media Drawer, 24-inch with #5798 availability #5720

1 19-inch rack to hold the #5790 and 7214-1U2 —

1 PDU for power in 19-inch rack For example, #7188

1.3.1 Minimum required processor card features

The minimum configuration requirement for the Power 595 server is one 4.2 GHz 8-core

processor book and three processor core activations, or two 5.0 GHz 8-core processor books

and six processor core activations. For a description of available processor features and their

associated feature codes, refer to 2.6, “Processor books” on page 70.

#5790

#7214-1U2

#5756

For example, #6671

For example, #3684

Chapter 1. General description 11

Page 24

1.3.2 Memory features

The Power 595 utilizes DDR2 DRAM memory cards. Each processor book provides 32

memory card slots for a maximum of 256 memory cards per server. The minimum system

memory is 16 GB of active memory per processor book.

The Power 595 has the following minimum and maximum configurable memory resource

allocation requirements:

Utilizes DDR2 DRAM memory cards.

Requires a minimum of 16 GB of configurable system memory.

Each processor book provides 32 memory card slots for a maximum of 256 memory cards

per server. The minimum system memory is 16 GB of active memory per processor book.

Supports a maximum of 4 TB DDR2 memory.

Memory must be configured with a minimum of four identical memory features per

processor book, excluding feature #5697 (4 DDR2 DIMMs per feature). Feature #5697,

0/64 GB memory must be installed with 8 identical features.

Different memory features cannot be mixed within a processor book. For example, in a

4.2 GHz processor book (#4694), four 0/4 GB (#5693) features, 100% activated DIMMs

are required to satisfy the minimum active system memory of 16 GBs. For two 4.2 GHz or

5.0 GHz processor books (#4694 or #4695), four 0/4 GB (#5693) features, 100% activated

in each processor book is required to satisfy the minimum active system memory of

32 GBs. If 0/8 GB (#5694) features are used, then the same minimum system memory

requirements can be satisfied with 50% of the DIMMs activated.

Each processor book has four dual-core MCMs, each of which are serviced by one or two

memory features (4 DIMMs per feature). DDR2 memory features must be installed in

increments of one per MCM (4 DIMM cards per memory feature), evenly distributing

memory throughout the processor books installed. Incremental memory for each

processor book must be added in identical feature pairs (8 DIMMs). As a result, each

processor book will contain either four, six, or eight identical memory features (two per

MCM), which equals a maximum of 32 DDR2 memory DIMM cards.

Memory features #5694, #5695, and #5696 must be 50% activated as a minimum at the

time of order with either feature #5680 or #5681.

Features #5693 (0/4 GB) and #5697 (0/64 GB) must be 100% activated with either feature

#5680 or #5681 at the time of purchase.

Memory can be activated in increments of 1 GB.

All bulk order memory features #8201, #8202, #8203, #8204, and #8205 must be

activated 100% at the time of order with feature #5681.

Maximum system memory is 4096 GB and 64 memory features (eight features per

processor book or 256 DDR2 DIMMs per system). DDR1 memory is not supported.

For a list of available memory features refer to Table 2-15 on page 80.

1.3.3 System disks and media features

This topic focuses on the I/O device support within the system unit. The Power 595 servers

have internal hot-swappable drives supported in I/O drawers. I/O drawers can be allocated in

24-inch or 19-inch rack (IBM i application only). Specific client requirements can be satisfied

with several external disk options supported by the Power 595 server.

12 IBM Power 595 Technical Overview and Introduction

Page 25

For further information about IBM disk storage systems, including withdrawn products, visit:

http://www.ibm.com/servers/storage/disk/

Note: External I/O drawers 7311-D11, 7311-D20, and 7314-G30 are not supported on the

Power 595 servers.

The Power 595 has the following minimum and maximum configurable I/O device allocation

requirements:

The 595 utilizes 4U-tall remote I/O drawers for directly attached PCI or PCI-X adapters

and SCSI disk capabilities. Each I/O drawer is divided into two separate halves. Each half

contains 10 blind-swap PCI-X slots for a total of 20 PCI slots and up to 16 hot-swap disk

bays per drawer.

When an AIX operating system is specified as the primary operating system, a minimum

of one I/O drawer (#5791) per system is required in the 5U location within the system rack.

When an IBM i operating system is specified as the primary operating system, a minimum

of one PCI-X Expansion Drawer (#5790) per system is required in a 19-inch expansion

rack. A RIO-2 Remote I/O Loop Adapter (#6438) is required to communicate with the 595

CEC RIO-G Adapter (#1814).

When the 12X I/O drawers (#5797. #5798) is available, the above minimum requirement

will be replaced by one feature #5797 or #5798 per system in the 5U location within the

system rack. All I/O drawer feature #5791, #5797, or #5798 contain 20 PCI-X slots and 16

disk bays.

Note: The 12X I/O drawer (#5798) attaches only to the central electronics complex

using 12X cables. The 12X I/O drawer (#5797) comes with a repeater card installed.

The repeater card is designed to strengthen signal strength over the longer cables used

with the Power Expansion Rack (#6954 or #5792) and nonpowered, bolt-on Expansion

Rack (#6983 or #8691). Features #5797 and #5798 will not be supported in p5-595

migrated Expansion Rack.

7040-61D I/O drawers are supported with the 9119-FHA.

A maximum of 12-feature #5791 (or #5807), 5794 (specified as #5808), or 30-feature

#5797 I/O drawers can be connected to a 595 server. The total quantity of features

(#5791+#5797+#5798+#5807+#5808) must be less than or equal to 30.

One single-wide, blind-swap cassette (equivalent to those in #4599) is provided in each

PCI or PCI-X slot of the I/O drawer. Cassettes not containing an adapter will be shipped

with a

dummy card installed to help ensure proper environmental characteristics for the

drawer. If additional single-wide, blind-swap cassettes are needed, feature #4599 should

be ordered.

All 10 PCI-X slots on each I/O drawer planar are capable of supporting either 64-bit or

32-bit PCI or PCI-X adapters. Each I/O drawer planar provides 10 PCI-X slots capable of

supporting 3.3-V signaling PCI or PCI-X adapters operating at speeds up to 133 MHz.

Each I/O drawer planar incorporates two integrated Ultra3 SCSI adapters for direct

attachment of the two 4-pack hot-swap backplanes in that half of the drawer. These

adapters do not support external SCSI device attachments. Each half of the I/O drawer is

powered separately.

For IBM i applications, if additional external communication and storage devices are

required, a 19-inch, 42U high non-powered Expansion Rack can be ordered as feature

#0553. Feature #0553 (IBM i) is equivalent to the 7014-T42 rack, which is supported for

use with a 9119-FHA server.

Chapter 1. General description 13

Page 26

For IBM i applications, a maximum of 96 RIO-2 drawers or 30 12X I/O drawers can be

attached to the 595, depending on the server and attachment configuration.The IBM i

supported #0595, #0588, #5094/#5294, #5096/#5296 and #5790 all provide PCI slots and

are supported when migrated to the Power 595. Up to six I/O drawers/towers per RIO loop

are supported. Prior to the 24" 12X drawer's availability, the feature #5790 is also

supported for new orders.

The #5786 EXP24 SCSI Disk Drawer and the #5886 EXP 12S SAS Disk Drawer are 19"

drawers which are supported on the Power 595.

For a list of the available Power 595 Expansion Drawers, refer to 2.8.2, “Internal I/O drawers”

on page 84.

Note: Also supported for use with the 9119-FHA are items available from a model

conversion (all IBM i supported, and AIX and Linux are not supported):

7014-T00 and feature 0551 (36U, 1.8 meters)

7014-S11 and feature 0551 (11U high)

7014-S25 and feature 0551 (25U high)

In addition to the above supported racks, the following expansion drawers and towers

are also supported:

– PCI-X Expansion Tower/Unit (#5094) (IBM i)

– PCI-X Expansion Tower (no disk) (#5096, #5088 - no longer available (IBM i)

– 1.8 m I/O Tower (#5294)

– 1.8 m I/O Tower (no disk) (#5296)

– PCI-X Tower Unit in Rack (#0595)

– PCI Expansion Drawer (#5790)

There is no limit on the number of 7014 racks allowed.

Table 1-13 lists the Power 595 hard disk drive features available for I/O drawers.

Table 1-13 IBM Power 595 hard disk drive feature codes and descriptions

Feature code Description Support

AIX

#3646 73 GB 15K RPM SAS Disk Drive 9 — 9

#3647 146 GB 15K RPM SAS Disk Drive 9 — 9

#3648 300 GB 15K RPM SAS Disk Drive 9 — 9

#3676 69.7 GB 15K RPM SAS Disk Drive — 9 —

#3677 139.5 GB 15K RPM SAS Disk Drive — 9 —

#3678 283.7 GB 15K RPM SAS Disk Drive — 9 —

IBM i

Linux

#3279 146.8 GB 15K RPM Ultra320 SCSI Disk Drive Assembly 9 — 9

#4328 141.12 GB 15K RPM Disk Unit — 9 —

14 IBM Power 595 Technical Overview and Introduction

Page 27

The Power 595 server must have access to a device capable of reading CD/DVD media or to

a NIM server. The recommended devices for reading CD/DVD media is the Power 595 media

drawer (#5720), or and external DVD device (7214-1U2, or 7212-103). Ensure there is a SAS

adapter available for the connection.

If an AIX or Linux for Power operating system is specified as the primary operating system, a

NIM server can be used. The recommended NIM server connection is a PCI based Ethernet

LAN adapter plugged in one of the system I/O drawers.

If an AIX or Linux for Power operating system is specified as the primary operating system, a

minimum of two internal SCSI hard disks is required per 595 server. It is recommended that

these disks be used as mirrored boot devices. These disks should be mounted in the first I/O

drawer whenever possible. This configuration provides service personnel the maximum

amount of diagnostic information if the system encounters any errors during in the boot

sequence. Boot support is also available from local SCSI and Fibre Channel adapters, or

from networks via Ethernet or token-ring adapters.

Placement of the operating systems disks in the first I/O drawer allows the operating system

to boot even if other I/O drawers are found offline during boot. If the boot source other than

internal disk is configured, the supporting adapter should also be in the first I/O drawer.

Table 1-14 lists the available Power 595 media drawer features.

Table 1-14 IBM Power 595 media drawer features

Feature code Description Support

AIX

IBM i

Linux

#0274 Media Drawer, 19-inch 99—

#4633 DVD RAM — 9 —

#5619 80/160 GB DAT160 SAS Tape Drive 9 — 9

#5689 DAT160 Data Cartridge 9 — 9

#5746 Half High 800 GB/1.6 TB LTO4 SAS Tape Drive 9 — 9

#5747 IBM LTO Ultrium 4 800 GB Data Cartridge 9 — 9

#5756 IDE Slimline DVD ROM Drive 999

#5757 IBM 4.7 GB IDE Slimline DVD RAM Drive 999

1.3.4 I/O Drawers attachment (attaching using RIO-2 or 12x I/O loop adapters)

Existing System i and System p model configurations have a set of I/O enclosures that have

been supported on RIO-2 (HSL-2) loops for a number of years.

Most continue to be supported on POWER6 models. This section highlights the newer I/O

enclosures that are supported by the POWER6 models that are actively marketed on new

orders. See 2.8, “Internal I/O subsystem” on page 82 for additional information about

supported I/O hardware.

System I/O drawers are always connected using RIO-2 loops or 12X HCA loops to the GX

I/O hub adapters located on the front of the processor books. Drawer connections are

always made in loops to help protect against a single point-of-failure resulting from an

open, missing, or disconnected cable.

Chapter 1. General description 15

Page 28

Systems with non-looped configurations could experience degraded performance and

serviceability.

RIO-2 loop connections operate bidirectional at 1 GBps (2 GBps aggregate). RIO-2 loops

connect to the system CEC using RIO-2 loop attachment adapters (#1814). Each adapter

has two ports and can support one RIO-2 loop. Up to four of the adapters can be installed

in each 8-core processor book.

12X HCA loop connections operate bidirectional at 3 GBps (6 GBps aggregate). 12X

loops connect to the system CEC using 12X HCA loop attachment adapters (#1816). For

AIX applications up to 12 RIO-2 drawers or 30 12X I/O drawers can be attached to the

595, depending on the server and attachment configuration.

The total quantity of features #5791+#5797+#5798+#5807+#5808 must be less than or

equal to 30.

Slot plugging rules are complex, and depend on the number of processor books present.

Generally, the guidelines are:

Slots are populated from the top down.

#1816 adapters are placed first and #1814 are placed second.

A maximum of 32 GX adapters per server are allowed.

Refer to 2.8.1, “Connection technology” on page 83 for a list of available GX adapter types

and their feature numbers.

I/O drawers can be connected to the CEC in either single-loop or dual-loop mode. In some

situations, dual-loop mode might be recommended because it provides the maximum

bandwidth between the I/O drawer and the CEC. Single-loop mode connects an entire I/O

drawer to the CEC through one loop (two ports). The two I/O planars in the I/O drawer are

connected with a short jumper cable. Single-loop connection requires one loop (two ports)

per I/O drawer.

Dual-loop mode connects each I/O planar in the drawer to the CEC separately. Each I/O

planar is connected to the CEC through a separate loop. Dual-loop connection requires two

loops (four ports) per I/O drawer.

Refer to Table 2-22 on page 89 for information about the number of single-looped and doublelooped I/O drawers that can be connected to a 595 server based on the number of processor

books installed.

Note: On initial Power 595 server orders, IBM manufacturing places dual-loop connected

I/O drawers as the lowest numerically designated drawers followed by any single-looped

I/O drawers.

1.3.5 IBM i, AIX, Linux for Power I/O considerations

As we indicated previously, some operating system-specific requirements, and current

System i and System p client environments dictate differences, which are documented where

appropriate in this publication.

Examples of unique AIX I/O features include graphic adapters, specific WAN/LAN adapters,

SAS disk/tape controllers, iSCSI adapters, and specific Fibre Channel adapters.

Examples of unique IBM i I/O features include the #5094/#5294/#5088/#0588/#0595 I/O

drawers/towers (I/O enclosures), I/O Processors (IOPs), IOP-based PCI adapter cards, very

16 IBM Power 595 Technical Overview and Introduction

Page 29

large write cache disk controllers, specific Fibre Channel adapters, iSCSI adapters, and

specific WAN/LAN adapters.

System i hardware technologies and the IBM i operating system (OS/400®, i5/OS, and so

forth) have a long history of supporting I/O adapters (IOAs, also commonly referred to as

controllers) that also required a controlling I/O Processor (IOP) card. A single IOP might

support multiple IOAs. The IOP card originally had a faster processor technology than its

attached IOAs. Thus, microcode was placed in the IOP to deliver the fastest possible

performance expected by clients.

IOAs introduced over the last two to three years (since the time of writing), have very fast

processors and do not require a supporting IOP. Among the System i community, these

adapters are sometimes referred to as

Sometimes, these IOAs are also referred to as a

not run with an IOP. These are sometimes referred to as an

not run with an IOP).

AIX or Linux client partitions hosted by an IBM i partition are independent of any unique IBM i

I/O hardware requirements.

For new system orders, IOP-less IOAs are what AIX or Linux users consider as the normal

I/O environment. New orders for IBM i, AIX, and Linux operating systems should specify the

smart or IOP-less IOAs.

However, many System i technology clients who are considering moving to the POWER6

models should determine how to handle any existing IOP-IOA configurations they might have.

Older technology IOAs and IOPs should be replaced or I/O enclosures supporting IOPs

should be used.

smart IOAs that can operate with or without an IOP.

dual mode IOA. There are also IOAs that do

IOP-less IOA (or one that does

The POWER6 system unit does not support IOPs and thus IOAs that require an IOP are not

supported. IOPs can be used in supported I/O enclosures attached to the system by using a

RIO-2 loop connection. RIO-2 is the System p technology term used in this publication to also

represent the I/O loop technology typically referred to as HSL-2 by System i clients.

Later in this publication, we discuss the PCI technologies that can be placed within the

processor enclosure. For complete PCI card placement guidance in a POWER6

configuration, including the system unit and I/O enclosures attached to loops, refer to the

documents available at the IBM Systems Hardware Information Center at the following

location (the documents are in the Power Systems information category):

http://publib.boulder.ibm.com/infocenter/systems/scope/hw/index.jsp

PCI placement information for the Power 595 server can be found in the Power Systems PCI

Adapter Placement Guide for Machine Type 820x and 91xx, SA76-0090.

1.3.6 Hardware Management Console models

Each Power 595 server must be connected to an Hardware Management Console (HMC) for

system control, LPAR, Capacity on Demand, and service functions. It is highly recommended

that each 595 server is connected to two HMCs for redundancy. The Power 595 is connected

to the HMC through Ethernet connections to the front and rear Bulk Power Hub (BPH) in the

CEC Bulk Power Assembly.

Several HMC models are available for POWER6-based systems at the time of writing. See

2.13, “Hardware Management Console (HMC)” on page 101 for details about specific HMC

models. HMCs are preloaded with the required Licensed Machine Code Version 7 (#0962) to

support POWER6 systems, in addition to POWER5™ and POWER5+™ systems.

Chapter 1. General description 17

Page 30

Existing HMC models 7310 can be upgraded to Licensed Machine Code Version 7 to support

environments that can include POWER5, POWER5+, and POWER6 processor-based

servers. Version 7 is not available for the 7315 HMCs. Licensed Machine Code Version 6

(#0961) is not available for 7042 HMCs, and Licensed Machine Code Version 7 (#0962) is not

available on new 7310 HMC orders.

1.3.7 Model conversion

Clients with installed p5-590, p5-595, i5-595, and i5-570 servers can increase their computing

power by ordering a model conversion to the 595 server. Table 1-15 lists the available model

conversions.

Table 1-15 Available model conversions

From type-model To type-model

9119 590 9119 FHA

9119 595 9119 FHA

9406 570 9119 FHA

9406 595 9119 FHA

Due to the size and complex nature of the miscellaneous equipment specification (MES)

model upgrades into the Power 595 server, a two-step MES process is required. The two

MESs are configured in a single eConfig session (the ordering tool used by sales and

technical professionals) and contained within the same eConfig Proposed Report. These

MESs are processed in sequence.

The initial MES is a Record Purpose Only (RPO) activity that positions the inventory record

and conceptually redefines the installed product with Power Systems feature nomenclature.

This MES contains a series of RPO feature additions and removals within the installed

machine type and model, and adds specify code #0396. This RPO MES serves several

purposes. It keeps your maintenance billing whole throughout the upgrade process, reduces

the number of feature conversions on the normal MES, and reduces the overall size of the

normal MES. This RPO MES should be stored in a separate eConfig file for reference prior to

order forward.

The second MES is a normal machine/model upgrade MES from 9406/9119 to 9119-FHA

with all the appropriate model/feature conversions and subject to the usual scheduling,

manufacturing, and installation rules and processes. Care must be taken that both MESs are

processed completely through installation prior to configuration/placement of any subsequent

MES orders.

Note: In the event that the RPO MES is reported as installed and the normal MES is

cancelled, a sales representative must submit an additional RPO MES reversing the

transactions of the initial RPO MES to return your inventory record to its original state.

Failure to do so prevents future MES activity for your machine and could corrupt your

maintenance billing. The saved eConfig Proposed Report can be used as the basis for

configuring this reversal RPO MES.

18 IBM Power 595 Technical Overview and Introduction

Page 31

Ordering a model conversion provides:

Change in model designation from p5-590, p5-595, i5-595, and i5-570 to 595 (9119-FHA)

Power 595 labels with the same serial number as the existing server

Any model-specific system documentation that ships with a new 595 server

Each model conversion order also requires feature conversions to:

Update machine configuration records.

Ship system components as necessary.

The model conversion requires an order of a set of feature conversions.

The existing components, which are replaced during a model or feature conversion,

become the property of IBM and must be returned.

In general, feature conversions are always implemented on a quantity-of-one for

quantity-of-one basis. However, this is not true for 16-core processor books.

Each p590, p595, or i595, 16-core processor book conversion to the Power 595 server

actually results in two, 8-core 595 processor books. The duplicate 8-core book is

implemented by using eConfig in a unique two-step, MES order process as part of a

model conversion described in section1.3.7, “Model conversion” on page 18.

Excluding p590, p595, and i595 processor books, single existing features might not be

converted to multiple new features. Also, multiple existing features might not be converted

to a single new feature.

DDR1 memory is not supported.

DDR2 memory card (#7814) 9119-590, 9119-595, 4 GB, 533 MHz is not supported.