Page 1

Service Manual

Preface

This manual describes information related with product repair. To repair the product properly, please

read this manual carefully.

This manual is applicable to the following model:

RD98X (X may indicate 2, 5, 6 or 8.)

Page 2

Service Manual

Contents

1. Revision History ...................................................................................................................................1

2. Copyright Information...........................................................................................................................2

3. Disclaimer.............................................................................................................................................

4. Introduction...........................................................................................................................................4

5. Product Controls...................................................................................................................................5

Front Panel........................................................................................................................................5

Rear Pan

6. Baseband Section................................................................................................................................6

6.1 Front Panel..................................................................................................................................6

6.2 Main Board................................................................................................................................10

6.3 PCB Vi

6.4 Block Diagram...........................................................................................................................27

6.5 Schematic Diagram...................................................................................................................

6.6 Parts List...................................................................................................................................

6.7 T

e

l........................................................................................................................................5

ew..................................................................................................................................23

roubleshooting Flow Chart ......................................................................................................77

3

29

43

7. Tuning Description..............................................................................................................................78

8. Interface Definition .............................................................................................................................79

9.UHF1 (400-470MHz) Information ........................................................................................................84

9.1 TX Circuit...................................................................................................................................84

9.2 RX Circuit..................................................................................................................................86

9.3 Frequency Generation Unit (FGU) ............................................................................................88

9.4 PCB View..................................................................................................................................

9.5 Block Diagram...........................................................................................................................96

9.6 Schematic Diagram...................................................................................................................

9.7 Parts List.................................................................................................................................

roubleshooting Flow Chart ....................................................................................................13

9.8 T

10. UHF2 (450-520MHz) Information ...................................................................................................144

10.1 TX Circuit...............................................................................................................................144

90

99

108

9

Page 3

Service Manual

10.2 RX Circuit..............................................................................................................................146

10.3 Frequency Generation Unit (FGU) ........................................................................................147

10.4 PCB View..............................................................................................................................150

10.5 Block Diagram.......................................................................................................................156

10.6 Schematic Diagram...............................................................................................................159

10.7 Parts List...............................................................................................................................168

10.8 Troubleshooting Flow Chart ..................................................................................................198

11.UHF3 (350-400MHz) Information.....................................................................................................203

1 1 .1 TX Circuit...............................................................................................................................203

11.2 RX Circuit ..............................................................................................................................205

11.3 Frequency Generation Unit (FGU).........................................................................................206

11.4 PCB View ..............................................................................................................................209

11.5 Block Diagram.......................................................................................................................215

11.6 Schematic Diagram...............................................................................................................218

11.7 Parts List................................................................................................................................

.8 Troubleshooting Flow Chart...................................................................................................258

11

12.VHF (136-174MHz) Information ......................................................................................................263

12.1 TX Circuit...............................................................................................................................263

12.2 RX Circuit..............................................................................................................................265

12.3 Frequency Generation Unit (FGU) ........................................................................................266

12.4 PCB View..............................................................................................................................269

12.5 Block Diagram.......................................................................................................................275

12.6 Schematic Diagram...............................................................................................................278

12.7 Parts List...............................................................................................................................287

12.8 Troubleshooting Flow Chart ..................................................................................................317

227

13. Disassembly and Assembly............................................................................................................322

14. Exploded View................................................................................................................................

15. Packing Guide..............................................................................................................

16. Specifications.................................................................................................................................328

17. T

able of Blind Spots........................................................................................................................330

..................327

324

Page 4

Service Manual

1. Revision History

Version Date Description

R2.0 09-2010 Initial Release

R3.5 06-2011 VHF, UHF2 and UHF3 service information is included.

1

Page 5

Service Manual

2. Copyright Information

Hytera is the trademark or registered trademark of Hytera Communications Co., Ltd. (the Company) in

PRC and/or other countries or areas. The Company retains the ownership of its trademarks and product

names. All other trademarks and/or product names that may be used in this manual are properties of

their respective owners.

The product described in this manual may include the Company’s computer programs stored in memory

or other media. Laws in PRC and/or other countries or areas protect the exclusive rights of the Company

with respect to its computer programs. The purchase of this product shall not be deemed to grant, either

directly or by implication, any rights to the purchaser regarding the Company’s computer programs. Any

of the Company’s computer programs may not be copied, modified, distributed, decompiled, or

reverse-engineered in any manner without the prior written consent of the Company.

TM

The AMBE+2

rights including patent rights, copyrights and trade secrets of Digital Voice Systems, Inc. This voice

coding technology is licensed solely for use within this product. The user of this technology is explicitly

prohibited from attempting to decompile, reverse engineer, or disassemble the Object Code or in any

other way convert the Object Code into a human readable form.

U.S. Patent Nos. #6,912,495 B2, #6,199,037 B1, #5,870,405, #5,826,222, #5,754,974, #5,701,390,

#5,715,365, #5,649,050, #5,630,011, #5,581,656, #5,517,511, #5,491,772, #5,247,579, #5,226,084 and

#5,195,166.

voice coding technology embodied in this product is protected by intellectual property

2

Page 6

Service Manual

3. Disclaimer

The Company endeavors to achieve the accuracy and completeness of this manual, but no warranty of

accuracy or reliability is given. All the specifications and designs are subject to change without notice

due to continuous technology development. No part of this manual may be copied, modified, translated,

or distributed in any manner without the express written permission of us.

If you have any suggestions or would like to learn more details, please visit our website at:

http://www.hytera.com

.

3

Page 7

4. Introduction

Intended User

This manual is intended for use by qualified technicians only.

Service Manual

4

Page 8

5. Product Controls

Front Panel

No. Part Name No. Part Name

1 Accessory Jack 9 Slot 1 RX Indicator

2 Volume Control Knob / Power Indicator 10 Alarm Indicator

Service Manual

3 Repeater Mode Indicator 11 Programmable Key

4 Analog Mode Indicator 12 LCD Display

5 Slot 2 RX Indicator 13 Channel Up (CH+)

6 Slot 2 TX Indicator 14 Navigation Knob

7 Digital Mode Indicator

8 Slot 1 TX Indicator 16 Speaker

Rear Panel

No. Part Name No. Part Name

15

Channel Down (CH-)

1 TX Antenna Interface 6 Accessory Jack

2 Optional Interface 1 7 DC Power Interface

3 RX/Duplex Antenna Interface 8 Ethernet Port

4 Optional Interface 2 9 Ground Screw

5 Monitor/Tuning Interface

5

Page 9

Service Manual

6. Baseband Section

6.1 Front Panel

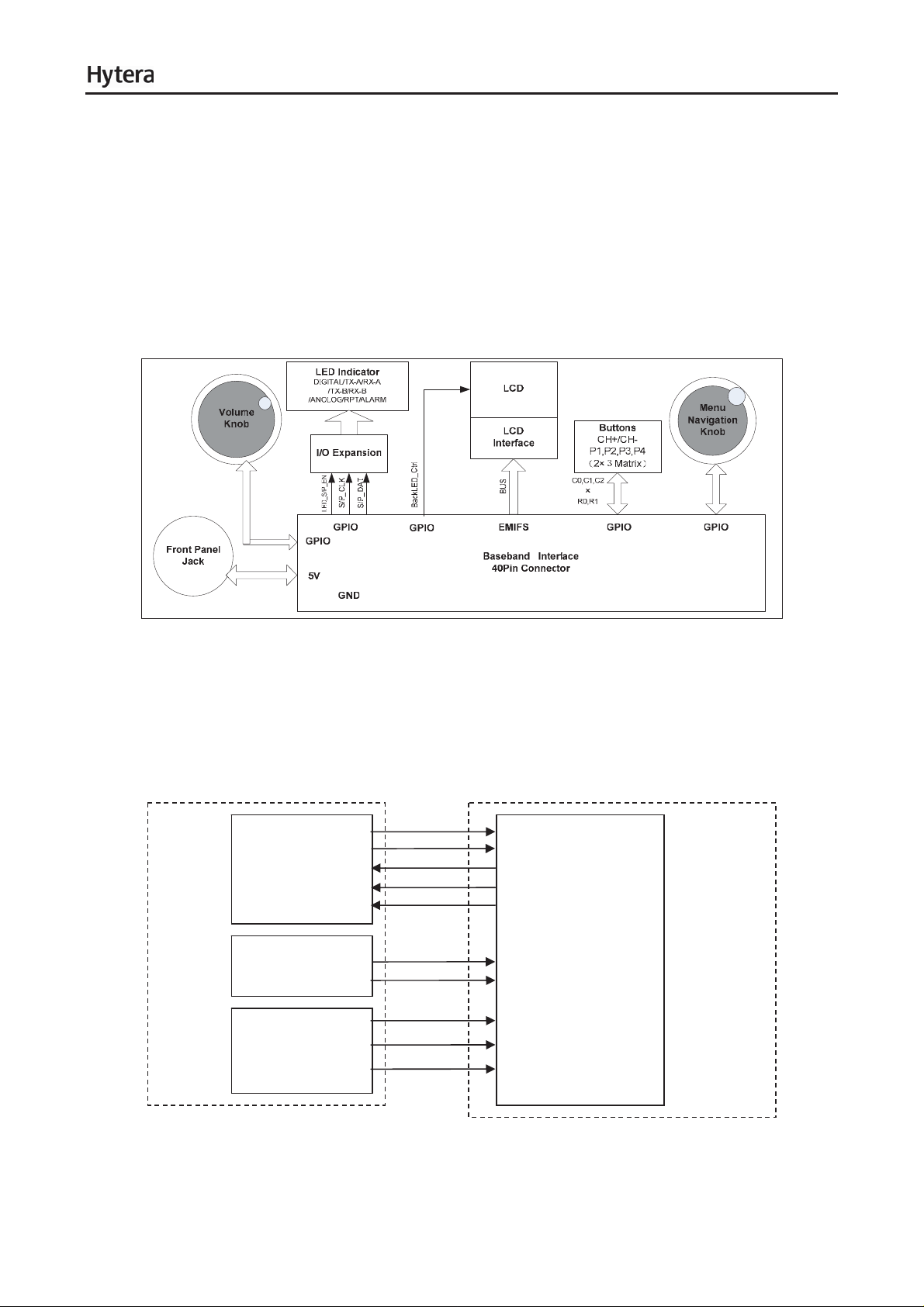

6.1.1 Overview

The front panel is the control panel, where you can see keys, Volume Control knob, Navigation knob,

LED indicator, LCD display and 10-Pin interface. The front panel is connected to the baseband board via

40-Pin FFC. See the following figure:

Figure 6-1 Front Panel Overview

6.1.2 Keys and Knobs

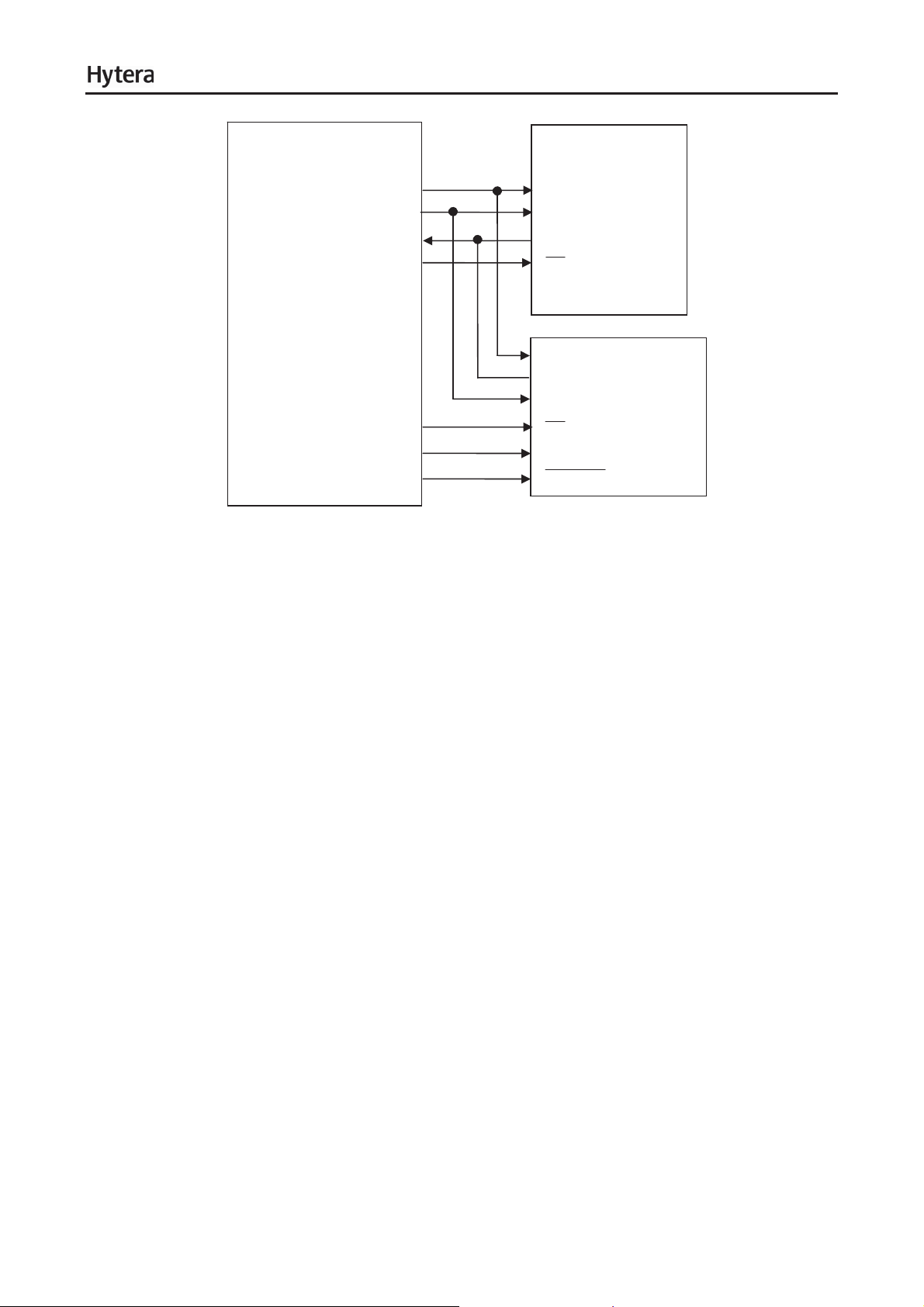

The keys on the front panel are controlled by key matrix of TX OMAP5912 (U102), and the Volume

Control knob and Navigation knob are controlled by GPIO of TX OMAP5912 (U102). See the following

figure:

KB_R0(G18)

KB_R1(F19)

KB_C0(F18)

KB_C1(D20)

KB_C2(D19)

TX OMAP5912

U102

GPIO4(P20)

GPIO6(P19)

GPIO46(W21)

GPIO49(L14)

GPIO26(AA9)

Baseband

Board

Front

Panel

BOARD

CH+/CH-

P1, P2, P3, P4

(2×3 Key matrix)

Volume control

knob

Menu navigation

knob

VOL_GPIO1

VOL_GPIO2

KNOB_A

KNOB_B

KNOB_C

Figure 6-2 Key and Knob Control Diagram for the Front Panel

6

Page 10

Service Manual

A

−

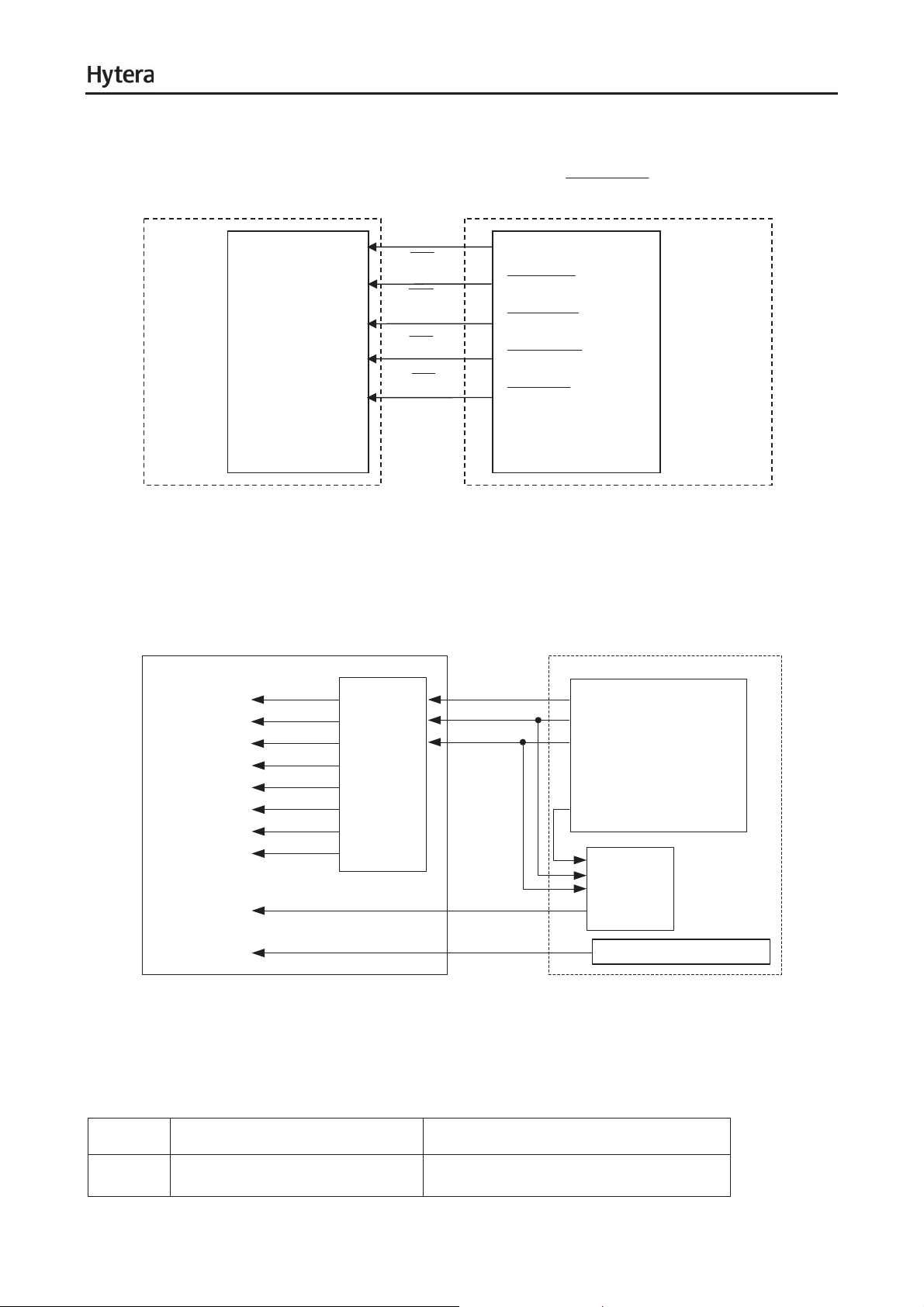

6.1.3 LCD Display

To enhance LCD refreshing rate, parallel data interface is used. It connects to EMIFS data bus of TX

OMAP5912 (U102) and the chip select is subject to the control of

D07D0

OE

FLASH.OE (U4)

WE

Front

Panel

BOARD

LCD

Interface

J1

CS

1

FLASH.WE (W2)

FLASH.CS2 (M4)

FLASH.A1(J8)

OMAP5912

6-3 LCD Control Diagram

FLASH.CS2 . See the following figure:

D7-FLASH.D0

Baseband

Board

BOARD

U102

6.1.4 LED Indicator

The 9 LED indicators on the front panel are controlled by the IO chip (U1), while the backlight of LCD

and keypad is controlled by the IO chip (U401) of baseband board. See the following figure:

Blue LED

Red LED

Green LED

Red LED

Green LED

Yellow LED

Green LED

Red LED

FNT BOARD

Backlight LED

Red and

Green LED

DIGITAL

TX-A

RX-A

TX-B

RX-B

ANALOG

RPT

ALARM

74HC594

BACK LED_CTRL

PWR_LED_CTRL

EN

DAT

CLK

U1

Figure 6-4 LED Control Diagram for the Front Panel

LED_S/P_EN

S/P_DAT

S/P_CLK

GPIO5(P3)

GPIO56 (V15)

GPIO42(W16)

TX OMAP5912

U102

GPIO39(AA15)

EN

DAT

CLK

74HC594

U401

PWR_LED_CTRL LOGIC

BASEBAND

BOARD

6.1.5 10-Pin Interface

The 10-Pin interface on the front panel is used to connect the audio accessory or data cable. Its

definition is as below:

Pin No. Name Description

1 Accessory identification port 1 To form an accessory identification

7

Page 11

matrix with Pin 10.

2 PTT input 3.3V CMOS, valid for low level

This pin can output received audio,

3 Handset output

when Handset is checked in the CPS.

When this pin is used for USB, USB of

4 USB0_D-

DB26 will be disabled

Service Manual

5GND

6 USB_VBUS 5V/500mA

7 Mic input MIC signal input of palm microphone

8 USB0_D+

9 HOOK Reserved

10 Accessory identification port 2

Table 6-1 10-Pin Interface Description

For grounding

When this pin is used for USB, USB of

DB26 will be disabled

To form an accessory identification

matrix with Pin 1.

6.1.6 Interface between Front Panel and Baseband Board

The interface is used to connect baseband board and front panel. Its definition is as below:

Pin No. Name Description

1 MMP10_Mic_IN Mic signal input

2 MIC_GROUND Mic signal ground

3 MMP_ACC_IO1 Accessory detection input

4 V_BUS 5V power supply (USB)

5 MMP_PRGM_IO4 Programmable key input

6 MMP_PRGM_IO3 Programmable key input

7 USB0_D- USB data -

8 USB0_D+ USB data +

9 MMP_PRGM_IO0 Programmable key input

10 KNOB_A Navigation knob input

11 KNOB_B Navigation knob input

12 MMP10_SPK_AUDIO SPK signal output

8

Page 12

13 VOL_GPIO1 Volume control knob input

14 VOL_GPIO2 Volume control knob input

15 KNOB_C Navigation knob input

16 BACKLED_CTRL Backlight control signal output

Service Manual

17

OUT_TX-RST

LCD reset signal

18 KB_C0

19 KB_C1

Keypad matrix signal output

20 KB_C2

21 KB_R0

Keypad matrix signal input

22 KB_R1

23 DC_PWR_LED_CTRL DC power LED control

24 LED_S/P_EN IO chip select signal

25 S/P_CLK IO chip clock signal

26 S/P_DAT IO chip data signal

27

28

OE_LCD

WE_LCD

LCD read signal

LCD write signal

29 CS2_LCD LCD chip select signal

30 F_A1_LCD LCD command/data address selection

31 F_D7_LCD

32 F_D6_LCD

33 F_D5_LCD

34 F_D4_LCD

LCD data bus

35 F_D3_LCD

36 F_D2_LCD

37 F_D1_LCD

38 F_D0_LCD

39 GND

For grounding

40 5V_GPS 5V power supply for front panel

Table 6-2 40-Pin Interface Description

9

Page 13

Service Manual

6.2 Main Board

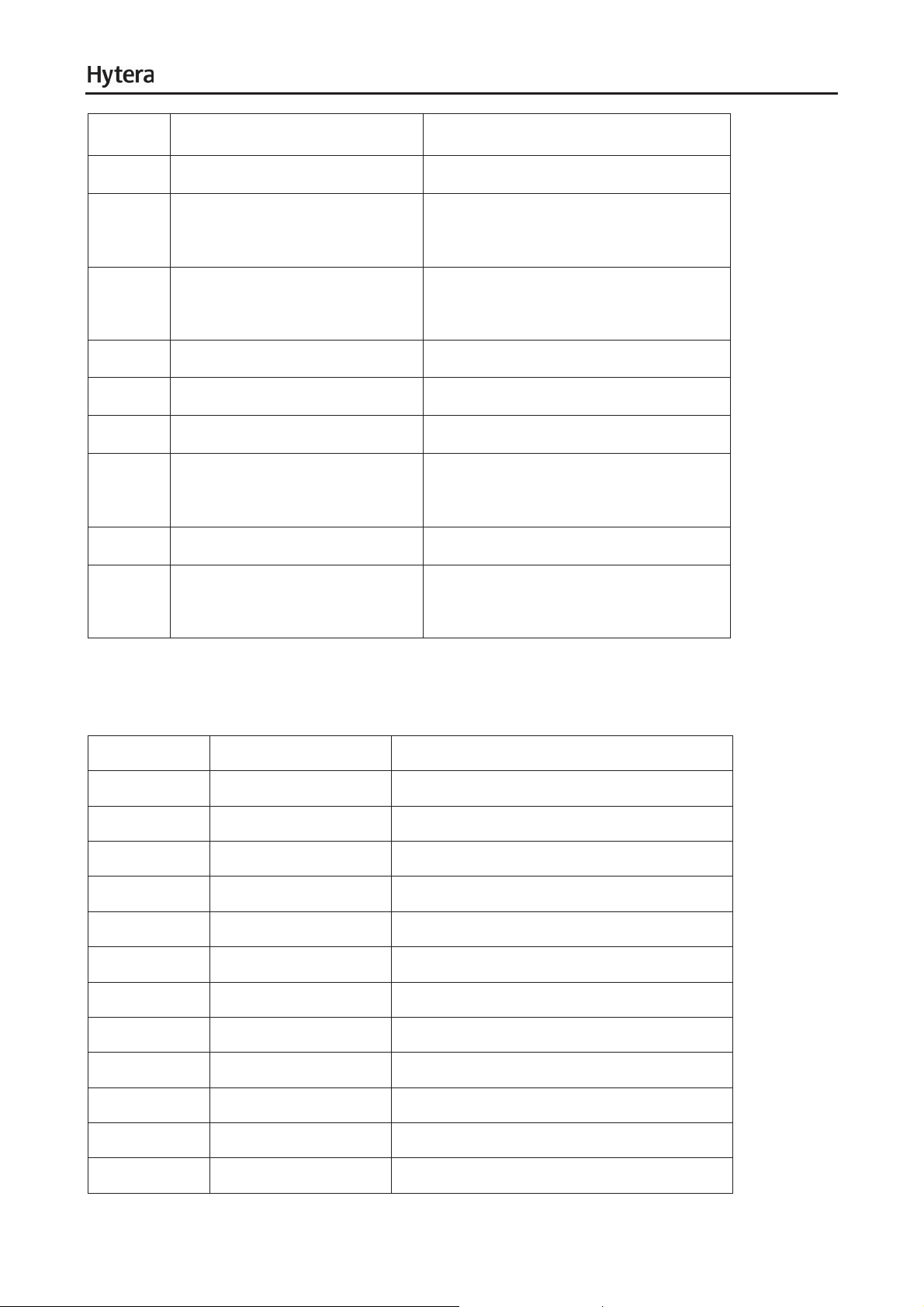

6.2.1 Overview

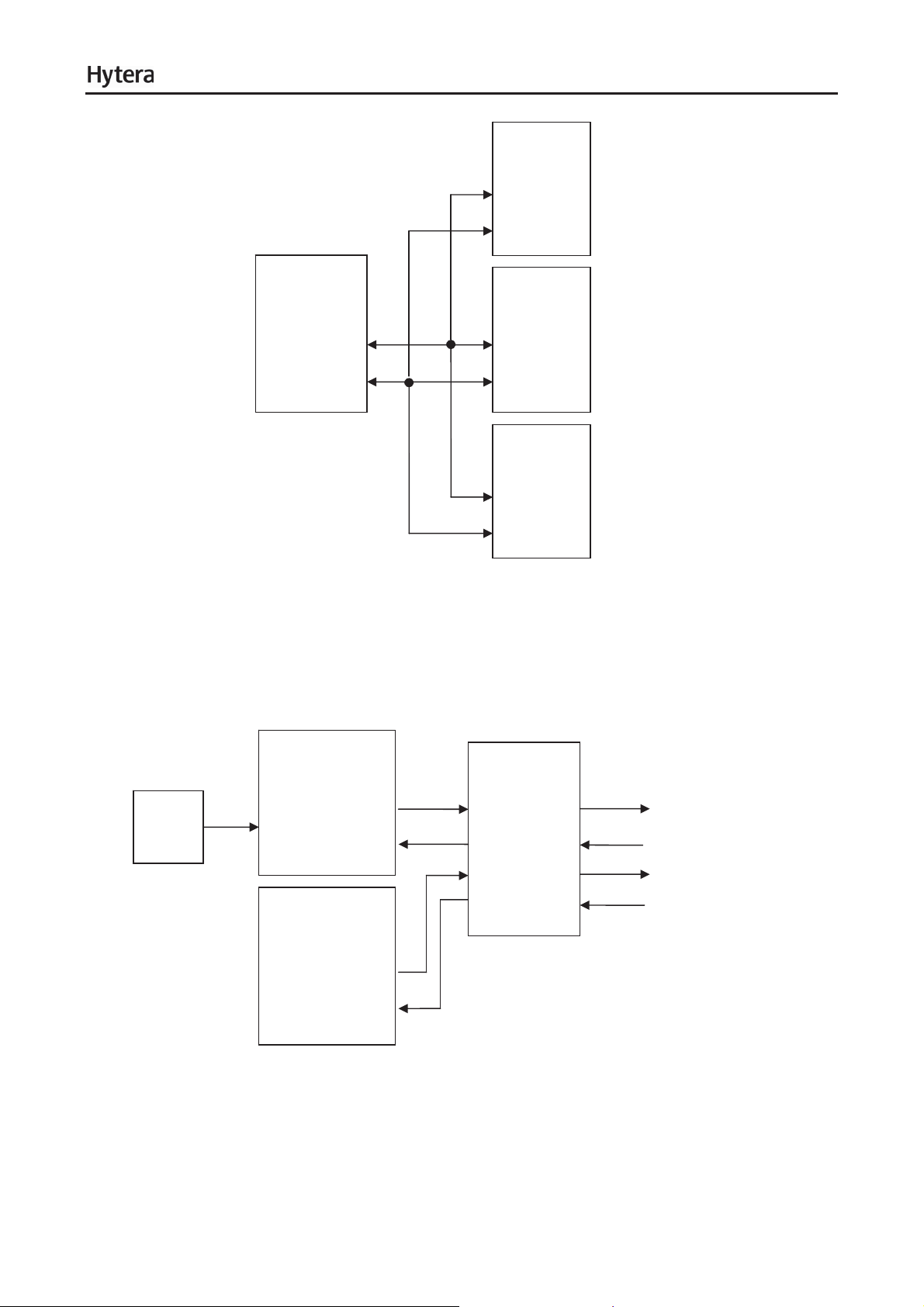

Baseband board consists of main chip (TX OMAP and RX OMAP), audio processing chip (CODEC) and

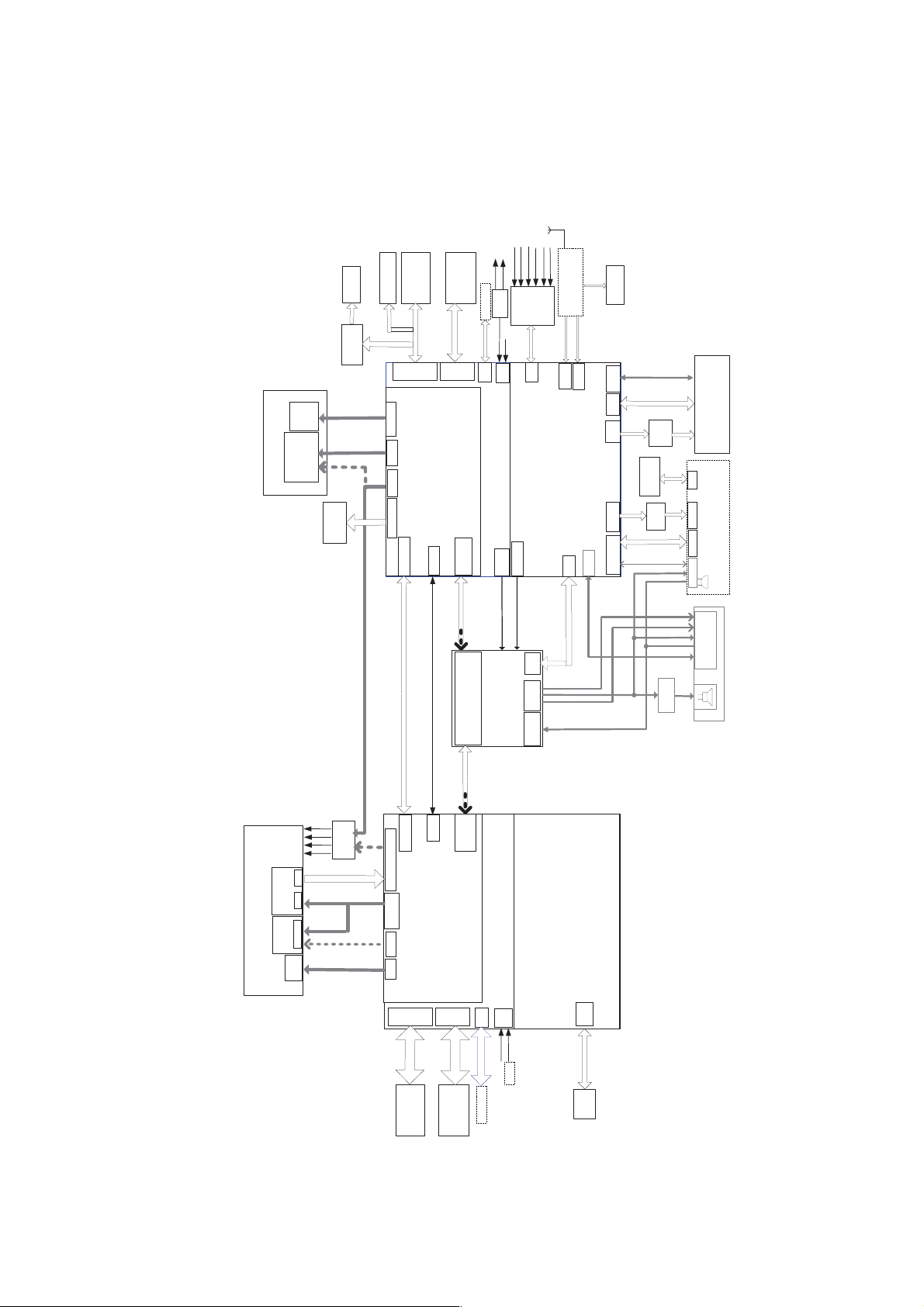

peripheral equipment. See the following figure:

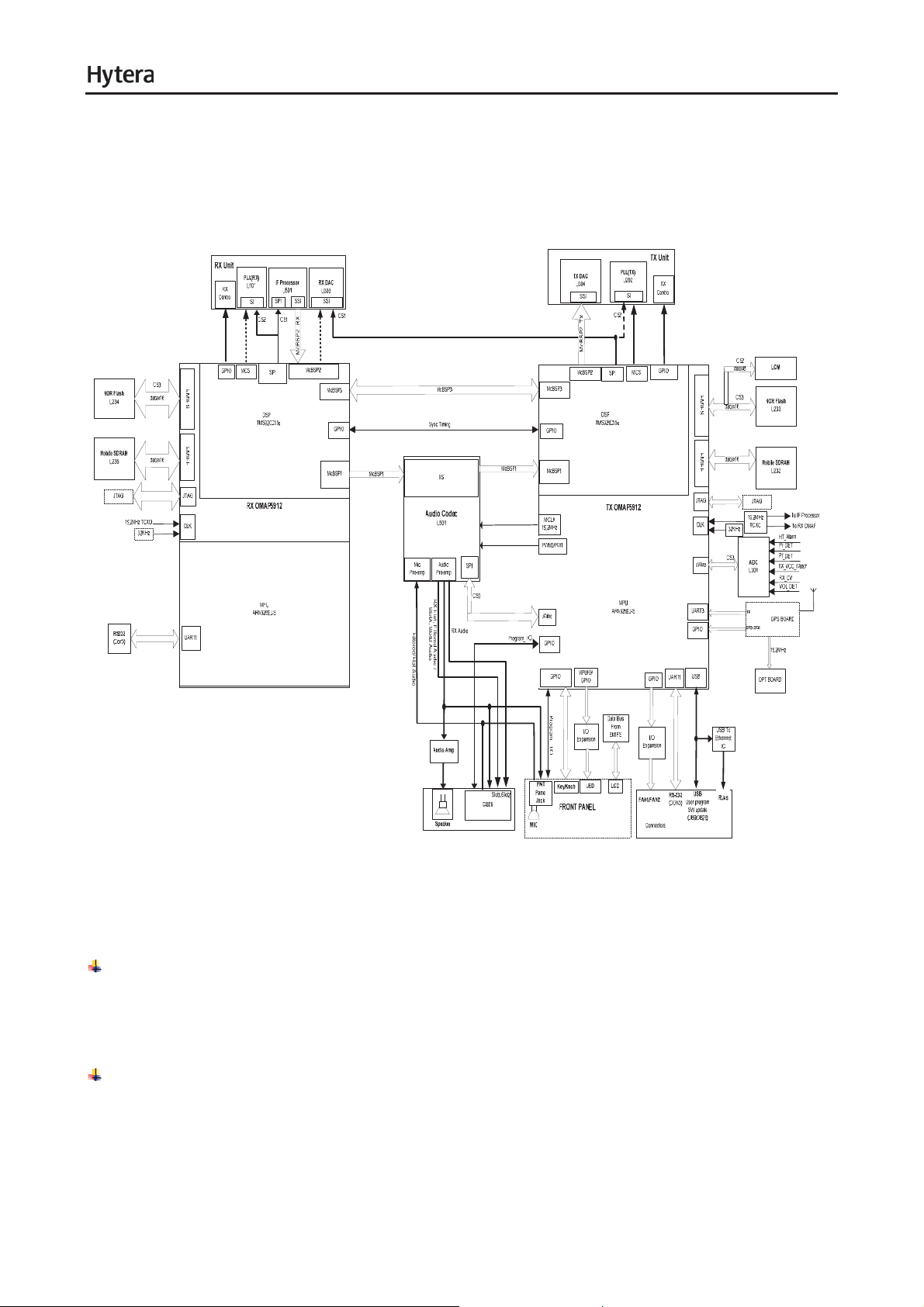

Figure 6-5 Baseband Block Diagram

As a highly integrated hardware platform, OMAP5912 incorporates 2 processors: ARM+DSP. The

function of RX OMAP and TX OMAP is described below:

RX OMAP5912

(1) ARM: Reserved.

(2) DSP: to handle the algorithm of RX baseband signal and to control SPI, McBSP1 and McBSP3

TX OMAP5912

(1) ARM: To run MMI software, part of stack software and related peripheral devices such as UART1,

UART3, USB, KEYPAD, LCD and LED.

(2) DSP: to handle the algorithm of TX baseband signal and to control SPI, McBSP1 and McBSP3

10

Page 14

Service Manual

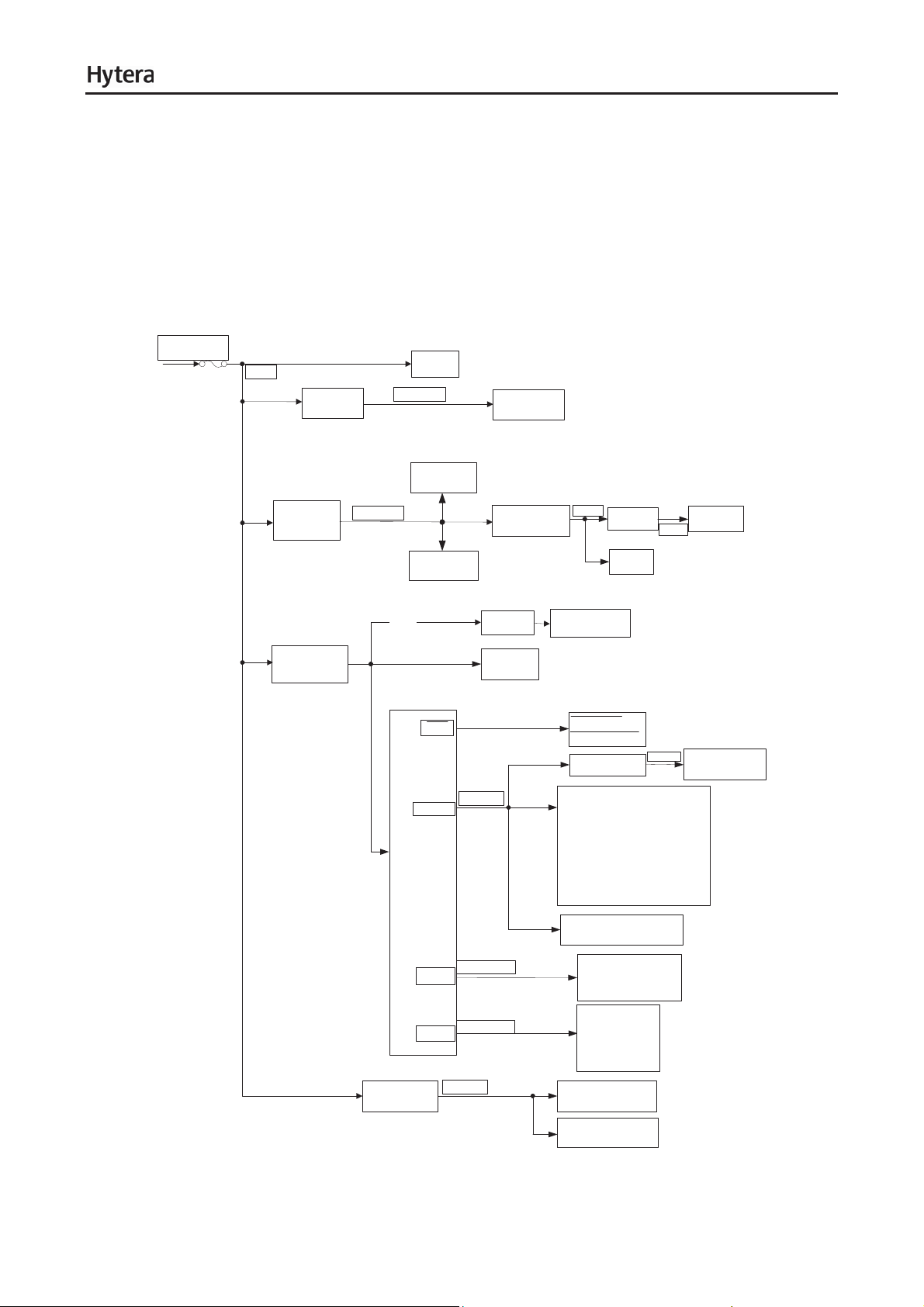

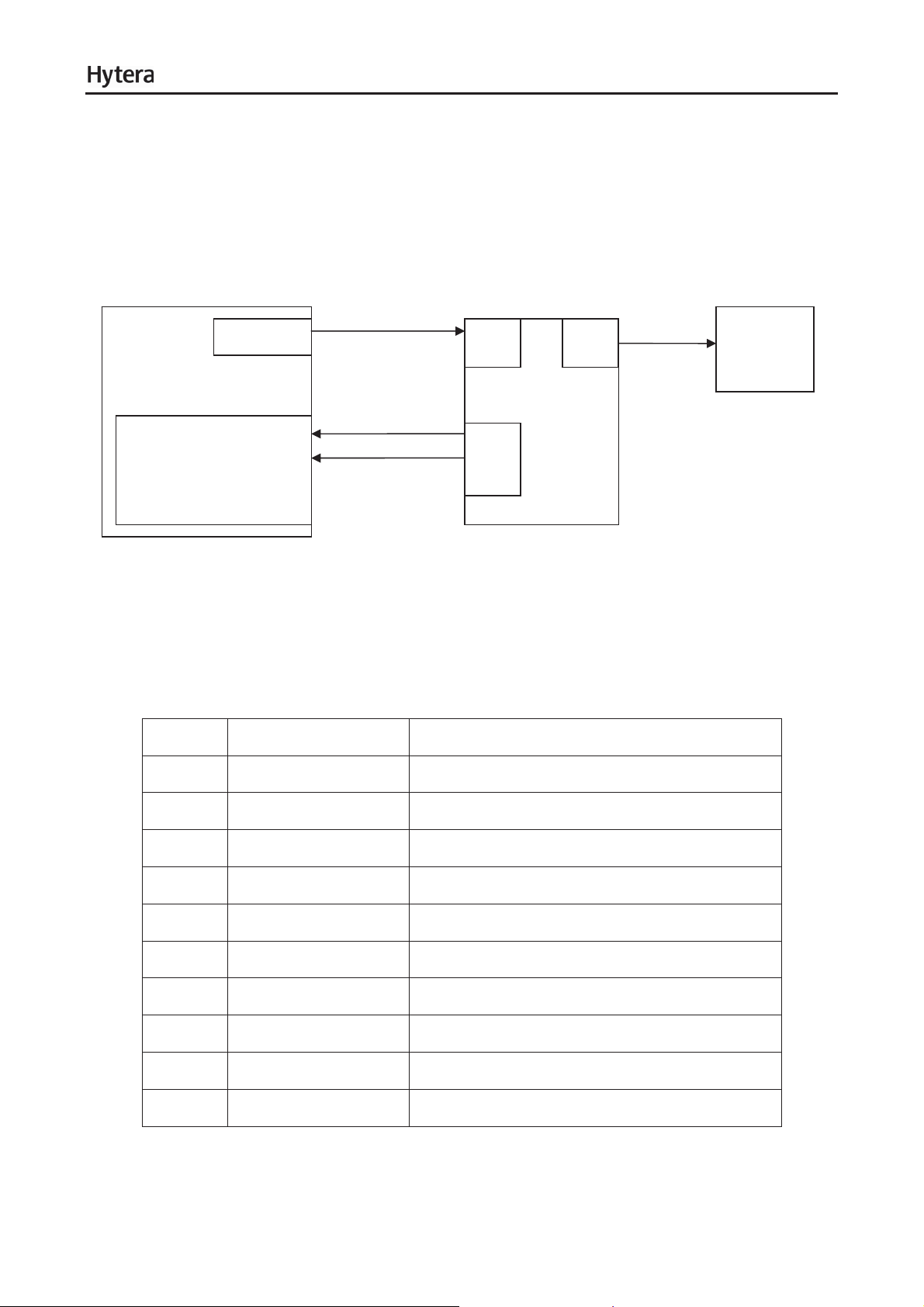

6.2.2 Power Supply Description

Both PA circuit and baseband circuit are powered by the external power supply directly. The power

supply circuit for the baseband board supplies power for the baseband circuit and its auxiliary modules,

and provides 9.3V voltage for the exciter board and RX board. After the DC power supply is connected,

the baseband board is powered up, and provides 13.6V voltage for the external development interface

via OMPA control. See the following figure:

Bat Power

11V~15.6V

B+

Filter and

Fuse

TX Board

13V6A(1A)

Receive Board

Accessory

Connectory(1A)

U821 (1A)

U801

(3A)

9V3A(1A)

Exciter Board

RST

DCDC1

PMU U803

VBUS_SW500mA

Accy Level

Translator

3V3D(1.2A)

U807

5VA

MMP/MMC_USB

MPU_RST

PWRON_RST

TPS72216DBVR

OMAP DVDD

(1.2.3.5.6.7.8.9)DVddrtc

OMAP Perpherial

FLASH

Indication LED

DAC 5610/5604

Shift/store register BU4094BCFV

ADM8515 VDDIOǃAVDDǃVREF

TUSB1105 VCCǃVCCIO

VRTC

CODEC_DigIO

MAX3232

U806

ADC U301

DAC U304

3V3A

1V6A

CODEC_AVDD

DSA321SDA

OMAP

CVDDA.CVCCDLL

DCDC2

DCDC3

U802

(3A)

5V_GPS

Figure 6-6 System Power Supply Block Diagram

11

1V8D(1A)

1V6D 900mA

CODEC Core

CODEC_VREF

SDRAM

OMAPDVDD4

OMAP Core

CVDD1.2.3.RTC

Reserved for

CVDDA of OMAP

GPS 5V

Front Panel Board

Audio_OpAmP

Page 15

Service Manual

After going through the filter and protection circuit, the 13.6V power supply will power external devices

via the expansion interface. The current may be up to 1A. For the 9V3A power supply, it is supplied by

U821, and output by ADJ with current up to 1A. It is used to power part of the exciter, RX and baseband

circuit. The U821 output control pin is valid at low level, and is grounded. It can output 9.3V power after

power-on. As for U807, it receives 9V3A power and outputs 5V power, which powers the D/A conversion

chip and power management IC (U806). U806 supplies power (3V3A) for CODEC chip (U501). The

U807 output control pin is valid at high level. It can output 5V power after power-on.

U801 is a DC-DC chip with adjustable output. After receiving 13.6V power, it will output 5VD power,

which supplies U803 and USB with 5V power. U803 is a PMU chip. It has 3 DC-DC output pins and 2

2

LDO output pins. U803 is configured by OMAP via the I

below:

C interface. Description of DC-DC pins is shown

1) DC-DC1 is controlled by U803 (PIN10). When the level is 0/1, the DC-DC1 output will be 3V/3.3V.

The maximum current is 1.2A.

2) DC-DC2 is controlled by U803 (PIN32). When the level is 0/1, the DC-DC2 output will be 1.8V/2.5V.

The maximum current is 1A.

3) DC-DC3 is controlled by U803 (PIN1). It can output 1V6D power. The maximum current is 900mA.

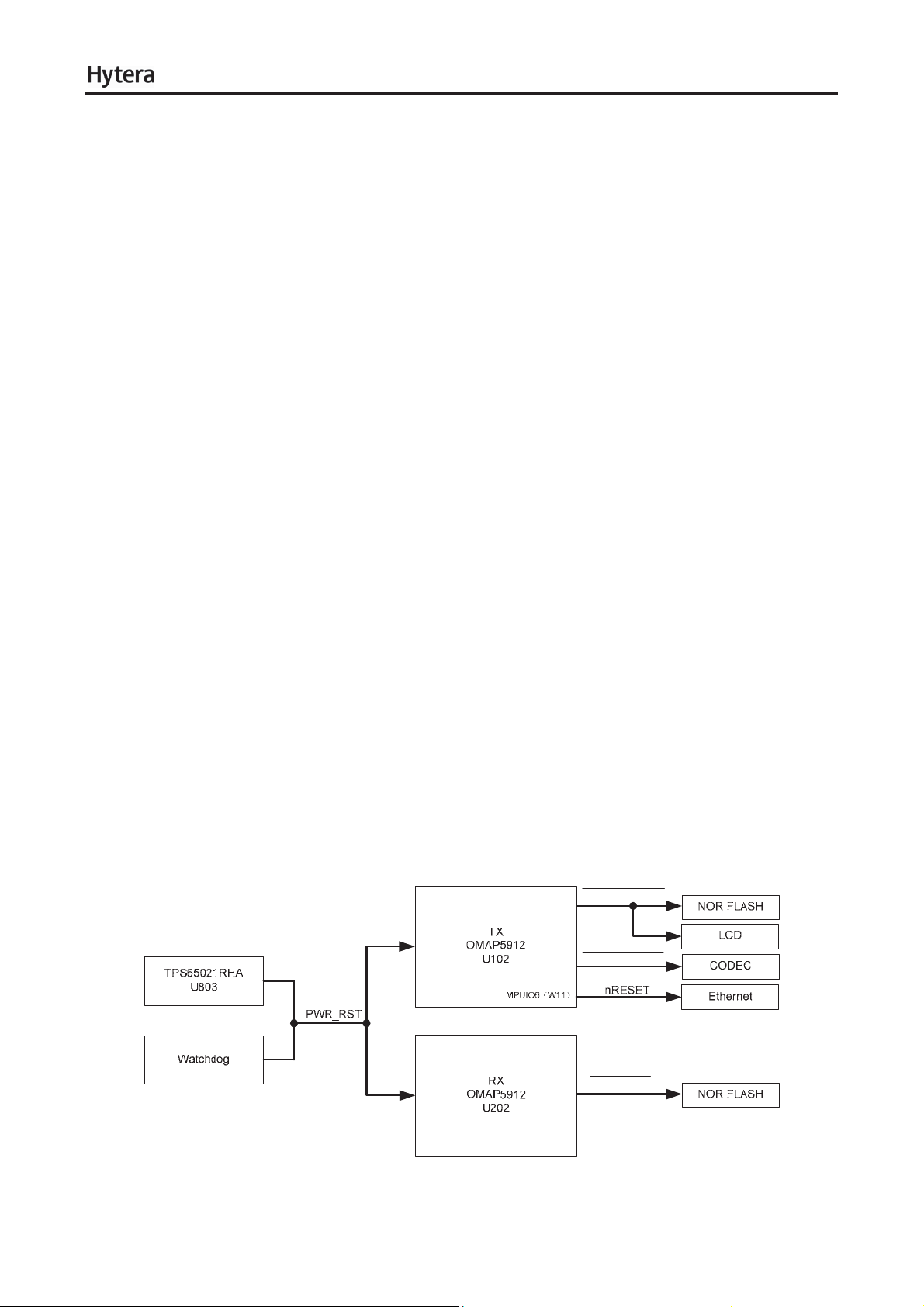

6.2.3 Reset

When the system is powered on, PMU will generate a reset signal “PWR_RST” to reset RX OMAP and

TX OMAP. When the system works abnormally, the watchdog will generate a 220ms reset signal as well.

See the following figure:

OUT_TX-RST

CODEC_RST

Figure 6-7 System Reset Block Diagram

12

OUT-RST

Page 16

Service Manual

After making response to power-up reset, OMAP5912 will output RST_OUT signal, and maintain low

level for some time to reset the peripheral equipment (NOR Flash) of OMAP. For CODEC chip (U501),

its resetting is subject to MPUIO6 of TX OMAP. The reset sequence of OMAP5912 is shown below:

Figure 6-8 Reset Sequence

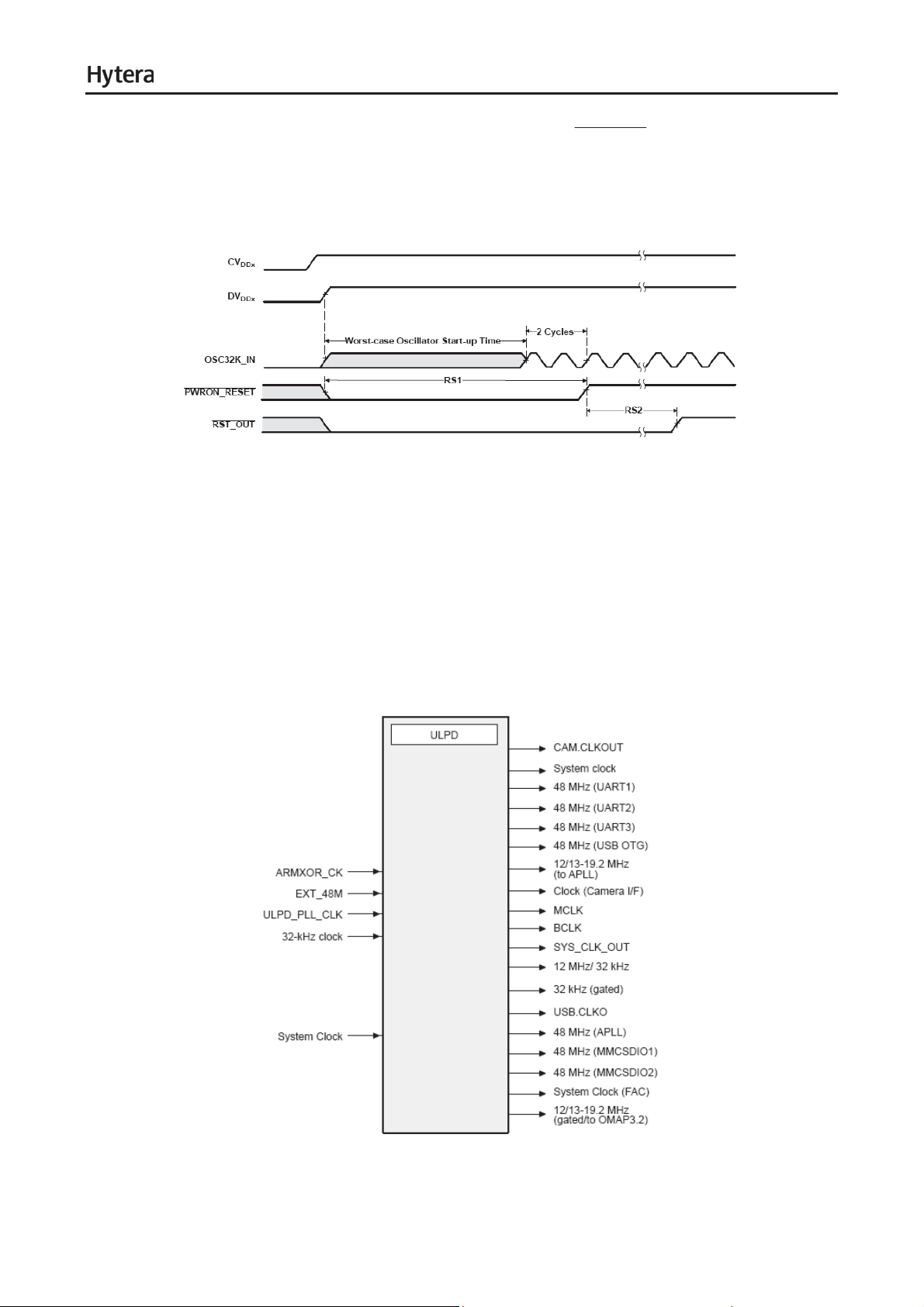

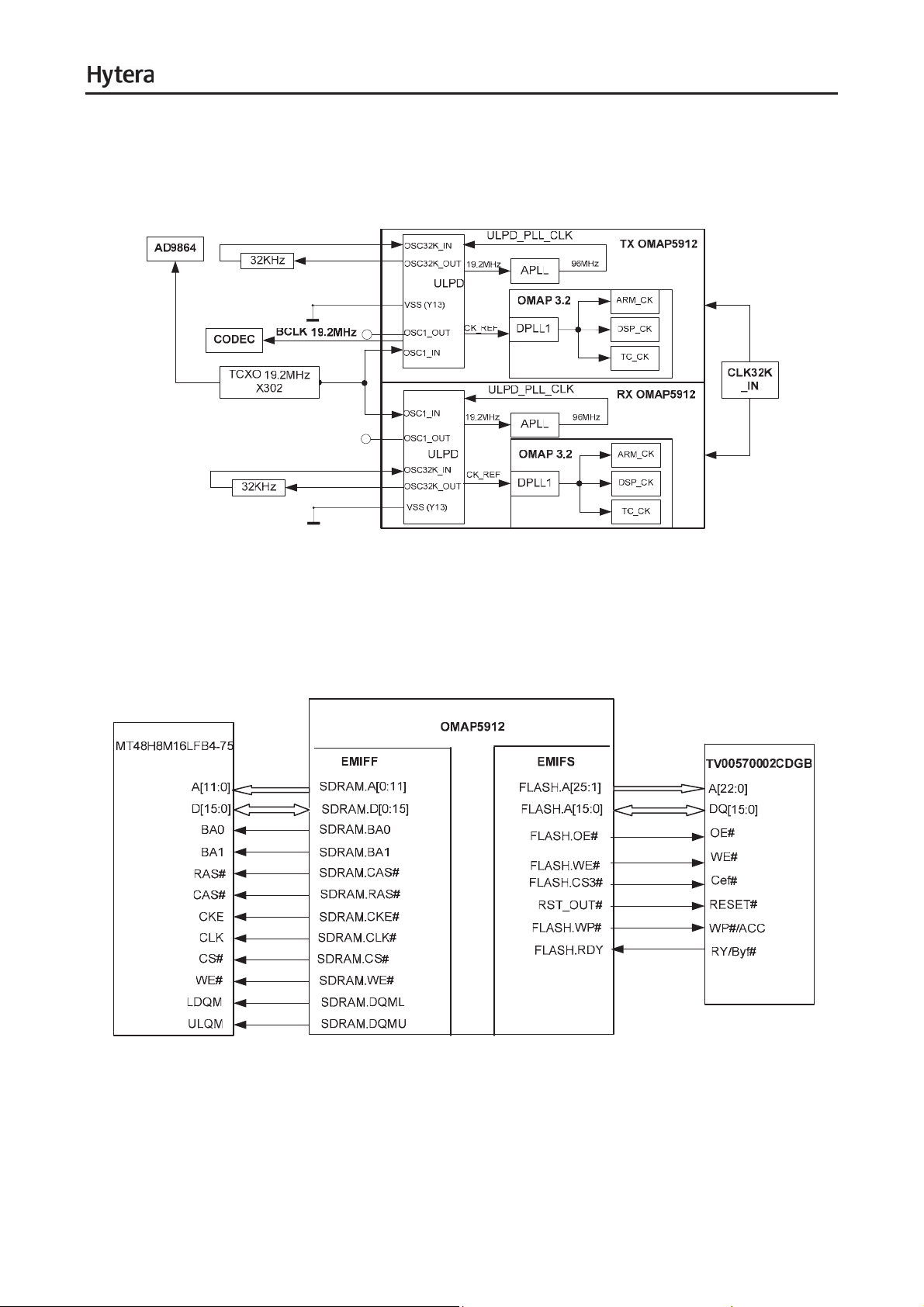

6.2.4 Clock

OMAP5912 requires two clocks: system clock and 32K clock. The system clock (12MHz, 13MHz or

19.2MHz) can be provided by an external oscillator or square-wave clock signal. This product’s system

clock is provided by

(Ultralow-power device), which is responsible for OMAP clock management. The clock output by UPLD

is connected to appropriate external interface. See the following figure:

19.2MHz TCXO. Both system clock and 32K clock are provided by ULPD

Figure 6-9 External Clock

13

Page 17

Service Manual

For the built-in and external clock of OMAP2912, there are two reset modes: Reset Mode0 and Reset

Mode1. Reset Mode0 is adopted for this system. As for this product, system clock uses external clock,

while 32K clock uses built-in clock. See the following figure:

Figure 6-10 Clock Connection Block Diagram

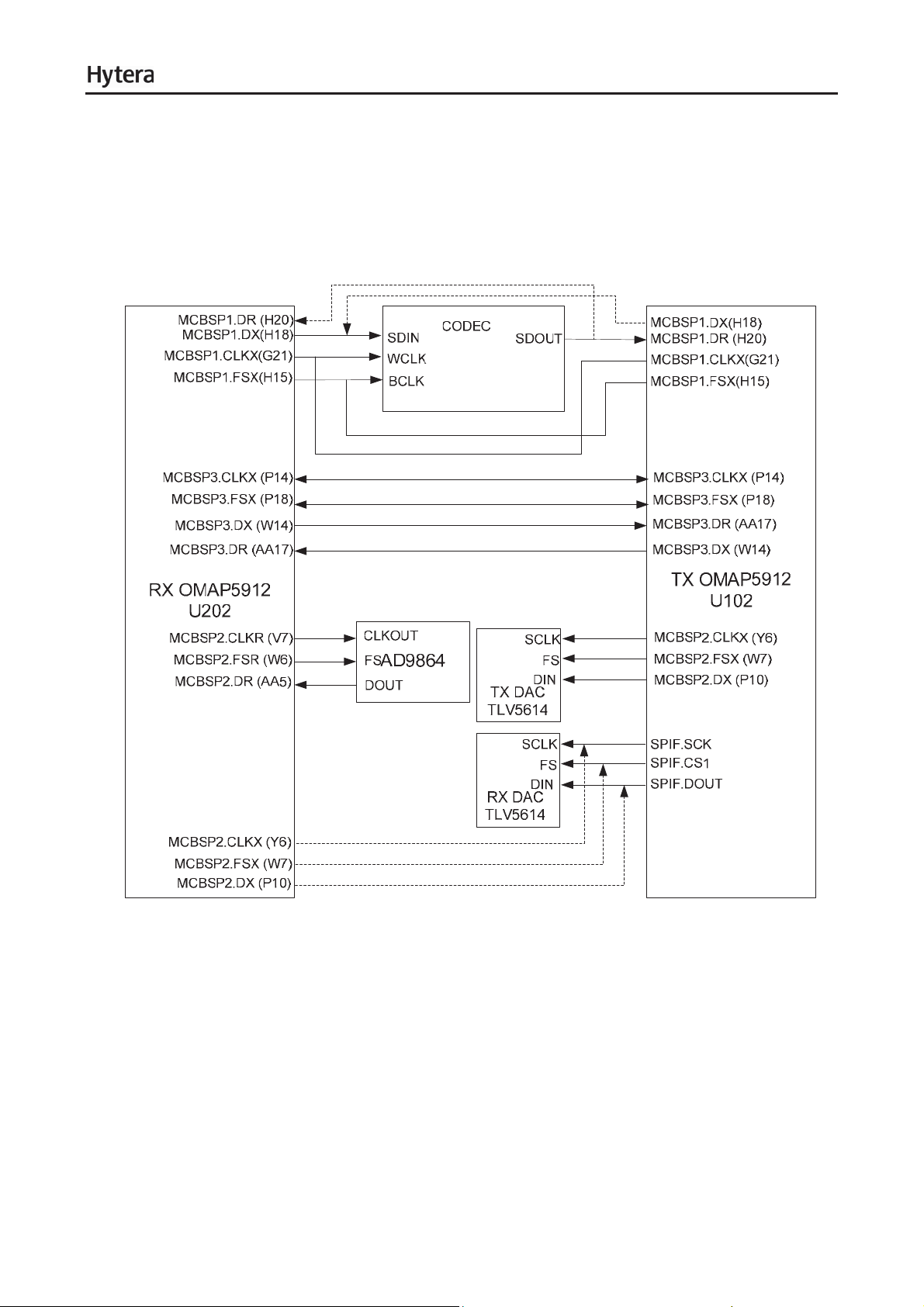

6.2.5 Memory

OMAP5912 provides two types of external memory interfaces: external memory interface slow (EMIFS)

and external memory interface fast (EMIFF). External NOR Flash and Mobile SDRAM have been

expanded for two OMAPs in the system. See the following figure:

6-11 Memory Block Diagram

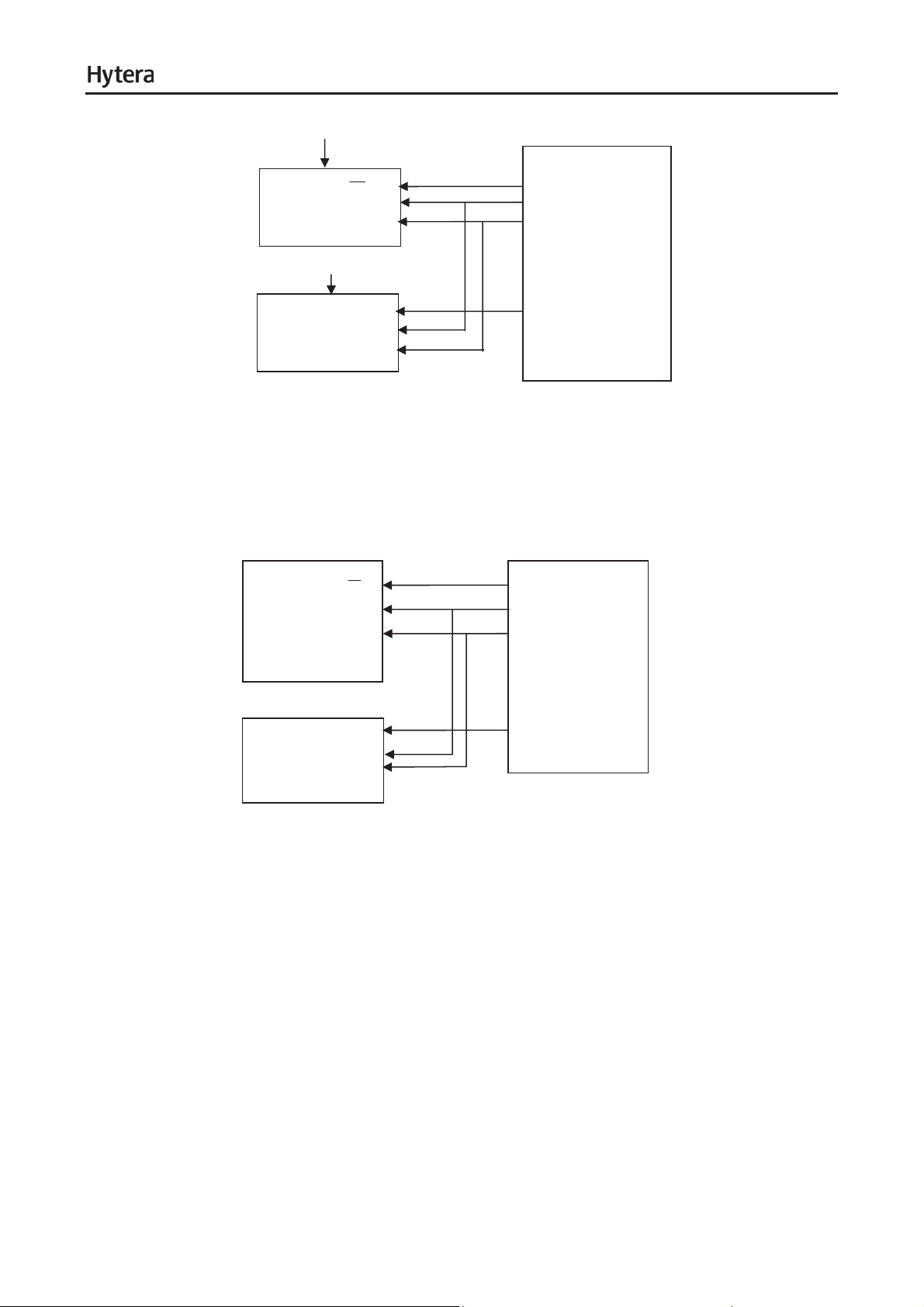

6.2.6 MCBSP

OMAP5912 has 3 McBSP interfaces: McBSP1, McBSP2 and McBSP3. McBSP1 of RX OMAP and TX

OMAP is used to communicate with Codec. RX OMAP McBSP2 is used to connect SSI interface of

14

Page 18

Service Manual

AD9864 to receive demodulation signal from AD9864, and TX OMAP McBSP2 is reserved for SPI

interface of RX DAC TLV5614. McBSP2 of TX OMAP is used to connect SSI interface of TX DAC

TLV5614. TLV5614 works in Slave mode and is managed by DSP. McBSP3 is used to connect RX

OMAP and TX OMAP for data transmission. See the following figure:

Figure 6-12 Diagram of MCBSP Connection

6.2.7 SPI

OMAP5912 has one SPI interface that can connect four SPI components. The descriptions are as follow:

(1) RX OPMAP5912 SPI Interface

The SPI interface of RX OMAP is used to configure IF processor (AD9894) and RX PLL chip

(SKY72310).

AD9894 is controlled by SPI chip select (CS1) of RX OMAP, and RX PLL chip is controlled by CS2. The

connection between RX OMAP SPI interface and AD9894/ RX PLL is shown below:

15

Page 19

3V3D

Service Manual

CS

SKY72310 SCK

Data

3V3D

SPIF.CS2(T19)

SPIF.SCK(U19)

SPIF.DOUT(R18)

RX OMAP5912

U202

PE

AD9864 PC

PD

SPIF.CS1 (N15)

Figure 6-13 RX OMAP SPI Connection Block Diagram

(2) TX OPMAP5912 SPI Interface

TX OMAP SPI is used to configure RX DAC TLV5614 (U303) and TX PLL chip (SKY72310). This chip is

controlled by CS2 and managed by DSP. RX DAC (U303) is controlled by CS1. See the following figure:

KY72310

s

CS

CLK

Data

SPIF.CS2(T19)

SPIF.SCK(U19)

SPIF.DOUT(R18)

OMAP5912

U102

FS

CLK

RX TLV5614 Data

Figure 6-

14 TX OMAP

SPI Connection Block Diagram

SPIF.CS1(N15)

6.2.8 MCSI

MCSI (Multi Channel Serial Interface) belongs to OMAP5912. There are two MCSIs with OMAP5912.

MCSI1 of RX/TX OMAP is reserved for appropriate RX/TX PLL chip to realize modulation feature. See

the following figure:

16

Page 20

Service Manual

˅

˅

CS

TX/RX SKY72310 SCK

Data

MCSI1.SYNC(W8)

MCSI1.CLK(M15)

MCSI1.DOUT(Y

8)

TX/RX OMAP5912

Figure 6-15 Diagram of MCSI Interfac

e

6.2.9 I2C

OMAP5912 provides one I2C interface, and supports communication rate up to 400Kbps. TX OMAP I2C

interface connects with PMU to dynamically adjust PMU voltage output. It works in Master mode. See

the following figure:

TX OMAP5912

U102

I2C.SDA˄V20

I2C.SCL˄T18

Figure 6-

16 Diagram of I

SDAT U803

SCLK

2

C Connection

6.2.10 MICROWIRE

OMAP5912 provides a MICROWIRE interface. The four chip select signals can drive four external

components. MICROWIRE interface signals include: ȝWIRE.CS, ȝWIRE.SCLK, ȝWIRE.SDO and

ȝWIRE.SDI.

In this system, only MICROWIRE interface of TX OMAP is used to connect CODEC and ADC TLV1548.

ȝWire CS0 controls CODEC and ȝWire CS3 controls ADC TLV1548. See the following figure:

17

Page 21

UWIRE.SDO(H19)

UWIRE.SCLK(J15)

UWIRE.SDI(J14)

UWIRE.CS0 (J18)

TX OMAP5912

U102

UWIRE.CS3 (J19)

GPIO37(M19)

GPIO2(D1

Service Manual

TLV320AIC29

U501

MOSI

SCLK

MISO

SS

DATA IN

DATA OUT

I/O CLK TLV1548

U301

CS

EOC

5)

CSTART

Figure 6-17 Diagram of MICROWIRE Connection

6.2.11 USB

OMAP processor provides 3 USB interfaces with rate of 1.5Mbps or 12Mbps. Available modes include

Host and Device. USB0 and USB2 of TX OMAP are used in this system. The description of TX OMAP

USB0 is as follow:

18

Page 22

TX

OMAP5912

U102

USB0_DM(R8)

Service Manual

DB9(J601)

USB_D-

USB_D+

DB26(J701)

USB_D-

USB0_DP(P9)

USB_D+

10pin Jack

USB_D-

USB_D+

Figure 6-18 Diagram of USB Interface

6.2.12 UART

OMAP5912 has 3 UART interfaces: UART1, UART2 and UART3. It supports hardware flow control. The

communication rate can be up to 1.5Mbps. See the following figure:

TX OMAP5912

GPS-XP4

GPS_TX

(TX)

UART1_TXD(Y14)

UART3.RX(K19)

UART1_RXD(V14)

UART3.TX(K18)

MAX3232

T1IN

R1OUT

T2IN

T1OUT

R1IN

T2OUT

TX_Data From Radio

TX_Data to Radio

RX_Data From Radio

RX

OMAP5912

UART1_TXD(Y14)

UART1_RXD(V14)

Figure 6-19 UART Connection Block Diagram

19

R2OUT

R2IN

RX_Data to Radio

Page 23

Service Manual

6.2.13 GPS (Reserved)

The system can obtain precise clock signal and related GPS data from the GPS module. The baseband

board connects with the GPS module via J108 and J109. J109 provides GPS module with 5V power

supply. The GPS module provides precise 19.2MHz clock source to exciter board through XS2. See the

following figure:

5V

J109

BASEBAND

GPIO63˄E18˅

UART3.RX˄K19˅

˄TX OMAP U102˅

J108

Figure 6The GPS module adopt

Definitions of GPS module are shown in table below:

Pin No. Name Description

s RS-232 port (baud rate: 9600BPS; 8 data bits; 1 stop bit; no parity check).

GPS-LOCK

TX

20 GPS Module Connection Block Diagram

XP3

XP4

GPS

XS2

19.2MHz

EXCITER

1 GPS-LOCKED GPS RX status

2NC

3NC

4NC

5NC

6NC

7NC

8NC

9 1PPS GPS pulse output

10 NC

Table 6-3 GPS Module Definitions

20

Page 24

Service Manual

6.2.14 Audio Path

The audio path is used to relay audio, output RX audio and input TX audio.

6.2.14.1 Relay Audio Path

After demodulated by AD9864, RX audio in digital/analog mode goes to RX OMAP. Then the audio is

sent to TX OMAP via McBSP3, and finally is subject to DA conversion to modulate VCO.See the

following figure:

AD9864

Q

McBSP2

RX

OMAP5912

U202

McBSP3

TX

OMAP5912

U102

McBSP2

DAC

TLV561

U304

MOD

Figure 6-21 Relay Audio Path

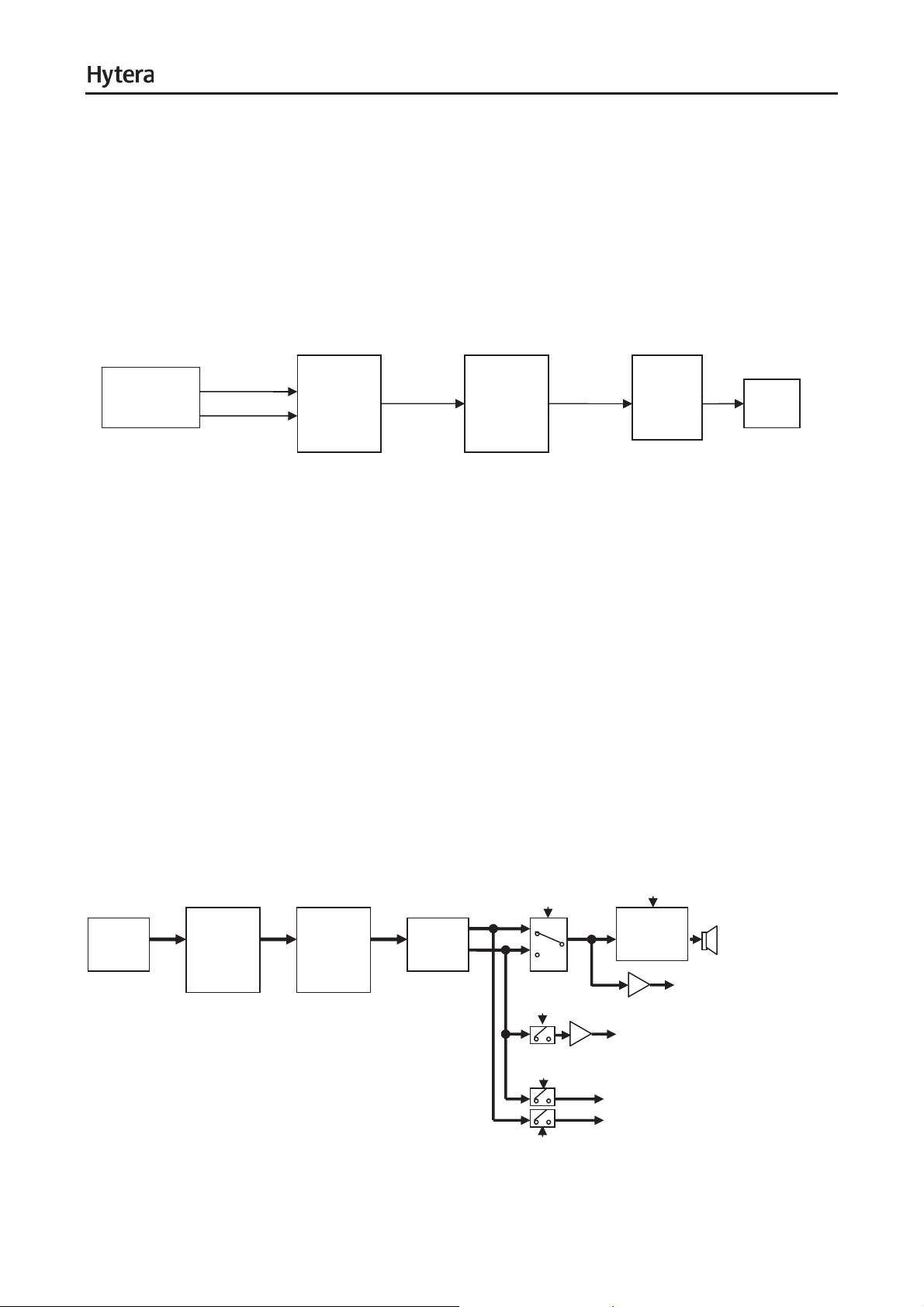

6.2.14.2 RX Audio Path

In digital mode, Codec can co

the left channel and right channel respectively, and select the time slot required for local audio

monitoring via the switch Slot1_EN. Meanwhile, under the control of Slot1_EN and Slot2_EN, the

outputs of Slot A and Slot B are sent to PIN24 and PIN25 of the further development port DB26 (J7

for further development.

In digital mode, SPK1 of CODEC can be configured to

the further development port DB26 (J701). The filtered audio from SPK2 is output to the speaker to

realize local monitoring via the audio amplifier or to the audio port of the front panel via the filter. See the

ntrol the audio output of Slot A from SPK1 and that of Slot B from SPK2 via

01)

output filtered audio or flat audio (RX_Audio) to

following figure:

RX

AD9864

McBSP2

RX

OMAP5912

U202

McBSP3

TX

OMAP5912

U102

McBSP1

CODEC

U501

Figure 6-22 RX Audio Block Diagram

21

Slot1_EN

SPK2

SPK1

RX _Audio_Mute

Slot1_EN

Slot2_EN

Slot A

Slot B

Audio_PA_EN

U502

TDA8547

MMP10_SPK_Audio

RX_Audio

DB26_PIN24

DB26_PIN25

Page 25

Service Manual

6.2.14.3 TX Audio Path

sy em ha wo ds of au sign ls: MM _Ext_Mic

The st s t kin MIC dio a P10_Mic_IN and DB26 _IN. The former is

from the accesso onnected to 10-Pin interface on the front panel, while the latter is from Pin 2 of

the further development port DB26 (J701). The EXT_MIC_C l can d through menu

or programming software to activate MMP10_Mic_IN or DB26_Ext_Mic_IN.

ry c the

TRL

signa be configure

This signal is sent to DSP of

TX OMAP via McBSP1 after processed by CODEC, and is transmitted via the TX circuit after DA

conversion and modulation. See the following figure:

Mod1

Mod2_RFCS

DAC

TLV5614

U304

MCBSP2 MCBSP1

TX

OMAP5912

U102

ADC

CODEC

U501

MMP10_Mic_IN

DB26_Ext_Mic_IN

EXT_MIC_CTRL

Figure 6-23 TX Audio Path

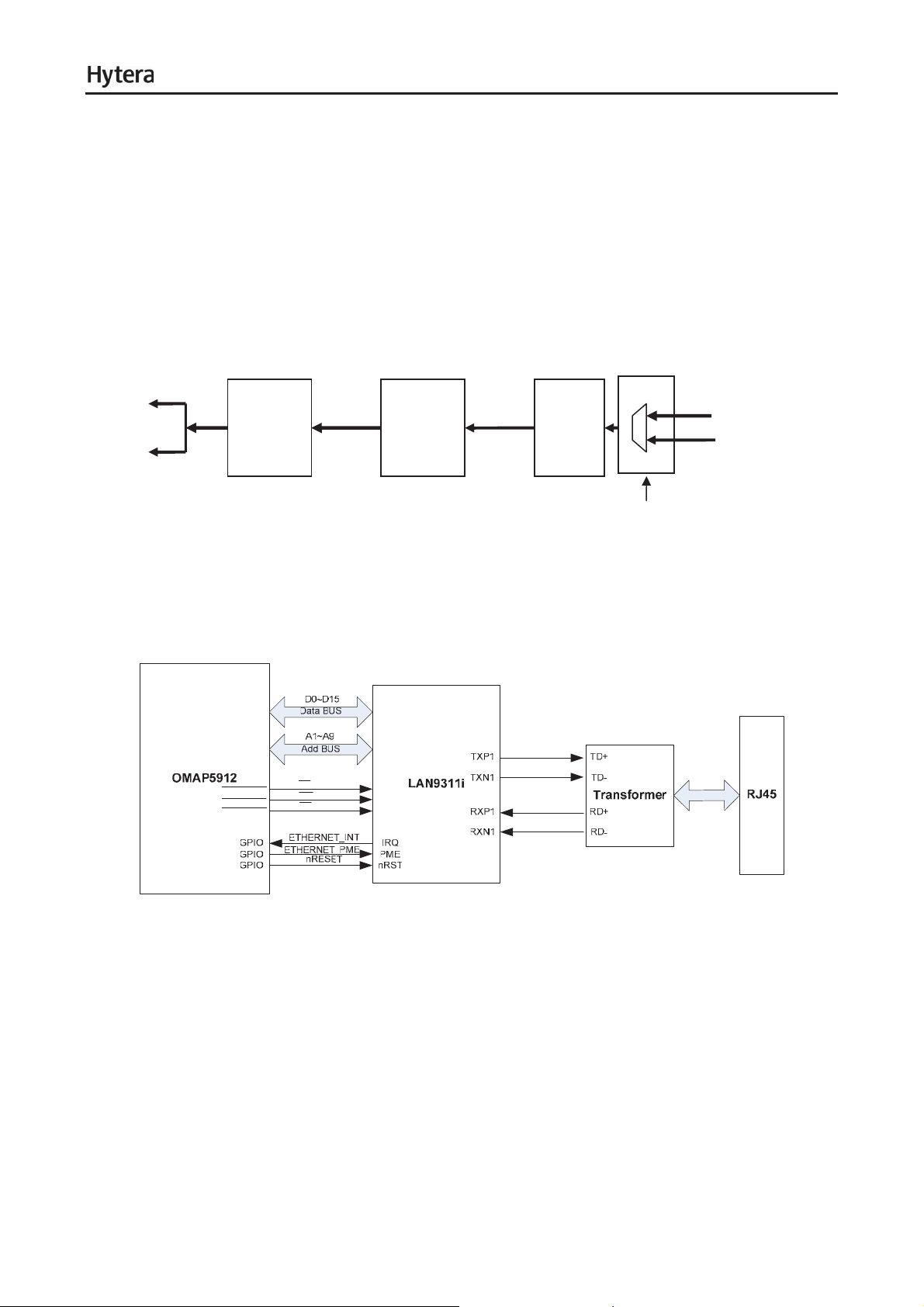

6.2.15 TCP/IP

TCP/IP is used to achieve remote monitoring and other exp

shown as below:

andable functions. The block diagram is

FLASH-OE

FLASH-WE

FLASH-CS0

OE

WR

CS

Figure 6-24 TCP/IP Block Diagram

22

Page 26

S

\

HU

/D

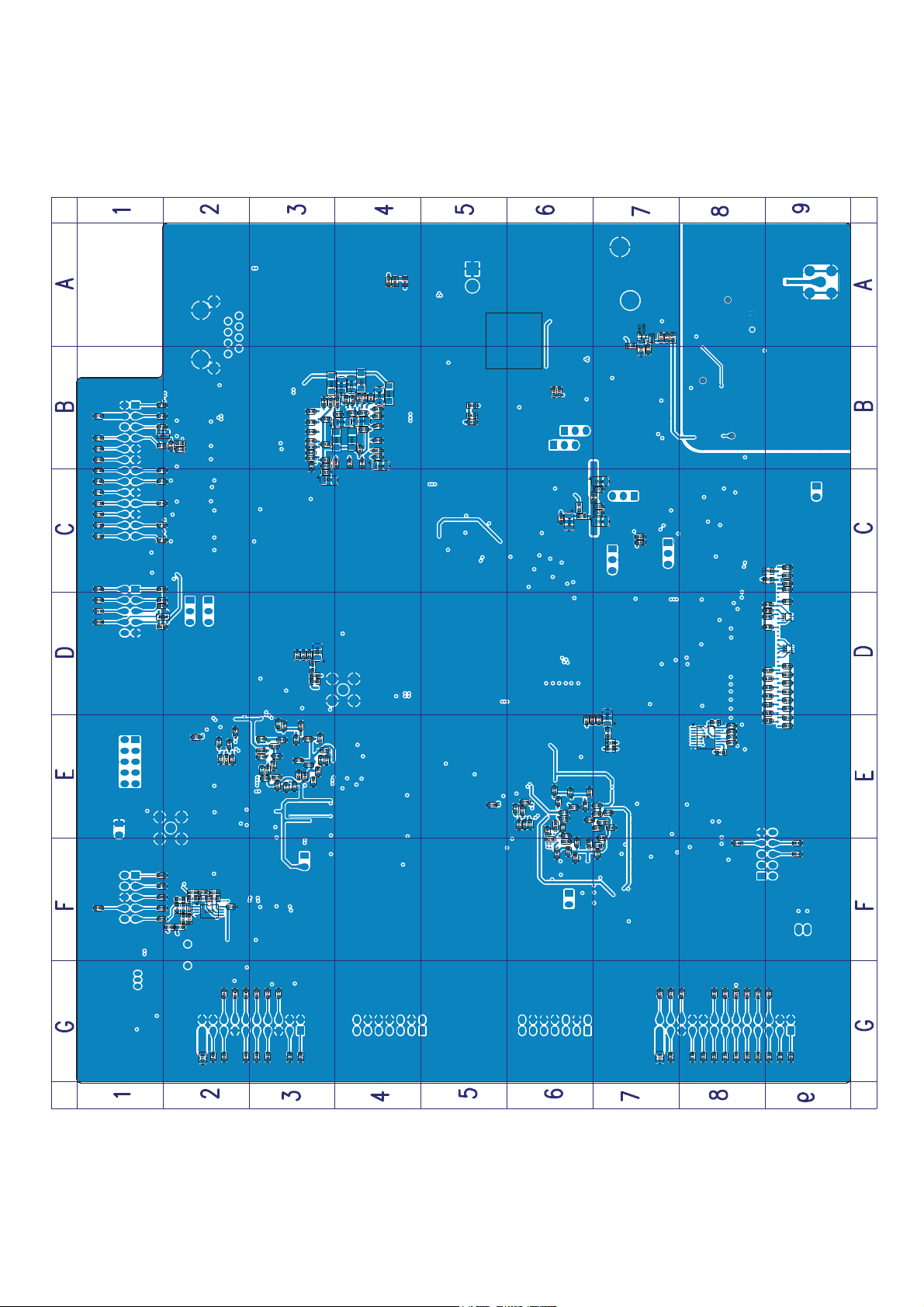

5';3&%9LHZ%DVHEDQG%RDUG

7R

3&%9LHZ

Page 27

\

HU

%RWWRP/D

5';3&%9LHZ%DVHEDQG%RDUG

Page 28

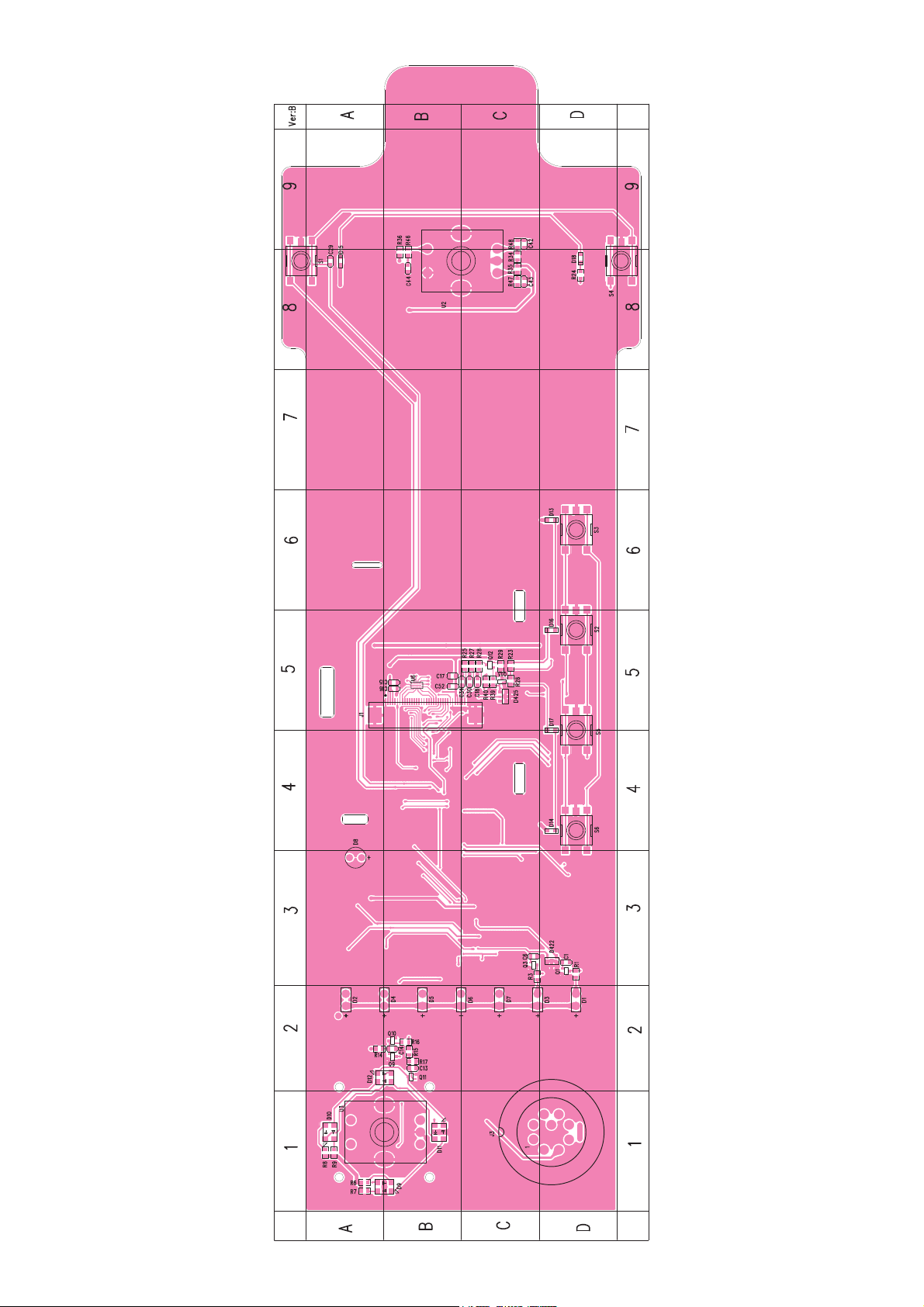

5';3&%9LHZ)URQW3DQHO

7RS/D\HU

Page 29

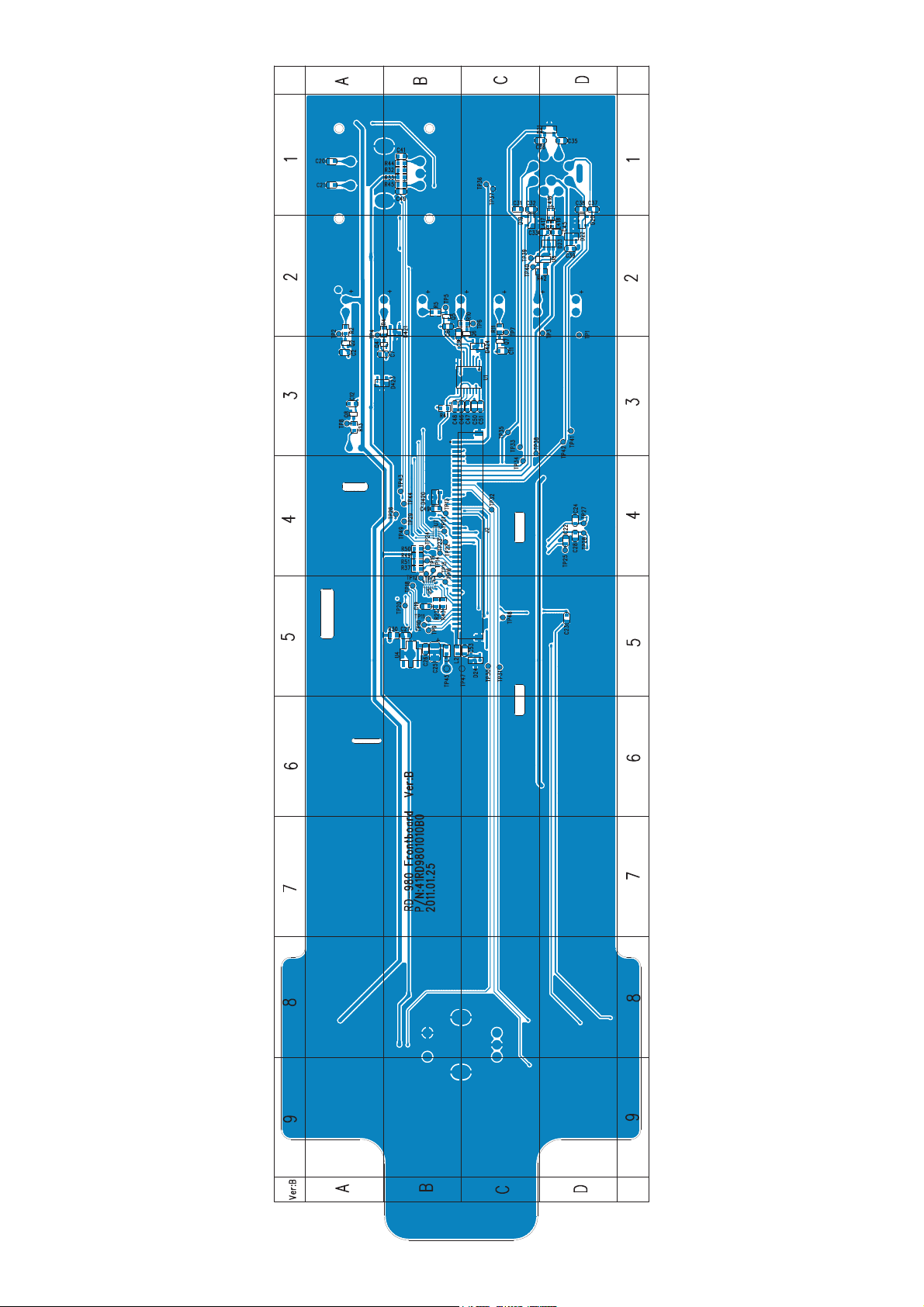

5';3&%9LHZ)URQW3DQHO

%RWWRP/D\HU

Page 30

TX Unit

g

To AD9864

To RX OMAP

VOL_DET

HT_Alarm

Pout_Check

TX_VCO_Watch

RX_VCO_Watch

,7

RJ45

/&'&6=/&0

72&21752/%2$5'

8

x

a

t

a

d

CS2

6

x

1

a

d

a

t

Ethernet

LAN9311

CS0

EMIFS EMIFF

TX

Control

PLL(TX)

SKY72310

TX DAC

TLV5614

GPIO

MCSI

CS2

SPI

M

c

B

2

P

S

X

T

McBSP2

McBSP3

3

P

S

B

c

M

32MB

Mobile SDRAM

79&'*%

6

1

x

a

t

a

d

07+0/)%

CS3

6

1

x

a

t

a

d

DSP

TMS320C55x

McBSP1

GPIO

McBSP1

IIS

Synchronous Timing

VSWR_Check

19.2MHz

19.2MHz

JTAG

TCXO

ADC

19.2MHz

TLV1548

32KHz

CS3

CLK

JTAG

uWire

TX OMAP5912

MCLK

PWM0/PWT

19.2MHz

19.2MHz

GPS BOARD

EXT BOARD

TX

GPS-LOCK

GPIO

UART3

UART1 US B

GPIO

MPU

ARM926EJ-S

GPIO

uWire

Program_ I/O

TX OMAP

Data Bus From

GPIO

MPUIO/

GPIO

Program_ I/O

USB

SW update

(DB9/DB26)

User program

RS-232

(CON5)

74HC594

EMIFS

74HC594

Connector

FAN1/FAN2

LCD

LED

FRONT PANEL

Key/knob

MMP10

MIC

27

Slot1/Slot2

CS0

SPI

RX Audio

Audio

preamp

RX FlatǃFiltered Audio/SlotAǃSlotB Audio

Mic

Audio Codec

TLV320AIC29

Filted/Flat Audio

preamp

DB26

TDA8547S

Speaker

1

P

S

B

c

M

GPIO

McBSP1

DSP

TMS320C55x

RX OMAP5912

CLK

JTAG

6

1

x

a

t

a

d

32MB

Mobile SDRAM

07+0/)%

32KHz

19.2MHz

32KHz

From 19.2MHz TCXO

JTAG

,7

MPU

ARM926EJ-S

UART1

RS232

(Con5)

ram

RD980 ᏺ⧚Ḛ

RD98X Block Diagram (Baseband Section)

RX Unit

CS1

RX DAC

TLV5614

R

X

M

P

c

S

2

SSI

AD9864

IF processor

SPI

SI

PLL(RX)

SKY72310

RX

Control

B

CS1

CS2

McBSP3

McBSP2

SPI

MCSI

GPIO

EMIFS EMIFF

6

1

x

a

t

CS3

a

d

79&'*%

6.4 Block Dia

Page 31

5VA

CODEC_AVDD(10mA)

3.3VA

RP102N331D

TCXO(2mA)

28

(300mA)

ADC TLV1548_AVDD(5mA)

DAC 5610/5604_AVDD10mA)

WTD

timer

OMAP Core_TX

CVDD1.2.3

CVDDRTC/CVDDDLL

(250mA)

OMAP Core_RX

CVDD1.2.3

CVDDRTC/CVDDDLL

OMAP DVDD (1.2.3.5.6.7.8.9)

DVddrtc(50mA*2)

OMAP Perpherial(10mA*2)

FLASH(50mA*2)

Indication LED(20mA*2)

DAC 5610/5604(5mA)

Shift/store register(5mA)

EthernetVDD33IO/VDD33A1/VDD33A2

CODEC_DigIO(5mA)

MAX3232(5mA)

CODEC Core(10mA)

CODEC_VREF(15mA)

SDRAM(85mA*2)

OMAPDVDD4(10mA*2)

EthernetVDD18CORE/VDDTX1/VD

OMAP TX/RX /MPU_RST

/PWRON_RST

DTX2/VDD18PLL

(250mA)

TX Board

Audio_PA

Accessory

Connectory(1A)

RD98X Block Diagram (Power Supply Section)

RD980ᏺ⬉⑤Ḛ

12.6V(1A)

2SB1184

B+

13.6V+/-15%

Vehicle Power In

Audio_OpAmP(20

mA)

Excite Board

Recive Board

(300mA)

XC6209E502PR

MAP Accessory

VBUS_SW

(500mA)

9V3A(700mA)

LM2941T(1A)

(5mA)

TPS5431(3A)

3V3D

1V8D

1V6D

/RESPWON

VDCDC2(1A)

VDCDC1(1.2A)

VDCDC3(0.9A)

PMU TPS65021

Controller

header(200mA)

Audio_PA(200mA

)

5V_GPS

GPS

TPS5431(3A)

connector(500mA

)

Page 32

1

1

KAA-3528RG

KAA-3528RG

KAA-3528RG

KAA-3528RG

150R9150

R9

43

ALARMD8ALARM

R11

R11

1

2

1

C7

3

Q5

470pC6470p

21

D10

D10

D9

21

43

KAA-3528RGD9KAA-3528RG

R13

R13

TP7TP7

1

150

150

3

Q6

2

DTC114EEQ5DTC114EE

1

C8

470pC7470p

TP8TP8

150

150

Q7

2

DTC114EEQ6DTC114EE

1

C9

470pC8470p

43

21

D12

D12

D11

D11

21

43

1

3

DTC114EEQ7DTC114EE

470pC9470p

KAA-3528RG

KAA-3528RG

DTC114EEQ8DTC114EE

Q8

2

1

C11

C11

RED

3

1

2

Q11

Q11

DTC114EE

DTC114EE

3

1

470p

470p

C12

C12

C141uC14

470p

470p

TP49TP49

R14 10KR14 10K

3V3D

R15 1KR15 1K

1

PWR_LED_CTRL

C131uC13

R17

R17

3

2

R16 1KR16 1K

5VD5VD

200R8200

R8

R7

200R7200

150R6150

R6

D8

12

5VD

D7

5VD

5VD

12

D5

RX-AD5RX-A

D6

R4

12

TX-BD6TX-B

R5

1

TP4TP4

150R4150

RX-BD7RX-B

TP6TP6

150

150

R10

R10

TP5TP5

1

150R5150

3

DTC114EEQ4DTC114EE

Q4

3

2

12

5VD

D4

TX-AD4TX-A

12

5VD

2

TP3TP3

D3

AnalogD3Analog

1

Q3

DTC114EEQ3DTC114EE

150R3150

R3

3

2

DTC114EEQ2DTC114EE

Q2

1

C1

1

2

C6

1

470pC2470p

C2

470pC1470p

12

5VD

TP2TP2

3

12

5VD

D1

RPDD1RPD

12

5VD

1

D2

DigitalD2Digital

180R2180

R2

3

TP1TP1

1

Q1

DTC114EEQ1DTC114EE

R1

150R1150

3

2

ࠡ䴶ᵓ⧚

RD980

5';6FKHPDWLF'LDJUDP)URQW3DQHO&LUFXLW

4

5

Repeater Disable_LED

3

Digital_LED

C49

C49

C48

C48

C47

C47

C46

C46

TX-A_LED

Analog _LED

U1

74AHCT594PW

U1

74AHCT594PW

0.1uF

0.1uF

D420

D420

1

MMBZ5V6ALT1G

MMBZ5V6ALT1G

2

100pF

100pF

100pF

100pF

100pF

100pF

1

15

QB

QA

QC2QD

RCLK12/RCLR13SER

14

LED_S/P_EN

PRST

LED_S/P_DAT

TX-B_LED

RX-A_LED

5

4

3

6

QF

QE

11

16

R41 10KR41 10K

3V3D

LED_S/P_CLK

QG

VCC

7

QH

GND8QH'9/SRCLR10SRCLK

RX-B_LED

C51

0.1uF

C51

0.1uF

C50

100pF

C50

100pF

ALARM_LED

6FKHPDWLF'LDJUDP

GRN

1u

1u

100K

100K

Q10

Q10

2

Q9

1

DTC114EE

DTC114EE

TP45TP45

1

2

D24

D24

1

5VD

1

DTC114EEQ9DTC114EE

3V3D

42

J2

MMBZ6V8ALT1G

MMBZ6V8ALT1G

3

C53

100pF

C53

100pF

BLM18PG300SN1

BLM18PG300SN1

L2

L2

1

TP47TP47

1

TP46TP46

1

TP17TP17

1

TP16TP16

1

TP15TP15

1

TP14TP14

1

TP13TP13

1

TP12TP12

1

TP11TP11

1

TP10TP10

1

TP9TP9

1

TP18TP18

1

TP19TP19

1

TP20TP20

R49

R49

R51

R51

R37

R37

R50

R50

1

TP24TP24

1

TP23TP23

1

TP22TP22

1

TP21TP21

X1A1X2A2X3A3X4A4X5A5X6

Y1C1Y2C2Y3C3Y4C4Y5C5Y6

U7 CM1440U7 CM1440

LED_S/P_CLK

5VD5VD 5VD

BACKLIGHT

GND2

S/P_CSLED

S/P_CLOCK25S/P_DATA26 WE_LCD

24

PRST

10K

10K

10K

10K

10K

10K

10K

10K

CM1440U6CM1440

A6

GND3

GND2

GND1

C6

LED_S/P_EN

LED_S/P_DAT

CH+

D15

D15

12

KPT-1608SGC

KPT-1608SGC

p1

12

D14

D14

KPT-1608SGC

KPT-1608SGC

P4

12

D13

D13

KPT-1608SGC

KPT-1608SGC

CS2_LCD29F_A1_LCD30F_D7_LCD31F_D6_LCD32F_D5_LCD33F_D4_LCD34F_D3_LCD35F_D2_LCD36F_D1_LCD37F_D0_LCD38 OE_LCD

28

27

X1A1X2A2X3A3X4A4X5A5X6

U6

Y1C1Y2C2Y3C3Y4C4Y5C5Y6

B3

B2

B1

J1

D18

D18

CH-

12

KPT-1608SGC

KPT-1608SGC

p2

12

D17

D17

KPT-1608SGC

KPT-1608SGC

p3

12

D16

D16

KPT-1608SGC

KPT-1608SGC

X1A1X2A2X3A3X4A4X5A5X6

Y1C1Y2C2Y3C3Y4C4Y5C5Y6

U5 CM1440U5 CM1440

A6

GND3

B3

GND2

B2

GND1

B1

C6

19

22

21

DB818DB9

DB1020DB11

DB1323DB1424DB1525DB1626DB17

DB112

17

R2456R24

56

R2656R26

56

R2356R23

56

ACC_ID3USB_VBUS4MMP_PRGM_IO4

KNOB_A10KNOB_B

VOL_GPIO113VOL_GPIO214KNOB_C

BACKLED_CTRL

PRST175VD40GND39KB_C018KB_C119KB_C220KB_R021KB_R122PWR_LED

11

15

16

MMP_PRGM_IO3

6

23

PWR_LED_CTRL

1

VOL_GPIO1

VOL_GPIO2

BACKLED_CTRL

1

1

A6

GND3

B3

GND2

B2

GND1

B1

1

C6

1

TP32TP32

TP31TP31

TP30TP30

1

1

1

R46 10KR46 10K

10K

10K

R36

R36

10K

10K

R35

R35

10K

10K

R34

R34

3V3D

C19

C19

C52

C52

C17

C17

R28 51R28 51

R27 51R27 51

R25 51R25 51

LED_A

LED_K132LED_K233LED_K3

Q13

Q13

2

U2

100p

100p

100p

100p

0.1uf

0.1uf

C18

100p

C18

100p

100p

100p

C30

C30

34

C34

C34

GND1VCI12VCI23IOVCC4FLM5CS6RS7 WR8 RD9DB010DB111DB212DB313DB414DB515DB616DB7

CSZLCM1830J1CSZLCM1830

C16

100p

C16

100p

C15

C15

0.1uf

0.1uf

BACKLED_CTRL

2SK1824

2SK1824

2

A4B

S2

S1

1

31

Q12

Q12

100p

100p

1

TP48TP48

R22 0R22 0

27

28

3V3D

30

IM329IM0

RESET

31

R43 10KR43 10K

31

3V3D

INT_MIC

MIC_GROUND

HANDSET_AUDIO

7

2

1

12

TP25TP25

TP26TP26

TP27TP27

100pf

100pf

C24

C24

TP28TP28

100pf

100pf

C28

C28

TP29TP29

100pf

100pf

C29

C29

C44

C44

C43

C43

R47 10KR47 10K

R48 10KR48 10K

5

KNOBU2KNOB

C

3

2

2SK1824

2SK1824

R39 33R39 33

BACKLED_CTRL

3V3D

U4

XC6209E332PR

U4

XC6209E332PR

5VD

GND1

41

con40J2con40

USB_D-

USB_D+8MMP_PRGM_IO0

5

9

S3P4S3

S2P3S2

S1

0.47uF

0.47uF

0.47uF

0.47uF

C42

0.47uF

C42

0.47uF

0

R290R29

10K

10K

R40

R40

3V3D

R30 0R30 0

C27

1uf

C27

1uf

1

5

Nc

Vout

Vin4Vss2CE

3

C26

1uF

C26

1uF

+

+

12

C25

C25

22uF/10V

22uF/10V

L1

L1

BLM18PG300SN1

BLM18PG300SN1

100pf

100pf

C22

C22

100pf

100pf

C23

C23

D22

MMBZ6V8ALT1G

D22

MMBZ6V8ALT1G

4

2

S2

S1

1

3

D21

D21

D20

D20

D19

D19

MMBZ5V6ALT1G

MMBZ5V6ALT1G

U8

U8

PRTR5V0U2X

PRTR5V0U2X

VOL_GPIO1

VOL_GPIO2

R45 10KR45 10K

R44 10KR44 10K

5

A4B

C

3

2

1

C39

C39

C36

100pf

C36

100pf

MMBZ20V

MMBZ20V

C35

C35

C38

C38

MMBZ5V6ALT1G

MMBZ5V6ALT1G

C37

C37

C32

C32

C31

C31

C45

100pf

C45

100pf

C33

C33

2 3

1

R310R31

NC

no use

C41

C41

0.47uF

0.47uF

C40

0.47uF

C40

0.47uF

E27U3E27

100pf

100pf

100pf

100pf

100pf

100pf

100pf

100pf

100pf

100pf

100pf

100pf

100pf

100pf

0

2

1

ACC_ID

GPIO3_PTT

J3

1

TP44TP44

1

TP43TP43

3

4

3

4

5

5

S6P1S6

P4

1

2

3

4

1

2

3

4

1

2

P1

1

2

3

4

5

5

S5P2S5

P3

P2

1

2

3

4

5

5

S4

CH-S4CH-

CH+S1CH+

1

2

5VD

R42

10K

R42

10K

100PF

100PF

C21

C21

10K

10K

R33

R33

10K

10K

3V3D

R32

R32

U3

100PF

100PF

C20

C20

BLM15AG121SN1

BLM15AG121SN1

L417

L417

1 2

7

3

6

5

4

USB_D-

INT_MIC

USB_VBUS

MIC_GROUND

HANDSET_AUDIO

1

1

1

1

1

1

1

1

1

1

2

1

BLM15AG121SN1

BLM15AG121SN1

L418

L418

CM2-2012MCIN-181T

CM2-2012MCIN-181T

L416

L416

3 4

8

10

9

USB_D+

GPIO4_HOOK

CON10_MMPJ3CON10_MMP

GPIO0_PWR ON

TP33TP33

TP34TP34

TP35TP35

TP36TP36

TP37TP37

2

TP38TP38

TP39TP39

TP40TP40

TP41TP41

TP42TP42

3

D23

MMBZ6V8ALT1G

D23

MMBZ6V8ALT1G

3

4

5

D D

C C

B B

A A

Page 33

TP813TP813

1

D810

D805

MMBZ6V8ALT1G

D805

MMBZ6V8ALT1G

5VD

C807NCC807

NC

1

TP806TP806

2

3

5'ᏺЏᵓ⧚˄⬉⑤⬉䏃˅

5';6FKHPDWLF'LDJUDP%DVHEDQGB3RZHU6XSSO\&LUFXLW

4

1

12

L803

L803

8

PH

VIN

U801

TPS5431DDA

U801

TPS5431DDA

7

L805

L805

+

+

C812

C812

12

C806

C806

+

C809

+

C809

12

R803

R803

+

C813

+

C813

15uH

15uH

C7121nC712

D801

D801

C803

C803

0.01uF

0.01uF

NC2NC

R801

R801

12

10uH

10uH

NC

NC

0.1uF

0.1uF

22uF/10V

22uF/10V

68K/F

68K/F

220uF/10V

220uF/10V

1n

B340A

B340A

1 2

1

BOOT

3

100K

100K

C808

0.01uF

C808

0.01uF

C805

1uF/25V

C805

1uF/25V

+

+

C804

C804

C862

1uF/25V

C862

1uF/25V

C863

0.01uF

C863

0.01uF

4

VSENSE

EN5GND

6

C802

C802

R802

R802

47uF/25V

47uF/25V

R806

R806

PowerPAD

9

1000pF

1000pF

22K

22K

22K/F

22K/F

3VRTC

5VD

3V3D

L801

L801

BLM18PG181SN1D

BLM18PG181SN1D

12

12

C817

2.2uF/10V

C817

2.2uF/10V

31

PWRFAIL

U803

U803

TPS65021RHA

TPS65021RHA

VCC37PWRFAIL_SNS

L825

L825

BLM18PG181SN1D

BLM18PG181SN1D

R81510R815

D810

C873

C873

C872

C872

+

+

C828

C828

+

+

16

21

LOWBAT

VINDCDC1

6

36

10

12

B802B802

D802

D802

+

+

12

C811

C811

C810

C810

1 2

MR2835SKG

MR2835SKG

330uF/35V

330uF/35V

470p/50V

470p/50V

L802

L802

BLM41PG600SN1

BLM41PG600SN1

5

1 2

L807

L807

B+

B801B801

J801

J801

13.6V

D803

D803

ZSH5MA27

ZSH5MA27

1

2

JK_PWR

JK_PWR

D D

MMBZ5V6ALT1G

MMBZ5V6ALT1G

1uF

1uF

0.01uF

0.01uF

C865

C865

68uF/6.3V

68uF/6.3V

22uF/10V

22uF/10V

L824 22uHL824 22uH

47K

47K

R819

R819

7

9

24

25

L1

VRTC

VDCDC1

DCDC2_EN

DCDC1_EN

VINDCDC3

VINDCDC2

LOWBAT_SNS

5

38

39

R840 100KR840 100K

R817

R817

C827

C827

+

+

12

C856

C856

+

+

12

C823

C823

+

+

12

C826

C826

TP801TP801

R816

R816

470K/F

470K/F

12

BLM41PG600SN1

BLM41PG600SN1

C C

TP814TP814

1

D811

D811

MMBZ5V6ALT1G

MMBZ5V6ALT1G

1V8D

C875

C875

C874

C874

L823

L823

BLM18PG181SN1D

BLM18PG181SN1D

C869

C869

+

+

12

C829

C829

+

+

12

L826 22uHL826 22uH

C857

C857

19

35

33

22

23

L2

VINLDO

VDCDC2

DCDC3_EN

HOT_RESET11DEFLDO112DEFLDO213VSYSIN14VBACKUP

TRESPWRON

26

C801 0.01uFC801 0.01uF

R846 100KR846 100K

R844

R844

100k

100k

100k

100k

R818

R818

100K

100K

1uF/25V

1uF/25V

10uF/10V

10uF/10V

10uF/10V

10uF/10V

10uF/10V

10uF/10V

VOL_DET

1uF

1uF

0.01uF

0.01uF

68uF/6.3V

68uF/6.3V

R842

R842

22uF/10V

22uF/10V

L821 6.2uHL821 6.2uH

1uF

1uF

18

20

VLDO2

VLDO1

LDO_EN

100K

100K

4

2

L3

VDCDC3

DEFDCDC1

10

PWR_RST

12

D807

D807

4.7K

4.7K

R821

R821

27

28

INT

RESPWON

DEFDCDC3

DEFDCDC2

1

32

1

D809

D809

UDZSTE(175.1B)

UDZSTE(175.1B)

1 2

R820

100K

R820

100K

C830

C830

1000P

1000P

I2C_SCL

I2C_SDA

MBRM120LT1G

MBRM120LT1G

R836 4.7KR836 4.7K

17

40

29

30

SCLK

SDAT

AGND1

PGND1

PGND2

3

8

15

34

R845

R845

13V6A

F803

F803

TP802TP802

Q802

Q802

L814

L814

TP815TP815

1

D812

D812

1V6D

C877

C877

C876

C876

L822

L822

BLM18PG181SN1D

BLM18PG181SN1D

+

+

12

+

+

12

C846

C846

41

PAD

AGND2

R8330R833

PGND3

10k

10k

C859

47uF/25V

C859

47uF/25V

+

+

12

LITTELFUSE0466002

LITTELFUSE0466002

C832

1000P

C832

1000P

1

2SB1184

2SB1184

3 2

R849

R849

12

BLM41PG600SN1

BLM41PG600SN1

MMBZ5V6ALT1G

MMBZ5V6ALT1G

1uF

1uF

0.01uF

0.01uF

C871

C871

68uF/6.3V

68uF/6.3V

R843

200K

R843

200K

22uF/10V

22uF/10V

0

31

Q803

Q803

2SK1824

2SK1824

R839 1KR839 1K

1

47K

47K

R841

R841

2

R850 1KR850 1K

PWR_ON

B B

120K

120K

9V3A

5VA

TP803TP803

U821

U821

L819

L819

12

D808

D808

MBRM120LT1G

MBRM120LT1G

R848 0R848 0

6

8

7

/RST

WDO

MR1VCC2GND3PFI

U805

U805

R814 0R814 0

R823 0R823 0

3V3D

TP805TP805

1

3V3A

L820

L820

BLM18PG181SN1D

BLM18PG181SN1D

5

VOUT

U806

U806

VDD1GND2CE

RP102N331B

RP102N331B

1

TP804TP804

BLM18PG181SN1D

BLM18PG181SN1D

VOUT

5

VIN

4

U807

U807

+

+

C836

10uF/16V

C836

10uF/16V

12

0.1u

0.1u

C835

C835

1

470P

470P

C834

C834

R829

4.32k/F

R829

4.32k/F

1

5

ADJ

OUT

GND

LM2941S

LM2941S

ON/OFF

IN

2

4

0.1u

0.1u

C837

C837

12

L816

L816

BLM41PG600SN1

BLM41PG600SN1

F802

F802

MINISMDC110F

MINISMDC110F

RST_CTRL

5

WDI

PFO

TPS3705-33DGN

TPS3705-33DGN

4

0.1u

0.1u

C878

C878

220p

220p

C840

C840

0.1u

0.1u

C839

C839

C838

2.2uF/10V

C838

2.2uF/10V

4

NC

3

C842

C842

2.2uF/10V

2.2uF/10V

0.1u

0.1u

C864

C864

+

+

12

C819

C819

22uF/10V

22uF/10V

XC6209F502PR

XC6209F502PR

R831

R831

3

NP(VREF)

GND

ON/OFF

681/F

681/F

1

2

3

R832

R832

C844

C844

C845

C845

47K

47K

TP807TP807

0.1u

0.1u

1000p

1000p

5V_GPS

U802

U802

12

1

12

C814

C814

12

L804

L804

15uH

15uH

D804

D804

C843

C843

8

PH

VIN

TPS5431DDA

TPS5431DDA

7

L813

L813

10uH

10uH

12

L815

L815

BLM41PG600SN1

BLM41PG600SN1

D806

D806

C822NCC822

+

+

C831

C831

C821

C821

+

C833

+

C833

R804

R804

+

+

C7001nC700

0.01uF

0.01uF

NC2NC

R808

R808

12

C861

C861

MMBZ6V8ALT1G

MMBZ6V8ALT1G

NC

NC

NC

0.1uF

0.1uF

22uF/10V

22uF/10V

68K/F

68K/F

220uF/10V

220uF/10V

1n

B340A

B340A

1 2

1

BOOT

EN5GND

3

100K

100K

C815

0.01uF

C815

0.01uF

C820

1uF/25V

C820

1uF/25V

+

+

C816

C816

47uF/25V

47uF/25V

C860

1uF/25V

C860

1uF/25V

0.01uF

0.01uF

A A

4

VSENSE

PowerPAD

6

9

C841

C841

R805

R805

R807

R807

1000pF

1000pF

22K

22K

22K/F

22K/F

1

2

3

4

5

Page 34

1

4

23

B+

1

3

D601

D601

L615

L615

BAV70

BAV70

1

1 2

BLM41PG600SN1

BLM41PG600SN1

2

2

MMP_PRGM_IO4

MIC_GROUND

MMP10_Mic_IN

MMP_ACC_IO1

V_BUS

R6240R624

3V3D

MMP_PRGM_IO3

USB0_D+

USB0_D-

470p

470p

2200UF

2200UF

+

+

1 2

C638

C638

C639

C639

0

10K

10K

R322

R322

J103

J103

MMP_PRGM_IO0

KNOB_A

KNOB_B

MMP10_SPK_AUDIO

VOL_GPIO2

VOL_GPIO1

D605

BAV70

D605

BAV70

3

C146

C146

R137 33R137 33

123

JK_FAN1

JK_FAN1

/RST-OUT_TX

KB_C1

KB_C0

KNOB_C

BACKLED_CTRL

KB_C2

32

47K

47K

R629

R629

2

1

100p

100p

Q605

Q605

3

R437 10KR437 10K

3V3D

R438 10KR438 10K

FAN_STOP_DET

LED_S/P_EN

DC_PWR_LED_CTRL

KB_R0

KB_R1

Q921

Q921

PZT2222AT1

PZT2222AT1

Q601

2SB1132

Q601

2SB1132

1

R627

R627

3

2

DTC114EE

DTC114EE

1

/OE_LCD

/WE_LCD

S/P_CLK

S/P_DAT

BLM18PG300SN1

BLM18PG300SN1

33R

33R

2

FAN1

CS2_LCD

F_A1_LCD

DTC114EE

Q603

DTC114EE

Q603

1

1.5K

1.5K

R628

R628

F_D7_LCD

F_D6_LCD

F_D5_LCD

R811NCR811

F_D4_LCD

F_D3_LCD

F_D2_LCD

NC

F_D1_LCD

F_D0_LCD

D608D608

2

1

5VD

4

5V_GPS

C649

C649

C650

C650

D604

D604

PRTR5V0U2X

PRTR5V0U2X

100p

100p

100p

100p

4 3

5

6

TP219TP219

TP218TP218

TP217TP217

1

2 3

J601

J601

12345

678

1

1

1

0

0

R6520R652

R6510R651

TX_PLL_CS2_DB9

TX_PLL_CLK_DB9

0

NC

R6180R618

R617NCR617

V_BUS

USB0_D-

9

0

R6530R653

TX_PLL_Data_DB9

2

S601S601

1

S602S602

1

0

NC

R6470R647

R619 0R619 0

R649NCR649

USB0_D+

BOOT_DOUT_TX

BOOT_DOUT_RX

2

JK_DB9

JK_DB9

C648

100p

C648

100p

C611

1000p

C611

1000p

C610

100p

C610

100p

C609

100p

C609

100p

C646

100p

C646

100p

C647

100p

C647

100p

D607

D607

MMBZ20V

MMBZ20V

3

3

NC

0

R650NCR650

R6480R648

BOOT_DIN_TX

BOOT_DIN_RX

1

2

10K

10K

R632

R632

3

5';6FKHPDWLF'LDJUDP%DVHEDQGB,QWHUIDFH&LUFXLW

5'ᏺЏᵓ⧚˄ষ⬉䏃˅

4

3V3D

R633

R633

R601NCR601

10K

10K

C608

C608

C607

C607

C606

C606

C605

C605

C604

C604

C603

C603

C602

C602

C601

C601

L611 BLM18PG300SN1L611 BLM18PG300SN1

L612 BLM18PG300SN1L612 BLM18PG300SN1

L613 BLM18PG300SN1L613 BLM18PG300SN1

L610 BLM18PG300SN1L610 BLM18PG300SN1

L609 BLM18PG300SN1L609 BLM18PG300SN1

R610 0R610 0

C636 100pC636 100p

C635 100pC635 100p

C634 100pC634 100p

C633 100pC633 100p

C632 100pC632 100p

C631 100pC631 100p

C630 100pC630 100p

C629 100pC629 100p

C628 100pC628 100p

C627 100pC627 100p

C626 100pC626 100p

C625 100pC625 100p

C624 100pC624 100p

C623 100pC623 100p

C622 100pC622 100p

C621 100pC621 100p

C620 100pC620 100p

C619 100pC619 100p

C618 100pC618 100p

C617 100pC617 100p

C616 100pC616 100p

C615 100pC615 100p

C614 100pC614 100p

C613 100pC613 100p

C612 100pC612 100p

3V3D

U601

U601

J603

J603

6

1

R620 4.7KR620 4.7K

1

5

2

2

DC_PWR_DET

DC_PWR_DET

DC_PWR_DET

DC_PWR_LED_CTRL

R622 1KR622 1K

R623 0R623 0

TIL113

TIL113

3 4

R6211KR621

1K

L607 BLM18PG300SN1L607 BLM18PG300SN1

L608 BLM18PG300SN1L608 BLM18PG300SN1

L606 BLM18PG300SN1L606 BLM18PG300SN1

L604 BLM18PG300SN1L604 BLM18PG300SN1

L602

L602

L605 BLM18PG300SN1L605 BLM18PG300SN1

L603 BLM18PG300SN1L603 BLM18PG300SN1

R604 0R604 0

R602 0R602 0

R603 0R603 0

R605 NCR605 NC

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

R608 33R608 33

R609 33R609 33

R606 33R606 33

R607 33R607 33

NC

R616 33R616 33

R615 33R615 33

R614 33R614 33

R612 33R612 33

R611 33R611 33

R613 33R613 33

3

4

6

5

1

2

43

5

D603D603

6

5

1

2

5

43

123456789101112131415161718192021222324252627282930313233343536373839

J602

J602

D D

C C

D602D602

40

HEAD

HEAD

B B

A A

Page 35

10K

10K

34

R730

R730

R724

10K

R724

10K

25

1

1

R725

R725

R723

R723

10K

10K

10K

10K

34

25

1

R2

R2

R1

R1

R1

R1

R2

R2

R1

R1

R2

R2

6

R2

R2

R1

R1

6

C710

C710

Q710

Q710

MUN5214DW1T1

MUN5214DW1T1

C711

C711

Q709

Q709

MUN5214DW1T1

MUN5214DW1T1

220p

220p

220p

220p

D707

D707

MMBZ20V

MMBZ20V

1

5VD 5VD 5VD

R722

10K

R722

10K

34

R2

5VD 5VD 5VD

R719

R719

10K

10K

25

1

R2

R1

R1

R1

R1

Q707

R2

R2

6

Q707

MUN5214DW1T1

MUN5214DW1T1

5VD

R718

10K

R718

10K

1

R2

R2

R1

2

25

34

R716

10K

R716

10K

5VD

R1

R1

R1

R2

R2

6

Q708

Q708

MUN5214DW1T1

MUN5214DW1T1

R796

R796

R795

R795

470

470

33K

33K

34

R2

5VD

R715

R715

10K

10K

25

1

R2

R1

R1

R1

R1

R2

R2

6

Q706

Q706

MUN5214DW1T1

MUN5214DW1T1

5VD5VD5VD

470

R711

R711

10K

10K

1

R2

R2

R1

25

34

10K

10K

R710

3

R710

1

25

R714

R714

R713

R713

R717

R717

10K

10K

10K

10K

3.9K

3.9K

34

1

25

34

34

25

1

R731

R731

10K

10K

R732

R732

10K

10K

R708

R708

10K

10K

R709

R709

10K

10K

R706

R706

10K

3V3D

R705

R705

R704

R704

R703

R703

R702

R702

10K

10K

10K

10K

10K

10K

10K

10K

10K

5VD

5VD

5'ᏺЏᵓ⧚˄'%ষ⬉䏃˅

5';6FKHPDWLF'LDJUDP%DVHEDQGB'%,QWHUIDFH&LUFXLW

4

R1

R1

R1

R2

R2

R2

R2

R1

R1

R1

R1

R2

R2

R2

R2

R1

R1

R1

R1

R2

R2

R2

R2

R1

R1

R1

R1

R2

R2

6

Q705

Q705

6

Q704

Q704

6

Q703

Q703

R798 3.9KR798 3.9K

6

470

R794

R794

33K

33K

R793

R793

470

470

R792

R792

33K

33K

R791

R791

R790

470

R790

470

33K

33K

R789

R789

MUN5214DW1T1

MUN5214DW1T1

Q702

Q702

MUN5214DW1T1

MUN5214DW1T1

C709

C709

C708

C708

C707

C707

C706

C706

D704

D704

C705

C705

MUN5214DW1T1

MUN5214DW1T1

C704

220p

C704

220p

MUN5214DW1T1

MUN5214DW1T1

D703

D703

C703

C703

C702

C702

220p

220p

220p

220p

220p

220p

220p

220p

220p

220p

MMBZ20V

MMBZ20V

220p

220p

DB26_PTT_IN

V_BUS

0.1uF

0.1uF

D706

D706

MMBZ20V

MMBZ20V

D705

D705

MMBZ20V

MMBZ20V

MMBZ20V

MMBZ20V

D710

D710

SQ2

NC

R788NCR788

MMBZ20V

MMBZ20V

SQ1

NC

R769NCR769

DB26_GPIO4_CH1

13V6A

NC

33

R753NCR753

R734 0RR734 0R

R73333R733

R735 33R735 33

DB26_Ext_Mic_IN

RX_AUDIO_FLAT

SLOT SYNC FUNCTION

USB0_D+

MIC_GND_DB26

DB26_ACC_IO2_CH2

DB26_GPIO2_PA_ALARM

33

33

R74033R740

R737 0R737 0

R739 33R739 33

R738 0R738 0

R75433R754

Pf_DET

Pf_DET_DA

DB26_GPIO3_CH3

DB26_GPIO5_CH4

NC

33R

33R

R736

R736

R755NCR755

USB0_D-

DB26_ACC_IO3_CH1

DB26_EMERGENCY_IN

33

33

33

R744 33R744 33

R745 33R745 33

R747 33R747 33

R746 33R746 33

R74333R743

R74233R742

R74133R741

SlotA_Audio

RSSI

SlotB_Audio

DB26_GPIO6_CH5

D709

D709

C7531nC753

D708

D708

R750 33R750 33

R748 33R748 33

R751 33R751 33

R749 33R749 33

2 3

MMBZ6V8ALT1G

MMBZ6V8ALT1G

1n

5VD

PRTR5V0U2X

PRTR5V0U2X

R752 0R752 0

4

1

2

3

FLAT_TX_AUDIO

RX_FLITER_AUDIO

R778 NCR778 NC

R777 33R777 33

4

ACC_IO2

ACC_IO3

PRGM_IN5

5

D D

C725

C725

C726

C726

C727

C727

PRGM_IN3

PRGM_IN2

PRGM_IN4

EMERGENCY

EXT_ALARM_IN

RX_AUDIO_MUTE

1

15

QA

74HC595DTR2G

74HC595DTR2G

U701

U701

LATCH CLK12OUT EN13A

100p

100p

100p

100p

100p

100p

S/P_EN

EXT_PTT

Slot2_EN

Slot1_EN

TP701TP701

1

3

QB

QC2QD

SHIFT CLK

11

14

S/P_CLK

S/P_DAT

PRGM_OUT4

PRGM_OUT3

PRGM_OUT2

PRGM_OUT5

4

5

6

7

QF

QE

QH

QG

GND

SQH9RESET

VCC

8

10

16

10K

10K

R720

R720

C701

C701

3V3D

0.1u

0.1u

3V3D

R712

R712

3V3D

10K

10K

1

U702

AAT4618IGV

U702

AAT4618IGV

5

5VD

R721

R721

OUT

IN

10K

10K

3

FAULT

GND

ON

4

VBUS0_EN

C C

C754NCC754

NC

C752

C752

100p

D702

D702

MMBZ6V8ALT1G

MMBZ6V8ALT1G

2

C751

C751

C750

C750

C748

C748

C747

C747

C746

C746

C755

C755

R7560R756

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

100p

0

12345678910111213141516171819202122232425

D711

D711

J701

J701

MMBZ5V6ALT1G

MMBZ5V6ALT1G

100p

100p

C745

C745

C744

C744

100p

100p

C743

100p

C743

100p

100p

100p

C742

C742

100p

100p

C741

C741

NC

C740NCC740

C739

C739

100P

100P

100p

100p

C738

C738

C737

100P

C737

100P

C736

C736

100p

100p

C735

C735

100P

100P

100p

100p

C734

C734

26

DB26

DB26

5

V_BUS

VBUS0_DEC

B B

A A

Page 36

MMP10_SPK_AUDIO

MMBZ20V

MMBZ20V

SPKR-

1

TP502TP502

5V_GPS

1 2

C510 10uF/16V+C510 10uF/16V

34

+

AUDIO_PA_EN

1

2

TP505TP505

C523 22uFC523 22uF

RX_AUDIO_FLAT

1

SPKR+

D505

1

TP501TP501

D505

1

Slot1 active high

Slot1_EN

RX_FLITER_AUDIO_SPK

RX Audio active high

RX_AUDIO_MUTE

SlotA_Audio

SlotB_Audio

Slot2_EN

1

C529 100pFC529 100pF

C534 22uFC534 22uF

TP507TP507

1

C555

0.1u

C555

0.1u

560R

560R

C536

C536

100P

100P

R810

R810

1

47K

47K

U504A

NJM2902V

U504A

NJM2902V

4 11

+

-

+

-

R544

R544

2

C563 22uFC563 22uF

R677 0R677 0

C533 22uFC533 22uF

9d3V

3

R549

27K

R549

27K

0R

R5800RR580

C693

1000P

C693

1000P

R594

R594

R3067NCR3067

VAG

3

1 2

NC

100K

100K

150K

150K

R564

R564

C549 10uFC549 10uF

TP508TP508

1

D504

D504

560R

560R

R696

R696

7

U504B

NJM2902V

U504B

NJM2902V

30K

30K

4 11

+

-

+

-

R570

C547 33pC547 33p

5

6

R570

R5690RR569

0R

VAG 9d3V

MMBZ20V

MMBZ20V

C552 330PC552 330P

TP509TP509

-

-

C554 10uFC554 10uF

1

8

U504C

NJM2902V

U504C

NJM2902V

4 11

+

+

9d3VVAG

9

10

R5740RR574

0R

2

5

NC

UMC4N

Q505

Q505

R676NCR676

-

-

R542 150KR542 150K

13

NC

R541NCR541

C532 22uFC532 22uF

TP511TP511

1

UMC4N

1

2

3 4

0

C551

100P

C551

100P

R6750R675

14

C535

C535

0.1U

0.1U

U503D

NJM2902V

U503D

NJM2902V

4 11

+

+

9d3V

R584 0R584 0

12

R547 30KR547 30K

C692

C692

1000pF

1000pF

0

R5790R579

3V3A

R561 1KR561 1K

VAG

3

R583

R583

10K

10K

R567 10KR567 10K

C695NCC695

NC

C548 10uFC548 10uF

0

R5660R566

TP512TP512

1

R5631K R5631K

Q506

Q506

2

DTC114EE

DTC114EE

1

R562

R562

R568

100K

R568

47K

47K

100K

5

1u

C5461uC546

Q501

Q501

1u

C5451uC545

UMC4N

UMC4N

1

2

3 4

TP513TP513

Q508

Q508

R571 10KR571 10K

C694

1000pF

C694

1000pF

C553 10uFC553 10uF

R572 0R572 0

1

3

R573

100K

R573

100K

5

UMC4N

UMC4N

1

2

3 4

Q502

GND2

GND1

VCC2

VCC1

OUT1+

OUT1-

OUT2+

OUT2-

U502

U502

R503

R503

C713

C713

TDA8547TS

TDA8547TS

270K

270K

330pF

330pF

9d3V

U503A

U503A

Q502

NC

NC

NC

9

NC

7

NC

2

SELECT

6

MODE

4

SVRR

5

IN1+

IN1IN2+

IN2-

VAG

R504

R504

NJM2902V

NJM2902V

-

-

2

9d3V

L502 BLM41PG600SN1L502 BLM41PG600SN1

2

3

L503 BLM41PG600SN1L503 BLM41PG600SN1

R585NCR585

NC

C561NCC561

NC

10

1

11

20

3

18

8

13

C502

C502

0.1uF

0.1uF

+

+

C503

22uF/10V

C503

22uF/10V

12

L507

BLM18PG181SN1D

L507

BLM18PG181SN1D

5V_GPS

12

C505

C505

L501

BLM18PG181SN1D

L501

BLM18PG181SN1D

C504

9V3A

C504

C556

C556

12

5'ᏺЏᵓ⧚˄&2'(&ঞ䷇乥ᬒ⬉䏃˅

R586 1KR586 1K

19

12

16

17

15

14

1

+

+

3

47K

47K

R505

R505

C507

C507

C506

C506

0.1u

0.1u

0.1u

0.1u

+

+

R513

R513

R575 NCR575 NC

C6911UC691

C690

C690

+

+

12

2.2K

2.2K

C508

C508

+

+

12

R506

R506

0.01u

0.01u

10uF/16V

10uF/16V

+

+

10uF/16V

10uF/16V

4.7K

4.7K

12

+

+

C509

C509

1U

10uF/16V

10uF/16V

4 11

10uF/16V

10uF/16V

47K

47K

5

47uF/16V

47uF/16V

R514

R514

R515

R515

9d3V

UMC4N

UMC4N

10K

10K

10K

10K

C514

C514

C513

C513

R5200R520

UMC4N

UMC4N

Q503

Q503

D501

MMBZ20V

D501

MMBZ20V

8

39K

39K

U503C

NJM2902V

U503C

NJM2902V

4 11

+

-

+

-

1

3 4

C522 22uFC522 22uF

TP504TP504

9d3V

9

10

R533

R533

10K

10K

0R

R5370RR537

VAG

C528 330pFC528 330pF

100K

100K

R535

R535

5

1

2

C519 100pFC519 100pF

R530

R530

NC

R529NCR529

1uF

1uF

1

TP503TP503

1uF

1uF

R528NCR528

NC

NC

C520NCC520

R5230RR523

0R

1u