Page 1

SERVICE MANUAL

DMR PORTABLE RADIO

数 字 手 持 对 讲 机

Page 2

Service Manual

Preface

This manual describes information related with prod uct repair. To repair the product properly, please

read this manual careful ly.

This manual is applica ble to the following model:

PD70X (X may indicate 2, 5, 6 or 8)

PD70XG (X may indicate 2, 5, 6 or 8)

PD78X (X may indicate 2, 5, 6 or 8)

PD78XG (X may indicate 2, 5, 6 or 8)

HD705

HD705G

HD785

HD785G

In this manual, the description related to the LCD is applicable to PD78X/ PD78XG/ HD785/ HD785G

only, while the description related to GPS is applicable t o PD70XG/ PD78XG/ HD705G / HD785G only.

Page 3

Service Manual

Contents

1. Revision History ................................................................................................................................... 1

2. Copyright Information.......................................................................................................................... 2

3. Disclaimer ............................................................................................................................................. 3

4. Introduction........................................................................................................................................... 4

5. Product Controls .................................................................................................................................. 5

6. Baseband Section ................................................................................................................................ 7

6.1 Power Section...............................................................................................................................7

6.2 Control Section.............................................................................................................................. 8

6.3 Audio Section..............................................................................................................................14

6.4 Troubleshoot ing Flow C

6.5 PCB Difference ...........................................................................................................................17

7. GPS Circuit.......................................................................................................................................... 18

7.1 Circuit Description.......................................................................................................................18

7.2 Schematic Diagram.....................................................................................................................19

7.3 Parts List .....................................................................................................................................20

7.4 Troubleshoot ing Flow C

8. Tuning Description ............................................................................................................................. 22

9. Interface Definition............................................................................................................................. 23

10. UHF1 (400-470MHz) Information

0.1 Transmitter Circuit..................................................................................................................... 27

1

10.2 Receiver Circuit.........................................................................................................................28

10.3 Frequency Generati

hart........................................................................................................16

hart........................................................................................................21

..................................................................................................... 27

o

n Unit (FGU)............................................................................................30

10.4 PCB View..................................................................................................................................32

10.5 Block Diagram........................................................................................................................... 40

10.6 Schematic Diagram...................................................................................................................43

10.7 Parts List ................................................................................................................................... 59

10.8 Troubleshooting Flow Chart...................................................................................................... 84

11. UHF2 (450-520MHz) Information ..................................................................................................... 90

1 1.1 Transmitter Circuit.....................................................................................................................90

i

Page 4

Service Manual

11.2 Receiver Circuit.........................................................................................................................91

11.3 Frequency Generation U

nit (FGU)............................................................................................93

11.4 PCB View .................................................................................................................................. 95

11.5 Block Diagram.........................................................................................................................103

11.6 Schematic Diagram................................................................................................................. 106

11.7 Parts List..................................................................................................................................122

1 1.8 T roubles hooting Fl

ow Chart....................................................................................................147

12. UHF3 (350-400MHz) Information................................................................................................... 154

1

2.1 Transmitter Circuit................................................................................................................... 154

12.2 Receiver Circuit.......................................................................................................................155

o

12.3 Frequency Generati

n Unit (FGU)..........................................................................................157

12.4 PCB View................................................................................................................................159

12.5 Block Diagram.........................................................................................................................167

12.6 Schematic Diagram.................................................................................................................170

12.7 Parts List ................................................................................................................................. 186

12.8 Troubleshooting Flow Chart....................................................................................................212

13. VHF (136-174MHz) Information ..................................................................................................... 218

13.1 Transmitter Circuit................................................................................................................... 218

13.2 Receiver Circuit.......................................................................................................................219

o

13.3 Frequency Generati

n Unit (FGU)..........................................................................................221

13.4 PCB View................................................................................................................................223

13.5 Block Diagram.........................................................................................................................231

13.6 Schematic Diagram.................................................................................................................234

13.7 Parts List ................................................................................................................................. 250

13.8 Troubleshooting Flow Chart....................................................................................................277

14. Disassembly and As

sembly.......................................................................................................... 283

15. Exploded View ................................................................................................................................ 285

16. Packing Guide ................................................................................................................................ 289

17. Specifications ................................................................................................................................. 290

18. Appendix ......................................................................................................................................... 292

ii

Page 5

Service Manual

1. Revision History

Version Date Description

R2.0 09-2010 Initial Release

dd descriptions on VHF, UHF2 and UHF3; update the battery

R3.5 05-2011

A

life.

1

Page 6

Service Manual

2. Copyright Information

Hytera is the trademark or registered trademark of Hytera Communications Co., Lt d. (t he Company) in

PRC and/or other countries or areas. The Company re tains the ownership of its trademarks and pro duct

names. A ll ot her trademarks and/or product na mes that may be used in this manual are properties of

their respective owners.

The product described in this ma nual may include the Company’s computer programs stored in memory

or other media. Laws in P RC an d/or ot her c ountr ies or areas protect the exclu siv e right s o f the Com pany

with respect to its comput er programs. The purchase of t hi s product shall not be deemed to grant , eit her

directly or by implication, any rights to the purchaser regarding the Company ’s computer programs. Any

of the Company’s computer programs may not be copi ed, modified, distributed, deco mpiled, or

reverse-engineered in any manner without the prior written consent of the Company.

TM

The AMBE+2

voice coding technology embod ied in this product is protect ed by intellectual propert y

rights including patent rights, copyrights and trade secrets of Digital Voice Systems, Inc. This voice

coding technology is licensed solely for use within this product. The user of this technology is explicitly

prohibited from attempting t o decompile, reverse engineer, or disassemble the Object Code or in any

other way convert the Object Code into a human readable form.

U.S. Patent Nos. #6,912, 495 B2, #6,199,037 B1, #5,870,405, #5,826,222, #5, 754,974, #5,701,390,

#5,715,365, #5,649,050, #5,630,011, #5,581,656, #5,517,511, #5,491,772, #5,247,579, #5,226,084 an d

#5,195,166.

2

Page 7

Service Manual

3. Disclaimer

The Company endeav ors to achieve the accuracy and comp let eness of this manual, but no warranty of

accuracy or reliability is gi ven. All the specificat ions and designs are subject to change without notice

due to continuous techno l ogy development. No p art of t his manual may be copied, mo dified, translated,

or distributed in any manner w ithout t he express written permissi on of us.

If you have any suggestions or would like to learn more details, please visit our website at:

http://www.hytera.com

.

3

Page 8

Service Manual

4. Introduction

Intended User

This manual is intended f or use by qualified technicians only.

4

Page 9

Service Manual

5. Product Controls

PD70X/ PD70XG/ HD705/ HD705G

No. Part Name No. Part Name

SK1 (Side Key 1)

1

○

PTT Key

2

○

SK2 (Side Key 2)

3

○

TK (Top Key)

4

○

Channel Selector kno b

5

○

Speaker

6

○

LED Indicator

7

○

○

○

10

○

11

○

12

○

13

○

14

○

Radio On-Off/V olume Control Knob

8

Microphone

9

Accessory Jack

Battery Latch

Antenna

Belt Clip

Battery

5

Page 10

Service Manual

PD78X/ PD78XG/ HD785/ HD785G

No. Part Name No. Part Name

1

○

2

○

3

○

4

○

5

○

6

○

7

○

8

○

SK1 (Side Key 1)

PTT Key

SK2 (Side Key 2)

TK (Top Key)

Channel Selector kno b

Microphone

LCD Display

OK/Menu Key

LED Indicator

11

○

Antenna

12

○

Radio On-Off/V olume Control Knob

13

○

Accessory Jack

14

○

Exit Key

15

○

Up Key

16

○

Down Key

17

○

Battery Latch

18

○

Speaker

9

○

Numeric Keypad

10

○

19

○

20

○

6

Belt Clip

Battery

Page 11

Service Manual

6. Baseband Section

6.1 Power Section

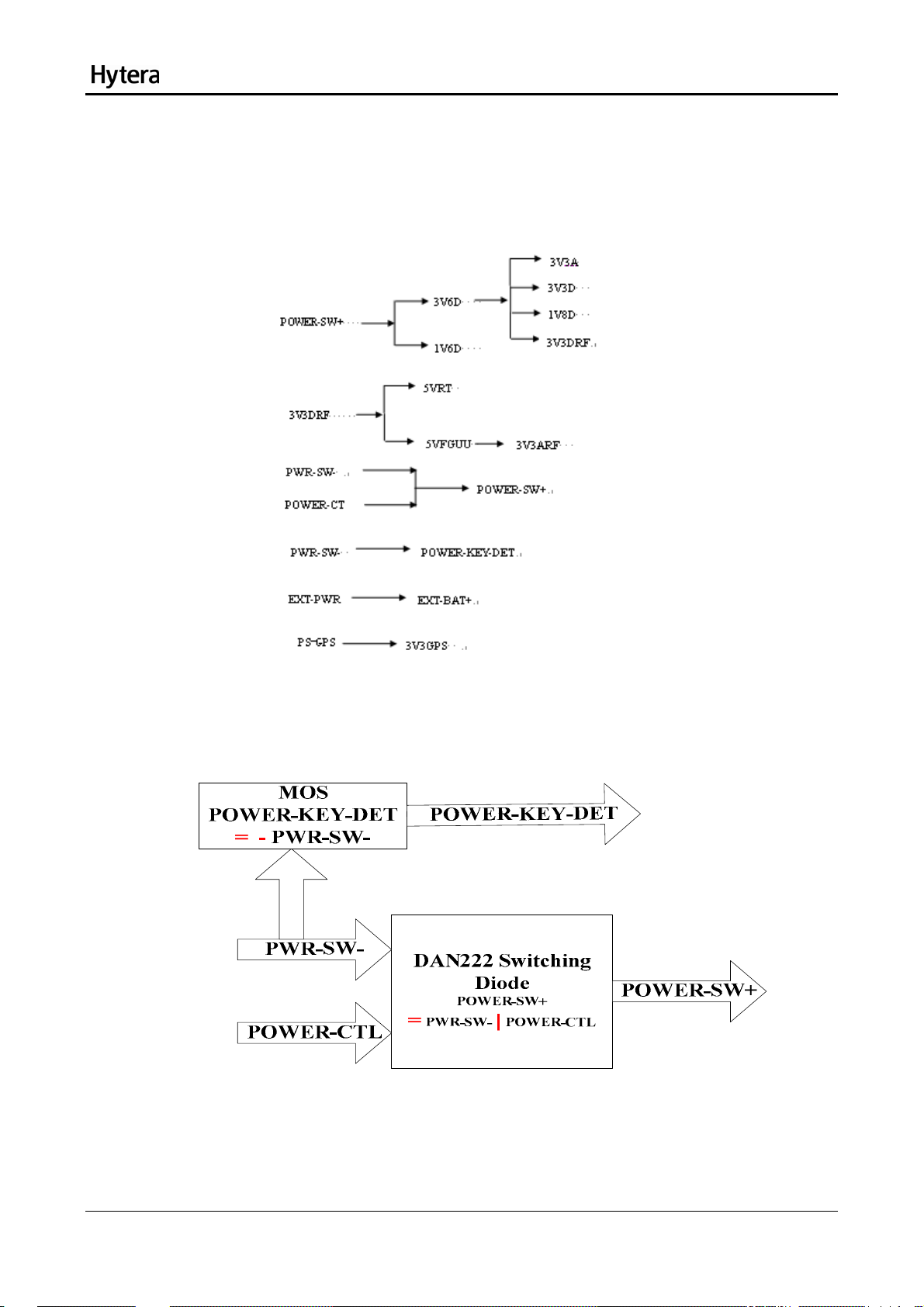

6.1.1 Diagram of Power Control

6.1.2 Radio On/Off

Figure 6-1 Diagram of Pow er Cont rol

Figure 6-2 Diagram of Radio O n/ Off Control

The radio-on signal (POWER-SW+) satisfies the equation: POWER-SW+= PWR-SW- | POWER-CTL.

When the V ol u me Swit ch is on, P WR-S W- an d POWER-SW+ are at high lev el, and the radi o powers u p.

7

Page 12

Service Manual

After power-on, POWER-CTL goes to high level, and POWER-KEY-DET goes to low level. During

power-off, POWER-SW+ is a t low level, while POWER-KEY-DET is at high level. The system detects

power-off procedure via POWER-KEY-DET and implements the power-off procedure. Then

POWER-KEY-DET and PO WER-SW+ go to low level, and the p o w er is cut off.

6.1.3 Power Protection

Power protection includes over-current, reverse-voltage and E SD protection.

6.1.4 Power Consumption Control

OMAP can control and configure the power supply and working mode of the peripheral modules (RF

section and baseband section) via I/O interface and serial bus, so as to reduce power consumption.

6.2 Control Section

6.2.1 OMAP5912 Dual-core Processor

The radio uses the dual-core processor OMAP5912, which is mainly composed of ARM926EJ-S and

TMS320C55xx. ARM926EJ-S is the main controller, while TMS320C55xx is used for

modulation/demodulation and voice encoding/ decoding.

Figure 6-3 Diagram of OM AP 5912

8

Page 13

Service Manual

Figure 6-4 Diagram of Overall Scheme

6.2.2 External Memory

OMAP5912 provides two types of external memory interfaces: external memory interface slow (EMIFS)

and external memory interfac e fa st (EMI FF).

MT48H8 M 16LFB 4-75

A[0:12]

D[0:15]

BA0

BA1

CAS#

RAS#

CKE

CLK

CS#

WE#

LDQM

ULQM

EMIFF EMIFS

SDRAM .A[0:12]

SDRAM .D[0:15] FLASH .A[15:0]

SDRAM.BA 0

SDRAM.BA 1

SDRAM.CAS#

SDRAM.RA S #

SDRAM.CKE#

SDRAM.CLK#

SDRAM.CS#

SDRAM .W E#

SDRAM.DQML

SDRAM.DQMU

Figure 6-5 Diagram of External Memory

OMA P5912

FLASH.A[24:1]

FLASH.OE#

FLASH.WE#

FLASH.CS3#

RST_OUT#

FLASH.WP#

FLASH.RDY

TV00570002C DG B

A[23:0]

DQ[15:0]

OE#

WE#

Cef#

RESET#

WP#/ACC

RY/Byf#

1) EMIFS

EMIFS is a 16-bit interface, and provides four 64MB chip selects (CS0~CS3). The interface supports

9

Page 14

Service Manual

memories such as NAND Flash, NOR Flash and SRAM.

2) EMIFF

EMIFF is a 16-bit interfa ce, and supports SDR AM (up to 128MB), mobile SDRAM and mobile DDR.

6.2.3 Clock

Option board

CLK-32K-OUT

32kHz

CLK-OPT

19.2MHz

1 2

32.768KHz

20pF 20pF

X20 3

1

VCC

VCONT

2 3

OUT

GND

TCXO 19 . 2MHz

X201

VCC

4

CLK_32K_OUT

OSC32K_OUT

OSC32K_IN

ULPD

VSS(Y13)

OSC1_OUT

OSC1_IN

MCLK

19.2MHz

MCLK

U821

TLV320AIC29

BCLK

ULPD_PLL_CLK

19.2MHz

CK_REF

OMAP5912

APLL

OMAP3.2

DPLL1

U201

96MHz

CLK32K_IN

ARM_CK

DSP_CK

TC_CK

Figure 6-6 Diagram of Baseband Clock

Input Clock:

(A) 32K Clock: It is also c alled “sleep clock” and is ma inly used for timing and sleeping of the system.

(B) 19.2MHz Clock: I t is mainly used to provide inp ut clock for APLL and DPLL.

Output Clock:

Three output clocks are provided: MCLK, BCLK and CLK32K_OUT. MCLK provides 19.2MHz clock to

the audio codec; BCL K provides 19.2MHz clock to the option boar d; and CLK32K_OUT provides 32KHz

clock to the option board.

6.2.4 Reset Signal

Figure 6-7 Diagram of Reset Signal

10

Page 15

Service Manual

6.2.5 SPI

OMAP5912 has a SPI, which has four chip-selects for connecting four external SPI components. The

SPI signals available are SPI.DOUT, SPI.DIN, SPI.CLK and SPI.CS. The system uses SPIF.CS2 to

select the IF processor AD9864, to configure register of AD9864. The connection of SPI is show n below.

PE

AD9864 PC

D9864 PC

PD

DOUTB

PEA

PD

DOUTB

SPIF.CS2(T19)

SPIF.SCK(U19)

SPIF.DOUT(W21)

SPIF.DIN(U18)

U201

OMAP5912

Figure 6-8 Diagram of SPI Connection

6.2.6 MCBSP

OMAP5912 provides 3 MCBSP interfaces: MCBSP1, MCBSP2 and MCBSP3. MCBSP1 is connected

with the I2S interface of the audio codec, to realize two-way transmission of digital voice and data.

MCBSP2 uses independent clock and frame synchronization for transmission and reception. AD9864

SSI is connected to the RX end of OMAP5912 MCBSP2. AD9864 works in master mode, while DSP

works in slave mode. DAC is connected with the TX end of MCBSP2, and DSP works in master mode.

MCBSP3 is connected to t he opt i on board. The connect ion of MCBSP is shown below.

11

Page 16

Service Manual

Figure 6-9 Diagram of MCBSP Connect ion

6.2.7 USB

OMAP5912 provides 3 USB interfaces. One interface integrates a USB transceiver, which is connected

to the accessory jack and is used for program downloading and data application.

Figure 6-10 Diagram of USB Int erface

6.2.8 UART

OMAP5912 has three UART interfaces (UART1, UART2 and UART3), and supports hardware flow

control. The maximum communication rate is 1.5Mb ps. The conn ection of UAR T is shown below. UART1

is connected with the accessory jack, and is used for updating and programming. UART2 is for GPS,

and UART3 is for the opti on board.

Figure 6-11 Diagram of UART Interface Connect ion

12

Page 17

Service Manual

6.2.9 I2C

OMAP5912 provides one I2C interface, and supports communication rate up to 400Kbps. The I2C

interface is connected with the acceleration sensor, and works in slave mode. The connection of I2C is

shown below.

Figure 6-12 Diagram of I2C Connection

6.2.10 MICROWIRE

OMAP5912 provides a MICROWIRE. The four chip select signals can drive four external components.

MICROWIRE is used to configure the audio codec and read the value of its register. It uses the chip

select signal 3. The connection is shown below.

Figure 6-13 Diagram of MICROWIRE Connection

6.2.11 MCSI1

OMAP5912 has two MCSI interfaces. MCSI1 is used for PLL configuration and data transmission. The

connection of MCSI1 is shown below.

Figure 6-14 Diagram of SPI Con nection

13

Page 18

Service Manual

6.3 Audio Section

6.3.1 Audio Diagram

The audio module is mainly for audio input and output. TLV320AIC29 is used as the audio codec to

convert and process audio signal and digital signal. The audio amplifier TDA8547TS is used to amplify

the analog audio signal. DSP processes digital signal (audio signal e n cod in g /dec odi ng, d igital I/Q signal

decoding, digital audio signal processing). AD9864 converts and processes the RF IF signal, and sends

the undemodulated serial digital I/Q signal to the DSP for proce ssing. Then DAC5614 conv erts the d igital

signal output by DSP to analog signal.

Figure 6-15 Diagram of Audio Section

6.3.2 Diagram of Signal Flow

The microphone converts the audio signal into electrical signal, which is then amplified by PGA of the

codec and sent to ADC of the codec for sampling. After digital audio processing, the signal is output to

DSP for processing. Then the signal is sent to DAC (TLV5614), which converts the signal to modulation

signal. After modulated and amplified in the RF mod ule, t he signal is sent out from the ant enna.

The RF signal received by the RF module is converted to digital signal by ADC (AD9864), and is then

14

Page 19

Service Manual

Ω

sent to DSP for demodulation and processing. Then the digital signal is sent to the digital audio

processor of the codec for digital audio processing, and is then converted into analog audio signal by

DAC of the codec. Finally the signal is amplified by the external audio amplifier (TDA8547TS) to drive

the speaker.

UWIRE.SCLK

UWIRE.CS3

UWIRE.SDO

UWIRE.SDI

Internal/

external MIC input

MIC

gain:

22dB

TX

TX

RX RX

APA

TDA8547TS

Gain: 31dB

Internal/external speak er

output

Figure 6-16 Diagram of Audio Signal Flow

RX

6.3.3 Audio Amplifier

Main parameters of TDA8547TS are listed in the table below:

Rated Power (Po) 0.5W

Maximum Power (P

) 1.2W

max

OMAP5912

MCLK

MCBSP1.DR

MCBSP1.FSX

MCBSP1.DX

MCBSP1.CLKX

Audio is processed via DSP.

=16Ω

R

L

=16

R

L

TX

MCBSP2.DX DIN

MCBSP2.DR

TLV5604

DAC

DOUTA

AD9864

RF TX

RF RX

The operation status of the audio amplifier is controlled via GPIO of OMAP. See the table below.

Mode-Amp SEL-SPK MODE SELECT OUT

1 1 0 0 OUT2

1 0 0 1 OUT1

0 1 1 1 Standby

15

Page 20

Service Manual

6.4 Troubleshooting Flow Chart

The GPS module

outputs normally?[1]

Yes

The channel from GPS to

OAMP is normal?

Yes

L506 outputs 2.8V

voltage?

Yes

U501 is normal?[3]

No

No

No

Yes

No

The power supply for GPS is

normal?[2]

No

Replace abnormal RC and

check OMAP.

GPS PIN17 outputs 2.8V voltage?

Replace U501.

Yes

Check the power

supply.

No

Replace the GPS

module.

Replace the

GPS module.

Yes

No

Z501 is normal?[4]

Replace Z501.

Description of Nor ma l S it uations:

[1] The radio shows normal power-on screen, and the backlight is norma l.

[2] The RF power supply out puts normally, and the RX channel is on.

[3] Vpp: 700mV~800mV, F: 19.2MHz.

16

Page 21

Service Manual

6.5 PCB Difference

For UHF1 PCB, Version H and Version K are made on the basis of Version F.

1. The following changes are made for Version H:

1) Remove the board border and the small board.

2) C802 is compatible with 1206 and 0805.

2. The following changes are made for Version K:

1) Add test points (P609 and P610) for the GPS power supply.

2) Add capacitors C301, C302, C303, C304 and C305.

3) Add R208.

4) Remove the board border.

5) C802 is compatible with 1206 and 0805.

For VHF PCB, Version B is made on the basis of Version A. However, some changes are made for

Version B:

1) Add test points (P609 and P610) for the GPS power supply.

2) Add R208.

3) C802 is compatible with 1206 and 0805.

17

Page 22

Service Manual

7. GPS Circuit

7.1 Circuit Description

Figure 7-1 Diagram of GPS Circuit

The GPS function is realized via REB-1315LPx. The GPS circuit integrates a baseband processor, a

LNA and a SAW. The 1575.42MHz GPS signal is received by the antenna, and then goes to HPF to

remove the in-band signals used for transmission and reception. After that, the signal goes to BPF to

further remove in-band signals, as well as harmonic and spurious signals. Then the weak GPS signal

goes to a low-noise amplifier (LNA) for amplification. After amplified, the signal goes to the GPS module

for further amplification and filtering, and is then sent to the baseband section for calculation. Then the

calculated GPS positioning information is sent to OMAP via the UART interface. Meanwhile, OMPA can

send appropriate comman d infor mation to t he GPS module v ia the UAR T inter face. Fin ally, OMAP sends

the processed data inf ormat ion to LCD.

18

Page 23

Service Manual

7.2 Schematic Diagram

Figure 7-2 Schematic Diagram

19

Page 24

Service Manual

7.3 Parts List

No. Ref. No. Part No. Description

1 C518 3101051590000 1.5P

2 C519 3199050758000 0.75P

3 C520 3101050100030 1P

4 C527 3101050200010 2P

5 C514 3101051210000 120P

6 C516 3101051590070 1.5P

7 C517 3101051800010 18P

8 C522 3101051040060 0.1U

9 C521 3101051210000 120P

10 C512 3101054710010 470P

11 C515 3101051050000 1UF

12 C513 3101055600000 56P

13 C523 3101051040060 0.1UF

14 C524 3101055600000 56P

15 C525 3101051040060 0.1UF

16 C526 3101051050000 1UF

17 L503 3297106339000 3.3nH

18 L504 3297106339000 3.3nH

19 L501 3297106339000 3.3nH

20 L508 3210305829000 8.2nH

21 L507 3210305180000 18nH

22 L506 3210106390000 39nH

23 L509 3210305829000 8.2nH

24 L502 322150660108 Bead

25 L505 322150660108 Bead

26 R502 3001053310000 330Ώ

27 R501 3001054710000 470Ώ

28 R504 3001051030050 10KΏ

29 R503 3001051010000 100Ώ

30 Z501 3804157560000 GPS filter

31 U501 3609999000300 GPS low-noise amplifier

32 U502 1615000001720 GPS module

20

Page 25

Service Manual

7.4 Troubleshooting Flow Chart

The GPS module

outputs normally?[1]

Yes

The channel from GPS to

OAMP is normal?

Yes

L506 outputs 2.8V

voltage?

Yes

U501 is normal?[3]

No

No

No

Yes

No

The power supply for GPS is

normal?[2]

No

Replace abnormal RC and

check OMAP.

GPS PIN17 outputs 2.8V voltage?

Replace U501.

Yes

Check the power

supply.

No

Replace the GPS

module.

Replace the

GPS module.

Yes

No

Z501 is normal?[4]

Replace Z501.

Description of Nor ma l S it uations:

[1] Detect with a multimeter. The volt age of TP502 changes w it hin the range 1.2V~2.8 V.

[2] V oltage at L502 and L505: about 3. 3V.

[3] Gain for U501 (@1.57542G Hz): >15dB.

[4] Insertion loss for Z501 (@1.57542GHz): <4dB.

21

Page 26

Service Manual

8. Tuning Description

For details about radio tuning, please refer to the help file of DMR Tuner Software supplied by the

Company.

22

Page 27

Service Manual

9. Interface Definition

J1601: 50-Pin Interface

Pin No. Name Function Valid Level

2、5、49

1

3

4

6

8

10

12

14

16

7 3V6D Power supply: 3.6V

9

11

13 EMERGENCY Emergency key L

32

43

18 GPIO GPIO

20 LED-K-KEY LED indication for key operation L

15

17

19

21

22

24

26

28

30

23 EXT - PTT External PTT detection L

25

27

29

34

36

38

40

42

44

31

33

35

GND Power supply: groun d (analog)

AF-CODEC-TO-50PIN

AF-50PIN-TO-CODEC

EXT-MIC+

EXT-MIC-

Analog audio signal o utput/input

External MIC interface

IO5-OPT

IO4-OPT

IO3-OPT

GPIO pin of the option board L/H

IO2-OPT

IO1-OPT

USB-D+

USB-D-

USB data cable

DGND Power supply: ground (dig ital)

KB-R1

KB-R2

KB-R3

Keyboard row L

KB-R4

KB-C4

KB-C3

KB-C2

Keyboard column

KB-C1

KB-C0

SEL1-Accessory

SEL2-Accessory

Accessory identifier L

SEL3-Accessory

UART1-RX-OPT/PS

UART1-TX-OPT/PS

UART1

UART3-TX-OPT

UART3-RX-OPT

UART3-CTS/IO30-OPT

UART3

UART3-RTS/IO29-OPT

MCBSP3-FSX-OPT

MCBSP3-DX-OPT

MCBSP3

MCBSP3-WCLK-OPT

23

Page 28

Service Manual

37 MCBSP3-DR-OPT

IIC-SDA-Acce (for Version K of

UHF1/UHF2/UHF3 and Vers ion B

39

41

IIC-SCL-Acce/CLK-32K-OUT

IIC-SDA-Acce/CLK-OPT

46 EXT-BAT+

48

50

45

47

IN-SPKIN-SPK+

EXT-SPKEXT-SPK+

of VHF)

CLK-32K-OUT (f or Version F /H of

UHF1)

IIC-SCL-Acce (for Version K of

UHF1/UHF2/UHF3 and Vers ion B

of VHF)

CLK-32K-OUT (f or Version F /H of

UHF1)

Power supply for accessory or

option board

Internal speaker

External speaker

J311: 30-Pin LCD Interface

Pin No. Name Function Valid Level

1

26

Ground (digital)

2-17 M-D0----M-D15 LCD data

18 /CS-LCD LCD chip select L

19 /RST-OUT Reset signal

20 M-A1 Data and command

21 /WE Write signal L

22 /OE Read signal L

23 IMO 16/8-bit LCD data selection

24 3V3D Power supply: 3.3V

25 VFLASH Power supply for IO

27 3V6D Power supply for backlight

28

29

Backlight control L

30

J821: Channel Board Interface

Pin No. Name Function Valid Level

1 Emergency Emergency L

2 CH2 Channel select

3 CH8 Channel select

4 VOL Volume adjust

5 CH4 Channel select

6 CH1 Channel select

24

Page 29

Service Manual

7 LED1 Red LED enable H

8 LED2 Green LED enable H

9 GND

10 INT-MIC+780 Microphone+

11 INT-MIC-780 Microphone-

12 NC/GND NC (for Version K of

UHF1/UHF2/UHF3 and Version

B of VHF)

GND (for Version F/H of UHF1)

13 PWR-SW- Power-on enable input

14 PWR-SW+ Power-on enable output

15 3V3DRF 3.3V power supply

16 NC/GND NC (for Version K of

UHF1/UHF2/UHF3 and Version B

of VHF)

GND (for Version F/H of UHF1)

J2: 20-Pin Option Board Interface

Pin No. Name Function Valid Level

1

3

5

7

9

11

13

15

17

2

4

6

8

10

12

IO1-OPT

IO2-OPT

IO3-OPT

IO4-OPT

IO5-OPT

UART3-TX-OPT

UART3-RX-OPT

UART3-CTS/IO30-OPT

UART3-CTS/IO30-OPT

IIC-SDA-Acce/CLK-32K-OUT

IIC-SCL-Acce/CLK-OPT

MCBSP3-DR-OPT

MCBSP3-WCLK-OPT

MCBSP3-DX-OPT

MCBSP3-FSX-OPT

GPIO L/H

UART3

IIC-SDA-Acce (for Version K of

UHF1/UHF2/UHF3 and Vers ion B

of VHF)

CLK-32K-OUT (f or Version F /H of

UHF1)

IIC-SCL-Acce (for Version K of

UHF1/UHF2/UHF3 and Vers ion B

of VHF)

CLK-32K-OUT (f or Version F /H of

UHF1)

MCBSP3

14 Ground (analog)

16 AF-50PI N-TO-CODEC Analog audio signal

25

Page 30

Service Manual

18 AF-CO DE C-TO-50PIN Analo g audio signal

19 Ground (digital)

20 3V6D Power supply for digital circuit

16-Pin Accessory Interface

Pin No. Name Function Valid Level

1 GND Ground (analog & digital)

2 SPK- External speaker-

3 SEL1-Accessory Accessory identifier 1 L

4 SEL2-Accessory Accessory identifier 2 L

5 Emergency Emergency L

6 SPK+ External speaker+

7 USB+ / RTS USB+ / RTS

8 USB- / CTS USB- / CTS

9 S WB+ Power supply for the interface

10 MIC- External MIC-

11 GPIO GPIO

12 MIC+ External MIC+

13 SEL3-Accessory

14 TX

15 RX

Accessory identifier 3 or 1-wire

communication interface

TX end of serial port

communication

RX end of serial port

communication

L

16 PTT TX control L

Definition of Accessory Identifiers

No. OPT_SEL1 OPT_SEL2 OPT_SEL3 Definition

1 0 0 0 Reserved

2 0 0 1 Reserved

3 0 1 0 USB master mode for t he radio

4 0 1 1 For connecting earpieces

5 1 0 0 For connecting MODEM

6 1 0 1 For connecting remote speaker microphones

7 1 1 0

Programming cable (serial port ) /

USB slave mode for the radio

8 1 1 1 No accessory

26

Page 31

Service Manual

10. UHF1 (400-470MHz) Information

10.1 Transmitter Circuit

Figure 10-1 Diagram of Transmitter Circuit

The transmitter circuit is ma inly composed of:

① RF power amplifier circuit

② Low-pass filter circuit (for suppressing harmonics)

③ Auto power control c ircu it (APC) (including temperature det ect ion circuit)

The carrier signal generated by TX VCO is modulated and amplified, and then feeds to the transmitter

circuit. In this circuit, the signal passes through a π-type attenuator first, allowing certain isolation

between the RF power am plifier c ircuit and TX VCO. Then it g oes to a pr e-driv er a mplifier (2S C3356) for

pre-amplification, also providing certain isolation. After that, the signal goes to another pre-driver

amplifier (2SC4988) and a driver amplifier (RD01) for further power amplification, to provide appropriate

signal to the final-stage amplifier (RD07) for final power amplification. After processed by multiple

amplifiers, the signal is processed by a microstrip matcher to complete output impedance matching, so

as to reduce output power loss due to impedance mismatch. Then the signal passes through the TX/RX

switch and goes to the low - pass filter.

The low-pass filter is a high-order Chebyshev filter composed of lumped-parameter inductors and

capacitors. V ia th is filt er, the spurious signal within the stop band ca n be att enuat ed as much as pos sib le

while the in-band ripple is w ithin the required range.

27

Page 32

Service Manual

In the auto power control and temperature detection circuit, the drain current from the driver amplifier

and final-stage ampl if ier is converted to volt age via the sampling resistor and subtraction circuit

(composed of the first operationa l amplifier). This voltage is compared with the APC control voltage

(output by DAC) at the second operational amplifier. Then the error voltage, which is out put by the

second operational a mp li fier, controls TX power by controlling the b ias v oltage at the gates of the

amplifiers (including t he driver amplifier and the fina l-stage amplifier). The temperature sensor detects

the surface temperature of the final-st age a mplifier, and converts it to DC vo ltag e. Then t he DC v oltag e is

compared with the voltage corresponding to the protection temperature (generally 80% of the extreme

temperature) of the amplifier. If the surface temperature is too high, the bias voltage of the amplifier will

be reduced, so as to reduce output pow er. The bias voltage will not be increased until the surface

temperature restores to normal level. This process will be repeated while the radio operates.

10.2 Receiver Circuit

1 2

Pi Attenuator

Figure 10-2 Diagram of Receiv er Circuit

The receiver circuit mainly comprises the RF band-pass filter, low-noise amplifier, mixer, IF filter, IF

amplifier and IF processor.

10.2.1 Receiver Front-end

The HF signal from the low-pass filter passes through the electrically tunable band-pass filter controlled

via APC/TV1 level, to remove out-of-band interference signal and to send wanted band-pass signal to

the low-noise amplifier (Q9001). The amplified signal goes to a band-pass filter controlled via APC/TV1

level, to remove out-of-band interference signal generated during amplification, and to send wanted HF

28

Page 33

Service Manual

signal to the mixer.

The wanted signal passes through t he RF band- pas s filter and l ow-noi se amp lif ier and goes t o the mixer

(D9017). Meanwhile, the first local osc illator (LO ) sig nal generat e d by VCO p a sses throu gh the low - pas s

filter and also goes to the mixer (D9017). In the mixer, the wanted signal and the first LO signal are

mixed to generate the first IF signal (73.35MHz). Then the signal passes through a π-type attenuator

(2dB) and the LC, to suppress carrier other than t he first IF signal, and to increase the isolation between

the mixer and the IF filter. After that, the first IF signal is processed by the crystal filter (Z9001), and is

sent to the two-stage IF amplifier circuit (composed of 2SC3356) for amplification. Then the amplified

signal goes to the IF processor AD9864(U401) for processing.

10.2.2 Receiver Back-end

Figure 10-3 Diagram of IF Processor

The first IF signal (73.35MHz) output by the IF amplifier goes into AD9864 (U401) via Pin 47, where the

signal is converted to the second IF signal (2.25MHz). Then the signal is converted to digital signal via

ADC sampling, an d outp ut v ia the S SI int er face. Fina lly, the digital signa l is sent t o DS P (OMA P59 12) for

demodulation.

AD9864 employs reference frequency of 19.2MHz and shares the crystal with OMAP. The second LO

VCO comprises an oscillator, a varactor and some other components, to provide the 71.1/75.6MHz LO

signal. The 18MHz clock frequency is generated by the LC resonance loop.

29

Page 34

Service Manual

10.3 Frequency Generation Unit (FGU)

Figure 10-4 Diagram of FGU

The FGU is composed of VCO and PLL. It is the core module of the whole TX-RX system. This circuit

provides accurate carrier frequency during transmission, and stable LO signal during reception. It has a

direct influence on the perfor ma nce of the system.

10.3.1 Working Principle of PLL

The 19.2MHz frequency g enerated by the referenc e cryst al oscillator g oes to P LL for div ision, gen erating

the reference frequency (i.e. step frequ ency f1). Mea nwhi le, the freq uency generated by VCO ge nerate s

another frequency (f2) through th e freque ncy divid er in PLL. Then freque ncies f1 and f2 are compared in

the phase detector (PD), to generate continuous pulse current. The current goes t o t he loop filter for RC

integration, and is then converted to CV voltage. Then the CV voltage is sent to the varactor of VCO. It

adjusts the outpu t fre quen cy of VCO dir ect ly until th e C V voltage becomes constant. Then PLL is locked ,

and the stable frequency output by VCO goes to the TX-RX channel after passing through two buffer

amplifiers.

10.3.2 Working Principle of VCO

VCO employs Colpit ts osc illator circu it (the RX oscil lator circuit is co mposed of D102, D103, D106, D107

and L1 1 2; the TX oscillato r circuit is composed o f D1 08, D109, D110, D101 and L117). It obtains different

30

Page 35

Service Manual

output frequencies by changing the varactor's control voltage (i.e. CV voltage).

There are two types of VCO: TX VCO and RX VCO. Both types control EMD22 to switch operating

status via OMAP. RX VCO is co mpos ed of the os ci lla tor loop and Q1 04, t o provide LO signa l. TX VCO is

composed of the oscillator loop and Q108, to provide carrier for TX signal.

10.3.3 Two-point Modulation

In TX mode, the two-point modu lation techn ology is empl oyed, to obt ain highe r modulation ac curacy and

lower 4FSK bit error rate. MOD-VCO and MOD-XO send th e mo dulation signal to the modulation end of

VCO and the reference crystal oscillator of PLL respectively to modulate TX VCO and the reference

crystal oscillator.

31

Page 36

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G PCB View (Main Board)

Top Layer

32

10.4 PCB View

Page 37

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G PCB View (Main Board)

Bottom Layer

33

Page 38

PD70X/PD70XG/HD705/HD705G PCB View (Channel Board)

Top Layer

34

Page 39

PD70X/PD70XG/HD705/HD705G PCB View (Channel Board)

Bottom Layer

35

Page 40

PD78X/PD78XG/HD785/HD785G PCB View (Channel Board)

Top Layer

36

Page 41

PD78X/PD78XG/HD785/HD785G PCB View (Channel Board)

Bottom Layer

37

Page 42

PD78X/PD78XG/HD785/HD785G PCB View (Keyboard)

Top Layer

38

Page 43

PD78X/PD78XG/HD785/HD785G PCB View (Keyboard)

Bottom Layer

39

Page 44

40

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G

Block Diagram (RF Section)

10.5 Block Diagram

TV1/APC

MOD1

4CH DAC

OMAP

MOD2+Freq error shift

CV Buffer

OP

Adapt control

Adap

SW

Tx_VCO

Rx_VCO

t

Reference OSC signal

AD9864

Pi Attenuator

Fr

om OMAP

1 2

Frequency

Synthesizer

Ref.

19.2MHZ

CV

SW

Pre-driver1

RX/TX

VCO buffer

Osc

.

CV-rea

IF FilterIF Processor IF Amp

Pre-Drive2 Drive-stage

RX/TX

VCO

amplifier

LPF

CV ou

t

d

control

1 2

Pi Attenuator

Pi Attenuator

Final-stage

Microstrip

Matcher

Tx/Rx Switch

Low-pass Filter

ANT

TV1/APC

HPF

LPF

APC module

BPF

Low-Noise Amp

BATT

+

GPS

module

TO omap

Mixer

Pi Attenuator

1 2

LPF

nd-pass Filter2

Ba

Low-

Noise Amp

nd-pass Filter1

Ba

Stop band filter

TV1

/APC

Page 45

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G

Block Diagram (Baseband Section)

41

Page 46

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G

Block Diagram (Power Section)

42

7.4V

Fuse

2.5A/32V

Main

Battery

LDO: 5V

LDO:5V

5VA-RTC/

150mA; VCO

5VA/150mA;

RX/TX/DAC

LTC1877

DC to DC 600mA

LTC1877

DC to DC 600mA

1.6A/7.4V/5W

230mA/7.4V/Po=0.9W

21mA/5VFGU

TX:53mA/RX:29mA

5VFGU

LDO 3V3 150mA

5VRT

LDO 3V3 150mA

LDO 3V3 150mA

3V6D

LDO 1V8 150mA

LDO 3V3 150mA

RESET IC

1V6D

LDO 3V3 150mA

3V3ARF

3V3DRF

LDO1

3V3A

1V8D

3V3D

3V3D

RESET(MIN:800mS)

Back-up

125uA-1000uA/5VFGU

3V3DRF

12.5mA

3V3ARF

1mA/3V3ARF

3.5mA/5VRT

2V5 /division

16mA/3V3ARF

5mA/5VFGU

3V3DRF

0.5mA/3V3D

0.5mA/3V3A

5mA/1V8D

1mA/3V3D

2V5 /division

17mA/3V3A

15mA/3V3D

20mA/3V6D

40mA/1.8VD

40mA/3V3D

30mA/3V3D

3mA/1V8D

210MA/1V6D

66mA/3V3D

10uA /3V6RTC

5mA/3V3D

6mA/3V3D

RF PA 7.4V/1.6A

Vcc1 /2 2.2V-18V 210mA/Po=0.89W/7.4V

AF PA(TDA8547TS)

VCO

RX/TX

VCCcp_main: Charge pump supply, 2.7V-5V(3 to 5 V);

VCCdigital: Digital supply, 2.7V-3V-3.3V;

VCCxtal : Crystal oscillator ECL/ C ML, 2.7V-3V-3.3V;

VCCecl/cml: ECL/CML, 2.7V-3V-3.3V ;

DVDD 4.5V-5V-5.5V(5V Supply) 2.7V-3V-3.3V(3 Supply)

DAC(TLV5604)

No load,run clk:: Slow1.4mA/Fast 3.5mA(5V) Slow1mA/Fast 3mA(3V)

AVDD 4.5V-5V-5.5V(5V Supply) 2.7V-3V-3.3V(3 Supply)

Vref

VDDF Positive supply for ADC back end

Analog voltage

V

DDA Positive supply for ADC front end

2.7V-3V-3.6V

V

DDI Positive supply for LNA and Mixer

Charge pump

V

DDQ Positive supply for CLK synthesizer

voltage

2.7V-5V-5.5V

V

DDP Positive supply for LO synthesizer charge pump

IF(AD98644) Op :17mA Std :0.01mA

Interface voltage

V

DDL Positive supply for LO synthesizer

1.8V--- -3.6V

V

DDD Positive supply for Internal digital

Digital voltage

V

DDC Positive supply for CLK synthesizer

2.7V-3V-3.6V

V

DDH Positive supply for digital Interface

DVDDI/O(1.71V-1.8V-AVDD)

AVDD(2.4V-2.8V-3.6V)

DVDD 1.65V-1.8V-1.95V Digital core

IOVDD

VREF 2.3V-2.5V-2.7V Pro=2.5V SAR ADC reference voltage

1.25V Pro=1.25V

VBAT 0.5V-6V Battery monitor input

Vbat/2

AVDD1

AVDD2

BVDD

DRVDD

VDD 3.3V/15mA(EMIFS Bus is used 3V3D)

LED (1*WLED 3.2±0.2V/15mA)

V

VDD/Q 1.7V-1.8-1.95V /5 0mA Operation mode

Vcc 2.7V-3.1V /33mA(read while write)

DVDD1

DVDD3

DVDD5

DVDD6

DVDD7

DVDD8

DVDD9

DVDDRTC

DVDD4

DVDD2

RESET

CVDD

CVDD1

CVDD2

CVDD3

CVDDRTC

CVDDA

CVDDDLL

Vin_3V3 (3.15V-3.45V)

GPS Module

(REB-1315 GSC3F/LPX)

V_RTC(

Vcc 3.3V/10mA LED

RQA0002DNS

PLL(SKY72310)

Accelerometer(MMA7455L)

2V-3.6V(MCLK=100M) I/O

2V-3.6V(MCLK=50M)

1.1V-2.5V External

Codec(TLV320AIC29IRGZR)

3V-3.3V-3.6V Audio ADC,DAC,Reference,SAR ADC

3V-3.3V-3.6V PLL analog

3V-4.2V Battery power supply

3V-3.3V-3.6V Headphone driver

LCM(TFT)

SDRAM

MCU(

Nor FLASH+PsRAM))

Peripheral I/O buffers

MCSI2 and McBSP2 peripheral I/O bu f fe r s

Flash I/F I/O buffers

Low voltage range

(1.65V-1.8V-1.95V)

MMC/SD1 I/F I/O buffers

McBSP3,MCSI1,UART,USB1 I/O buffers

High voltage range

Camera I/F and ETM I/O buffers

(2.5V-2.75Vor 3.3V-

3.6V)

GPIO,MPUIO,Microwire I/O buffers

RTC I/O

DDR/SDRAM interface I/O buffers

Not use transceiver

1.65V-1.8V-1.95V

Internal USB transceiver buffers

Use transceiver

3V-3.3V-3.6V

OMAP5912

core logic and low voltage sections of I/O

Low power standby

core logic

(1.05V-1.1V-1.21V)

MPU subsystem logic and memory

Active mode

DSP subsystem logic and memory

(1.525V-1.6V-1.65V)

RTC core logic

1.525V-1.6V-1.65V

APLL provide 48MHz to peripherals

1.525V-1.6V-1.65V

(DDR)SDRAM timing

2.5V-3.6V)

Vcc (3.0V-5.5V)/1mA(No load max)

RS232(MAX3232ESE)

Page 47

5

A

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G Schematic Diagram (Transmitter/Receiver)

43

10.6 Schematic Diagram

4

3

2

1

PD780 UHF Schematic Diagram(TX/RX Circuit)

C9002

C9002

L9002

L9002

100P

100P

82n

C9034

C9034

D D

LO

TP9002LOTP9002

31

R9002

R9012

R9012

100

100

12

C9064

C9064

C9018

C9018

470P

470P

R9098

R9098

3.3K

3.3K

R9097

R9097

3.3K

3.3K

1000p

1000p

2

R9002

47K

47K

R9091ncR9091

nc

1

3

C9096

C9096

470pF

470pF

U9003

U9003

+VS

GND

Q9002

Q9002

2SC3356

2SC3356

R9013

R9013

3.3K

3.3K

C9033

C9033

470P

470P

LM45

LM45

L9009

L9009

22nH

22nH

R902222R9022

22

2

VO

C9025

C9025

D9007

D9007

1 2

R9096

R9096

3.3K

3.3K

MA2S077

MA2S077

D9008

D9008

MA2S077

MA2S077

R9036

R9036

10k

10k

12

C9092

C9092

0.1uF

0.1uF

Q9006

Q9006

2SA1745

2SA1745

2 3

1

R9041

R9041

4.7K

4.7K

Q9008

Q9008

3

DTC114EE

DTC114EE

1

LO1

R9095

R9095

3.3K

3.3K

R5V

C C

10P

10P

R9011

R9011

100

100

C9098

C9098

470pF

470pF

2

PS-TX 3

R900782R9007

82

C9095

C9095

1uF

1uF

L9015

L9015

BLM15PD121SN1

BLM15PD121SN1

R9014ncR9014

680

680

R90331kR9033

C90268pC9026

nc

R9018

R9018

1k

DISCHARGE-SW-TX3

R9008

R9008

8p

1.5K

1.5K

1

Q9004

Q9004

2SC4988

2SC4988

R902147R9021

47

C9059

C9059

1000p

1000p

23

R9015

R9015

330

330

C9045

C9045

C9037

C9037

470P

470P

470P

470P

R9032NCR9032

NC

TEM-LEV-DET-TC 13

Q9007

Q9007

DTC114EE

DTC114EE

2

C90287pC9028

7p

L9010

L9010

22n

22n

R9039

R9039

100

100

C9046

C9046

0.1u

0.1u

3

1

L9007

L9007

10n

10n

C90328pC9032

8p

R9023

R9023

NC

3.9K

3.9K

R9037NCR9037

C9029

C9029

470P

470P

R9026ncR9026

nc

C9053NCC9053

NC

NC

C9058NCC9058

BAT+

R900933R9009

33

R9016

R9016

150

150

C9069

C9069

470P

470P

5VRT

C9073ncC9073

R90940R9094

C9075

L9027

L9027

C9119NCC9119

NC

C9091

C9091

C9086

C9086

0.1u

0.1u

0.1u

0.1u

C9110

C9110

0.01u

0.01u

C9075

L9020

L9020

BLM15PD121SN1

BLM15PD121SN1

B B

1 2

PS-RX 3

Q9019

Q9019

4 3

2

1

C9103

C9103

IF8

1000P

1000P

R9086NCR9086

NC

EMD22

EMD22

C9122

C9122

27p

27p

L9026

L9026

100n

100n

5

R9068

R9068

6

3.3K

3.3K

C9099

C9099

10p

10p

C9118

C9118

27p

27p

C9090

C9090

0.01u

0.01u

0.1U

0.1U

C9104

C9104

Q9017

Q9017

PBR941

PBR941

R5V

C9085

C9085

1000P

1000P

R9067

R9067

6.8k

6.8k

C9094NCC9094

R907551R9075

NC

51

820nH

820nH

R9081

R9081

31

10K

10K

2

R9084

R9084

56K

56K

0

470p

470p

R9093ncR9093

R9092ncR9092

nc

nc

R9066

R9066

1.5k

1.5k

R9071

R9071

330

330

C9097

31

C9097

0.1u

0.1u

Q9018

Q9018

PBR941

PBR941

33K

33K

R9079

R9079

R9078

R9078

5.6K

5.6K

C9121

C9121

2

1000P

1000P

R9085

R9085

100K

100K

C91248pC9124

8p

L9032

L9032

L9017

L9017

22n(high Q)

22n(high Q)

C9077

C9077

10p

10p

L90380L9038

0

470n

470n

C9074ncC9074

nc

C9078

C9078

20p

20p

C9105

C9105

15p

15p

nc

L9018

L9018

15n(high Q)

15n(high Q)

GNDGND

GNDGND

OUT

OUT

C91077pC9107

7p

C9079

C9079

15p

15p

23456

1u

C90411uC9041

R9034NCR9034

NC

1000P

1000P

Z9001

Z9001

73.35M

73.35M

1

IN

IN

C9101

C9101

15p

15p

C9038

C9038

0.1u

0.1u

C9060

C9060

L9022

L9022

270nH

270nH

TP9005TPTP9005

R9003

R9003

270

270

C9141

C9141

47pF

47pF

Q9005

Q9005

RD01MUS2

RD01MUS2

1

C9066

C9066

0.01u

0.01u

R9053

R9053

TP9003TPTP9003

TP

TP

32

0.39

0.39

D9017

D9017

HSMS-2827

HSMS-2827

L9001

L9001

82n

82n

1 2

C9071

C9071

0.1u

0.1u

L9006

L9006

L90111uL9011

1u

C9039

C9039

470P

470P

D9010

D9010

EDZ3.6B

EDZ3.6B

61243

4

10n

10n

R9054

R9054

0.39

0.39

T9002

T9002

XFMR

XFMR

C9027

C9027

12P

12P

R9024

R9024

6.8K

6.8K

L9014

L9014

BLM18SG121TN1

BLM18SG121TN1

1 2

R9055

R9055

0.39

0.39

32

6 124 3

C90149pC9014

9p

C9050

C9050

470P

470P

R9048

R9048

150K-F

150K-F

C9139NCC9139

NC

R9027

R9027

8.2k

8.2k

R9057

R9057

150K-F

150K-F

1

T9001

T9001

XFMR

XFMR

C9035

C9035

22P

22P

L90390L9039

L9016

L9016

3.3n

3.3n

R9017

R9017

100

100

C9048

C9048

470P

470P

0

R9029

R9029

TP9004TPTP9004

TP

C9140ncC9140

nc

330

330

R9100

R9100

150K-F

150K-F

C9070NCC9070

NC

R9101

R9101

150K-F

150K-F

C91378pC9137

8p

470P

470P

Q9003

Q9003

RD07MUS2B

RD07MUS2B

C9049

C9049

0.1u

0.1u

R9045

R9045

1M-F

1M-F

C91139pC9113

9p

1

C9047

C9047

470P

470P

R9072

R9072

100K

100K

C9136

C9136

4pF

4pF

L90355TL9035

5T

C9020

C9020

32

C9044

C9044

0.01u

0.01u

470K-F

470K-F

HVC350B

HVC350B

2 1

43p

43p

L9008

L9008

47nH

47nH

R9046

R9046

1M-F

1M-F

C9062NCC9062

NC

R9058

R9058

C9111

C9111

D9001

D9001

C9089

C9089

1000P

1000P

2.4p

2.4p

C9012ncC9012

nc

C9008ncC9008

nc

D9012

D9012

HVC350B

HVC350B

1

100K-F

100K-F

2 1

12

+

+

APC-out

APC-out

TP9001

TP9001

R9059

R9059

C9135

C9135

L90335TL9033

5T

C9138

C9138

0.047u

0.047u

R9073

R9073

100K

100K

4pF

4pF

C90158PC9015

C9021

C9021

C9051

C9051

22u/10v

22u/10v

8P

3.6P

3.6P

C9042

C9042

470P

470P

C9109

C9109

15p

15p

C9120

C9120

12P

12P

1

2

3

4

C9080

C9080

0.1u

0.1u

C90094PC9009

C9006NCC9006

4P

NC

C9043

C9043

0.1u

0.1u

A OUTPUT

A -INPUT

A +INPUT

GND

C90077PC9007

7P

C9022NCC9022

NC

R9025

R9025

R90381kR9038

1k

U9002

U9002

AD8566ARMZ

AD8566ARMZ

R5V

C9081

C9081

470P

470P

C9100

C9100

2.7p

2.7p

22n

22n

L9028

L9028

AT-41511

AT-41511

Q9001

Q9001

C90199PC9019

9P

270

270

B OUTPUT

B -INPUT

B +INPUT

L9024

L9024

220N

220N

R9028

R9028

C9057

C9057

0.1u

0.1u

V+

4

270

270

3

2

R9004

R9004

4.4nH

4.4nH

8

7

6

5

R9083

R9083

330

330

R9080

R9080

47P

47P

C9114

C9114

R9099

R9099

C9011

C9011

C9030

C9030

2.4p

2.4p

L9012

L9012

220n

220n

R9043

R9043

C9065

C9065

1500p

1500p

R9056ncR9056

5.6K

5.6K

1

1nH

1nH

82n

D9002

D9002

100P

100P

1 2

1SS356

1SS356

C90319pC9031

9p

C9040ncC9040

nc

D9005

D9005

MA2S077

MA2S077

3.3K

3.3K

C9063

C9063

1000p

1000p

R9047

R9047

33K

33K

C9067

C9067

nc

1000p

1000p

C9093

C9093

1000P

1000P

R9074

R9074

10k

10k

C9112

C9112

18p

18p

R9089

R9089

C9130ncC9130

5.6k

5.6k

nc

C9013

C9013

470P

470P

L9013

L9013

18nH

18nH

C90031pC9003

1p

L9003

L9003

18nH

18nH

C9016NCC9016

C90237pC9023

NC

12

12

D9006

D9006

MA2S077

MA2S077

C9061

C9061

1000P

1000P

R9050

R9050

47K

47K

C9106

C9106

20p

20p

L9030

L9030

C9001

C9001

1000P

1000P

3.3nH

3.3nH

HSM88AS

HSM88AS

L9029NCL9029

C9126NCC9126

NC

NC

C90042pC9004

2p

L9004

L9004

18nH

18nH

7p

Q9020

Q9020

5

6

EMD22

EMD22

C9087

C9087

C9088

C9088

1000p

1000p

0.047u

0.047u

R9076

R9076

100K

100K

C91158PC9115

8P

D9013

D9013

3

C91284pC9128

4p

2

1

C91346PC9134

6P

C90248pC9024

BAT+

43

2

1

D9014

D9014

HVC350B

HVC350B

2 1

8p

C9116

C9116

3.6p

3.6p

R9063

R9063

10K

10K

5T

L90365TL9036

C9005NCC9005

NC

L9005

L9005

18nH

18nH

PS-APC 3

R9069ncR9069

nc

R9077

R9077

100K

100K

D9015

D9015

C91334pC9133

HVC350B

HVC350B

2 1

5T

L90375TL9037

C9017NCC9017

NC

ANT-GPS9

APC/TV1 1,11

L90344pL9034

4p

C91176pC9117

6p

L9025

L9025

4p

39NH

39NH

C91298PC9129

8P

D9016ncD9016

nc

C91317pC9131

2 1

ANT1ANT1

1

R9006

R9006

L9031ncL9031

10k

10k

nc

C9123ncC9123

nc

R9090ncR9090

nc

7p

C91320C9132

0

A

Page 48

5 4 3 2 1

A

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G Schematic Diagram (CODEC)

44

PD780 UHF Schematic Diagram(CODEC Circuit)

1V8D

L823

L823

L827

L827

L828

L828

AF-CODEC-IN

AF-CODEC-OUT

3V3A

AF-OUT 12

5

2

L821

L821

BLM15PD121SN1

R823

R823

10K

10K

R824

R824

R826

R826

C839

C839

14

0.1u

0.1u

Vcc

Y

Y0

Y1

A

B

C

ENABLE

4

13

16

15

9

8

7

BLM15PD121SN1

C824

C824

C822

C822

0.22u

0.22u

0.01u

0.01u

PD-CODEC

TP821TP821

C827

C827

0.01u

0.01u

15K-F

15K-F

47K-F

47K-F

Vref=2.5V

C836

C836

0.1u

0.1u

C821

C821

0.22u

0.22u

1

IOVDD

2

PWR_DN

3

RESET

4

1

GPIO2

5

GPIO1

6

AVDD2

7

AVSS2

8

AVDD1

9

NC

10

NC

11

NC

12

NC

C8311uC831

1u

R830

R830

33K-F

33K-F

SEL1-ADC 3

SEL-Acoustic 3

SEL2-ADC 3

D

Add R823 del C823

L822

L822

BLM15PD121SN1

PWR-SW-6,7,10,12

CV-ADC1

ADC_IN

VOL7

BLM15PD121SN1

RESET-CODEC3

L820

L820

BLM18AG601SN1

BLM18AG601SN1

C828

C828

2.2u/10V

2.2u/10V

R828

R828

5

NC

10

X0

11

X1

12

X

1

Z1

2

Z

3

Z0

U820U820

GND

6

15K-F

15K-F

3V3A

3V3D

C

3V3A

B

TEM-LEV-DET-TC14

5

IIS-BLCK-CODEC

48

47

45

46

49

BCLK

DVSS

DVDD

T-PAD

AVSS113VREF14VBAT15AUX216AUX117BUZZ_IN/CP_INN18CP_OUTP19CP_INP20MICIN_HND21MICBIAS_HND22MICIN_HED23MICBIAS_HED

ADC_IN

C838

C838

270P

270P

C844ncC844

nc

A

IIS-WCLK-CODEC

IIS-DI-CODEC 5

IIS-DO-CODEC 5

43

44

SDIN

WCLK

SDOUT

AF-CODEC-OUT

5

5

5

CLK-CODEC

uW-CLK-CODEC

uW-SDI-CODEC

uW-SDO-CODEC

42

39

40

41

MISO

SCLK

MCLK

VGND/CP_OUTN

AF-CODEC-IN

C841

C841

1500P

1500P

MICBIAS--HND

5

uW-CS3-CODEC

R821

R821

100

100

37SS38

DAV

MOSI

DRVSS2

OUT8P

BVDD

OUT8N

DRVSS1

SPKFC

DRVDD

SPK2

SPK1

OUT32N

MIC_DET

24

MICBIAS--HED

C8321uC832

1u

3

DAV-CODEC

U821U821

36

35

34

33

32

31

30

29

28

27

26

25

C833

C833

0.1u

0.1u

C843

C843

0.1u

0.1u

C850

C850

0.1u

0.1u

C852

C852

0.1u

0.1u

R8252KR825

C8471uC847

1u

R8332KR833

2K

2K

C845

C845

270P

270P

C851

C851

270P

270P

C853

C853

270P

270P

C825

C825

2.2u/10V

2.2u/10V

C835

C835

270P

270P

TP822

TP822

TP823

TP823

GND

GND

MIC+

MIC+

1

1

TP820

TP820

AF-OUT

AF-OUT

C848

C848

100P

100P

R8202KR820

2K

1

C830

C830

100p

100p

R822 0R822 0

C842

C842

100P

100P

R8322KR832

2K

BLM18AG601SN1

BLM18AG601SN1

C826

C826

0.01u

0.01u

BLM18AG601SN1

BLM18AG601SN1

BLM18AG601SN1

BLM18AG601SN1

C829

C829

270P

270P

R834 0R834 0

R835 0R835 0

C8341uC834

1u

C8401uC840

1u

1500P

1500P

C858

C858

C856

C856

270P

270P

C857

C857

270P

270P

C837

C837

0.01u

0.01u

C846

C846

270P

270P

R841 10KR841 10K

C849

C849

270P

270P

R829 470KR829 470K

R838 10KR838 10K

TONE-CODEC 3

AF 50PIN to CODEC

AF CODEC TO 50PIN

EXT-MIC+ 7

EXT-MIC- 7

INT-MIC+780 7

INT-MIC-780 7

Page 49

5 4 3 2 1

A

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G Schematic Diagram (Audio Amplifier)

45

PD780 UHF Schematic Diagram(AF Amplifier Circuit)

D

BAT++

L802

L802

BLM18PG181SN1

BLM18PG181SN1

C804

C804

C803

C802

C802

22u/10V

22u/10V

C803

0.22u

0.22u

270P

270P

L803L803

EXT-SPK- 7

C805

C817

C817

0.1u

0.1u

2

C805

100p

100p

2

C808

C808

3900p

3900p

C813

C813

3900p

3900p

3

1

3

1

R803

R803

330K

330K

Q802

Q802

DTC114EE

DTC114EE

Q801

Q801

DTC114EE

DTC114EE

C806

C806

100p

100p

C815

C815

NC*0.01u

NC*0.01u

C819

C819

0.01u

0.01u

C816

C816

1u/16V

1u/16V

U801

U801

TDA8547TS

TDA8547TS

17

IN1-

16

IN1+

14

IN2-

15

IN2+

5

SVRR

4

MODE

6

SELECT

19

11

VCC120VCC2

OUT1-

OUT1+

OUT2-

OUT2+

GND11GND2

NC2NC7NC9NC12NC

C807

C807

270P

270P

18

3

13

8

10

C811

C811

270P

270P

C814

C814

270P

270P

C818

C818

270P

270P

L804L804R804

L801L801

L805L805

R802

R802

330K

C810

C810

0.1u

0.1u

C812

C812

0.1u

0.1u

R807

R807

20K

20K

330K

R804

10K

10K

R805

R805

10K

10K

C

AF-OUT13

B

Mode-AMP3

PWR-SW-6,7,10,13

SEL-Acoustic3

R80110R801

10

C809

C809

0.1u

0.1u

R80610R806

10

C801

C801

0.1u

0.1u

TP801TP801

1

TP802TP802

1

EXT-SPK+ 7

IN-SPK- 7

IN-SPK+ 7

A

Page 50

5 4 3 2 1

A

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G Schematic Diagram (DAC)

46

PD780 UHF Schematic Diagram(DAC Circuit)

D

R712

5VRT

R712

BLM15PD121SN1

BLM15PD121SN1

1 2

C705

C705

1000P

1000P

C7061uC706

1u

R709

R709

100k

100k

R713

R713

100

100

R710

R710

100k

100k

C

C7111uC711

1u

R702

R702

68k

68k

R707

R707

33k

33k

L702

L702

3V3DRF

B

PD-DAC3

MCBSP2-DX-DAC5

MCBSP2-CLKX-DAC5

MCBSP2-FSX-DAC5

LOAD-DAC5

BLM15PD121SN1

BLM15PD121SN1

1 2

C701

C701

1u/10v

1u/10v

C710

C710

0.1u

0.1u

C7071uC707

1u

C7121uC712

1u

13

15

REFINAB

OUTA14OUTB

OUTC12OUTD

11

9

10

AGND

REFINCD

8

16

AVDD

DVDD1PD2LDAC3DIN4SCLK5CS6FS7DGND

R7011KR701

R704 100R704 100

R705

R705

10K-F

10K-F

U701

U701

TLV5614IPW

TLV5614IPW

C703

C703

470P

470P

1K

APC/TV1

APC/TV1

TP702

TP702

1

MOD2

1

MOD2

TP701

TP701

C709

C709

330p

330p

C708

C708

100p

100p

R706

R706

10K-F

10K-F

C704

C704

470p

470p

TO VCO

MOD-VCO 1

APC/TV1 1,14

MOD-XO 1

TO VCTCXO

A

Page 51

5

A

PD70X/PD70XG/PD78X/PD78XG/HD705/HD705G/HD785/HD785G Schematic Diagram (Power)

47

4

3

2

1

PD780 UHF Schematic Diagram(Power Circuit)

R607 100R607 100

P607P607

J601

J601

D D

D-700/BATB

D-700/BATB

3

2

1

1 2

1

F601

F601

2.5A-32V

2.5A-32V

P608P608

1

BAT+

C614

C614

C615

C615

5.6pF

5.6pF

0.1u/16V

D601D601

D602D602

1 2

2 1

0.1u/16V

C616

C616

100pF

100pF

BAT++ 3V3ARF

R602R602

R631

2 3

Q601Q601

1

R626R626

3

NC*DTC114EE

NC*DTC114EE

1

Q602

Q602

3V3DRF

2

32

3

Q603Q603

D604

D604

DAN222

DAN222

1

R631

R6321KR632

15K

15K

31

Q604

Q604

2SK1824

2SK1824

R627

R627

47K

47K

2

R630

R630

47K

47K

1

R628

R628

47K

47K

R629

R629

2.7K

2.7K

C C

BAT++

0.22UF 10V

0.22UF 10V

C628

C628

POWER-SW+

L607L607

C630

C630

0.1uF/16V

0.1uF/16V

C619C619

B B

L613L613

C655

C655

0.22UF 10V

0.22UF 10V

C658

C658

0.1uF/16V

0.1uF/16V

EXT-BAT+

R625R625

C627C627

C645

C645

220P/50V

220P/50V

R621

R621

100K

100K

C674

C674

220P/50V

220P/50V

112

C654C654

112

2

3

3

U601U601

6

1

RUN

SW

VIN

7

SYNC

3

VFB

8

PLLPF

2

ITH

GND

4

2

3

3

U611U611

6

1

RUN

SW

VIN

7

SYNC

3

VFB

8

PLLPF

2

ITH

GND

4

L610L610

5

20pF/50V

20pF/50V

C644

C644

R617

R617

470K-F

470K-F

R618

R618

130K-F

130K-F

L614L614

5

C672

C672

20pF/50V

20pF/50V

R601

R601

100K-F

100K-F

R623

R623

150K-F

150K-F

C637

C637

47uF

47uF

C665

C665

47uF

47uF

C638

C638

0.01uF/16V

0.01uF/16V

C666

C666

0.01uF/16V

0.01uF/16V

1K

2

P606P606

1

PWR-SW- 6,7,12,13

POWER-CTL 3

C636C636

112

3

3

C661C661

112

3

3

PWR-SW+ 6,7

R6040R604

0

POWER-KEY-DET 3

POWER-SW+

TP603

TP603

3.6V

3.6V

2

2

R614R614

1

C682

C682

0.1uF/16V

0.1uF/16V

TP605

TP605

1.6V

1.6V

1

C679

C679

0.1uF/16V

0.1uF/16V

3V6D

R622R622

C681

C681

270P

270P

1V6D

C680

C680

270P

270P

C602

C602

100pF/16V

100pF/16V

C620

C620

100pF/16V

100pF/16V

BLM18PG181SN1

BLM18PG181SN1

4.7uF/16V

4.7uF/16V

BLM18PG181SN1

BLM18PG181SN1

4.7uF/16V

4.7uF/16V

3V6D

C676

C676

0.22uF 10V

0.22uF 10V

BLM18PG181SN1

BLM18PG181SN1

C656

C656

0.1uF

0.1uF

BLM18PG181SN1

BLM18PG181SN1

C688

C688

0.1uF

0.1uF

L602

L602

C603

C603

R608NCR608

NC

L605

L605

C621

C621

C678

C678

0.22uF 10V

0.22uF 10V

L612

L612

L601

L601

PS-GPS3

L615L615

L616L616

C647

C647

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF/16V

0.1uF/16V

C668

C668

C604

C604

0.1uF/16V

0.1uF/16V

C622

C622

C675

C675

1uF

1uF

C677

C677

1uF

1uF

C648

C648

1uF

1uF

C669

C669

1uF

1uF

GND_EARTH

C605

C605

1uF/25V

1uF/25V

C623

C623

1uF/25V

1uF/25V

RP102N331B

RP102N331B

1

VDD

2

GND

CE3NC

RP102N331B

RP102N331B

1

VDD

2

GND

CE3NC

RP102N331B

RP102N331B

1

VDD

2

GND

CE3NC

RP102N181D

RP102N181D

1

VDD

2

GND

CE3NC

RP102N331B

RP102N331B

1

VDD

2

GND

CE3NC

C617

C617

0.1uF/16V

0.1uF/16V

U606

U606

VOUT

C634NCC634

NC

U608

U608

VOUT

C643NCC643

NC

U609

U609

VOUT

C651NCC651

U610

U610

VOUT

C663NCC663

NC

U612

U612

VOUT

C673NCC673

NC

NC

R611

R611

10K

10K

6

6

5

VIN

ON/OFF1GND2NP(VREF)

5

VIN

ON/OFF1GND2NP(VREF)

5

4

5

4

5

4

5

4

5

4

4

GND

VOUT

U604

U604

TK11250CM

TK11250CM

3

C618

C618

0.1uF/16V

0.1uF/16V

4

GND

VOUT

U605

U605

TK11250CM

TK11250CM

3

C626

C626

0.1uF/16V

0.1uF/16V

TP601

TP601

3.3V

3.3V

1

TP604

TP604

1.8V

1.8V

1

GND_SIGNAL

C641

C641

2.2uF

2.2uF

C649

C649

2.2uF

2.2uF

C670

C670

2.2uF

2.2uF

C601

C601

2.2uF

2.2uF

C660

C660

2.2uF

2.2uF

C606

C606

2.2uF

2.2uF

BLM18PG181SN1

BLM18PG181SN1

C607

C607

0.1uF

0.1uF

BLM18PG181SN1

BLM18PG181SN1

C624

C624

C625

C625

0.1uF

0.1uF

2.2uF

2.2uF

L609

L609

BLM18PG181SN1

BLM18PG181SN1

C635

C635

0.1uF

0.1uF

3V3GPS

L611

L611

BLM18PG181SN1

BLM18PG181SN1

C642

C642

0.1uF

0.1uF

C646C646

112

3

3

C650

C650

0.1uF

0.1uF

C657C657

112

3

3

C662

C662

0.1uF

0.1uF

C667C667

112

3

3

C671

C671

0.1uF

0.1uF

L603

L603

L606

L606

3V3DRF

3V3A

C686

C686

1500P

1500P

3V3D

2

1V8D

2

3V3DRF

2

5VFGU

C687

C687

0.01uF

0.01uF

C683

C683

0.01uF

0.01uF

5VRT

C608