HYNIX HMS39C7092 Datasheet

HMS39C7092

Embedded Flash MCU

Specification Ver 1.0

System IC SBU, SP BU

MCU Business Division,

Flash Team

Flash MCU(HMS39C7092)

Released : February. 2001

ARM

is trademark of Advanced RISC Machine Ltd.

ARM7TDMI is designed by ARM Ltd.

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by Hynix for any infringements of patents or other rights of the third parties

which may result from its use. No license is granted by implication or otherwise under any patent or

patent rights of Hynix or others.

These Hynix products are intended for usage in general electronic equipment (office equipment,

communication equipment, measuring equipment, domestic electrification, etc.).

Please make sure that you consult with us before you use these Hynix products in equipment which

require high quality and / or reliability, and in equipment which could have major impact to the welfare of

human life (atomic energy control, airplane, spaceship, traffic signal, combustion control, all types of

safety devices, etc.). Hynix cannot accept liability to any damage which may occur in case these Hynix

products were used in the mentioned equipment without prior consult ation with Hynix.

Copyright 2000 Hynix Semiconductor, Inc.

All Rights Reserved

2 Preliminary

Flash MCU(HMS39C7092)

Contents

Chapter 1........................................................................................................................... 13

Introduction................................................................................................................. 13

1.1 General Description................................................................................ 14

1.2 Feature.................................................................................................. 15

1.3 Pin Descriptions ..................................................................................... 16

1.4 Operation Mode description.................................................................... 21

1.5 Memory Map.......................................................................................... 25

Chapter 2........................................................................................................................... 27

ARM7TDMI Core......................................................................................................... 27

2.1 General Description................................................................................ 28

2.2 Feature.................................................................................................. 28

2.3 Core Block Diagram ............................................................................... 29

2.4 Instruction Set........................................................................................ 30

2.4.1 ARM Instruction .................................................................................. 30

2.4.2 THUMB Instruction ..............................................................................33

2.4.3 The Program Status Registers ............................................................. 36

2.4.3.1 The condition code flags ............................................................ 37

2.4.3.2 The control bits.......................................................................... 37

2.4.4 ARM pseudo -instructions .....................................................................39

2.4.5 THUMB pseudo-instructions ................................................................ 43

Chapter 3........................................................................................................................... 47

BUS Controller ............................................................................................................ 47

3.1 Overview............................................................................................... 48

3.1.1 Features ............................................................................................. 48

3.1.2 Pin Configuration .................................................................................49

3.2 Bus Controller Registers ......................................................................... 50

3.2.1 Configuration Registers ....................................................................... 51

3.3 Operation .............................................................................................. 52

3.3.1 Area Division ...................................................................................... 52

3.3.2 Area Division ...................................................................................... 53

3.3.3 Chip Select Signals ............................................................................. 53

3.4 Basic Bus Interface ................................................................................ 54

3.4.1 Overview............................................................................................ 54

3.4.2 Byte Lane Write Control....................................................................... 54

3.4.3 Basic Bus Control Signal Timing ...........................................................56

3.4.4 Wait Control........................................................................................ 62

3.4.5 Bus Arbiter ..........................................................................................63

Chapter 4........................................................................................................................... 65

MCU Controller ........................................................................................................... 65

4.1 General Description................................................................................ 66

4.2 Pin Function Description .........................................................................66

4.3 Register Description .............................................................................67

4.3.1 Register Memory Map ......................................................................... 67

4.3.2 PINMUX Register................................................................................ 68

4.3.3 MCU Device Code Register (0x0900_002C Read Only) ......................72

Preliminary 3

Flash MCU(HMS39C7092)

Chapter 5........................................................................................................................... 73

Power Management Unit ..............................................................................................73

5.1 General Description................................................................................ 74

5.2 Operation Modes ....................................................................................75

5.2.1 Introduction......................................................................................... 75

5.2.2 Reset and Operation Modes ................................................................ 75

5.3 Power Management Unit Register Map.................................................... 77

5.4 Register Description ............................................................................... 78

5.5 Signal Timing Diagram ............................................................................ 81

5.5.1 Power on Reset .................................................................................. 81

5.5.2 Watch Dog Timer Overflow .................................................................. 81

5.5.3 Soft-Reset .......................................................................................... 82

Chapter 6........................................................................................................................... 83

The Interrupt Controller ................................................................................................83

6.1 About the Interrupt controller................................................................... 84

6.1.1 Interrupt sources ................................................................................. 85

6.1.2 Interrupt Control .................................................................................. 85

6.2 Interrupt Controller Registers .................................................................. 87

Chapter 7........................................................................................................................... 91

Watchdog Timer.......................................................................................................... 91

7.1 General Description................................................................................ 92

7.2 Watchdog Timer Introduction ...................................................................93

7.3 Watchdog Timer Operation ..................................................................... 94

7.3.1 Timing of Setting and Clearing the Overflow Flag .................................. 95

7.4 Watchdog Timer Memory Map .................................................................96

7.5 Watchdog Timer Register Descriptions .................................................... 97

7.6 Examples of Register Setting ................................................................100

7.6.1 Interval Timer Mode .........................................................................100

7.6.2 Watchdog Timer Mode with Internal Reset Disable ..............................101

7.6.3 Watchdog Timer Mode with Power-on Reset .......................................102

7.6.4 Watchdog Timer Mode with Manual Reset ..........................................103

Chapter 8.........................................................................................................................105

The General Purpose Timer.......................................................................................105

8.1 About the General Purpose Timer Unit...................................................106

8.1.1 General Purpose Timer Unit Introduction ............................................107

8.2 General Purpose Timer Unit Memory Map .............................................108

8.2.1 Register Assignment .........................................................................108

8.2.2 General Purpose Timer Unit Re gister Descriptions ..............................109

8.2.2.1 Timer Global Control Registers.................................................109

8.2.2.2 Timer Channel Control Registers .............................................. 110

8.3 General Purpose Timer Unit Operation.................................................. 114

8.3.1 Free Running Mode........................................................................... 115

8.3.2 Compare Match Mode ....................................................................... 117

8.3.3 Input Capture Mode........................................................................... 119

8.3.4 Synchronized Clear and Write Mode ...................................................120

8.3.5 PWM Mode .......................................................................................121

8.3.5.1 PWM Mode Operation .............................................................121

Chapter 9.........................................................................................................................125

UART (Universal Asynchronous Receiver/Transmitter) .................................................125

4 Preliminary

Flash MCU(HMS39C7092)

9.1 General Description..............................................................................126

9.2 Features ..............................................................................................127

9.3 Signal Description ................................................................................127

9.4 Internal Block Diagram .........................................................................128

9.5 Registers Description ...........................................................................129

9.6 UART Operations .................................................................................140

9.6.1 FIFO Interrupt Mode Operation ..........................................................140

9.6.2 FIFO Polled Mode Operation .............................................................141

9.7 Register Summary ................................................................................142

Chapter 10. ......................................................................................................................143

GPIO (General Purpose Input Output) ........................................................................143

10.1 General Description..............................................................................144

10.2 GPIO Registers ....................................................................................145

10.2.1 Register Memory Map ......................................................................145

10.3.1 Register Description ........................................................................146

10.3 Functional Description ..........................................................................147

Chapter 11 .......................................................................................................................149

On-Chip SRAM .........................................................................................................149

11.1 General Description..............................................................................150

11.2 Function Description.............................................................................150

Chapter 12 .......................................................................................................................151

On-chip Flash Memory...............................................................................................151

12.1 General Description..............................................................................152

12.2 Features ..............................................................................................152

12.3 Block Diagram .....................................................................................154

12.4 Flash Memory Register Description .......................................................156

12.5 On-Board Programming Mode ..............................................................161

12.5.1 Boot Mode .....................................................................................161

12.5.2 User Program Mode .......................................................................164

12.6 Flash Memory Programming/Erasing.....................................................166

12.6.1 Program & Program-Verify Mode ......................................................166

12.6.2 Pre-program & Pre -program Verify Mode .........................................168

12.6.3 Erase & Erase Verify Mode .............................................................170

12.6.4 Erase Algorithm ..............................................................................172

12.7 Flash Memory PROM Mode..................................................................173

12.7.1 PROM Mode Setting .......................................................................173

12.7.2 Memory Map ..................................................................................174

12.7.3 PROM Mode Operation...................................................................174

12.7.4 Timing Diagram and AC/DC Characteristics .....................................175

Chapter 13 .......................................................................................................................179

A/D Converter...........................................................................................................179

13.1 Overview.............................................................................................180

13.1.1 Features .........................................................................................180

13.1.2 Pin Configuration.............................................................................181

13.2 A/D Converter Registers .......................................................................182

13.2.1 Register Descriptions.......................................................................182

13.3 Operation ............................................................................................185

13.4 Interrupts.............................................................................................186

13.5 Usage Notes ........................................................................................187

Preliminary 5

Flash MCU(HMS39C7092)

13.6 Example ..............................................................................................190

Chapter 14 .......................................................................................................................191

Electrical Characteristics ............................................................................................191

14.1 Absolute Maximum Ratings ...................................................................192

14.2 Recommended Operating Conditions: ...................................................192

14.3 DC Characteristics ...............................................................................193

14.4 AC Characteristics................................................................................194

14.4 AD Conversion characteristics (Preliminary)...........................................196

14.5 Operational Timing ...............................................................................197

14.5.1 Clock Timing.....................................................................................197

14.5.2 Reset Timing ....................................................................................197

14.5.3 Bus Timing .......................................................................................198

Appendix

A-1 Peripheral Setting & Flash memory control Examples

A-2 Package Dimension

6 Preliminary

Flash MCU(HMS39C7092)

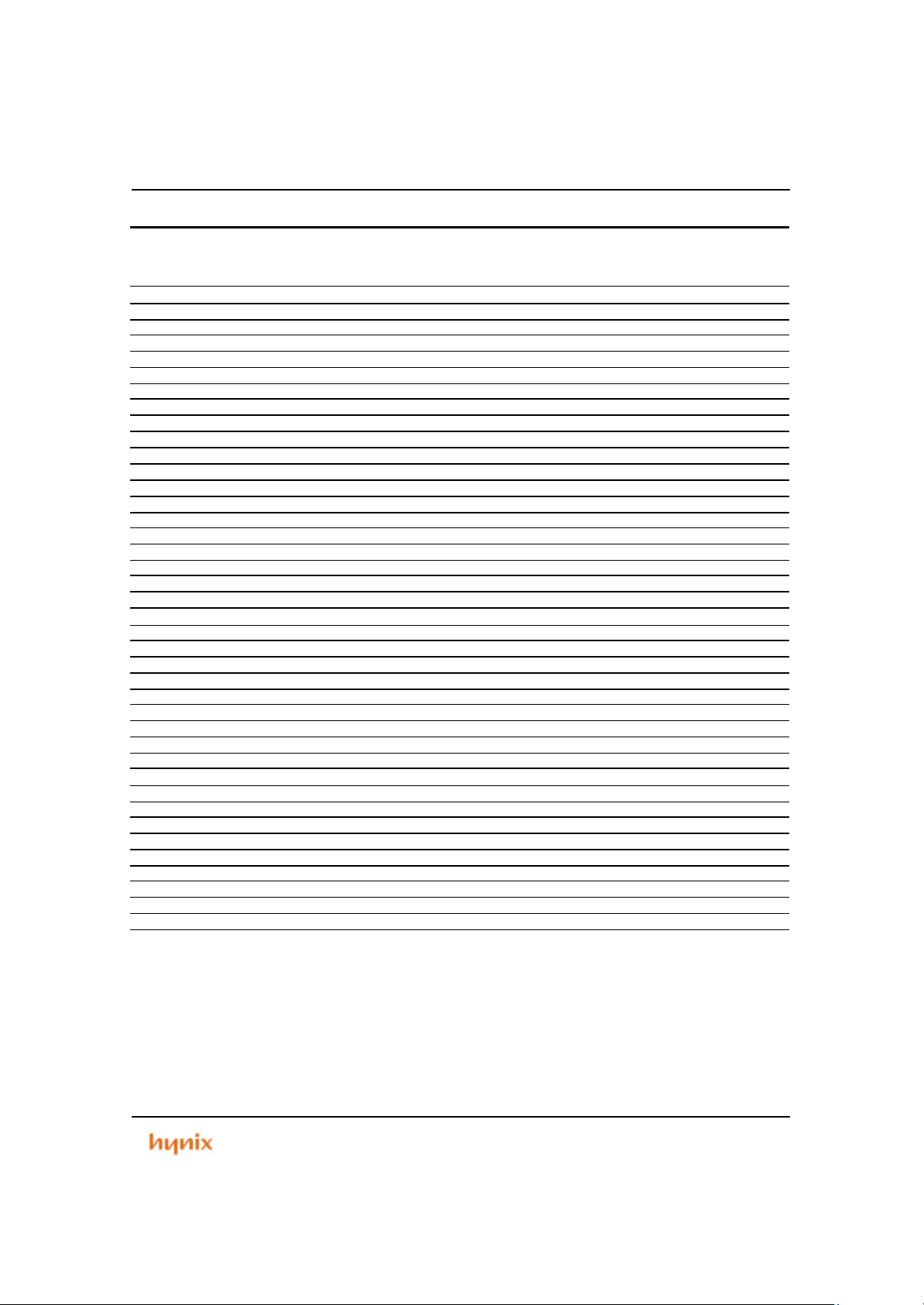

Figures

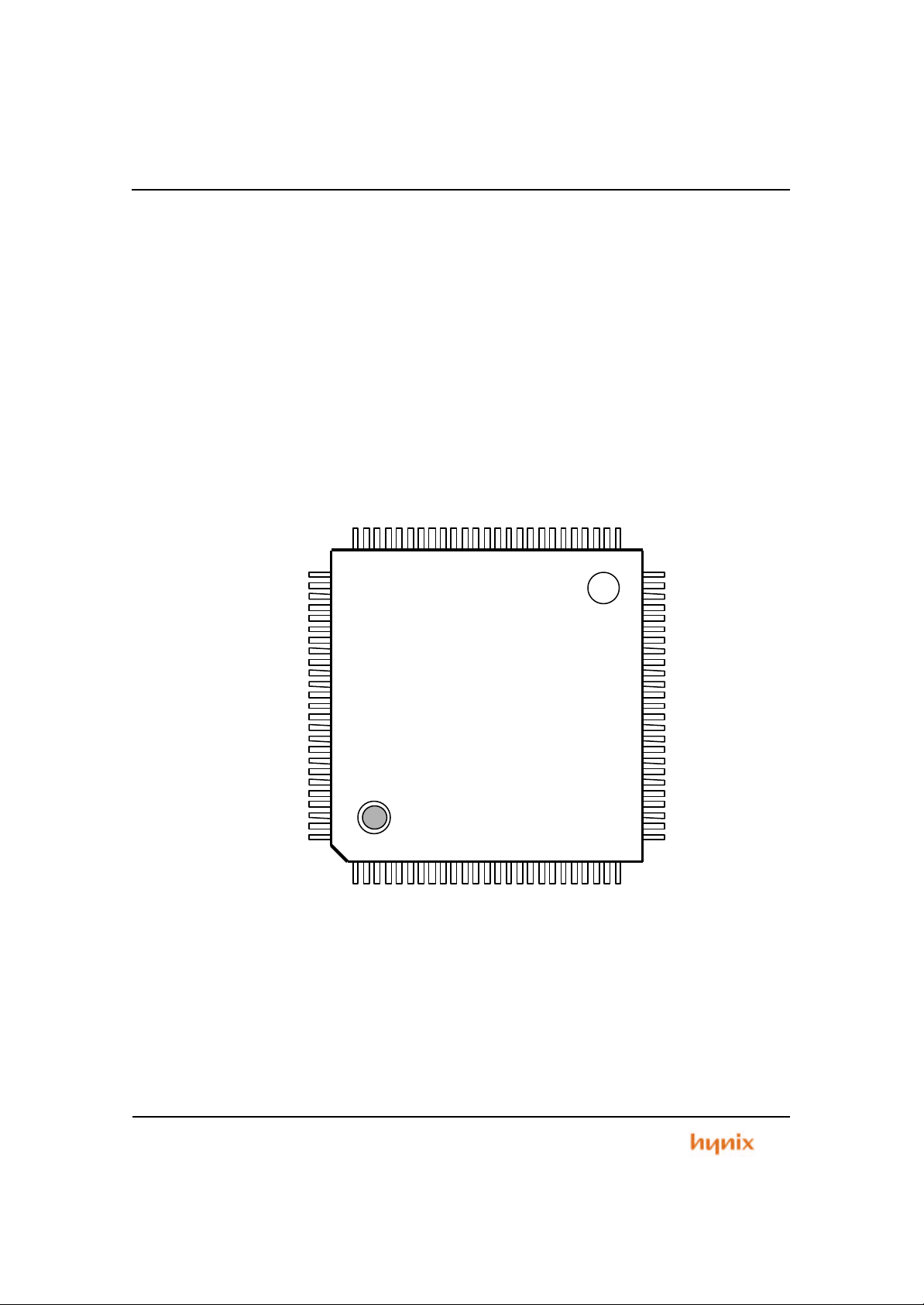

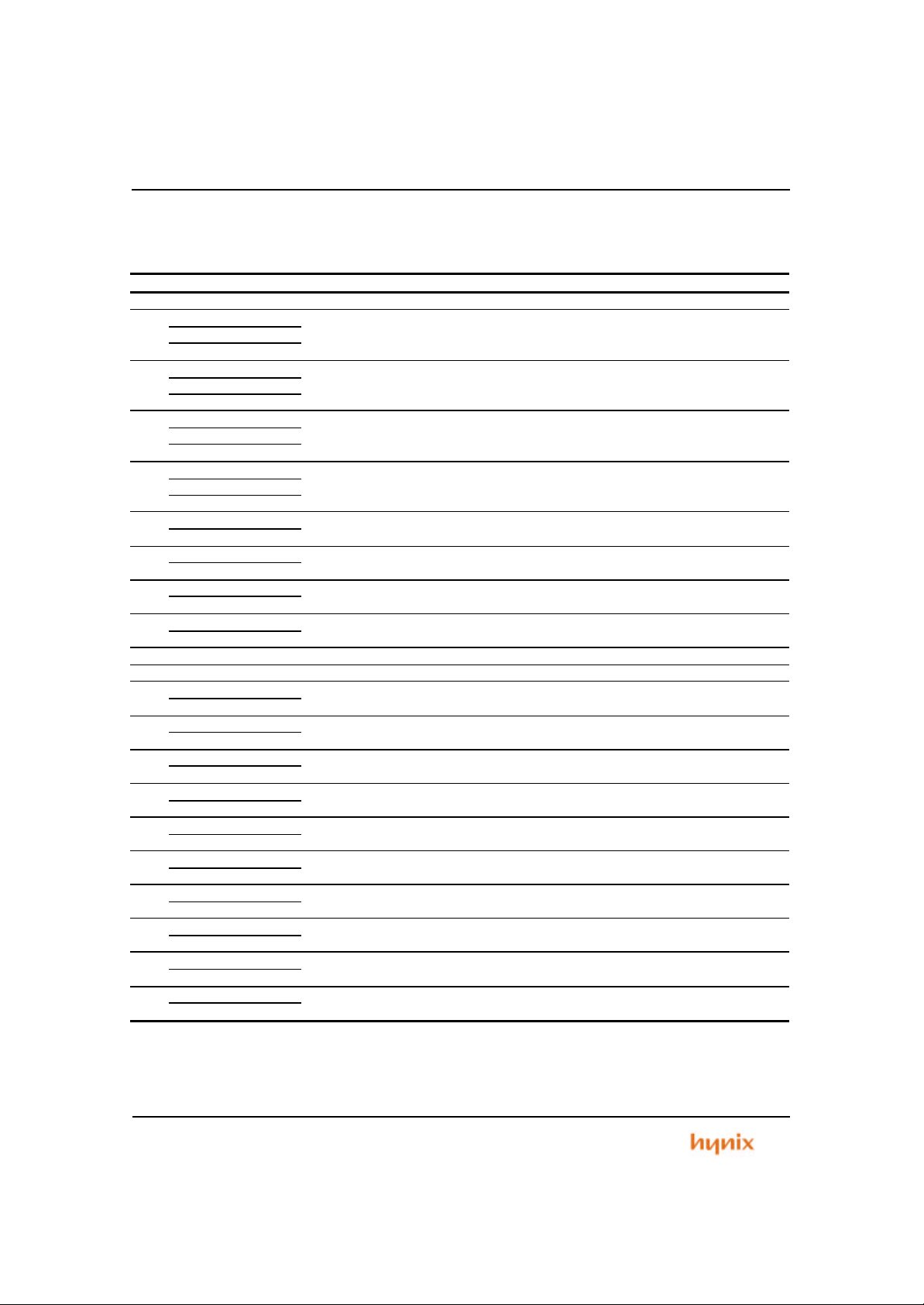

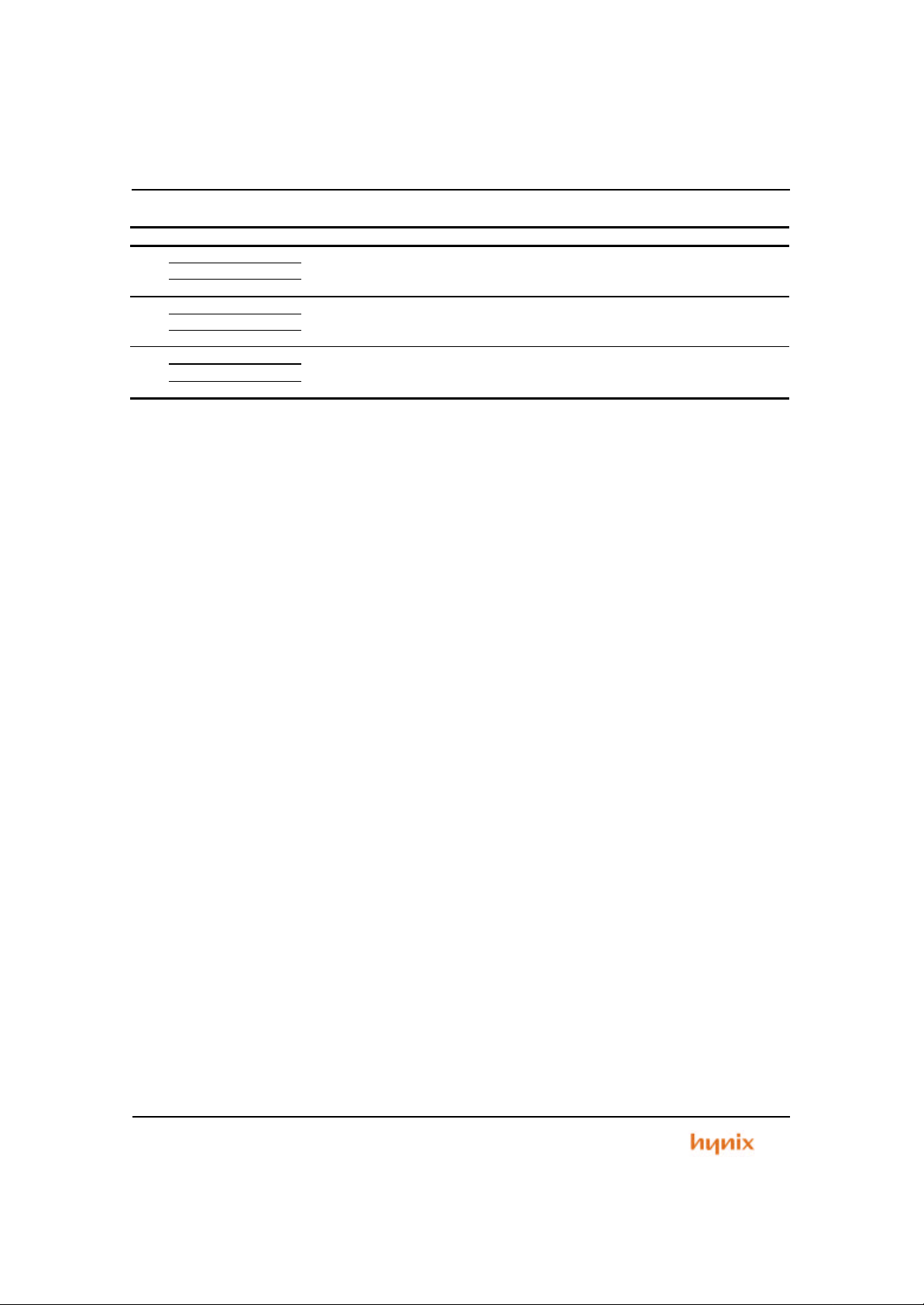

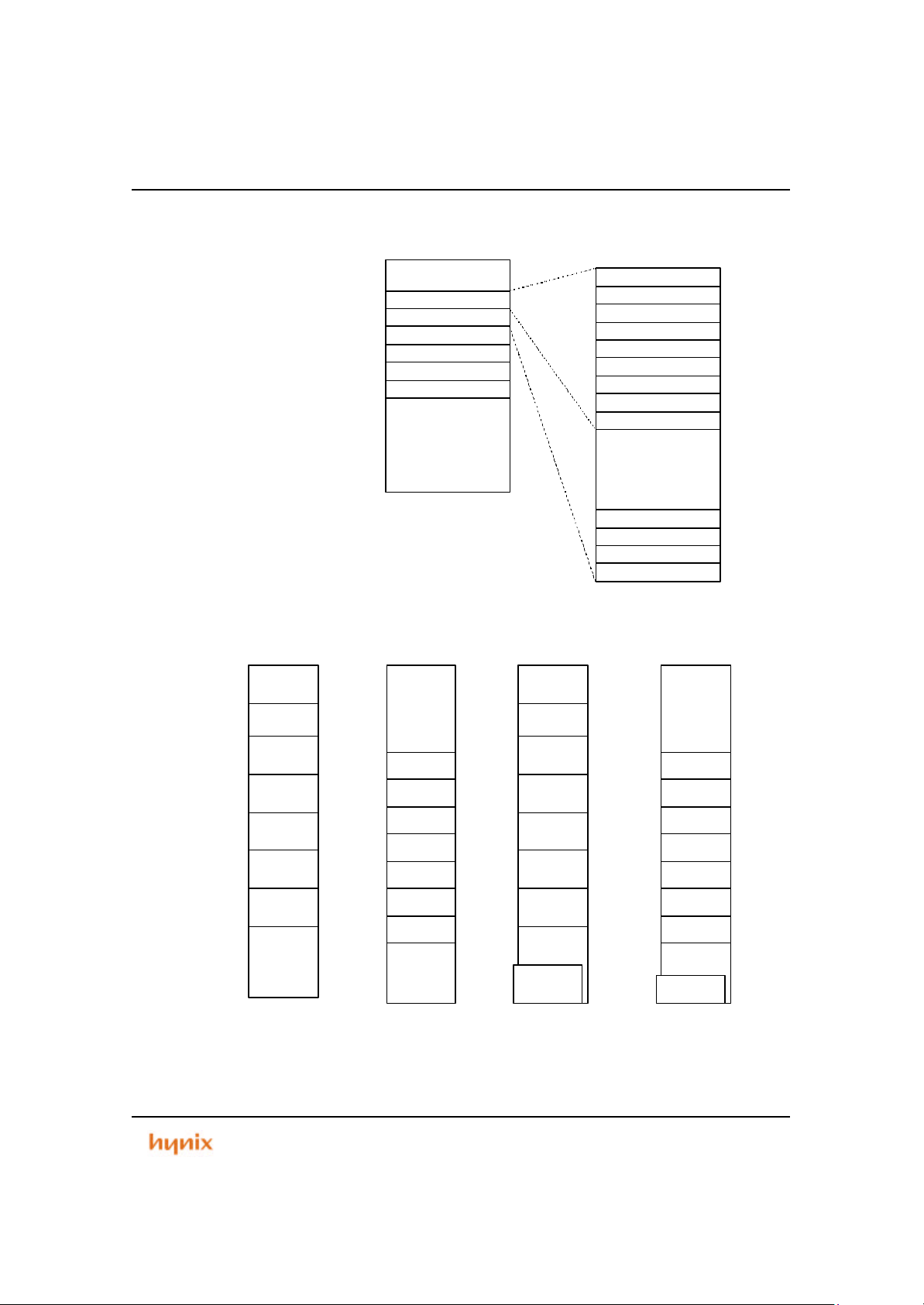

Figure 1.1 Package Outline ........................................................................................14

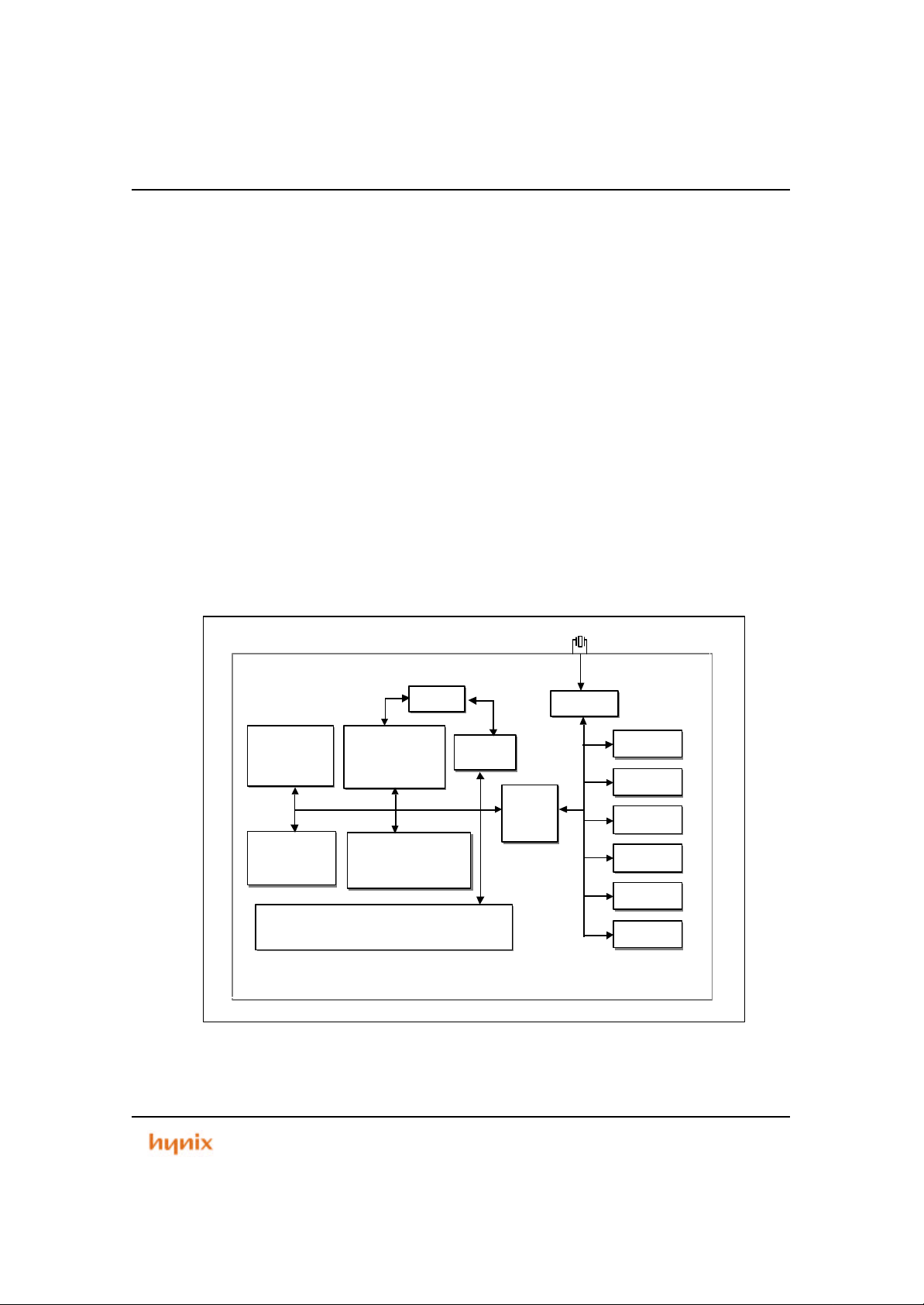

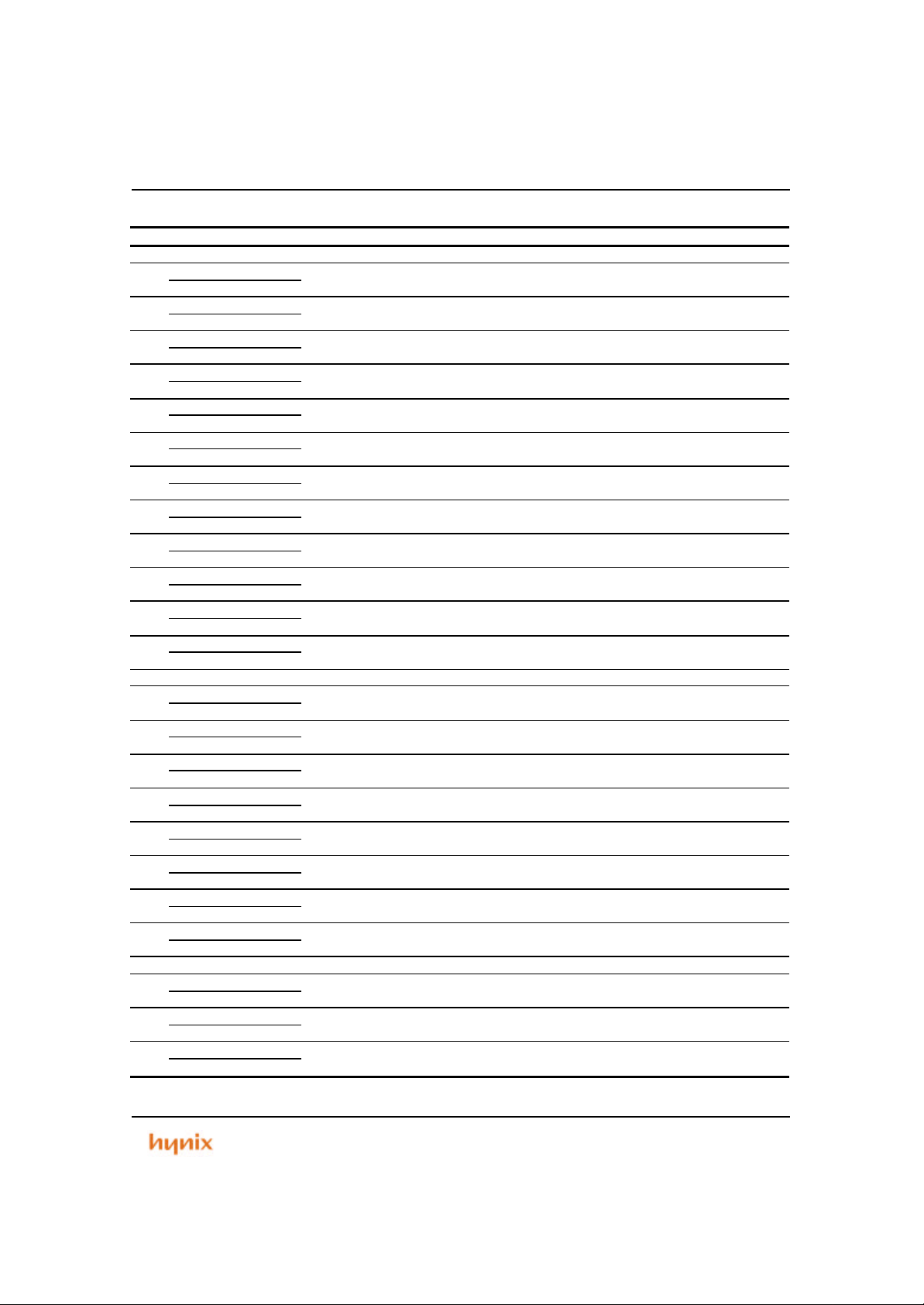

Figure 1.2 HMS39C7092 Block Diagram .................................................................... 15

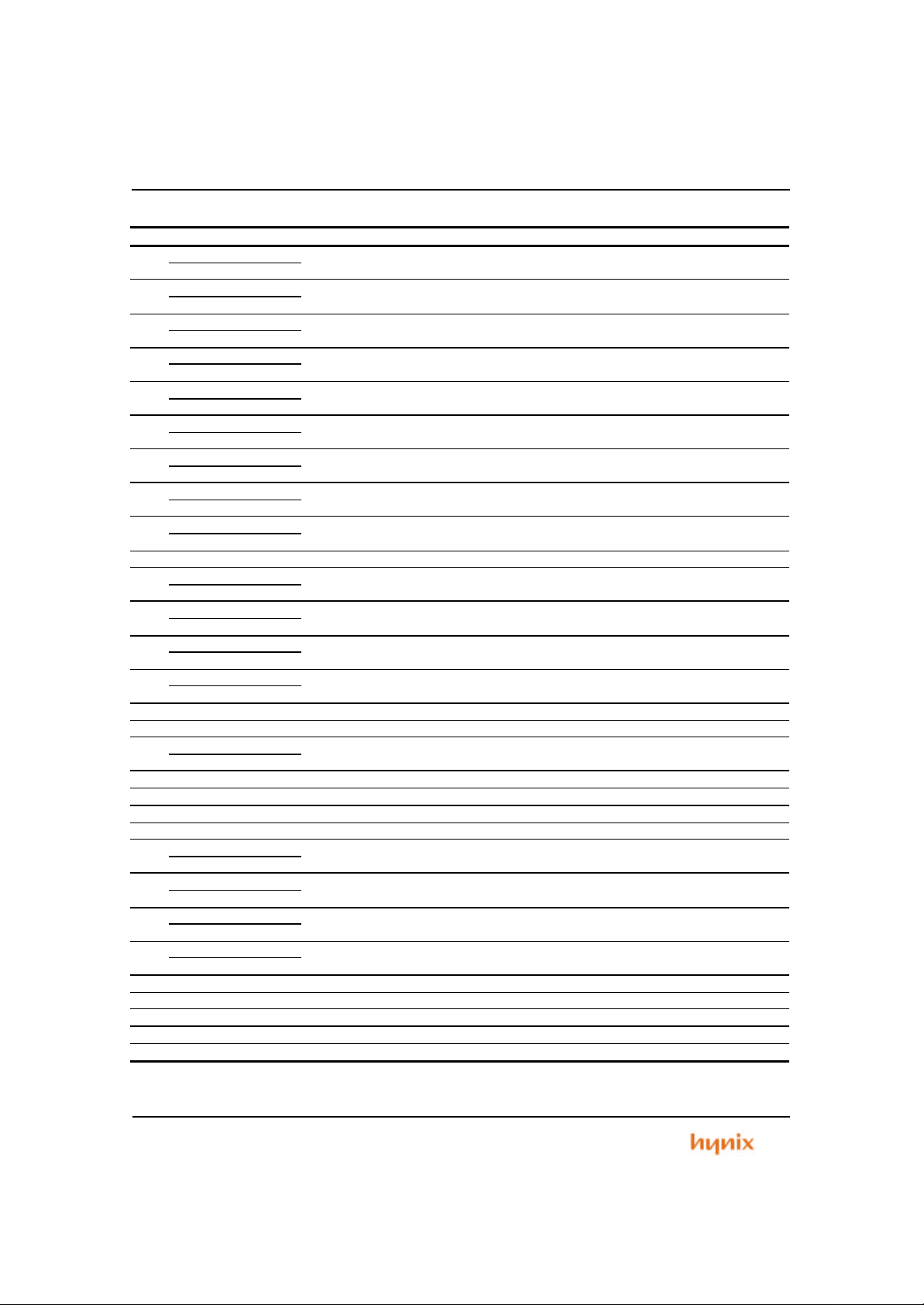

Figure 1.3 HMS39C7092 Memory Map....................................................................... 25

Figure 1.4 Memory Map of Mode 3 .............................................................................25

Figure 1.5 Memory Map of when Mode 4 and Mode 5 ................................................. 26

Figure 1.6 Memory Map of Mode 6 and Mode 7 .......................................................... 26

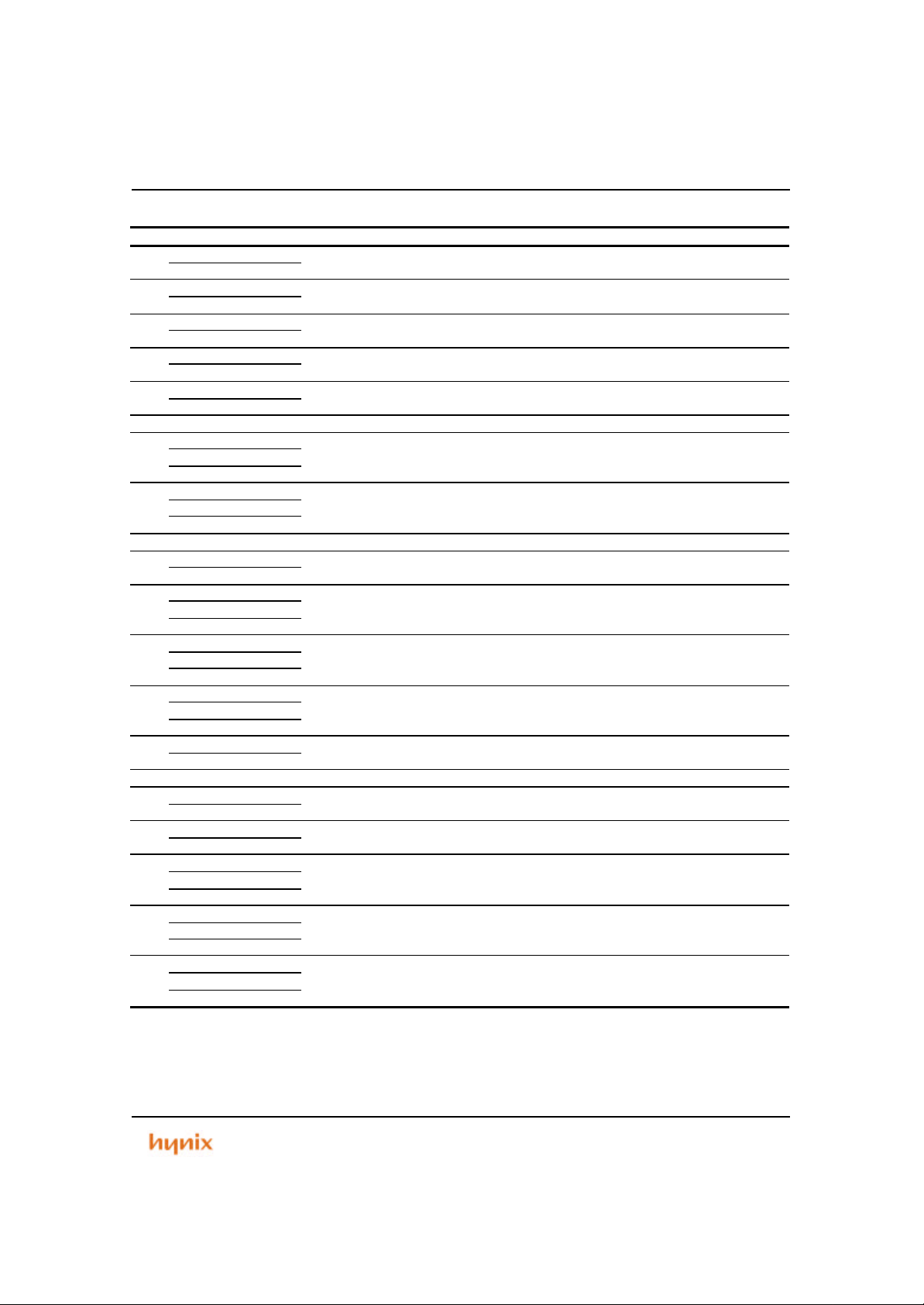

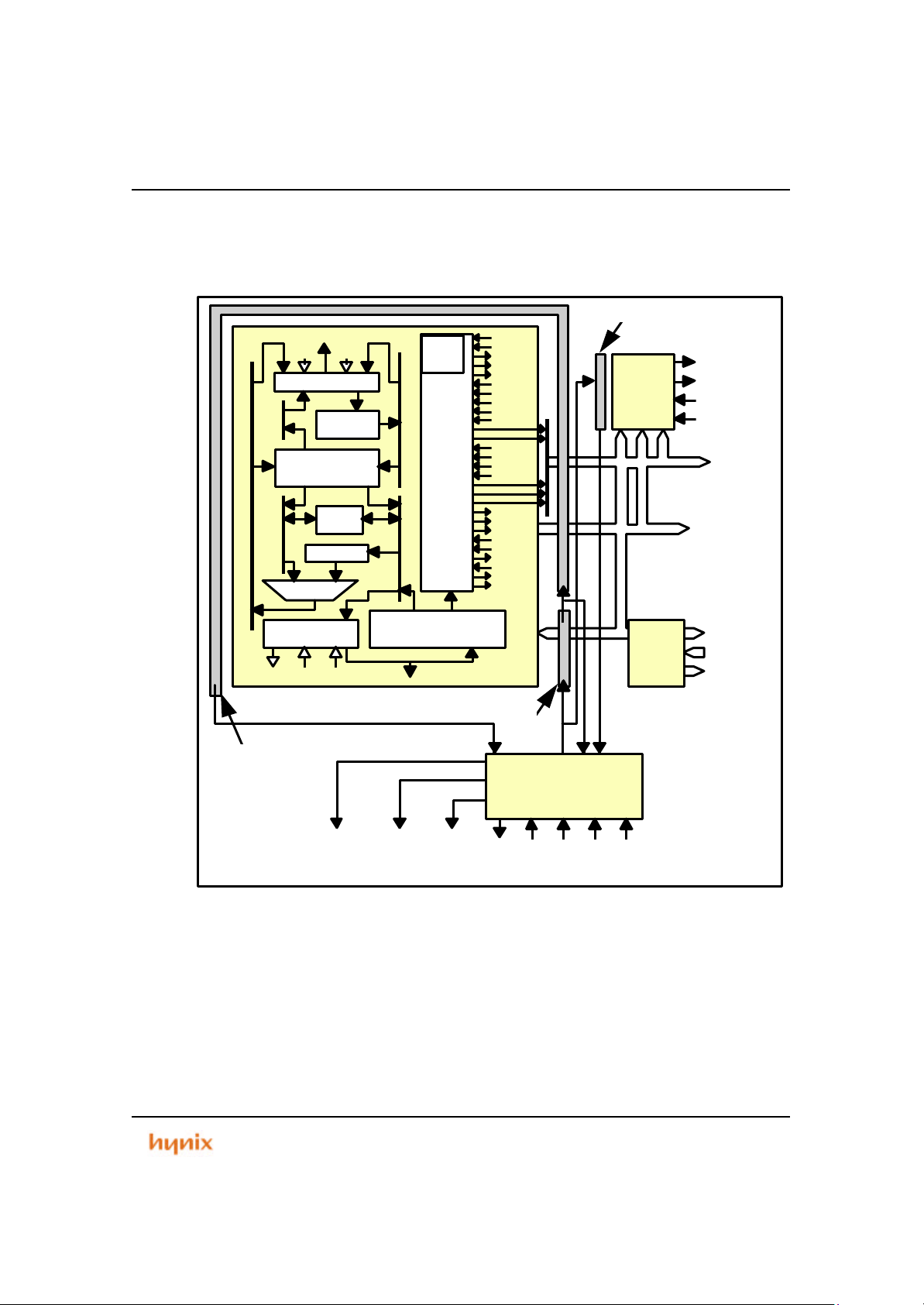

Figure 2.1 ARM7TDMI Core Block Diagram ................................................................29

Figure 2.2 ARM instruction set formats .......................................................................30

Figure 2.3 Register Organization in ARM state............................................................ 32

Figure 2.4 THUMB instruction set formats................................................................... 33

Figure 2.5 Register Organization in THUMB state .......................................................35

Figure 2.6 Mapping of THUMB state registers onto ARM state registers. ...................... 35

Figure 2.7 Program status register format ................................................................... 36

Figure 3.1 Block Diagram of the Bus Controller ........................................................... 48

Figure 3.2 Access Area Map for Each Operating Mode................................................ 52

Figure 3.3 Access Size and Data Alignment Control (8 -Bit Access Area) ......................54

Figure 3.4 Access Size and Data Alignment Control (16-Bit Access Area) .................... 55

Figure 3.5 Bus Control Signal Write Timing for 16 -Bit, 1-Wait (Word Access)................ 56

Figure 3.6 Bus Control Signal Read Timing for 16 -Bit, 1-Wait (Word Access)................56

Figure 3.7 Bus Control Signal Write Timing for 16 -Bit, 1-Wait (Half-word Access) ..........57

Figure 3.8 Bus Control Signal Read Timing for 16 -Bit, 1-Wait (Half-word Access)..........57

Figure 3.9 Bus Control Signal Write Timing for 16 -Bit, 1-Wait (Byte Access).................. 58

Figure 3.10 Bus Cont rol Signal Read Timing for 16-Bit, 1-Wait (Byte Access)................58

Figure 3.11 Bus Control Signal Write Timing for 16-Bit, 2-Wait (Word Access)............... 59

Figure 3.12 Bus Control Signal Read Timing for 16-Bit, 2-Wait (Word Access).............. 59

Figure 3.13 Bus Control Signal Write Timing for 16-Bit, 2-Wait (Half-Word Access)........ 60

Figure 3.14 Bus Control Signal Read Timing for 16-Bit, 2-Wait (Half-Word Access)....... 60

Figure 3.15 Bus Control Signal Write Timing for 16-Bit, 2-Wait (Byte Access)................ 61

Figure 3.16 Bus Control Signal Read Timing for 16-Bit, 2-Wait (Byte Access)................ 61

Figure 3.17 Example of Wait State Insertion Timing. .................................................... 62

Figure 3.18 Example of External Bus Master Operation ...............................................64

Figure 5.1 PMU Block Diagram .................................................................................. 74

Figure 5.2 Reset and Powe r Management State Machine............................................76

Figure 5.3 Power on Reset Timing Diagram ................................................................81

Figure 5.4 Watch Dog Timer Overflow Timing Diagram ................................................81

Figure 5.5 Soft Reset (from WDT) Timing Diagram ......................................................82

Figure 5.6 Soft Reset (from PMU) Timing Diagram ......................................................82

Figure 6.1 Interrupt Control Flow Diagram .................................................................. 84

Figure 7.1 Watchdog Timer Module Block Diagram ..................................................... 92

Figure 7.2 Operation in the Watchdog Timer Mode ......................................................94

Figure 7.3 Operation in the Interval Timer Mode ..........................................................95

Figure 7.4 Interrupt Clear in the Interval Timer Mode ................................................. 100

Figure 7.5 Interrupt Clear in the Watchdog Timer Mode with Reset Disable.................101

Figure 7.6 Interrupt Clear in the Watchdog Timer Mode with Power-on Reset ..............102

Figure 7.7 Interrupt Clear in the Watchdog Timer Mode with Manual Reset .................103

Figure 8.1 General-purpose Timer Unit Module Block Diagram ..................................106

Preliminary 7

Flash MCU(HMS39C7092)

Figure 8.2 Free-Running Counter Operation ............................................................. 115

Figure 8.3 Periodic Counter Operation ......................................................................116

Figure 8.4 Example of 0 Output/1 Output .................................................................. 117

Figure 8.5 Example of Toggle Output ........................................................................ 118

Figure 8.6 Compare Match Signal Output Timing ...................................................... 118

Figure 8.7 Input Capture Operation .......................................................................... 119

Figure 8.8 Synchronized Operation Example ............................................................120

Figure 8.9 PWM Mode Operation Example 1 ............................................................121

Figure 8.10 PWM Mode Operation Example 2...........................................................122

Figure 8.11 Reset-Synchronized PWM Mode Operation Example ...............................123

Figure 9.1 TOP BLOCK Diagram .............................................................................126

Figure 9.2 Internal UART Diagram ...........................................................................128

Figure 10.1 GPIO Block Diagram and PADS Connections(example for Port A and Port B)

.........................................................................................................................144

Figure 12.1 Block Diagram of Flash Memory ............................................................. 154

Figure 12.2 System Configuration When Using On -Board Boot Mode......................... 161

Figure 12.3 Boot Mode Execution Procedure ............................................................162

Figure 12.4 User Mode Execution Procedure ............................................................164

Figure 12.5 Flash Program & Program Verify Sequence ............................................167

Figure 12.6 Flash Pre-program & Pre -program Verify Sequence ................................169

Figure 12.7 Flash Erase & Erase Verify Sequence ....................................................171

Figure 12.8 Flash Erase Algorithm ...........................................................................172

Figure 12.9 Timing Diagram of Read ........................................................................175

Figure 12.10 Timing Diagram of Pre -Program/Program.............................................176

Figure 12.11 Timing Diagram of Erase ......................................................................176

Figure 12.12 Timing Diagram of Pre -Program/Program Verify ....................................177

Figure 12.13 Timing Diagram of Erase Verify ............................................................177

Figure 13.1 Block Diagram of A/D Converter.............................................................180

Figure 13.2 A/D converter Operation ........................................................................185

Figure 13.3 Example of Analog Input Circuit .............................................................188

Figure 13.4 A/D Converter Accuracy Definitions (1) ...................................................188

Figure 13.5 A/D Converter Accuracy Definitions (2) ...................................................189

Figure 14.1 The settling time of the crystal oscillator ..................................................197

Figure 14.2 Reset Input Timing ................................................................................197

Figure 14.3 The Write Timing Diagram of the Bus Controller ......................................198

Figure 14.4 The Read Timing Diagram of the Bus Controller ...................................... 198

Figure 14.5 Basic Bus Cycle with External Wait State................................................199

Figure 14.6 Bus Release Mode Timing .....................................................................199

8 Preliminary

Flash MCU(HMS39C7092)

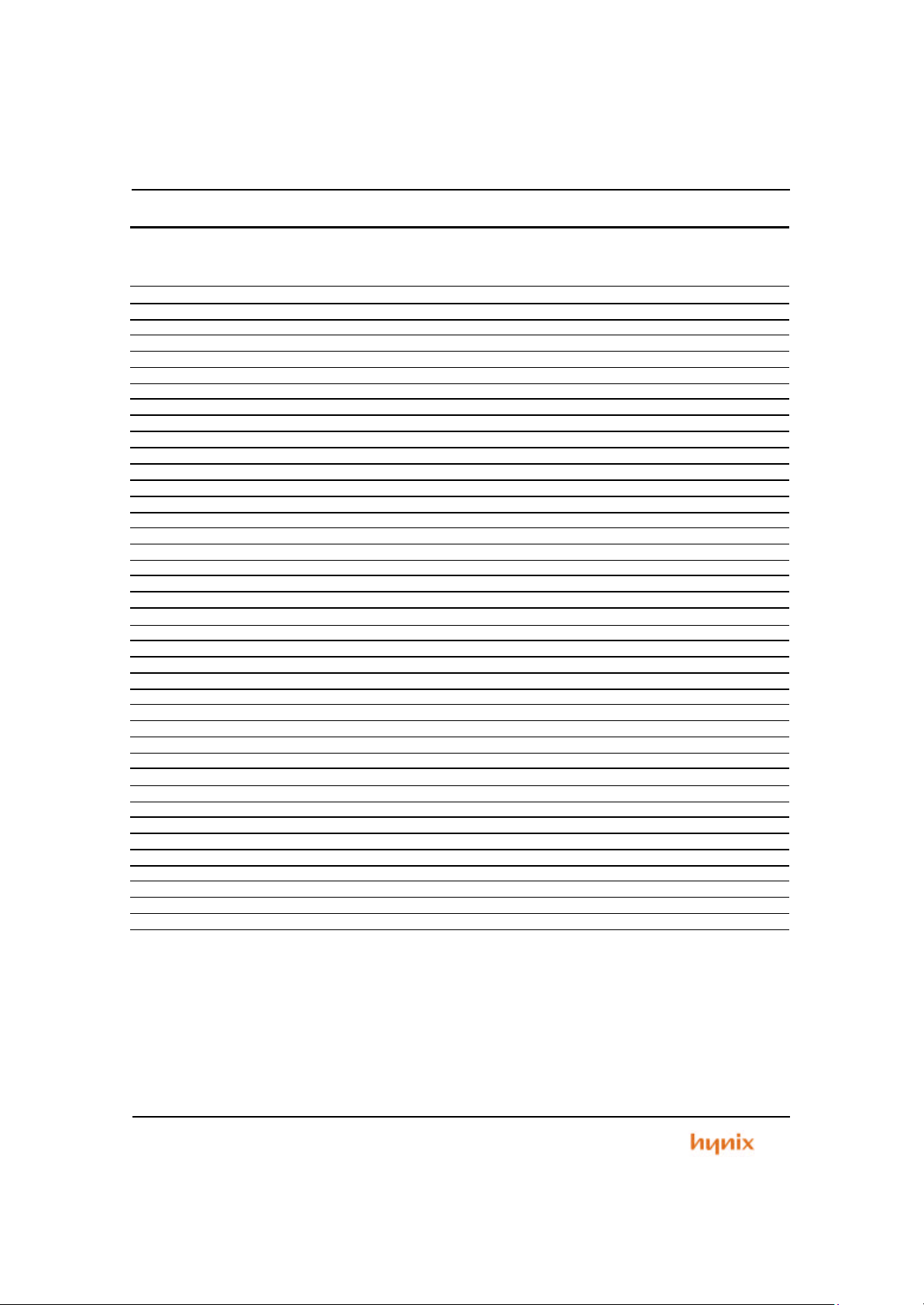

Tables

Table 1.1 Pin Descriptions ......................................................................................... 16

Table 1.1 Pin Descriptions (Continued) ....................................................................... 17

Table 1.1 Pin Descriptions (Continued) ....................................................................... 18

Table 1.1 Pin Descriptions (Continued) ....................................................................... 19

Table 1.1 Pin Descriptions (Continued) ....................................................................... 20

Table 1.2 HMS39C7092 Operation modes .................................................................. 21

Table 1.3 Pin assignment by mode .............................................................................22

Table 1.3 Pin assignment by mode (continued) ........................................................... 23

Table 1.3 Pin assignment by mode (continued) ........................................................... 24

Table 2.1 The ARM Instruction set ..............................................................................31

Table 2.2 THUMB instruction set opcodes ...................................................................34

Table 2.3 Condition code summary .............................................................................36

Table 2.4 PSR mode bit values .................................................................................. 38

Table 3.1 Bus Controller Pins ..................................................................................... 49

Table 3.2 BUS Controller Register Map .......................................................................50

Table 3.3 Byte Lane condition by XA[0] .......................................................................55

Table 4.1 Pin Function Descriptions............................................................................ 66

Table 4.2 Memory map of the MCU Controller .............................................................67

Table 4.3 MCU Controller Initial values in each mode .................................................. 67

Table 5.1 Register Map of the PMU ............................................................................ 77

Table 6.1 Interrupt Controller Default Setting Value...................................................... 85

Table 6.2 Memory Map of the Interrupt Controller ........................................................ 87

Table 6.3 Interrupt Source Trigger Mode .....................................................................88

Table 7.1 Memory Map of the Watchdog Timer APB Peripheral.................................... 96

Table 7.2 Internal Counter Clock Sources (SYSCLK = 40 MHz).................................... 98

Table 8.1 Timer Global Control Register Map ............................................................108

Table 8.2 Timer Channel Control Register Map .........................................................108

Table 8.3 Timer Channel Starting Address ................................................................108

Table 9.1 Signal Descriptions ...................................................................................127

Table 9.2 UART Register Address Map (0x1500 in UART1) .......................................129

Table 9.3 UART Register Reset Values .....................................................................129

Table 9.4a Divisor Values for each Baud rate (CLK=1.8432MHz)................................133

Tab le 9.4b Divisor Values for each Baud rate (CLK=3.6864MHz)................................ 133

Table 9.5 Interrupt Control Functions ........................................................................138

Table 9.6 Summary of Registers ............................................................................... 142

Table 10.1 GPIO Register Memory Map ....................................................................145

Table 12.1 Operating mode......................................................................................153

Table 12.2 Signal description of Figure 12.1(BUS Interface) ....................................... 155

Table 12.3 Flash Memory Registers ..........................................................................156

Table 12.4 Control Register ...................................................................................... 158

Table 12.5 Erase Block Register ...............................................................................159

Table 12.6 Status & Power Register .........................................................................160

Table 12.7 FR_SEL Value for access to internal Register...........................................173

Table 12.8 Setting for Register read/write..................................................................173

Table 12.9 Erase Block Register ...............................................................................174

Table 12.10 Setting for Flash PROM read/write ......................................................... 175

Preliminary 9

Flash MCU(HMS39C7092)

Table 12.11 DC Characteristics ................................................................................178

Table 12.12 AC Characteristics ................................................................................178

Table 13.1 A/D Converter Pins .................................................................................181

Table 13.2 Summarizes the A/D convert er’s registers................................................182

Table 14.1 Absolute Maximum Ratings - Preliminary -............192

Table 14.2 Recommended Operating Conditions - Preliminary - .............192

Table 14.3 DC Characteristics - Preliminary - ..........193

Table 14.4 IO Circuits with pull-ups - Preliminary - ...........193

Table 14.5 IO Circuits with pull-downs - Preliminary - ............193

Table 14.6 Clock Timing - Preliminary -...........194

Table 14.7 Control Signal Timing - Preliminary - ...........194

Table 14.8 Bus Timing - Preliminary -..........195

Table 14.9 Operating Conditions of the AD Conversion - Preliminary -.............196

Table 14.10 Electrical characteristics of the AD converter - Preliminary -.............196

10 Preliminary

Flash MCU(HMS39C7092)

Preliminary 11

Flash MCU(HMS39C7092)

12 Preliminary

Flash MCU(HMS39C7092) Introduction

Chapter 1

Introduction

Preliminary 13

Introduction Flash MCU(HMS39C7092)

1.1 General Description

The 16bit MCU with embedded flash memory for optical storage is the first member

of Hynix Micro Electronics 16/32bit MCU Family of high performance microcontroller

units (MCUs). This family includes a series of peripherals from which numerous

MCUs are assembled. Th is MCU contains extensive peripherals : 192Kbytes flas h

memory, 4K bytes SRAM, 6 channel 16bit Timer, Watch Dog Timer, 2 channel UART,

Programmable Priority Interrupt Controller, 81bits PIO, BUS Controller including Chip

select logic, which is On-Chip Modular Architecture (using AMBA).

nBREQ/P6

nBACK/P6

MODE

1

2

MODE

MODE

0

VDD

XTALOUT

XTALIN

VSS

nTRST/P9

nRES

7

nHWR/P6

nLWR/P6

nRD/P6

nAS/P6

3

4

5

6

CLKO/P6

nSTBY

7

nWAIT/P6

A

A

A

A

A

A

19

/P53VSS

0

1

2

14

15

16

17

18

/P2

/P2

/P5

/P5

/P5

6

7

0

1

2

AVDD

AV

AN0/P7

AN0/P7

AN0/P7

AN0/P7

AN0/P7

TIOCA5/nIRQ6/P7

TIOCB5/nIRQ7/P7

nCS3/nIRQ1/P8

nCS2/nIRQ2/P8

nCS1/nIRQ3/P8

TCLKC/TCIOA0/PA

TCLKD/TCIOB0/PA

VSS

nIRQ0/P8

nCS0/P8

VSS

TCLKA/PA

TCLKB/PA

A23/TIOCA1/PA

A22/TIOCB1/PA

A21/TIOCA2/PA

A20/TIOCB2/PA

75

74

73

72

71

70

69

68

76

REF

P7

77

78

0

79

1

80

2

81

3

82

4

83

84

6

85

7

86

5

87

0

88

1

89

2

90

3

91

4

92

93

0

94

1

95

2

96

3

97

4

98

5

99

6

100

7

HMS39C7092

2001.02

1

2

3

4

5

6

7

8

0

1

2

3

5

/PB

/PB

4

4

/TIOCA

/TIOCB

5

4

6

TDI/PB

TMS/PB4TDO/PB

VDD

/PB

/PB

3

3

/TIOCA

/TIOCB

7

6

67

66

9

7

TCK/PB

10

XP9

63

65

64

62

61

60

59

58

57

56

55

54

53

52

51

A13/P2

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

11

12

13

14

15

16

17

18

19

20

21

0

2

4

1

/P9

0

RxD

/P9

1

TxD

3

/P9

1

RxD

/P9

4

nIRQ

5

/P9

5

nIRQ

/P4

D

0

0

2

3

/P4

/P4

/P4

0

0

2

3

D

D

D

6

/P9

VSS

0

TxD

22

VSS

23

/P4

D

26

24

25

4

5

6

/P4

/P4

4

5

6

D

D

A12/P2

A11/P2

A10/P2

A9/P2

A8/P2

VSS

A7/P1

A6/P1

A5/P1

A4/P1

A3/P1

A2/P1

A1/P1

A0/P1

VDD

D15/P3

D14/P3

D13/P3

D12/P3

D11/P3

D10/P3

D9/P3

/P3

D8

D7/P4

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

Figure 1.1 Package Outline

14 Preliminary

Flash MCU(HMS39C7092) Introduction

1.2 Feature

• On-Chip Modular Architecture (using AMBA)

• Utilizes the ARM7TDMI 32/16bit RISC Family

• 192Kbyte flash memory

• 4Kbyte internal SRAM

• 8/16-bit external Data Bus

• Eight Programmable Chip Select Output s with external wait input

• Low Power Consumption using Power Management Unit

• Fully static operation : Max. 50MHz

• Programmable Priority Interrupt Controller (8 external sources)

• Six 16bit Multi Function Timers/Counters for General Purpose Applications

• One 8bit Watch Dog Timer (WDT)

• Two UARTs (Universal Asynchronous Receiver Transmitter) compatible with

16C550 UART

• Programmable Input/Output ports (81-bits)

• 100 TQFP Package

BUS

BUS

Controller

Controller

SRAM

SRAM

4kbyte

4kbyte

Arbiter

Arbiter

ARM7TDMI

ARM7TDMI

ASB (Max. 50MHz)

Flash Memory

Flash Memory

192kbyte

192kbyte

Multi-Function Pin MUX

Multi-Function Pin MUX

TIC*

TIC*

APB

APB

Bridge

Bridge

* TIC : Test Interface Controller

PMU

PMU

Figure 1.2 HMS39C7092 Block Diagram

Max. 50MHz

PIO

INTC

INTC

WDT

WDT

TIMER

TIMER

UART

UART

ADC

ADC

PIO

Preliminary 15

Introduction Flash MCU(HMS39C7092)

1.3 Pin Descriptions

Table 1.1 Pin Descriptions

PIN SYMBOL DIR DESCRIPTION

1 VDD - Power Supply 3.3V

nCS7 O External Chip Selection Number 7

2

TCIOA3 I/O PWM output, Compare match output of Reg.A and signal capture input of Timer Ch3

PB0 I/O General purpose input output of port B bit0

nCS6 O External Chip Selection Number 6

3

TCIOB3 I/O PWM output, Compare match output of Reg.B and signal capture input of Timer Ch3

PB1 I/O General purpose input output of port B bit 1

nCS5 O External Chip Selection Number 5

4

TIOCA4 I/O PWM output, Compare match output of Reg.A and signal capture input of Timer Ch4

PB2 I/O General purpose input output of port B bit2

nCS4 O External Chip Selection Number 4

5

TIOCB4 I/O PWM output, Compare match output of Reg.B and signal capture input of Timer Ch4

PB3 I/O General purpose input output of port B bit3

6

7

8

9

10 TVPPD I 5Vinput for the use of Programming and Erasing of the Flash Memory

11 VSS - Power ground

12

13

14

15

16

17

18

19

20

21

TMS I JTAG Test Mode Selection

PB4 I/O General purpose input output of port B bit4

TDO O JTAG Test Data Output

PB5 I/O General purpose input output of port B bit5

TDI I JTAG Test Data Input

PB6 I/O General purpose input output of port B bit6

TCK I JTAG Test Clock

PB7 I/O General purpose input output of port B bit7

TxD0 O Transmit Data of UART Ch0

P90 I/O General purpose input output of port 9 bit 0

RxD0 O Receive Data of UART Ch0

P91 I/O General purpose input output of port 9 bit 1

TxD1 O Transmit Data of UART Ch1

P92 I/O General purpose input output of port 9 bit 2

RxD1 O Receive Data of UART Ch1

P93 I/O General purpose input output of port 9 bit 3

nIRQ4 I External Interrupt Request number 4

P94 I/O General purpose input output of port 9 bit 4

nIRQ5 I External Interrupt Request number 5

P95 I/O General purpose input output of port 9 bit 5

D0 I/O External Data Bus bit 0

P40 I/O General purpose input output or port 4 bit 0

D1 I/O External Data Bus bit 1

P41 I/O General purpose input output or port 4 bit 1

D2 I/O External Data Bus bit 2

P42 I/O General purpose input output or port 4 bit 2

D3 I/O External Data Bus bit 3

P43 I/O General purpose input output or port 4 bit 3

16 Preliminary

Flash MCU(HMS39C7092) Introduction

Table 1.1 Pin Descriptions (Continued)

PIN SYMBOL DIR DESCRIPTION

22 VSS - Power ground

23

24

25

26

27

28

29

30

31

32

33

34

35 VDD - Power Supply 3.3V

36

37

38

39

40

41

42

43

44 VSS - Power ground

45

46

47

D4 I/O External Data Bus bit 4

P44 I/O General purpose input output or port 4 bit 4

D5 I/O External Data Bus bit 5

P45 I/O General purpose input output or port 4 bit 5

D6 I/O External Data Bus bit 6

P46 I/O General purpose input output or port 4 bit 6

D7 I/O External Data Bus bit 7

P47 I/O General purpose input output or port 4 bit 7

D8 I/O External Data Bus bit 8

P30 I/O General purpose input output or port 3 bit 0

D9 I/O External Data Bus bit 9

P31 I/O General purpose input output or port 3 bit 1

D10 I/O External Data Bus bit 10

P32 I/O General purpose input output or port 3 bit 2

D11 I/O External Data Bus bit 11

P33 I/O General purpose input output or port 3 bit 3

D12 I/O External Data Bus bit 12

P34 I/O General purpose input output or port 3 bit 4

D13 I/O External Data Bus bit 13

P35 I/O General purpose input output or port 3 bit 5

D14 I/O External Data Bus bit 14

P36 I/O General purpose input output or port 3 bit 6

D15 I/O External Data Bus bit 15

P37 I/O General purpose input out put or port 3 bit 7

A0 O External Address Bus bit 0

P10 I/O General purpose input output or port 1 bit 0

A1 O External Address Bus bit 1

P11 I/O General purpose input output or port 1 bit 1

A2 O External Address Bus bit 2

P12 I/O General purpose input output or port 1 bit 2

A3 O External Address Bus bit 3

P13 I/O General purpose input output or port 1 bit 3

A4 O External Address Bus bit 4

P14 I/O General purpose input output or port 1 bit 4

A5 O External Address Bus bit 5

P15 I/O General purpose input output or port 1 bit 5

A6 O External Address Bus bit 6

P16 I/O General purpose input output or port 1 bit 6

A7 O External Address Bus bit 7

P17 I/O General purpose input output or port 1 bit 7

A8 O External Address Bus bit 8

P20 I/O General purpose input output or port 2 bit 0

A9 O External Address Bus bit 9

P21 I/O General purpose input output or port 2 bit 1

A10 O External Address Bus bit 10

P22 I/O General purpose input output or port 2 bit 2

Preliminary 17

Introduction Flash MCU(HMS39C7092)

Table 1.1 Pin Descriptions (Continued)

PIN SYMBOL DIR DESCRIPTION

48

49

50

51

52

53

54

55

56

57 VSS - Power ground

58

59

60

61

62 nSTBY O Standby mode signal. Power Down mode indicating

63 nRES I External Reset input

64

65 VSS - Power ground

66 XTALOUT O Crystal feedback output

67 XTALIN I Crystal or External Oscillator input

68 VDD - Power Supply 3.3V

69

70

71

72

73 MODE0 I MODE bit 0

74 MODE1 I MODE bit 1

75 MODE2 I MODE bit 2

76 AVDD - Analog Power Supply 3.3V

77 AVREF - ADC Reference Voltage

A11 O External Address Bus bit 11

P23 I/O General purpose input output or port 2 bit 3

A12 O External Address Bus bit 12

P24 I/O General purpose input output or port 2 bit 4

A13 O External Address Bus bit 13

P25 I/O General purpose input output or port 2 bit 5

A14 O External Address Bus bit 14

P26 I/O General purpose input output or port 2 bit 6

A15 O External Address Bus bit 15

P27 I/O General purpose input output or port 2 bit 7

A16 O External Address Bus bit 16

P50 I/O General purpose input output of port 5 bit 0

A17 O External Address Bus bit 17

P51 I/O General purpose input output of port 5 bit 1

A18 I External Address Bus bit 18

P52 I/O General purpose input output of port 5 bit 2

A19 O External Address Bus bit 19

P53 I/O General purpose input output of port 5 bit 3

nWAIT I External BUS cycle wait signal

P60 I/O General purpose input output of port 6 bit 0

nBREQ I External BUS Request

P61 I/O General purpose input output of port 6 bit 1

nBACK I External BUS Acknowledge

P62 I/O General purpose input output of port 6 bit 2

CLKO O BUS Clock Output

P67 I/O General purpose input output of port 6 bit 7

nTRST I JTAG Test Reset input

P97 I/O General purpose input output of port 9 bit 7

nAS O External Address Bus strobe

P63 I/O General purpose input output of port 6 bit 3

nRD O External Bus Read

P64 I/O General purpose input output of port 6 bit 4

nHWR O External upper 8 bit data bus write

P65 I/O General purpose input output of port 6 bit 5

nLWR O External lower 8 bit data bus write

P66 I/O General purpose input output of port 6 bit 6

18 Preliminary

Flash MCU(HMS39C7092) Introduction

Table 1.1 Pin Descriptions (Continued)

PIN SYMBOL DIR DESCRIPTION

78

79

80

81

82

83 VSS - Power ground

85

86 P75 I/O General purpose input output of port 7 bit 5

87

89

91

92 VSS - Power ground

93

94

95

96

97

P70 O General purpose output of port 7 bit 0

AN0 I ADC Channel 0 input

P71 O General purpose output of port 7 bit 1

AN1 I ADC Channel 1 input

P72 O General purpose output of port 7 bit 2

AN2 I ADC Channel 2 input

P73 O General purpose output of port 7 bit 3

AN3 I ADC Channel 3 input

P74 O General purpose output of port 7 bit 4

AN4 I ADC Channel 4 input

TIOCA5 I/O PWM output, Compare match output of Reg.A and signal capture input of Timer Ch5

nIRQ6 I External Interrupt Request number 6 84

P76 I/O General purpose input output of port 7 bit 6

TIOCB5 I/O PWM output, Compare match output of Reg.B and signal capture input of Timer Ch5

nIRQ7 I External Interrupt Request number 7

P77 I/O General purpose input output of port 7 bit 7

nIRQ0 I External Interrupt Request number 0

P80 I/O General purpose input output of port 8 bit 0

nCS3 O External Chip Selection Number 3

nIRQ1 I External Interrupt Request number 1 88

P81 I/O General purpose input output of port 8 bit 1

nCS2 O External Chip Selection Number 2

nIRQ2 I External Interrupt Request number 2

P82 I/O General purpose input output of port 8 bit 2

nCS1 O External Chip Selection Number 1

nIRQ3 I External Interrupt Request number 3 90

P83 I/O General purpose input output of port 8 bit 3

nCS0 O External Chip Selection Number 0

P84 I/O General purpose input output of port 8 bit 4

TCLKA I External timer input clock A

PA0 I/O General purpose input output of port A bit 0

TCLKB I External timer input clock B

PA1 I/O General purpose input output of port A bit 1

TCLKC I External timer input clock C

TIOCA0 I/O PWM output, Compare match output of Reg.A and signal capture input of Timer Ch0

PA2 I/O General purpose input output of port A bit 2

TCLKD I External timer input clock D

TIOCB0 I/O PWM output, Compare match output of Reg.B and signal capture input of Timer Ch0

PA3 I/O General purpose input output of port A bit 3

A23 O External Address Bus bit 23

TIOCA1 I/O PWM output, Compare mat ch output of Reg.A and signal capture input of Timer Ch1

PA4 I/O General purpose input output of port A bit 4

Preliminary 19

Introduction Flash MCU(HMS39C7092)

Table 1.1 Pin Descriptions (Continued)

PIN SYMBOL DIR DESCRIPTION

98

99

100

A22 O External Address Bus bit 22

TIOCB1 I/O PWM output, Compare match output of Reg.B and signal capture input of Timer Ch1

PA5 I/O General purpose input output of port A bit 5

A21 O External Address Bus bit 21

TIOCA2 I/O PWM output, Compare match output of Reg.A and signal capture input of Timer Ch2

PA6 I/O General purpose input output of port A bit 6

A20 O External Address Bus bit 20

TIOCB2 I/O PWM output, Compare match output of Reg.B and signal capture input of Timer Ch2

PA7 I/O General purpose input output of port A bit 7

20 Preliminary

Flash MCU(HMS39C7092) Introduction

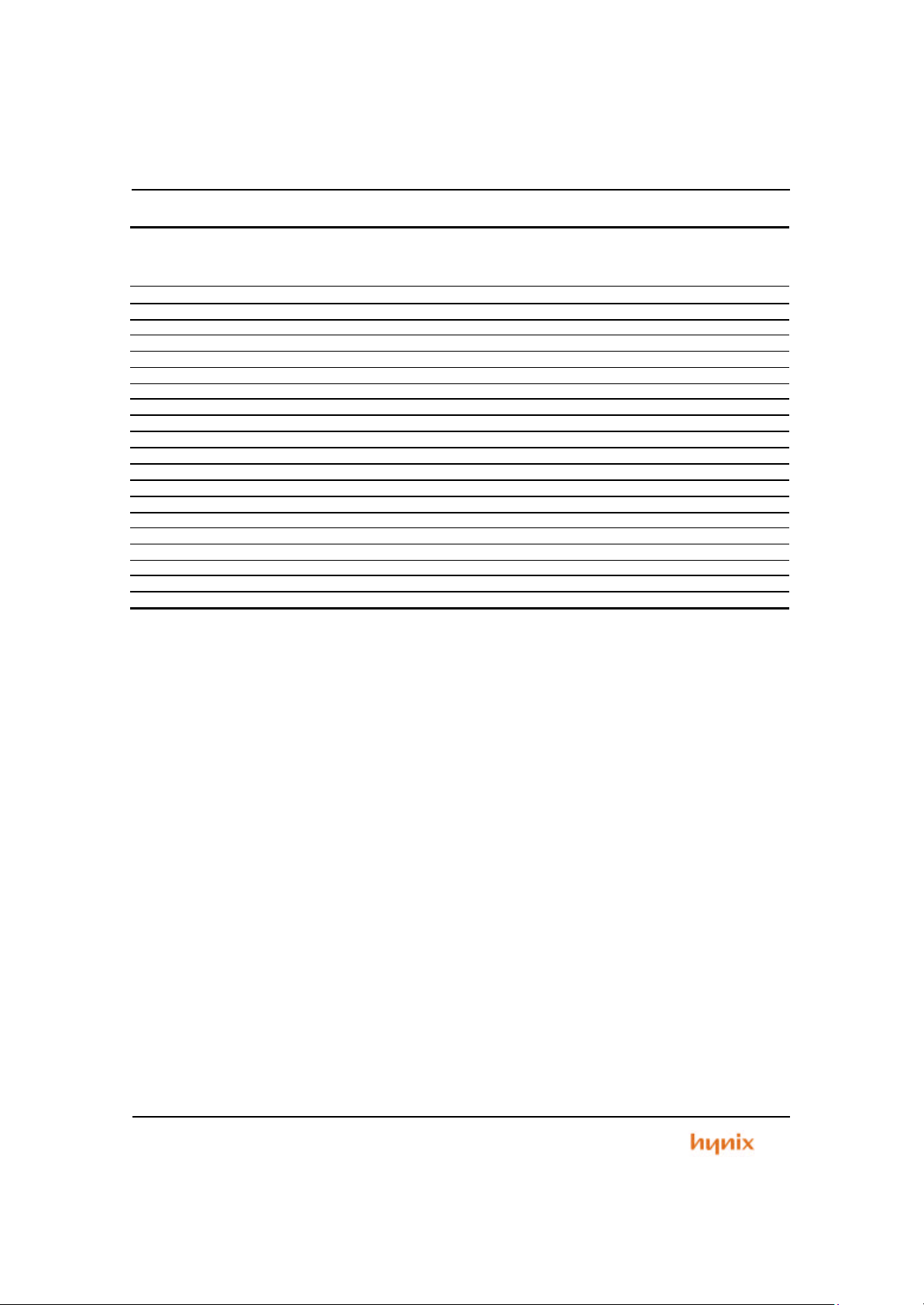

1.4 Operation Mode description

HMS39C7092 is Flash Memory-embedded ARM microcontroller. It has six-operation

modes shown in Table 1.2. HMS39C7092 External pin function is changed by setting

external MODE pin or configuring the PIN MUX registers. The pin assignment by

mode is shown in Table 1.3 . Especially changing mode causes memory remap for

appropriate mode. Figure 1.3 shows default memory map and the memory maps of

respective modes are shown in Figure 1.4, Figure 1.5 and Figure 1.6.

The Mode definition is listed as follows:

Table 1.2 HMS39C7092 Operation modes

MODE MODE DESCRIPTION

0,1 Reserved for Test

2 External 8-bit data bus with 16MBytes of Address Range

3 External 16-bit data bus with 16MBytes of Address Range

4 Flash-boot mode with 16-bit data bus

5 Flash-boot mode (micro-computer mode)

6 UART-boot mode with 16-bit data bus

7 UART-boot mode (micro-computer mode)

Preliminary 21

Introduction Flash MCU(HMS39C7092)

Table 1.3 Pin assignment by mode

MODE 2 MODE 3 MODE 4 MODE 6 MODE 5 MODE 7 PIN

External

8bit BUS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

VDD

nCS7

nCS6

nCS5

nCS4

TMS

TDO

TDI

TCK

TVPPD

VSS

TxD0

RxD0

TxD1

RxD1

nIRQ4

nIRQ5

D0

D1

D2

D3

VSS

D4

D5

D6

D7

P30 D8

P31 D9

P32 D10

P33 D11

P34 D12

P35 D13

P36 D14

P37 D15

VDD

A0

A1

A2

A3

A4

External

16bit BUS

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

Flash boot mode

with 16bit BUS

ß ß

ß ß

ß ß

ß ß

ß ß

ß ß

ß ß

ß ß

UART boot mode

with 16bit BUS

Flash boot mode

(MICOM mode)

TIOCA3

TIOCB3

TIOCA4

TIOCB4

P40

P41

P42

P43

P44

P45

P46

P47

P30

P31

P32

P33

P34

P35

P36

P37

P10

P11

P12

P13

P14

UART boot mode

(MICOM mode)

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

22 Preliminary

Flash MCU(HMS39C7092) Introduction

Table 1.3 Pin assignment by mode (continued)

MODE2 MODE3 MODE4 MODE6 MODE5 MODE7 PIN

No.

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

73

75

76

77

78

79

80

External

8bit BUS

A5

A6

A7

VSS

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

VSS

nWAIT

nBREQ

nBACK

CLKO

nSTBY

nRES

nTRST

VSS

XTALOUT

XTALIN

VDD

nAS

nRD

nHWR

nLWR

MODE0

MODE1

MODE2

AVDD

AVREF

AN0

AN1

AN2

External

16bit BUS

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

Flash boot mode

with 16bit BUS

UART boot mode

with 16bit BUS

Flash boot mode

(MICOM mode)

P15

P16

P17

P20

P21

P22

P23

P24

P25

P26

P27

P50

P51

P52

P53

P60

P61

P62

P67

nSTBY

nRES

nTRST

P63

P64

P65

P66

UART boot mode

(MICOM mode)

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

ß

Preliminary 23

Introduction Flash MCU(HMS39C7092)

Table 1.3 Pin assignment by mode (continued)

MODE2 MODE3 MODE4 MODE6 MODE5 MODE7 PIN

No.

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

External

8bit BUS

AN3

AN4

VSS

TIOCA5

TIOCB5

P75

nIRQ0

nCS3

nCS2

nCS1

nCS0

VSS

TCLKA

TCLKB

TCLKC

TCLKD

A23

A22

A21

A20

External

16bit BUS

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß ß ß ß

ß ß

ß ß

ß ß

ß ß

Flash boot mode

with 16bit BUS

UART boot mode

with 16bit BUS

TIOCA1

TIOCB1

TIOCA2

TIOCB2

Flash boot mode

(MICOM mode)

P81

P82

P83

P84

ß ß

ß ß

ß ß

ß ß

UART boot mode

(MICOM mode)

ß

ß

ß

ß

24 Preliminary

Flash MCU(HMS39C7092) Introduction

1.5 Memory Map

0xFFFF FFFF

0x0900 2000

0x0900 1FFF

0x0900 1000

0x0900 0FFF

0x0900 0000

0x0804 FFFF

0x0804 0000

0x0803 FFFF

0x0803 0000

0x0802 FFFF

0x0800 0000

0x07FF FFFF

0x0000 0000

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

0x07FF FFFF

0x0700 0000

0x06FF FFFF

0x0600 0000

0x05FF FFFF

0x0500 0000

0x04FF FFFF

0x0400 0000

0x03FF FFFF

0x0300 0000

0x02FF FFFF

0x0200 0000

0x01FF FFFF

0x0100 0000

0x00FF FFFF

nCS0

0x0000 0000

Default.

SM=0 in the PMU register.

Reserved

Reserved

APB Register

ASB Register

Reserved

On Chip

BOOT ROM

On Chip

SRAM(4KB)

FLASH

nCS0 ~ nCS7

Chip Select

Area

Reserved

ARM7TEST

Figure 1.3 HMS39C7092 Memory Map

0x07FF FFFF

nCS7

Reserved

0x0080 0000

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

SM=1 in the PMU register. Remap mode (Remap =1)

0x007F FFFF

0x0070 0000

0x006F FFFF

0x0060 0000

0x005F FFFF

0x0050 0000

0x004F FFFF

0x0040 0000

0x003F FFFF

0x0030 0000

0x002F FFFF

0x0020 0000

0x001F FFFF

0x0010 0000

0x000F FFFF

0x0000 0000

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

On Chip

SRAM

SM=0 in the PMU register.

0x07FF FFFF

0x0700 0000

0x06FF FFFF

0x0600 0000

0x05FF FFFF

0x0500 0000

0x04FF FFFF

0x0400 0000

0x03FF FFFF

0x0300 0000

0x02FF FFFF

0x0200 0000

0x01FF FFFF

0x0100 0000

0x00FF FFFF

0x0000 1000

0x0000 0FFF

0x0000 0000

ADC

GPIO

UART1

UART0

TIMER

INTC

WDT

PMU

FMI

SMI

MCUC

Reserved

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

On Chip

SRAM

Remap mode (Remap =1)

SM=1 in the PMU register.

0x0900 1FFF

0x0900 1800

0x0900 17FF

0x0900 1700

0x0900 16FF

0x0900 1600

0x0900 15FF

0x0900 1500

0x0900 14FF

0x0900 1400

0x0900 13FF

0x0900 1300

0x0900 12FF

0x0900 1200

0x0900 11FF

0x0900 1100

0x0900 10FF

0x0900 1000

0x0900 0FFF

0x0900 0400

0x0900 03FF

0x0900 0300

0x0900 02FF

0x0900 0200

0x0900 01FF

0x0900 0100

0x0900 00FF

0x0900 0000

0x07FF FFFF

0x0080 0000

0x007F FFFF

0x0070 0000

0x006F FFFF

0x0060 0000

0x005F FFFF

0x0050 0000

0x004F FFFF

0x0040 0000

0x003F FFFF

0x0030 0000

0x002F FFFF

0x0020 0000

0x001F FFFF

0x0010 0000

0x000F FFFF

0x0000 1000

0x0000 0FFF

0x0000 0000

Figure 1.4 Memory Map of Mode 3

Preliminary 25

Introduction Flash MCU(HMS39C7092)

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

FLASH

(192KB)

Default.

SM=0 in the PMU register.

0 x07FF FFFF

0x0700 0000

0 x06FF FFFF

0x0600 0000

0 x05FF FFFF

0x0500 0000

0 x04FF FFFF

0x0400 0000

0 x03FF FFFF

0x0300 0000

0 x02FF FFFF

0x0200 0000

0 x01FF FFFF

0x0100 0000

0 x00FF FFFF

0x0003 0000

0 x0002 FFFF

0x0000 0000

Reserved

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

FLASH

(192KB)

SM=1 in the PMU register. Remap mode ( Remap=1)

0x07FF FFFF

0x0080 0000

0x007F FFFF

0x0070 0000

0x006F FFFF

0x0060 0000

0x005F FFFF

0x0050 0000

0x004F FFFF

0x0040 0000

0x003F FFFF

0x0030 0000

0x002F FFFF

0x0020 0000

0x001F FFFF

0x0010 0000

0x000F FFFF

0x0003 0000

0x0002 FFFF

0x0000 0000

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

FLASH

(192KB)

On Chip

SRAM(4KB)

SM=0 in the PMU register.

0x07FF FFFF

0x0700 0000

0x06FF FFFF

0x0600 0000

0x05FF FFFF

0x0500 0000

0x04FF FFFF

0x0400 0000

0x03FF FFFF

0x0300 0000

0x02FF FFFF

0x0200 0000

0x01FF FFFF

0x0100 0000

0x00FF FFFF

0x0003 0000

0x0002 FFFF

0x0000 1000

0x0000 0FFF

0x0000 0000

Reserved

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

FLASH

(192KB)

On Chip

SRAM(4KB)

Remap mode (Remap=1)

SM=1 in the PMU register.

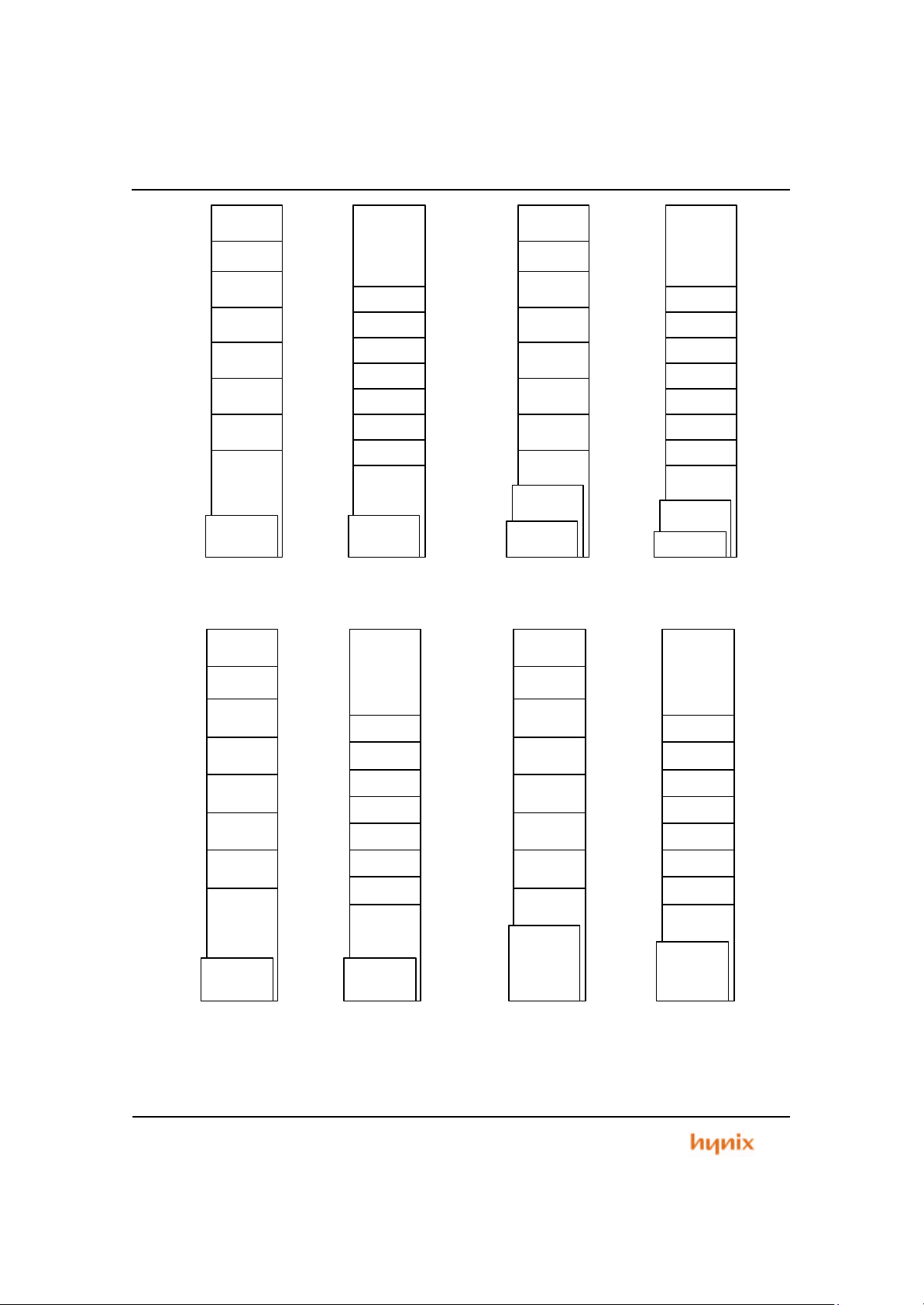

Figure 1.5 Memory Map of when Mode 4 and Mode 5

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

0x07FF FFFF

0x0700 0000

0x06FF FFFF

0x0600 0000

0x05FF FFFF

0x0500 0000

0x04FF FFFF

0x0400 0000

0x03FF FFFF

0x0300 0000

0x02FF FFFF

0x0200 0000

0x01FF FFFF

0x0100 0000

0x00FF FFFF

nCS0

0x0000 0100

On Chip

Boot ROM

(256Byte)

Default.

SM=0 in the PMU register.

0x0000 00FF

0x0000 0000

Reserved

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

On Chip

Boot ROM

(256Byte)

SM=1 and OnFLASH=0

in the PMU register.

0x07FF FFFF

0x0080 0000

0x007F FFFF

0x0070 0000

0x006F FFFF

0x0060 0000

0x005F FFFF

0x0050 0000

0x004F FFFF

0x0040 0000

0x003F FFFF

0x0030 0000

0x002F FFFF

0x0020 0000

0x001F FFFF

0x0010 0000

0x000F FFFF

0x0000 0100

0x0000 00FF

0x0000 0000

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

FLASH

(192KB)

SM=0 and On FLASH=1

in the PMU register.

0x07FF FFFF

0x0700 0000

0x06FF FFFF

0x0600 0000

0x05FF FFFF

0x0500 0000

0x04FF FFFF

0x0400 0000

0x03FF FFFF

0x0300 0000

0x02FF FFFF

0x0200 0000

0x01FF FFFF

0x0100 0000

0x00FF FFFF

0x0003 0000

0x0002 FFFF

0x0000 1000

0x0000 0FFF

0x0000 0000

0x07FF FFFF

Reserved

0x0080 0000

nCS7

nCS6

nCS5

nCS4

nCS3

nCS2

nCS1

nCS0

FLASH

(192KB)

SM=1 andOnFLASH =1

in the PMU register.

0x007F FFFF

0x0070 0000

0x006F FFFF

0x0060 0000

0x005F FFFF

0x0050 0000

0x004F FFFF

0x0040 0000

0x003F FFFF

0x0030 0000

0x002F FFFF

0x0020 0000

0x001F FFFF

0x0010 0000

0x000F FFFF

0x0003 0000

0x0002 FFFF

0x0000 1000

0x0000 0FFF

0x0000 0000

0x07FF FFFF

0x0080 0000

0x007F FFFF

0x0070 0000

0x006F FFFF

0x0060 0000

0x005F FFFF

0x0050 0000

0x004F FFFF

0x0040 0000

0x003F FFFF

0x0030 0000

0x002F FFFF

0x0020 0000

0x001F FFFF

0x0010 0000

0x000F FFFF

0x0003 0000

0x0002 FFFF

0x0000 1000

0x0000 0FFF

0x0000 0000

Figure 1.6 Memory Map of Mode 6 and Mode 7

26 Preliminary

Flash MCU(HMS39C7092) ARM7TDMI Core

Chapter 2

ARM7TDMI Core

Preliminary 27

ARM7TDMI Core Flash MCU(HMS39C7092)

2.1 General Description

The ARM7TDMI is a member of the ARM family of general-purpose 32bit

microprocessors, which offer s high performance for very low power consumption and

price. This processor employs a unique architectural strategy known as THUMB,

which makes it ideally suited to high volume applications with memory restrictions or

applications where code density is an issue.

The key idea behind THUMB is a super reduced instruction set. Essentially, the

ARM7TDMI has two instruction sets, the standard 32bit ARM set and 16bit THUMB

set. The THUMB set’s 16bit instruction length allows it to approach twice the density

of standard ARM code while retaining most of the ARM’s performance advantage

over a traditional 16bit processor by using 16bit registers. Th is is possible because

THUMB code operates on the same 32bit register set as ARM code.

See also ARM7TDMI Datasheet (ARM DDI 0029E) for detail.

2.2 Feature

• 32bit RISC architecture

• Low power consumption

• ARM7TDMI core with;

- On-chip ICEbreaker debug support

- 32bit x 8 hardware multiplier

- Thumb decompressor

• Utilizes the ARM7TDMI embedded processor

- High performance 32 bit RISC architecture

- High density 16 bit instruction set (THUMB code)

• Fully static operation : 0 ~ 80MHz

• 3-stage pipeline architecture (Fetch, decode, and execut ion stage)

• Enhanced ARM software toolkit

THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the

performance of an equivalent ARM processor connected to a 16-bit memory system.

28 Preliminary

Flash MCU(HMS39C7092) ARM7TDMI Core

2.3 Core Block Diagram

ScanChain2

P

C

b

u

s

A

(31 x 32-bit registers)

L

U

b

u

s

A

b

u

s

A [31:0]

ALE ABE

Address Register

Address

Incrementer

Register Bank

(6 status registers)

32 x 8

Multiplier

Barrel Shifter

32-bit ALU

I

n

c

r

e

m

e

n

t

e

r

b

u

s

B

b

u

s

Scan

Control

Instruction

Decoder

&

Control

Logic

DBGRQI

BREAKPTI

DBGACK

ECLK

nEXEC

ISYNC

BL [3:0]

APE

MCLK

nWAIT

nIRQ

nFIQ

nRESET

ABORT

SEQ

LOCK

nCPI

CPA

CPB

nM [4:0]

TBE

TBIT

HIGHZ

ICE

Breaker

RANGEOUT0

RANGEOUT1

ESTERN1

EXTERN0

nRW

MAS [1:0]

nTRANS

nMREQ

nOPC

A [0:31]

Instruction Pipeline

Write Data Register

nENOUT nENINDBE

& Read Data Register

& Thumb Instruction Decoder

D [31:0]

Core

Bus

Splitter

Scan

Chain 1

Scan

Chain 0

TAP Controller

TASPM [3:0]IR [3:0]SCREG [3:0]

Figure 2.1 ARM7TDMI Core Block Diagram

TCKTMSnTRSTTDITDO

D [0:31]

DIN [0:31]

DOUT [0:31]

Preliminary 29

ARM7TDMI Core Flash MCU(HMS39C7092)

2.4 Instruction Set

2.4.1 ARM Instruction

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Cond 0 0 I Opcode S Rn Rd Operand Data Processi ng / PSR Transfer

Cond 0 0 0 0 0 0 A S Rd Rn Rs 1 0 0 1 Rm Multiply

Cond 0 0 0 0 1 U A S RdHi RdLo Rn 1 0 0 1 Rm Multiply Long

Cond 0 0 0 1 0 B 0 0 Rn Rd 0 0 0 0 1 0 0 1 Rm Single Data Swap

Cond 0 0 0 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 1 Rn Branch and Exchange

Cond 0 0 0 P U 0 W L Rn Rd 0 0 0 0 1 S H 1 Rm Halfword Data Transfer: register offset

Cond 0 0 0 P U 1 W L Rn Rd Offset 1 S H 1 Offset Halfword Data Transfer: immediate offset

Cond 0 1 I P U B W L Rn Rd Offset Single Data Transfer

Cond 0 1 1

Cond 1 0 0 P U S W L Rn Register List Block Data Transfer

Cond 1 0 1 L Offset Branch

Cond 1 1 0 P U N W L Rn CRd CP# Offset Coprocessor Data Transfer

Cond 1 1 1 0 CP Opc CRn CRd CP# CP 0 CRm Coprocessor Data Operation

Cond 1 1 1 0 CP

Cond 1 1 1 1 Ignored by processor Software Interrupt

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

L CRn Rd CP# CP 1 CRm

Opc

1 Undefined

Coprocessor Register Transfer

Figure 2.2 ARM instruction set formats

30 Preliminary

Loading...

Loading...