HYNIX GM71C17400CLJ-7, GM71C17400CLJ-6, GM71C17400CLJ-5, GM71C17400CJ-7, GM71C17400CJ-5 Datasheet

...

GM71C(S)17400C/CL

4,194,304 WORDS x 4 BIT

CMOS DYNAMIC RAM

Description

The GM71C(S)17400C/CL is the new

generation dynamic RAM organized 4,194,304

words x 4 bit. GM71C(S)17400C/CL has

realized higher density, higher performance and

various functions by utilizing advanced CMOS

process technology. The GM71C(S)17400C/CL

offers Fast Page Mode as a high speed access

mode. Multiplexed address inputs permit the

GM71C(S)17400C/CL to be packaged in a

standard 300 mil 24(26) pin SOJ, and a standard

300 mil 24(26) pin plastic TSOP II. The

package size provides high system bit densities

and is compatible with widely available

automated testing and insertion equipment.

System oriented features include single power

supply 5.0V+/-10% tolerance, direct interfacing

capability with high performance logic families

such as Schottky TTL.

Features

* 4,194,304 Words x 4 Bit Organization

* Fast Page Mode Capability

* Single Power Supply (5.0V+/-10%)

* Fast Access Time & Cycle Time

* Low Power

Active : 660/605/550mW (MAX)

Standby : 11mW (CMOS level : MAX)

: 0.83mW (L-version : MAX)

* RAS Only Refresh, CAS before RAS Refresh,

Hidden Refresh Capability

* All inputs and outputs TTL Compatible

* 2048 Refresh Cycles/32ms

* 2048 Refresh Cycles/128ms (L-version)

* Battery backup operation (L-version)

* Test function : 16bit parallel test mode

(Unit: ns)

GM71C(S)17400C/CL-5

GM71C(S)17400C/CL-6

GM71C(S)17400C/CL-7

tRAC tCAC tRC tPC

5060131590

1103540

70 18 130 45

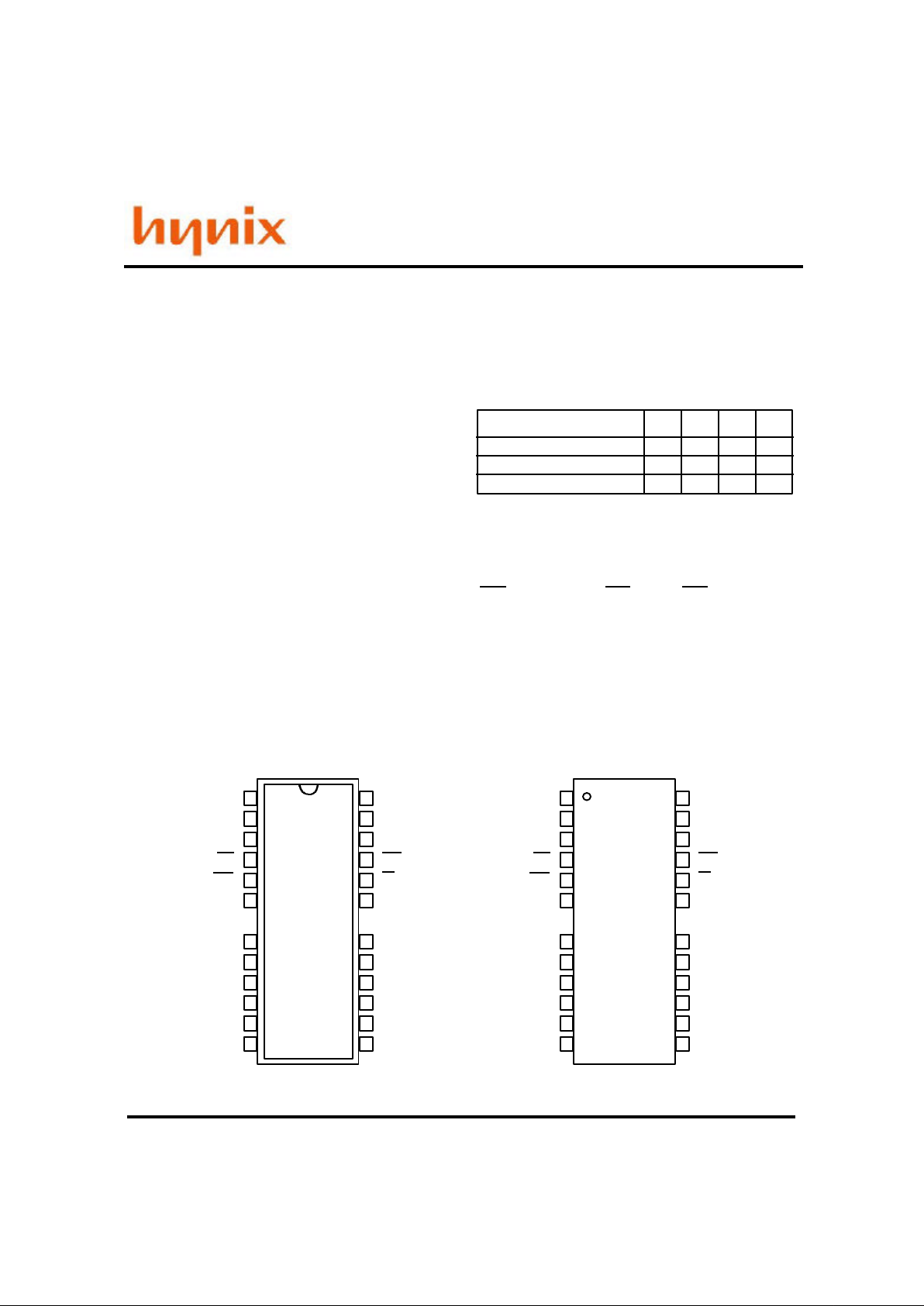

Pin Configuration

24(26) SOJ

(Top View)

VCC

I/O1

I/O2

WE

RAS

NC

A10

A0

A1

A2

A3

VCC

VSS

I/O4

I/O3

CAS

OE

A9

A8

A7

A6

A5

A4

VSS

1

2

3

4

5

6

8

9

10

11

12

13 14

15

16

17

18

19

21

22

23

24

25

26

24(26) TSOP II

VCC

I/O1

I/O2

WE

RAS

A11

A10

A0

A1

A2

A3

VCC

VSS

I/O4

I/O3

CAS

OE

A9

A8

A7

A6

A5

A4

VSS

1

2

3

4

5

6

8

9

10

11

12

13 14

15

16

17

18

19

21

22

23

24

25

26

Rev 0.1 / Apr’ 01

GM71C(S)17400C/CL

Rev 0.1 / Apr’ 01

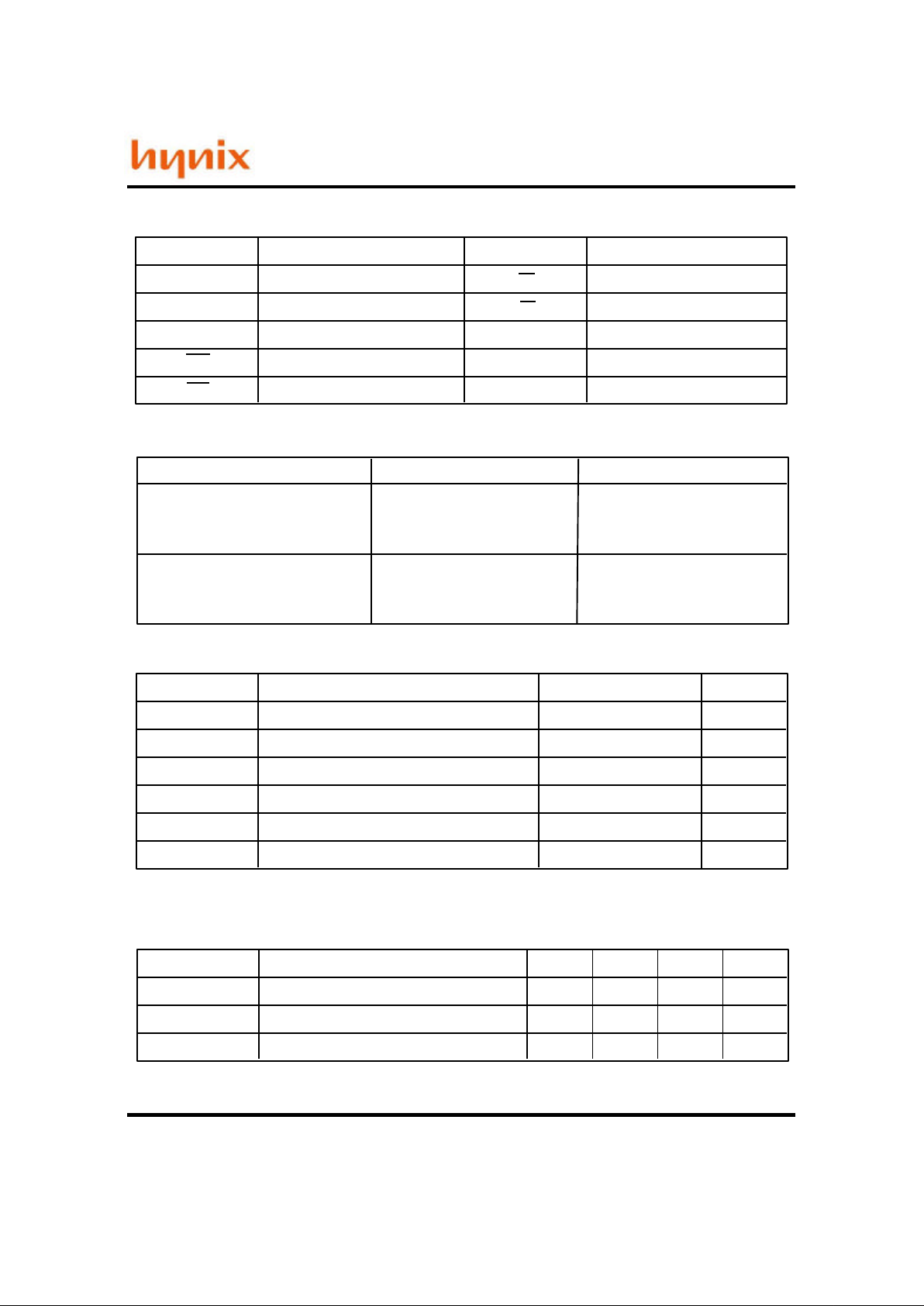

Pin Description

Pin Function Pin Function

A0-A10

A0-A10

I/O1-I/O4

VCC

VSS

Address Inputs

Refresh Address Inputs

Data Input/Data Output

Row Address Strobe

Column Address Strobe

Read/Write Enable

Output Enable

Power (5.0V)

Ground

Ordering Information

Type No. Access Time Package

GM71C(S)17400CJ/CLJ-5

GM71C(S)17400CJ/CLJ-6

GM71C(S)17400CJ/CLJ-7

50ns

60ns

70ns

300 Mil

24(26) Pin

Plastic SOJ

GM71C(S)17400CT/CLT-5

GM71C(S)17400CT/CLT-6

GM71C(S)17400CT/CLT-7

50ns

60ns

70ns

300 Mil

24(26) Pin

Plastic TSOP II

Absolute Maximum Ratings*

Note: All voltage referred to Vss.

RAS

CAS

Recommended DC Operating Conditions (TA = 0 ~ 70C)

OE

NC No Connection

WE

Symbol Parameter Rating Unit

TA

TSTG

VIN/VOUT

VCC

IOUT

0 ~ 70

-55 ~ 125

-1.0 ~ 7.0

-1.0 ~ 7.0

50

Ambient Temperature under Bias

Storage Temperature (Plastic)

Voltage on any Pin Relative to VSS

Voltage on VCC Relative to VSS

Short Circuit Output Current

V

V

mA

PD

1.0Power Dissipation W

*Note: Operation at or above Absolute Maximum Ratings can adversely affect device reliability.

C

C

Symbol Parameter Unit

VCC

VIH

VIL

Supply Voltage

Input High Voltage

Input Low Voltage

V

V

V

Max

5.5

6.0

0.8

Typ

5.0

-

-

Min

4.5

2.4

-1.0

GM71C(S)17400C/CL

Rev 0.1 / Apr’ 01

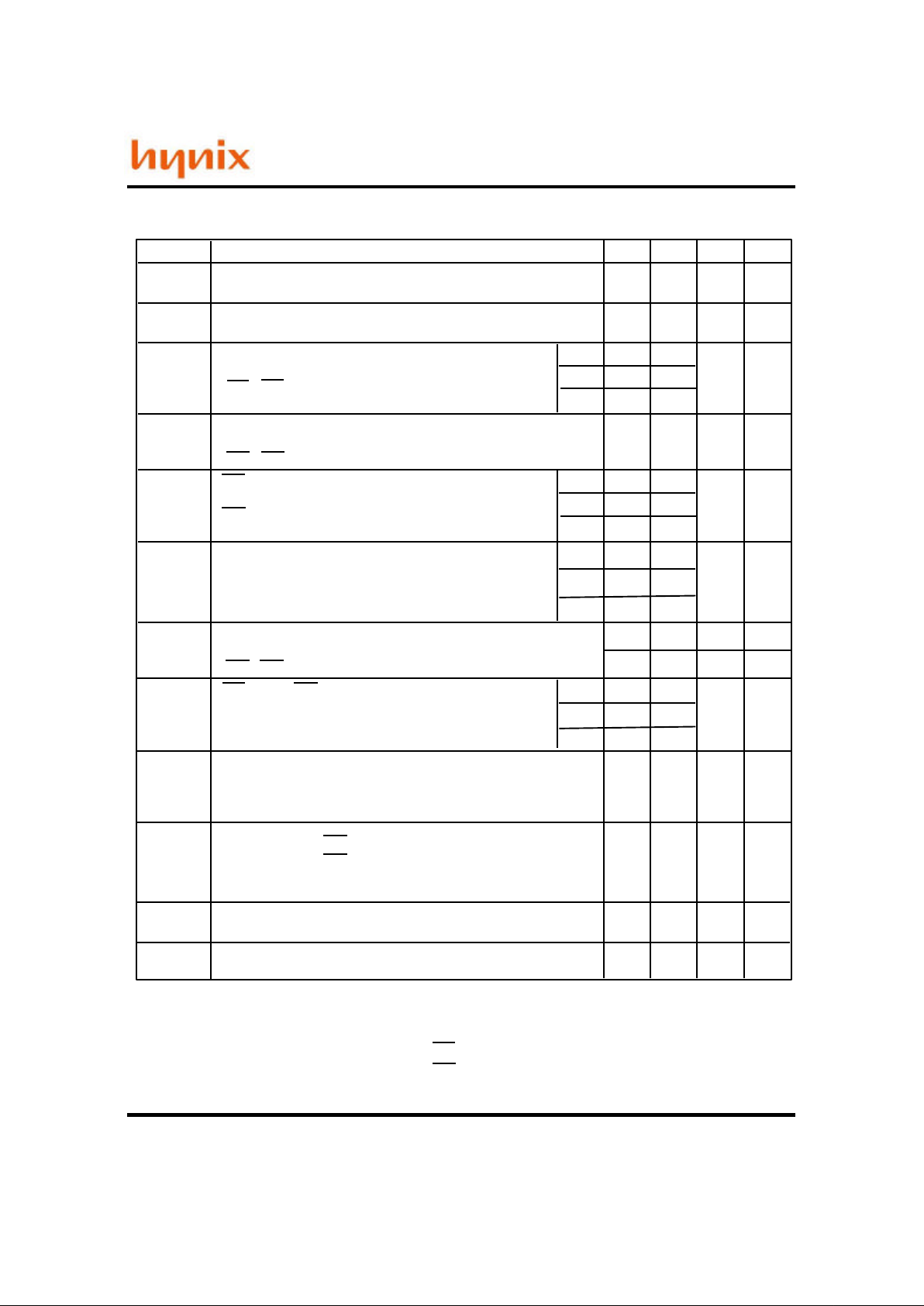

DC Electrical Characteristics (VCC = 5.0V+/-10%, Vss = 0V, TA = 0 ~ 70C)

Symbol Parameter Note

VOH

VOL

Output Level

Output "H" Level Voltage (IOUT = -5mA)

UnitMax

VCC

0.4

Min

2.4

0

Output Level

Output "L" Level Voltage (IOUT = 4.2mA)

ICC1

Operating Current

Average Power Supply Operating Current

(RAS, CAS Cycling : tRC = tRC min)

ICC2 Standby Current (TTL)

Power Supply Standby Current

(RAS, CAS = VIH, DOUT = High-Z)

ICC3 RAS Only Refresh Current

Average Power Supply Current

RAS Only Refresh Mode

(tRC = tRC min)

ICC4

ICC5 Standby Current (CMOS)

Power Supply Standby Current

(RAS, CAS >= VCC - 0.2V, DOUT = High-Z)

1-

ICC6 CAS-before-RAS Refresh Current

(tRC = tRC min)

150-

ICC8

IL(I)

10-10

IL(O)

10-10

Input Leakage Current

Any Input (0V<=VIN<= 6V)

Output Leakage Current

(DOUT is Disabled, 0V<=VOUT<= 6V)

Note: 1. ICC depends on output load condition when the device is selected.

ICC(max) is specified at the output open condition.

2. Address can be changed once or less while RAS = VIL.

3. Address can be changed once or less while CAS = VIH.

4. L-version.

Fast Page Mode Current

Average Power Supply Current

Fast Page Mode

(tPC = tPC min)

2-

100-50ns

60ns

70ns

90

80

-

-

-

100-50ns

60ns

70ns

90

80

-

-

90-50ns

60ns

70ns

80

70

-

V

V

mA

uA

uA

ICC7

- 5

Standby Current RAS = VIH

CAS = VIL

DOUT = Enable

1mA

Battery Backup Operating Current(Standby with CBR Refresh)

(CBR refresh, tRC=62.5us, tRAS<=0.3us,

DOUT=High-Z, CMOS interface)

350- uA 4

uA

4

mA

mA 1, 2

mA 2

mA 1, 3

mA

-

100-50ns

60ns

70ns

90

80

-

Loading...

Loading...