HYNIX GM16C550 Datasheet

1

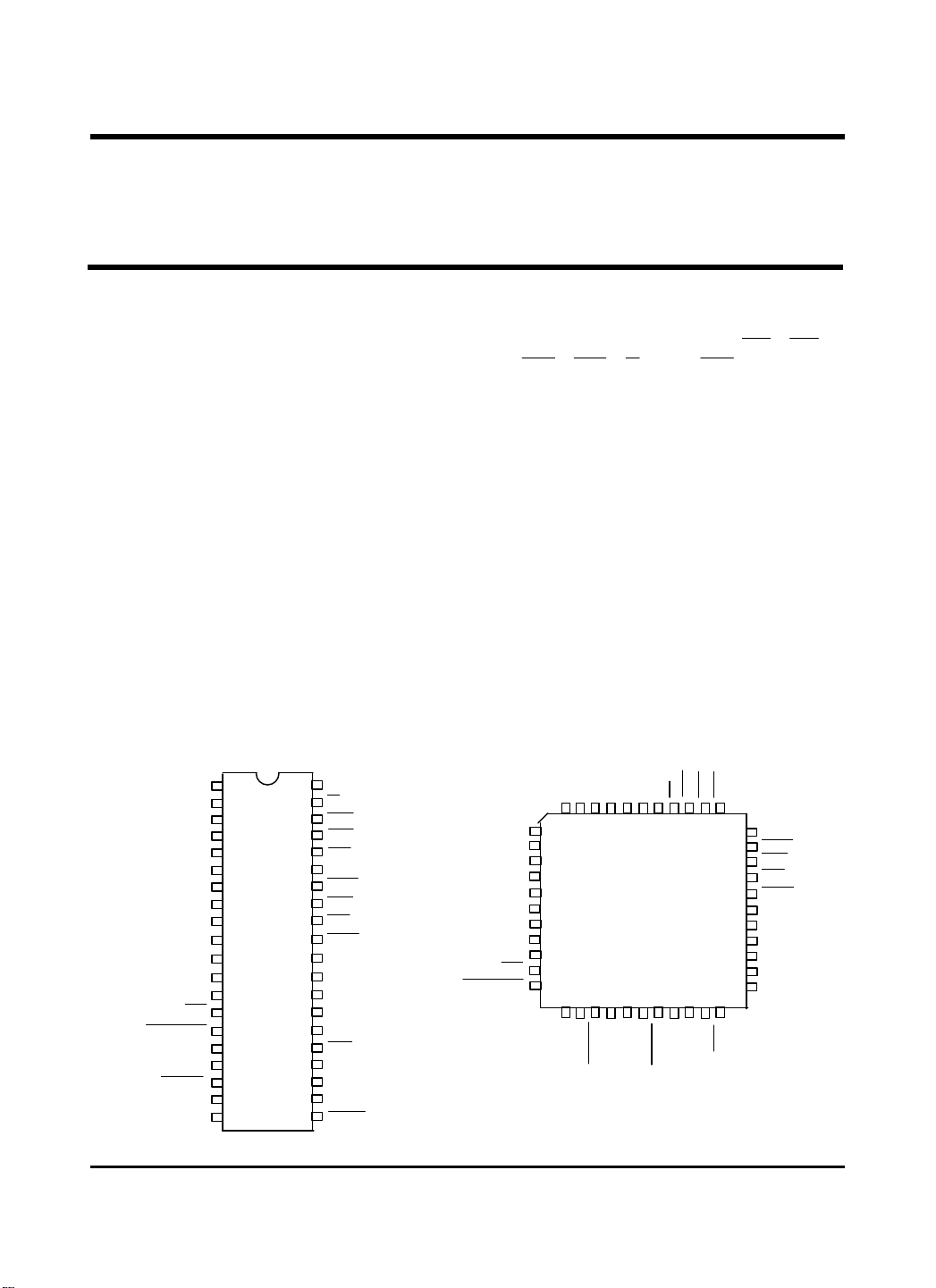

D0

D1

D2

D3

D4

D5

D6

D7

RCLK

SIN

SOUT

CS0

CS1

XTAL1

XTAL2

DOSTR

VSS

VCC

MR

INTRPT

RXRDY

A0

A1

A2

DISTR

DDIS

TXRDY

D6

D5

D7

RCLK

SIN

N.C.

SOUT

CS0

CS1

A1

A2

A0

RXRDY

INTRPT

N.C.

MR

D1 D2 D3 D4 D0 N.C. VCC RI

DCD DSR CTS

VSS N.C. DISTR

DISTR

DDIS TXRDY

GM16C550

GM16C550

ASYNCHRONOUS COMMUNICATIONS

ELEMENT WITH FIFOs

Descriptions

The GM16C550 is an asynchronous communications element (ACE) that is functionally

equivalent to the GM16C450, and addition-ally

incorporates a 16byte FIFOs are available on both

the transmitter and receiver, and can be activated by

placing the device in the FIFO mode. After a reset,

the registers of the GM16C550 are identical to those

of the GM16C450.

The UART performs serial-to-parallel conver- sion

on data characters received from a peri-pheral

device or a MODEM, and parallel-to- serial

conversion on data characters received from the

CPU. The CPU can read the com- plete status of

the UART at any time during the functional

operation. Status information reported includes the

type and condition of the transfer operations

being performed by the UART, as well as any

error conditions (parity, overrun, framing, or break

interrupt).

Pin Configulation

CS2

BAUDQUT

DOSTR

RI

DCD

DSR

CTS

OUT1

DTR

RTS

OUT2

ADS

DISTR

Features

l Fully compatible with GM16C450.

l Modem controm signals include

DSR, DTR , RI and -DCD .

l Programmable serial characteristics:

— 5-, 6-, 7- or 8-bit characters

— Even-, odd-, or no-parity bit generation and

detection

— 1-, 11/2- or 2-stop bit generation

— Baud rate generation (DC to 256K baud)

l 16 byte FIFO reduces CPU interrupts.

l Independent control of transmit, receive, line

status, data set interrupts, FIFOs.

l Full status reporting capabilities

l Three-state, TTL drive capabilities for bi-

derectional data bus and control bus.

l 40DIP/44PLCC

CS2

BAUDQUT

CTS, RTS

OUT1

DTR

RTS

OUT2

,

2

°

°

°

−

°

−

=

mA

−

=

mA

mA

±

±

=

=

=

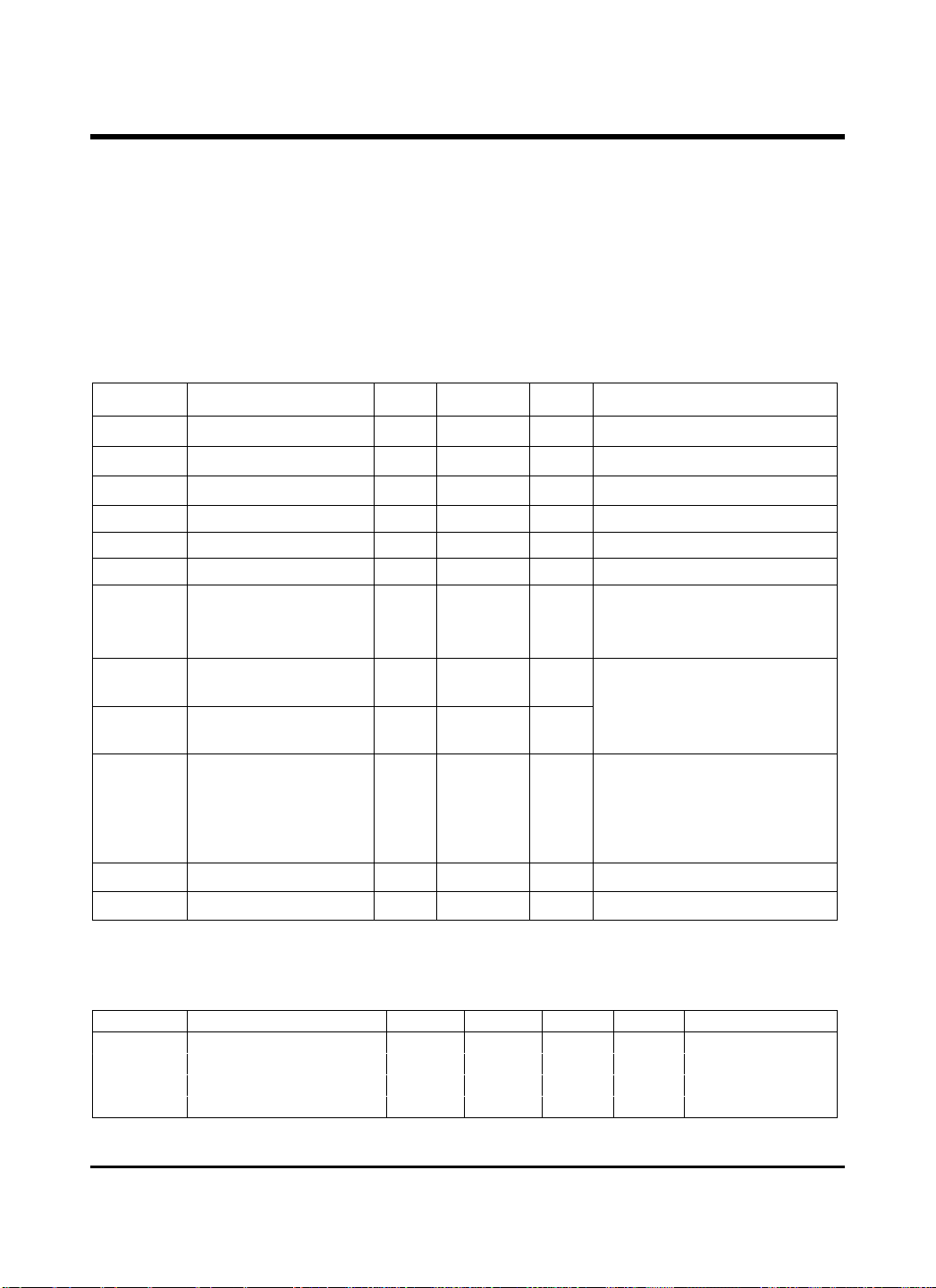

Absolute Maximum Ratings

Temperature under Bias

Storage Temperature

All Input or Output Voltages

with respect to

Power Dissipation 500 mW

V V5.0

SS

to +

C0

to +

C65

to + V0.7

C70

C150

DC Electrical Characteristics

GM16C550

Note: Maximum ratings indicates limits beyond which

permanent damage may occur. Continuous opera-tion

at these limits is not intended and should be limited

to those conditions specified under DC electrical

characteristics.

T °= TO +

Note 1. Does not apply to XOUT.

Note 2. Ta=25C

C0

A

Symbol Parameter Min Max Units

V Clock Input Low Voltage

ILX

V Clock Input High Voltage

IHX

V Input Low Voltage -0.5 0.8

IL

V Input High Voltage 2.2 CCV

IH

V Output Low Voltage 0.4

OL

V Output High Voltage 2.4

OH

CC

I Input Leakage

IL

I Clock Leakage

CL

I 3-State Leakage

OZ

V MR Schmitt ILV

ILMR

V MR Schmitt IHV

IHMR

)AV(I

, %5V5

V ±= , V0

C70°

CC

Average Power Supply

Current(

V )

CC

V = unless otherwise specified

SS

-0.5 0.8

2.0

V

CC

10

(Note 2)

10

Aµ

V

V

V

V

6.1I

V

V

0.1I

OL

OH

V =5.25

CC

output SIN DSR, DCD, CTS

V =5.25

CC

All other pins floating.

Aµ

10

Aµ

20±

IN

V =5.25 V , GND =0 V .

CC

OUT

1) Chip Deselected

2) Write mode, chip selected

2.2

0.8

V

V

Conditions

, No loads on

V

,

V

V0V

, 5.25V

V0V

,5.25 V

on all, Note 1

, Note 1

V =0

SS

V

.

Capitance C25T

A

°= , V0VV

==

SSCC

Symbol Parameter Min Tye Max Units Conditions

C Clock Input Capitance 15

XIN

C Clock Output Capitance 20

XOUT

C Input Capitance 6

IN

C Output Capitance 10

OUT

20 pF MHz1f

C

30 pF Unmeasured pins

10 pF Returned to

V

SS

20 pF

3

60

2

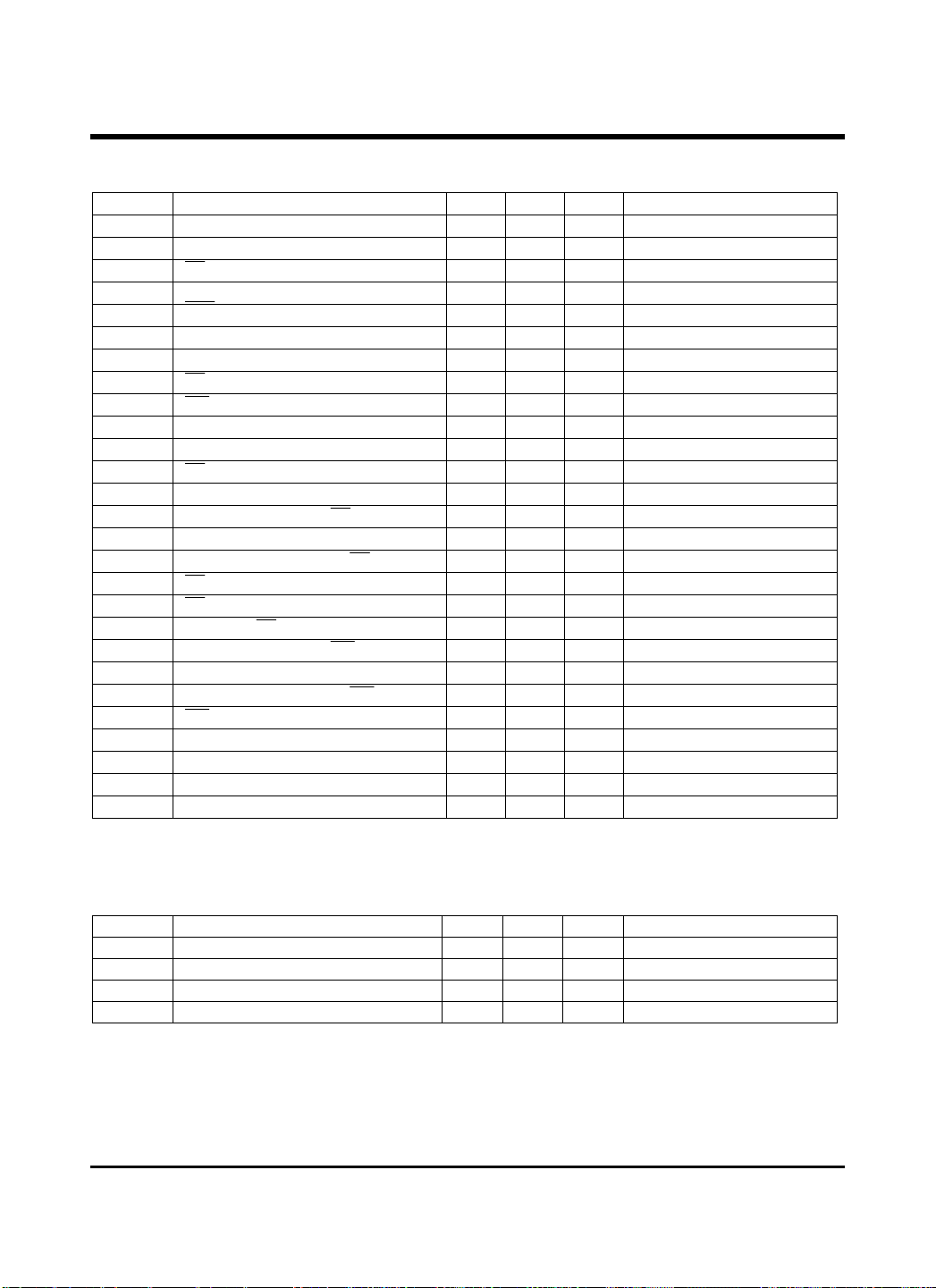

AC Characteristics C0T

Symbol

t

ADS

AHt Address Hold Time

ARt RD,RD Delay from Address

t

Address Setup Time

AS

t

AW

t

Chip Select Hold Time

CH

t

Chip Select Setup time

CS

t

CSR

t

CSW

DHt Data Hold Time

t

Date Setup Time

DS

HZt RD,RD to Floating Data Delay

MRt Master Reset Pulse Width

RAr Address Hold Time from RD,RD

t

Read Cycle Delay

RC

t

RCS

RDt RD,RD Strobe Width

RDDt

t

RVD

t

WA

t

Write Cycle Delay

WC

t

WCA

t

WR

XHt Duration of clock High Pulse

XLt Duration of clock Low Pulse

RC Read Cycle=

WC Write Cycle=

°= to V5V,C70

A

Parameter Min Max Units

Address Srobe Width

WR,WR Delay from Select

RD,RD Delay from Chip Select

WR,WR Delay from Select

Chip Select Hold Time from

to Driver Enable/Disable

RD,RD

Delay from - RD,RD to Data

Address Hold Time from WR,WR

Chip Select Hold Time from WR,WR

WR,WR Strobe Width

++

RD,RD

ttt

RCRDAR

ttt

WCWRAW

++

GM16C550

=°+ ±5%

CC

Conditions

60

0

30

60

30

0

60

30

30

30

30

0

100 ns

5

20

125

20

125

125 ns

20

150

20

100

55

55

280

280

ns

ns

Note 1

ns

ns

Note 1

ns

ns

ns

Note 1

ns

Note 1

ns

ns

ns

100 pF loading, Note 3

ns

Note 1

ns

ns

Note 1

ns

ns

100 pF loading, Note 3

ns

100 pF loading,

Note 1

ns

ns

Note 1

ns

ns

External Clock (8.0 MHz Max.)

ns

Exrternal Clock (8.9 MHz Max.)

ns

Note 4

ns

ns

Baud Generator

N Baud Divisor 1

BHDt Baud Output Positive Edge Delay 175 ns 100 pF load

BLDt Baud Output Negative Edge Delay 175 ns 100 pF load

t

Baud Output Up Time 75 ns MHz0.8fX= , +2, 100 pF load

HW

t

Baud Output Down Time 100 ns MHz0.8fX= , +2, 100 pF load

LW

16

-1

4

°

+

s

µ

s

µ

24

24

8

8

GM16C550

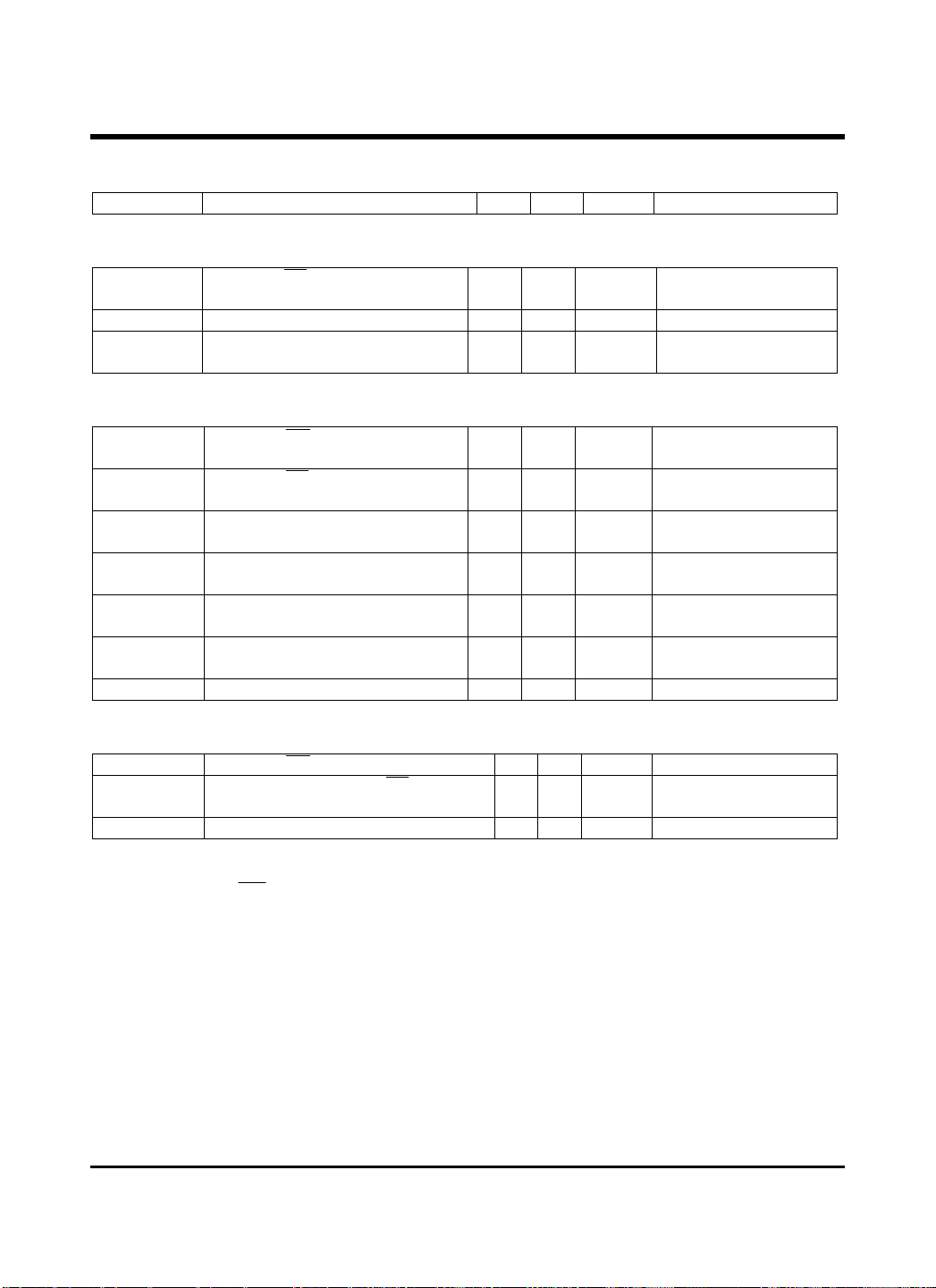

AC Characteristics C0T

A

°= to

C70

, %5V5V

CC

±=

Symbol Parameter Min Max Units Conditions

Receiver

t

RINT

t

SCD

t

SINT

Delay from RD,RD (RD RBR/ or

RD LSR) to Reset Interupt

Delay from RCLK to Sample Time 2

Delay from Stop to Set Interrupt 1

1

100 pF load

RCLK

Cycles

Note 2

Transmitter

HRt

t

IRS

t

t

STI

t

SXV

t

WXI

IRt

SI

Delay from WR,WR (WR THR)

To Reset Interrupt

Delay from RD,RD (RD IIR)

To Reset Interrupt (THRE)

Delay from Initial INTR Reset

To Transmit Start

Delay from Initial Write to Interrupt 16

Delay from Stop to Interrupt (THRE) 8

Delay from Start to TXRDY Active

Delay from Write to TXRDY inactive

175

250

8

195

ns 100 pF load

ns 100 pF load

Baudout

Cycles

Baudout

Cycles

Baudout

Cycles

Baudout

Cycles

Note 5

Note 5

100 pF load

ns 100 pF load

Modem Control

t

Delay from WR,WR (WR MCR) to Output 200

MDO

RIMt

t

SIM

Delay to Reset Interrupt from RD,RD

(RD MSR)

Delay to Set Interrupt from MODEM Input 250

ns 100 pF load

250

ns 100 pF load

ns 100 pF load

Notes

1. Applicable only when

2. In the FIFO mode (FCRO=1) the trigger level interrupts, the receiver data available indication, the active RXRDY indica-tion

and the overrun error indication will be delayed 3 RCLKs. Status indicators (PE, FE, BI) will be delayed 3 RCLKs after the first

byte has been received. For subsequently received bytes these indicators will be updated immediately after RDRBR goes

inactive. Timeout interrupt is delayed 8 RCLKs.

3. Change and discharge time is determined by VOL, VOH and the external loading.

4.In FIFO mode RC=425 ns (minimum) between reads of the receiver FIFO and the status registers (interrupt identifica- tion

register or line status register).

5. This delay will be lengthened by 1 character time, minus the last stop bit time if the transmitter interrupt delay circuit is active

(See FIFO Interrupt Mode Operatione)

ADS

is tied low.

5

÷

÷

÷

>

÷

HWtLW

HWtHW

LWtLW

LW

=2 XIN CTLES

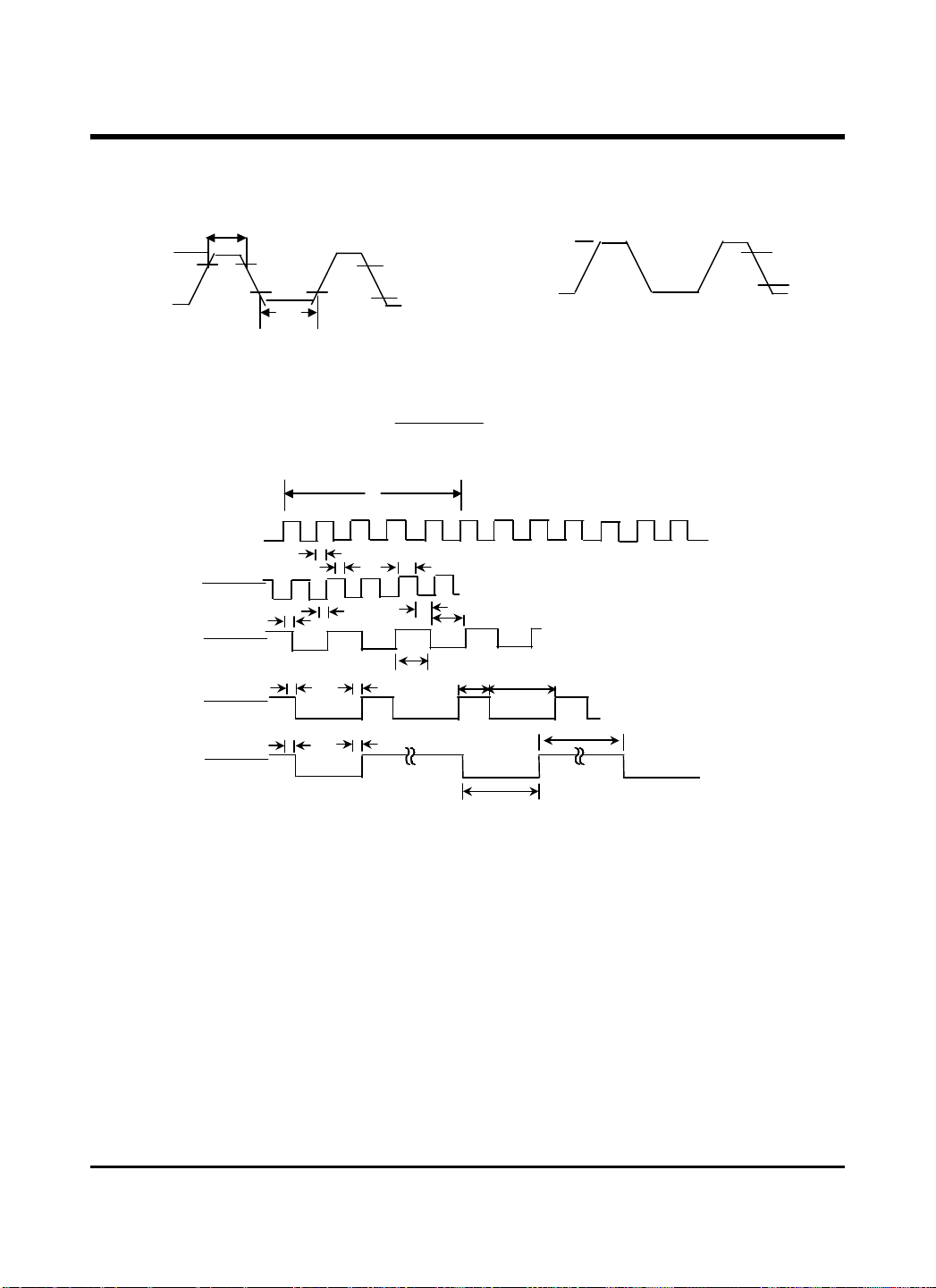

Timing Waveforms (All timings are referenced to valid 0 and valid)

External Clock Input (8.0 MHz Max.) AT Test Points

2.4V

XIN

0.4V

Note 1: The 2.4V and 0.4V levels are the voltages that the inputs are driven to during AC testing.

Note 2: The 2.2V and 0.8V levels are the voltages at which the timing tests are made.

t

2.2V

0.8V

t

2.4V

(Note 1) (Note 2)

0.4V

BAUDOUTTiming

XIN

t

t

OUT BAUD

)1(

OUT BAUD

)2(

OUT BAUD

)3(

OUT BAUD

)3N.N(

N

t

t

t

t

t

t

t

t

t

t

GM16C550

2.2V

0.8V

CYCLES XIN)2N(HWt−=

6

OR

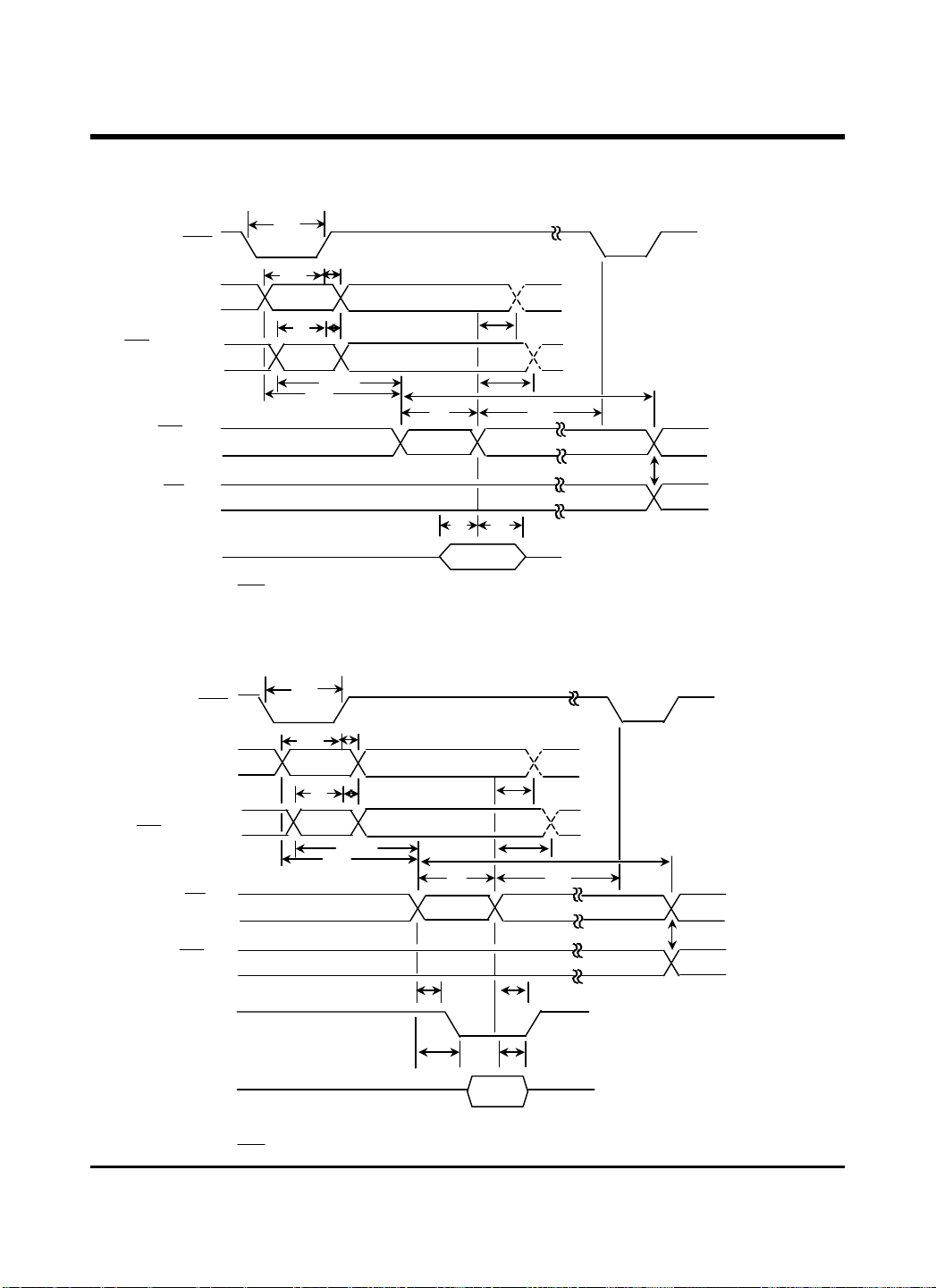

Timing Waveforms (Continued)

ADS

A2,A1,A0

2CS ,CS1,CS0

WR ,WR

RD ,RD

*Applicable Only When ADS is Tied Low.

DATA

D0-D7

ADS

A2,A1,A0

2CS ,CS1,CS0

RD ,RD

WR ,WR

*Applicable Only When

DDIS

DATA

D0-D7

tADS

is Tied Low.

ADS

tAS tAH

VALID

tCS tCH tWA*

VALID

tSCW*

tAW*

tADS

tAS tAH

VALID

tCS tCH tRA*

VALID

tCSR*

tAR*

Write Cycle

ACTIVE

tDS tDH

VALID DATA

Read Cycle

ACTIVE

tRDD

tRVD

VALID

DATA

tCSW*

tWC tWR

tRDD

tHZ

tRC tRD

tRCS*

GM16C550

WC

ACTIVE

ACTIVE

RC

ACTIVE

OR

ACTIVE

7

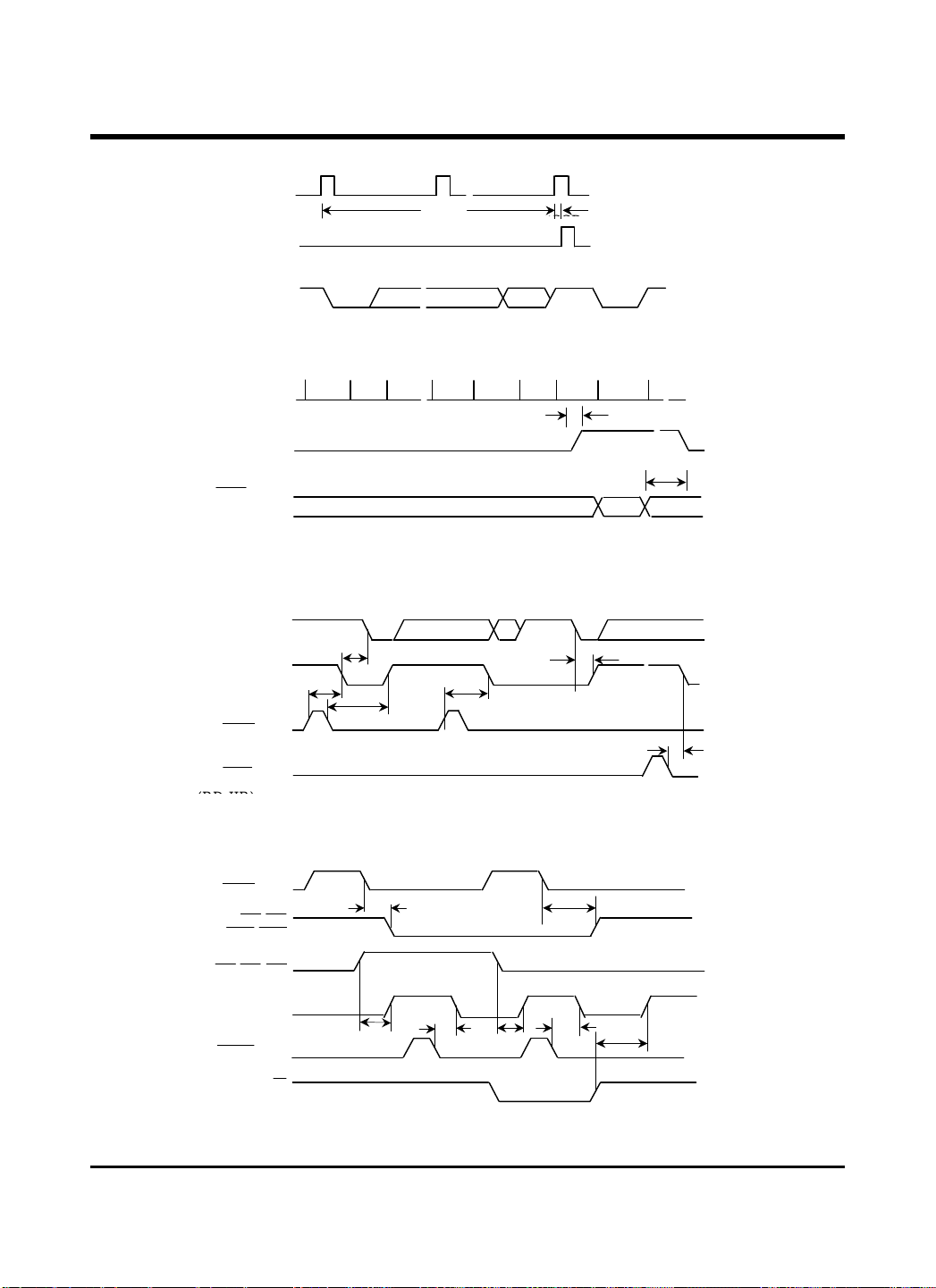

SERIAL OUT

INTERRUPT

(THRE)

DISTR/DISTR

DISTR/DISTR

DISTR/DISTR

RTS. DTR

CTS. DSR. DCD

INTERRUPT

tRIM

DISTR/DISTR

SIN

START

PARITY

SAMPLE

CLK

tRIN

ACTIVE

INTERRUPT

(DATA READY OR

RCVR ERR

/DOSTR

(READ REC

DATA BUFFER

OR RDLSR)

Receiver Timing

GM16C550

SAMPLE CLK

RECEIVER

DISTR

Transmitter Timing

(WR, THR)

RCKK

INPUT

DATA

(SOUT)

tHR

tSI

DATA BITS(5-8)

START

tiRS

tMR

PARITY

STOP

tSINT

START

tSTI

tIR

MODEM Comtrol Timing

(WR MCR)

OUT1. OUT2

Note 1: See Write Cycle Timing

Note 2: See Read Cycle Timing

(RD MSR)

tMDO

tSIM

RI

tSIM

tMDO

tRIM

tSIM

Loading...

Loading...