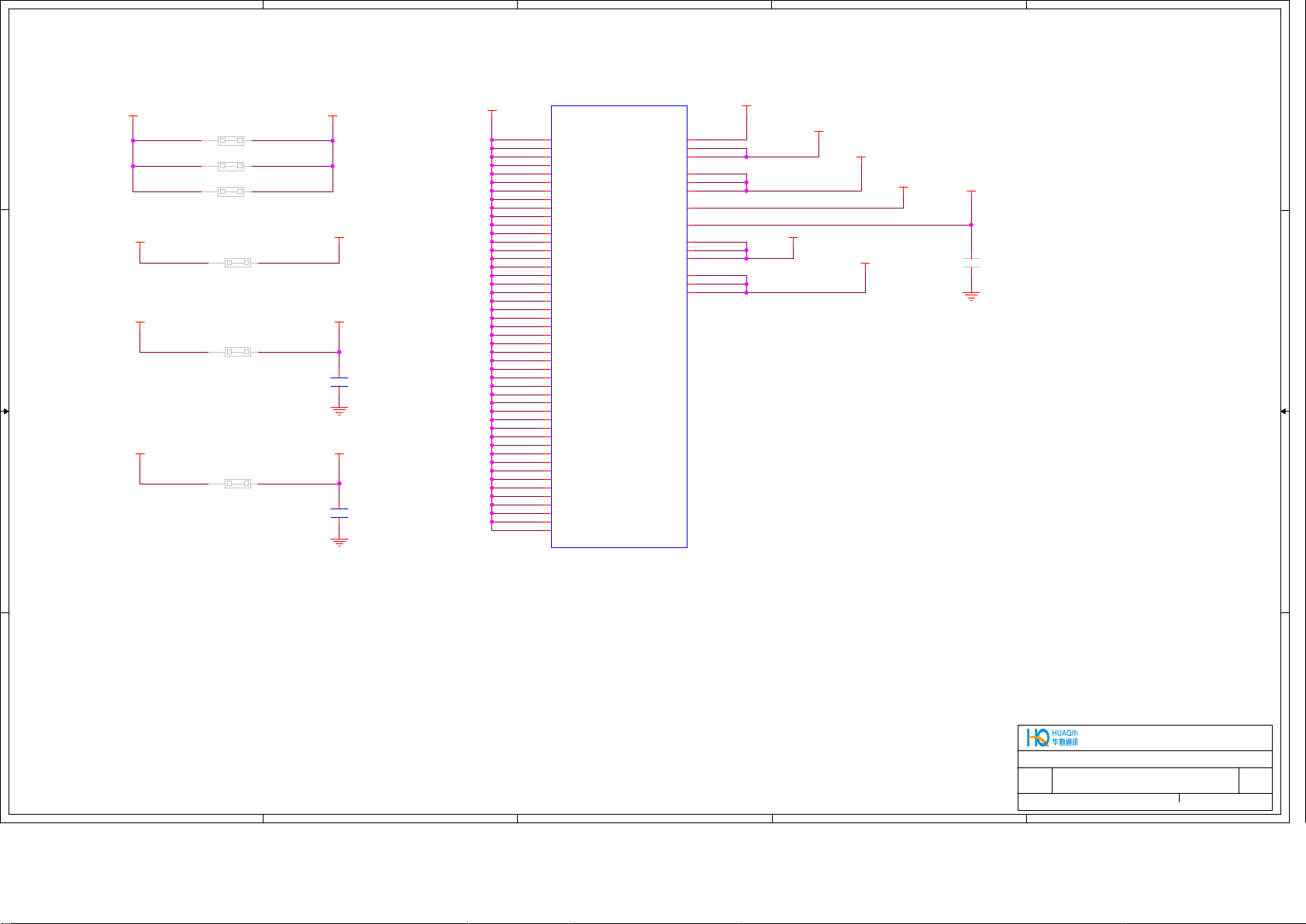

Huaqin NB2672 Schematic

5

D D

4

3

2

1

HuaQin Confidential

M/B Schematics Document

C C

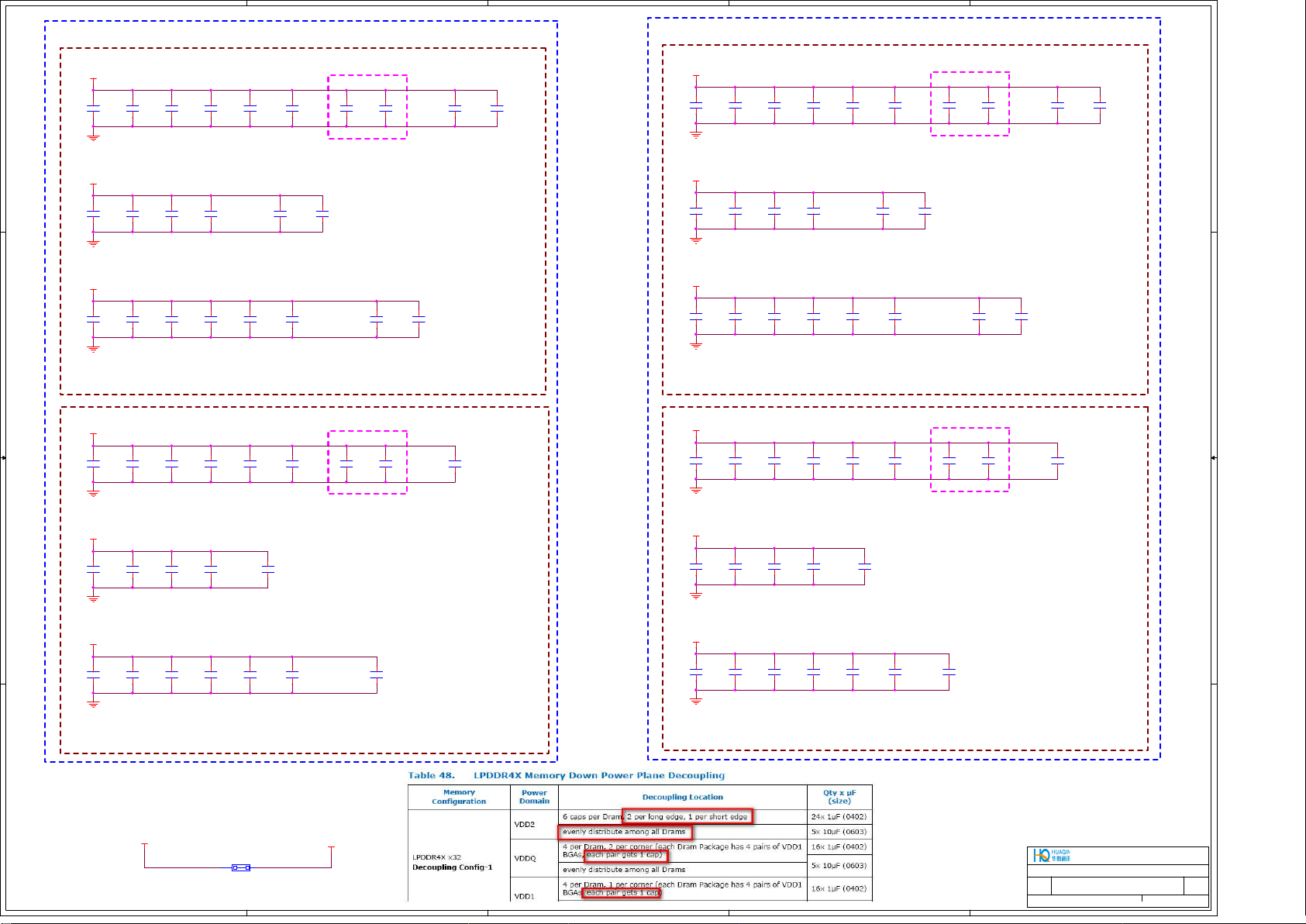

Intel TGL U-Processor with LPDDR4x

REV 4.0

2020-0825

B B

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date:

Date:

5

4

3

2

Date:

Cover page

Cover page

Cover page

Project

Project

Project

Name:

Name:

Name:

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Friday, August 28, 2020 1 84

Friday, August 28, 2020 1 84

Friday, August 28, 2020 1 84

1

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

V4.0

V4.0

V4.0

5

D D

C C

4

3

2

1

B B

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date:

Date:

Date:

5

4

3

2

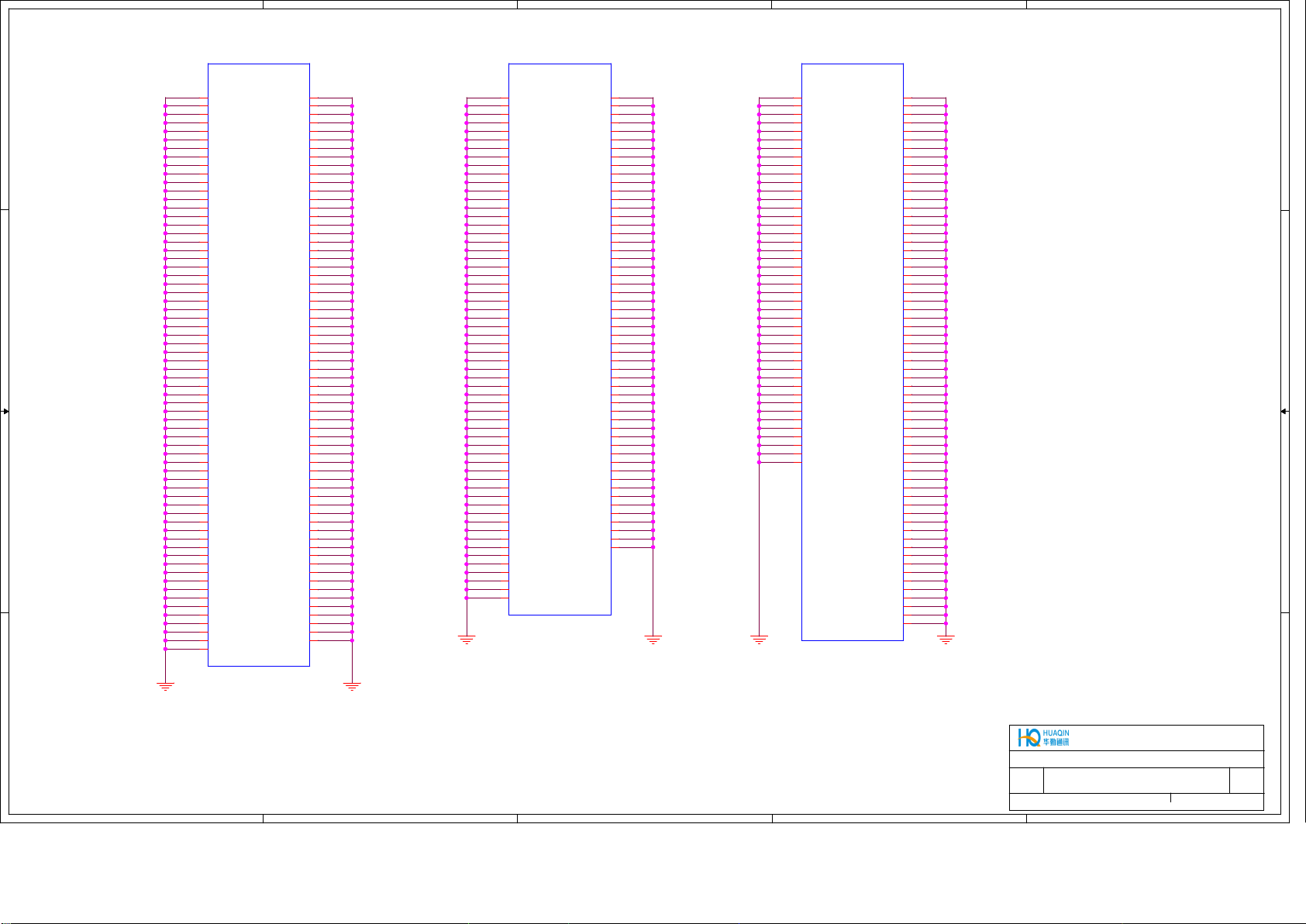

Block Diagram

Block Diagram

Block Diagram

Project

Project

Project

Name:

Name:

Name:

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Thursday, July 09, 2020 2 84

Thursday, July 09, 2020 2 84

Thursday, July 09, 2020 2 84

1

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

V4.0

V4.0

V4.0

D D

5

MEM ID

4

3

2

1

C C

B B

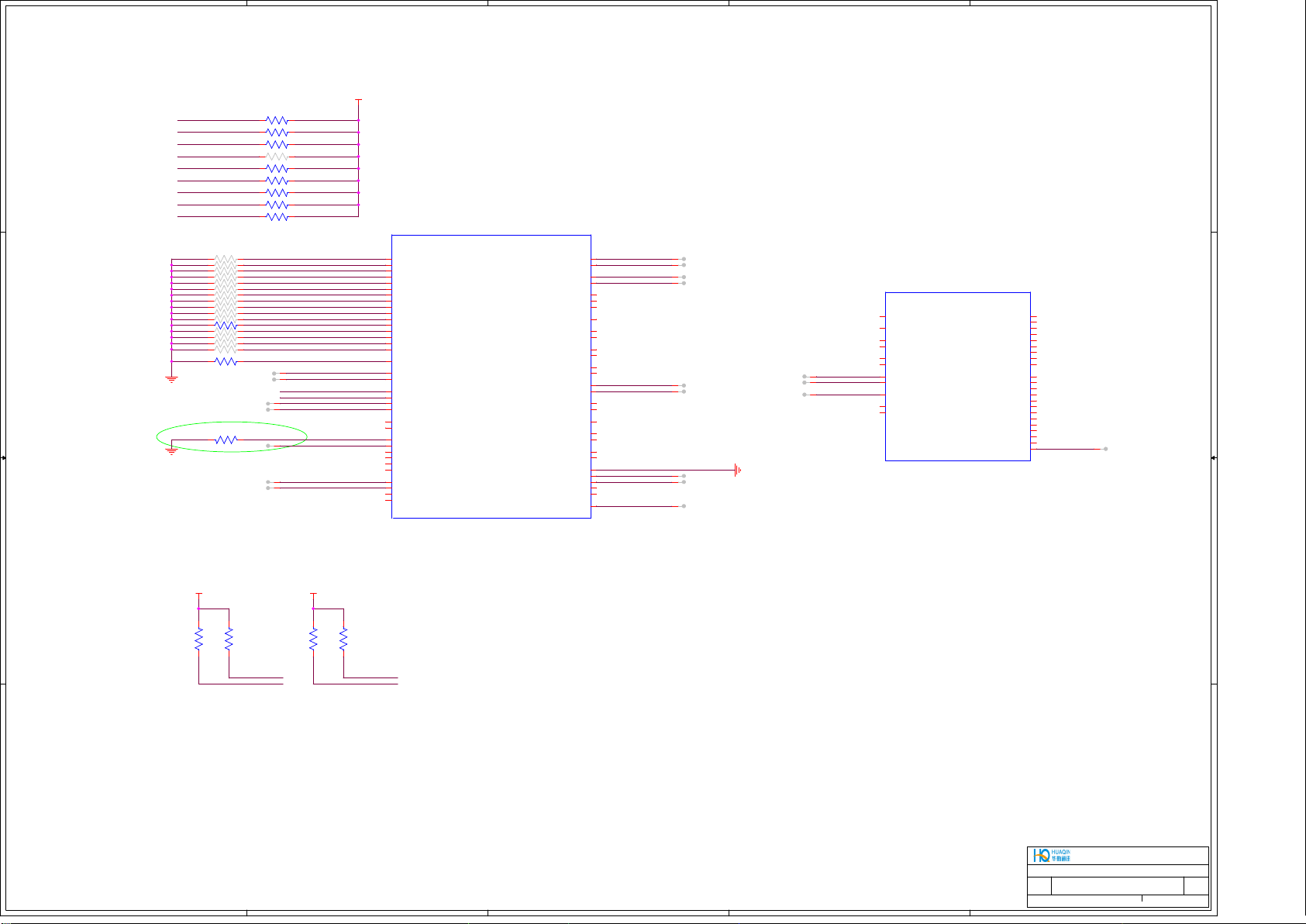

HW_ID3 HW_ID2 HW_ID1

0

0 0 0

0

0 0

0

0 0

1

0

0 1 0 0

1

0 0 0

GPU ID

HW_ID4

1

Description

UMA0

DGPU

KB BL ID

HW_ID6

0 No keyboard Backlignt

1 Keyboard Backlignt

Reserve ID

HW_ID7

0

1

Reserve

Reserve

HW_ID0

1

001

Description

Description

SAMSUNG LPDDR4 3733 1GB K4F8E304HB-MGCJ LF+HF D20

HYNIX LPDDR4 3733 1GB H9HCNNN8KUMLHR-NME LF+HF DDP

MICRON LPDDR4 4266 2GB MT53E512M32D2NP-046 WT:E LF+HF Z11N

HYNIX LPDDR4 3733 2GB H9HCNNNBPUMLHR-NME LF+HF DE

HYNIX LPDDR4X 4266 4GB H9HCNNNCPMALHR-NEE LF+HF QDP

4x 16Gb(reserve)

T.ME/SCHEMATICSLAPTOP

TotalDescription

4GB

4GB

8GB

8GB

16GB

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date:

Date:

Date:

5

4

3

2

I2C Table

I2C Table

I2C Table

Project

Project

Project

Name:

Name:

Name:

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Thursday, July 09, 2020 3 84

Thursday, July 09, 2020 3 84

Thursday, July 09, 2020 3 84

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

1

V4.0

V4.0

V4.0

5

D D

C C

4

3

2

1

T.ME/SCHEMATICSLAPTOP

B B

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date:

Date:

5

4

3

2

Date:

Huaqin Telecom Technology Com.,Ltd.

Blank

Blank

Blank

Project

Project

Project

Name:

Name:

Name:

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Thursday, July 09, 2020 4 84

Thursday, July 09, 2020 4 84

Thursday, July 09, 2020 4 84

1

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

V4.0

V4.0

V4.0

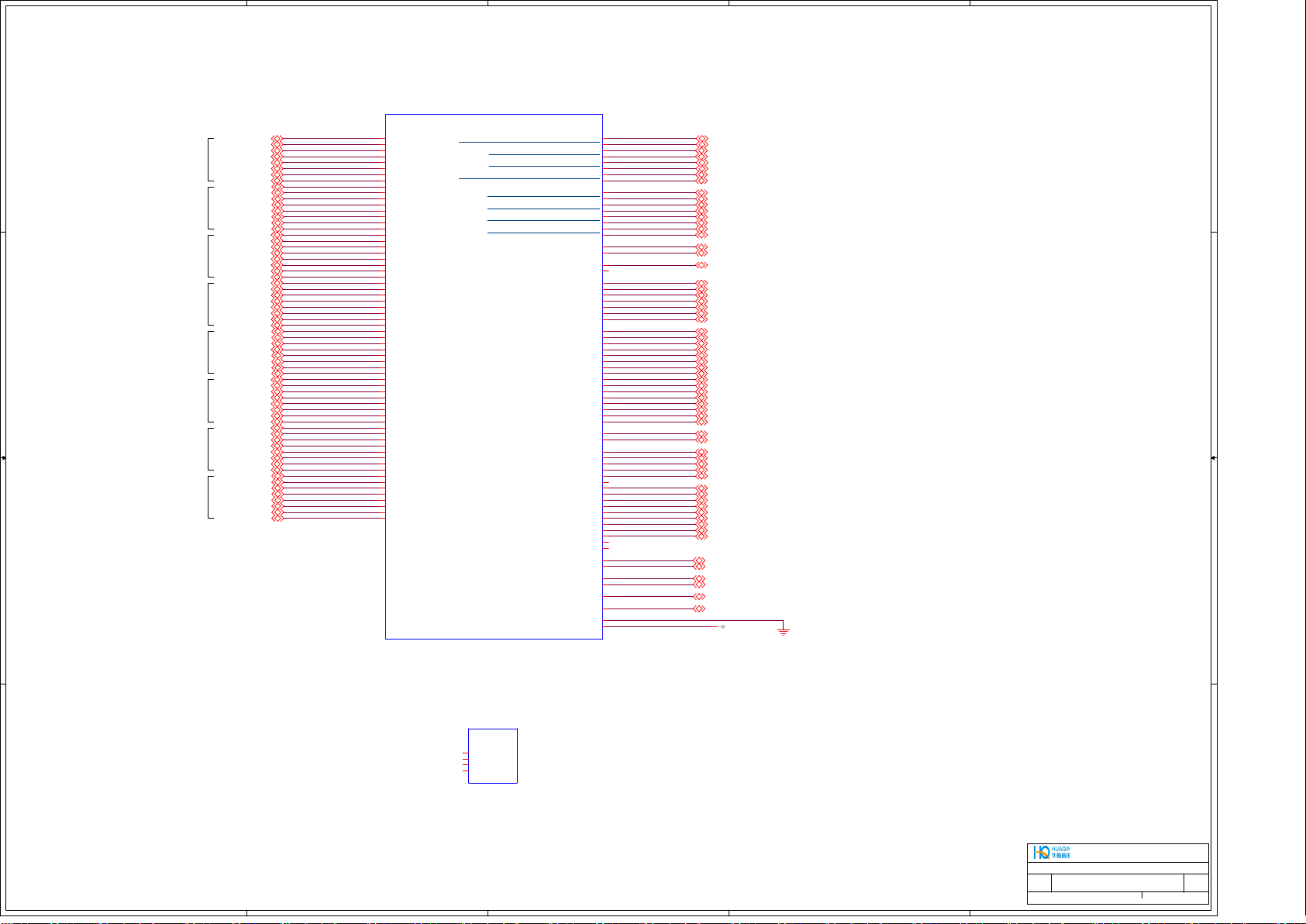

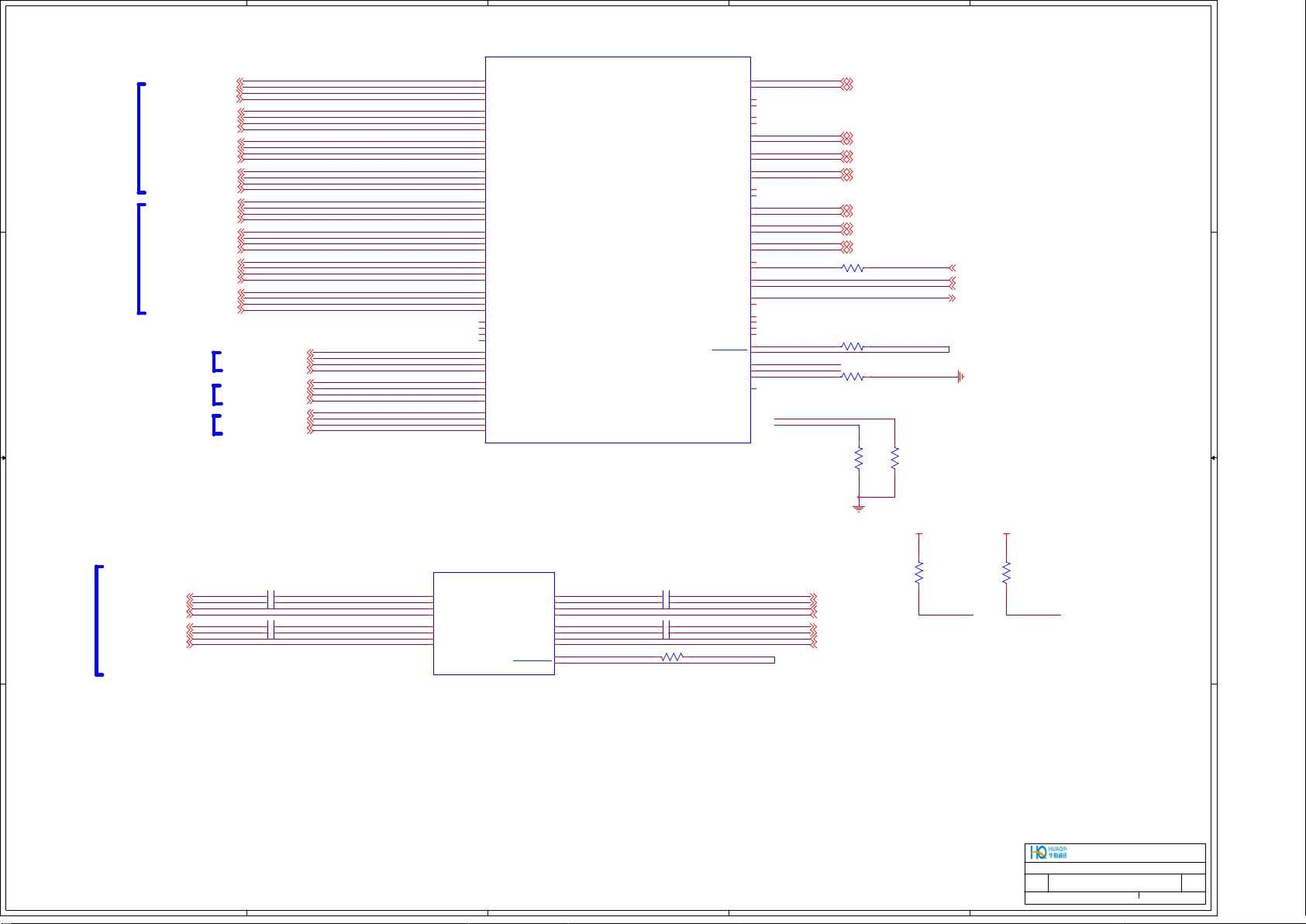

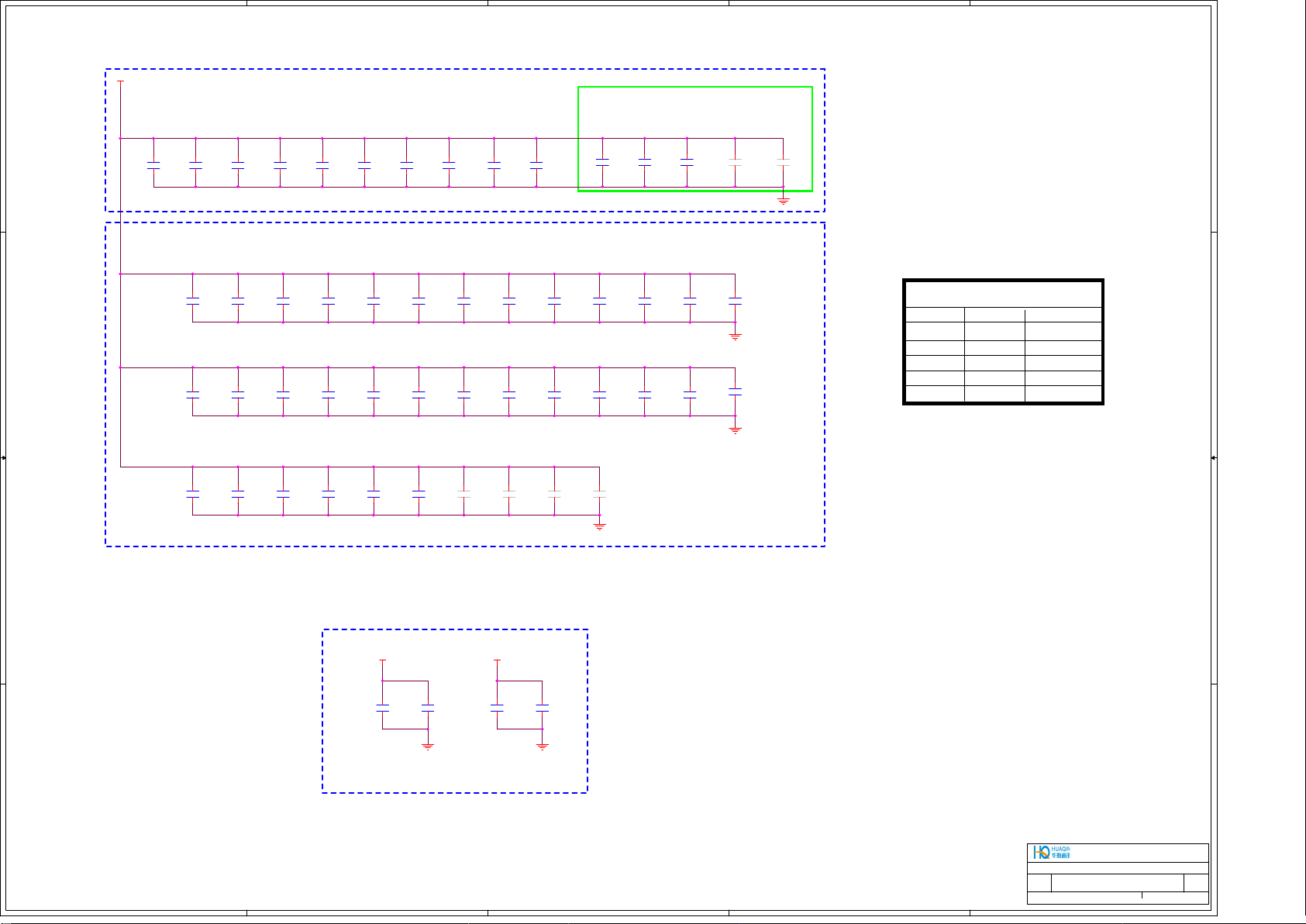

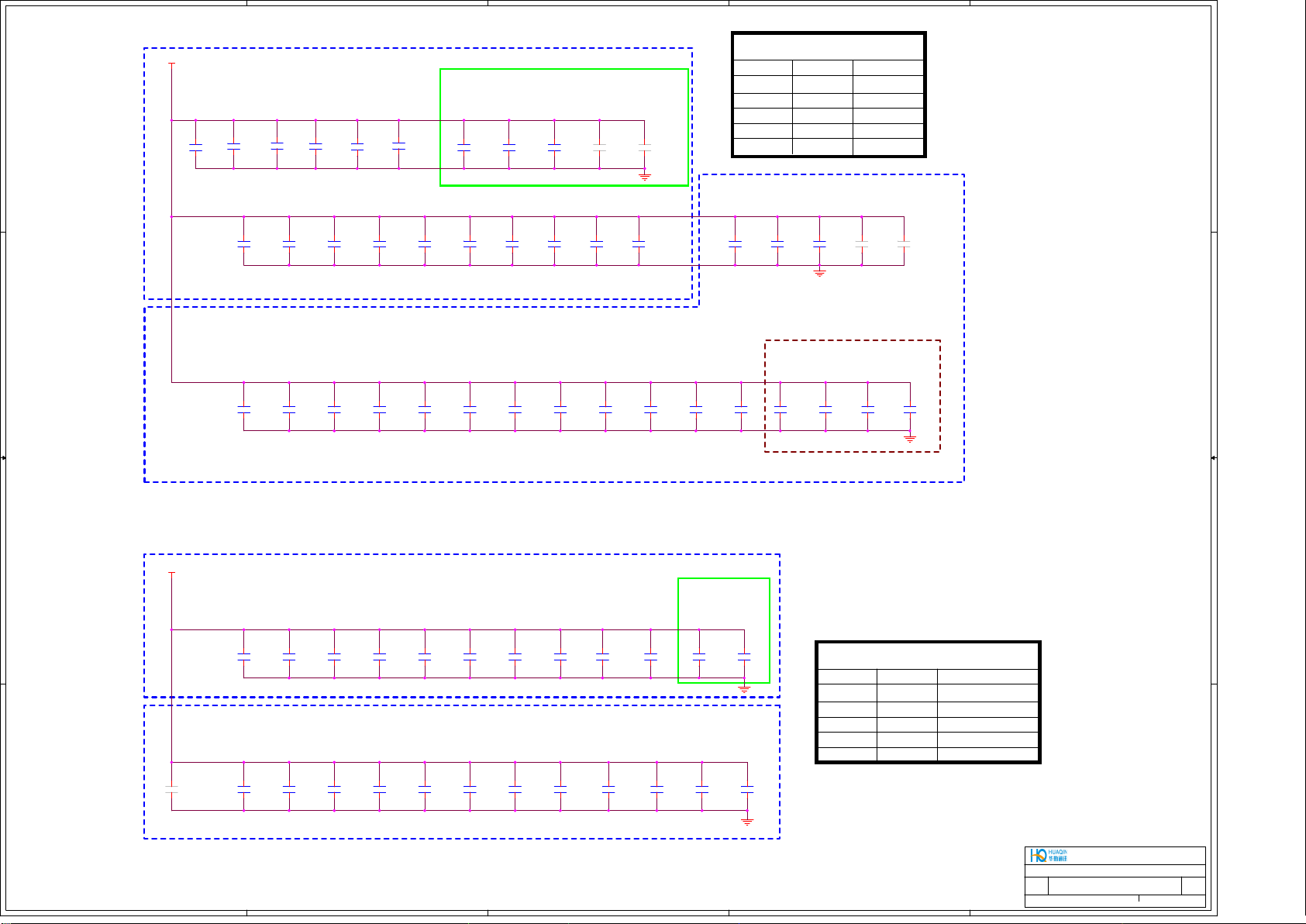

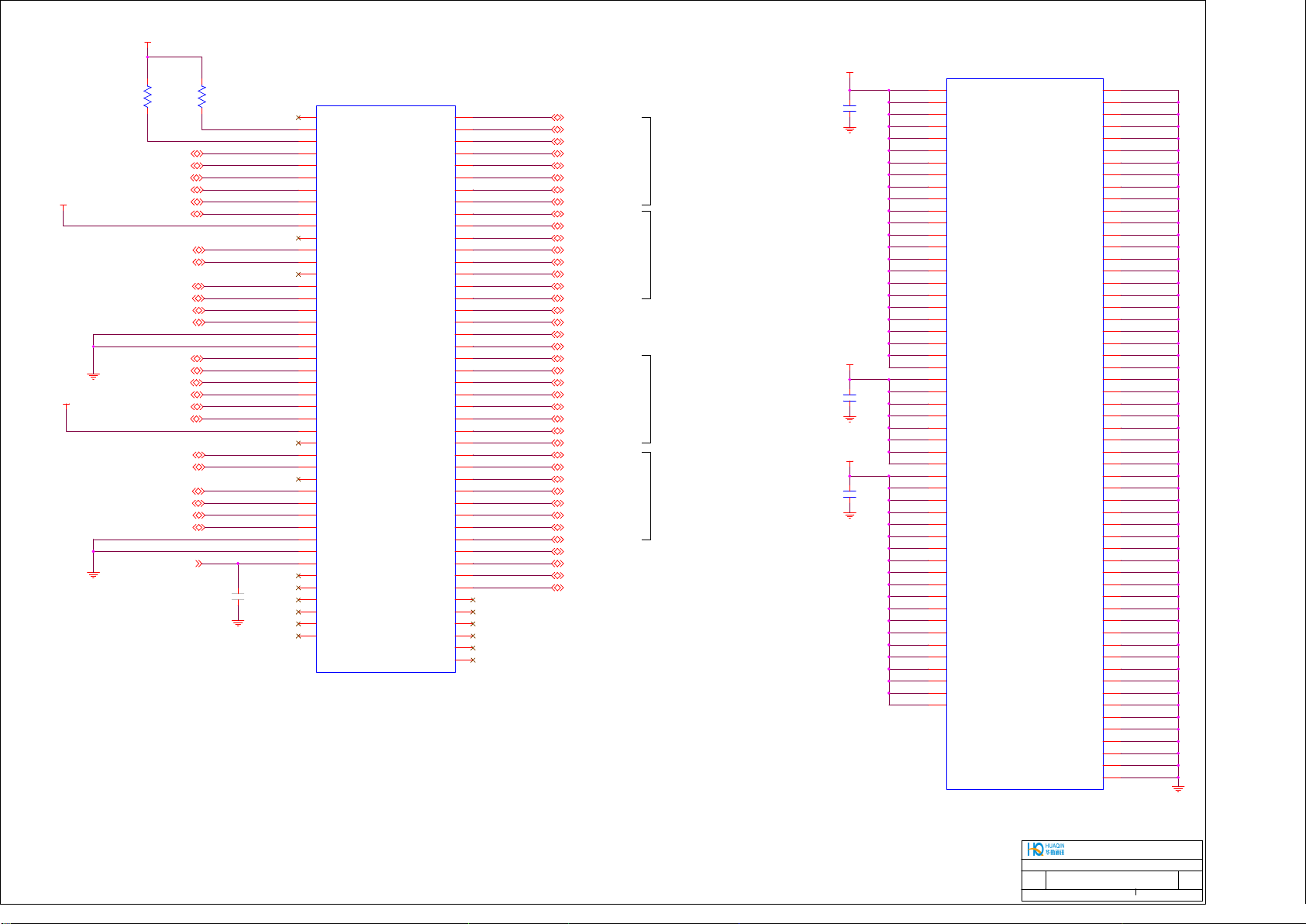

CHA

5

4

3

2

1

UU1B

M_0_DQ_0<7>21

M_0_DQ_0<6>21

D D

BYTE0

BYTE1

BYTE2

BYTE3

BYTE4

C C

BYTE5

BYTE6

BYTE7

B B

M_0_DQ_0<5>21

M_0_DQ_0<4>21

M_0_DQ_0<3>21

M_0_DQ_0<2>21

M_0_DQ_0<1>21

M_0_DQ_0<0>21

M_0_DQ_1<7>21

M_0_DQ_1<6>21

M_0_DQ_1<5>21

M_0_DQ_1<4>21

M_0_DQ_1<3>21

M_0_DQ_1<2>21

M_0_DQ_1<1>21

M_0_DQ_1<0>21

M_0_DQ_2<7>21

M_0_DQ_2<6>21

M_0_DQ_2<5>21

M_0_DQ_2<4>21

M_0_DQ_2<3>21

M_0_DQ_2<2>21

M_0_DQ_2<1>21

M_0_DQ_2<0>21

M_0_DQ_3<7>21

M_0_DQ_3<6>21

M_0_DQ_3<5>21

M_0_DQ_3<4>21

M_0_DQ_3<3>21

M_0_DQ_3<2>21

M_0_DQ_3<1>21

M_0_DQ_3<0>21

M_0_DQ_4<7>22

M_0_DQ_4<6>22

M_0_DQ_4<5>22

M_0_DQ_4<4>22

M_0_DQ_4<3>22

M_0_DQ_4<2>22

M_0_DQ_4<1>22

M_0_DQ_4<0>22

M_0_DQ_5<7>22

M_0_DQ_5<6>22

M_0_DQ_5<5>22

M_0_DQ_5<4>22

M_0_DQ_5<3>22

M_0_DQ_5<2>22

M_0_DQ_5<1>22

M_0_DQ_5<0>22

M_0_DQ_6<7>22

M_0_DQ_6<6>22

M_0_DQ_6<5>22

M_0_DQ_6<4>22

M_0_DQ_6<3>22

M_0_DQ_6<2>22

M_0_DQ_6<1>22

M_0_DQ_6<0>22

M_0_DQ_7<7>22

M_0_DQ_7<6>22

M_0_DQ_7<5>22

M_0_DQ_7<4>22

M_0_DQ_7<3>22

M_0_DQ_7<2>22

M_0_DQ_7<1>22

M_0_DQ_7<0>22

M_0_DQ_0<7>

M_0_DQ_0<6>

M_0_DQ_0<5>

M_0_DQ_0<4>

M_0_DQ_0<3>

M_0_DQ_0<2>

M_0_DQ_0<1>

M_0_DQ_0<0>

M_0_DQ_1<7>

M_0_DQ_1<6>

M_0_DQ_1<5>

M_0_DQ_1<4>

M_0_DQ_1<3>

M_0_DQ_1<2>

M_0_DQ_1<1>

M_0_DQ_1<0>

M_0_DQ_2<7>

M_0_DQ_2<6>

M_0_DQ_2<5>

M_0_DQ_2<4>

M_0_DQ_2<3>

M_0_DQ_2<2>

M_0_DQ_2<1>

M_0_DQ_2<0>

M_0_DQ_3<7>

M_0_DQ_3<6>

M_0_DQ_3<5>

M_0_DQ_3<4>

M_0_DQ_3<3>

M_0_DQ_3<2>

M_0_DQ_3<1>

M_0_DQ_3<0>

M_0_DQ_4<7>

M_0_DQ_4<6>

M_0_DQ_4<5>

M_0_DQ_4<4>

M_0_DQ_4<3>

M_0_DQ_4<2>

M_0_DQ_4<1>

M_0_DQ_4<0>

M_0_DQ_5<7>

M_0_DQ_5<6>

M_0_DQ_5<5>

M_0_DQ_5<4>

M_0_DQ_5<3>

M_0_DQ_5<2>

M_0_DQ_5<1>

M_0_DQ_5<0>

M_0_DQ_6<7>

M_0_DQ_6<6>

M_0_DQ_6<5>

M_0_DQ_6<4>

M_0_DQ_6<3>

M_0_DQ_6<2>

M_0_DQ_6<1>

M_0_DQ_6<0>

M_0_DQ_7<7>

M_0_DQ_7<6>

M_0_DQ_7<5>

M_0_DQ_7<4>

M_0_DQ_7<3>

M_0_DQ_7<2>

M_0_DQ_7<1>

M_0_DQ_7<0>

LP4-LP5(NIL)/DDR4 (NIL)/DDR4 (IL)

CP53

DDR0_DQ0_7/DDR0_DQ0_7/DDR0_DQ0_7

CP52

DDR0_DQ0_6/DDR0_DQ0_6/DDR0_DQ0_6

CP50

DDR0_DQ0_5/DDR0_DQ0_5/DDR0_DQ0_5

CP49

DDR0_DQ0_4/DDR0_DQ0_4/DDR0_DQ0_4

CU53

DDR0_DQ0_3/DDR0_DQ0_3/DDR0_DQ0_3

CU52

DDR0_DQ0_2/DDR0_DQ0_2/DDR0_DQ0_2

CU50

DDR0_DQ0_1/DDR0_DQ0_1/DDR0_DQ0_1

CU49

DDR0_DQ0_0/DDR0_DQ0_0/DDR0_DQ0_0

CH53

DDR0_DQ1_7/DDR0_DQ1_7/DDR0_DQ1_7

CH52

DDR0_DQ1_6/DDR0_DQ1_6/DDR0_DQ1_6

CH50

DDR0_DQ1_5/DDR0_DQ1_5/DDR0_DQ1_5

CH49

DDR0_DQ1_4/DDR0_DQ1_4/DDR0_DQ1_4

CL53

DDR0_DQ1_3/DDR0_DQ1_3/DDR0_DQ1_3

CL52

DDR0_DQ1_2/DDR0_DQ1_2/DDR0_DQ1_2

CL50

DDR0_DQ1_1/DDR0_DQ1_1/DDR0_DQ1_1

CL49

DDR0_DQ1_0/DDR0_DQ1_0/DDR0_DQ1_0

CT47

DDR1_DQ0_7/DDR0_DQ2_7/DDR1_DQ0_7

CV47

DDR1_DQ0_6/DDR0_DQ2_6/DDR1_DQ0_6

CT45

DDR1_DQ0_5/DDR0_DQ2_5/DDR1_DQ0_5

CV45

DDR1_DQ0_4/DDR0_DQ2_4/DDR1_DQ0_4

CT42

DDR1_DQ0_3/DDR0_DQ2_3/DDR1_DQ0_3

CV42

DDR1_DQ0_2/DDR0_DQ2_2/DDR1_DQ0_2

CT41

DDR1_DQ0_1/DDR0_DQ2_1/DDR1_DQ0_1

CV41

DDR1_DQ0_0/DDR0_DQ2_0/DDR1_DQ0_0

CK47

DDR1_DQ1_7/DDR0_DQ3_7/DDR1_DQ1_7

CM47

DDR1_DQ1_6/DDR0_DQ3_6/DDR1_DQ1_6

CK45

DDR1_DQ1_5/DDR0_DQ3_5/DDR1_DQ1_5

CM45

DDR1_DQ1_4/DDR0_DQ3_4/DDR1_DQ1_4

CK42

DDR1_DQ1_3/DDR0_DQ3_3/DDR1_DQ1_3

CM42

DDR1_DQ1_2/DDR0_DQ3_2/DDR1_DQ1_2

CM41

DDR1_DQ1_1/DDR0_DQ3_1/DDR1_DQ1_1

CK41

DDR1_DQ1_0/DDR0_DQ3_0/DDR1_DQ1_0

BF53

DDR2_DQ0_7/DDR0_DQ4_7/DDR0_DQ2_7

BF52

DDR2_DQ0_6/DDR0_DQ4_6/DDR0_DQ2_6

BF50

DDR2_DQ0_5/DDR0_DQ4_5/DDR0_DQ2_5

BF49

DDR2_DQ0_4/DDR0_DQ4_4/DDR0_DQ2_4

BH53

DDR2_DQ0_3/DDR0_DQ4_3/DDR0_DQ2_3

BH52

DDR2_DQ0_2/DDR0_DQ4_2/DDR0_DQ2_2

BH50

DDR2_DQ0_1/DDR0_DQ4_1/DDR0_DQ2_1

BH49

DDR2_DQ0_0/DDR0_DQ4_0/DDR0_DQ2_0

AY53

DDR2_DQ1_7/DDR0_DQ5_7/DDR0_DQ3_7

AY52

DDR2_DQ1_6/DDR0_DQ5_6/DDR0_DQ3_6

AY50

DDR2_DQ1_5/DDR0_DQ5_5/DDR0_DQ3_5

AY49

DDR2_DQ1_4/DDR0_DQ5_4/DDR0_DQ3_4

BC53

DDR2_DQ1_3/DDR0_DQ5_3/DDR0_DQ3_3

BC52

DDR2_DQ1_2/DDR0_DQ5_2/DDR0_DQ3_2

BC50

DDR2_DQ1_1/DDR0_DQ5_1/DDR0_DQ3_1

BC49

DDR2_DQ1_0/DDR0_DQ5_0/DDR0_DQ3_0

BK47

DDR3_DQ0_7/DDR0_DQ6_7/DDR1_DQ2_7

BK45

DDR3_DQ0_6/DDR0_DQ6_6/DDR1_DQ2_6

BH47

DDR3_DQ0_5/DDR0_DQ6_5/DDR1_DQ2_5

BH45

DDR3_DQ0_4/DDR0_DQ6_4/DDR1_DQ2_4

BH42

DDR3_DQ0_3/DDR0_DQ6_3/DDR1_DQ2_3

BK42

DDR3_DQ0_2/DDR0_DQ6_2/DDR1_DQ2_2

BK41

DDR3_DQ0_1/DDR0_DQ6_1/DDR1_DQ2_1

BH41

DDR3_DQ0_0/DDR0_DQ6_0/DDR1_DQ2_0

BD47

DDR3_DQ1_7/DDR0_DQ7_7/DDR1_DQ3_7

BB47

DDR3_DQ1_6/DDR0_DQ7_6/DDR1_DQ3_6

BD45

DDR3_DQ1_5/DDR0_DQ7_5/DDR1_DQ3_5

BB45

DDR3_DQ1_4/DDR0_DQ7_4/DDR1_DQ3_4

BB42

DDR3_DQ1_3/DDR0_DQ7_3/DDR1_DQ3_3

BB41

DDR3_DQ1_2/DDR0_DQ7_2/DDR1_DQ3_2

BD42

DDR3_DQ1_1/DDR0_DQ7_1/DDR1_DQ3_1

BD41

DDR3_DQ1_0/DDR0_DQ7_0/DDR1_DQ3_0

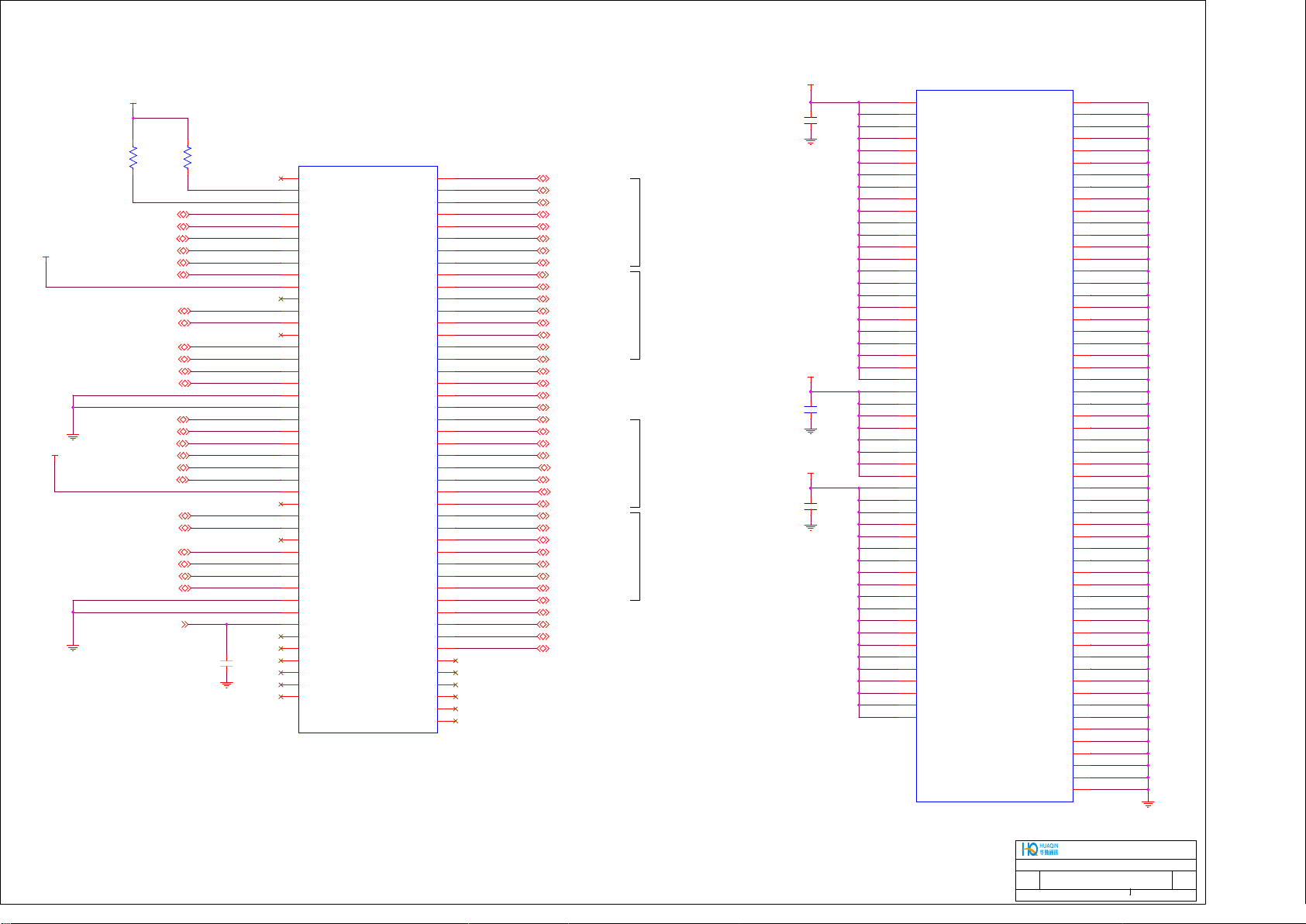

TGL_UP3_IP_EXT/BGA

2 OF 21

DDR0_CLK_P1/DDR3_CLK_P/DDR3_CLK_P/DDR3_CLK_P

DDR0_CLK_N1/DDR3_CLK_N/DDR3_CLK_N/DDR3_CLK

DDR0_CLK_P0/DDR0_CLK_P/DDR0_CLK_P/DDR0_CLK_P

DDR0_CLK_N0/DDR0_CLK_N/DDR0_CLK_N/DDR0_CLK

DDR4/LP4/LP5/LP5 CMD Flip

NC/DDR2_CLK_P/DDR2_CLK_P/DDR2_CLK_P

NC/DDR2_CLK_N/DDR2_CLK_N/DDR2_CLK

NC/DDR1_CLK_P/DDR1_CLK_P/DDR1_CLK_P

NC/DDR1_CLK_N/DDR1_CLK_N/DDR1_CLK

DDR4/LP4/LP5/LP5 CMD Flip

NC/DDR3_CKE0/DDR3_WCK_P/DDR3_WCK_P

NC/DDR3_CKE1/DDR3_WCK_N/DDR3_WCK

NC/DDR2_CKE0/DDR2_WCK_P/DDR2_WCK_P

NC/DDR2_CKE1/DDR2_WCK_N/DDR2_WCK

NC/DDR1_CKE0/DDR1_WCK_P/DDR1_WCK_P

NC/DDR1_CKE1/DDR1_WCK_N/DDR1_WCK

NC/DDR0_CKE0/DDR0_WCK_P/DDR0_WCK_P

NC/DDR0_CKE1/DDR0_WCK_N/DDR0_WCK

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_CKE1/DDR2_CA4/DDR2_CA5/DDR2_CA1

DDR0_CKE0/DDR2_CA5/DDR2_CA6/DDR2_CA0

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_CS1/DDR1_CA1/DDR1_CA1/DDR1_CA5

DDR0_CS0/NC/DDR1_CS1/DDR1_CA4

DDR4/LP4/LP5/LP5 CMD Flip

NC/DDR0_CA0/DDR0_CA0/DDR0_CA6

NC/DDR0_CA1/DDR0_CA1/DDR0_CA5

NC/DDR2_CS0/DDR2_CA2/DDR2_CA2

NC/DDR3_CA5/DDR3_CA6/DDR3_CA0

NC/DDR3_CA4/DDR3_CA5/DDR3_CA1

NC/DDR3_CA3/DDR3_CA4/DDR3_CS1

NC/DDR3_CA2/DDR3_CA3/DDR3_CS0

LP4-LP5(NIL)/DDR4 (NIL)/DDR4 (IL)

DDR3_DQSP_1/DDR0_DQSP_7/DDR1_DQSP_3

DDR3_DQSN_1/DDR0_DQSN_7/DDR1_DQSN_3

DDR3_DQSP_0/DDR0_DQSP_6/DDR1_DQSP_2

DDR3_DQSN_0/DDR0_DQSN_6/DDR1_DQSN_2

DDR2_DQSP_1/DDR0_DQSP_5/DDR0_DQSP_3

DDR2_DQSN_1/DDR0_DQSN_5/DDR0_DQSN_3

DDR2_DQSP_0/DDR0_DQSP_4/DDR0_DQSP_2

DDR2_DQSN_0/DDR0_DQSN_4/DDR0_DQSN_2

DDR1_DQSP_1/DDR0_DQSP_3/DDR1_DQSP_1

DDR1_DQSN_1/DDR0_DQSN_3/DDR1_DQSN_1

DDR1_DQSP_0/DDR0_DQSP_2/DDR1_DQSP_0

DDR1_DQSN_0/DDR0_DQSN_2/DDR1_DQSN_0

DDR0_DQSP_1/DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSN_1/DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSP_0/DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSN_0/DDR0_DQSN_0/DDR0_DQSN_0

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_ODT1/DDR1_CA0/DDR1_CA0/DDR1_CA6

DDR0_ODT0/DDR1_CS0/DDR1_CA2/DDR1_CA2

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_MA16/DDR1_CA4/DDR1_CA5/DDR1_CA1

DDR0_MA15/DDR1_CA3/DDR1_CA4/DDR1_CS1

DDR0_MA14/DDR1_CA2/DDR1_CA3/DDR1_CS0

DDR0_MA13/DDR1_CS1/DDR1_CS0/DDR1_CA3

DDR0_MA12/DDR2_CA1/DDR2_CA1/DDR2_CA5

DDR0_MA11/NC/DDR2_CS1/DDR2_CA4

DDR0_MA10/DDR3_CA1/DDR3_CA1/DDR3_CA5

DDR0_MA9/DDR2_CA0/DDR2_CA0/DDR2_CA6

DDR0_MA8/DDR0_CA2/DDR0_CA3/DDR0_CS0

DDR0_MA7/DDR0_CA4/DDR0_CA5/DDR0_CA1

DDR0_MA6/DDR0_CA3/DDR0_CA4/DDR0_CS1

DDR0_MA5/DDR0_CA5/DDR0_CA6/DDR0_CA0

DDR0_MA4/DDR0_CS0/DDR0_CA2/DDR0_CA2

DDR0_MA3/DDR0_CS1/DDR0_CS0/DDR0_CA3

DDR0_MA2/DDR3_CS0/DDR3_CA2/DDR3_CA2

DDR0_MA1/NC/DDR0_CS1/DDR0_CA4

DDR0_MA0/NC/DDR3_CS1/DDR3_CA4

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_BG1/DDR2_CA2/DDR2_CA3/DDR2_CS0

DDR0_BG0/DDR2_CA3/DDR2_CA4/DDR2_CS1

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_BA1/DDR1_CA5/DDR1_CA6/DDR1_CA0

DDR0_BA0/DDR3_CA0/DDR3_CA0/DDR3_CA6

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_ACT#/DDR2_CS1/DDR2_CS0/DDR2_CA3

DDR4/LP4/LP5/LP5 CMD Flip

DDR0_PAR/DDR3_CS1/DDR3_CS0/DDR3_CA3

DDR0_ALERT#

DDR0_VREF_CA

DDR_VTT_CTL

DRAM_RESET#

DDR_RCOMP

M_0_LP4_3CLK_DP

BT42

M_0_LP4_3CLK_DN

BT41

M_0_LP4_2CLK_DP

BP52

M_0_LP4_2CLK_DN

BP53

M_0_LP4_1CLK_DP

CD42

M_0_LP4_1CLK_DN

CD41

M_0_LP4_0CLK_DP

CC52

M_0_LP4_0CLK_DN

CC53

M_0_LP4_3CKE0

BT45

M_0_LP4_3CKE1

BT47

M_0_LP4_2CKE0

BN51

M_0_LP4_2CKE1

BN53

M_0_LP4_1CKE0

CD45

M_0_LP4_1CKE1

CD47

M_0_LP4_0CKE0

CA51

M_0_LP4_0CKE1

CA53

M_0_LP4_2CA4

BU52

M_0_LP4_2CA5

BL50

M_0_LP4_1CA1

CF42

CF47

M_0_LP4_0CA0

CE53

M_0_LP4_0CA1

CE50

M_0_LP4_2CS0

BL53

M_0_LP4_3CA5

BP47

M_0_LP4_3CA4

BP42

M_0_LP4_3CA3

BP45

M_0_LP4_3CA2

BP44

M_0_DQS_7_DP

BB44

M_0_DQS_7_DN

BD44

M_0_DQS_6_DP

BK44

M_0_DQS_6_DN

BH44

M_0_DQS_5_DP

BA51

M_0_DQS_5_DN

BA50

M_0_DQS_4_DP

BG51

M_0_DQS_4_DN

BG50

M_0_DQS_3_DP

CK44

M_0_DQS_3_DN

CM44

M_0_DQS_2_DP

CT44

M_0_DQS_2_DN

CV44

M_0_DQS_1_DP

CK51

M_0_DQS_1_DN

CK50

M_0_DQS_0_DP

CR51

M_0_DQS_0_DN

CR50

M_0_LP4_1CA0

CF44

M_0_LP4_1CS0

CF45

M_0_LP4_1CA4

CB47

M_0_LP4_1CA3

CB44

M_0_LP4_1CA2

CB45

M_0_LP4_1CS1

CF41

M_0_LP4_2CA1

BU53

BT51

M_0_LP4_3CA1

BV42

M_0_LP4_2CA0

BU50

M_0_LP4_0CA2

BY53

M_0_LP4_0CA4

CA50

M_0_LP4_0CA3

BY52

M_0_LP4_0CA5

BY50

M_0_LP4_0CS0

CD51

M_0_LP4_0CS1

CD53

M_0_LP4_3CS0

BV47

CE52

BV41

M_0_LP4_2CA2

BN50

M_0_LP4_2CA3

BL52

M_0_LP4_1CA5

CB42

M_0_LP4_3CA0

BV44

M_0_LP4_2CS1

BT53

M_0_LP4_3CS1

BV45

AU50

?

TP_+V_D4CH0_CA_VREF

AU49

TP_DDR_VTT_CTRL

E52

DV47

DDR_RCOMP_0

C49

M_0_LP4_3CLK_DP 22

M_0_LP4_3CLK_DN 22

M_0_LP4_2CLK_DP 22

M_0_LP4_2CLK_DN 22

M_0_LP4_1CLK_DP 21

M_0_LP4_1CLK_DN 21

M_0_LP4_0CLK_DP 21

M_0_LP4_0CLK_DN 21

M_0_LP4_3CKE0 22

M_0_LP4_3CKE1 22

M_0_LP4_2CKE0 22

M_0_LP4_2CKE1 22

M_0_LP4_1CKE0 21

M_0_LP4_1CKE1 21

M_0_LP4_0CKE0 21

M_0_LP4_0CKE1 21

M_0_LP4_2CA4 22

M_0_LP4_2CA5 22

M_0_LP4_1CA1 21

M_0_LP4_0CA0 21

M_0_LP4_0CA1 21

M_0_LP4_2CS0 22

M_0_LP4_3CA5 22

M_0_LP4_3CA4 22

M_0_LP4_3CA3 22

M_0_LP4_3CA2 22

M_0_DQS_7_DP 22

M_0_DQS_7_DN 22

M_0_DQS_6_DP 22

M_0_DQS_6_DN 22

M_0_DQS_5_DP 22

M_0_DQS_5_DN 22

M_0_DQS_4_DP 22

M_0_DQS_4_DN 22

M_0_DQS_3_DP 21

M_0_DQS_3_DN 21

M_0_DQS_2_DP 21

M_0_DQS_2_DN 21

M_0_DQS_1_DP 21

M_0_DQS_1_DN 21

M_0_DQS_0_DP 21

M_0_DQS_0_DN 21

M_0_LP4_1CA0 21

M_0_LP4_1CS0 21

M_0_LP4_1CA4 21

M_0_LP4_1CA3 21

M_0_LP4_1CA2 21

M_0_LP4_1CS1 21

M_0_LP4_2CA1 22

M_0_LP4_3CA1 22

M_0_LP4_2CA0 22

M_0_LP4_0CA2 21

M_0_LP4_0CA4 21

M_0_LP4_0CA3 21

M_0_LP4_0CA5 21

M_0_LP4_0CS0 21

M_0_LP4_0CS1 21

M_0_LP4_3CS0 22

M_0_LP4_2CA2 22

M_0_LP4_2CA3 22

M_0_LP4_1CA5 21

M_0_LP4_3CA0 22

M_0_LP4_2CS1 22

M_0_LP4_3CS1 22

1

TPU2 18MIL

ns

1

TPU4 18MIL

ns

电阻

_100R_0201_1/20 W_F

RU1

+VDDQ_CPU

RU2

电阻

电阻

_0R_0201_1/20 W_J(±5%)

_470R_0201_1/20 W_J

RU3

电容

DRAM_RESET_N_RDRAM_RESET_N

_100nF_0201_X5R_6.3 V_K(±10%)

CU173

DRAM_RESET_N_R 21,22,23,24

ns

PLACE RESET COMPONENTS CLOSE TO CPU

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date:

Date:

5

4

3

2

Date:

Huaqin Telecom Technology Com.,Ltd.

TGL-UP3(CHA)

TGL-UP3(CHA)

TGL-UP3(CHA)

Project

Project

Project

Name:

Name:

Name:

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Thursday, July 09, 2020 5 84

Thursday, July 09, 2020 5 84

Thursday, July 09, 2020 5 84

1

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

V4.0

V4.0

V4.0

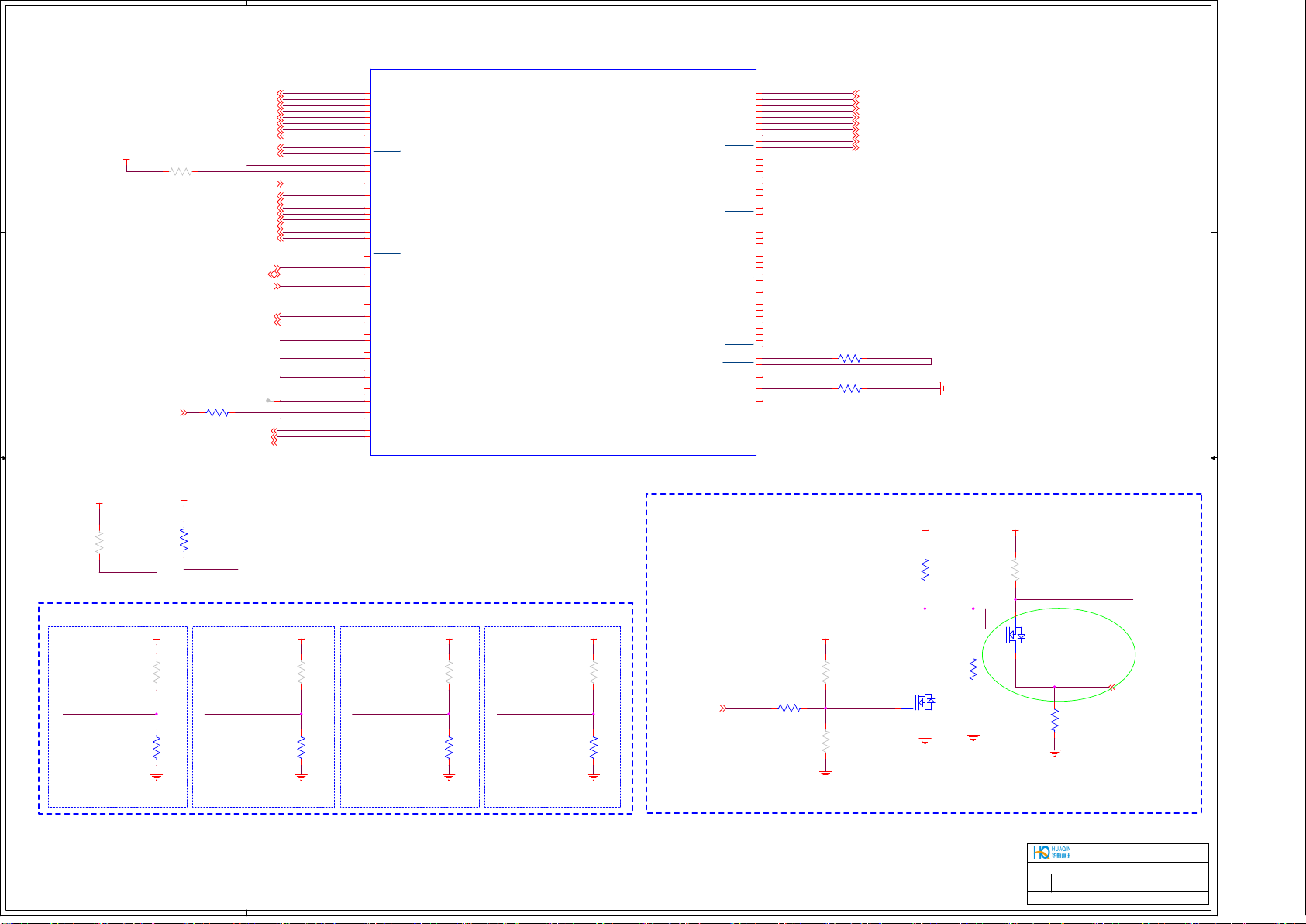

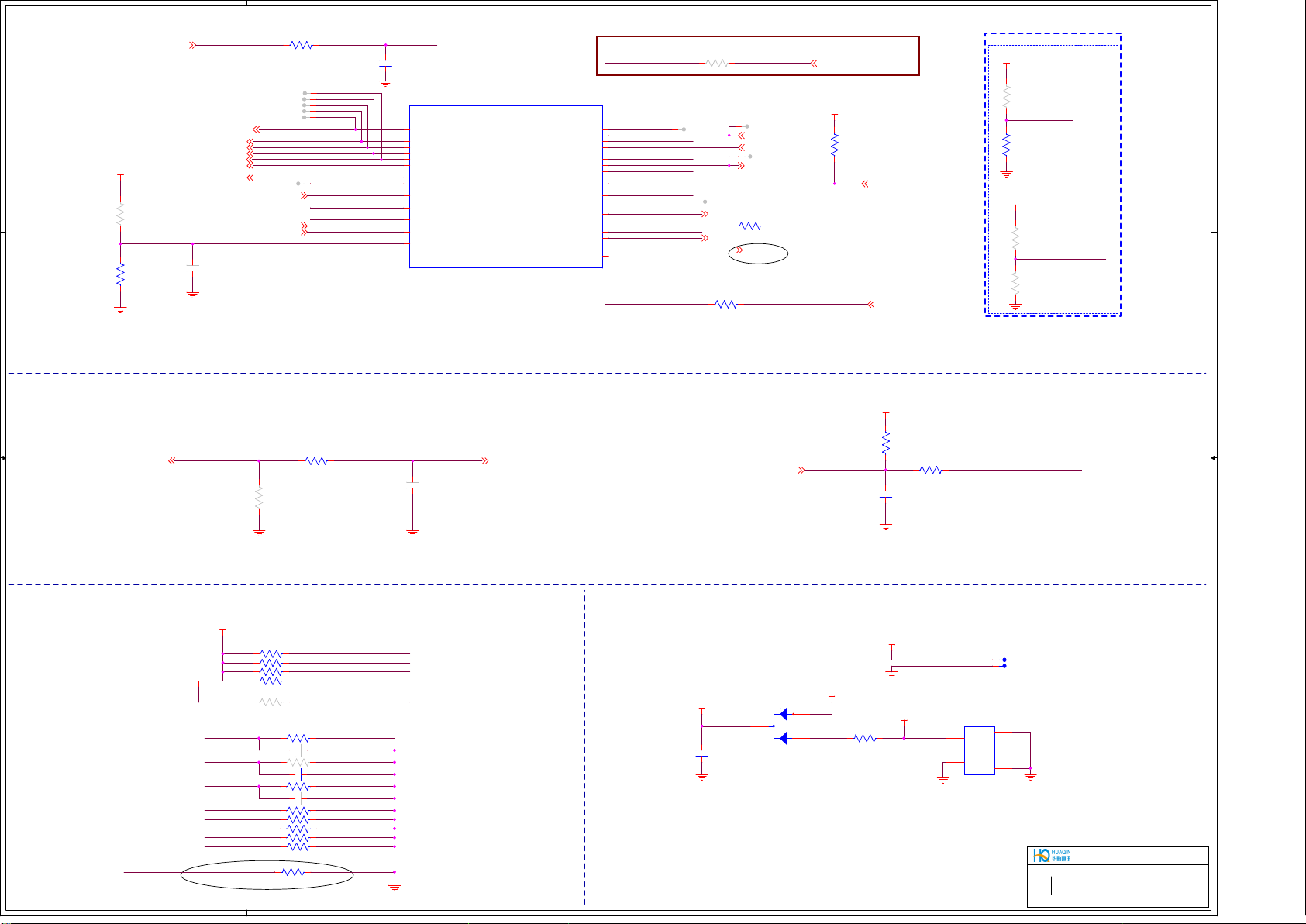

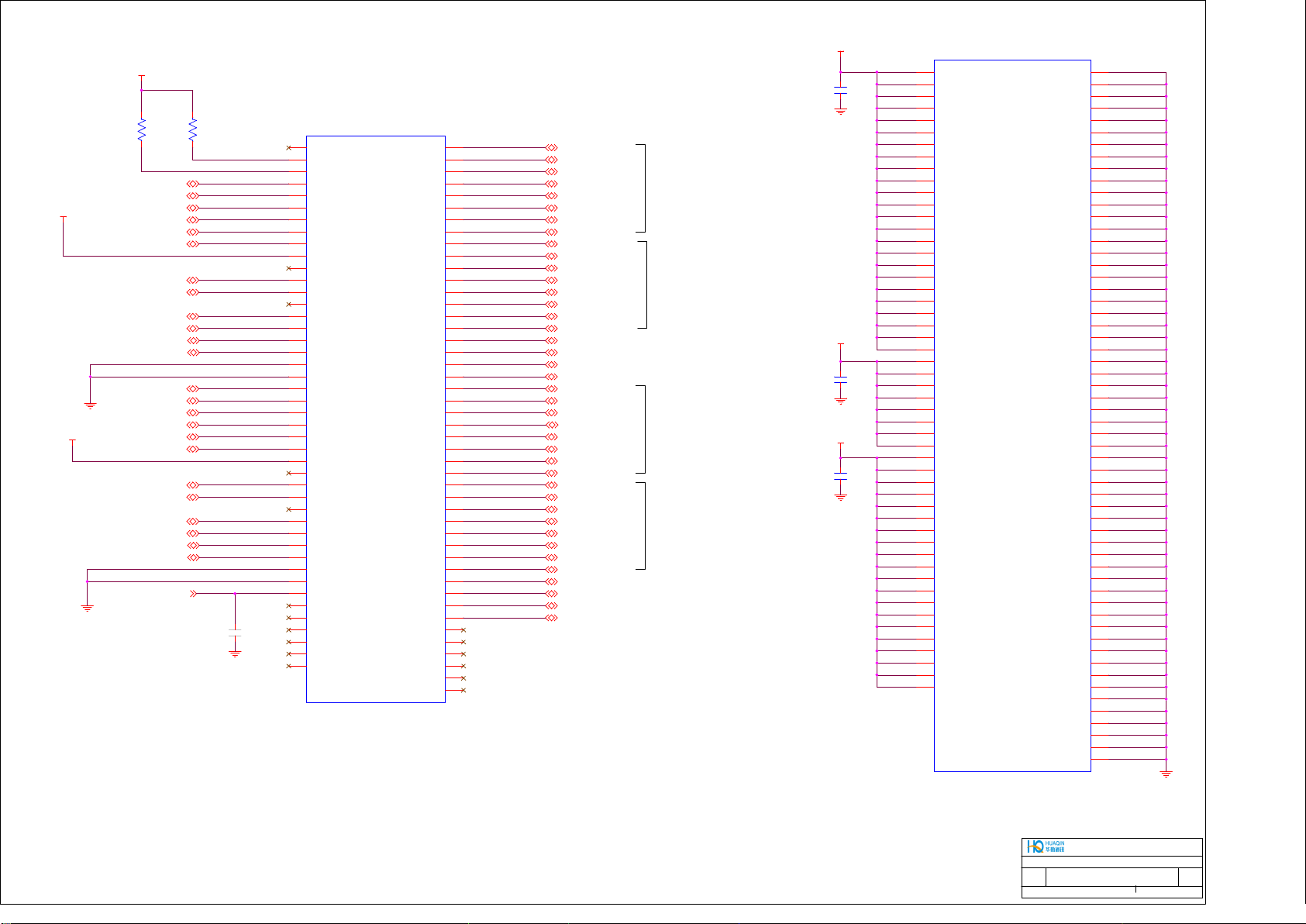

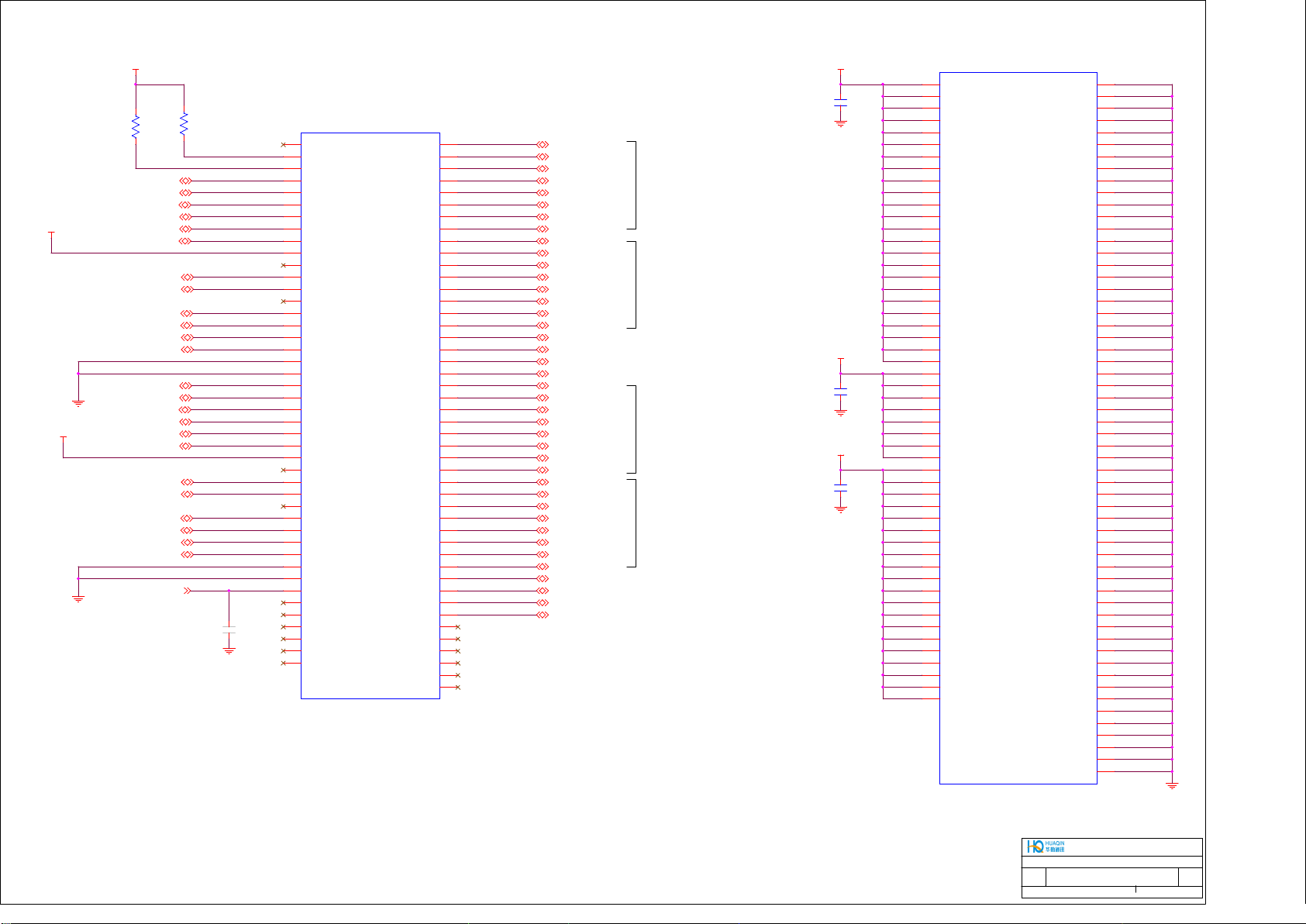

CHB

5

4

3

2

1

D D

M_1_DQ_0<7>23

M_1_DQ_0<6>23

M_1_DQ_0<5>23

BYTE0

BYTE1

BYTE2

BYTE3

C C

BYTE4

BYTE5

BYTE6

BYTE7

B B

M_1_DQ_0<4>23

M_1_DQ_0<3>23

M_1_DQ_0<2>23

M_1_DQ_0<1>23

M_1_DQ_0<0>23

M_1_DQ_1<7>23

M_1_DQ_1<6>23

M_1_DQ_1<5>23

M_1_DQ_1<4>23

M_1_DQ_1<3>23

M_1_DQ_1<2>23

M_1_DQ_1<1>23

M_1_DQ_1<0>23

M_1_DQ_2<7>23

M_1_DQ_2<6>23

M_1_DQ_2<5>23

M_1_DQ_2<4>23

M_1_DQ_2<3>23

M_1_DQ_2<2>23

M_1_DQ_2<1>23

M_1_DQ_2<0>23

M_1_DQ_3<7>23

M_1_DQ_3<6>23

M_1_DQ_3<5>23

M_1_DQ_3<4>23

M_1_DQ_3<3>23

M_1_DQ_3<2>23

M_1_DQ_3<1>23

M_1_DQ_3<0>23

M_1_DQ_4<7>24

M_1_DQ_4<6>24

M_1_DQ_4<5>24

M_1_DQ_4<4>24

M_1_DQ_4<3>24

M_1_DQ_4<2>24

M_1_DQ_4<1>24

M_1_DQ_4<0>24

M_1_DQ_5<7>24

M_1_DQ_5<6>24

M_1_DQ_5<5>24

M_1_DQ_5<4>24

M_1_DQ_5<3>24

M_1_DQ_5<2>24

M_1_DQ_5<1>24

M_1_DQ_5<0>24

M_1_DQ_6<7>24

M_1_DQ_6<6>24

M_1_DQ_6<5>24

M_1_DQ_6<4>24

M_1_DQ_6<3>24

M_1_DQ_6<2>24

M_1_DQ_6<1>24

M_1_DQ_6<0>24

M_1_DQ_7<7>24

M_1_DQ_7<6>24

M_1_DQ_7<5>24

M_1_DQ_7<4>24

M_1_DQ_7<3>24

M_1_DQ_7<2>24

M_1_DQ_7<1>24

M_1_DQ_7<0>24

M_1_DQ_0<7>

M_1_DQ_0<6>

M_1_DQ_0<5>

M_1_DQ_0<4>

M_1_DQ_0<3>

M_1_DQ_0<2>

M_1_DQ_0<1>

M_1_DQ_0<0>

M_1_DQ_1<7>

M_1_DQ_1<6>

M_1_DQ_1<5>

M_1_DQ_1<4>

M_1_DQ_1<3>

M_1_DQ_1<2>

M_1_DQ_1<1>

M_1_DQ_1<0>

M_1_DQ_2<7>

M_1_DQ_2<6>

M_1_DQ_2<5>

M_1_DQ_2<4>

M_1_DQ_2<3>

M_1_DQ_2<2>

M_1_DQ_2<1>

M_1_DQ_2<0>

M_1_DQ_3<7>

M_1_DQ_3<6>

M_1_DQ_3<5>

M_1_DQ_3<4>

M_1_DQ_3<3>

M_1_DQ_3<2>

M_1_DQ_3<1>

M_1_DQ_3<0>

M_1_DQ_4<7>

M_1_DQ_4<6>

M_1_DQ_4<5>

M_1_DQ_4<4>

M_1_DQ_4<3>

M_1_DQ_4<2>

M_1_DQ_4<1>

M_1_DQ_4<0>

M_1_DQ_5<7>

M_1_DQ_5<6>

M_1_DQ_5<5>

M_1_DQ_5<4>

M_1_DQ_5<3>

M_1_DQ_5<2>

M_1_DQ_5<1>

M_1_DQ_5<0>

M_1_DQ_6<7>

M_1_DQ_6<6>

M_1_DQ_6<5>

M_1_DQ_6<4>

M_1_DQ_6<3>

M_1_DQ_6<2>

M_1_DQ_6<1>

M_1_DQ_6<0>

M_1_DQ_7<7>

M_1_DQ_7<6>

M_1_DQ_7<5>

M_1_DQ_7<4>

M_1_DQ_7<3>

M_1_DQ_7<2>

M_1_DQ_7<1>

M_1_DQ_7<0>

UU1C

LP4-LP5(NIL)/DDR4 (NIL)/DDR4 (IL)

AL53

DDR4_DQ0_7/DDR1_DQ0_7/DDR0_DQ4_7

AL52

DDR4_DQ0_6/DDR1_DQ0_6/DDR0_DQ4_6

AL50

DDR4_DQ0_5/DDR1_DQ0_5/DDR0_DQ4_5

AL49

DDR4_DQ0_4/DDR1_DQ0_4/DDR0_DQ4_4

AP53

DDR4_DQ0_3/DDR1_DQ0_3/DDR0_DQ4_3

AP52

DDR4_DQ0_2/DDR1_DQ0_2/DDR0_DQ4_2

AP50

DDR4_DQ0_1/DDR1_DQ0_1/DDR0_DQ4_1

AP49

DDR4_DQ0_0/DDR1_DQ0_0/DDR0_DQ4_0

AF53

DDR4_DQ1_7/DDR1_DQ1_7/DDR0_DQ5_7

AF52

DDR4_DQ1_6/DDR1_DQ1_6/DDR0_DQ5_6

AF50

DDR4_DQ1_5/DDR1_DQ1_5/DDR0_DQ5_5

AF49

DDR4_DQ1_4/DDR1_DQ1_4/DDR0_DQ5_4

AH53

DDR4_DQ1_3/DDR1_DQ1_3/DDR0_DQ5_3

AH52

DDR4_DQ1_2/DDR1_DQ1_2/DDR0_DQ5_2

AH50

DDR4_DQ1_1/DDR1_DQ1_1/DDR0_DQ5_1

AH49

DDR4_DQ1_0/DDR1_DQ1_0/DDR0_DQ5_0

AR41

DDR5_DQ0_7/DDR1_DQ2_7/DDR1_DQ4_7

AV42

DDR5_DQ0_6/DDR1_DQ2_6/DDR1_DQ4_6

AR42

DDR5_DQ0_5/DDR1_DQ2_5/DDR1_DQ4_5

AV41

DDR5_DQ0_4/DDR1_DQ2_4/DDR1_DQ4_4

AR45

DDR5_DQ0_3/DDR1_DQ2_3/DDR1_DQ4_3

AV45

DDR5_DQ0_2/DDR1_DQ2_2/DDR1_DQ4_2

AR47

DDR5_DQ0_1/DDR1_DQ2_1/DDR1_DQ4_1

AV47

DDR5_DQ0_0/DDR1_DQ2_0/DDR1_DQ4_0

AJ41

DDR5_DQ1_7/DDR1_DQ3_7/DDR1_DQ5_7

AJ42

DDR5_DQ1_6/DDR1_DQ3_6/DDR1_DQ5_6

AL41

DDR5_DQ1_5/DDR1_DQ3_5/DDR1_DQ5_5

AL42

DDR5_DQ1_4/DDR1_DQ3_4/DDR1_DQ5_4

AJ45

DDR5_DQ1_3/DDR1_DQ3_3/DDR1_DQ5_3

AJ47

DDR5_DQ1_2/DDR1_DQ3_2/DDR1_DQ5_2

AL45

DDR5_DQ1_1/DDR1_DQ3_1/DDR1_DQ5_1

AL47

DDR5_DQ1_0/DDR1_DQ3_0/DDR1_DQ5_0

A43

DDR6_DQ0_7/DDR1_DQ4_7/DDR0_DQ6_7

B43

DDR6_DQ0_6/DDR1_DQ4_6/DDR0_DQ6_6

D43

DDR6_DQ0_5/DDR1_DQ4_5/DDR0_DQ6_5

E44

DDR6_DQ0_4/DDR1_DQ4_4/DDR0_DQ6_4

A46

DDR6_DQ0_3/DDR1_DQ4_3/DDR0_DQ6_3

B46

DDR6_DQ0_2/DDR1_DQ4_2/DDR0_DQ6_2

D46

DDR6_DQ0_1/DDR1_DQ4_1/DDR0_DQ6_1

E47

DDR6_DQ0_0/DDR1_DQ4_0/DDR0_DQ6_0

E38

DDR6_DQ1_7/DDR1_DQ5_7/DDR0_DQ7_7

D38

DDR6_DQ1_6/DDR1_DQ5_6/DDR0_DQ7_6

B38

DDR6_DQ1_5/DDR1_DQ5_5/DDR0_DQ7_5

A38

DDR6_DQ1_4/DDR1_DQ5_4/DDR0_DQ7_4

E41

DDR6_DQ1_3/DDR1_DQ5_3/DDR0_DQ7_3

D40

DDR6_DQ1_2/DDR1_DQ5_2/DDR0_DQ7_2

B40

DDR6_DQ1_1/DDR1_DQ5_1/DDR0_DQ7_1

A40

DDR6_DQ1_0/DDR1_DQ5_0/DDR0_DQ7_0

G42

DDR7_DQ0_7/DDR1_DQ6_7/DDR1_DQ6_7

G41

DDR7_DQ0_6/DDR1_DQ6_6/DDR1_DQ6_6

J41

DDR7_DQ0_5/DDR1_DQ6_5/DDR1_DQ6_5

J42

DDR7_DQ0_4/DDR1_DQ6_4/DDR1_DQ6_4

G45

DDR7_DQ0_3/DDR1_DQ6_3/DDR1_DQ6_3

J45

DDR7_DQ0_2/DDR1_DQ6_2/DDR1_DQ6_2

G47

DDR7_DQ0_1/DDR1_DQ6_1/DDR1_DQ6_1

J47

DDR7_DQ0_0/DDR1_DQ6_0/DDR1_DQ6_0

G38

DDR7_DQ1_7/DDR1_DQ7_7/DDR1_DQ7_7

G36

DDR7_DQ1_6/DDR1_DQ7_6/DDR1_DQ7_6

H36

DDR7_DQ1_5/DDR1_DQ7_5/DDR1_DQ7_5

H38

DDR7_DQ1_4/DDR1_DQ7_4/DDR1_DQ7_4

N36

DDR7_DQ1_3/DDR1_DQ7_3/DDR1_DQ7_3

L36

DDR7_DQ1_2/DDR1_DQ7_2/DDR1_DQ7_2

L38

DDR7_DQ1_1/DDR1_DQ7_1/DDR1_DQ7_1

N38

DDR7_DQ1_0/DDR1_DQ7_0/DDR1_DQ7_0

TGL_UP3_IP_EXT/BGA

3 OF 21

DDR1_CLK_P1/DDR7_CLK_P/DDR7_CLK_P/DDR7_CLK_P

DDR1_CLK_N1/DDR7_CLK_N/DDR7_CLK_N/DDR7_CLK

DDR1_CLK_P0/DDR4_CLK_P/DDR4_CLKP/DDR4_CLK_P

DDR1_CLK_N0/DDR4_CLK_N/DDR4_CLK_N/DDR4_CLK

DDR1_CKE1/DDR6_CA4/DDR6_CA5/DDR6_CA1

DDR1_CKE0/DDR6_CA5/DDR6_CA6/DDR6_CA0

DDR7_DQSN_1/DDR1_DQSN_7/DDR1_DQSN_7

DDR7_DQSN_0/DDR1_DQSN_6/DDR1_DQSN_6

DDR6_DQSN_1/DDR1_DQSN_5/DDR0_DQSN_7

DDR6_DQSN_0/DDR1_DQSN_4/DDR0_DQSN_6

DDR5_DQSN_1/DDR1_DQSN_3/DDR1_DQSN_5

DDR5_DQSN_0/DDR1_DQSN_2/DDR1_DQSN_4

DDR4_DQSN_1/DDR1_DQSN_1/DDR0_DQSN_5

DDR4_DQSN_0/DDR1_DQSN_0/DDR0_DQSN_4

DDR1_ODT1/DDR5_CA0/DDR5_CA0/DDR5_CA6

DDR1_ODT0/DDR5_CS0/DDR5_CA2/DDR5_CA2

DDR1_MA16/DDR5_CA4/DDR5_CA5/DDR5_CA1

DDR1_MA15/DDR5_CA3/DDR5_CA4/DDR5_CS1

DDR1_MA14/DDR5_CA2/DDR5_CA3/DDR5_CS0

DDR1_MA13/DDR5_CS1/DDR5_CS0/DDR5_CA3

DDR1_MA12/DDR6_CA1/DDR6_CA1/DDR6_CA5

DDR1_MA10/DDR7_CA1/DDR7_CA1/DDR7_CA5

DDR1_ACT#/DDR6_CS1/DDR6_CS0/DDR6_CA3

DDR4/LP4/LP5/LP5 CMD Flip

NC/DDR6_CLK_P/DDR6_CLK_P/DDR6_CLK_P

NC/DDR6_CLK_N/DDR6_CLK_N/DDR6_CLK

NC/DDR5_CLK_P/DDR5_CLK_P/DDR5_CLK_P

NC/DDR5_CLK_N/DDR5_CLK_N/DDR5_CLK

DDR4/LP4/LP5/LP5 CMD Flip

NC/DDR7_CKE0/DDR7_WCK_P/DDR7_WCK_P

NC/DDR7_CKE1/DDR7_WCK_N/DDR7_WCK

NC/DDR6_CKE0/DDR6_WCK_P/DDR6_WCK_P

NC/DDR6_CKE1/DDR6_WCK_N/DDR6_WCK

NC/DDR5_CKE0/DDR5_WCK_P/DDR5_WCK_P

NC/DDR5_CKE1/DDR5_WCK_N/DDR5_WCK

NC/DDR4_CKE0/DDR4_WCK_P/DDR4_WCK_P

NC/DDR4_CKE1/DDR4_WCK_N/DDR4_WCK

DDR4/LP4/LP5/LP5 CMD Flip

DDR4/LP4/LP5/LP5 CMD Flip

DDR1_CS1/DDR5_CA1/DDR5_CA1/DDR5_CA5

DDR1_CS0/NC/DDR5_CS1/DDR5_CA4

DDR4/LP4/LP5/LP5 CMD Flip

NC/DDR7_CA5/DDR7_CA6/DDR7_CA0

NC/DDR7_CA4/DDR7_CA5/DDR7_CA1

NC/DDR7_CA3/DDR7_CA4/DDR7_CS1

NC/DDR7_CA2/DDR7_CA3/DDR7_CS0

NC/DDR6_CS0/DDR6_CA2/DDR6_CA2

NC/DDR4_CA1/DDR4_CA1/DDR4_CA5

NC/DDR4_CA0/DDR4_CA0/DDR4_CA6

LP4-LP5(NIL)/DDR4 (NIL)/DDR4 (IL)

DDR7_DQSP_1/DDR1_DQSP_7/DDR1_DQSP_7

DDR7_DQSP_0/DDR1_DQSP_6/DDR1_DQSP_6

DDR6_DQSP_1/DDR1_DQSP_5/DDR0_DQSP_7

DDR6_DQSP_0/DDR1_DQSP_4/DDR0_DQSP_6

DDR5_DQSP_1/DDR1_DQSP_3/DDR1_DQSP_5

DDR5_DQSP_0/DDR1_DQSP_2/DDR1_DQSP_4

DDR4_DQSP_1/DDR1_DQSP_1/DDR0_DQSP_5

DDR4_DQSP_0/DDR1_DQSP_0/DDR0_DQSP_4

DDR4/LP4/LP5/LP5 CMD Flip

DDR4/LP4/LP5/LP5 CMD Flip

DDR1_MA11/NC/DDR6_CS1/DDR6_CA4

DDR1_MA9/DDR6_CA0/DDR6_CA0/DDR6_CA6

DDR1_MA8/DDR4_CA2/DDR4_CA3/DDR4_CS0

DDR1_MA7/DDR4_CA4/DDR4_CA5/DDR4_CA1

DDR1_MA6/DDR4_CA3/DDR4_CA4/DDR4_CS1

DDR1_MA5/DDR4_CA5/DDR4_CA6/DDR4_CA0

DDR1_MA4/DDR4_CS0/DDR4_CA2/DDR4_CA2

DDR1_MA3/DDR4_CS1/DDR4_CS0/DDR4_CA3

DDR1_MA2/DDR7_CS0/DDR7_CA2/DDR7_CA2

DDR1_MA1/NC/DDR4_CS1/DDR4_CA4

DDR1_MA0/NC/DDR7_CS1/DDR7_CA4

DDR4/LP4/LP5/LP5 CMD Flip

DDR1_BG1/DDR6_CA2/DDR6_CA3/DDR6_CS0

DDR1_BG0/DDR6_CA3/DDR6_CA4/DDR6_CS1

DDR4/LP4/LP5/LP5 CMD Flip

DDR1_BA1/DDR5_CA5/DDR5_CA6/DDR5_CA0

DDR1_BA0/DDR7_CA0/DDR7_CA0/DDR7_CA6

DDR1_PAR/DDR7_CS1/DDR7_CS0/DDR7_CA3

DDR1_ALERT#

DDR1_VREF_CA

M_1_LP4_7CLK_DP

R41

M_1_LP4_7CLK_DN

R42

M_1_LP4_6CLK_DP

M52

M_1_LP4_6CLK_DN

M53

M_1_LP4_5CLK_DP

AC42

M_1_LP4_5CLK_DN

AC41

M_1_LP4_4CLK_DP

Y52

M_1_LP4_4CLK_DN

Y53

M_1_LP4_7CKE0

R47

M_1_LP4_7CKE1

R45

M_1_LP4_6CKE0

K51

M_1_LP4_6CKE1

K53

M_1_LP4_5CKE0

AC47

M_1_LP4_5CKE1

AC45

M_1_LP4_4CKE0

W51

M_1_LP4_4CKE1

W53

M_1_LP4_6CA4

P52

M_1_LP4_6CA5

J50

M_1_LP4_5CA1

AE42

?

AE47

M_1_LP4_7CA5

N42

M_1_LP4_7CA4

N45

M_1_LP4_7CA3

N44

M_1_LP4_7CA2

N47

M_1_LP4_6CS0

J53

M_1_LP4_4CA1

AC50

M_1_LP4_4CA0

AC53

M_1_DQS_7_DP

K36

M_1_DQS_7_DN

K38

M_1_DQS_6_DP

G44

M_1_DQS_6_DN

J44

M_1_DQS_5_DP

D39

M_1_DQS_5_DN

C39

M_1_DQS_4_DP

C45

M_1_DQS_4_DN

D45

M_1_DQS_3_DP

AJ44

M_1_DQS_3_DN

AL44

M_1_DQS_2_DP

AV44

M_1_DQS_2_DN

AR44

M_1_DQS_1_DP

AG51

M_1_DQS_1_DN

AG50

M_1_DQS_0_DP

AN51

M_1_DQS_0_DN

AN50

M_1_LP4_5CA0

AE44

M_1_LP4_5CS0

AE45

M_1_LP4_5CA4

AA47

M_1_LP4_5CA3

AA44

M_1_LP4_5CA2

AA45

M_1_LP4_5CS1

AE41

M_1_LP4_6CA1

P53

N51

M_1_LP4_7CA1

U42

M_1_LP4_6CA0

P50

M_1_LP4_4CA2

U53

M_1_LP4_4CA4

W50

M_1_LP4_4CA3

U52

M_1_LP4_4CA5

U50

M_1_LP4_4CS0

AA51

M_1_LP4_4CS1

AA53

M_1_LP4_7CS0

U47

AC52

U41

M_1_LP4_6CA2

K50

M_1_LP4_6CA3

J52

M_1_LP4_5CA5

AA42

M_1_LP4_7CA0

U44

M_1_LP4_6CS1

N53

M_1_LP4_7CS1

U45

AU53

TP_+V_D4CH1_CA_VREF

AU52

M_1_LP4_7CLK_DP 24

M_1_LP4_7CLK_DN 24

M_1_LP4_6CLK_DP 24

M_1_LP4_6CLK_DN 24

M_1_LP4_5CLK_DP 23

M_1_LP4_5CLK_DN 23

M_1_LP4_4CLK_DP 23

M_1_LP4_4CLK_DN 23

M_1_LP4_7CKE0 24

M_1_LP4_7CKE1 24

M_1_LP4_6CKE0 24

M_1_LP4_6CKE1 24

M_1_LP4_5CKE0 23

M_1_LP4_5CKE1 23

M_1_LP4_4CKE0 23

M_1_LP4_4CKE1 23

M_1_LP4_6CA4 24

M_1_LP4_6CA5 24

M_1_LP4_5CA1 23

M_1_LP4_7CA5 24

M_1_LP4_7CA4 24

M_1_LP4_7CA3 24

M_1_LP4_7CA2 24

M_1_LP4_6CS0 24

M_1_LP4_4CA1 23

M_1_LP4_4CA0 23

M_1_DQS_7_DP 24

M_1_DQS_7_DN 24

M_1_DQS_6_DP 24

M_1_DQS_6_DN 24

M_1_DQS_5_DP 24

M_1_DQS_5_DN 24

M_1_DQS_4_DP 24

M_1_DQS_4_DN 24

M_1_DQS_3_DP 23

M_1_DQS_3_DN 23

M_1_DQS_2_DP 23

M_1_DQS_2_DN 23

M_1_DQS_1_DP 23

M_1_DQS_1_DN 23

M_1_DQS_0_DP 23

M_1_DQS_0_DN 23

M_1_LP4_5CA0 23

M_1_LP4_5CS0 23

M_1_LP4_5CA4 23

M_1_LP4_5CA3 23

M_1_LP4_5CA2 23

M_1_LP4_5CS1 23

M_1_LP4_6CA1 24

M_1_LP4_7CA1 24

M_1_LP4_6CA0 24

M_1_LP4_4CA2 23

M_1_LP4_4CA4 23

M_1_LP4_4CA3 23

M_1_LP4_4CA5 23

M_1_LP4_4CS0 23

M_1_LP4_4CS1 23

M_1_LP4_7CS0 24

M_1_LP4_6CA2 24

M_1_LP4_6CA3 24

M_1_LP4_5CA5 23

M_1_LP4_7CA0 24

M_1_LP4_6CS1 24

M_1_LP4_7CS1 24

1

ns

TPU1 18MIL

UU1D

4 OF 21

DV24

RSVD_2

?

DW47

RSVD_3

?

DW49

RSVD_4

?

A48

RSVD_5

?

A A

5

4

TGL_UP3_IP_EXT/BGA

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date:

Date:

Date:

3

2

Huaqin Telecom Technology Com.,Ltd.

TGL-UP3(CHB)

TGL-UP3(CHB)

TGL-UP3(CHB)

Project

Project

Project

Name:

Name:

Name:

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Thursday, July 09, 2020 6 84

Thursday, July 09, 2020 6 84

Thursday, July 09, 2020 6 84

1

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

V4.0

V4.0

V4.0

5

4

3

2

1

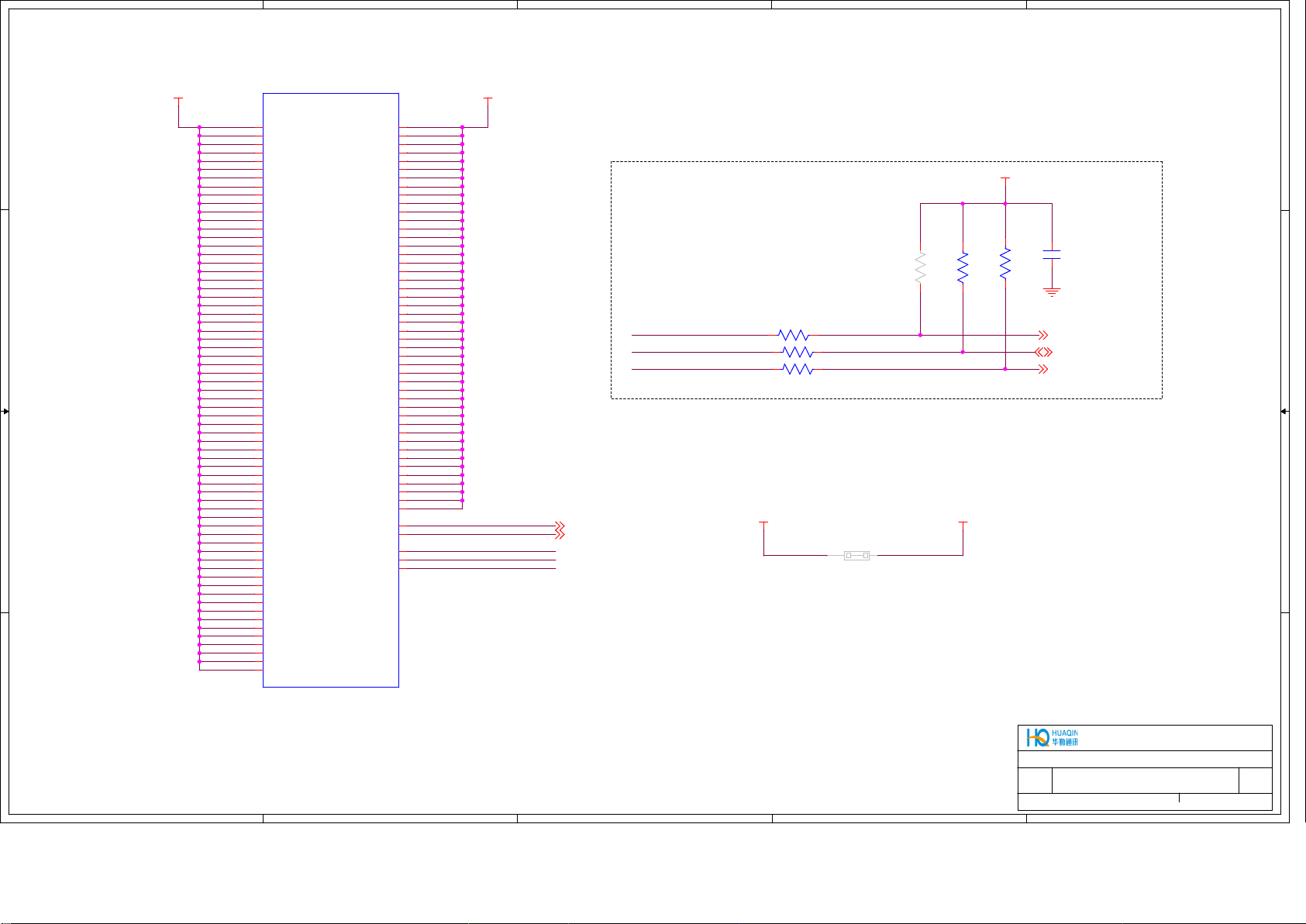

UU1A

EDP_TX3_SOC_DP46

EDP_TX3_SOC_DN46

EDP_TX2_SOC_DP46

EDP_TX2_SOC_DN46

D D

+V3P3A_PCH

RU4

ns

HDMI

C C

GPPC_A14_GPU_RTD3_COLD_POR_N34

+V3P3A_PCH

电阻

_10K_0201_1/20 W_J(±5%)

RU7

ns

B B

USB_OC1_N

电阻

_0R_0201_1/20 W_J(±5%)

+V3P3A_PCH

电阻

_10K_0201_1/20 W_J(±5%)

eDP

电阻

_2.2K_0201_1/20 W_J(±5%)

HDMI_DDI_TX3_SOC_DP47

HDMI_DDI_TX3_SOC_DN47

HDMI_DDI_TX2_SOC_DP47

HDMI_DDI_TX2_SOC_DN47

HDMI_DDI_TX1_SOC_DP47

HDMI_DDI_TX1_SOC_DN47

HDMI_DDI_TX0_SOC_DP47

HDMI_DDI_TX0_SOC_DN47

HDMI_DDI_SOC_SCL47

HDMI_DDI_SOC_SDA47

HDMI_DDI_SOC_HPD47

RU430

RU143

USB_OC2_N

EDP_TX1_SOC_DP46

EDP_TX1_SOC_DN46

EDP_TX0_SOC_DP46

EDP_TX0_SOC_DN46

EDP_AUX_SOC_DP46

EDP_AUX_SOC_DN46

EDP_SOC_HPD46

TBT_LSX0_TXD53

TBT_LSX0_RXD53

EDP_VDD_EN46

EDP_BKLT_EN45,46

EDP_BKLT_PWM46

EDP_TX3_SOC_DP

EDP_TX3_SOC_DN

EDP_TX2_SOC_DP

EDP_TX2_SOC_DN

EDP_TX1_SOC_DP

EDP_TX1_SOC_DN

EDP_TX0_SOC_DP

EDP_TX0_SOC_DN

EDP_AUX_SOC_DP

EDP_AUX_SOC_DN

GPPC_E22_DNX_FORCE_RELOAD

GPP_E23

EDP_SOC_HPD

HDMI_DDI_TX3_SOC_DP

HDMI_DDI_TX3_SOC_DN

HDMI_DDI_TX2_SOC_DP

HDMI_DDI_TX2_SOC_DN

HDMI_DDI_TX1_SOC_DP

HDMI_DDI_TX1_SOC_DN

HDMI_DDI_TX0_SOC_DP

HDMI_DDI_TX0_SOC_DN

HDMI_DDI_SOC_SCL

HDMI_DDI_SOC_SDA

HDMI_DDI_SOC_HPD

TBT_LSX0_TXD

TBT_LSX0_RXD

GPP_E21

TBT_LSX2_RXD

GPP_D12

GPP_A20

1

TPU618MIL

ns

USB_OC1_N

USB_OC2_N

EDP_VDD_EN

EDP_BKLT_EN

EDP_BKLT_PWM

AC2

DDIA_TXP_3

AC1

DDIA_TXN_3

AD2

DDIA_TXP_2

AD1

DDIA_TXN_2

AF1

DDIA_TXP_1

AF2

DDIA_TXN_1

AG2

DDIA_TXP_0

AG1

DDIA_TXN_0

AJ2

DDIA_AUX_P

AJ1

DDIA_AUX

DN4

GPP_E22/DDPA_CTRLCLK/DNX_FORCE_RELOAD

DT6

GPP_E23/DDPA_CTRLDATA

DR5

GPP_E14/DDSP_HPDA/DISP_MISCA

T12

DDIB_TXP_3

T11

DDIB_TXN_3

Y11

DDIB_TXP_2

Y9

DDIB_TXN_2

T9

DDIB_TXP_1

P9

DDIB_TXN_1

V11

DDIB_TXP_0

V9

DDIB_TXN_0

AB9

DDIB_AUX_P

AD9

DDIB_AUX

DM29

GPP_H16/DDPB_CTRLCLK/PCIE_LNK_DOWN

DK27

GPP_H17/DDPB_CTRLDATA

DG43

GPP_A18/DDSP_HPDB/DISP_MISCB/I2S4_RXD

DG47

GPP_A21/DDPC_CTRLCLK/I2S5_TXD

DJ47

GPP_A22/DDPC_CTRLDATA/I2S5_RXD

DU8

GPP_E18/DDP1_CTRLCLK/TBT_LSX0_TXD

DV8

GPP_E19/DDP1_CTRLDATA/TBT_LSX0_RXD

DF6

GPP_E20/DDP2_CTRLCLK/TBT_LSX1_TXD

DD6

GPP_E21/DDP2_CTRLDATA/TBT_LSX1_RXD

DN23

GPP_D9/ISH_SPI_CS#/DDP3_CTRLCLK/TBT_LSX2_TXD/GSPI2_CS0#

DM23

GPP_D10/ISH_SPI_CLK/DDP3_CTRLDATA/TBT_LSX2_RXD/GSPI2_CLK

DK23

GPP_D11/ISH_SPI_MISO/DDP4_CTRLCLK/TBT_LSX3_TXD/GSPI2_MISO

DN21

GPP_D12/ISH_SPI_MOSI/DDP4_CTRLDATA/TBT_LSX3_RXD/GSPI2_MOSI

DF43

GPP_A17/DISP_MISCC/I2S4_TXD

DF45

GPP_A19/DDSP_HPD1/DISP_MISC1/I2S5_SCLK

DF47

GPP_A20/DDSP_HPD2/DISP_MISC2/I2S5_SFRM

DH52

GPP_A14/USB_OC1#/DDSP_HPD3/I2S3_RXD/DISP_MISC3/DMIC_CLK_B1

DK45

GPP_A15/USB_OC2#/DDSP_HPD4/DISP_MISC4/I2S4_SCLK

DM8

EDP_VDDEN

DN8

EDP_BKLTEN

DG10

EDP_BKLTCTL

TGL_UP3_IP_EXT/BGA

PCH STRAP---VCCIO CONFIGURATION

+V3P3A_PCH +V3P3A_PCH +V3P3A_PCH +V3P3A_PCH

电阻

_4.7K_0201_1/20 W_J

RU8

ns

TBT_LSX0_RXD GPP_E21

电阻

_20K_0201_1/20 W_J

RU13

电阻

_4.7K_0201_1/20 W_J

RU9

ns

电阻

_20K_0201_1/20 W_J

RU14

GPP_D12 TBT_LSX2_RXD

电阻

_4.7K_0201_1/20 W_J

RU10

ns

电阻

_20K_0201_1/20 W_J

RU15

1 OF 21

TCP0_TXRX_P1

TCP0_TXRX_N1

TCP0_TXRX_P0

TCP0_TXRX_N0

TCP0_TX_P1

TCP0_TX_N1

TCP0_TX_P0

TCP0_TX_N0

TCP0_AUX_P

TCP0_AUX

TCP1_TXRX_P1

TCP1_TXRX_N1

TCP1_TXRX_P0

TCP1_TXRX_N0

TCP1_TX_P1

TCP1_TX_N1

TCP1_TX_P0

TCP1_TX_N0

TCP1_AUX_P

TCP1_AUX

TCP2_TXRX_P1

TCP2_TXRX_N1

TCP2_TXRX_P0

TCP2_TXRX_N0

TCP2_TX_P1

TCP2_TX_N1

TCP2_TX_P0

TCP2_TX_N0

TCP2_AUX_P

TCP2_AUX

TCP3_TXRX_P1

TCP3_TXRX_N1

TCP3_TXRX_P0

TCP3_TXRX_N0

TCP3_TX_P1

TCP3_TX_N1

TCP3_TX_P0

TCP3_TX_N0

TCP3_AUX_P

TCP3_AUX

TC_RCOMP_P

TC_RCOMP

DSI_DE_TE_2

DDI_RCOMP

DISP_UTILS/DSI_DE_TE_1

AY2

AY1

BB1

BB2

AM5

AM7

AT7

AT5

AP7

AP5

AT2

AT1

AU1

AU2

AD5

AD7

AH7

AH5

AF7

AF5

BF1

BF2

BE2

BE1

BD7

BD5

AY5

AY7

BB5

BB7

BK1

BK2

BJ2

BJ1

BM7

BM5

BH5

BH7

BK5

BK7

AN2

AN1

M8

AB1

CE4

TCP0_TXRX1_DN

TCP0_TXRX0_DP

TCP0_TXRX0_DN

TCP0_TX1_DP

TCP0_TX1_DN

TCP0_TX0_DP

TCP0_TX0_DN

TCP0_AUX_DP

TCP0_AUX_DN

TCRCOMP_DN

TCRCOMP_DP

DISP_RCOMP

RU5

RU6

TCP0_TXRX1_DP 53

TCP0_TXRX1_DN 53

TCP0_TXRX0_DP 53

TCP0_TXRX0_DN 53

TCP0_TX1_DP 53

TCP0_TX1_DN 53

TCP0_TX0_DP 53

TCP0_TX0_DN 53

TCP0_AUX_DP 53

TCP0_AUX_DN 53

_150R_0201_1/20 W_F

电阻

电阻

_150R_0201_1/20 W_F

TBT 1

TCP0_TXRX1_DP

DNX CIRCUIT

+V3P3A+V5P0A

电阻

电阻

_10K_0201_1/20 W_J(±5%)

RU300

PM_SLP_S3_DNX

RU296

+V3P3A

ns

PM_SLP_S3_N_DNX_RSLP_S3_SOC_N

RU298

ns

电阻

RU295

_10K_0201_1/20 W_J(±5%)

电阻

_1M_0201_1/20 W_J

QU8

G

1

2N7002

S DS D

2 3

电阻

_4.7K_0201_1/20 W_J

RU11

ns

电阻

_20K_0201_1/20 W_J

RU16

SLP_S3_SOC_N12,45,80,84

电阻

_0R_0201_1/20 W_J(±5%)

_2.2K_0201_1/20 W_J(±5%)

RU297

ns

GPPC_E22_DNX_FORCE_RELOAD

S DS D

23

1

2N7002

G

电阻

_20K_0201_1/20 W_J

RU299

QU9

RU304

电阻

_100K_0201_1/20 W_J

V2

DNX_FORCE_RELOAD_EC 45

TBT_LSX0_RXD

TBT LSX#0 PINS VCCIO CONFIGURATION

HIGH: 3.3V

A A

LOW: 1.8V

WEAK INTERNAL PD 20K

5

GPP_E21

TBT LSX#1 PINS VCCIO CONFIGURATION

HIGH: 3.3V

LOW: 1.8V

WEAK INTERNAL PD 20K

GPP_D12

TBT LSX#3 PINS VCCIO CONFIGURATION

HIGH: 3.3V

LOW: 1.8V

WEAK INTERNAL PD 20K

4

GPP_D10

TBT LSX#2 PINS VCCIO CONFIGURATION

HIGH: 3.3V

LOW: 1.8V

WEAK INTERNAL PD 20K

teknisi indonesia

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date:

Date:

Date:

3

2

Huaqin Telecom Technology Com.,Ltd.

TGL-UP3(DISPLAY)

TGL-UP3(DISPLAY)

TGL-UP3(DISPLAY)

Project

Project

Project

Name:

Name:

Name:

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Thursday, July 09, 2020 7 84

Thursday, July 09, 2020 7 84

Thursday, July 09, 2020 7 84

1

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

V4.0

V4.0

V4.0

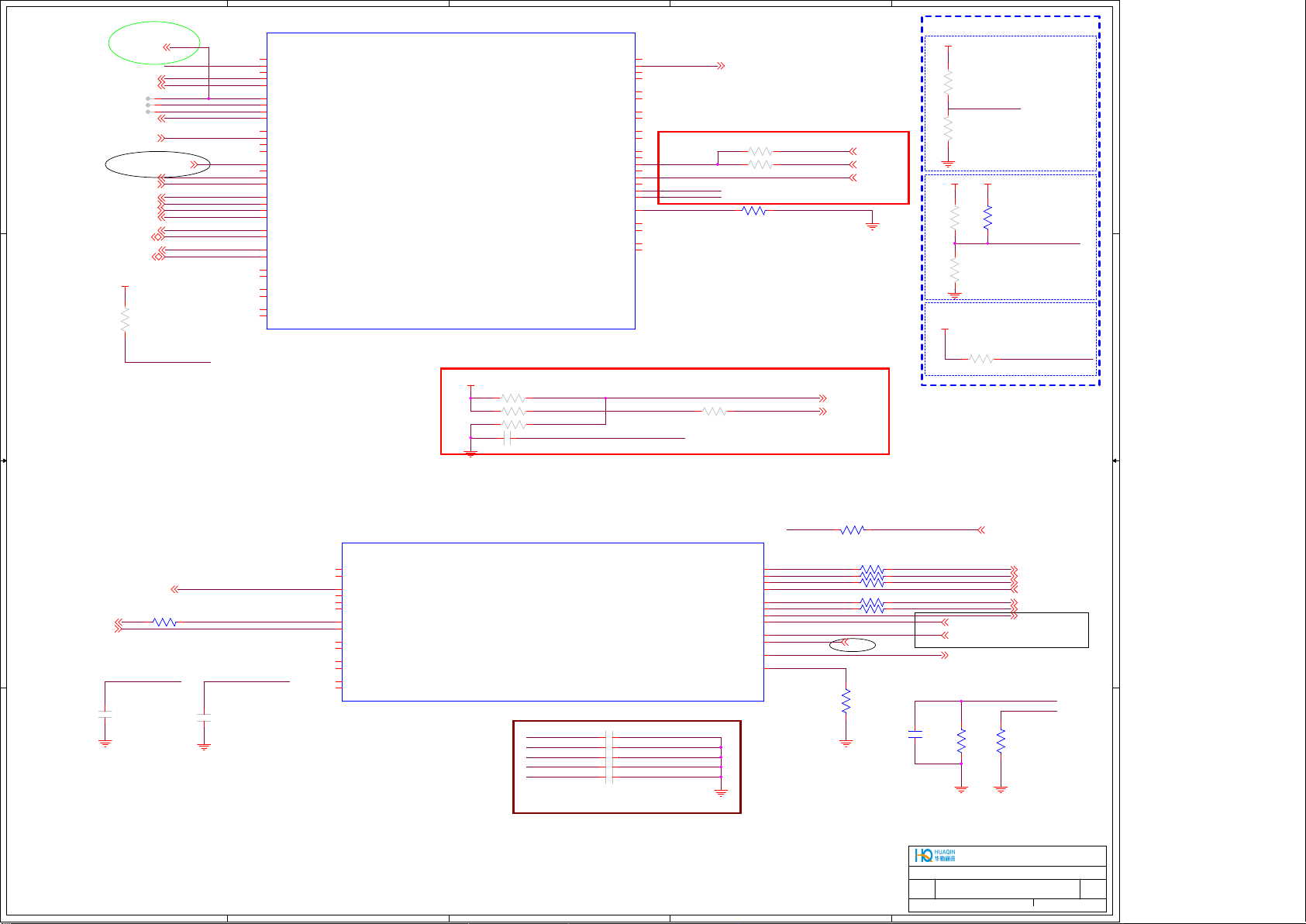

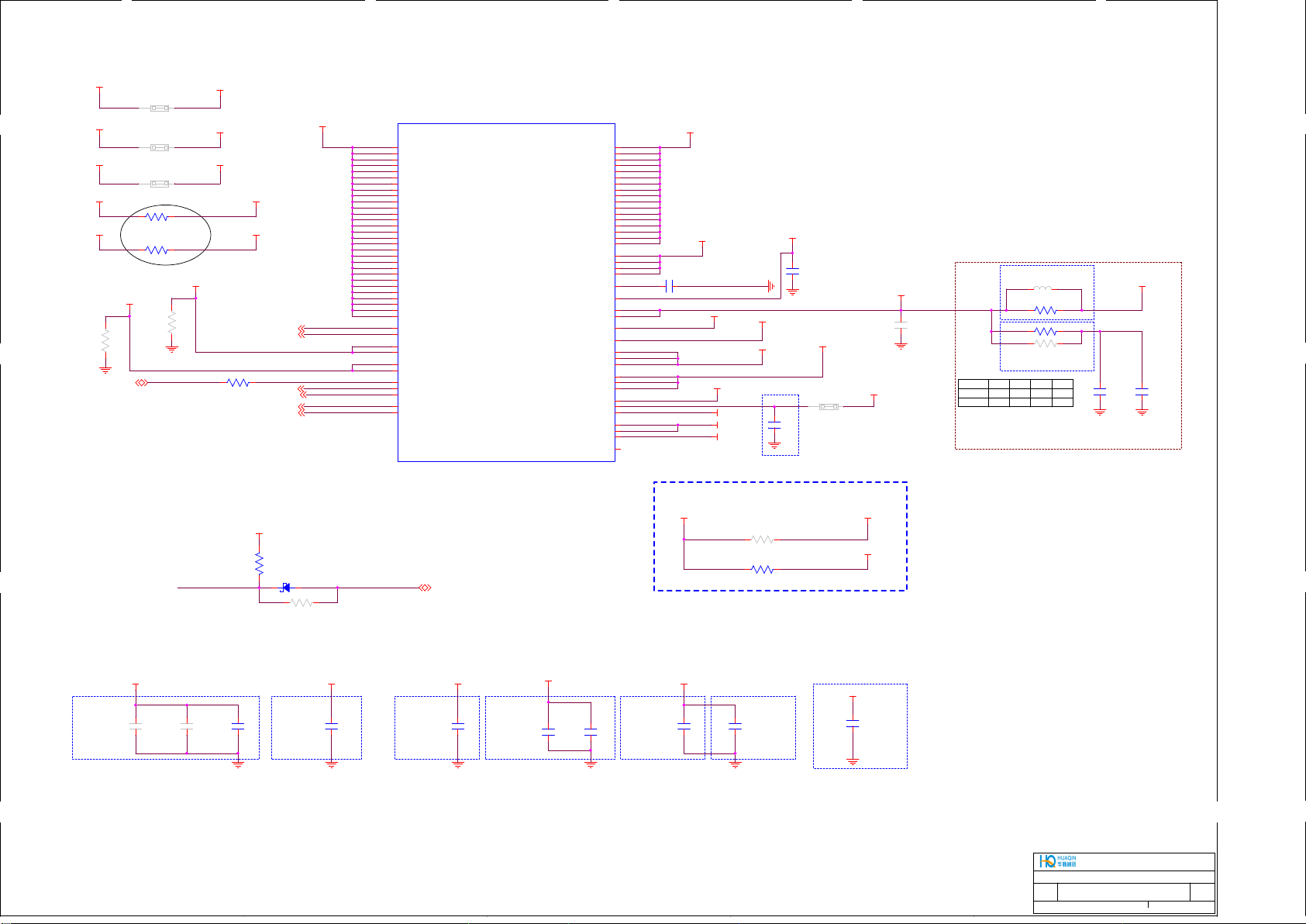

5

+VCCSTG _TERM

RU17

_1K_02 01_1/20 W_J(±5 %)

CATERR _SOC_N

PECI_S OC

PECI_S OC45

PROCHOT _SOC_N_ R

THERMTRI P_SOC_ N

CPU_POPI_RCOMP

PCH_POPI_RCOMP

DBG_PMO DE

1

TP17718MIL

ns

SOC_SC I_N

SOC_SC I_N45

GPP_E7

1

TP18618MIL

ns

GPP_E3

1

TP18518MIL

ns

GPP_H2

GPP_H1

GPPC_H0

GPPC_H048

UART_BT _WAKE _N_SOC

SPI_SO C_CLK

SPI_SO C_IO3

SPI_SO C_IO2

SPI_SO C_MISO

SPI_SO C_MOSI

SPI_SO C_CS1

SPI_SO C_CS0

SPI_SO C_CS2

SPI1_C LK

GPP_E1 2

1

HW_ID9

1

SPI1_C S0_N

EC_SLP _S0_CS _N

HW_ID8

GPPC_E 6_THC0_ SPI1_ RST_N

1

HW_ID0

HW_ID1

HW_ID2

HW_ID3

HW_ID4

HW_ID5

HW_ID6

HW_ID7

CLNK_CL K_SOC

CLNK_DA TA_SOC

CLNK_RE SET_SO C

电阻

DG35

DF35

DG37

DF39

DV11

DK13

DM13

DV14

+V1P0S_ VCCST

电阻

_1K_0201_1/20 W_J(±5%)

+V1P0S_ VCCST

RU21

D D

C C

B B

THERMTRI P_SOC_ N34

+VCC1P0 5_OUT_ FET

RU222

_1K_02 01_1/20 W_J(±5 %)

电阻

DBG_PMO DE

TP_I2C _INT_N46

1

TP918MIL

ns

1

TP1018MIL

ns

TP_I2C _RST_N4 6

EC_SLP _S0_CS _N45,47,66

AUDIO ID

RU19

_499Ω_0 201_1 /20 W_F

电阻

_1K_02 01_1/20 W_J(±5 %)

电阻

RU24

RU26电阻_49.9R_ 0201_1 /20 W_ F

RU28电阻_49.9R_ 0201_1 /20 W_ F

UART_BT _WAKE _N_SOC50

+V3P3SX

RU32

ns

_10K_0 201_1/2 0 W_J (±5%)

电阻

SOC_SC I_N

SPI_SO C_CLK44

SPI_SO C_IO344

SPI_SO C_IO244

SPI_SO C_MISO44

SPI_SO C_MOSI44

SPI_SO C_CS144

SPI_SO C_CS044

SPI_SO C_CS243

TP1118MIL

ns

TP1218MIL

ns

TP1518MIL

ns

Memory ID

GPU ID

LCD ID

Project ID

CLNK_CL K_SOC50

CLNK_DA TA_SOC50

CLNK_RE SET_SO C50

预留WLAN Vpro

4

+VCCSTG _TERM

PLACE NEAR THE FAR DEVICE

RU18

ns

_10K_0 201_1/2 0 W_J (±5%)

电阻

UU1U

TGL_UP3 _IP_EX T/BGA

PROCHOT _SOC_N

21 OF 21

EAR_N/EAR_N_TEST_NCTF

5P0VA_ EN

3P3VA_ EN

RSMRST_ N_EC

TP111

18MIL

ns

1

M7

CATERR#

BK9

PECI

E2

PROCHOT#

M5

THRMTRIP#

CT39

PROC_POPIRCOMP

CB9

PCH_OPIRCOMP

CW12

TP_1

CM39

TP_2

DF4

DBG_PMODE

DB42

GPP_B4/CPU_GP3

DB41

GPP_B3/CPU_GP2

DF8

GPP_E7/CPU_GP1

DU5

GPP_E3/CPU_GP0

DF31

GPP_H2

DV32

GPP_H1

DW32

GPP_H0

DJ27

GPP_H19/TIME_SYNC0

EC_IMVP _PWRG D45,78

5P0VA_ EN45,74

3P3VA_ EN45,68,73

RSMRST_ N_EC12,44,45 ,69

add thermal trip control

add QU7,RU232 for thermal trip control

UU1E

DJ37

SPI0_CLK

SPI0_IO3

DJ39

SPI0_IO2

DJ33

SPI0_MISO

DJ35

SPI0_MOSI

SPI0_CS1#

SPI0_CS0#

SPI0_CS2#

DJ6

GPP_E11/THC0_SPI1_CLK

DN5

GPP_E2/THC0_SPI1_IO3

DR9

GPP_E1/THC0_SPI1_IO2

DM6

GPP_E12/THC0_SPI1_IO1

DK6

GPP_E13/THC0_SPI1_IO0

DK8

GPP_E10/THC0_SPI1_CS#

GPP_E8/SATA_LED#

DW9

GPP_E17/THC0_SPI1_INT#

DT8

GPP_E6/THC0_SPI1_RST#

DN15

GPP_F11/THC1_SPI2_CLK

GPP_F15/GSXSRESET#/THC1_SPI2_IO3

GPP_F14/GSXDIN/THC1_SPI2_IO2

DN13

GPP_F13/GSXSLOAD/THC1_SPI2_IO1

DJ15

GPP_F12/GSXDOUT/THC1_SPI2_IO0

DK15

GPP_F16/GSXCLK/THC1_SPI2_CS#

DN10

GPP_F18/THC1_SPI2_INT#

GPP_F17/THC1_SPI2_RST#

DH3

CL_CLK

DH4

CL_DATA

DF2

CL_RST#

TGL_UP3 _IP_EX T/BGA

PROCHOT _SOC_N 14,45,78

K4

PROC_TRST#

B9

PROC_TMS

D12

PROC_TDO

A12

PROC_TDI

B6

PROC_TCK

D8

PCH_JTAGX

A9

PCH_TMS

E12

PCH_TDO

B12

PCH_TDI

A7

PCH_TCK

H4

PCH_TRST#

C11

PROC_PREQ#

D11

PROC_PRDY#

G1

DT15

GPP_F7

DR15

GPP_F9

DT14

GPP_F10

QU6

1

ns

2 3

2 3

LMBT390 4LT1G

5 OF 21

GPP_B23/SML1ALERT#/PCHHOT#/GSPI1_CS1#

GPP_A2/ESPI_IO2/SUSWARN#_SUSPWRDNACK

MIPI60_ CPU_JTA G_TRS T_N

MIPI60_ CPU_JTA G_TMS

MIPI60_ CPU_JTA G_TDO

MIPI60_ CPU_JTA G_TDI

MIPI60_ CPU_JTA G_TCL K

MIPI60_ PCH_JTA GX

MIPI60_ PCH_JTA G_TMS

MIPI60_ PCH_JTA G_TDO

MIPI60_ PCH_JTA G_TDI

MIPI60_ PCH_JTA G_TCL K

MIPI60_ PCH_JTA G_TRS T_N

MIPI60_ PREQ_N

MIPI60_ PRDY_N

CPU_EAR

GPP_F7

GPPC_F 9_BOOT MPC

GPPC_F 10

QU4

1

LMBT390 4LT1G

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A5/ESPI_CLK

GPP_A3/ESPI_IO3/SUSACK#

GPP_A1/ESPI_IO1

GPP_A0/ESPI_IO0

GPP_A4/ESPI_CS#

GPP_A6/ESPI_RESET#

QU5

1

ns

2 3

LMBT390 4LT1G

GPP_C0/SMBCLK

+V1P0S_ VCCST

G

1

THERMTRI P_SOC_ N

DK21

DM19

DN19

DK19

DM17

DN17

DK17

DJ17

CY50

DN53

DJ53

DH50

DP50

DP52

DK52

DL50

3

V2

QU7

2N7002

S DS D

2 3

RU224

_1K_02 01_1/20 W_J(±5 %)

电阻

RU232

PCH_SMB1 _CLK

PCH_SMB1 _DATA

GPPC_C 2_SMBAL ERT_N

SMBUS_CL K0

SMBUS_DA T0

GPPC_C 5_SML0A LERT_ N

TYPEC_P D_SOC_ CLK

TYPEC_P D_SOC_ DAT

GPPC_B 23_SML1 _ALER T_N

ESPI_S OC_CLK

ESPI_S OC_IO3

ESPI_S OC_IO2

ESPI_S OC_IO1

ESPI_S OC_IO0

ESPI_S OC_CS

ESPI_S OC_RST

电阻

_100K_0201_1/20 W_J

CPU_EAR

电容

_100nF_0201_X5R_6.3 V_K(±10%)

+VCCIN

RU289

RU253

ns

RU37

RU43

RU40

RU39

RU38

+VCCSTG _IO

ns

CU168

+V3P3A_ PCH

电阻

电阻

_1K_0201_1/20 W_J(±5%)

_4.7K_0201_1/20 W_J

RU255

ns

电阻

GPPC_F 10

电阻

_20K_0201_1/20 W_J

_1K_0201_1/20 W_J(±5%)

RU256

ns

VPRO

_49.9R_ 0201_1 /20 W_ F

电阻

_49.9R_ 0201_1 /20 W_ F

电阻

_49.9R_ 0201_1 /20 W_ F

电阻

_49.9R_ 0201_1 /20 W_ F

电阻

_49.9R_ 0201_1 /20 W_ F

电阻

ESPI_C LK_EC

ESPI_I O3_EC

ESPI_I O2_EC

ESPI_I O1_EC

ESPI_I O0_EC

V2

+V3P3A +V3P3A +V3P3A_ EC

CU385

_47nF_0 201_10 V_K(±10 %)

电容

Stitching caps

MIPI60_ PCH_JTA G_TRS T_N

MIPI60_ PCH_JTA G_TCL K

MIPI60_ PCH_JTA G_TDI

MIPI60_ PCH_JTA G_TDO

MIPI60_ PCH_JTA G_TMS

MIPI60_ PCH_JTA GX

MIPI60_ PRDY_N

MIPI60_ PREQ_N

MIPI60_ CPU_JTA G_TDI

MIPI60_ CPU_JTA G_TDO

MIPI60_ CPU_JTA G_TMS

MIPI60_ CPU_JTA G_TRS T_N

+V1P8A

RU92电阻_4.7K_0 201_1/2 0 W_J

ns_LP4/X_ID@

RU94电阻_4.7K_0 201_1/2 0 W_J

ns_LP4/X_ID@

RU96电阻_4.7K_0 201_1/2 0 W_J

ns_LP4/X_ID@

RU98电阻_4.7K_0 201_1/2 0 W_J

ns_LP4X_ID@

RU102电阻_4.7K_0 201_1/2 0 W_J

RU105电阻_4.7K_0 201_1/2 0 W_J

UMA_ID@

RU107电阻_4.7K_0 201_1/2 0 W_J

LCD4X@

RU109电阻_4.7K_0 201_1/2 0 W_J

NB2672@

RU318电阻_4.7K_0 201_1/2 0 W_J

ALC256 @

RU441电阻_4.7K_0 201_1/2 0 W_J

NB2672@

+V3P3A_ PCH

电阻

_2.2K_0201_1/20 W_J(±5%)

SMBUS_CL K0 53

SMBUS_DA T0 53

TYPEC_P D_SOC_ CLK 52,67

TYPEC_P D_SOC_ DAT 52,67

ESPI_C LK_EC 45

ESPI_I O3_EC 45

ESPI_I O2_EC 45

ESPI_I O1_EC 45

ESPI_I O0_EC 45

ESPI_S OC_CS 4 5

ESPI_S OC_RST 4 5

CU386

_47nF_0 201_10 V_K(±10 %)

电容

2

1

TP1 18MIL

ns

1

TP2 18MIL

ns

1

TP3 18MIL

ns

1

TP4 18MIL

ns

1

TP5 18MIL

ns

1

TP6 18MIL

ns

1

TP7 18MIL

ns

1

TP8 18MIL

ns

RU20

_0R_02 01_1/20 W_J(±5 %)

电阻

RU22

_51R_0 201_1/2 0 W_J

电阻

RU25

_0R_02 01_1/20 W_J(±5 %)

电阻

RU29

_0R_02 01_1/20 W_J(±5 %)

电阻

_0R_02 01_1/20 W_J(±5 %)

电阻

RU31

RU33

_0R_02 01_1/20 W_J(±5 %)

电阻

HW_ID0

HW_ID1

HW_ID2

HW_ID3

3 4

ns

D

QU1A

5

G

S

+V3P3SX

6 1

ns

D

QU1B

LBSS13 9DW1T 1G

HW_ID8

HW_ID4

HW_ID5

HW_ID6

HW_ID7

HW_ID9

2

G

S

ns

电阻

_2.2K_0201_1/20 W_J(±5%)

RU36

RU35

LBSS13 9DW1T 1G

MIPI_60

RU23

ns

RU27

_51R_0 201_1/2 0 W_J

电阻

RU30

ns

_51R_0 201_1/2 0 W_J

电阻

MIPI60_ PCH_JTA G_TRS T_N

RU34

ns

_51R_0 201_1/2 0 W_J

电阻

RU93电阻_4.7K_0 201_1/2 0 W_J

LP_4/X_ID@

RU95电阻_4.7K_0 201_1/2 0 W_J

LP_4I/X_ID@

RU97电阻_4.7K_0 201_1/2 0 W_J

LP_4/X_ID@

RU99电阻_4.7K_0 201_1/2 0 W_J

LP4_ID@

RU100电阻_4.7K_0 201_1/2 0 W_J

N18S_ID@

RU106电阻_4.7K_0 201_1/2 0 W_J

N17S-LP_ID@

RU108电阻_4.7K_0 201_1/2 0 W_J

LCD2X@

RU110电阻_4.7K_0 201_1/2 0 W_J

NB2629@

RU317电阻_4.7K_0 201_1/2 0 W_J

ALC256M@

RU442电阻_4.7K_0 201_1/2 0 W_J

NB2672@

SMB2_EC _SCL 34,4 5,68

SMB2_EC _SDA 34,4 5,68

MIPI60_ PCH_JTA GXMIPI60_ CPU_JTA G_TCL K

+VCCSTG _TERM

_51R_0 201_1/2 0 W_J

电阻

MIPI60_ PCH_JTA G_TDI

+VCCSTG _TERM

MIPI60_ PCH_JTA G_TDO

+VCCSTG _TERM

MIPI60_ PCH_JTA G_TMS

HW ID

ESPI_C LK_EC

ESPI_I O0_EC

ESPI_I O1_EC

ESPI_I O2_EC

ESPI_I O3_EC

电容

_22pF_0201_C0G_25 V_J(±5%)

CU1

ns

1

电容

电容

_22pF_0201_C0G_25 V_J(±5%)

CU2

ns

电容

电容

_22pF_0201_C0G_25 V_J(±5%)

_22pF_0201_C0G_25 V_J(±5%)

_22pF_0201_C0G_25 V_J(±5%)

CU4

CU5

CU3

ns

ns

ns

0000 = Master Attached Flash Configuration (BIOS / CSME on SPI).

1000 = Slave Attached Flash Configuration (BIOS / CSME on e SPI attached device).

0100 = BIOS on eSPI Peripher al Channel; CSME on master atta ched SPI

PCH STRAP

+V3P3A_ PCH

电阻

_4.7K_0201_1/20 W_J

电阻

_4.7K_0201_1/20 W_J

ns

A A

JTAG ODT DISAB LE

SPI_SO C_IO3 SPI_SOC_I O2

FLASH_SPI_IO3

0: ENABLED

1: DISABLED

NO INTERNAL PU/PD

TLS CONFIDENTI ALITY

BOOT HALT

RU47

GPPC_C 2_SMBAL ERT_N

SPI_SO C_MOSI

RU57

FLASH_SPI_MOSI

1: DISABLED

GPPC_C2_SMBALERT_N

0: ENABLED

0: TLS CONFIDENTIALITY DISABLE(Default)

WEAK INTERNAL PU

1: TLS CONFIDENTIALITY ENABLE

Internal 20K PD

+V3P3A_ SPI_F LASH +V3P3A _SPI_F LASH

电阻

_100K_0201_1/20 W_J

RU52

电阻

_100K_0201_1/20 W_J

RU60

ns

5

+V1P8A

RU311

CONSENT STRAP

FLASH_SPI_IO2

0: ENABLED

1: DISABLED

NO INTERNAL PU/PD

电阻

_4.7K_0201_1/20 W_J

RU48

RU302

+V3P3A_ PCH

ns

ns

RU53

RU61

ns

BOOT STRAP 0- BIT 1

电阻

_4.7K_0201_1/20 W_J

电阻

_4.7K_0201_1/20 W_J

WEAK INTERNAL PD 20K

SAMPLING - RSMRSTB

电阻

_100K_0201_1/20 W_J

电阻

_4.7K_0201_1/20 W_J

1100 = BIOS on eSPI peripher al Channel; CSME on slave attac hed SPI.

Others: Reserved

+V3P3A_ PCH

RU49

GPPC_C 5_SML0A LERT_ N

RU252

DFXTESTMODE

DBG_PMO DE

DBG_PMODE

0: DFXTESTMODE ENABLED

1: DFXTESTMODE DISABLED(DEFAULT)

WEAK INTERNAL PU 20K

RU54

BOOT STRAP 1- BIT 2

电阻

_4.7K_0201_1/20 W_J

ns

电阻

_20K_0201_1/20 W_J

ns

WEAK INTERNAL PD 20K

SAMPLING - RSMRSTB

电阻

_1K_0201_1/20 W_J(±5%)

ns

4

+V3P3A_ PCH

电阻

_4.7K_0201_1/20 W_J

RU251

ns

GPPC_H0

电阻

_20K_0201_1/20 W_J

电阻

_20K_0201_1/20 W_J

电阻

_20K_0201_1/20 W_J

RU250

ns

RU313电阻_0R_02 01_1/20 W_J(±5 %)

RU245电阻_0R_02 01_1/20 W_J(±5 %)

电阻

_20K_0201_1/20 W_J

RU56

RU55

电阻

_20K_0201_1/20 W_J

RU62

RU63

ns

ns

BOOT STRAP 2- BIT 3

GPP_H1

WEAK INTERNAL PD 20K

SAMPLING - RSMRSTB

+V3P3A_ PCH

ns

XTAL INPUT FRE QUENCY

1.SPI1_CS0_N

XTAL INPUT FREQUENCY [0]

2.SPI1_CLK

XTAL INPUT FREQUENCY [1]

SPI1_C S0_N

SPI1_C LK

00: DIVIDER BYPASS

01: DIVIDE BY 2 (HVM: 38.4MHZ INPUT)

10: DIVIDE BY 10 (HVM: 250MHZ INPUT)

11: DIVIDE BY 4 (BI: 100MHZ INPUT)

( QUALIFIED BY DFXTESTMODE)

NO INTERNAL PU/PD

+V3P3A_ PCH

RU248

RU249

ns

ns

+V1P8A

BOOT STRAP 3- BIT 4

电阻

_4.7K_0201_1/20 W_J

GPP_H2

电阻

_20K_0201_1/20 W_J

WEAK INTERNAL PD 20K

SAMPLING - RSMRSTB

CPUNSSC CLOCK FREQ

+V1P8A

+V3P3A_ PCH

电阻

_4.7K_0201_1/20 W_J

RU123

RU316

ns

GPPC_B 23_SML1 _ALER T_N

电阻

_20K_0201_1/20 W_J

RU124

ns

GPPC_B23_SML1_ALERT_N

0: 38.4MHZ CLOCK FROM DIRECT

CRYSTAL (DEFAULT)

1: 19.2MHZ CLOCK FROM DIVIDER

(DERIVED FROM 38.4MHZ CRYSTAL)

WEAK INTERNAL PD 20K

3

JTAG ODT DISAB LE

+V3P3A_ PCH

电阻

_4.7K_0201_1/20 W_J

RU50

ns

EC_SLP _S0_CS _N

电阻

_20K_0201_1/20 W_J

RU58

ns

EC_SLP_S0_CS_N

0: JTAG ODT DISABLED

1: JTAG ODT ENABLED

NO INTERNAL PU/PD

电阻

_4.7K_0201_1/20 W_J

ns

RU51

RU59

+V3P3A_ PCH

ns

ns

RU315

RU314

+V1P8A

电阻

电阻

_100K_0201_1/20 W_J

_100K_0201_1/20 W_J

RU310

GPPC_E 6_THC0_ SPI1_ RST_N

电阻

_4.7K_0201_1/20 W_J

GPPC_E6_THC0_SPI1_RST_N

+V3P3A_ PCH

ns

ns

电阻

_100K_0201_1/20 W_J

电阻

_4.7K_0201_1/20 W_J

WEAK INTERNAL PD 20K

GPP_F7

+V3P3A_ PCH

电阻

_4.7K_0201_1/20 W_J

RU293

ns

电阻

_20K_0201_1/20 W_J

RU294

ns

SPI_SO C_CLK ESPI_S OC_CS

_100K_ 0201_1 /20 W_ J

电阻

2

+V3P3A_ PCH

RU42

电阻

RU41

电阻

_499Ω_0201_1/20 W_F

_499Ω_0201_1/20 W_F

SMBUS_CL K0

SMBUS_DA T0

ESPI_S OC_RST

_75K_0 201_1/2 0 W_F (±1%)

电阻

RU45

ns

_75K_0 201_1/2 0 W_F (±1%)

电阻

Page name:

Page name:

Page name:

Size:

Size:

Size:

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

RU44

GPPC_F 9_BOOT MPC

RU46

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

TGL-UP3(SPI/ESPI/MIPI60)

TGL-UP3(SPI/ESPI/MIPI60)

TGL-UP3(SPI/ESPI/MIPI60)

Project

Project

Project

Name:

Name:

Name:

A4

A4

A4

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Thursday, July 09, 2 020 8 84

Thursday, July 09, 2 020 8 84

Thursday, July 09, 2 020 8 84

1

电阻

_75K_0201_1/20 W_F(±1%)

RU254

REV:

REV:

REV:

V4.0

V4.0

V4.0

5

4

3

2

1

UU1J

D22

CSI_F_DP_1

B22

CSI_F_DN_1

E22

CSI_F_DP_0

D20

CSI_F_DN_0

A20

CSI_F_CLK_P

D D

RU76

C C

电阻

_150R_0201_1/20 W_F

CSI_COMP

B20

CSI_F_CLK

B18

CSI_E_DP_1/CSI_F_DP_2

A18

CSI_E_DN_1/CSI_F_DN_2

D18

CSI_E_DP_0/CSI_F_DP_3

E18

CSI_E_DN_0/CSI_F_DN_3

C16

CSI_E_CLK_P

D16

CSI_E_CLK

D15

CSI_C_DP_2

E15

CSI_C_DN_2

A15

CSI_C_DP_3

B15

CSI_C_DN_3

L18

CSI_C_DP_1

N18

CSI_C_DN_1

L20

CSI_C_DP_0

N20

CSI_C_DN_0

G20

CSI_C_CLK_P

H20

CSI_C_CLK

H16

CSI_B_DP_1

G16

CSI_B_DN_1

G18

CSI_B_DP_0

H18

CSI_B_DN_0

L16

CSI_B_CLK_P

N16

CSI_B_CLK

G14

CSI_B_DP_2

H14

CSI_B_DN_2

L14

CSI_B_DP_3

N14

CSI_B_DN_3

K14

CSI_RCOMP

DK25

GPP_H23/IMGCLKOUT4

DM25

GPP_H22/IMGCLKOUT3

DN25

GPP_H21/IMGCLKOUT2

DJ25

GPP_H20/IMGCLKOUT1

DR30

GPP_D4/IMGCLKOUT_0/BK4/SBK4

TGL_UP3_IP_EXT/BGA

10 OF 21

CNVI_WT_D1P

CNVI_WT_D1N

CNVI_WT_D0P

CNVI_WT_D0N

CNVI_WT_CLKP

CNVI_WT_CLKN

CNVI_WR_D1P

CNVI_WR_D1N

CNVI_WR_D0P

CNVI_WR_D0N

CNVI_WR_CLKP

CNVI_WR_CLKN

GPP_F3/CNV_RGI_RSP/UART0_CTS#

GPP_F1/CNV_BRI_RSP/UART0_RXD

GPP_F0/CNV_BRI_DT/UART0_RTS#

GPP_F5/MODEM_CLKREQ/CRF_ XTAL_CLKREQ

CNVI_WT_RCOMP

GPP_F2/CNV_RGI_DT/UART0_TXD

GPP_F6/CNV_PA_BLANKING

GPP_F4/CNV_RF_RESET#

only 3vias allowed for CNVi High speed signals on PCB routi ng;

if more than 3 vias,PLS remo ve all the serial resistors

CNV_WT_LANE1_DP_R

DK47

CNV_WT_LANE1_DN_R

DM47

CNV_WT_LANE0_DP_R

DN49

CNV_WT_LANE0_DN_R

DR49

CNV_WT_CLK_DP_R

DN45

CNV_WT_CLK_DN_R

DN47

CNV_WR_LANE1_DP

DU43

CNV_WR_LANE1_DN

DV43

CNV_WR_LANE0_DP

DR44

CNV_WR_LANE0_DN

DT43

CNV_WR_CLK_DP

DV44

CNV_WR_CLK_DN

DW44

CNV_WT_RCOMP

DN51

CNV_RGI_RSP_SOC

DJ13

CNV_RGI_DT_SOC

DG13

CNV_BRI_RSP_SOC

DF15

CNV_BRI_DT_SOC

DF17

DJ10

DV15

DK10

RU70

RU69

RU68

RU66

RU72

RU71

RU73

RU74

RU75

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_150R_0201_1/20 W_F

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

CNV_WT_LANE1_DP

CNV_WT_LANE1_DN

CNV_WT_LANE0_DP

CNV_WT_LANE0_DN

CNV_WT_CLK_DP

CNV_WT_CLK_DN

CNV_RGI_DT

CNV_BRI_DT

GPU_WAKE_N

CNV_WT_LANE1_DP 50

CNV_WT_LANE1_DN 50

CNV_WT_LANE0_DP 50

CNV_WT_LANE0_DN 50

CNV_WT_CLK_DP 50

CNV_WT_CLK_DN 50

CNV_WR_LANE1_DP 50

CNV_WR_LANE1_DN 50

CNV_WR_LANE0_DP 50

CNV_WR_LANE0_DN 50

CNV_WR_CLK_DP 50

CNV_WR_CLK_DN 50

CNV_RGI_RSP_SOC 50

CNV_RGI_DT 50

CNV_BRI_RSP_SOC 50

CNV_BRI_DT 50

GPU_WAKE_N 29

1.8V level

+V1P8A

电阻

_10K_0201_1/20 W_J(±5 %)

RU79

ns

电阻

_20K_0201_1/20 W_J

RU80

ns

+V3P3A_PCH

电阻

RV1

_10K_0201_1/20 W_J(±5 %)

close to SOC

CNV_RGI_RSP_SOC

CNV_BRI_RSP_SOC

GPU_WAKE_N

UU1K

BW1

CLKOUT_PCIE_P6

BW2

CLKOUT_PCIE_N6

CB2

CLKOUT_PCIE_P5

CB1

B B

PCIE_REFCLK_SSD_DP148

SSD1

SSD2

WLAN

GPU

A A

PCIE_REFCLK_SSD_DN148

PCIE_REFCLK_SSD2_DP49

PCIE_REFCLK_SSD2_DN49

PCIE_REFCLK_WLAN_DP50

PCIE_REFCLK_WLAN_DN50

CLK_SRC2_PCIE_R_DP29

CLK_SRC2_PCIE_R_DN29

5

PCIE_REFCLK_SSD_DP1

PCIE_REFCLK_SSD_DN1

PCIE_REFCLK_SSD2_DP

PCIE_REFCLK_SSD2_DN

PCIE_REFCLK_WLAN_DP

PCIE_REFCLK_WLAN_DN

CLK_SRC2_PCIE_R_DP

CLK_SRC2_PCIE_R_DN

XCLK_BIASREF

RU88

电阻

_60.4R_0201_1/20_F(±1%)

BW4

BW5

CL7

CL8

CB4

CB5

BY4

BY3

CN7

CN8

DJ5

CLKOUT_PCIE_N5

CLKOUT_PCIE_P4

CLKOUT_PCIE_N4

CLKOUT_PCIE_P3

CLKOUT_PCIE_N3

CLKOUT_PCIE_P2

CLKOUT_PCIE_N2

CLKOUT_PCIE_P1

CLKOUT_PCIE_N1

CLKOUT_PCIE_P0

CLKOUT_PCIE_N0

XCLK_BIASREF

TGL_UP3_IP_EXT/BGA

11 OF 21

GPP_F19/SRCCLKREQ6#

GPP_H11/SRCCLKREQ5#

GPP_H10/SRCCLKREQ4#

GPP_D8/SRCCLKREQ3#

GPP_D7/SRCCLKREQ2#

GPP_D6/SRCCLKREQ1#

GPP_D5/SRCCLKREQ0#

GPD8/SUSCLK

+V3P3SX

电阻

_10K_0201_1/20 W_J(±5 %)

4

XTAL_OUT

XTAL_IN

RTCX2

RTCX1

RTCRST#

SRTCRST#

RU101

PCIE_WLAN_REQ_N

DU14

DF23

DG25

PCIE_REFCLK_SSD_REQ_N

DT24

PCIE_REFCLK_SSD2_REQ_N

DT30

PCIE_WLAN_REQ_N

DV30

GPPC_D5_GPU_CLKREQ0_N

DW30

XTAL_38P4M_SOC_OUT XTAL_38P4M_SOC_OUT_R

DM1

DL1

DW41

DT47

DR47

DN37

DK37

XTAL_38P4M_SOC_IN

XTAL_32K_SOC_OUT

XTAL_32K_SOC_IN

RTC_RST_N

SRTC_RST_N

V2

QU2

2N7002

RU86

RU85

RU84

RU82

RU83

S DS D

2 3

电阻

PCIE_REFCLK_SSD_REQ_N 48

PCIE_REFCLK_SSD2_REQ_N 49

PCIE_WLAN_REQ_N 9,50

PCIE_WLAN_REQ_N 9,50

GPPC_D5_GPU_CLKREQ0_N 42

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_33R_0201_1/20 W_F

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

G

1

RU90

_10K_0201_1/20 W_J(±5%)

3

XTAL_38P4M_SOC_IN_R

SUS_CLK_WLANSUS_CLK

XTAL_32K_SOC_OUT_R

XTAL_32K_SOC_IN_R

EC_RTCRST 45

电阻

_200K_0201_1/20 W_F( ±1%)

SUS_CLK_WLAN 50

电阻

_10M_0201_1/20 W_J(±5%)

RU81

YU2

38.4MHZ

2

GND1

RU87

1

1

GND2

X3S038400BA1H-HS

CU6电容_5.6pF_0201_C0G_50 V_C(±0.25pF)

YU1

Q13FC1350000200

RTC CRYSTAL

1 2

CU7电容_5.6pF_0201_C0G_50 V_C(±0.25pF)

2

CU8电容_8.2pF_0201_C0G_50 V_C(±0.25pf)

3

3

MAIN 38.4MHZ CRYSTAL

4

CU9电容_8.2pF_0201_C0G_50 V_C(±0.25pf)

Page name:

Page name:

Page name:

Size:

Size:

Size:

Date:

Date:

Date:

电阻

_27K_0201_1/20 W_F

RU91

SRTC_RST_N

RTC_RST_N

TPU818MIL

TPU918MIL

TGL-UP3(CNVI/CSI/CLK)

TGL-UP3(CNVI/CSI/CLK)

TGL-UP3(CNVI/CSI/CLK)

Project

Project

Project

Name:

Name:

Name:

A4

A4

A4

Thursday, July 09, 2020 9 84

Thursday, July 09, 2020 9 84

Thursday, July 09, 2020 9 84

电容

_1uF_0201_X5R_6.3 V_M(±20%)

1

ns

1

ns

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

CU10

Sheet: of

Sheet: of

Sheet: of

1

+VCCRTC

电阻

_27K_0201_1/20 W_F

电容

_1uF_0201_X5R_6.3 V_M(±20%)

RU89

CU11

REV:

REV:

REV:

V4.0

V4.0

V4.0

5

V2

SSD1_PWR_EN48,49

GPPC_B_14_SPKR62

PCH_WLAN_OFF_N50

TPU1018MIL

TPU1118MIL

TPU1218MIL

I2C1_SOC_SCL64

I2C1_SOC_SDA64

TP_I2C1_SOC_SCL46

TP_I2C1_SOC_SDA46

TCH_EN_SOC46

TOUCHPAD_INT_N64

GPPC_C_13_GPU_PERST_N42

GPU_EVENT_N

RIPQ_N_SOC43

WAKE_PCIE_N_SOC50

WLAN_RST_N50

+V3P3SX

UART2_TXD67

UART2_RXD67

D D

TOUCH PAD

ns

C C

GPPC_B18_GSPI0_MOSI

GPPC_B_14_SPKR

PCH_WLAN_OFF_N

GPSI1_CLK

1

ns

GPSI1_MOSI

1

ns

GPSI1_MISO

1

ns

TCH_EN_SOC

TOUCHPAD_INT_N

GPU_EVENT_N

RIPQ_N_SOC

UART2_TXD

UART2_RXD

WAKE_PCIE_N_SOC

WLAN_RST_N

I2C1_SOC_SCL

I2C1_SOC_SDA

RU111

电阻

_10K_0201_1/20 W_J(±5%)

GPU_EVENT_N

UU1F

DC53

GPP_B16/GSPI0_CLK

DA51

GPP_B18/GSPI0_MOSI

DC49

GPP_B17/GSPI0_MISO

DC50

GPP_B14/SPKR/TIME_SYNC1/GSPI0_CS1#

DC52

GPP_B15/GSPI0_CS0#

CY49

GPP_B20/GSPI1_CLK

CY53

GPP_B22/GSPI1_MOSI

CY52

GPP_B21/GSPI1_MISO

DA50

GPP_B19/GSPI1_CS0#

DV21

GPP_C9/UART0_TXD

DT21

GPP_C8/UART0_RXD

DR21

GPP_C11/UART0_CTS#

DW21

GPP_C10/UART0_RTS#

DV19

GPP_C13/UART1_TXD/ISH_UART1_TXD

DT19

GPP_C12/UART1_RXD/ISH_UART1_RXD

DR18

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

DU19

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

DJ21

GPP_C21/UART2_TXD

DG23

GPP_C20/UART2_RXD

DJ19

GPP_C23/UART2_CTS#

DF21

GPP_C22/UART2_RTS#

DV18

GPP_C17/I2C0_SCL

DW18

GPP_C16/I2C0_SDA

DJ23

GPP_C19/I2C1_SCL

DT18

GPP_C18/I2C1_SDA

DJ29

GPP_H5/I2C2_SCL

DJ31

GPP_H4/I2C2_SDA

DF29

GPP_H7/I2C3_SCL

DG29

GPP_H6/I2C3_SDA

DF25

GPP_H9/I2C4_SCL/CNV_MFUART2_TXD

DF27

GPP_H8/I2C4_SDA/CNV_MFUART2_RXD

TGL_UP3_IP_EXT/BGA

4

6 OF 21

GPP_D15/ISH_UART0_RTS#/GSPI2_CS1#/IM GCLKOUT5

+V3P3SX

ns

RU119

RU120

ns

RU122

ns

CU13

ns

3

GPP_D14/ISH_UART0_TXD

GPP_D13/ISH_UART0_RXD

GPP_D16/ISH_UART0_CTS#

GPP_B6/ISH_I2C0_SCL

GPP_B5/ISH_I2C0_SDA

GPP_B8/ISH_I2C1_SCL

GPP_B7/ISH_I2C1_SDA

GPP_B10/I2C5_SCL/ISH_I2C2_SCL

GPP_B9/I2C5_SDA/ISH_I2C2_SDA

GPP_E16/ISH_GP7

GPP_E15/ISH_GP6

GPP_D18/ISH_GP5

GPP_D17/ISH_GP4

GPP_D3/ISH_GP3/BK3/SBK3

GPP_D2/ISH_GP2/BK2/SBK2

GPP_D1/ISH_GP1/BK1/SBK1

GPP_D0/ISH_GP0/BK0/SBK0

可以删掉,待再确认

电阻

_10K_0201_1/20 W_J(±5%)

电阻

_10K_0201_1/20 W_J(±5%)

电阻

_10K_0201_1/20 W_J(±5%)

电容

_10nF_0201_X7R_16 V_K

GPP_RCOMP

GPP_T3

GPP_T2

GPP_U5

GPP_U4

GPU_PWREN

PCH_GPU_RST_N_R

PCH_GPU_RST_N

DR27

CNVI_EN_N

DW27

DV25

DT25

DB45

DB44

CY39

DB47

DD47

DD44

DJ8

DR7

GPU_PWROK_R

DR24

DU25

FB_GC6_EN_R

DV31

DU31

PCH_GPU_RST_N_R

DT27

GPU_PWREN

DV27

GPPC_RCOMP

DR51

DN33

DT35

DG17

DG19

RU121

CNVI_EN_N 50

可以删掉,待再确认

ns

RU116

RU115

ns

RU309

ns

电阻

电阻

_0R_0201_1/20 W_J(±5%)

2

电阻

_0R_0201_1/20 W_J(±5%)

电阻

_0R_0201_1/20 W_J(±5%)

_200R_0201_1/20 W_F(±1%)

GPU_PWREN

PCH_GPU_RST_N

GPU_PG_Q

GPU_PWROK

FB_GC6_EN_R

1

PCH STRAP

+V3P3SX

ns

+V3P3A_PCH

电阻

_4.7K_0201_1/20 W_J

FLASH DESCRIPTOR SECURITY OVERRIDE

+V3P3A_PCH

RU118

RU112

ns

电阻

_4.7K_0201_1/20 W_J

GPPC_B_14_SPKR

RU113

电阻

_20K_0201_1/20 W_J

+V1P8SX

RU114

ns

RU117

ns

电阻

_20K_0201_1/20 W_J

ns

TOP SWAP OVERRIDE

GPPC_B_14_SPKR

0: Disable Top Swap mode. (Default)

1: Enable

Internal 20K PD

NO REBOOT

GPPC_B18_GSPI0_MOSI

0: Disable No Reboot mode. (Default)

1: Enable

Internal 20K PD

RU312

电阻

_4.7K_0201_1/20 W_J

GPPC_B18_GSPI0_MOSI

HDA_SDO_R

0: SECURITY MEASURES NOT OVERRIDEN

1: OVERRIDEN

WEAK INTERNAL PD 20K

电阻

_4.7K_0201_1/20 W_J

HDA_SDO

UU1G

DW15

GPP_F8/I2S_MCLK2_INOUT

B B

A A

RETIMER_FORCE_PWR52,53

PCH_DMIC1_CLK046

PCH_DMIC1_DATA046

RU136

电容

_27pF_0201_C0G_25 V_J

CU15

ns

5

RETIMER_FORCE_PWR

电阻

_33R_0201_1/20 W_F

电容

_27pF_0201_C0G_25 V_J

CU14

ns

PCH_DMIC1_CLK0_R

PCH_DMIC1_DATA0PCH_DMIC1_CLK0

DW24

GPP_D19/I2S_MCLK1

DG41

GPP_A23/I2S1_SCLK

DT38

GPP_R7/I2S1_SFRM

DV38

GPP_R6/I2S1_TXD

DW38

GPP_R5/HDA_SDI1/I2S1_RXD

DN31

GPP_S6/SNDW3_CLK/DMIC_ CLK_A0

DM31

GPP_S7/SNDW3_DATA/DMIC_DATA0

DK33

GPP_S4/SNDW2_CLK/DMIC_ CLK_A1

DK31

GPP_S5/SNDW2_DATA/DMIC_DATA1

DW35

GPP_S2/SNDW1_CLK/DMIC_ CLK_B0

DV35

GPP_S3/SNDW1_DATA/DMIC_CLK_ B1

DT32

GPP_S0/SNDW0_CLK

DR35

GPP_S1/SNDW0_DATA

TGL_UP3_IP_EXT/BGA

4

7 OF 21

GPP_R0/HDA_BCLK/I2S0_SCLK

GPP_R1/HDA_SYNC/I2S0_SFRM

GPP_R2/HDA_SDO/I2S0_TXD

GPP_R3/HDA_SDI0/I2S0_RXD

GPP_A8/I2S2_SFRM/CNV_RF_RESET#/DM IC_DATA_0

GPP_A9/I2S2_TXD/MODEM_CLKREQ/CRF_ XTAL_CLKREQ/DMIC_CLK_A1

HDA_SYNC

HDA_BCLK

HDA_SDO

HDA_RST

HDA_SDI

CU18电容_2pF_0201_

ns

CU19电容_2pF_0201_

ns

CU20电容_2pF_0201_

ns

CU21电容_2pF_0201_

ns

CU22电容_2pF_0201_

ns

GPP_A7/I2S2_SCLK/DMIC_CLK_A0

GPP_A10/I2S2_RXD/DMIC_DATA1

GPP_A11/PMC_I2C_SDA/I2S3_SCLK

GPP_A13/PMC_I2C_SCL/I2S3_TXD/DMI C_CLK_B0

国际标准

国际标准

国际标准

国际标准

国际标准

Close to CPU

3

GPP_R4/HDA_RST#

SNDW_RCOMP

_25 V_C(±0.25pf)

_25 V_C(±0.25pf)

_25 V_C(±0.25pf)

_25 V_C(±0.25pf)

_25 V_C(±0.25pf)

HDA_SDO EC_ME_UNLOCK

DR38

DU37

DT37

HDA_SDI

DV37

HDA_RST HDA_RST_R

DV41

SOC_BT_PCMCLK M.2_BT_PCMCLK

DL53

CNV_RF_RESET_N

DG51

CNV_MFUART2_RXD

DG50

CNV_MODEM_CLKREQ

DL49

DL52

BT_RF_KILL_N

DH49

SNDW_RCOMP

DF33

2

RU125

电阻

_4.7K_0201_1/20 W_J

Close to CPU

电阻

_200R_0201_1/20 W_F( ±1%)

电阻

RU127

电阻

RU129

电阻

RU131

电阻

RU133

电阻

RU135

GPPC_A_11_GPU_PERST_N 42

RU137

电容

_100nF_0201_X5R_6.3 V_ K(±10%)

EC_ME_UNLOCK 45

_33R_0201_1/20 W_F

_33R_0201_1/20 W_F

_33R_0201_1/20 W_F

_33R_0201_1/20 W_F

_33R_0201_1/20 W_F

Page name:

Page name:

Page name:

Size:

Size:

Size:

Date:

Date:

Date:

HDA_BCLK_RHDA_BCLK

HDA_SYNC_RHDA_SYNC

HDA_SDO_RHDA_SDO

CNV_MFUART2_RXD 50

CNV_MODEM_CLKREQ 50

Config to 1.8V level

BT_RF_KILL_N 50

CNV_MODEM_CLKREQ

电阻

电阻

_71.5K_0201_1/20_F(±1%)

CU169

TGL-UP3(HDA/I2C/ISH/GSPI)

TGL-UP3(HDA/I2C/ISH/GSPI)

TGL-UP3(HDA/I2C/ISH/GSPI)

Project

Project

Project

Name:

Name:

Name:

A4

A4

A4

Thursday, July 09, 2020 10 84

Thursday, July 09, 2020 10 84

Thursday, July 09, 2020 10 84

CNV_RF_RESET_N

_75K_0201_1/20 W_F(±1%)

RU140

RU139

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

Swift 3X_TGL-UP3

1

HDA_BCLK_R 62

HDA_SYNC_R 62

HDA_SDO_R 62

HDA_SDI 62

HDA_RST_R 62

M.2_BT_PCMCLK 50

CNV_RF_RESET_N 50

Sheet: of

Sheet: of

Sheet: of

REV:

REV:

REV:

V4.0

V4.0

V4.0

5

4

3

2

1

UU1I

PCIE3_SATA_SSD_TX3_DP48

PCIE3_SATA_SSD_TX3_DN48

PCIE3_SATA_SSD_RX3_DP48

PCIE3_SATA_SSD_RX3_DN48

PCIE3_SSD_TX2_DP48

D D

SSD1

SSD2

PCIE3_SSD_TX2_DN48

PCIE3_SSD_RX2_DP48

PCIE3_SSD_RX2_DN48

PCIE3_SSD_TX1_DP48

PCIE3_SSD_TX1_DN48

PCIE3_SSD_RX1_DP48

PCIE3_SSD_RX1_DN48

PCIE3_SSD_TX0_DP48

PCIE3_SSD_TX0_DN48

PCIE3_SSD_RX0_DP48

PCIE3_SSD_RX0_DN48

PCIE8_CTX_DRX_P49

PCIE8_CTX_DRX_N49

PCIE8_CRX_DTX_P49

PCIE8_CRX_DTX_N49

PCIE7_CTX_DRX_P49

PCIE7_CTX_DRX_N49

PCIE7_CRX_DTX_P49

PCIE7_CRX_DTX_N49

PCIE6_CTX_DRX_P49

PCIE6_CTX_DRX_N49

PCIE6_CRX_DTX_P49

PCIE6_CRX_DTX_N49

PCIE5_CTX_DRX_P49

PCIE5_CTX_DRX_N49

PCIE5_CRX_DTX_P49

PCIE5_CRX_DTX_N49

PCIE3_SATA_SSD_TX3_DP

PCIE3_SATA_SSD_TX3_DN

PCIE3_SATA_SSD_RX3_DP

PCIE3_SATA_SSD_RX3_DN

PCIE3_SSD_TX2_DP

PCIE3_SSD_TX2_DN

PCIE3_SSD_RX2_DP

PCIE3_SSD_RX2_DN

PCIE3_SSD_TX1_DP

PCIE3_SSD_TX1_DN

PCIE3_SSD_RX1_DP

PCIE3_SSD_RX1_DN

PCIE3_SSD_TX0_DP

PCIE3_SSD_TX0_DN

PCIE3_SSD_RX0_DP

PCIE3_SSD_RX0_DN

PCIE8_CTX_DRX_P

PCIE8_CTX_DRX_N

PCIE8_CRX_DTX_P

PCIE8_CRX_DTX_N

PCIE7_CTX_DRX_P

PCIE7_CTX_DRX_N

PCIE7_CRX_DTX_P

PCIE7_CRX_DTX_N

PCIE6_CTX_DRX_P

PCIE6_CTX_DRX_N

PCIE6_CRX_DTX_P

PCIE6_CRX_DTX_N

PCIE5_CTX_DRX_P

PCIE5_CTX_DRX_N

PCIE5_CRX_DTX_P

PCIE5_CRX_DTX_N

teknisi indonesia

C C

WLAN

USB3.1 Type-A for DB

USB3.1 Type-A AOU

PCIE3_WLAN_TX_DP50

PCIE3_WLAN_TX_DN50

PCIE3_WLAN_RX_DP50

PCIE3_WLAN_RX_DN50

USB3_TYPEA2_TX_DP66

USB3_TYPEA2_TX_DN66

USB3_TYPEA2_RX_DP66

USB3_TYPEA2_RX_DN66

USB3_TYPEA_TX_DP61

USB3_TYPEA_TX_DN61

USB3_TYPEA_RX_DP61

USB3_TYPEA_RX_DN61

PCIE3_WLAN_TX_DP

PCIE3_WLAN_TX_DN

PCIE3_WLAN_RX_DP

PCIE3_WLAN_RX_DN

USB3_TYPEA2_TX_DP

USB3_TYPEA2_TX_DN

USB3_TYPEA2_RX_DP

USB3_TYPEA2_RX_DN

USB3_TYPEA_TX_DP

USB3_TYPEA_TX_DN

USB3_TYPEA_RX_DP

USB3_TYPEA_RX_DN

BT7

PCIE12_TXP/SATA1_TXP

BT8

PCIE12_TXN/SATA1_TXN

CE2

PCIE12_RXP/SATA1_RXP

CE1

PCIE12_RXN/SATA1_RXN

BT9

PCIE11_TXP/SATA0_TXP

BV9

PCIE11_TXN/SATA0_TXN

CF4

PCIE11_RXP/SATA0_RXP

CF3

PCIE11_RXN/SATA0_RXN

BV7

PCIE10_TXP

BV8

PCIE10_TXN

CG2

PCIE10_RXP

CG1

PCIE10_RXN

BY7

PCIE9_TXP

BY8

PCIE9_TXN

CG5

PCIE9_RXP

CG4

PCIE9_RXN

CB8

PCIE8_TXP

CB7

PCIE8_TXN

CK5

PCIE8_RXP

CK4

PCIE8_RXN

CD9

PCIE7_TXP

CD8

PCIE7_TXN

CK1

PCIE7_RXP

CK2

PCIE7_RXN

CG8

PCIE6_TXP

CG7

PCIE6_TXN

CL4

PCIE6_RXP

CL3

PCIE6_RXN

CJ8

PCIE5_TXP

CJ7

PCIE5_TXN

CN2

PCIE5_RXP

CN1

PCIE5_RXN

CR8

PCIE4_TXP/USB31_4_TXP

CR7

PCIE4_TXN/USB31_4_TXN

CN5

PCIE4_RXP/USB31_4_RXP

CN4

PCIE4_RXN/USB31_4_RXN

CU8

PCIE3_TXP/USB31_3_TXP

CU7

PCIE3_TXN/USB31_3_TXN

CT2

PCIE3_RXP/USB31_3_RXP

CT1

PCIE3_RXN/USB31_3_RXN

CW8

PCIE2_TXP/USB31_2_TXP

CW7

PCIE2_TXN/USB31_2_TXN

CU3

PCIE2_RXP/USB31_2_RXP

CT4

PCIE2_RXN/USB31_2_RXN

DA8

PCIE1_TXP/USB31_1_TXP

DA7

PCIE1_TXN/USB31_1_TXN

CV2

PCIE1_RXP/USB31_1_RXP

CV1

PCIE1_RXN/USB31_1_RXN

TGL_UP3_IP_EXT/BGA

9 OF 21

GPP_E0/SATAXPCIE0/SATAGP0

GPP_A12/SATAXPCIE1/SATAGP1/I2S3_SFRM

GPP_A16/USB_OC3#/I2S4_SFRM

GPP_H15/M2_SKT2_CFG3

GPP_H14/M2_SKT2_CFG2

GPP_H13/M2_SKT2_CFG1

GPP_H12/M2_SKT2_CFG0

USB2P_10

USB2N_10

USB2P_9

USB2N_9

USB2P_8

USB2N_8

USB2P_7

USB2N_7

USB2P_6

USB2N_6

USB2P_5

USB2N_5

USB2P_4

USB2N_4

USB2P_3

USB2N_3

USB2P_2

USB2N_2

USB2P_1

USB2N_1

GPP_E9/USB_OC0#

GPP_E5/DEVSLP1

GPP_E4/DEVSLP0

PCIE_RCOMP_P

PCIE_RCOMP

USB_VBUSSENSE

USB_ID

USB2_COMP

RSVD_BSCAN

CV4

CY3

DD5

DD4

CW9

DA9

DD1

DD2

DA1

DA2

DA12

DA11

DC8

DC7

DB4

DB3

DA5

DA4

DC11

DC9

DP4

DF41

DD8

DJ45

DN6

DG8

DN29

DK29

DT31

DR32

DV9

DT9