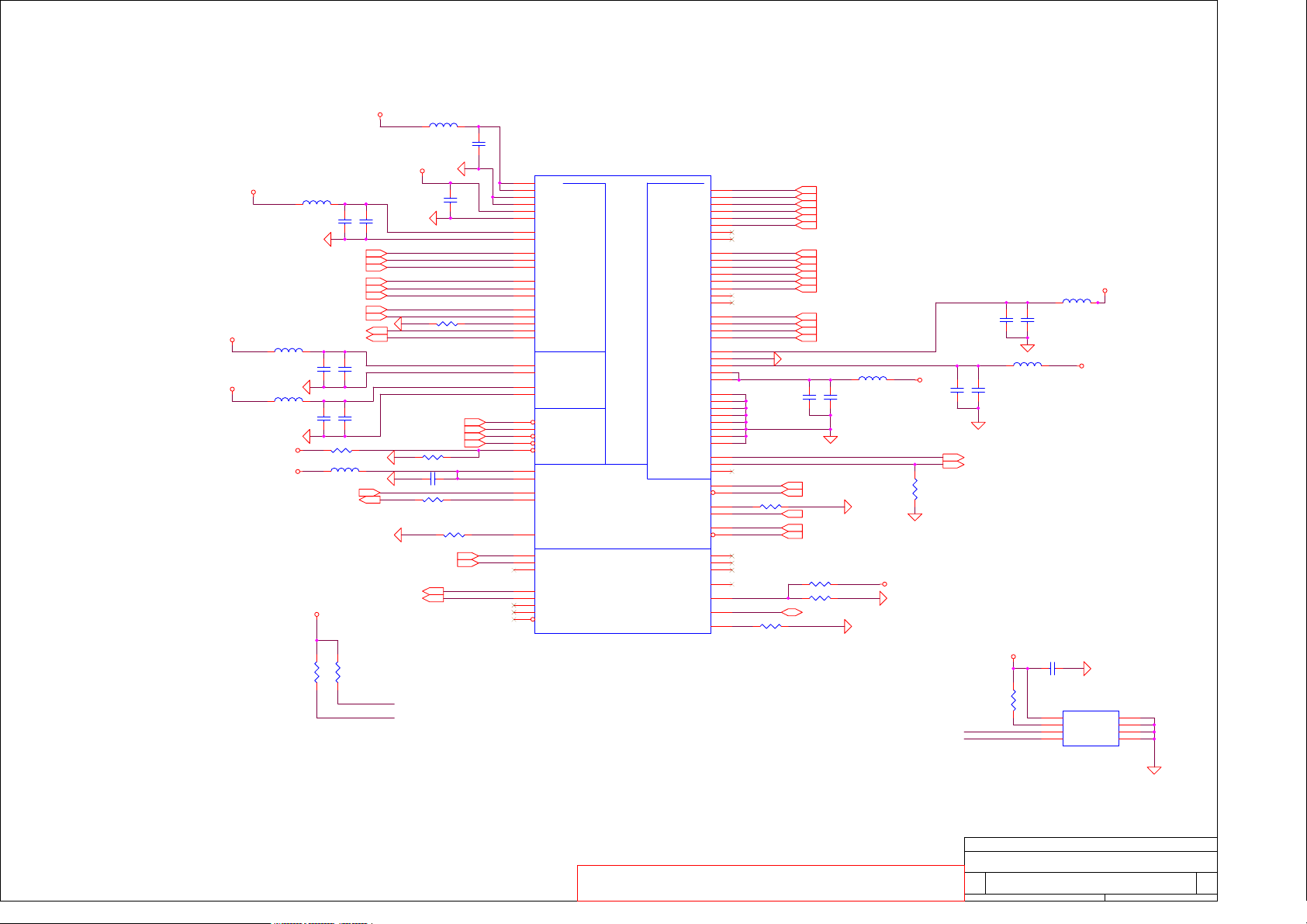

HP ZV6000 Schematics

A

1 1

2 2

B

C

D

E

Compal confidential

Schematics Document

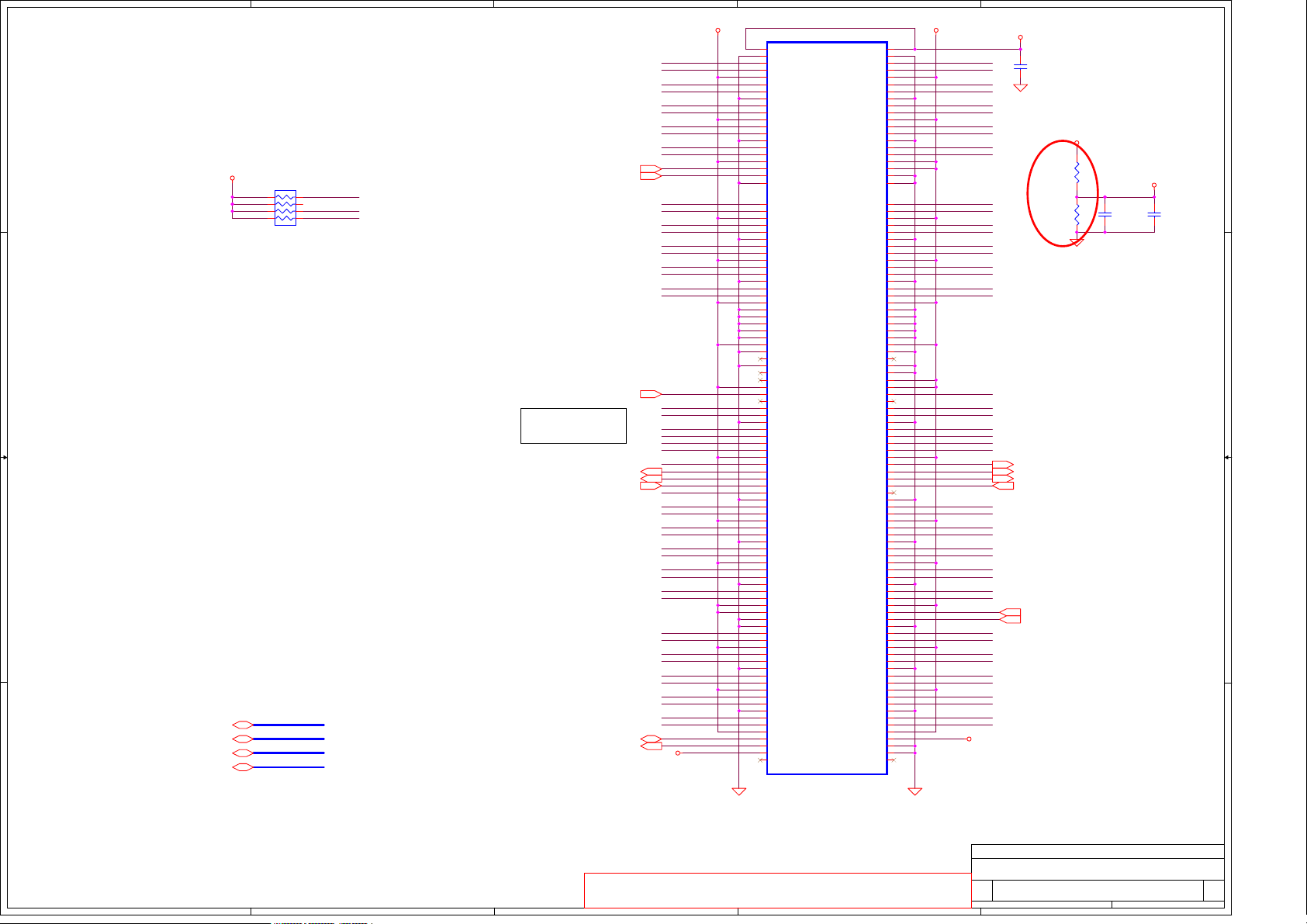

AMD K8 with

3 3

4 4

A

ATI RS480M+ATI SB400

2005-01-04

REV:0.6

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

LA-2421

Cover Sheet

E

of

156Wednesday, January 05, 2005

0.6

A

Compal confidential

File Name : LA-2421

B

C

D

E

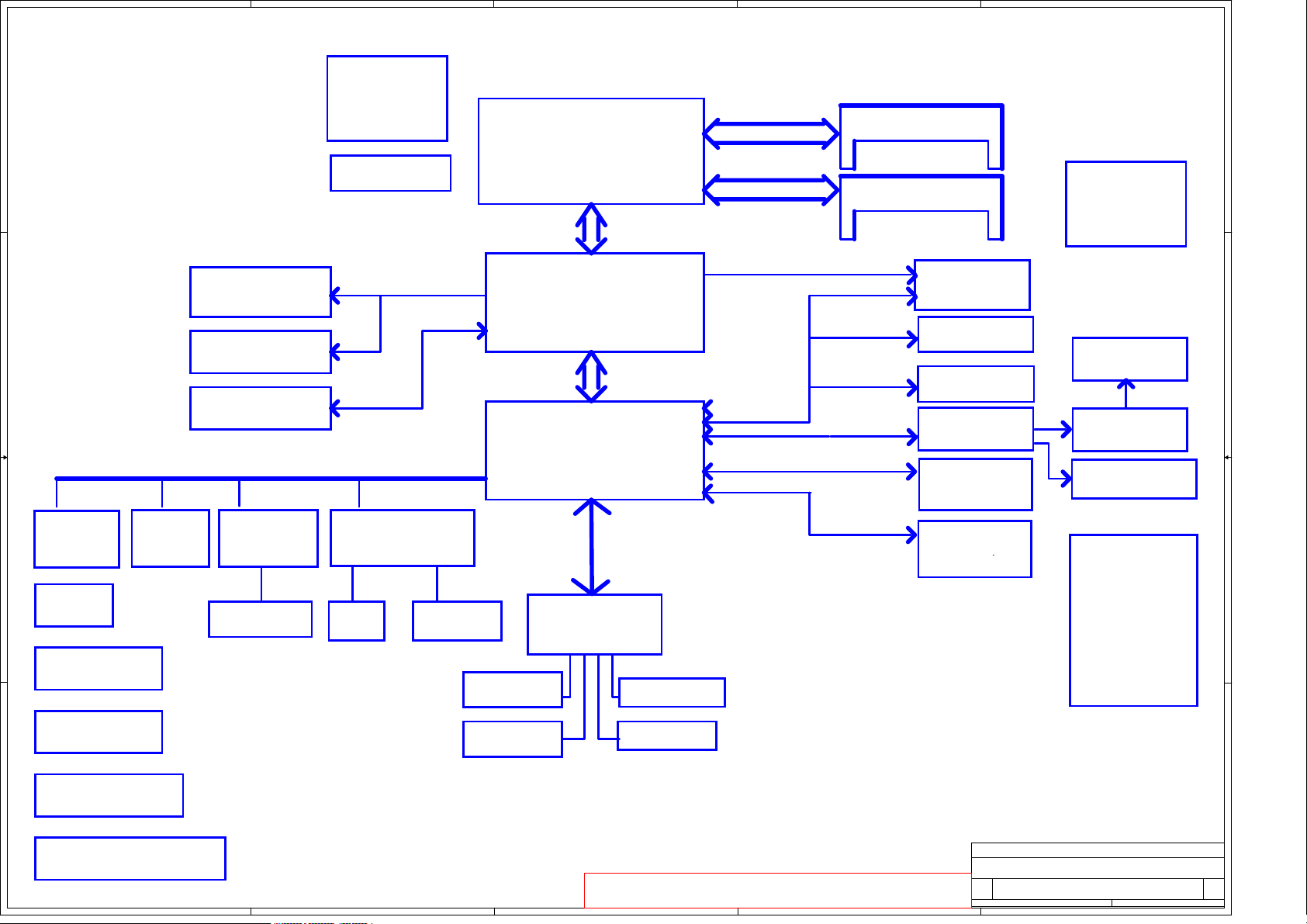

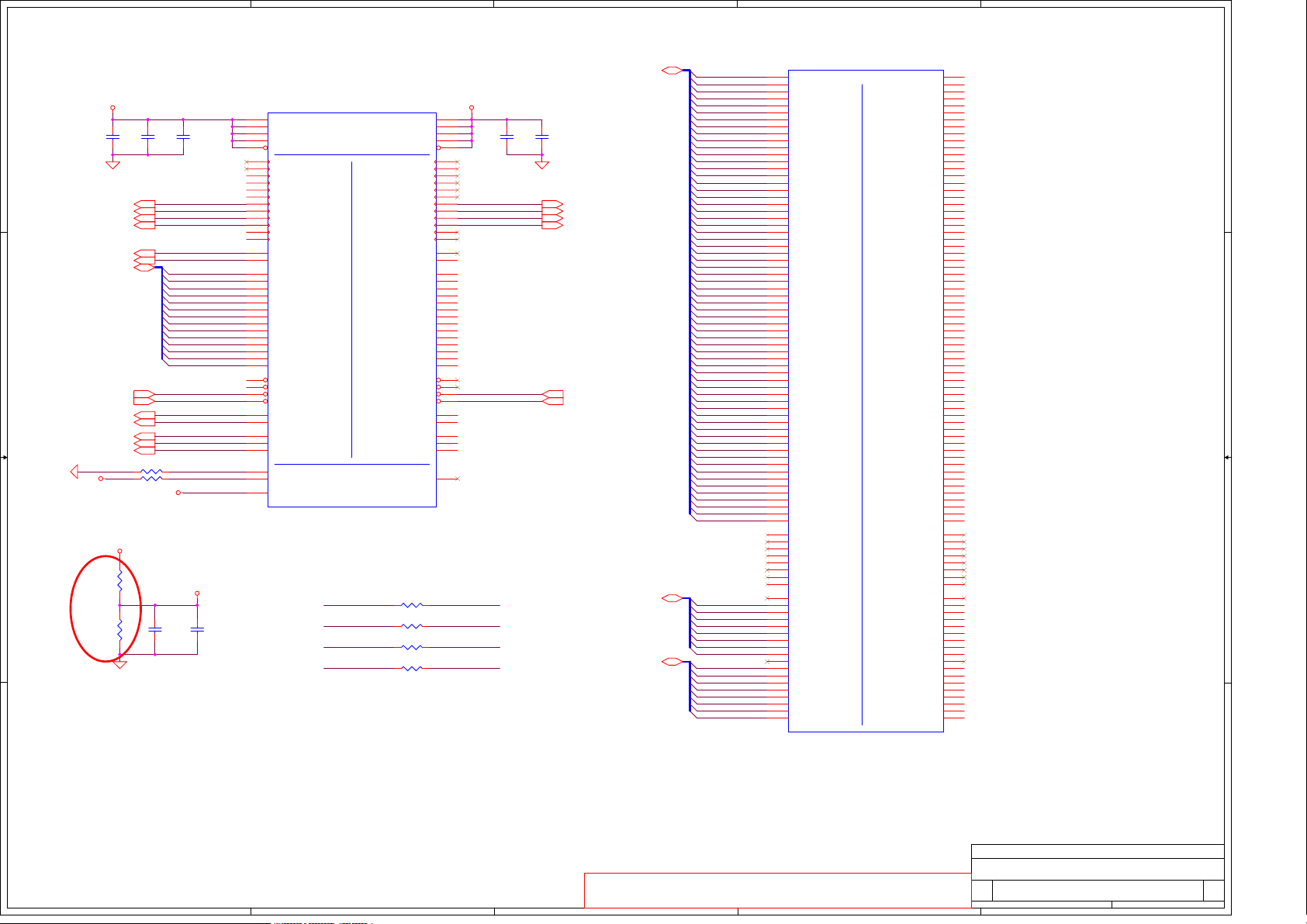

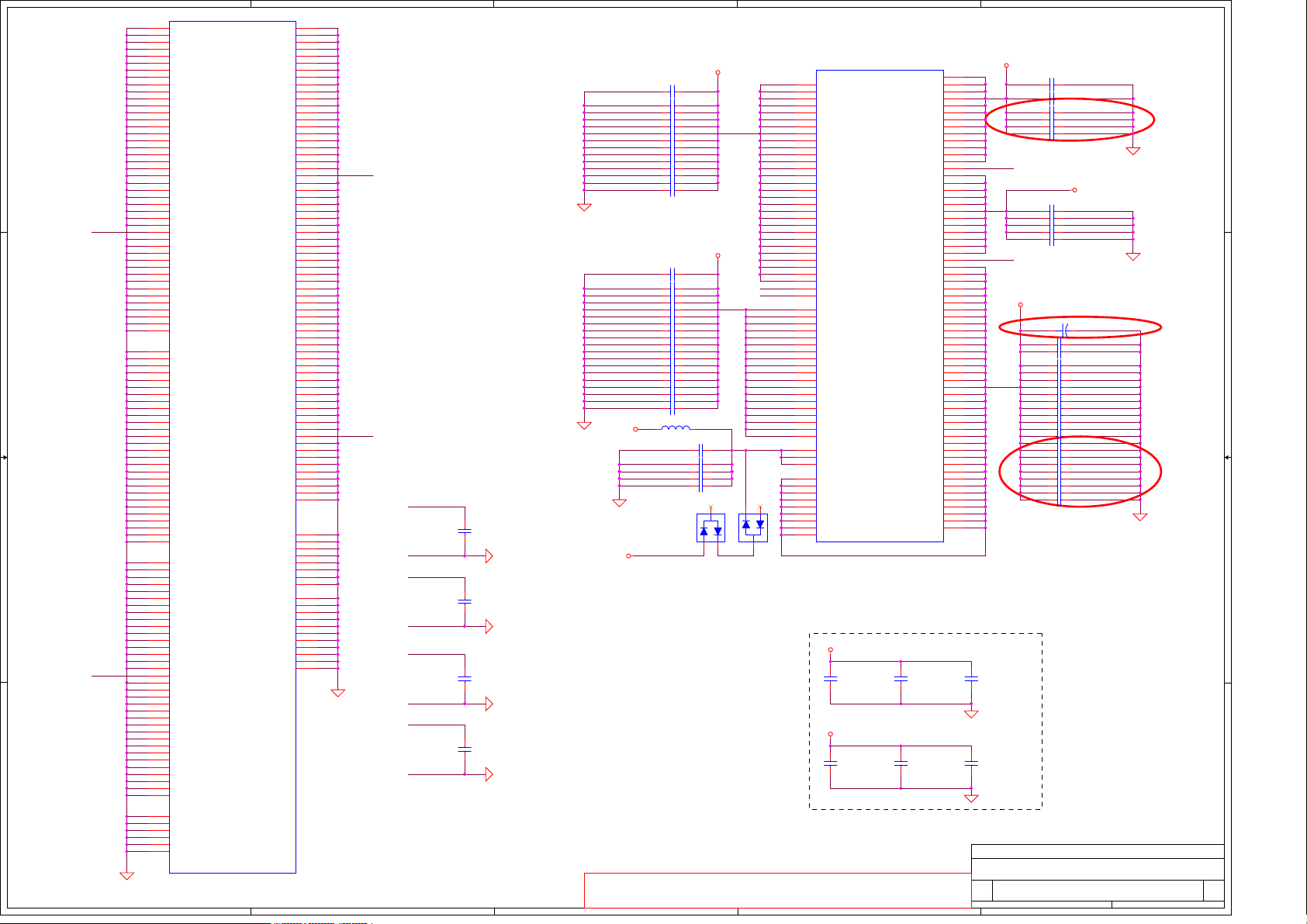

Thermal Sensor

1 1

LVDS Panel

Interface

page 17

ADM1032

Fan Control

page 6

page 4

AMD K8

939-pin

page 4, 5, 6, 7

HT 16x16 1000MHZ

ATI-RS480M

705 BGA

2 2

CRT & TV OUT

page 18

page 11, 12, 13, 14

A-Link Express

2 x PCIE

VGA DDR X2

page 15

ATI-SB400

IDSEL:AD18

(PIRQF#,GNT#3,REQ#3)

IDSEL:AD16

(PIRQE#,GNT#0,REQ#0)

TSB43AB22

IEEE 1394

3 3

page 27

Mini PCI

socket

page 29

RTL 8100CL

3.3V 33 MHz

IDSEL:AD22

(PIRQG#,GNT#1,REQ#1)

LAN

page 28

CardBus Controller

TI PCI6411

RTC CKT.

page 19

RJ45 CONN

page 28

Slot 0

page 25

Power OK CKT.

page 40

PCI BUS

IDSEL:AD20

(PIRQE#/F#/G#/H#,GNT#2,REQ#2)

page 24

Card reader

page 25

Touch Pad

564 BGA

page 19, 20, 21, 22

LPC BUS

ENE KB910(L)

page 37, 38

Int.KBD

page 36

Memory BUS(DDR)

2. 5V DDR- 200

2. 5V DDR- 200

1 x PCIE

USB2.0

AC-LINK

ATA-100

Primary IDE

ATA-100

Secondary IDE

page 36

DDR-SO-DIMM-0

BANK 0, 1, 2, 3

DDR-SO-DIMM-1

BANK 0, 1, 2, 3

page 8,10

page 9,10

New Card

Connector

USB conn X4

BT Conn

Audio CKT

HDD

Connector

CDROM

Connector

page 26

page 33

page 31

page 30

page 34

page 34

Clock Generator

ICS 951412

page 16

RJ45 CONN

page 31

MODEM

page 31

AMP & Audio Jack

page 32

SPR CONN.

page 41

*RJ45 CONN

*MIC IN JACK

*LINE OUT JACK

*1394 CONN

*SPDIF CONN

*DC JACK

*TVOUT CONN

*USB CONN x1

Power On/Off CKT.

page 36

DC/DC Int erface CKT.

4 4

page 42

Power Circuit DC/DC

page 43~49

A

B

EC I/O Bu ffer

page 39

BIOS

page 39

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

LA-2421

Block Diagram

E

of

256Wednesday, January 05, 2005

0.6

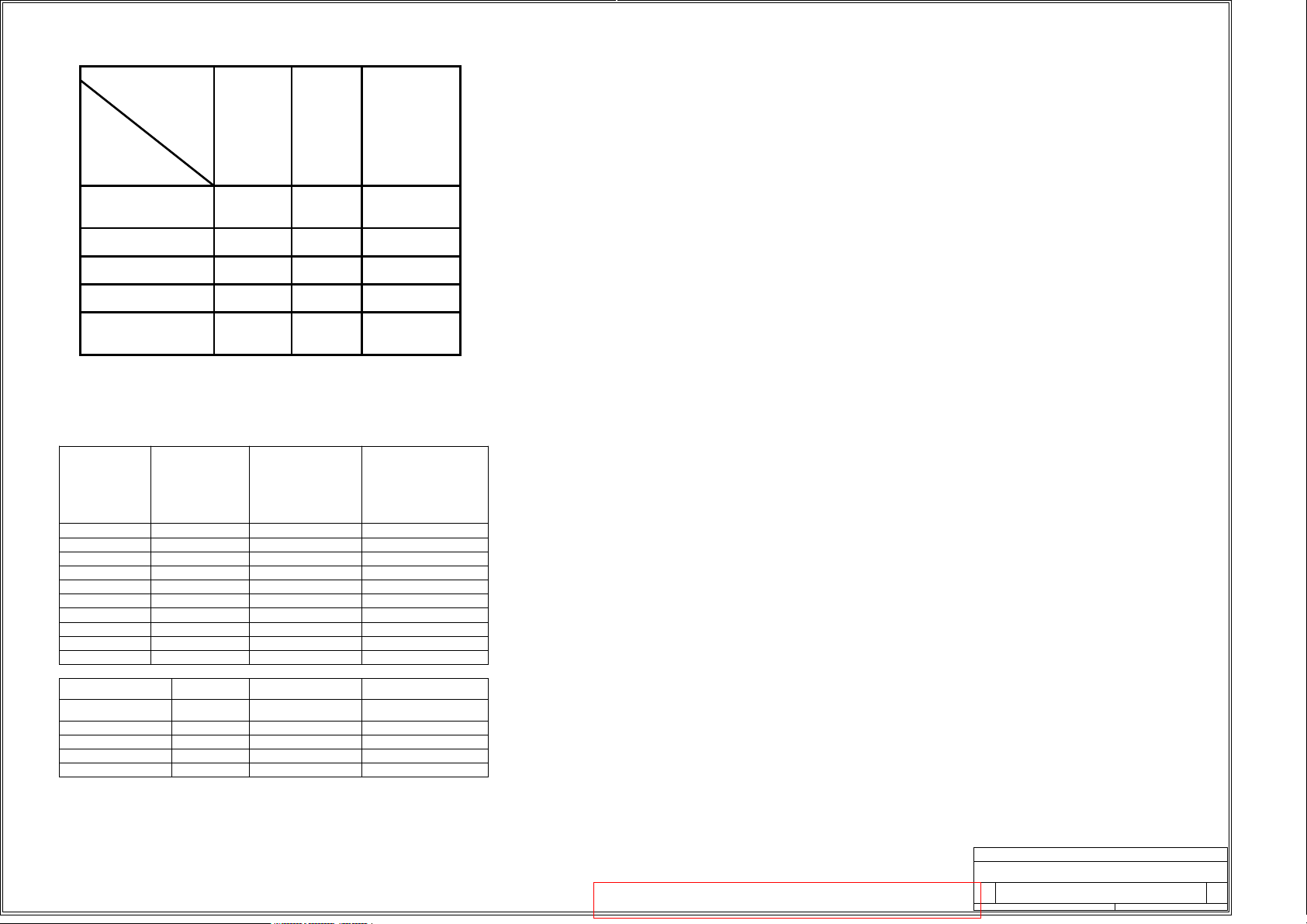

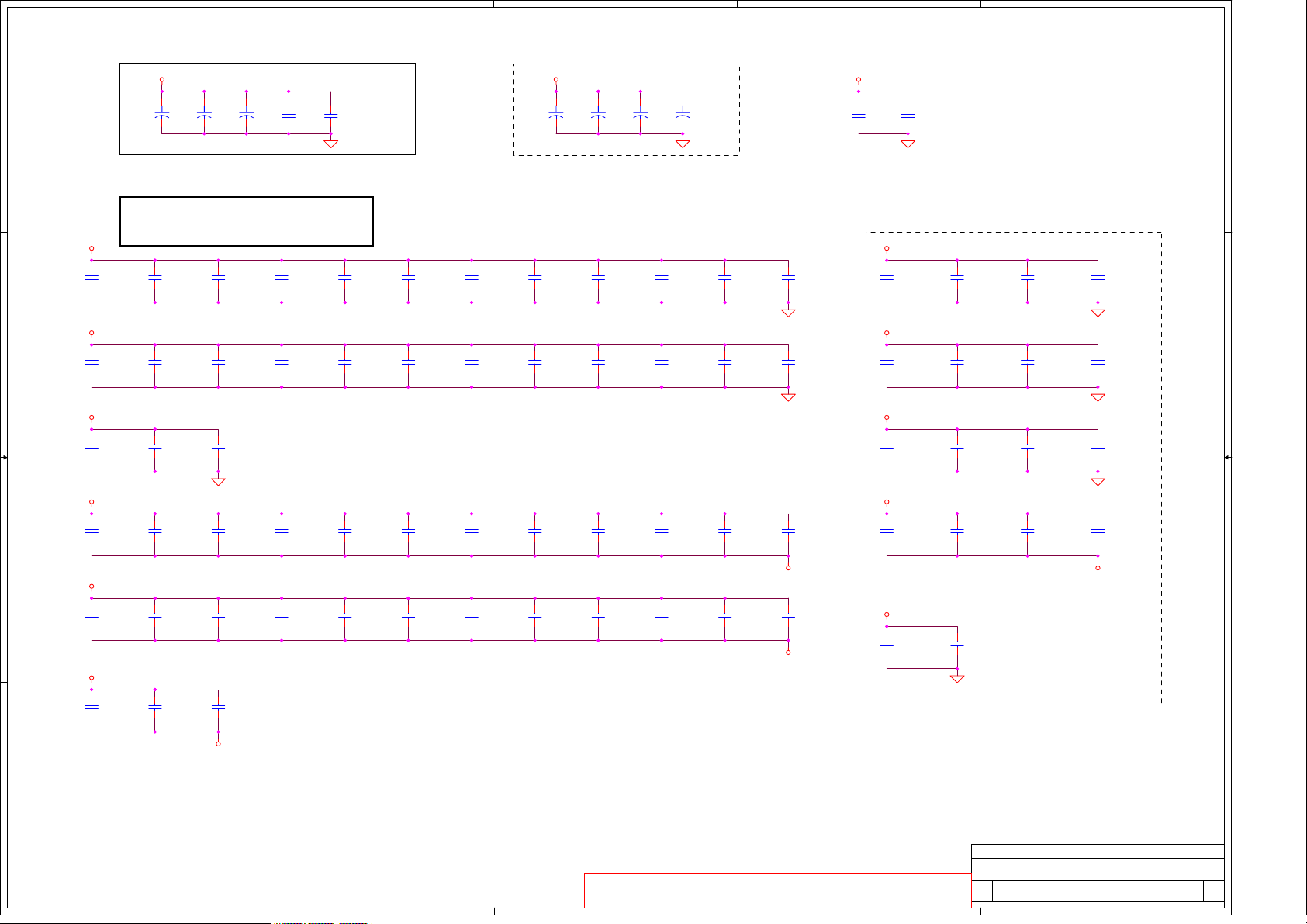

Voltage Rails

power

plane

State

+12VALW

+5VALW

+3VALW

+1.8VALW

+5V

+2.5V

+1.25V

A

+5VS

+3VS

+2.5VS

+1.8VS

+1.5VS

+2.5VDDA

+CPU_CORE

+1.2V_HT

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

O MEANS ON

X MEANS OFF

O

O

O

O

X

OO

OO

O

X

XX

XX

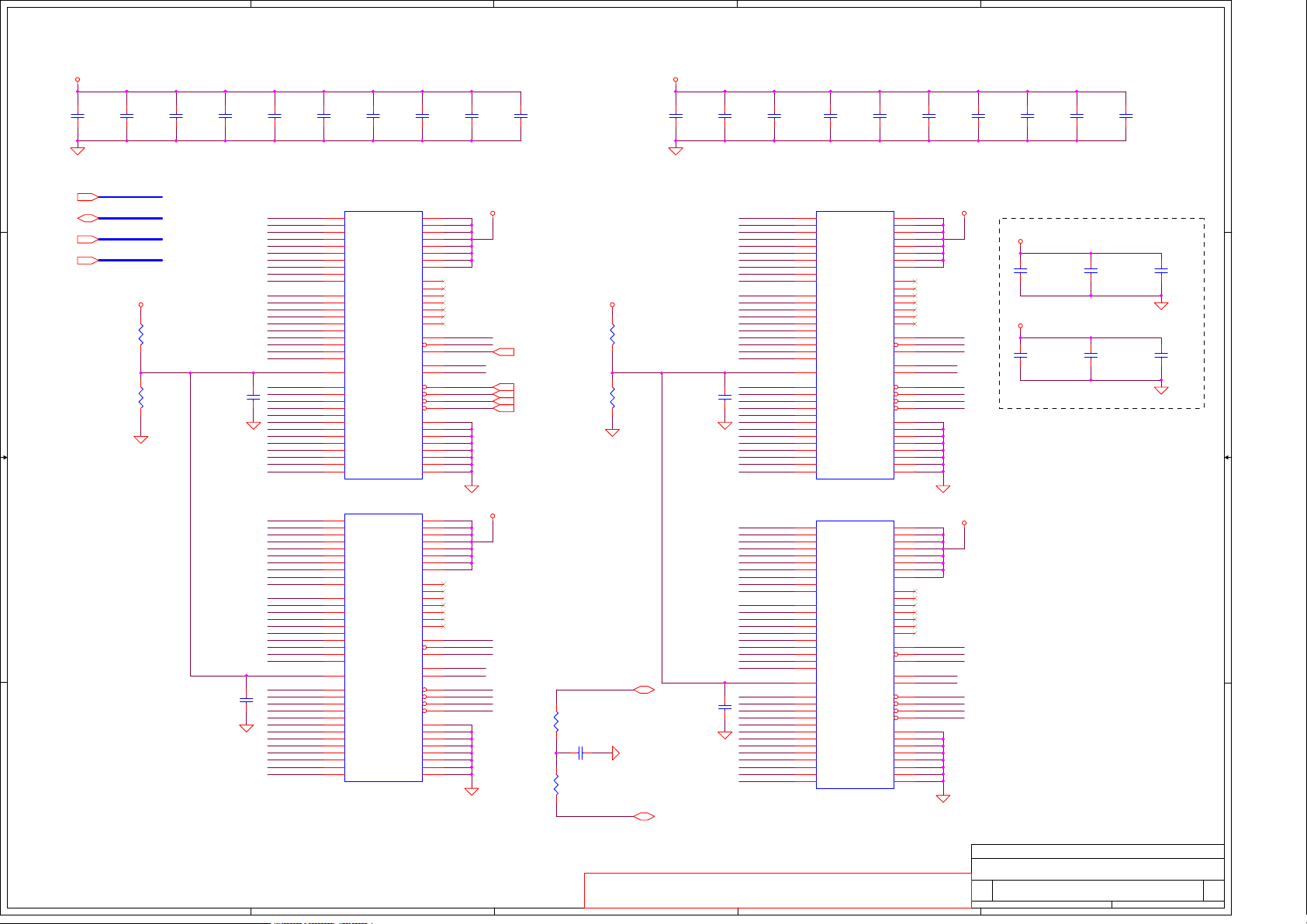

PCI Devices

1 1

INTERNAL

DEVICE

SMBUS

IDE

LPC I/F

PCI to PCI

AC97 AUDIO

AC97 MODEM B

OHCI#1 USB

OHCI#1 USB

EHCI USB

SATA#1

SATA#2

IDSEL # PIRQREQ/GNT #

A

B

D

D

D

A

A

EXTERNAL

1394

Wireless LAN

LAN

CARD BUS

Mini-PCI (no use)

AD16

AD18

AD22

AD20

AD19

0

3

1

2

4

E

F

G

E,F,G,H

F

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

LA-2421

Notes List

of

356Wednesday, January 05, 2005

0.6

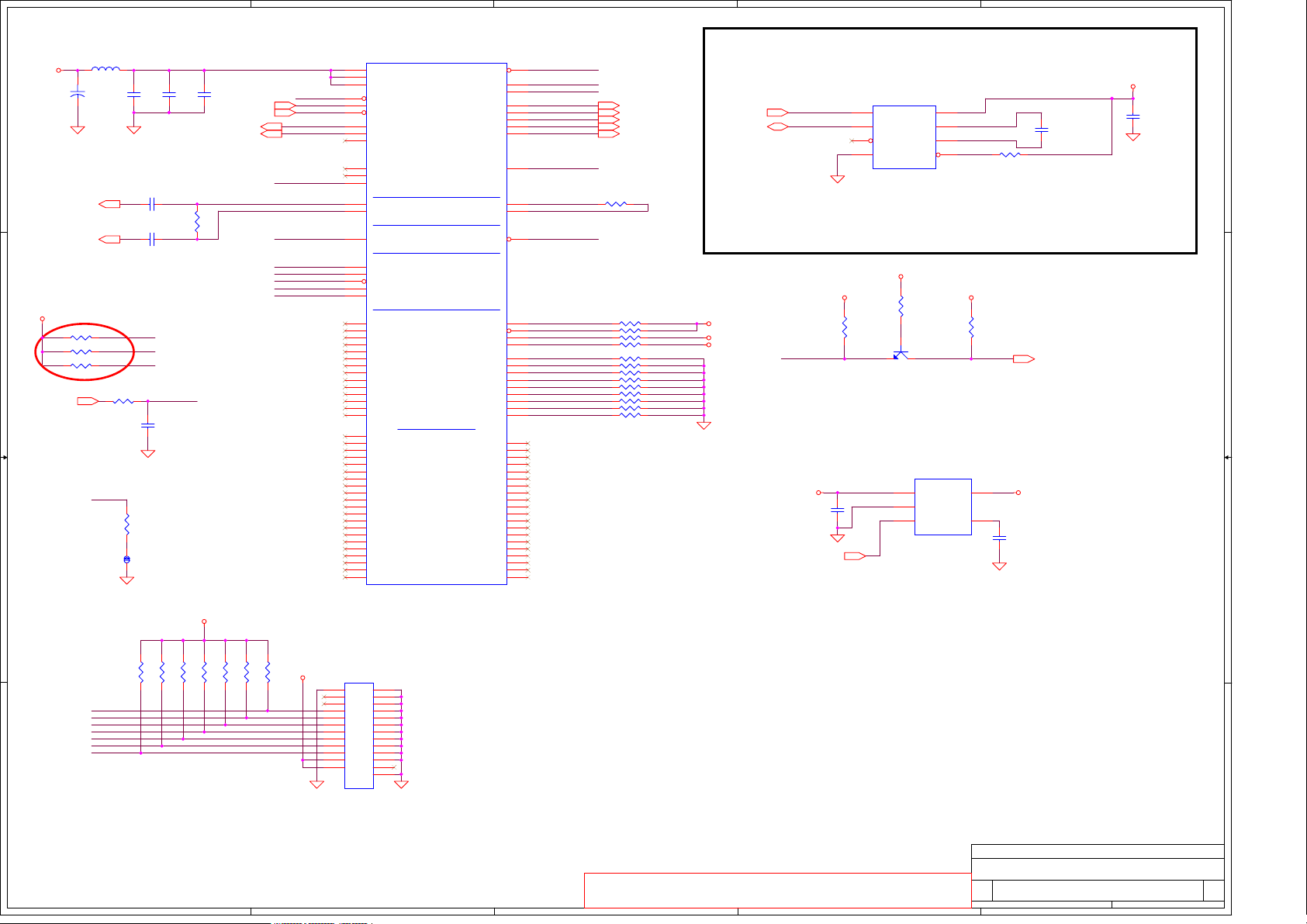

A

B

C

D

E

ZZZ

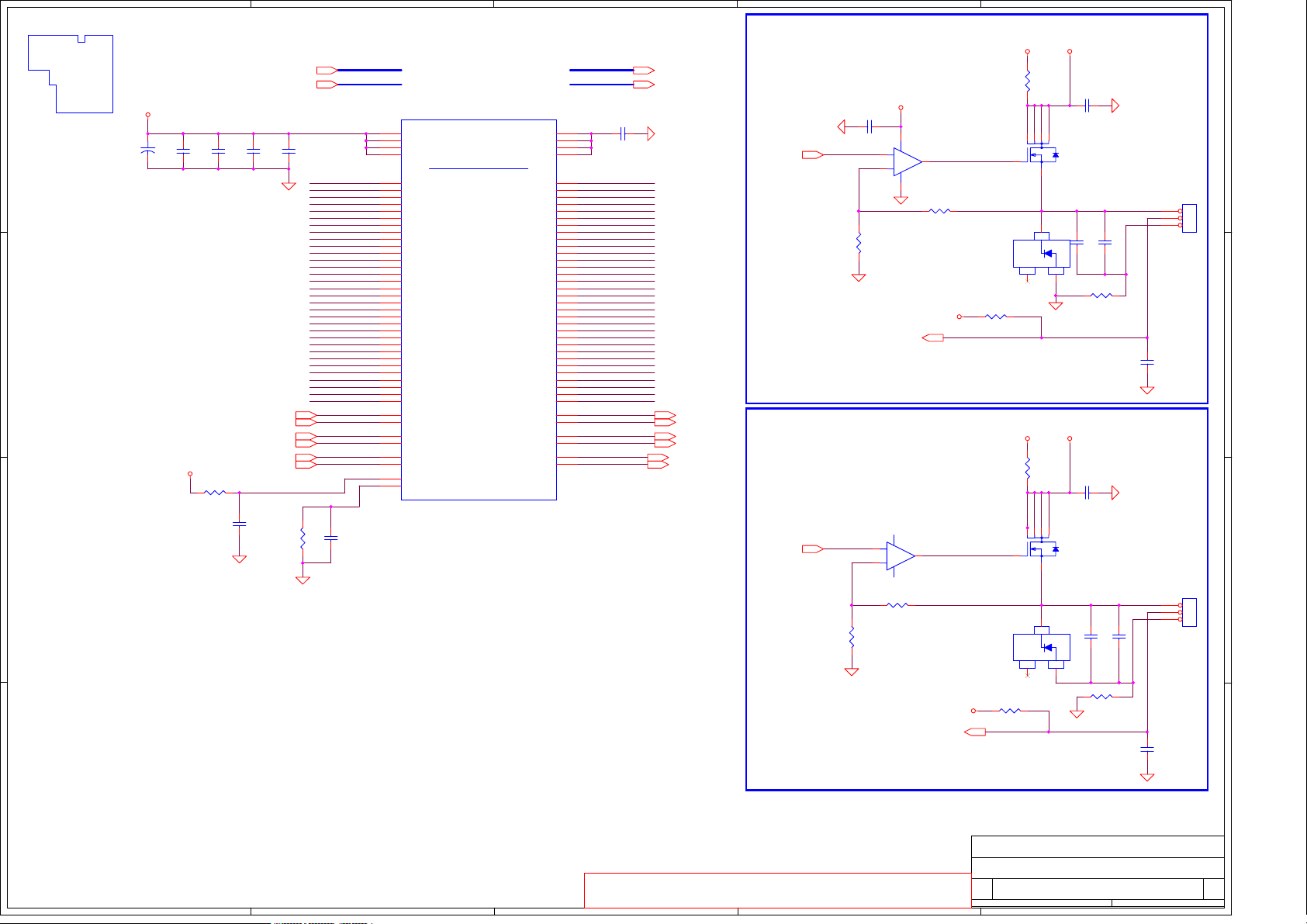

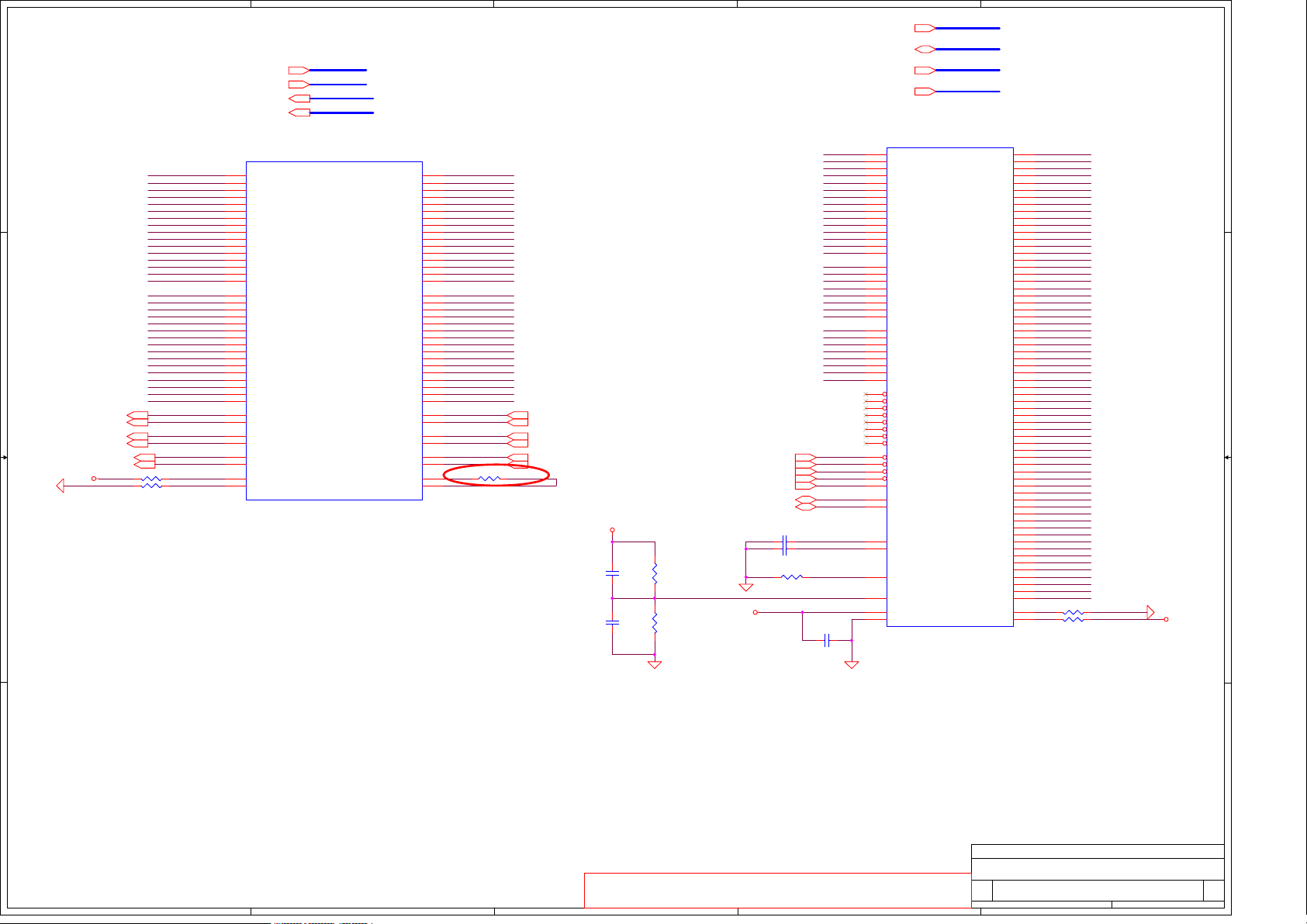

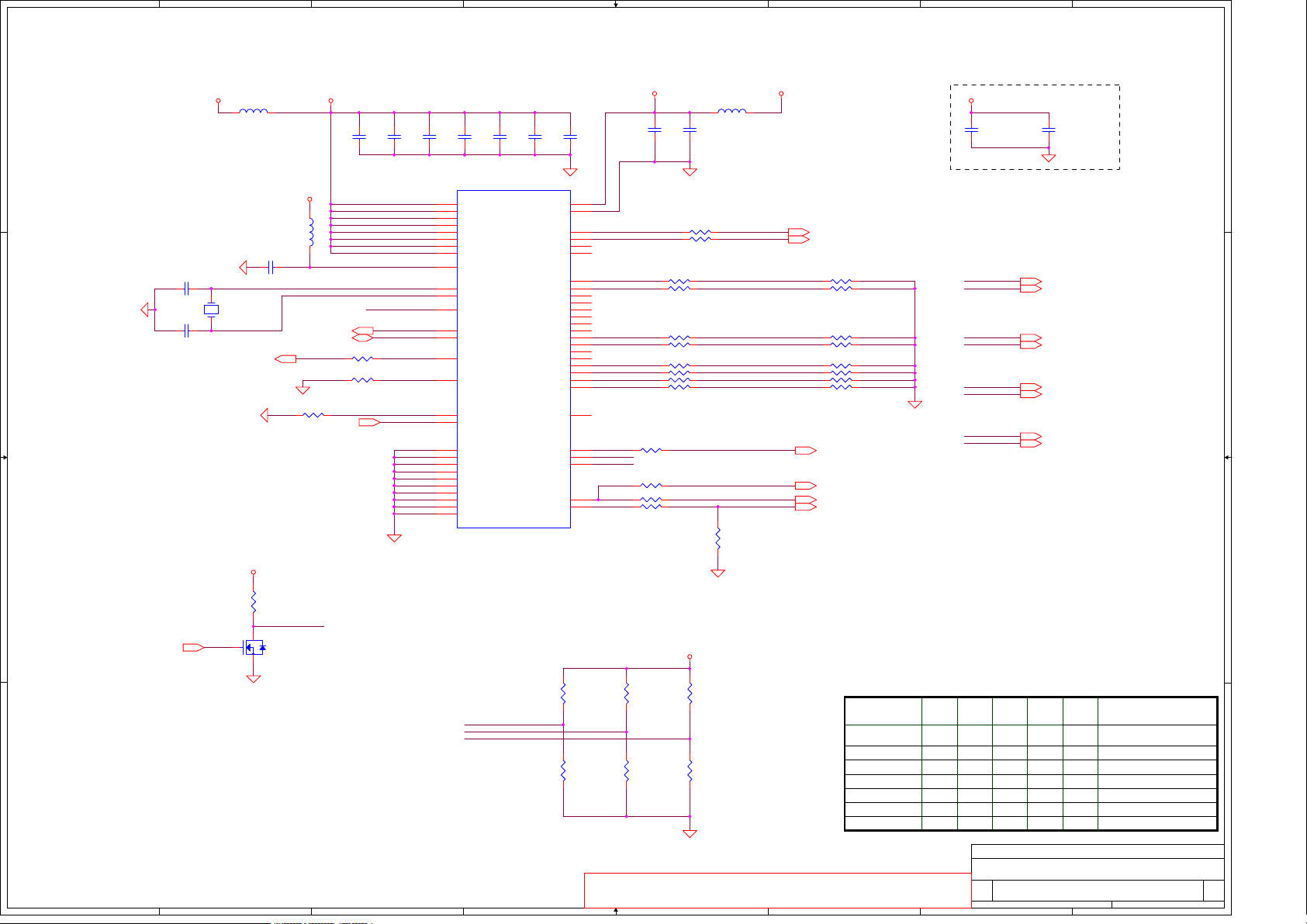

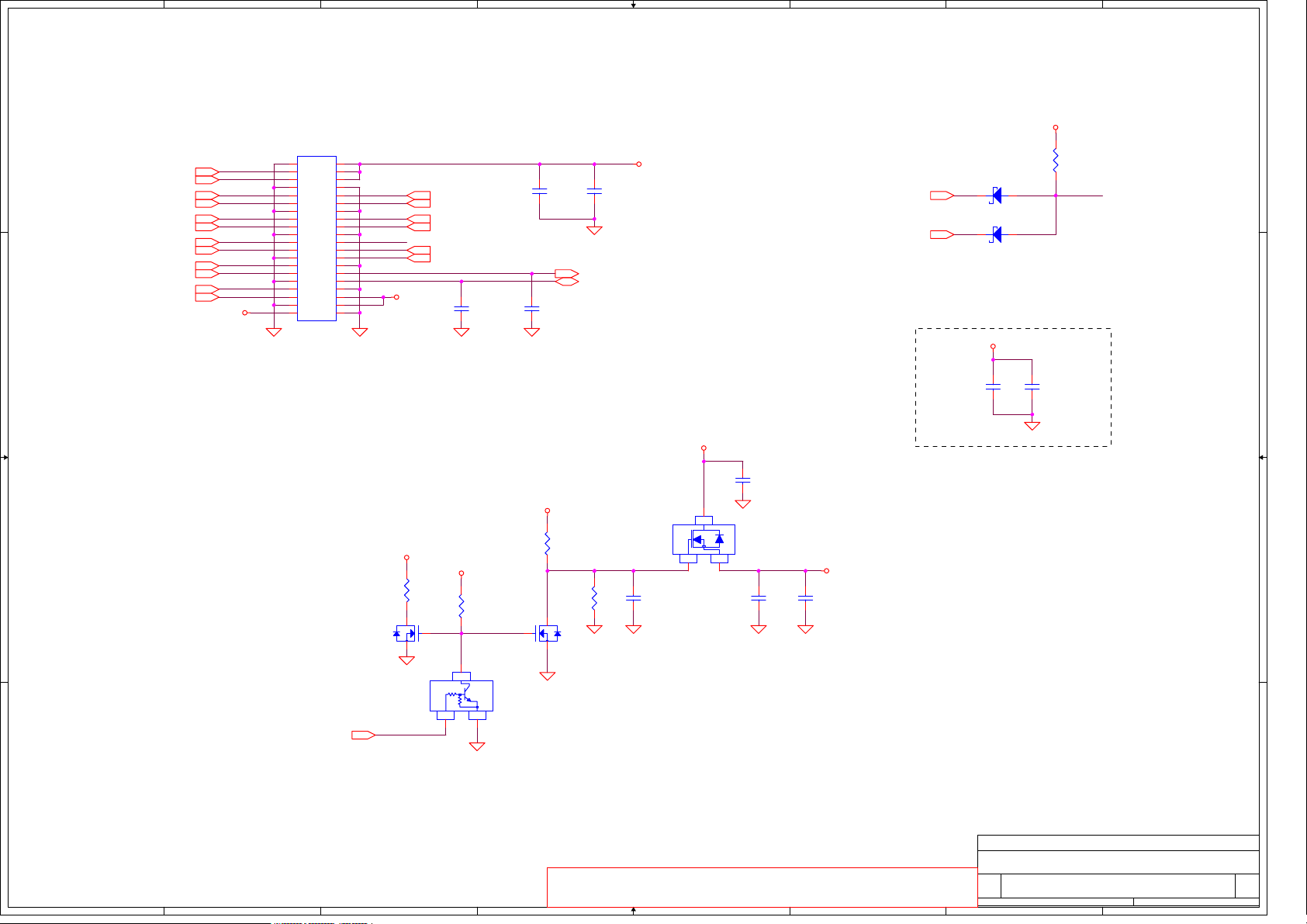

Fan Control Circuit 1

LA-2421 REV 0

4 4

3 3

2 2

+1.2V_HT

0.22U_0603_10V7K

1

+

2

100U_6.3V_M

C18

+1.2V_HT

1000P_0402_50V7K

1

C9

2

0.22U_0603_10V7K

R23 44.2_0603_1%

0.22U_0603_10V7K

1

1

C10

2

2

12

1

C22

2

H_CADIP[0..15]<11>

1

C14

C11

2

0.22U_0603_10V7K

H_CLKIP1<11>

H_CLKIN1<11>

H_CLKIP0<11>

H_CLKIN0<11>

H_CTLIP0<11>

H_CTLIN0<11>

LVREF1

R25

44.2_0603_1%

H_CADIP[0..15]

H_CADIN[0..15]

250 mil/20 mil 150 mil

H_CADIP15

H_CADIN15

H_CADIP14

H_CADIN14

H_CADIP13

H_CADIN13

H_CADIP12

H_CADIN12

H_CADIP11

H_CADIN11

H_CADIP10

H_CADIN10

H_CADIP9

H_CADIP8

H_CADIN8

H_CADIP7

H_CADIN7

H_CADIP6

H_CADIN6

H_CADIP5

H_CADIN5

H_CADIP4

H_CADIN4

H_CADIP3

H_CADIN3

H_CADIP2

H_CADIN2

H_CADIP1

H_CADIN1

H_CADIP0

H_CADIN0

H_CLKIP1

H_CLKIN1

H_CLKIP0

H_CLKIN0

H_CTLIP0

H_CTLIN0

LVREF0

12

1

C23

1000P_0402_50V7K

2

U22A

E2

VLDT

E1

VLDT

F1

VLDT

F2

VLDT

R5

L0_CADIN_H15

T5

L0_CADIN_L15

P3

L0_CADIN_H14

P4

L0_CADIN_L14

N5

L0_CADIN_H13

P5

L0_CADIN_L13

M3

L0_CADIN_H12

M4

L0_CADIN_L12

K3

L0_CADIN_H11

K4

L0_CADIN_L11

J5

L0_CADIN_H10

K5

L0_CADIN_L10

H3

L0_CADIN_H9

H4

L0_CADIN_L9

G5

L0_CADIN_H8

H5

L0_CADIN_L8

R3

L0_CADIN_H7

R2

L0_CADIN_L7

N1

L0_CADIN_H6

P1

L0_CADIN_L6

N3

L0_CADIN_H5

N2

L0_CADIN_L5

L1

L0_CADIN_H4

M1

L0_CADIN_L4

J1

L0_CADIN_H3

K1

L0_CADIN_L3

J3

L0_CADIN_H2

J2

L0_CADIN_L2

G1

L0_CADIN_H1

H1

L0_CADIN_L1

G3

L0_CADIN_H0

G2

L0_CADIN_L0

L5

L0_CLKIN_H1

M5

L0_CLKIN_L1

L3

L0_CLKIN_H0

L2

L0_CLKIN_L0

R1

L0_CTLIN_H0

T1

L0_CTLIN_L0

D1

L0_REF1

C1

L0_REF0

FOX_PZ93903-3146-03

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

HT Interface

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

VLDT

VLDT

VLDT

VLDT

H_CADOP[0..15]

H_CADON[0..15]

AG4

AG3

AG1

AG2

V4

V3

Y5

W5

Y4

Y3

AB5

AA5

AD5

AC5

AD4

AD3

AF5

AE5

AF4

AF3

V1

U1

W2

W3

Y1

W1

AA2

AA3

AC2

AC3

AD1

AC1

AE2

AE3

AF1

AE1

AB4

AB3

AB1

AA1

U2

U3

C17

1 2

4.7U_0805_6.3V6K

H_CADOP15

H_CADON15

H_CADOP14

H_CADON14

H_CADOP13

H_CADON13

H_CADOP12

H_CADON12

H_CADOP11

H_CADON11

H_CADOP10

H_CADON10

H_CADOP9

H_CADON9H_CADIN9

H_CADOP8

H_CADON8

H_CADOP7

H_CADON7

H_CADOP6

H_CADON6

H_CADOP5

H_CADON5

H_CADOP4

H_CADON4

H_CADOP3

H_CADON3

H_CADOP2

H_CADON2

H_CADOP1

H_CADON1

H_CADOP0

H_CADON0

H_CLKOP1

H_CLKON1

H_CLKOP0

H_CLKON0

H_CTLOP0

H_CTLON0

H_CADOP[0..15] <11>

H_CADON[0..15] <11>H_CADIN[0..15]<11>

H_CLKOP1 <11>

H_CLKON1 <11>

H_CLKOP0 <11>

H_CLKON0 <11>

H_CTLOP0 <11>

H_CTLON0 <11>

+12VALW

C614

12

3

2

12

R432

150K_0402_5%

FAN_SPEED1<37,38>

+IN

-IN

8

P

OUT

U37A

G

LM358A_SO8

4

R433

1

1 2

+3VS

FAN1_ON

100K_0402_5%

0.1U_0402_16V4Z

EN_FAN1<37,38>

Fan Control Circuit 2

U37B

12

R137

5

+IN

OUT

6

-IN

1 2

R139 100K_0402_5%FAN2@

150K_0402_5%FAN2@

FAN2_ON

7

LM358A_SO8

+3VS

FAN_SPEED2<37,38>

EN_FAN2<37,38>

1N4148_SOT23

1N4148_SOT23FAN2@

D29

R437

1 2

10K_0402_5%

D17

R138

1 2

10K_0402_5%

+5VS +12VS_FAN

12

R150

0_0805_5%

6

2

1

D

G

3

S

4 5

1

3

2

+12VS_FAN+5VS

12

R147

0_0805_5%FAN2@

6

2

1

D

G

3

S

4 5

1

3

2

C251

1 2

10U_1206_16V4Z

Q14

SI3456DV-T1_TSOP6

FAN1

1

1

C68

10U_0805_10V4Z

2

2

C61

1000P_0402_50V7K

R1151

1 2

0_0603_5%

1000P_0402_50V7K

C269

1 2

10U_1206_16V4ZFAN2@

Q16

FAN2@

SI3456DV-T1_TSOP6

FAN2

1

2

C268

10U_0805_10V4Z FAN2@

R1152

1 2

0_0603_5% FAN2@

1000P_0402_50V7K

C618

1

C241

1000P_0402_50V7K FAN2@

2

C240

FAN2@

JP24

1

2

3

ACES_85205-0300

1

2

JP29

1

2

3

ACES_85205-0300

1

2

1 1

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Claw Harmmer CPU (Host Bus)

Size Document Number Rev

Custom

LA-2421

Date: Sheet

E

of

456Wednesday, January 05, 2005

0.6

A

B

C

D

E

DDR_SDQ[0..63]<8,9>

+1.25V +1.25V

1 1

4.7U_0805_6.3V6K

DDR_CLK_1L_H2<8>

DDR_CLK_1L_L2<8>

DDR_CLK_1L_H1<8>

DDR_CLK_1L_L1<8>

DDR_SMAA[0..13]<8,9>

2 2

3 3

15_0402_1%

15_0402_1%

0.22U_0603_10V7K

1

C496

2

DDR_CKEB<9>

DDR_CKEA<8>

DDRA_SCS#1<8>

DDRA_SCS#0<8>

DDR_BSA1<8,9>

DDR_BSA0<8,9>

DDR_RASA_L<8,9>

DDR_CASA_L<8,9>

DDR_WEA_L<8,9>

R46 34.8_0603_1%

R47 34.8_0603_1%

+2.5V

R286

R290

+1.25VREF_CPU

+2.5V

12

12

0.1U_0402_16V4Z

250 mil width

1

1

C505

C498

2

2

0.22U_0603_10V7K

DDR_CLK_1L_H2

DDR_CLK_1L_L2

DDR_CLK_1L_H1

DDR_CLK_1L_L1

DDR_CKEB

DDR_CKEA

DDR_SMAA13

DDR_SMAA12

DDR_SMAA11

DDR_SMAA10

DDR_SMAA9

DDR_SMAA8

DDR_SMAA7

DDR_SMAA6

DDR_SMAA5

DDR_SMAA4

DDR_SMAA3

DDR_SMAA2

DDR_SMAA1

DDR_SMAA0

DDRA_SCS#1

DDRA_SCS#0

12

12

15 mil width/20 mil space

+1.25VREF_CPU

1

1

C506

2

2

MEMZP

MEMZN

C502

1000P_0402_50V7K

AG14

AK14

AJ14

AH14

AL14

AL22

AL23

AH23

AG23

AF23

AL29

AJ29

AG28

AF29

W25

AC27

AD27

AF27

AE28

AE15

AF15

A22

A23

R31

R30

D23

E23

R27

R26

E25

G24

C26

E28

V27

F29

H25

G28

J26

J25

L27

L28

N26

P25

U25

F15

U22B

VTT

VTT

VTT

VTT

VTT

MEMCLK_1H_H2

MEMCLK_1H_L2

MEMCLK_1H_H1

MEMCLK_1H_L1

MEMCLK_1H_H0

MEMCLK_1H_L0

MEMCLK_1L_H2

MEMCLK_1L_L2

MEMCLK_1L_H1

MEMCLK_1L_L1

MEMCLK_1L_H0

MEMCLK_1L_L0

MEMCKEB

MEMCKEA

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMCS_1H_L1

MEMCS_1H_L0

MEMCS_1L_L1

MEMCS_1L_L0

MEMBANKA1

MEMBANKA0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMZP

MEMZN

MEMVREF

FOX_PZ93903-3146-03

A Channel

DDR_CLK_1L_L2

DDR_CLK_1L_L1

DDR_CLK_2L_L2

DDR_CLK_2L_L1

VTT

VTT

VTT

VTT

VTT

MEMCLK_2H_H2

MEMCLK_2H_L2

MEMCLK_2H_H1

MEMCLK_2H_L1

MEMCLK_2H_H0

MEMCLK_2H_L0

MEMCLK_2L_H2

MEMCLK_2L_L2

MEMCLK_2L_H1

MEMCLK_2L_L1

MEMCLK_2L_H0

MEMCLK_2L_L0

MEMCKED

MEMCKEC

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

B Channel

MEMADDB2

MEMADDB1

MEMADDB0

MEMCS_2H_L1

MEMCS_2H_L0

MEMCS_2L_L1

MEMCS_2L_L0

MEMBANKB1

MEMBANKB0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMRESET_L

1 2

R68 120_0402_5%

1 2

R66 120_0402_5%

1 2

R332 120_0402_5%

1 2

R333 120_0402_5%

E14

D14

C14

B14

A14

AJ21

AH21

C21

D21

T31

U31

DDR_CLK_2L_H2

AF21

DDR_CLK_2L_L2

AE21

DDR_CLK_2L_H1

G21

DDR_CLK_2L_L1

G22

T27

U27

C25

B25

AK23

A26

A29

W30

C29

E29

D31

G29

F31

J31

K31

N28

N30

U29

AL28

AJ30

AG27

AE26

Y31

AE30

AG30

AK29

AH31

D19

DDR_CLK_1L_H2

DDR_CLK_1L_H1

DDR_CLK_2L_H2

DDR_CLK_2L_H1

0.22U_0603_10V7K

DDRB_SCS#1

DDRB_SCS#0

1

2

C495

1

C493

4.7U_0805_6.3V6K

2

DDR_CLK_2L_H2 <9>

DDR_CLK_2L_L2 <9>

DDR_CLK_2L_H1 <9>

DDR_CLK_2L_L1 <9>

DDRB_SCS#1 <9>

DDRB_SCS#0 <9>

DDR_SDM_L[0..7]<8,9>

DDR_SDQS_L[0..7]<8,9>

DDR_SDQ63

DDR_SDQ62

DDR_SDQ61

DDR_SDQ60

DDR_SDQ59

DDR_SDQ58

DDR_SDQ57

DDR_SDQ56

DDR_SDQ55

DDR_SDQ54

DDR_SDQ53

DDR_SDQ52

DDR_SDQ51

DDR_SDQ50

DDR_SDQ49

DDR_SDQ48

DDR_SDQ47

DDR_SDQ46

DDR_SDQ45

DDR_SDQ44

DDR_SDQ43

DDR_SDQ42

DDR_SDQ41

DDR_SDQ40

DDR_SDQ39

DDR_SDQ38

DDR_SDQ37

DDR_SDQ36

DDR_SDQ35

DDR_SDQ34

DDR_SDQ33

DDR_SDQ32

DDR_SDQ31

DDR_SDQ30

DDR_SDQ29

DDR_SDQ28

DDR_SDQ27

DDR_SDQ26

DDR_SDQ25

DDR_SDQ24

DDR_SDQ23

DDR_SDQ22

DDR_SDQ21

DDR_SDQ20

DDR_SDQ19

DDR_SDQ18

DDR_SDQ17

DDR_SDQ16

DDR_SDQ15

DDR_SDQ14

DDR_SDQ13

DDR_SDQ12

DDR_SDQ11

DDR_SDQ10

DDR_SDQ9

DDR_SDQ8

DDR_SDQ7

DDR_SDQ6

DDR_SDQ5

DDR_SDQ4

DDR_SDQ3

DDR_SDQ2

DDR_SDQ1

DDR_SDQ0

DDR_SDM_L7

DDR_SDM_L6

DDR_SDM_L5

DDR_SDM_L4

DDR_SDM_L3

DDR_SDM_L2

DDR_SDM_L1

DDR_SDM_L0

DDR_SDQS_L7

DDR_SDQS_L6

DDR_SDQS_L5

DDR_SDQS_L4

DDR_SDQS_L3

DDR_SDQS_L2

DDR_SDQS_L1

DDR_SDQS_L0

U22C

AE16

AG17

AG18

AE18

AJ16

AG16

AE17

AJ18

AJ20

AE20

AE23

AG24

AG19

AE19

AJ24

AE24

AG25

AE25

AD25

AC25

AF25

AJ26

AE27

AD29

AB25

AB27

AA28

Y25

AC26

AB29

AA27

Y27

N25

M25

K27

K25

M29

M27

K29

J27

H27

G27

D27

F25

H29

G26

E26

G25

G23

F23

C20

F19

E24

C24

G19

E19

E18

G17

E16

E15

G18

C18

G16

C16

Y29

W27

P27

R25

W26

V25

R28

P29

V29

AF17

AG21

AH27

AA25

L26

F27

G20

E17

U26

AH17

AG20

AG26

AA26

L25

E27

E20

F17

FOX_PZ93903-3146-03

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

MEMDM_LO8

MEMDM_LO7

MEMDM_LO6

MEMDM_LO5

MEMDM_LO4

MEMDM_LO3

MEMDM_LO2

MEMDM_LO1

MEMDM_LO0

MEMDQS_LO8

MEMDQS_LO7

MEMDQS_LO6

MEMDQS_LO5

MEMDQS_LO4

MEMDQS_LO3

MEMDQS_LO2

MEMDQS_LO1

MEMDQS_LO0

MEMDATA127

MEMDATA126

MEMDATA125

MEMDATA124

MEMDATA123

MEMDATA122

MEMDATA121

MEMDATA120

MEMDATA119

MEMDATA118

MEMDATA117

MEMDATA116

MEMDATA115

MEMDATA114

MEMDATA113

MEMDATA112

MEMDATA111

MEMDATA110

MEMDATA109

MEMDATA108

MEMDATA107

MEMDATA106

MEMDATA105

MEMDATA104

MEMDATA103

MEMDATA102

MEMDATA101

MEMDATA100

MEMDATA99

MEMDATA98

MEMDATA97

MEMDATA96

MEMDATA95

MEMDATA94

MEMDATA93

MEMDATA92

MEMDATA91

MEMDATA90

MEMDATA89

MEMDATA88

MEMDATA87

MEMDATA86

MEMDATA85

MEMDATA84

MEMDATA83

MEMDATA82

MEMDATA81

MEMDATA80

MEMDATA79

MEMDATA78

MEMDATA77

A Channel

MEMDATA76

B Channel

MEMDATA75

MEMDATA74

MEMDATA73

MEMDATA72

MEMDATA71

MEMDATA70

MEMDATA69

MEMDATA68

MEMDATA67

MEMDATA66

MEMDATA65

MEMDATA64

MEMCHECK15

MEMCHECK14

MEMCHECK13

MEMCHECK12

MEMCHECK11

MEMCHECK10

MEMCHECK9

MEMCHECK8

MEMDM_UP8

MEMDM_UP7

MEMDM_UP6

MEMDM_UP5

MEMDM_UP4

MEMDM_UP3

MEMDM_UP2

MEMDM_UP1

MEMDM_UP0

MEMDQS_UP8

MEMDQS_UP7

MEMDQS_UP6

MEMDQS_UP5

MEMDQS_UP4

MEMDQS_UP3

MEMDQS_UP2

MEMDQS_UP1

MEMDQS_UP0

AJ15

AL16

AL18

AL19

AL15

AK15

AK17

AJ17

AH19

AL21

AJ23

AL25

AK19

AJ19

AL24

AK25

AJ25

AL26

AG29

AF31

AH25

AL27

AJ31

AG31

AE31

AD31

AB31

AA29

AE29

AC28

AC31

AA30

M31

L30

H31

G31

L31

L29

J28

G30

E30

C31

C27

D25

E31

C30

B27

A27

C23

B23

A20

B19

A25

A24

C19

A19

D17

B17

C15

A15

A18

C17

D15

B15

AA31

W29

N31

N29

W28

W31

R29

P31

V31

AL17

AK21

AK27

AC29

J30

B29

B21

A16

U30

AH15

AL20

AJ27

AC30

J29

A28

A21

A17

4 4

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Claw Harmmer (MEMORY BUS)

Size Document Number Rev

Custom

LA-2421

Date: Sheet

E

of

556Wednesday, January 05, 2005

0.6

A

B

C

D

E

L2

+2.5VDDA

1 1

2 2

3 3

LQG21F4R7N00_0805

1 2

1

+

C28

100U_6.3V_M

2

Place 169 Ohm within 0.5" from CPU

Route as DIF 5/5/5/20

CPUCLK0_H<16>

CPUCLK0_L< 16>

+2.5VS

R259 680_0402_5%

R35 680_0402_5%

R34 680_0402_5%

H_RST#<19>

@

100_0402_5%

4.7U_0805_6.3V6K

LDTSTOP#

12

H_RST#

12

H_PWRGD

12

R31

1 2

0_0402_5%

H_RST#

R38

J1

JOPEN

1

C483

2

C484

3900P_0402_50V7K

C482 3900P_0402_50V7K

12

1 2

3300P_0402_50V7K

1

C478

2

0.22U_0603_10V7K

Route as DIFF pair 10/5/10

12

12

R267

169_0402_1%

12

H_RST_CPU#

1

C27

0.001U_0402_50V7M

2

@

50 mil/20 mil

+VDDA

1

C477

H_PWRGD<19>

2

LDTSTOP#<13,19> EC_SMC_2<37,38>

CPU_COREFB<50>

CPU_COREFB#<50>

Place within 0.5" from CPU

Route as 80 Ohm DIFF impedence 8/5/20

H_RST_CPU#

H_PWRGD

LDTSTOP#

CPU_COREFB

CPU_COREFB#

VDDIO_SENSE

CLKIN

DBRDY

TMS

TCK

TRST#

TDI

TDO

U22D

C3

B3

A3

F8

E8

B6

E5

E6

E7

Y24

AA24

AE13

A8

B8

B11

AG6

AG7

AF8

AJ9

AG8

A4

D4

B4

C4

C7

C6

AL8

AL7

V5

U5

C13

E9

C5

A5

AE22

AG22

AH8

AH29

AJ4

AJ5

AJ6

AJ7

AJ8

AJ22

AJ28

AK3

AK4

AK6

AK8

AK10

AK12

AL3

AL4

AL5

AL6

FOX_PZ93903-3146-03

VDDA3

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

COREFB_H

COREFB_L

CORESENSE

Miscellaneous

VDDIOFB_H

VDDIOFB_L

VDDIOSENSE

CLKIN_H

Clock

CLKIN_L

Debug

DBRDY

TMS

TCK

JTAG

TRST_L

TDI

TDO

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

VTT_SENSE

FBCLKOUT_H

FBCLKOUT_L

DBREQ_L

STRAP_HI

STRAP_HI

STRAP_HI

STRAP_HI

STRAP_LO

STRAP_LO

STRAP_LO

STRAP_LO

STRAP_LO

STRAP_LO

STRAP_LO

STRAP_LO

STRAP_LO

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

H_THERMTRIP_S#

AG10

AJ2

AJ1

A13

A12

C12

A11

A10

AF13

F13

E13

A6

AJ12

AF12

T3

E11

AG9

AH6

AF10

AH10

AJ10

B13

C10

T4

F11

AL9

AL10

AL11

AL12

C22

C28

D8

D11

D12

D29

E21

E22

G15

N27

T25

T29

U28

C11

AG15

AH12

THERMDA_CPU

THERMDC_CPU

VID4

VID3

VID2

VID1

VID0

VTT_SENSE

FBCLKOUT

FBCLKOUT#CLKIN#

DBREQ#

STRAP_HI_AJ12

STRAP_HI_AF12

STRAP_HI_T3

STRAP_HI_E11

STRAP_LO_AG9

STRAP_LO_AH6

STRAP_LO_AF10

STRAP_LO_AH10

STRAP_LO_AJ10

STRAP_LO_B13

STRAP_LO_C10

STRAP_LO_T4

STRAP_LO_F11

VID4 <50>

VID3 <50>

VID2 <50>

VID1 <50>

VID0 <50>

1 2

R4580.6_0402_1%

R265 680_0402_5%

1 2

R263 680_0402_5%

1 2

R18 49.9_0402_1%

1 2

R42 820_0402_5%

1 2

R255 680_0402_5%

1 2

R253 680_0402_5%

1 2

R258 680_0402_5%

1 2

R264 680_0402_5%

1 2

R266 680_0402_5%

1 2

R43 680_0402_5%

1 2

R39 680_0402_5%

1 2

R19 49.9_0402_1%

1 2

R40 820_0402_5%

1 2

+2.5VS

+1.2V_HT

+2.5V

EC_SMD_2<37,38>

H_THERMTRIP_S# H_THERMTRIP#

1U_0603_10V4Z

Thermal Sensor

ADM1032

U19

8

7

6

5

+2.5VS

12

R254

680_0402_5%

+3VS +2.5VDDA

1

C33

2

VDDA_EN<37,38>

SCLK

SDATA

ALERT#

THERM#

GND

ADM1032AR_SOP8

+2.5VS

12

R257

1K_0402_5%

2

Q27

3 1

MMBT3904_SOT23

U2

1

2

3

SI9183_SOT23-5

VDD

D+

D-

VIN

GND

SD#

1

THERMDA_CPU

2

THERMDC_CPU

3

4

+3VALW

VOUT

BP

W=15mil

R247 10K_0402_5%@

12

R252

10K_0402_5%

5

4

1 2

1

C40

0.01U_0402_16V7K

2

H_THERMTRIP# <20>

1

C472

2200P_0402_50V7K

2

+3VS

2

C474

0.1U_0402_16V4Z

1

+2.5VS

R11

R12

R13

12

12

12

560_0402_5%@

560_0402_5%@

560_0402_5%@

DBREQ#

DBRDY

TCK

TMS

TDI

TRST#

TDO

4 4

A

R8

R9

R10

12

560_0402_5%@

R7

12

12

12

560_0402_5%@

560_0402_5%@

+2.5VS

560_0402_5%@

JP1

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC_ASP-68200-07

@

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

ClawHarmmer ( MISC )

Size Document Number Rev

Custom

LA-2421

Date: Sheet

E

of

656Wednesday, January 05, 2005

0.6

A

B

C

D

E

+CPU_CORE

U22E

AA4

VDD1

AA7

VDD2

AA9

VDD3

W24

W22

W20

W18

W16

W14

W12

W10

V28

V26

V23

V21

V19

V17

V15

V13

V11

U24

U22

U20

U18

U16

U14

U12

U10

VSS233

VSS128H7VSS129H9VSS130

T28

T26

VSS225

T23

VSS232

VSS224

VSS231

VSS230

VSS229

VSS228U8VSS227U6VSS226

VSS135

VSS134

VSS133

H11

H21

H19

H17

H15

T21

VSS223

T19

VSS222

T17

VSS221

T15

VSS220

T13

VSS219

T11

VSS218

T9

VSS217

T7

VSS216

R24

VSS215

R22

VSS214

R20

VSS213

R18

VSS212

R16

VSS211

R14

VSS210

R12

VSS209

R10

VSS208

R8

VSS207

R6

VSS206

R4

VSS205

P28

VSS204

P26

VSS203

P23

VSS202

P21

VSS201

P19

VSS200

P17

VSS199

P15

VSS198

P13

VSS197

P11

VSS196

P9

VSS195

P7

VSS194

P2

VSS193

N24

VSS192

N22

VSS191

N20

VSS190

N18

VSS189

N16

VSS188

N14

VSS187

N12

VSS186

N10

VSS185

N8

VSS184

N6

VSS183

M28

VSS182

M26

VSS181

M23

VSS180

M21

VSS179

M19

VSS178

M17

VSS177

M15

VSS176

M13

VSS175

M11

VSS174

M9

VSS173

M7

VSS172

L24

VSS171

L22

VSS170

L20

VSS169

L18

VSS168

L16

VSS167

L14

VSS166

L12

VSS165

L10

VSS164

L8

VSS163

L6

VSS162

L4

VSS161

K28

VSS160

K26

VSS159

K23

VSS158

K21

VSS157

K19

VSS156

K17

VSS155

K15

VSS154

K13

VSS153

K11

VSS152

K9

VSS151

K7

VSS150

K2

VSS149

J24

VSS148

J22

VSS147

J20

VSS146

J18

VSS145

J16

VSS144

J14

VSS143

J12

VSS142

J10

VSS141

J8

VSS140

J6

VSS139

H28

VSS138

H26

VSS137

H23

VSS136

VSS132

VSS131

H13

Y28

U22F

A7

VSS1

A9

VSS2

VSS268

VSS269

1 1

2 2

3 3

4 4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB2

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AB28

AC4

AC6

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD21

AD23

AD26

AD28

AE6

AE8

AE10

AE12

AE14

AF2

AF6

AF7

AF9

AF11

AF14

AF16

AF20

AF22

AF24

AF26

AF28

AG5

AG11

AG13

AG12

AH1

AH2

AH3

AH4

AH5

AH7

AH9

AH11

AH13

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AJ3

AJ13

AK13

AL13

FOX_PZ93903-3146-03

VSS270

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

B7

VSS86

B9

VSS87

C2

VSS88

C8

VSS89

C9

VSS90

VSS91D2VSS92D3VSS93D5VSS94D6VSS95D7VSS96D9VSS97

Y7

VSS259

VSS258

VSS257

VSS256

VSS255

VSS254

VSS253

VSS252

VSS251W8VSS250W6VSS249W4VSS248

VSS247

VSS246

VSS245

VSS244

VSS243

VSS242

VSS241

VSS240

VSS239V9VSS238V7VSS237V2VSS236

VSS235

VSS261Y9VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS260

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105E3VSS106E4VSS107

VSS108

VSS109

VSS110F5VSS111F6VSS112F7VSS113F9VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

F10

F12

F14

F16

F18

F22

E10

D13

D16

D18

D20

D22

E12

D24

D26

D28

G12

F24

VSS234

VSS121

VSS122

VSS123G4VSS124G6VSS125G8VSS126

VSS127

F26

F28

G10

G14

Y11

Y13

Y15

Y17

Y19

Y21

Y23

Y26

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AC9

AC11

AC13

AC15

AC17

AC19

AD2

AD6

AD8

AD10

AD12

AD14

AD16

AD18

AE4

AE7

AE9

AE11

AJ11

AK5

AK7

AK9

AK11

B5

B10

B12

D10

G7

G9

G11

G13

H2

H6

H8

H10

H12

H14

H16

H18

J4

J7

J9

J11

J13

J15

J17

J19

K6

K8

K10

K12

K14

K16

K18

K20

L7

L9

L11

L13

L15

L17

L19

L21

M2

M6

M8

M10

M12

M14

M16

M18

M20

N4

N7

N9

N11

N13

N15

N17

N19

N21

P6

P8

P10

P12

P14

P16

P18

P20

R7

R9

FOX_PZ93903-3146-03

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD95

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD134

VDD135

VDD136

VDD137

VDD138

VDD139

VDD140

VDD141

VDD142

VDD143

VDD144

VDD145

VDD146

VDD147

VDD148

VDD149

VDD150

VDD151

VDD152

VDD153

VDD154

VDD155

VDD156

VDD157

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO51

VDDIO52

VDDIO53

VDDIO54

VDDIO55

VDDIO56

VDDIO57

VDDIO58

R11

R13

R15

R17

R19

R21

T2

T6

T8

T10

T12

T14

T16

T18

T20

U4

U7

U9

U11

U13

U15

U17

U19

U21

V6

V8

V10

V12

V14

V16

V18

V20

W7

W9

W11

W13

W15

W17

W19

W21

Y2

Y6

Y8

Y10

Y12

Y14

Y16

Y18

Y20

AA23

AB22

AB24

AB30

AC21

AC23

AD20

AD22

AD24

AD30

AF30

AH30

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

B16

B18

B20

B22

B24

B26

B28

B30

D30

F30

H20

H22

H24

H30

J21

J23

K22

K24

K30

L23

M22

M24

M30

N23

P22

P24

P30

R23

T22

T24

T30

U23

V22

V24

V30

W23

Y22

Y30

+CPU_CORE

+2.5V

+CPU_CORE

330U_D_2VM_R15@

1

1

+

+

C12

2

330U_D_2VM_R15@

+CPU_CORE

1

+

@

2

+CPU_CORE

1

C34

2

10U_0805_10V4Z

On backside under socket

+CPU_CORE

1

C37

2

0.22U_0603_10V7K

On backside under socket

+CPU_CORE

1

2

0.01U_0402_16V7K

4.7U_0805_6.3V6K

C13

2

C462

820U_E9_2_5V_M_R7

10U_0805_10V4Z

1

C35

2

10U_0805_10V4Z

0.22U_0603_10V7K

1

C38

2

0.22U_0603_10V7K

0.01U_0402_16V7K

1

C19

C5

2

0.01U_0402_16V7K

4.7U_0805_6.3V6K

1

C173

2

330U_D_2VM_R15@

1

2

1

2

1

2

1

C104

2

330U_D_2VM_R15

1

+

C15

2

1

+

C461

820U_E9_2_5V_M_R7

2

10U_0805_10V4Z

1

C36

C50

2

10U_0805_10V4Z

0.22U_0603_10V7K

1

C39

C47

2

0.22U_0603_10V7K

0.01U_0402_16V7K

1

C42

C30

2

+1.2V_HT

1

+

2

C16

330U_D_2VM_R15

10U_0805_10V4Z

1

C51

2

0.22U_0603_10V7K

1

C48

2

1

+

+

C530

C549

2

2

330U_D_2VM_R15@

1

+

C481

820U_E9_2_5V_M_R7

2

1

C52

2

1

C49

2

For EMI require

+CPU_CORE

1

C1183

2

1000P_0402_50V7K

1

+

C569

2

1

+

C480

820U_E9_2_5V_M_R7

@

2

+CPU_CORE

1

2

1000P_0402_50V7K

1

C1184

2

330U_D_2VM_R15

1

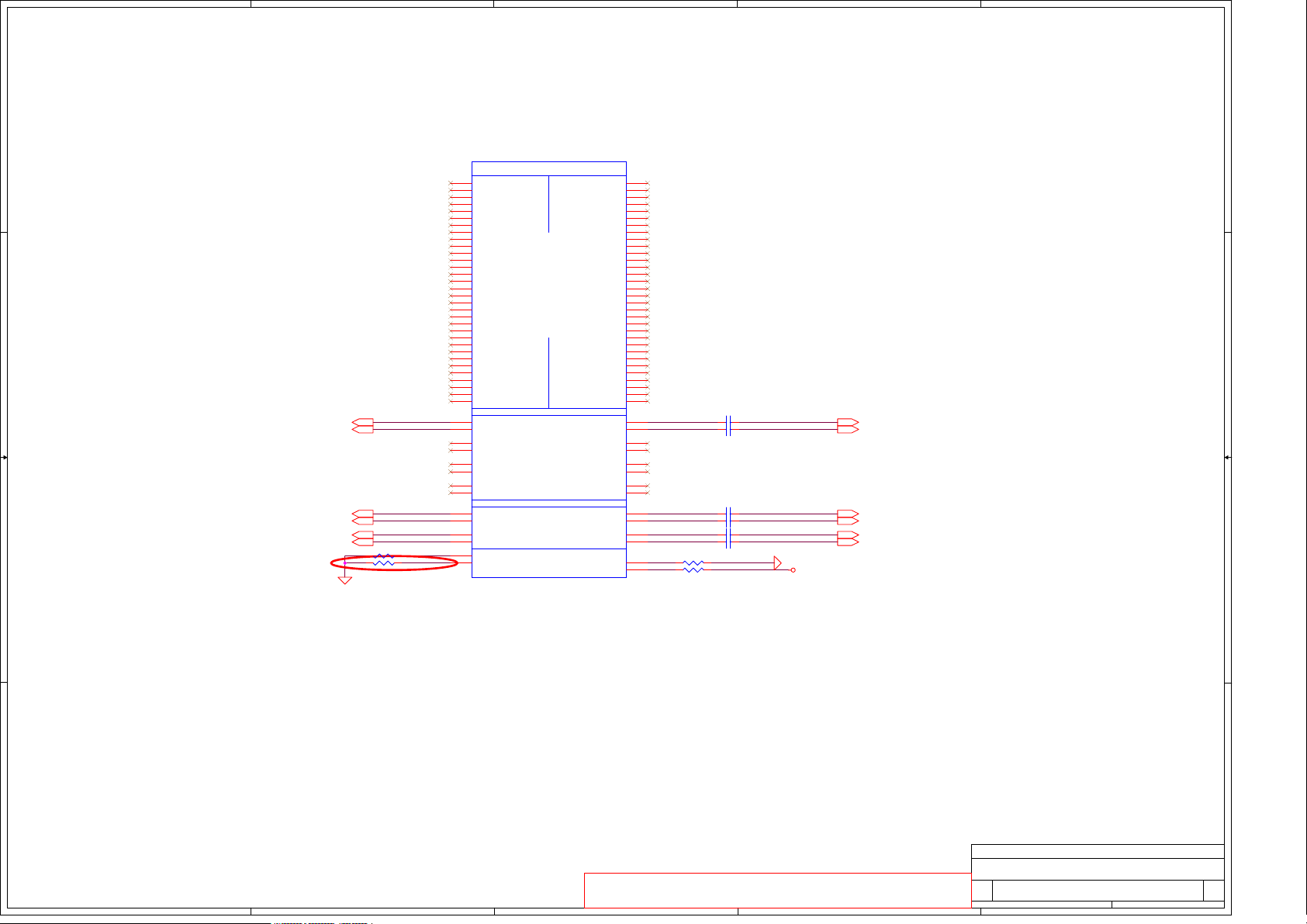

CPU Decouping Capacitor

Loop Bandwidth

KHz

Bulk Cappacitance

uF

2300020

900050

* 300

+2.5V+2.5V

0.22U_0603_10V7K

1

1

C142

2

2

0.22U_0603_10V7K

Near Socket

C141

1500

0.22U_0603_10V7K

1

C144

2

0.22U_0603_10V7K

1

2

330U_D_2VM_R15@

1

+

C568

2

330U_D_2VM_R15

C43

1000P_0402_50V7K

1

C1185

2

1000P_0402_50V7K

1

C55

C143

2

0.22U_0603_10V7K

1

+

C26

2

1

C41

0.1U_0402_16V4Z

2

1000P_0402_50V7K

1

C1186

2

Total

ESR

2.5m ohm

(AMD)

0.9m ohm

2.5m ohm

0.22U_0603_10V7K

1

C56

2

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Claw Harmme r ( Pow er & Gr ound)

Size Document Number Rev

Custom

LA-2421

Date: Sheet

E

of

756Wednesday, January 05, 2005

0.6

A

DDR_SDQ63

DDR_SDQ62

DDR_SDQ59

DDR_SDQ58

DDR_SDM_L7

A

DDR_SDQS_L7

DDR_SDQ61

DDR_SDQ60

DDR_SDQ57

DDR_SDQ56

DDR_SDQ55

DDR_SDQ51

DDR_SDQ50

DDR_SDM_L6

DDR_SDQS_L6

DDR_SDQ54

DDR_SDQ53

DDR_SDQ52

DDR_SDQ49

DDR_SDQ48

DDR_SDQ47

DDR_SDQ43

DDR_SDQ42

DDR_SDQ46

DDR_SDM_L5

DDR_SDQS_L5

DDR_SDQ45

DDR_SDQ44

DDR_SDQ41

DDR_SDQ40

DDR_SDQ39

DDR_SDQ38

DDR_SDQ35

DDR_SDQ34

DDR_SDM_L4

DDR_SDQS_L4

DDR_SDQ37

DDR_SDQ36

DDR_SDQ33

DDR_SDQ32

DDR_SDQ31

DDR_SDQ30

DDR_SDQ27

DDR_SDQ26

DDR_SDM_L3

DDR_SDQS_L3

DDR_SDQ29

DDR_SDQ28

DDR_SDQ25

DDR_SDQ24

DDR_SDQ23

DDR_SDQ22

1 1

2 2

3 3

4 4

DDR_SDQ[0..63]<5,9>

DDR_SDQS_L[0..7]<5,9>

DDR_SDM_L[0..7]<5,9>

DDR_SMAA[0..13]<5,9>

RP17

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP16

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP15

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP14

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP13

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP12

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP11

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP10

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP9

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP8

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP7

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP6

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP5

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

DDR_SDQ[0..63]

DDR_SDQS_L[0..7]

DDR_SDM_L[0..7]

DDR_SMAA[0..13]

+1.25V

B

B

RP25

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP26

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP27

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP28

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP30

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP29

1 4

2 3

47_0404_4P2R_5%

RP22

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP21

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP20

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP19

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP18

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP24

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP23

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

DDR_CKEA

DDR_SMAA11

DDR_SMAA12

DDR_SMAA8

DDR_SMAA9

DDR_SMAA6

DDR_SMAA4

DDR_SMAA7

DDR_SMAA5

DDR_SMAA2

DDR_SMAA0

DDR_SMAA3

DDR_SMAA1

DDR_BSA1

DDR_RASA_L

DDR_SMAA10

DDR_CASA_L

DDRA_SCS#1

DDRA_SCS#0

DDR_SMAA13

DDR_BSA0

DDR_WEA_L

DDR_SDQ10

DDR_SDQ11

DDR_SDQ14

DDR_SDQ15

DDR_SDQ12

DDR_SDQ13

DDR_SDM_L1

DDR_SDQS_L1

DDR_SDQ3

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ6

DDR_SDQS_L0

DDR_SDM_L0

DDR_SDQ2

DDR_SDQ0

DDR_SDQ1

DDR_SDQ4

DDR_SDQ5

DDR_SDQS_L2

DDR_SDM_L2

DDR_SDQ18

DDR_SDQ19

DDR_SDQ16

DDR_SDQ17

DDR_SDQ20

DDR_SDQ21

C

Note:

DDR_SMAA13 Recommend for AMD

C

D

DDR_SDQ0

DDR_SDQ1

DDR_SDQS_L0

DDR_SDQ2

DDR_SDQ3

DDR_SDQ8

DDR_SDQ9

DDR_SDQS_L1

DDR_SDQ10

DDR_SDQ11

DDR_CLK_1L_H1<5>

DDR_CLK_1L_L1<5>

DDR_SDQ16

DDR_SDQ17

DDR_SDQS_L2

DDR_SDQ18

DDR_SDQ19

DDR_SDQ24

DDR_SDQ25

DDR_SDQS_L3

DDR_SDQ26

DDR_SDQ27

DDR_CKEA<5>

DDR_BSA0<5,9>

DDR_WEA_L<5,9>

DDRA_SCS#0<5> DDRA_SCS#1 <5>

D

DDR_CKEA

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_BSA0

DDR_WEA_L

DDRA_SCS#0

DDR_SMAA13

DDR_SDQ32

DDR_SDQ33

DDR_SDQS_L4

DDR_SDQ34

DDR_SDQ35

DDR_SDQ40

DDR_SDQ41

DDR_SDQS_L5

DDR_SDQ42

DDR_SDQ43

DDR_SDQ48

DDR_SDQ49

DDR_SDQS_L6

DDR_SDQ50

DDR_SDQ51

DDR_SDQ56

DDR_SDQ57

DDR_SDQS_L7

DDR_SDQ58

DDR_SDQ59

SB_SDAT<9,16,20,26>

SB_SCLK<9,16,20,26>

+3VS

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+2.5V

E

JP11

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

AMP_1565917-1

SO-DIMM0

Top Side

E

VREF

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQ30

DQ31

DU/RESET#

CKE0

DU/BA2

RAS#

CAS#

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQ46

DQ47

CK1#

DQ52

DQ53

DQ54

DQ55

DQ60

DQ61

DQ62

DQ63

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

VDD

DM1

VSS

VDD

VDD

VSS

VSS

VDD

DM2

VSS

VDD

DM3

VSS

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

VSS

VDD

BA1

VSS

VDD

DM4

VSS

VDD

DM5

VSS

VDD

CK1

VSS

VDD

DM6

VSS

VDD

DM7

VSS

VDD

SA0

SA1

SA2

F

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

F

20mil

DDR_SDQ4

DDR_SDQ5

DDR_SDM_L0

DDR_SDQ6

DDR_SDQ7

DDR_SDQ12

DDR_SDQ13

DDR_SDM_L1

DDR_SDQ14

DDR_SDQ15

DDR_SDQ20

DDR_SDQ21

DDR_SDM_L2

DDR_SDQ22

DDR_SDQ23

DDR_SDQ28

DDR_SDQ29

DDR_SDM_L3

DDR_SDQ30

DDR_SDQ31

DDR_CKEA

DDR_SMAA11

DDR_SMAA8

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_BSA1

DDR_RASA_L

DDR_CASA_L

DDRA_SCS#1

DDR_SDQ36

DDR_SDQ37

DDR_SDM_L4

DDR_SDQ38

DDR_SDQ39

DDR_SDQ44

DDR_SDQ45

DDR_SDM_L5

DDR_SDQ46

DDR_SDQ47

DDR_SDQ52

DDR_SDQ53

DDR_SDM_L6

DDR_SDQ54

DDR_SDQ55

DDR_SDQ60

DDR_SDQ61

DDR_SDM_L7

DDR_SDQ62

DDR_SDQ63

G

1

C291

0.1U_0402_16V4Z

2

DDR_BSA1 <5,9>

DDR_RASA_L <5,9>

DDR_CASA_L <5,9>

DDR_CLK_1L_L2 <5>

DDR_CLK_1L_H2 <5>

Compal Electronics, Inc.

Title

DDR-SODIMM SLOT0

Size Document Number Rev

Custom

LA-2421

Date: Sheet

G

+1.25VREF_MEM

H

0.6

of

856Wednesday, January 05, 2005

H

A

1 1

+1.25V

2 2

3 3

DDR_SDQS_L[0..7]<5,8>

DDR_SDM_L[0..7]<5,8>

DDR_SMAA[0..13]<5,8>

DDR_SDQ[0..63]<5,8>

4 4

RP43

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

DDR_SDQS_L[0..7]

DDR_SDM_L[0..7]

DDR_SMAA[0..13]

DDR_SDQ[0..63]

DDRB_SCS#1

DDRB_SCS#0

DDR_CKEB

B

Layout note

Note:

DDR_SMAA13 Recommend

for AMD.

C

+2.5V

DDR_SDQ4

DDR_SDQ5

DDR_SDQS_L0

DDR_SDQ6

DDR_SDQ7

DDR_SDQ12

DDR_SDQ13

DDR_SDQS_L1

DDR_SDQ15

DDR_CLK_2L_H1<5>

DDR_CLK_2L_L1<5>

DDR_CKEB<5>

DDR_BSA0<5,8> DDR_RASA_L <5,8>

DDR_WEA_L<5,8>

DDRB_SCS#0<5> DDRB_SCS#1 <5>

SB_SDAT<8,16,20,26>

SB_SCLK<8,16,20,26>

DDR_CLK_2L_H1

DDR_CLK_2L_L1

DDR_SDQ20

DDR_SDQ21

DDR_SDQS_L2

DDR_SDQ23

DDR_SDQ28

DDR_SDQ29

DDR_SDQS_L3

DDR_SDQ30

DDR_SDQ31

DDR_CKEB DDR_CKEB

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_BSA0

DDR_WEA_L

DDR_SMAA13

DDR_SDQ36

DDR_SDQ37

DDR_SDQS_L4

DDR_SDQ38

DDR_SDQ39

DDR_SDQ44

DDR_SDQ45

DDR_SDQS_L5

DDR_SDQ47

DDR_SDQ52

DDR_SDQ53

DDR_SDQS_L6

DDR_SDQ54

DDR_SDQ55

DDR_SDQ60

DDR_SDQ61

DDR_SDQS_L7

DDR_SDQ62

DDR_SDQ63

+3VS

JP30

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

TYCO_1470804-2

D

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

VSS

VDD

RAS#

CAS#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

BA1

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

SA0

196

SA1

198

SA2

200

DU

50 mil width

DDR_SDQ0

DDR_SDQ1

DDR_SDM_L0

DDR_SDQ2

DDR_SDQ3

DDR_SDQ8

DDR_SDQ9

DDR_SDM_L1

DDR_SDQ10DDR_SDQ14

DDR_SDQ11

DDR_SDQ16

DDR_SDQ17

DDR_SDM_L2

DDR_SDQ18DDR_SDQ22

DDR_SDQ19

DDR_SDQ24

DDR_SDQ25

DDR_SDM_L3

DDR_SDQ26

DDR_SDQ27

DDR_SMAA11

DDR_SMAA8

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_BSA1

DDR_RASA_L

DDR_CASA_L

DDRB_SCS#1DDRB_SCS#0

DDR_SDQ32

DDR_SDQ33

DDR_SDM_L4

DDR_SDQ34

DDR_SDQ35

DDR_SDQ40

DDR_SDQ41

DDR_SDM_L5

DDR_SDQ42DDR_SDQ46

DDR_SDQ43

DDR_CLK_2L_L2

DDR_CLK_2L_H2

DDR_SDQ48

DDR_SDQ49

DDR_SDM_L6

DDR_SDQ50

DDR_SDQ51

DDR_SDQ56

DDR_SDQ57

DDR_SDM_L7

DDR_SDQ58

DDR_SDQ59

+3VS

+1.25VREF_MEM

1

2

DDR_BSA1 <5,8>

DDR_CASA_L <5,8>

DDR_CLK_2L_L2 <5>

DDR_CLK_2L_H2 <5>

C648

0.1U_0402_16V4Z

+2.5V

R473

15_0402_1%

R486

15_0402_1%

E

12

12

1

2

0.1U_0402_16V4Z

+1.25VREF_MEM

C638

1

C640

1000P_0402_50V7K

2

DIMM1

Bottom Side

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

DDR-SODIMM SLOT1

Size Document Number Rev

Custom

LA-2421

Date: Sheet

E

of

956Wednesday, January 05, 2005

0.6

A

B

C

D

E

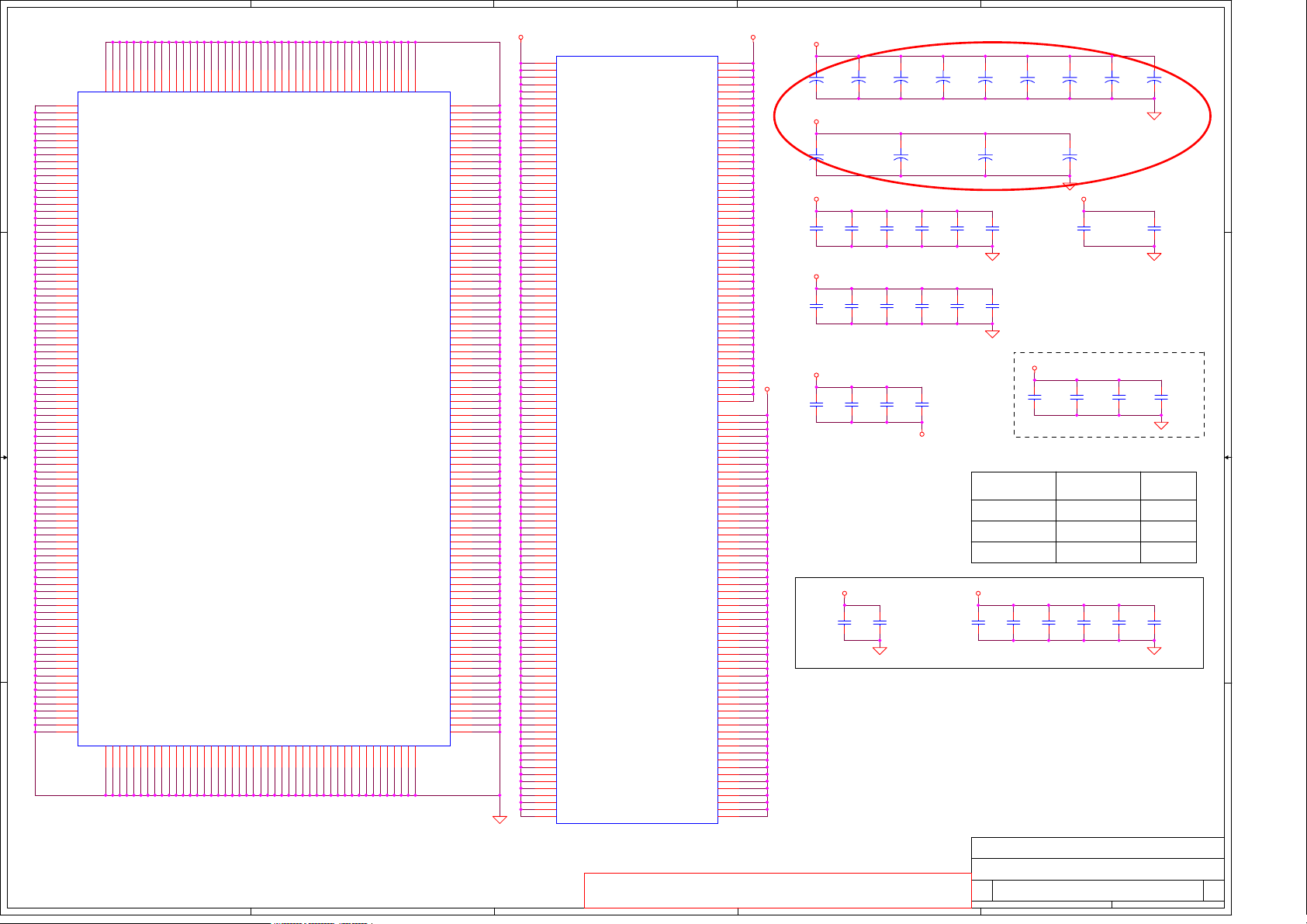

+2.5V +1.25V

470U_6.3V_M

1

+

1 1

C612

2

1

+

2

470U_D_4VM

C294

220U_D2_4VM@

1

+

C296

2

4.7U_0805_6.3V6K

4.7U_0805_6.3V6K

1

C274

2

1

2

C275

Near DIMMs

Near Power Supply

470U_D_4VM@

1

+

C367

2

330U_D_2VM_R15

1

2

+

C325

1

+

2

470U_6.3V_M

330U_6.3V_M

C411

1

+

C318

2

+1.25V

4.7U_0805_10V4Z

C324

1

C323

2

1

2

4.7U_0805_10V4Z

At either end of VTT island (=250 mil)

Layout note :

Place one cap close to every 2 pull up resistors termination to

+1.25VS

+1.25V

0.1U_0402_16V4Z

+1.25V

2 2

0.1U_0402_16V4Z

+1.25V

0.1U_0402_16V4Z

+1.25V

3 3

0.1U_0402_16V4Z

+1.25V

0.1U_0402_16V4Z

+1.25V

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C401

2

1

C389

2

1

C377

2

1

C363

2

1

C351

2

1

C339

2

1

C400

2

0.1U_0402_16V4Z

1

C388

2

0.1U_0402_16V4Z

1

C376

2

0.1U_0402_16V4Z

1

C362

2

0.1U_0402_16V4Z

1

C350

2

0.1U_0402_16V4Z

1

C338

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+2.5V

0.1U_0402_16V4Z

1

C399

2

1

C387

2

1

C375

2

1

C361

2

1

C349

2

1

C337

2

1

C398

2

0.1U_0402_16V4Z

1

C386

2

0.1U_0402_16V4Z

1

C360

2

0.1U_0402_16V4Z

1

C348

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C397

2

1

C385

2

1

C359

2

1

C347

2

1

C396

2

0.1U_0402_16V4Z

1

C384

2

0.1U_0402_16V4Z

1

C358

2

0.1U_0402_16V4Z

1

C346

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C395

2

1

C383

2

1

C357

2

1

C345

2

1

C394

2

0.1U_0402_16V4Z

1

C382

2

0.1U_0402_16V4Z

1

C356

2

0.1U_0402_16V4Z

1

C344

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C393

2

1

C381

2

1

C355

2

1

C343

2

1

C392

2

0.1U_0402_16V4Z

1

C380

2

0.1U_0402_16V4Z

1

C354

2

0.1U_0402_16V4Z

1

C342

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C391

2

1

C379

2

1

C353

2

1

C341

2

1

C390

2

0.1U_0402_16V4Z

1

C378

2

0.1U_0402_16V4Z

1

C352

2

+2.5V

0.1U_0402_16V4Z

1

C340

2

+2.5V

For EMI require

+2.5V

1

C1187

1000P_0402_50V7K

2

+2.5V

1

C1191

1000P_0402_50V7K

2

+1.25V

1

C1195

220P_0402_25V8K

2

+1.25V

1

C1199

220P_0402_25V8K

2

+1.25V

1

C1203

220P_0402_25V8K

2

1

C1188

1000P_0402_50V7K

2

1

C1192

1000P_0402_50V7K

2

1

C1196

220P_0402_25V8K

2

1

C1200

220P_0402_25V8K

2

1

C1204

220P_0402_25V8K

2

1

C1189

1000P_0402_50V7K

2

1

C1193

1000P_0402_50V7K

2

1

C1197

220P_0402_25V8K

2

1

C1201

220P_0402_25V8K

2

1

C1190

1000P_0402_50V7K

2

1

C1194

1000P_0402_50V7K

2

1

C1198

220P_0402_25V8K

2

1

C1202

220P_0402_25V8K

2

+2.5V

4 4

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

DDR SODIMM Decoupling

Size Document Number Rev

Custom

LA-2421

Date: Sheet

E

of

10 56Wednesday, January 05, 2005

0.6

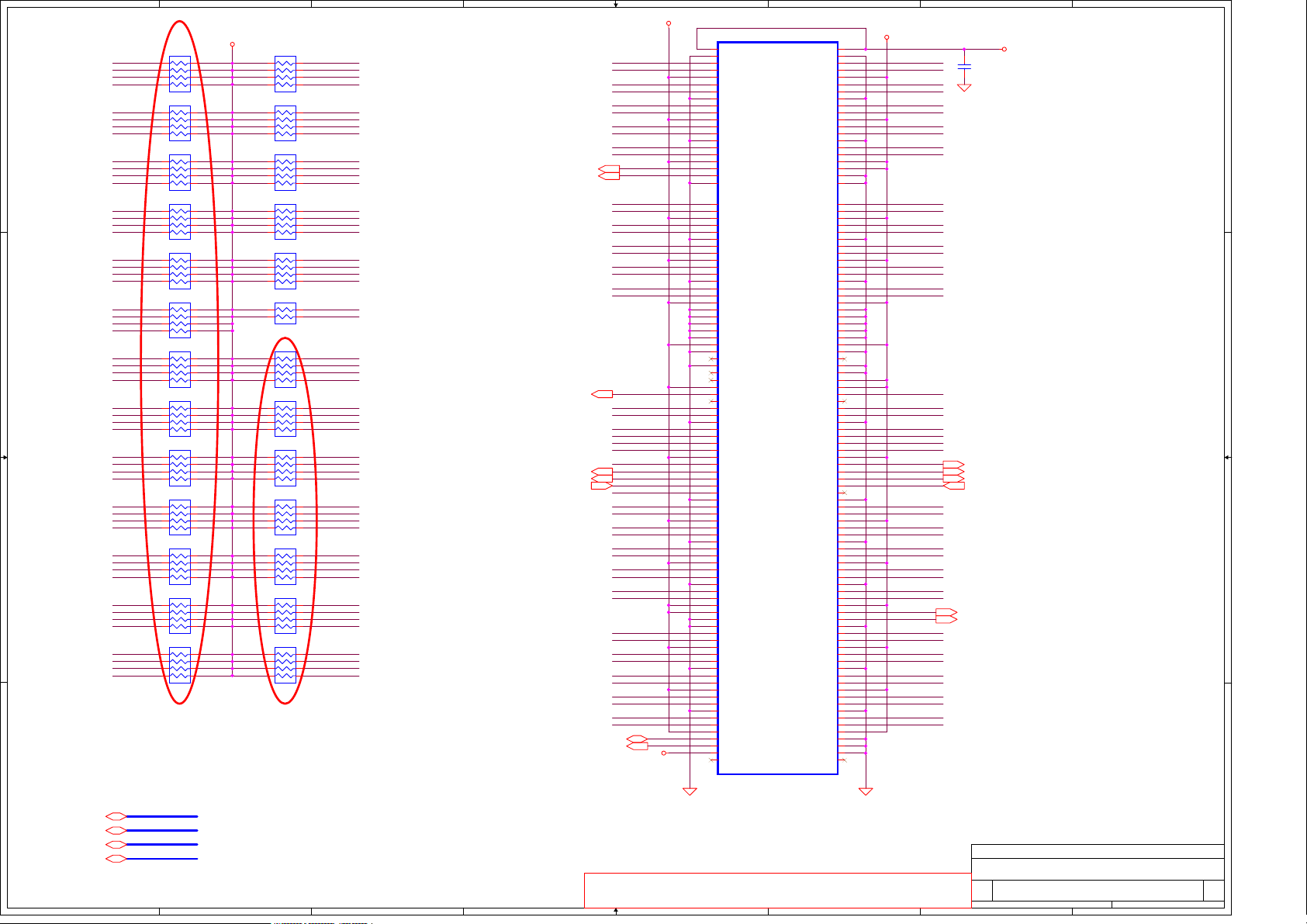

5

H_CADIP[0..15]<4>

H_CADIN[0..15]<4>

H_CADOP[0..15]<4>

D D

H_CADOP15

H_CADON15

H_CADOP14

H_CADON14

H_CADOP13

H_CADON13

H_CADOP12

H_CADON12

H_CADOP11

H_CADON11

H_CADOP10

H_CADON10

H_CADOP9

H_CADON9

H_CADOP8

H_CADON8

H_CADOP7

H_CADON7

H_CADOP6

H_CADON6

H_CADOP5

H_CADON5

H_CADOP4

1 2

1 2

H_CADON4

H_CADOP3

H_CADON3

H_CADOP2

H_CADON2

H_CADOP1

H_CADON1

H_CADOP0

H_CADON0

H_CLKOP1

H_CLKON1

H_CLKOP0

H_CLKON0

H_CTLOP0

H_CTLON0

C C

H_CLKOP1<4>

H_CLKON1<4>

H_CLKOP0<4>

H_CLKON0<4>

H_CTLOP0<4>

H_CTLON0<4>

+1.2V_HT

B B

R49 49.9_0402_1%

R48 49.9_0402_1%

H_CADON[0..15]<4>

U27A

T26

HT_RXCAD15P

R26

HT_RXCAD15N

U25

HT_RXCAD14P

U24

HT_RXCAD14N

V26

HT_RXCAD13P

U26

HT_RXCAD13N

W25

HT_RXCAD12P

W24

HT_RXCAD12N

AA25

HT_RXCAD11P

AA24

HT_RXCAD11N

AB26

HT_RXCAD10P

AA26

HT_RXCAD10N

AC25

HT_RXCAD9P

AC24

HT_RXCAD9N

AD26

HT_RXCAD8P

AC26

HT_RXCAD8N

R29

HT_RXCAD7P

R28

HT_RXCAD7N

T30

HT_RXCAD6P

R30

HT_RXCAD6N

T28

HT_RXCAD5P

T29

HT_RXCAD5N

V29

HT_RXCAD4P

U29

HT_RXCAD4N

Y30

HT_RXCAD3P

W30

HT_RXCAD3N

Y28

HT_RXCAD2P

Y29

HT_RXCAD2N

AB29

HT_RXCAD1P

AA29

HT_RXCAD1N

AC29

HT_RXCAD0P

AC28

HT_RXCAD0N

Y26

HT_RXCLK1P

W26

HT_RXCLK1N

W29

HT_RXCLK0P

W28

HT_RXCLK0N

P29

HT_RXCTLP

N29

HT_RXCTLN

D27

HT_RXCALN

E27

HT_RXCALP

216RS480M_BGA706

H_CADIP[0..15]

H_CADIN[0..15]

H_CADOP[0..15]

H_CADON[0..15]

4

H_CADIP15

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

R24

H_CADIN15

R25

H_CADIP14

N26

H_CADIN14

P26

H_CADIP13

N24

H_CADIN13

N25

H_CADIP12

L26

H_CADIN12

M26

H_CADIP11

J26

H_CADIN11

K26

H_CADIP10

J24

H_CADIN10

J25

H_CADIP9

G26

H_CADIN9

H26

H_CADIP8

G24

H_CADIN8

G25

H_CADIP7

L30

H_CADIN7

M30

H_CADIP6

L28

H_CADIN6

L29

H_CADIP5

J29

H_CADIN5

K29

H_CADIP4

H30

H_CADIN4

H29

H_CADIP3

E29

H_CADIN3

E28

H_CADIP2

D30

H_CADIN2

E30

H_CADIP1

D28

H_CADIN1

D29

H_CADIP0

B29

H_CADIN0

C29

H_CLKIP1

L24

H_CLKIN1

L25

H_CLKIP0

F29

H_CLKIN0

G29

H_CTLIP0

M29

H_CTLIN0

M28

R53 91_0402_5%

B28

1 2

A28

H_CLKIP1 <4>

H_CLKIN1 <4>

H_CLKIP0 <4>

H_CLKIN0 <4>

H_CTLIP0 <4>

H_CTLIN0 <4>

0.1U_0402_16V4Z

0.1U_0402_16V4Z

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HYPER TRANSPORT CPU

I/F

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

C124

C110

+2.5VS

1

2

1

2

3

NMRASA#<15>

NMCASA#<15>

NMWEA#<15>

NMCSA0#<15>

NMCKEA<15>

NMCLKA0<15>

NMCLKA0#<15>

C69 0.47U_0603_16V7K

1 2

C183 0.47U_0603_16V7K

12

R62

1K_0402_1%

12

R59

1K_0402_1%

MEM_VREF

1 2

R55 1K_0402_5%

1 2

+1.8VS

1U_0603_10V4Z

NMAA0

NMAA1

NMAA2

NMAA3

NMAA4

NMAA5

NMAA6

NMAA7

NMAA8

NMAA9

NMAA10

NMAA11

NMAA12

NMAA13

NMAA14

NDQMA0

NDQMA1

NDQMA2

NDQMA3

NDQMA4

NDQMA5

NDQMA6

NDQMA7

NDQSA0

NDQSA1

NDQSA2

NDQSA3

NDQSA4

NDQSA5

NDQSA6

NDQSA7

NMRASA#

NMCASA#

NMWEA#

NMCSA0#

NMCKEA

NMCLKA0

NMCLKA0#

C140

1 2

2

NMAA[0..14]<15>

NMDA[0..63]<15>

NDQMA[0..7]<15>

NDQSA[0..7]<15>

AF17

AK17

AH16

AF16

AJ22

AJ21

AH20

AH21

AK19

AH19

AJ17

AG16

AG17

AH17

AJ18

AG26

AJ29

AE21

AH24

AH12

AG13

AH8

AE8

AF25

AH30

AG20

AJ25

AH13

AF14

AJ7

AG8

AG25

AH29

AF21

AK25

AJ12

AF13

AK7

AF9

AE17

AH18

AE18

AJ19

AF18

AK16

AJ16

AE28

AJ4

AJ20

AK20

AJ15

AJ14

U27B

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_DQS0P

MEM_DQS1P

MEM_DQS2P

MEM_DQS3P

MEM_DQS4P

MEM_DQS5P

MEM_DQS6P

MEM_DQS7P

MEM_DQS0N

MEM_DQS1N

MEM_DQS2N

MEM_DQS3N

MEM_DQS4N

MEM_DQS5N

MEM_DQS6N

MEM_DQS7N

MEM_RAS#

MEM_CAS#

MEM_WE#

MEM_CS#

MEM_CKE

MEM_CKP

MEM_CKN

MEM_CAP1

MEM_CAP2

MEM_VMODE

MEM_VREF

MPVDD

MPVSS

216RS480M_BGA706

NMAA[0..14]

NMDA[0..63]

NDQMA[0..7]

NDQSA[0..7]

MEM_A I/F

MEM_COMPP

MEM_COMPN

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24