HP V3706TX Schematics

5

4

3

2

1

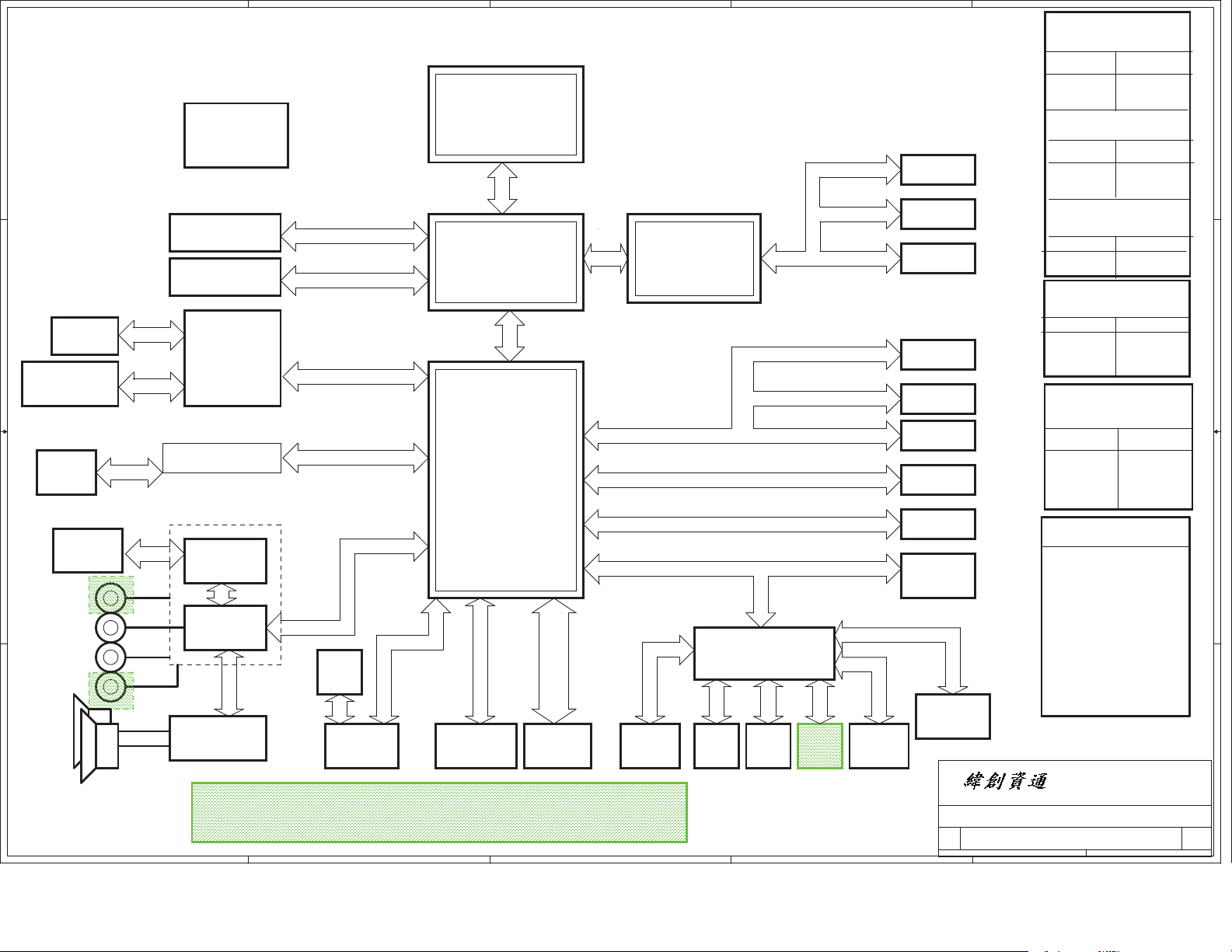

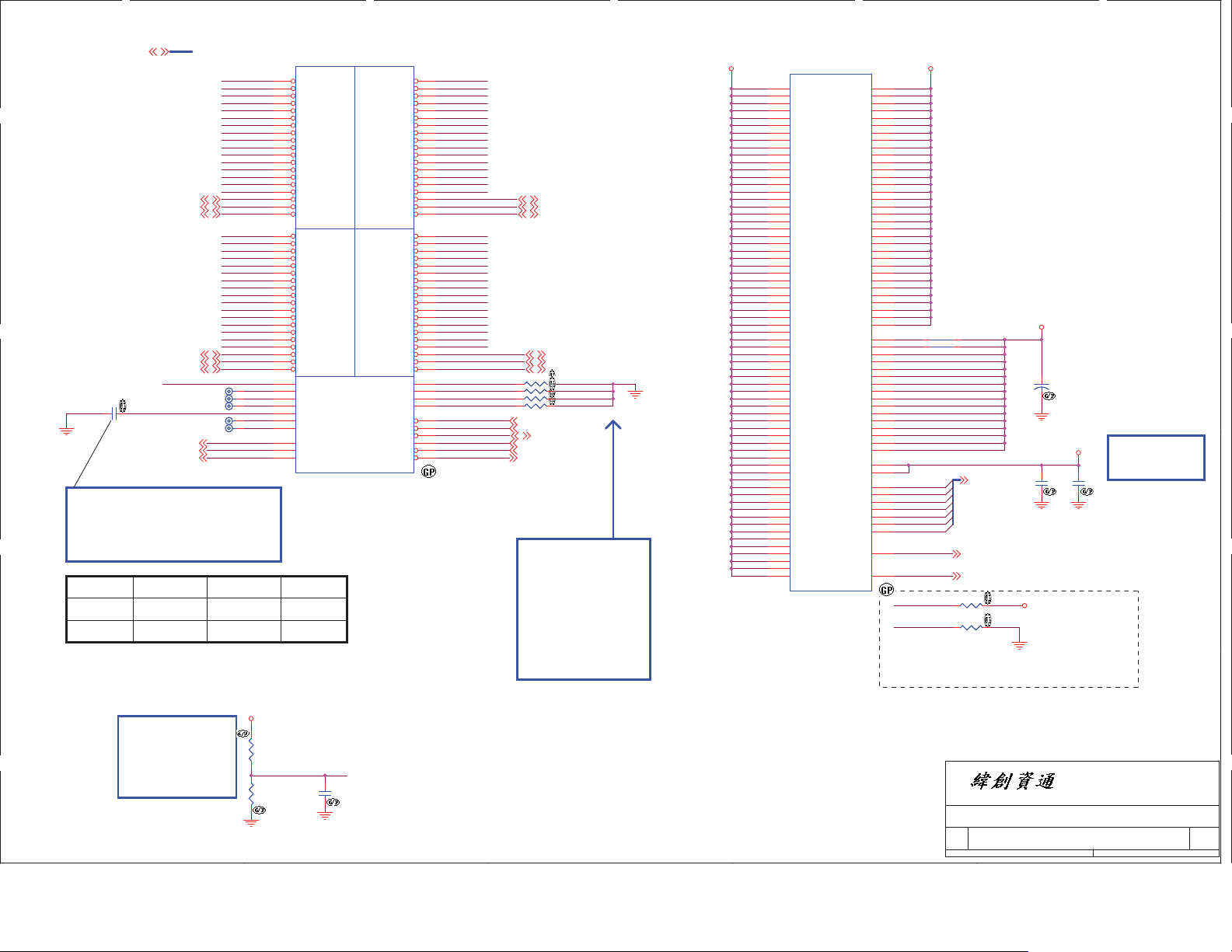

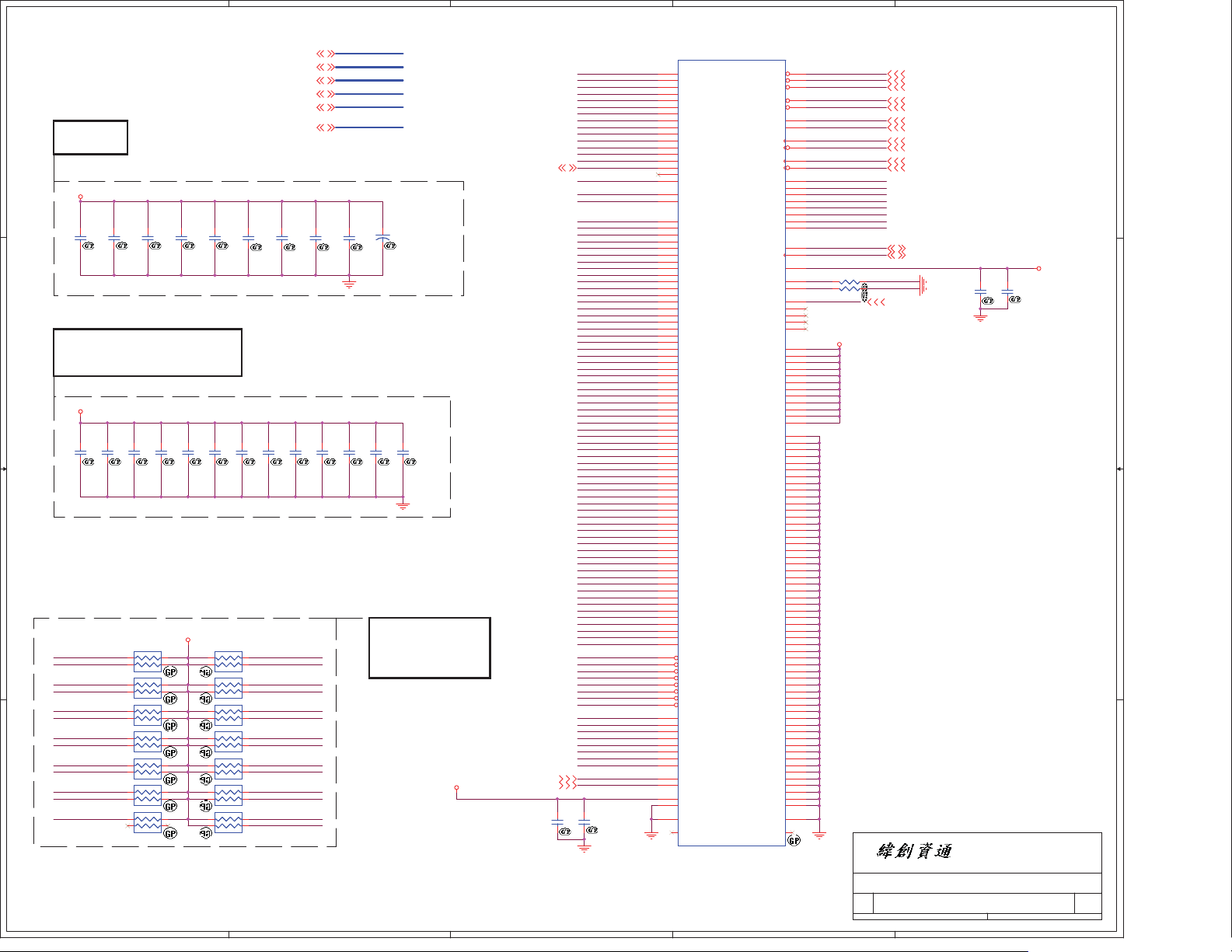

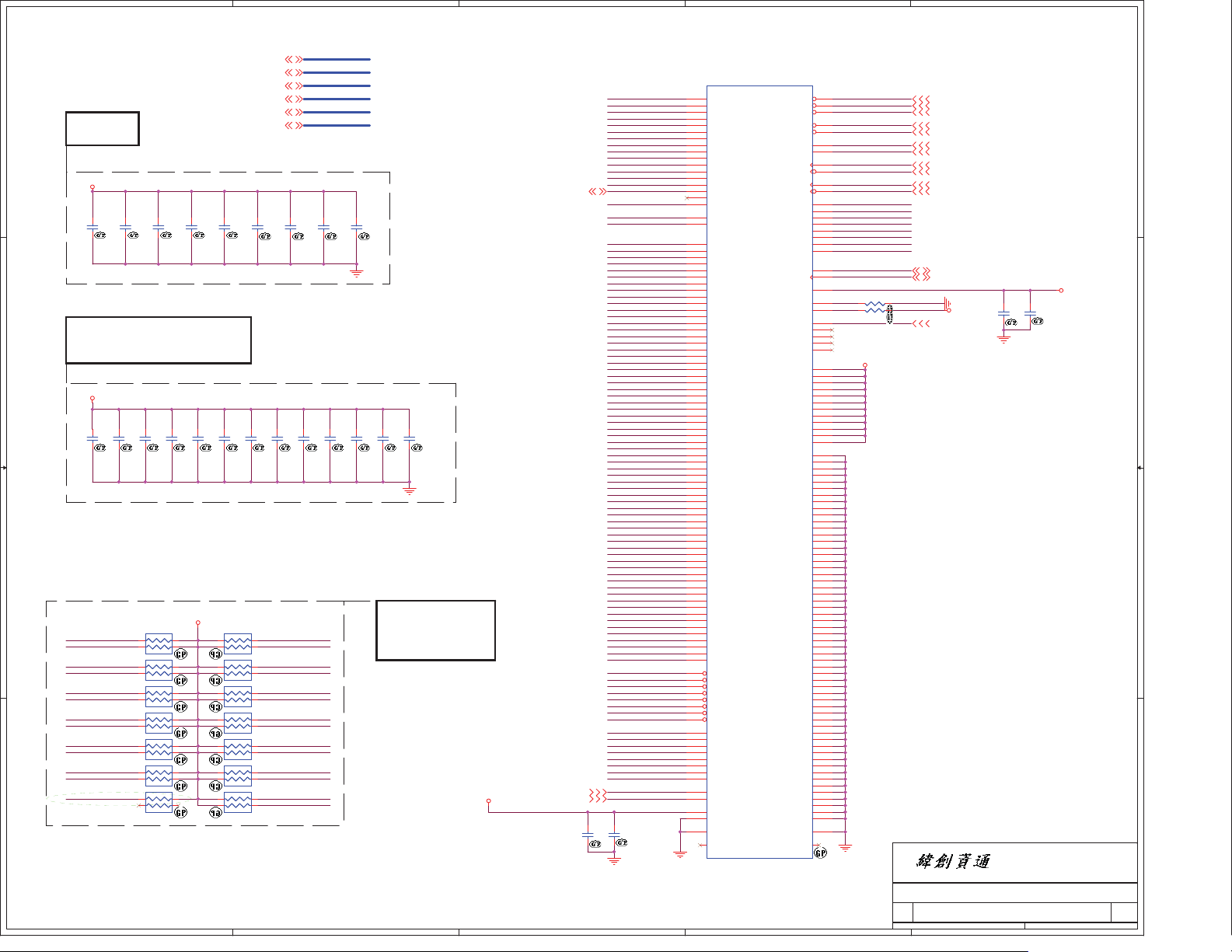

Viking-Discrete Block Diagram

Intel CPU

D D

CLK GEN

REALTEK RTM875

DDRII

533/667

DDRII

533/667

Slot 0

Slot 1

3

13

14

DDRII 667 Channel A

DDR II 667 Channel B

Meron 2M/4M SV

FSB:667 or 800 MHz

4,5,6

Host BUS

533/667MHz

Crestline-GM/GML

AGTL+ CPU I/F

INTEGRATED GRAHPICS

LVDS, CRT I/F

DDR I/F

7,8,9,10,11,12

PCIE x 16

Project code : 91.4S501.001

PCB P/N :06230

Revision : MV-5

RGB CRT

LVDS

nVIDIA

SVIDEO

NB8M-GS

38,39,40

CRT

LCD

TVOUT

13

14

13

SYSTEM DC/DC

TPS51120

INPUTS

DCBATOUT

OUTPUTS

5V_S3

3V_S5

SYSTEM DC/DC

MAX8743

INPUTS

DCBATOUT

OUTPUTS

1D05V_S0

1D8V_S3

SYSTEM DC/DC

FAN5234

INPUTS

DCBATOUT

OUTPUTS

VGA_CORE_S0

11A

MAXIM CHARGER

MAX8725

C C

1394

25

SD/SDIO/MMC

MS/MS Pro/xD

25

1394

Ricoh

R5C833

CardReader

PCI

24,25

ICH8-M

10/100 NIC

RJ45

CONN

28

B B

RJ11

CONN

29

Marvell 88E8039

AMOM

MODEM

CX20548

27

INTERNAL

ARRAY MIC

MIC IN

LINE OUT

HD AUDIO

CODEC

CX20561-12Z

29

SPDIF

Ricoh

R5538

PCIE

HD Audio

28

10 USB 2.0/1.1 ports

High Definition Audio

PCI/PCI BRIDGE

PCIE x 1

PCIE+USB 2.0

INTEL

(10/100/1000Mb)ETHERNET

ATA 66/100

ACPI 1.1

LPC I/F

DMI I/F

100MHz

18,19,20,21

PCIE x 1

USB 2.0 x 1

USB 2.0

SATA

PATA

LPC Bus

KBC

ENE KB3910SF

CAMERA

BLUE

TOOTH

USB x 3

HDD

ODD

32

32

23

23

23

TPM

SLB9635TT

31

34

Flash ROM

1MB

OP AMP

A A

APA2031

30

New Card

28

2CH

SPEAKER

5

CRT LINE OUTMIC IN S/PDIF TVOUT

4

DOCK

Mini-Card

802.11a/b/g

26

Mini-Card

WWAN

10/100

Ethernet

3

Capacity

Button

CIR

Touch

Pad

3226

Int.

CIR

KB

32 32 22

Thermal

& Fan

EMC2102

2

33

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

INPUTS

DCBATOUT

CPU DC/DC

INPUTS

DCBATOUT

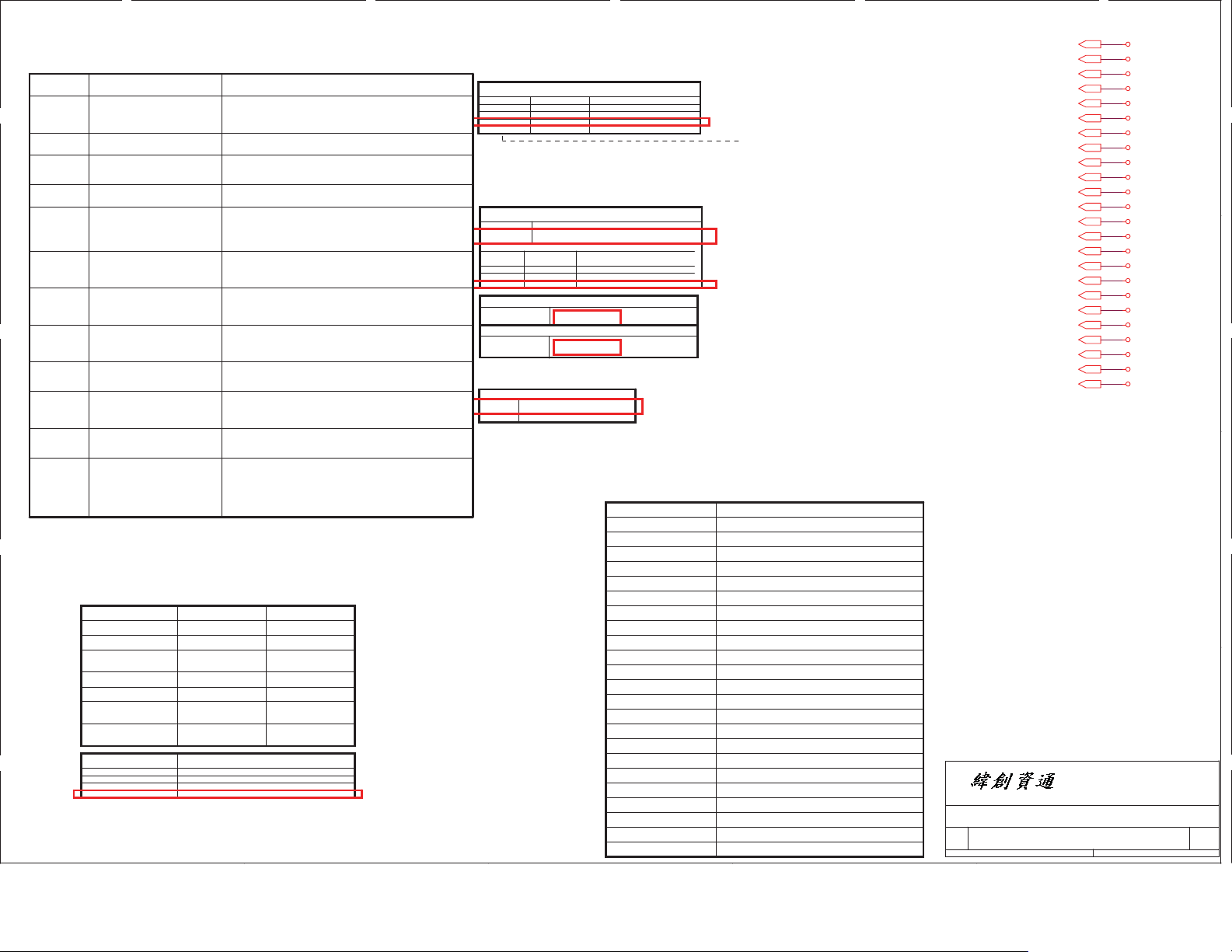

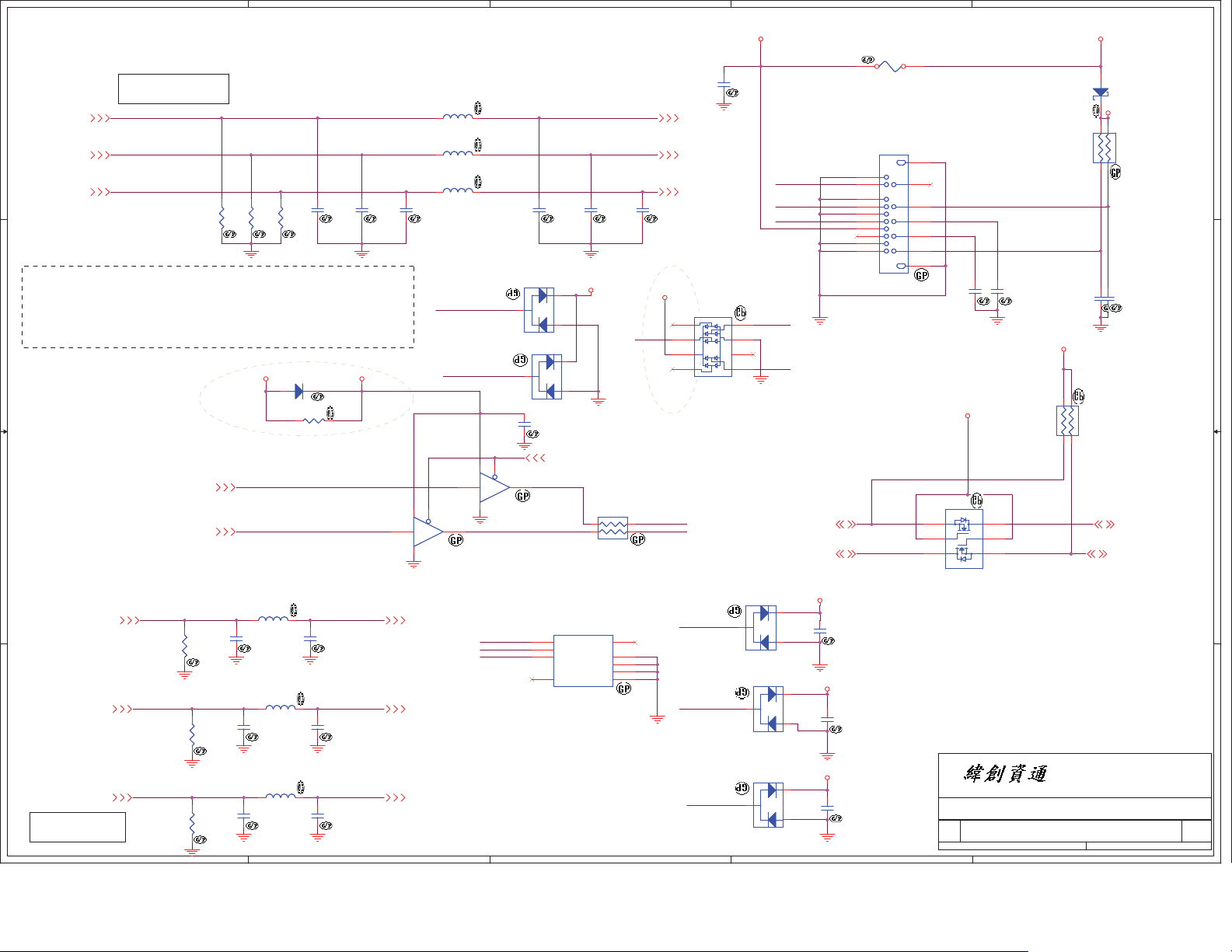

PCB LAYER

L1:

L2:

L3:

L4:

L5:

L6:

L8:

L9:

L10:

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

Pamirs-Discrete -5

Pamirs-Discrete -5

Pamirs-Discrete -5

OUTPUTS

BT+

18V 3.0A

5V 100mA

MAX8736ETL

OUTPUTS

VCC_CORE

0.844~1.3V

44A

Signal 1

GND

Signal 2

Signal 3

GND

VCC

Signal 4L7:

Signal 5

GND

Signal 5

147Wednesday, September 12, 2007

147Wednesday, September 12, 2007

147Wednesday, September 12, 2007

of

of

1

of

http://hobi-elektronika.net

A

B

C

D

E

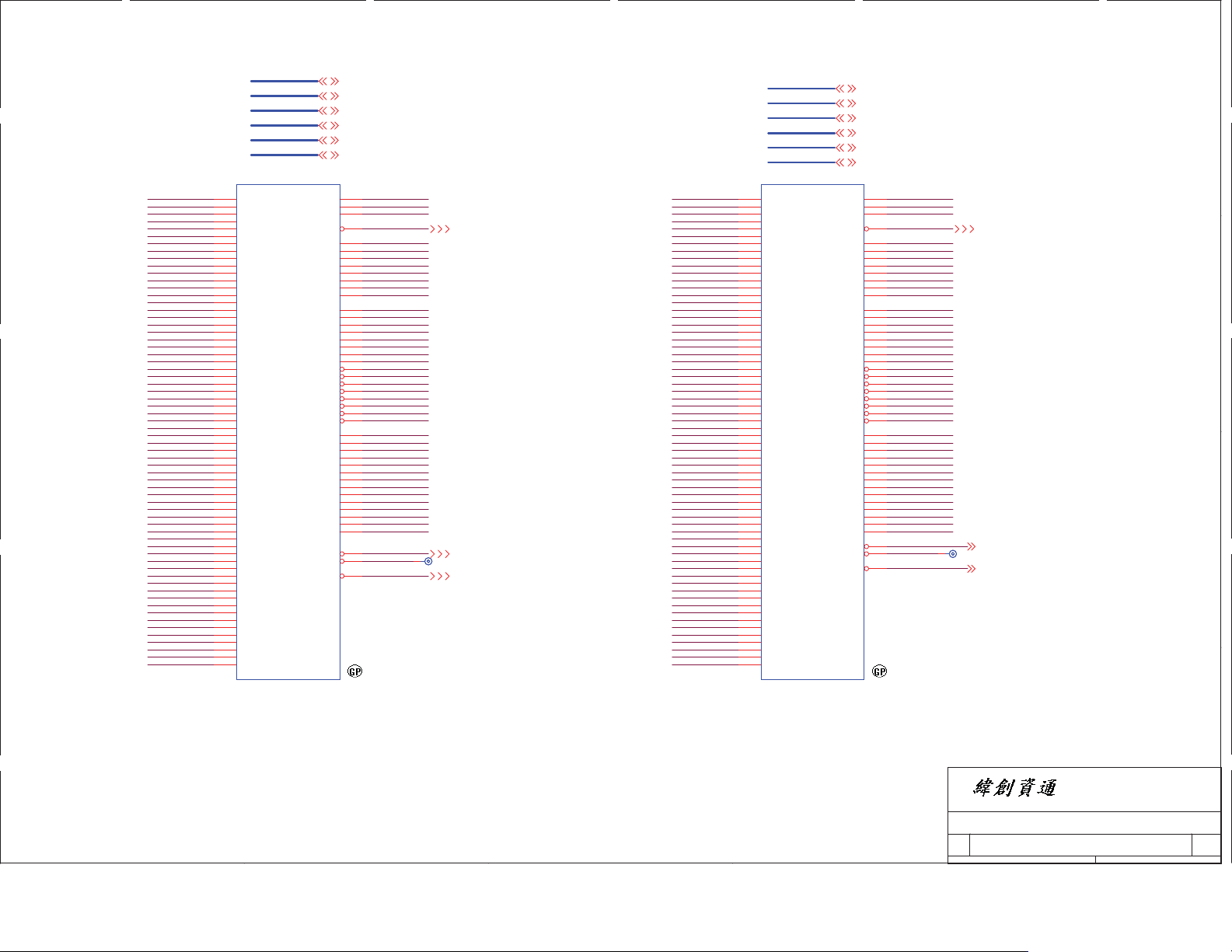

INTEL ICH8-M STRAP PIN

Signal Usage/When Sampled

HDA_SDOUT XOR Chain Entrance/

4 4

HDA_SYNC

GNT2#

GPIO20

GNT3#

GNT0#

SPI_CS1#

INTVRMEN

3 3

LAN100_SLP

SATALED#

SPKR

TP3

GPIO33/

HDA_DOCK_EN#

PCIE Port Config 1 bit1,

Rising Edge of PWROK

PCIE Port Config 1 bit0,

Rising Edge of PWROK.

PCIE Port Config 2 bit0,

Rising Edge of PWROK.

Reserved

Top-Block Swap Override.

Rising Edge of PWROK.

Boot BIOS Destination

Selection.

Rising Edge of PWROK.

Integrated VccSus1_05

VccSus1_5 and VccCL1_5

VRM Enable/Disable.Always

sampled.

Integrated VccLAN1_05

VccCL1_05 VRM enable

/Disable. Always sampled.

PCIE LAN REVERSAL.Rising

Edge of PWROK.

No Reboot.

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

Flash Descriptor Security

Override Strap

Rising Edge of PWROK.

2 2

INTEL CRESTLINE STRAP PIN

CFG Strap HIGH 1LOW 0

CFG 5

CFG 8

Low Power PCI Express Normal Low Power mode

CFG 9

PCI Express Graphics

Lane Reversal

CFG 16

FSB Dynamic ODT Disabled Enabled

CFG 19

DMI Lane Reserved Normal Operation Reserved Lane

CFG 20

Concurrent SDVO/PCIE

SDVO_CTRL_DATA

SDVO Present

1 1

CFG 12

CFG 13

LL(00)

LH(01)

HL(10)

HH(11)

+RTCVCC19,21

1D05V_S04,5,6,7,9,10,11,19,21,37,47

Allows entrance to XOR Chain testing when TP3

Comment

pulled low at rising edge of PWROK.When TP3 not

pulled low at rising edge of PWROK,sets bit1 of

RPC.PC(Config Registers:offset 224h)

Sets bit0 of RPC.PC(Config Registers:Offset 224h)

Sets bit2 of RPC.PC(Config Registers:Offset 224h)

Weak Internal PULL-DOWN.NOTE:This signal should

not be pull HIGH.

Sampled low:Top-Block Swap mode(inverts A16 for all

cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

Controllable via Boot BIOS Destination bit

(Config Registers:Offset 3410h:bit 11:10).

GNT0# is MSB, 01-SPI, 10-PCI, 11-LPC.

Enables integrated VccSus1_05,VccSus1_5 and

VccCL1_5 VRM when sampled high

Enables integrated VccLAN1_05,VccCL1_05 VRM

when sampled high

This signal has weak internal pull-up.

set bit27 of MPC.LR(Device28:Function0:Offset D8)

If sampled high, the system is strapped to the

"No Reboot" mode(ICH8M will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.(Offset:3410h:bit5)

This signal should not be pull low unless using

XOR Chain testing.

Internal Pull-Up.If sampled low,the Flash Descriptor

Security will be overidden.if high,the Security

measures defined in the Flash Descriptor will be in

effect.

This should only be used in manufacturing

environments

DMI X 2 DMI X 4

Ϫ

Lane Reversal Normal Mode(Lanes

Only PCIE or SDVO

is operation

NO SDVO Card

Present

XOR/ALL-Z

Reserved

XOR Mode Enabled

All Z Mode Enabled

Normal Operation

Ϫ

Ϫ

A

Ϫ

number in order)

Ϫ

Ϫ

PCIE and SDVO are

operation simultaneous

SDVO Card Present

Ϫ

B

XOR Chain Entrance Strap

ICH_RSVD

A16 swap override strap

PCI_GNT#3

BOOT BIOS Strap

PCI_GNT#0 BOOT BIOS Location

integrated VccSus1_05,VccSus1_5,VccCL1_5

SM_INTVRMEN

integrated VccLan1_05VccCL1_05

LAN100_SLP

AZ_DOUT_ICH

tp3

0

0

10

low = A16 swap override enable

high = default

SPI_CS#1

10

1

1

Description

0

1

Normal Operation(default)

Set PCIE port cofig bit1

11

SPI10

PCI

LPC(Default)

High=Enable Low=Disable

High=Enable Low=Disable

RSVD

Enter XOR Chain

DEFAULE HIGH

No Reboot Strap

LOW = DefauleSPKR

High=No Reboot

INTEL ICH8-M INTEGRATED

8.2K PULL HIGH

PULL-UPS and PULL-DOWNS

SIGNAL Resistor Type/Value

HDA_BIT_CLK

HDA_RST#

HDA_SDIN[3:0]

HDA_SDOUT

HDA_SYNC

GNT[3:0]

GPIO[20]

LDA[3:0]#/FHW[3:0]#

LAN_RXD[2:0]

LDRQ[0]

LDRQ[1]/GPIO23

PME#

PWRBTN#

SATALED#

SPI_CS1#

SPI_CLK

SPI_MOSI

SPI_MISO

TACH_[3:0]

SPKR

TP[3]

USB[9:0][P,N]

CL_RST#

C

PULL-DOWN 20K

NONE

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 15K

TBD

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

D

1D25V_S03,7,10,21,38

1D2V_LAN_S527

1D5V_NEW_S028

1D5V_S05,10,17,19,20,21,26,28,38,47

1D8V_S37,10,11,13,14,34,37,38

2D5V_LAN_S527,28

3D3V_AUD_S029,30

3D3V_AUX_S519,31,32,33,36,39,46

3D3V_LAN_S527,28

3D3V_S03,4,7,10,11,13,14,15,16,18,19,20,21,22,23,24,25,26,27,28,29,31,32,33,34,35,36,40,41,42,43,47

3D3V_S517,18,20,21,22,26,27,28,29,31,34,36,39,47

5V_AUX_S522,26,29,31,34,36

5V_S316,23,32,33,34,36,37,38

5V_S015,16,17,20,21,22,23,29,30,31,32,33,34,35,47

5V_S516,21,34,37,40

AD+17,39,46,47

DCBATOUT16,17,34,35,36,37,39,40,47

DDR_VREF_S013,14,38

DDR_VREF_S37,13,14,38

KBC_3D3V_AUX22,31,33,39

LCDVDD_S016

VCC_CORE_S05,6,35

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

Table of Content

Table of Content

Pamirs-Discrete SA

Pamirs-Discrete SA

Pamirs-Discrete SA

E

+RTCVCC

1D05V_S0

1D25V_S0

1D2V_LAN_S5

1D5V_NEW_S0

1D5V_S0

1D8V_S3

2D5V_LAN_S5

3D3V_AUD_S0

3D3V_AUX_S5

3D3V_LAN_S5

3D3V_S0

3D3V_S5

5V_AUX_S5

5V_S3

5V_S0

5V_S5

AD+

DCBATOUT

DDR_VREF_S0

DDR_VREF_S3

KBC_3D3V_AUX

LCDVDD_S0

VCC_CORE_S0

247Wednesday, September 12, 2007

247Wednesday, September 12, 2007

247Wednesday, September 12, 2007

of

of

of

http://hobi-elektronika.net

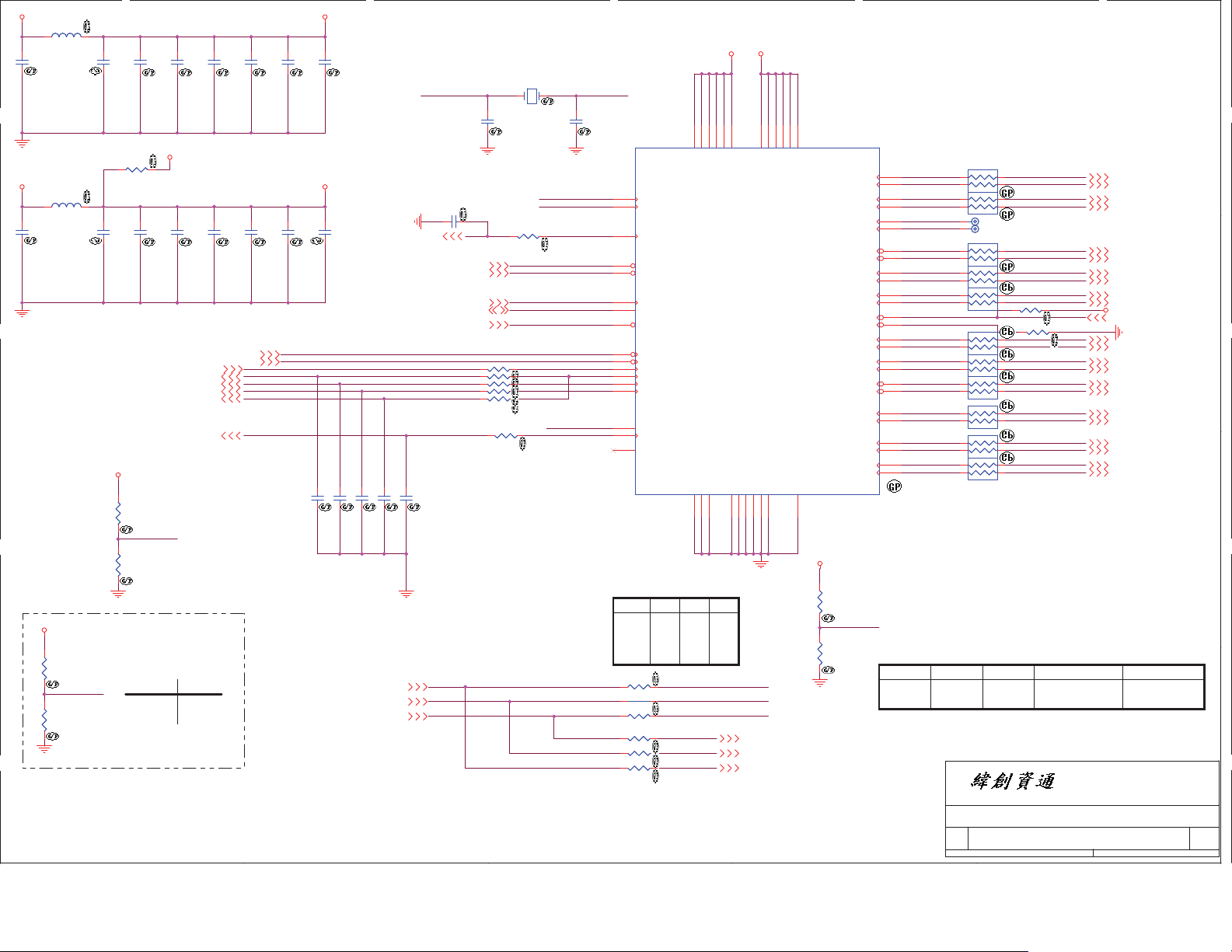

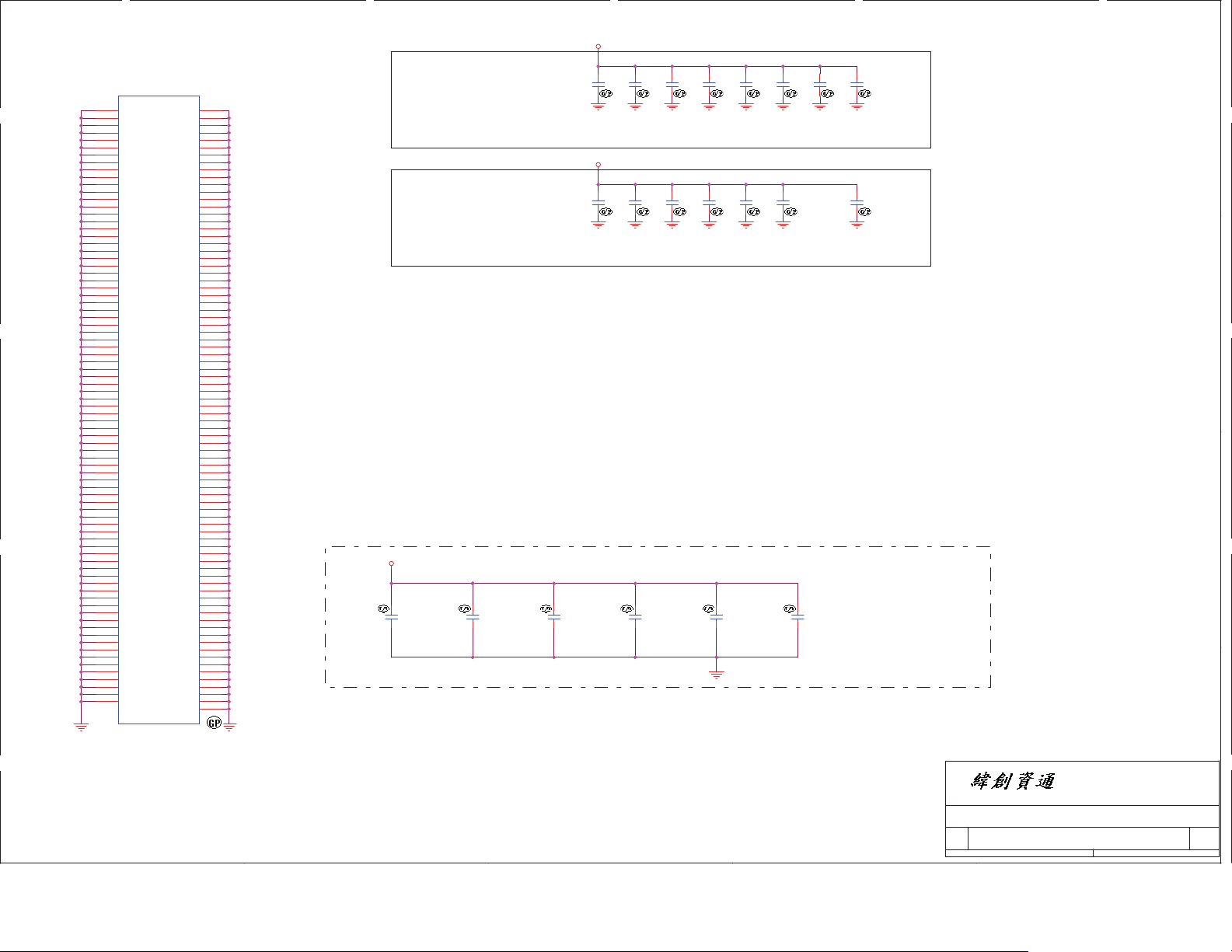

A

3D3V_S0 3D3V_S0_CK505

L21

L21

1 2

MLB-160808-18-GP

MLB-160808-18-GP

12

C639

C639

SC1U10V3KX-3GP

SC1U10V3KX-3GP

5

DY

12

C594

C594

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

12

C597

C597

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C630

C630

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C595

C595

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

12

12

C337

C337

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C603

C603

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

D D

3D3V_S0

R329

R329

1D25V_S0

MLB-160808-18-GP

MLB-160808-18-GP

12

C601

C601

L49

L49

1 2

SC1U10V3KX-3GP

SC1U10V3KX-3GP

1 2

12

0R3-0-U-GP

0R3-0-U-GP

DY

DY

C354

C354

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C596

C596

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C621

C621

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

12

C614

C614

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C620

C620

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

1D25V_S0_CK505_IO

12

C342

C342

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C C

CLKSATAREQ#20

CLKREQ#_B7

PCLK_FWH33

CLK_PCI_TCG34

PCLK_KBC31

CLK_PCI_ICH18

PCLK_PCM24

CLK_14M_ICH20

3D3V_S0_CK505

12

B B

3D3V_S0_CK505

12

R448

R448

10KR2J-3-GP

10KR2J-3-GP

ITP_EN

12

R447

R447

10KR2J-3-GP

10KR2J-3-GP

DY

DY

12

R453

R453

10KR2J-3-GP

10KR2J-3-GP

PCI2_TME

12

R454

R454

10KR2J-3-GP

10KR2J-3-GP

DY

DY

ITP_EN Output

0 SRC8

1 CPU_ITP

Design Note:

1. All of Input pin didn't have internal pull up resistor.

2. Clock Request (CR) function are enable by registers.

3. CY28548 integrated serial resistor of differential clock,

so put 0 ohm serial resistor in the schematic.

5

4

12

C600

C600

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C348

C348

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

12

C316SC4D7P50V2CN-1GP C316SC4D7P50V2CN-1GP

C314SC4D7P50V2CN-1GP C314SC4D7P50V2CN-1GP

CPU_BSEL25

CPU_BSEL15

CPU_BSEL05

4

CLK_48M_ICH20

12

12

C612SC4D7P50V2CN-1GP C612SC4D7P50V2CN-1GP

C313SC4D7P50V2CN-1GP C313SC4D7P50V2CN-1GP

C315SC4D7P50V2CN-1GP C315SC4D7P50V2CN-1GP

12

SC33P50V2JN-3GP

SC33P50V2JN-3GP

C332 SC4D7P50V2CN-1GPC332 SC4D7P50V2CN-1GP

1 2

H_STP_PCI#20

H_STP_CPU#20

ICH_SMBCLK13,14,20

ICH_SMBDATA13,14,20

CK_PWRGD20

R185 33R2J-2-GPR185 33R2J-2-GP

1 2

R192 33R2J-2-GPDYR192 33R2J-2-GPDY

1 2

R193 33R2J-2-GPR193 33R2J-2-GP

1 2

R195 33R2J-2-GPR195 33R2J-2-GP

1 2

R194 33R2J-2-GPR194 33R2J-2-GP

1 2

R450 33R2J-2-GPR450 33R2J-2-GP

1 2

3

3D3V_S0_CK505

X1

X1

1 2

X-14D31818M-36GP

X-14D31818M-36GP

C328

C328

1 2

R200 33R2J-2-GPR200 33R2J-2-GP

CLK_XTAL_OUTCLK_XTAL_IN

12

SC33P50V2JN-3GP

SC33P50V2JN-3GP

CLK_XTAL_IN

CLK_XTAL_OUT

FSA

PCI2_TME

27_SEL

ITP_EN

FSB

FSC

ICS9LPRS355BKLFT-GP

ICS9LPRS355BKLFT-GP

C327

C327

U28

U28

3

X1

2

X2

17

USB_48MHZ/FSLA

45

PCI_STOP#

44

CPU_STOP#

7

SCLK

6

SDATA

63

CK_PWRGD/PD#

8

PCI0/CR#_A

10

PCI1/CR#_B

11

PCI2/TME

12

PCI3

13

PCI4/27_SELECT

14

PCI_F5/ITP_EN

64

FSLB/TEST_MODE

5

REF0/FSLC/TEST_SEL

55

NC#55

4

16

VDDREF

GND48

15

18

9

VDD48

VDDPCI

GNDREF

GNDPCI

1

FS_C FS_B FS_A CPU

1 0 1 100M

0 0 1 133M

0 1 0 200M

0 1 1 166M

1 2

R449 10KR2J-3-GPR449 10KR2J-3-GP

1 2

R203 0R0402-PADR203 0R0402-PAD

1 2

R201 2K2R2J-2-GPR201 2K2R2J-2-GP

R191 1KR2J-1-GPR191 1KR2J-1-GP

1 2

R174 1KR2J-1-GPR174 1KR2J-1-GP

1 2

R445 1KR2J-1-GPR445 1KR2J-1-GP

1 2

3

http://hobi-elektronika.net

46

62

VDDSRC

VDDCPU

23

VDDPLL3

GND

22

1D25V_S0_CK505_IO

27

19

43

VDD96_IO

VDDSRC_IO

VDDPLL3_IO

GND

GNDSRC

GNDSRC

GNDSRC

GNDCPU

26

30

36

49

59

FSC

FSB

FSA

MCH_CLKSEL0 7

MCH_CLKSEL1 7

MCH_CLKSEL2 7

33

52

56

VDDSRC_IO

VDDSRC_IO

VDDCPU_IO

27MHZ_NONSS/SRCT1/SE1

27MHZ_SS/SRCC1/SE2

GND

65

CPUT1_F

CPUC1_F

CPUT2_ITP/SRCT8

CPUC2_ITP/SRCC8

SRCT7/CR#_F

SRCC7/CR#_E

SRCT11/CR#_H

SRCC11/CR#_G

SRCT3/CR#_C

SRCC3/CR#_D

SRCT2/SATAT

SRCC2/SATAC

SRCT0/DOTT_96

SRCC0/DOTC_96

3D3V_S0_CK505

12

R183

R183

10KR2J-3-GP

10KR2J-3-GP

12

R184

R184

10KR2J-3-GP

10KR2J-3-GP

DY

DY

CPUC0

SRCC6

SRCT10

SRCC10

SRCC9

SRCC4

27_SEL

2

CPUT0

SRCT6

SRCT9

SRCT4

61

60

58

57

54

53

51

50

48

47

41

42

40

39

37

38

34

35

31

32

28

29

24

25

20

21

CPU_BCLK

CPU_BCLK#

MCH_BCLK

MCH_BCLK#

CPU_XDP

CPU_XDP#

PCIE_LAN

PCIE_LAN#

PCIE_MINI1

PCIE_MINI1#

PCIE_NEW

PCIE_NEW#

PCIE_MINI2

PCIE_MINI2#

MCH_3GPLL

MCH_3GPLL#

PCIE_ICH

PCIE_ICH#

PCIE_SATA

PCIE_SATA#

27MHZ

27MHZSS

REFCLKP

REFCLKN

RN40

RN40

RN30

RN30

RN33

RN33

RN39

RN39

RN45

RN45

RN43

RN43

RN41

RN41

1

4

2 3

1

4

2 3

TP39 TPAD28TP39 TPAD28

TP40 TPAD28TP40 TPAD28

1

4

2 3

1

4

2 3

2 3

1

4

R228 10KR2J-3-GPR228 10KR2J-3-GP

RN42

RN42

R227

2 3

1

4

2 3

1

4

2 3

1

4

RN37

RN37

2 3

1

4

RN34

RN34

2 3

1

4

2 3

1

4

RN32

RN32

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

1 2

DYR227

DY

1 2

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN0J-6-GP

SRN33J-5-GP-U

SRN33J-5-GP-U

SRN0J-6-GP

SRN0J-6-GP

10KR2J-3-GP

10KR2J-3-GP

1

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_BCLK 7

CLK_MCH_BCLK# 7

CLK_PCIE_LAN 27

CLK_PCIE_LAN# 27

CLK_PCIE_MINI1 26

CLK_PCIE_MINI1# 26

CLK_PCIE_NEW 28

CLK_PCIE_NEW# 28

3D3V_S0

NEWCARD_CLKREQ# 28

CLK_PCIE_MINI2 26

CLK_PCIE_MINI2# 26

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

CLK_PCIE_ICH 20

CLK_PCIE_ICH# 20

CLK_PCIE_SATA 19

CLK_PCIE_SATA# 19

VGA_27MHZ 43

VGA_27MHZSS 43

PEG_REFCLKP 41

PEG_REFCLKN 41

27_SEL PIN 20 PIN 21 PIN 24 PIN 25

0 DOT96T DOT96C SRCT1/LCDT_100 SRCT1/LCDT_100

1 SRCT0 SRCC0 27M_NSS 27M_SS

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Clock generator CY28548

Clock generator CY28548

Clock generator CY28548

2

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete SC

Pamirs-Discrete SC

Pamirs-Discrete SC

347Wednesday, September 12, 2007

347Wednesday, September 12, 2007

347Wednesday, September 12, 2007

1

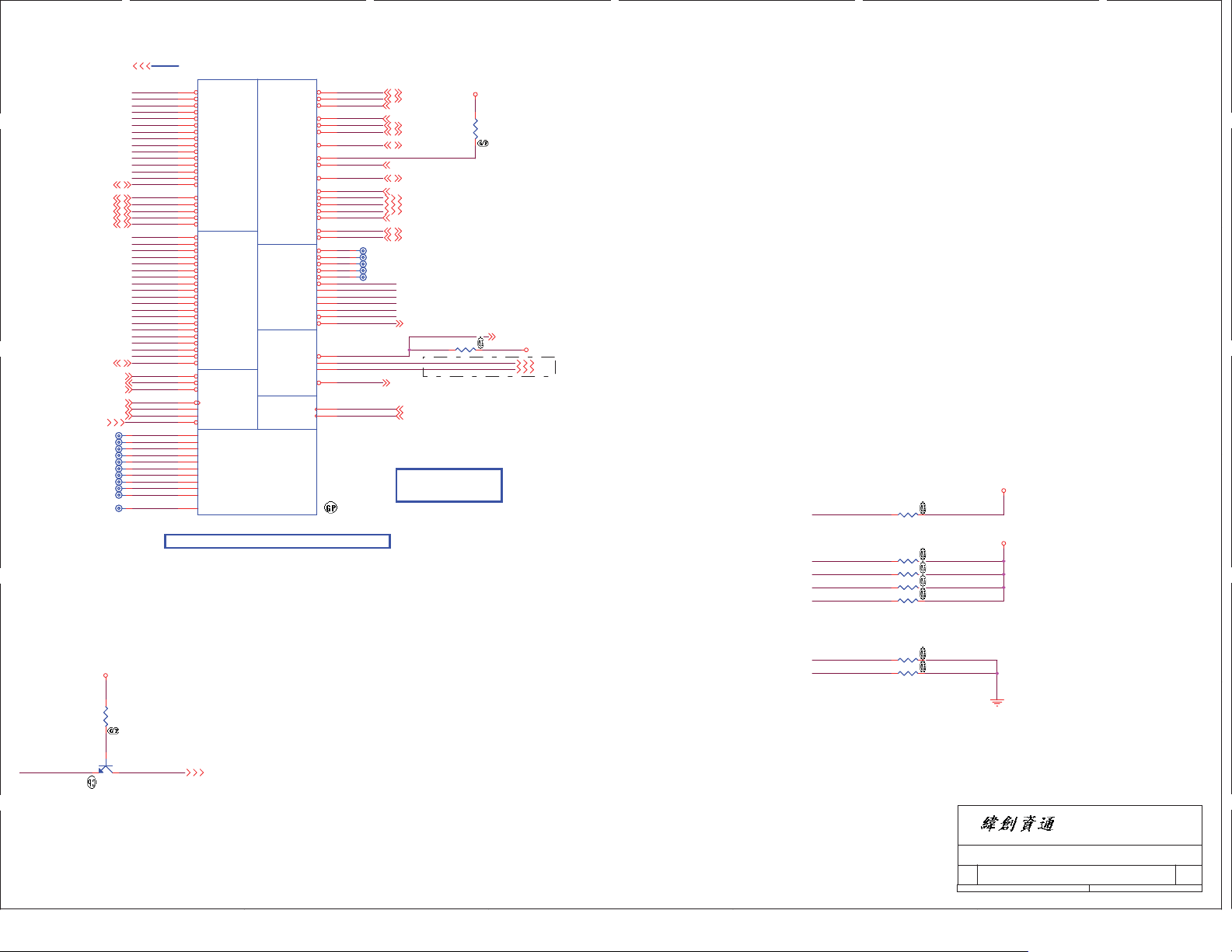

A

of

of

of

5

C

A

4

3

2

1

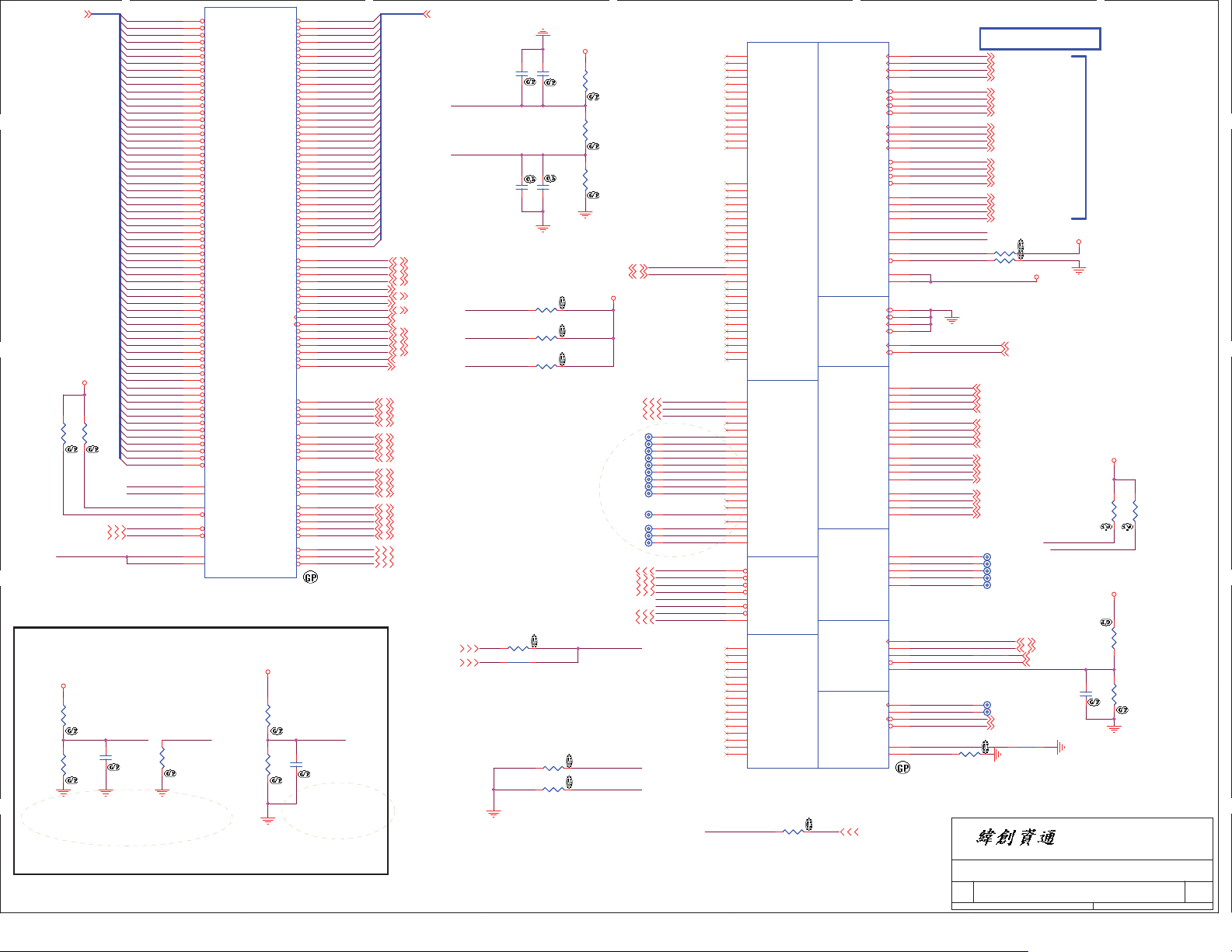

H_A#[3..35]7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

D D

H_ADSTB#07

H_REQ#07

H_REQ#17

H_REQ#27

H_REQ#37

H_REQ#47

C

H_ADSTB#17

H_A20M#19

H_FERR#19

H_IGNNE#19

H_STPCLK#19

H_INTR19

H_NMI19

H_SMI#19

TP13TPAD28 TP13TPAD28

TP16TPAD28 TP16TPAD28

TP7TPAD28 TP7TPAD28

TP9TPAD28 TP9TPAD28

TP5TPAD28 TP5TPAD28

TP10TPAD28 TP10TPAD28

TP6TPAD28 TP6TPAD28

TP18TPAD28 TP18TPAD28

TP8TPAD28 TP8TPAD28

TP17TPAD28 TP17TPAD28

TP4TPAD28 TP4TPAD28

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

CPU_RSVD01

CPU_RSVD02

CPU_RSVD03

CPU_RSVD04

CPU_RSVD05

CPU_RSVD06

CPU_RSVD07

CPU_RSVD08

CPU_RSVD09

CPU_RSVD10

CPU_RSVD11

B B

1 OF 4

1 OF 4

U62A

U62A

J4

A3#

L5

A4#

L4

A5#

K5

A6#

M3

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L2

A13#

P4

A14#

P1

A15#

R1

A16#

M1

ADSTB0#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L1

REQ4#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U1

A23#

R4

A24#

T5

A25#

T3

A26#

W2

A27#

W5

A28#

Y4

A29#

U2

A30#

V4

A31#

W3

A32#

AA4

A33#

AB2

A34#

AA3

A35#

V1

ADSTB1#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD#M4

N5

RSVD#N5

T2

RSVD#T2

V3

RSVD#V3

B2

RSVD#B2

C3

RSVD#C3

D2

RSVD#D2

D22

RSVD#D22

D3

RSVD#D3

F6

RSVD#F6

B1

KEY_NC

BGA479-SKT6-GPU3

BGA479-SKT6-GPU3

ADDR GROUP 0

ADDR GROUP 0

ADDR GROUP 1

ADDR GROUP 1

XDP/ITP SIGNALS CONTROL

XDP/ITP SIGNALS CONTROL

THERMAL

THERMAL

PROCHOT#

ICH

ICH

THERMTRIP#

HCLK

HCLK

RESERVED

RESERVED

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

THRMDA

THRMDC

BCLK0

BCLK1

TDI

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

XDP_DBRESET#

C20

D21

A24

B25

H_THERMTRIP#

C7

CLK_CPU_BCLK

A22

CLK_CPU_BCLK#

A21

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

H_IERR#

H_INIT#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_HIT#

H_HITM#

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

H_THERMDA

H_THERMDC

original value:BGA479-SKT6-GPU1

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

H_INIT# 19

H_LOCK# 7

H_RESET# 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

TP41 TPAD28TP41 TPAD28

TP108 TPAD28TP108 TPAD28

TP109 TPAD28TP109 TPAD28

TP110 TPAD28TP110 TPAD28

TP111 TPAD28TP111 TPAD28

XDP_DBRESET# 20

H_THERMTRIP# 7,19

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

layout note:Zo =55

ohm , 0.5" MAX for

GTLREF

H_RS#0 7

H_RS#1 7

H_RS#2 7

1 2

R164 68R3J-GPR164 68R3J-GP

1D05V_S0

12

R156

R156

56R2J-4-GP

56R2J-4-GP

CPU_PROCHOT# 35

1D05V_S0

H_THERMDA 22

H_THERMDC 22

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

layout note : Change R237 to 649 ohm if using XTP to ITP adapter

XDP_DBRESET#

XDP_TDI

XDP_TMS

XDP_TDO

XDP_BPM#5

R59

R59

1 2

1KR2J-1-GP

1KR2J-1-GP

1 2

R61 54D9R2F-L1-GPR61 54D9R2F-L1-GP

1 2

R60 54D9R2F-L1-GPR60 54D9R2F-L1-GP

1 2

R63 54D9R2F-L1-GPR63 54D9R2F-L1-GP

1 2

R89 54D9R2F-L1-GPR89 54D9R2F-L1-GP

3D3V_S0

1D05V_S0

CPU_PROCHOT#

1D05V_S0

12

DY

DY

CBE

MMBT3904WT1G-GP

MMBT3904WT1G-GP

R165

R165

56R2J-4-GP

56R2J-4-GP

DY

DY

Q10

Q10

5

OCP# 20

XDP_TRST#

XDP_TCK

http://hobi-elektronika.net

4

3

1 2

R58 51R2F-2-GPR58 51R2F-2-GP

1 2

R74 54D9R2F-L1-GPR74 54D9R2F-L1-GP

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Meron(1/3)-AGTL+/XDP

Meron(1/3)-AGTL+/XDP

Meron(1/3)-AGTL+/XDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete

Pamirs-Discrete

Pamirs-Discrete

4

4

4

of

of

of

1

A

SC

SC

SC

47Friday, September 14, 2007

47Friday, September 14, 2007

47Friday, September 14, 2007

5

A

4

3

2

1

H_D#[0..63]7

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

TP19TPAD28 TP19TPAD28

TP22TPAD28 TP22TPAD28

TP20TPAD28 TP20TPAD28

TP3TPAD28 TP3TPAD28

TP21TPAD28 TP21TPAD28

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

D D

H_DSTBN#07

H_DSTBP#07

H_DINV#07

C C

H_DSTBN#17

H_DSTBP#17

H_DINV#17

C296

C296

CPU_BSEL03

CPU_BSEL13

CPU_BSEL23

V_CPU_GTLREF

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1 2

DY

DY

PLACE C173 close to the TEST4 PIN,

make sure TEST3,TEST4,TEST5 trace

routing is reference to GND and

away other noisy signals

B B

CPU_BSEL CPU_BSEL2 CPU_BSEL1 CPU_BSEL0

166

200

0

00

1

U62B

U62B

E22

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL0

B23

BSEL1

C21

BSEL2

BGA479-SKT6-GPU3

BGA479-SKT6-GPU3

11

2 OF 4

2 OF 4

DATA GRP0 DATA GRP1

DATA GRP0 DATA GRP1

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

MISC

MISC

DPRSTP#

PWRGOOD

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPSLP#

DPWR#

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

COMP0

COMP1

R171 27D4R2F-L1-GPR171 27D4R2F-L1-GP

COMP2

R172 54D9R2F-L1-GPR172 54D9R2F-L1-GP

COMP3

R132 27D4R2F-L1-GPR132 27D4R2F-L1-GP

R131 54D9R2F-L1-GPR131 54D9R2F-L1-GP

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGOODH_PWRGOODH_PWRGOODH_PWRGOOD

H_CPUSLP#

PSI#

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#2 7

H_DSTBN#3 7

H_DSTBP#3 7

H_DINV#3 7

1 2

1 2

1 2

1 2

H_DPRSTP# 7,19

H_DPSLP# 19

H_DPWR# 7

H_PWRGOOD 19

H_CPUSLP# 7

PSI# 35

Resistor Placed

within 0.5" of CPU

pin. Trace should

be at least 25 mils

away from any other

toggling signal .

COMP[0,2] trace

width is 18 mils.

COMP[1,3] trace

width is 4 mils .

VCC_CORE_S0 VCC_CORE_S0

U62C

U62C

A7

VCC

A9

VCC

A10

VCC

A12

VCC

A13

VCC

A15

VCC

A17

VCC

A18

VCC

A20

VCC

B7

VCC

B9

VCC

B10

VCC

B12

VCC

B14

VCC

B15

VCC

B17

VCC

B18

VCC

B20

VCC

C9

VCC

C10

VCC

C12

VCC

C13

VCC

C15

VCC

C17

VCC

C18

VCC

D9

VCC

D10

VCC

D12

VCC

D14

VCC

D15

VCC

D17

VCC

D18

VCC

E7

VCC

E9

VCC

E10

VCC

E12

VCC

E13

VCC

E15

VCC

E17

VCC

E18

VCC

E20

VCC

F7

VCC

F9

VCC

F10

VCC

F12

VCC

F14

VCC

F15

VCC

F17

VCC

F18

VCC

F20

VCC

AA7

VCC

AA9

VCC

AA10

VCC

AA12

VCC

AA13

VCC

AA15

VCC

AA17

VCC

AA18

VCC

AA20

VCC

AB9

VCC

AC10

VCC

AB10

VCC

AB12

VCC

AB14

VCC

AB15

VCC

AB17

VCC

AB18

VCC

BGA479-SKT6-GPU3

BGA479-SKT6-GPU3

3 OF 4

3 OF 4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCA

VCCA

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

R155

R155

R146

R146

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

VCC_SENSE

VSS_SENSE

VCC_SENSE

VSS_SENSE

1 2

1 2

R142 100R2F-L1-GP-UR142 100R2F-L1-GP-U

Close to CPU pin

within 500mils

0R0402-PAD

0R0402-PAD

0R0402-PAD

0R0402-PAD

CPU_VID[0..6] 35

VCC_SENSE 35

VSS_SENSE 35

1 2

R143 100R2F-L1-GP-UR143 100R2F-L1-GP-U

1 2

1D05V_S0

TC7

TC7

SE330U2VDM-6-GP

SE330U2VDM-6-GP

12

DY

DY

1D5V_S0

C298

C298

12

12

VCC_CORE_S0

C303

C303

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

Length match within

25 mils . The trace

width/space/other is

20/7/25 .

layout note:

place C3 near

PIN B26

1D05V_S0

Close to CPU

pin AD26

Z0=55 ohm

with in

500mils .

5

R422

R422

1KR2F-3-GP

1KR2F-3-GP

1 2

V_CPU_GTLREF

12

R423

R423

2KR2F-3-GP

2KR2F-3-GP

C602

C602

12

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Meron(2/3)-AGTL+/PWR

Meron(2/3)-AGTL+/PWR

Meron(2/3)-AGTL+/PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

4

3

2

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete

Pamirs-Discrete

Pamirs-Discrete

5

5

5

1

of

of

of

A

SC

SC

SC

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

http://hobi-elektronika.net

5

A

4 OF 4

4 OF 4

U62D

U62D

A4

VSS

D D

C C

B B

A8

VSS

A11

VSS

A14

VSS

A16

VSS

A19

VSS

A23

VSS

AF2

VSS

B6

VSS

B8

VSS

B11

VSS

B13

VSS

B16

VSS

B19

VSS

B21

VSS

B24

VSS

C5

VSS

C8

VSS

C11

VSS

C14

VSS

C16

VSS

C19

VSS

C2

VSS

C22

VSS

C25

VSS

D1

VSS

D4

VSS

D8

VSS

D11

VSS

D13

VSS

D16

VSS

D19

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E11

VSS

E14

VSS

E16

VSS

E19

VSS

E21

VSS

E24

VSS

F5

VSS

F8

VSS

F11

VSS

F13

VSS

F16

VSS

F19

VSS

F2

VSS

F22

VSS

F25

VSS

G4

VSS

G1

VSS

G23

VSS

G26

VSS

H3

VSS

H6

VSS

H21

VSS

H24

VSS

J2

VSS

J5

VSS

J22

VSS

J25

VSS

K1

VSS

K4

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L21

VSS

L24

VSS

M2

VSS

M5

VSS

M22

VSS

M25

VSS

N1

VSS

N4

VSS

N23

VSS

N26

VSS

P3

VSS

BGA479-SKT6-GPU3

BGA479-SKT6-GPU3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

5

4

Place these capacitors on L1

(North side ,Secondary Layer)

Place these capacitors on L1

(North side ,Secondary Layer)

1D05V_S0

C249

C246

C246

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1 2

C249

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1 2

4

VCC_CORE_S0

VCC_CORE_S0

C247

C247

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1 2

3

C271

C271

C263

C263

C252

C252

12

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C281

C281

C275

C275

12

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C274

C274

C277

C277

C284

12

12

DY

DY

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C267

C267

C287

C287

12

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C284

12

12

DY

DY

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C269

C269

C278

C278

12

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

2

C288

C288

C286

C286

12

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C259

C259

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

1

Mid Frequencd

Decoupling

Place these

3

C293

C293

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1 2

C292

C292

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1 2

C291

C291

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

1 2

2

inside socket

cavity on L1

(North side

Secondary)

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Meron(3/3)-GND&Bypass

Meron(3/3)-GND&Bypass

Meron(3/3)-GND&Bypass

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete

Pamirs-Discrete

Pamirs-Discrete

1

A

SC

SC

SC

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

of

of

of

6

6

6

http://hobi-elektronika.net

A

1 OF 10

1 OF 10

U23A

12

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

M10

N12

N9

H5

P13

K9

M2

W10

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

AD12

AE3

AD9

AC9

AC7

AC14

AD11

AC11

AB2

AD7

AB1

Y3

AC6

AE2

AC5

AG3

AJ9

AH8

AJ14

AE9

AE11

AH12

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

AH13

B3

C2

W1

W2

B6

E5

B9

A9

H_RCOMP

R168

R168

24D9R2F-L-GP

24D9R2F-L-GP

U23A

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE-GP-U

CRESTLINE-GP-U

H_ADSTB#0

H_ADSTB#1

HOST

HOST

H_DEFER#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

1D05V_S0

R163

R163

100R2F-L1-GP-U

100R2F-L1-GP-U

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_BNR#

H_BPRI#

H_BREQ#

H_DBSY#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

12

12

R162

R162

221R2F-2-GP

221R2F-2-GP

12

4

H_A#3

J13

H_A#4

B11

H_A#5

C11

H_A#6

M11

H_A#7

C15

H_A#8

F16

H_A#9

L13

H_A#10

G17

H_A#11

C14

H_A#12

K16

H_A#13

B13

H_A#14

L16

H_A#15

J17

H_A#16

B14

H_A#17

K19

H_A#18

P15

H_A#19

R17

H_A#20

B16

H_A#21

H20

H_A#22

L19

H_A#23

D17

H_A#24

M17

H_A#25

N16

H_A#26

J19

H_A#27

B18

H_A#28

E19

H_A#29

B17

H_A#30

B15

H_A#31

E17

H_A#32

C18

H_A#33

A19

H_A#34

B19

H_A#35

N19

H_ADS#

G12

H_ADSTB#0

H17

H_ADSTB#1

G20

H_BNR#

C8

H_BPRI#

E8

H_BR0#

F12

H_DEFER#

D6

H_DBSY#

C10

CLK_MCH_BCLK

AM5

CLK_MCH_BCLK#

AM7

H_DPWR#

H8

H_DRDY#

K7

H_HIT#

E4

H_HITM#

C6

H_LOCK#

G10

H_TRDY#

B7

H_DINV#0

K5

H_DINV#1

L2

H_DINV#2

AD13

H_DINV#3

AE13

H_DSTBN#0

M7

H_DSTBN#1

K3

H_DSTBN#2

AD2

H_DSTBN#3

AH11

H_DSTBP#0

L7

H_DSTBP#1

K2

H_DSTBP#2

AC2

H_DSTBP#3

AJ10

H_REQ#0

M14

H_REQ#1

E13

H_REQ#2

A11

H_REQ#3

H13

H_REQ#4

B12

H_RS#0

E12

H_RS#1

D7

H_RS#2

D8

H_SWNGH_VREF

C295

C295

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

Layout Note :

Place C153 near

pin B3 of NB

H_A#[3..35] 4H_D#[0..63]5

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BR0# 4

H_DEFER# 4

H_DBSY# 4

CLK_MCH_BCLK 3

CLK_MCH_BCLK# 3

H_DPWR# 5

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

H_DINV#0 5

H_DINV#1 5

H_DINV#2 5

H_DINV#3 5

H_DSTBN#0 5

H_DSTBN#1 5

H_DSTBN#2 5

H_DSTBN#3 5

H_DSTBP#0 5

H_DSTBP#1 5

H_DSTBP#2 5

H_DSTBP#3 5

H_REQ#0 4

H_REQ#1 4

H_REQ#2 4

H_REQ#3 4

H_REQ#4 4

H_RS#0 4

H_RS#1 4

H_RS#2 4

PM_PWROK20,22

VGATE_PWRGD20,35

12

C253

SC2D2U10V3ZY-1GP

C253

SC2D2U10V3ZY-1GP

SM_RCOMP_VOH

SM_RCOMP_VOL

C270

C270

1 2

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

PM_EXTTS#0

PM_EXTTS#1

CLKREQ#_B

CFG[17:3] have internal pull up

CFG[19:18] have internal pull down

R407 10KR2J-3-GPR407 10KR2J-3-GP

R400 10KR2J-3-GPR400 10KR2J-3-GP

R399 10KR2J-3-GPR399 10KR2J-3-GP

From Astro demo schematic

0R2J-2-GP

0R2J-2-GP

DY

DY

R112

R112

1 2

1 2

R114 0R0402-PADR114 0R0402-PAD

R597 2K2R2J-2-GPR597 2K2R2J-2-GP

5

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

D D

C C

1D05V_S0

R179

R179

R178

R178

12

12

54D9R2F-L1-GP

54D9R2F-L1-GP

54D9R2F-L1-GP

54D9R2F-L1-GP

H_RESET#4

H_CPUSLP#5

H_VREF

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWNG

H_RCOMP

H_SCOMP

H_SCOMP#

H_RESET#

H_CPUSLP#

B B

layout note :

Route H_SCOMP and H_SCOMP# with trace width, spacing and impedance (55 ohm) same as FSB data traces

Layout Note :

H_RCOMP / H_VREF / H_SWNG

trace width and spacing is 10/20

1D05V_S0

12

R158

R158

1KR2F-3-GP

1KR2F-3-GP

12

R157

R157

2KR2F-3-GP

2KR2F-3-GP

Layout Note :

Place C151 within 100 mils of NB

12

C290

C290

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

http://hobi-elektronika.net

5

4

1D8V_S3

12

12

C257

C257

SCD01U25V2KX-3GP

SCD01U25V2KX-3GP

12

12

C266

C266

1 2

SCD01U25V2KX-3GP

SCD01U25V2KX-3GP

DDR_A_MA1413

DDR_B_MA1414

1 2

1 2

1 2

PM_BMBUSY#20

H_DPRSTP#5,19

PM_EXTTS#013

PM_EXTTS#114

H_THERMTRIP#4,19

DPRSLPVR20,35

1 2

1 2

R598 2K2R2J-2-GPR598 2K2R2J-2-GP

3

R147

R147

1KR2F-3-GP

1KR2F-3-GP

R148

R148

3K01R2F-3-GP

3K01R2F-3-GP

R149

R149

1KR2F-3-GP

1KR2F-3-GP

3D3V_S0

MCH_CLKSEL03

MCH_CLKSEL13

MCH_CLKSEL23

TP49TP49

TP54TP54

TP51TP51

TP55TP55

TP56TP56

TP48TP48

TP52TP52

TP50TP50

TP57TP57

TP53TP53

TP47TP47

TP46TP46

TP45TP45

PM_POK_R

CFG9

ICH_SDVO_DATA

3

DDR_A_MA14

DDR_B_MA14

MCH_CLKSEL0

MCH_CLKSEL1

MCH_CLKSEL2

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG16

CFG18

CFG19

CFG20

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PM_POK_R

PLT_RST_R#

H_THERMTRIP#

DPRSLPVR

P36

P37

R35

N35

AR12

AR13

AM12

AN13

J12

AR37

AM36

AL36

AM37

D20

H10

B51

BJ20

BK22

BF19

BH20

BK18

BJ18

BF23

BG23

BC23

BD24

BJ29

BE24

BH39

AW20

BK20

C48

D47

B44

C44

A35

B37

B36

B34

C34

P27

N27

N24

C21

C23

F23

N23

G23

J20

C20

R24

L23

J23

E23

E20

K23

M20

M24

L32

N33

L35

G41

L39

L36

J36

AW49

AV20

N20

G36

BJ51

BK51

BK50

BL50

BL49

BL3

BL2

BK1

BJ1

E1

A5

C51

B50

A50

A49

BK2

PLT_RST_R#

2 OF 10

2 OF 10

U23B

U23B

RSVD#P36

RSVD#P37

RSVD#R35

RSVD#N35

RSVD#AR12

RSVD#AR13

RSVD#AM12

RSVD#AN13

RSVD#J12

RSVD#AR37

RSVD#AM36

RSVD#AL36

RSVD#AM37

RSVD#D20

RSVD#H10

RSVD#B51

RSVD#BJ20

RSVD#BK22

RSVD#BF19

RSVD#BH20

RSVD#BK18

RSVD#BJ18

RSVD#BF23

RSVD#BG23

RSVD#BC23

RSVD#BD24

RSVD#BJ29

RSVD#BE24

RSVD#BH39

RSVD#AW20

RSVD#BK20

RSVD#C48

RSVD#D47

RSVD#B44

RSVD#C44

RSVD#A35

RSVD#B37

RSVD#B36

RSVD#B34

RSVD#C34

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PM_BM_BUSY#

PM_DPRSTP#

PM_EXT_TS#0

PM_EXT_TS#1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC#BJ51

NC#BK51

NC#BK50

NC#BL50

NC#BL49

NC#BL3

NC#BL2

NC#BK1

NC#BJ1

NC#E1

NC#A5

NC#C51

NC#B50

NC#A50

NC#A49

NC#BK2

CRESTLINE-GP-U

CRESTLINE-GP-U

1 2

RSVD

RSVD

CFG PM NC

CFG PM NC

R414

R414

100R2J-2-GP

100R2J-2-GP

2

SM_CK0

SM_CK1

SM_CK3

SM_CK4

SM_CK#0

SM_CK#1

SM_CK#3

SM_CK#4

SM_CKE0

SM_CKE1

SM_CKE3

SM_CKE4

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

DDR MUXING

DDR MUXING

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_RCOMP

SM_RCOMP#

SM_VREF#AR49

SM_VREF#AW4

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

CLK

CLK

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI

DMI

DMI_RXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLKREQ#

ICH_SYNC#

TEST1

TEST2

MISC ME GRAPHICS VID

MISC ME GRAPHICS VID

PLT_RST1# 18,20,26,28,31,33,34,41

2

M_CLK_DDR0

AV29

M_CLK_DDR1

BB23

M_CLK_DDR2

BA25

M_CLK_DDR3

AV23

M_CLK_DDR#0

AW30

M_CLK_DDR#1

BA23

M_CLK_DDR#2

AW25

M_CLK_DDR#3

AW23

DDR_CKE0_DIMMA

BE29

DDR_CKE1_DIMMA

AY32

DDR_CKE2_DIMMB

BD39

DDR_CKE3_DIMMB

BG37

DDR_CS0_DIMMA#

BG20

DDR_CS1_DIMMA#

BK16

DDR_CS2_DIMMB#

BG16

DDR_CS3_DIMMB#

BE13

M_ODT0

BH18

M_ODT1

BJ15

M_ODT2

BJ14

M_ODT3

BE16

SM_RCOMP_VOH

BK31

SM_RCOMP_VOL

BL31

SM_RCOMP

BL15

SM_RCOMP#

BK14

AR49

AW4

B42

C42

H48

H47

CLK_MCH_3GPLL

K44

CLK_MCH_3GPLL#

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

DFGT_VID0

E35

DFGT_VID1

A39

DFGT_VID2

C38

DFGT_VID3

B39

DFGT_VR_EN

E36

AM49

AK50

CLPWROK_MCH

AT43

AN49

CL_VREF

AM50

H35

K36

G39

MCH_ICH_SYNC#

G40

TEST1_GMCH

A37

TEST2_GMCH

R32

1

FOR Calero: 80.6 ohm

Crestline: 20 ohm

M_CLK_DDR0 13

M_CLK_DDR1 13

M_CLK_DDR2 14

M_CLK_DDR3 14

M_CLK_DDR#0 13

M_CLK_DDR#1 13

M_CLK_DDR#2 14

M_CLK_DDR#3 14

DDR_CKE0_DIMMA 13

DDR_CKE1_DIMMA 13

DDR_CKE2_DIMMB 14

DDR_CKE3_DIMMB 14

DDR_CS0_DIMMA# 13

DDR_CS1_DIMMA# 13

DDR_CS2_DIMMB# 14

DDR_CS3_DIMMB# 14

M_ODT0 13

M_ODT1 13

M_ODT2 14

M_ODT3 14

1D8V_S3

1 2

R154 20R2F-GPR154 20R2F-GP

1 2

R413 20R2F-GPR413 20R2F-GP

DDR_VREF_S3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

ICH_SDVO_CLK

ICH_SDVO_DATA

1 2

R406

R406

20KR2J-L2-GP

20KR2J-L2-GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DDR_VREF_S3

CLK_MCH_3GPLL 3

CLK_MCH_3GPLL# 3

DMI_TXN0 20

DMI_TXN1 20

DMI_TXN2 20

DMI_TXN3 20

DMI_TXP0 20

DMI_TXP1 20

DMI_TXP2 20

DMI_TXP3 20

DMI_RXN0 20

DMI_RXN1 20

DMI_RXN2 20

DMI_RXN3 20

DMI_RXP0 20

DMI_RXP1 20

DMI_RXP2 20

DMI_RXP3 20

ICH_SDVO_DATA

TP44TP44

TP11TP11

TP15TP15

TP12TP12

TP14TP14

1 2

R410 0R0402-PADR410 0R0402-PAD

TP43TP43

TP42TP42

CLKREQ#_B 3

MCH_ICH_SYNC# 20

1 2

CRESTLINE(1/6)-AGTL+/DMI/DDR2

CRESTLINE(1/6)-AGTL+/DMI/DDR2

CRESTLINE(1/6)-AGTL+/DMI/DDR2

ICH_SDVO_CLK

CL_CLK0 20

CL_DATA0 20

VGATE_PWRGD 20,35

CL_RST# 20

R144 0R0402-PADR144 0R0402-PAD

Pamirs-Discrete

Pamirs-Discrete

Pamirs-Discrete

2D5V_S0

12

R401

R401

2K2R2J-2-GP

2K2R2J-2-GP

DY

DY

1D25V_S0

R115

R115

1KR2F-3-GP

1KR2F-3-GP

1 2

12

12

R116

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

R116

392R2F-GP

392R2F-GP

7

7

7

C193

C193

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

1

12

R402

R402

2K2R2J-2-GP

2K2R2J-2-GP

DY

DY

of

of

of

A

SA

SA

SA

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

5

A

4

3

2

1

DDR_A_D[0..63] 13

DDR_A_BS[0..2] 13

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_RAS#

SA_WE#

DDR_A_DM[0..7] 13

DDR_A_DQS[0..7] 13

DDR_A_DQS#[0..7] 13

DDR_A_MA[0..13] 13

DDR_A_BS0

BB19

DDR_A_BS1

BK19

DDR_A_BS2

BF29

DDR_A_CAS#

BL17

DDR_A_DM0

AT45

DDR_A_DM1

BD44

DDR_A_DM2

BD42

DDR_A_DM3

AW38

DDR_A_DM4

AW13

DDR_A_DM5

BG8

DDR_A_DM6

AY5

DDR_A_DM7

AN6

DDR_A_DQS0

AT46

DDR_A_DQS1

BE48

DDR_A_DQS2

BB43

DDR_A_DQS3

BC37

DDR_A_DQS4

BB16

DDR_A_DQS5

BH6

DDR_A_DQS6

BB2

DDR_A_DQS7

AP3

DDR_A_DQS#0

AT47

DDR_A_DQS#1

BD47

DDR_A_DQS#2

BC41

DDR_A_DQS#3

BA37

DDR_A_DQS#4

BA16

DDR_A_DQS#5

BH7

DDR_A_DQS#6

BC1

DDR_A_DQS#7

AP2

DDR_A_MA0

BJ19

DDR_A_MA1

BD20

DDR_A_MA2

BK27

DDR_A_MA3

BH28

DDR_A_MA4

BL24

DDR_A_MA5

BK28

DDR_A_MA6

BJ27

DDR_A_MA7

BJ25

DDR_A_MA8

BL28

DDR_A_MA9

BA28

DDR_A_MA10

BC19

DDR_A_MA11

BE28

DDR_A_MA12

BG30

DDR_A_MA13

BJ16

DDR_A_RAS#

BE18

SA_RCVEN#

AY20

DDR_A_WE#

BA19

5 OF 10

5 OF 10

U23E

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_A_CAS# 13 DDR_B_CAS# 14

DDR_A_RAS# 13

TP58TP58

DDR_A_WE# 13

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BK10

BH5

BG1

BC2

BD3

AR1

AU2

BL9

BK5

BL5

BK9

BJ8

BJ6

BF4

BK3

BE4

BJ2

BA3

BB3

AT3

AY2

AY3

AT2

U23E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

CRESTLINE-GP-U

CRESTLINE-GP-U

D D

4 OF 10

4 OF 10

U23D

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

C C

B B

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BD8

AY9

BG10

AW9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AN10

AT9

AN9

AM9

AN11

U23D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

CRESTLINE-GP-U

CRESTLINE-GP-U

DDR SYSTEM MEMORRY A

DDR SYSTEM MEMORRY A

SA_RCVEN#

DDR_B_D[0..63] 14

DDR_B_BS[0..2] 14

DDR_B_DM[0..7] 14

DDR_B_DQS[0..7] 14

DDR_B_DQS#[0..7] 14

DDR_B_MA[0..13] 14

DDR_B_BS0

AY17

SB_BS0

SB_BS1

SB_BS2

SB_CAS#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_RAS#

SB_RCVEN#

SB_WE#

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

DDR_B_BS1

DDR_B_BS2

DDR_B_CAS#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_RAS#

SB_RCVEN#

DDR_B_WE#

DDR_B_RAS# 14

TP59TP59

DDR_B_WE# 14

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CRESTLINE(2/6)-DDR2 A/B CH

CRESTLINE(2/6)-DDR2 A/B CH

CRESTLINE(2/6)-DDR2 A/B CH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete

Pamirs-Discrete

Pamirs-Discrete

8

8

8

1

of

of

of

A

SA

SA

SA

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

47Wednesday, September 12, 2007

http://hobi-elektronika.net

5

A

3 OF 10

3 OF 10

U23C

U23C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

D D

C C

B B

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#0

E51

LVDSA_DATA#1

F49

LVDSA_DATA#2

G50

LVDSA_DATA0

E50

LVDSA_DATA1

F48

LVDSA_DATA2

G44

LVDSB_DATA#0

B47

LVDSB_DATA#1

B45

LVDSB_DATA#2

E44

LVDSB_DATA0

A47

LVDSB_DATA1

A45

LVDSB_DATA2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL0

P33

TV_DCONSEL1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

E33

CRT_VSYNC

C32

CRT_TVO_IREF

F33

CRT_HSYNC

CRESTLINE-GP-U

CRESTLINE-GP-U

PEG_COMPI

PEG_COMPO

LVDS

LVDS

TV VGA

TV VGA

PCI_EXPRESS GRAPHICS

PCI_EXPRESS GRAPHICS

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

4

1D05V_S0

N43

M43

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

1 2

R398 24D9R2F-L-GPR398 24D9R2F-L-GP

PEGCOMP

PEG_RXP15 41

PEG_RXP14 41

PEG_RXP13 41

PEG_RXP12 41

PEG_RXP11 41

PEG_RXP10 41

PEG_RXP9 41

PEG_RXP8 41

PEG_RXP7 41

PEG_RXP6 41

PEG_RXP5 41

PEG_RXP4 41

PEG_RXP3 41

PEG_RXP2 41

PEG_RXP1 41

PEG_RXP0 41

PEG_RXN15 41

PEG_RXN14 41

PEG_RXN13 41

PEG_RXN12 41

PEG_RXN11 41

PEG_RXN10 41

PEG_RXN9 41

PEG_RXN8 41

PEG_RXN7 41

PEG_RXN6 41

PEG_RXN5 41

PEG_RXN4 41

PEG_RXN3 41

PEG_RXN2 41

PEG_RXN1 41

TXN0

TXN1

TXN2

TXN3

TXN4

TXN5

TXN6

TXN7

TXN8

TXN9

TXN10

TXN11

TXN12

TXN13

TXN14

TXN15

TXP0

TXP1

TXP2

TXP3

TXP4

TXP5

TXP6

TXP7

TXP8

TXP9

TXP10

TXP11

TXP12

TXP13

TXP14

TXP15

PEG_RXN0 41

1 2

C489 SCD1U10V2KX-5GPC489 SCD1U10V2KX-5GP

1 2

C506 SCD1U10V2KX-5GPC506 SCD1U10V2KX-5GP

1 2

C480 SCD1U10V2KX-5GPC480 SCD1U10V2KX-5GP

1 2

C195 SCD1U10V2KX-5GPC195 SCD1U10V2KX-5GP

1 2

C196 SCD1U10V2KX-5GPC196 SCD1U10V2KX-5GP

1 2

C502 SCD1U10V2KX-5GPC502 SCD1U10V2KX-5GP

1 2

C499 SCD1U10V2KX-5GPC499 SCD1U10V2KX-5GP

1 2