HP ProLiant DL370 G6, ProLiant ML350 G6 Introduction Manual

Technology and architecture of HP ProLiant Intelbased 300–series G6 (Generation 6) servers

Technology brief

Abstract.............................................................................................................................................. 3

Introduction......................................................................................................................................... 3

Intel Xeon 5500 Series processor technology .......................................................................................... 3

Multi-level caches............................................................................................................................. 3

Integrated memory controller ............................................................................................................. 4

QuickPath Interconnect controller ....................................................................................................... 4

Hyper Threading.............................................................................................................................. 5

Turbo Boost technology..................................................................................................................... 6

Memory.............................................................................................................................................. 6

DDR-3............................................................................................................................................. 6

DIMM Choices............................................................................................................................. 7

Memory Mirroring with DDR3........................................................................................................ 8

Memory channel interleaving......................................................................................................... 9

I/O technologies ................................................................................................................................. 9

PCI Express technology..................................................................................................................... 9

HP Smart Array and SAS/SATA technology ...................................................................................... 10

SAS-2 ....................................................................................................................................... 10

New generation HP Smart Array controllers .................................................................................. 11

Battery backed write cache ......................................................................................................... 11

Zero Memory RAID..................................................................................................................... 11

Smart Array Advanced Pack (SAAP) ............................................................................................. 11

Software RAID ........................................................................................................................... 12

Networking technologies ................................................................................................................ 12

Power and thermal technologies .......................................................................................................... 13

Efficient power delivery................................................................................................................... 13

Common slot power supplies ....................................................................................................... 13

Increasing power efficiency in redundant power operation.............................................................. 14

Voltage regulation...................................................................................................................... 14

Improved thermal sensors and fan control ......................................................................................... 14

Dynamic Power Capping ................................................................................................................ 15

Phase shedding ............................................................................................................................. 16

Phase shedding based on the installed processor ........................................................................... 16

Memory phase shedding............................................................................................................. 16

Dynamic CPU phase shedding..................................................................................................... 17

Managing processor technologies.................................................................................................... 17

QuickPath Interconnect power...................................................................................................... 17

Disabling processor cores............................................................................................................ 17

Minimum processor idle power state............................................................................................. 17

Managing memory technologies ...................................................................................................... 17

Memory channel interleaving....................................................................................................... 17

Maximum memory data rates.......................................................................................................17

Managing I/O technologies............................................................................................................ 18

Disable PCIe 2.0........................................................................................................................ 18

I/O Power Provisioning............................................................................................................... 18

Power profiles................................................................................................................................ 18

Power Performance Benchmarks .......................................................................................................... 18

Security ............................................................................................................................................ 19

Trusted Platform Module.................................................................................................................. 19

BitLocker Drive Encryption ............................................................................................................... 19

Systems management and monitoring .................................................................................................. 19

HP Insight Control Environment ........................................................................................................ 20

HP Insight Dynamics – VSE.............................................................................................................. 20

HP ProLiant Onboard Administrator powered by iLO 2....................................................................... 20

OS support ....................................................................................................................................... 20

Summary .......................................................................................................................................... 20

For more information.......................................................................................................................... 21

Call to action .................................................................................................................................... 22

Abstract

This technology brief describes the key technologies implemented in Intel-based HP ProLiant 300-series

G6 servers.

Introduction

HP ProLiant 300-series G6 servers have been the focus of extensive engineering and development.

Characterized by increased performance, better power efficiency, and more powerful management

tools, the servers include these new technologies:

• The Intel® Xeon® Processor 5500 Series

• Double Data Rate-3 (DDR-3) DIMMs

• Thermal sensors incorporated throughout the ProLiant 300-series G6 servers

• The ProLiant Onboard Administrator powered by Integrated Lights-Out 2 (iLO 2) that delivers power

and temperature management through multiple sensors and fan control

• Dynamic Power Capping that limits peak power consumption without impacting performance and

without risk of overloading data center branch circuits

• Input/output (I/O) technologies such as PCIe generation 2 (PCIe 2.0) and faster Smart Array

controllers that incorporate common form factor components

• ”Right Size” common slot power supplies in multiple sizes to provide the required amount of power

and improve power efficiency

The technologies discussed in this paper are implemented in all Intel-based ProLiant 300-series G6

servers. Exceptions are noted where different levels of technology implementation or service exist

among individual ProLiant 300-series G6 platforms.

For complete specifications of all ProLiant 300-series servers, see the HP website:

www.hp.com/products/servers/platforms

.

Intel Xeon 5500 Series processor technology

ProLiant Intel-based 300-series G6 servers contain the Xeon 5500 Series processors. The Xeon 5500

Series microarchitecture is built on hafnium-based, 45 nanometer, high-k metal gate silicon

technology. Xeon 5500 Series processors use a new material combination of high-k gate dielectrics

and conductors which reduce electrical leakage—enabling smaller, more energy-efficient, and higher

performance processors. This new silicon technology, along with technologies such as distributed

shared memory, simultaneous multi-threading, Turbo Boost, and dynamic power management,

represent the technological heart of the HP ProLiant G6 servers.

Multi-level caches

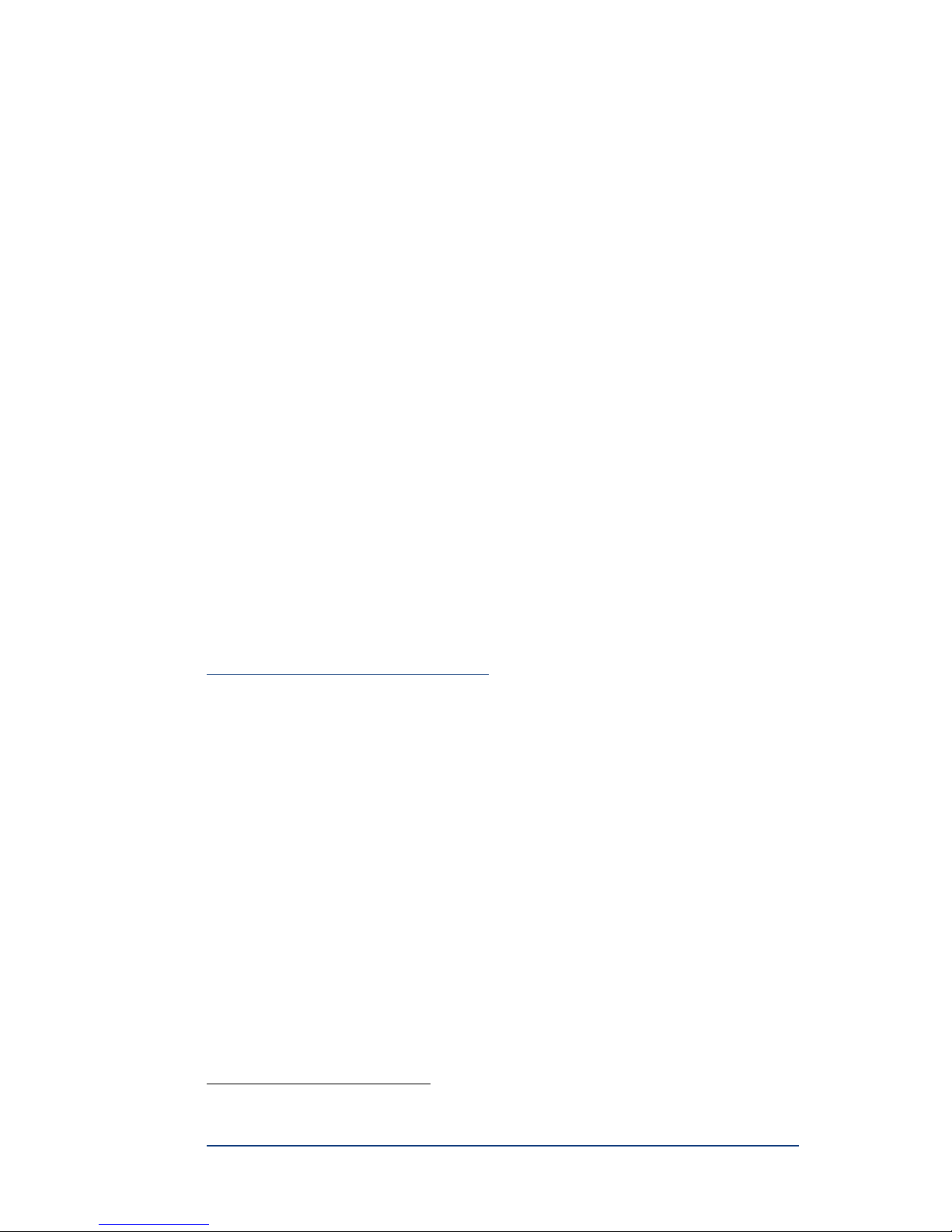

Xeon 5500 Series processors have a three-level cache hierarchy (Figure 1):

• An on-core 64-kilobyte Level 1 cache, split into two 32 kilobyte caches: one for data and one for

instructions

• 256-kilobyte, Level 2 cache for each core to reduce latency

• A Level 3 cache of up to 8 megabytes shared by all cores

1

For additional information about Intel processors, see the HP technology brief titled “The Intel processor

roadmap for industry-standard servers”:

http://h20000.www2.hp.com/bc/docs

/support/SupportManual/c00164255/c00164255.pdf.

1

3

Figure 1. Block diagram of three-level cache hierarchy for Intel Xeon 5500 Series processors

The Level 3 cache is shared and inclusive, which means that it du

1 and Level 2 caches of each core. This guarantees that data is stored outside the cores and

minimizes latency by eliminating unnecessary core snoops to the Level 1 and Level 2 caches. Flags in

the Level 3 cache track which core’s cache supplied the original data. Therefore, if one core modifies

another core’s data in Level 3 cache, the Level 1 and Level 2 caches are updated as well. This

eliminates excessive inter-core traffic and ensures multi-level cache coherency.

plicates the data stored in the Level

Integrated memory controller

Instead of sharing a single pool of system memory, each processor accesses its own dedicated DDR-3

system memory directly through an integrated memory controller. Three memory channels from each

memory controller to its dedicated memory provide a total bandwidth of 32 gigabytes per second.

The three memory channels eliminate the bottleneck associated with earlier processor architectures in

which all system memory access took place through a single memory controller over the front side

bus. In cases in which a processor needs to access the memory of another processor, it can do so

through the QuickPath Interconnect.

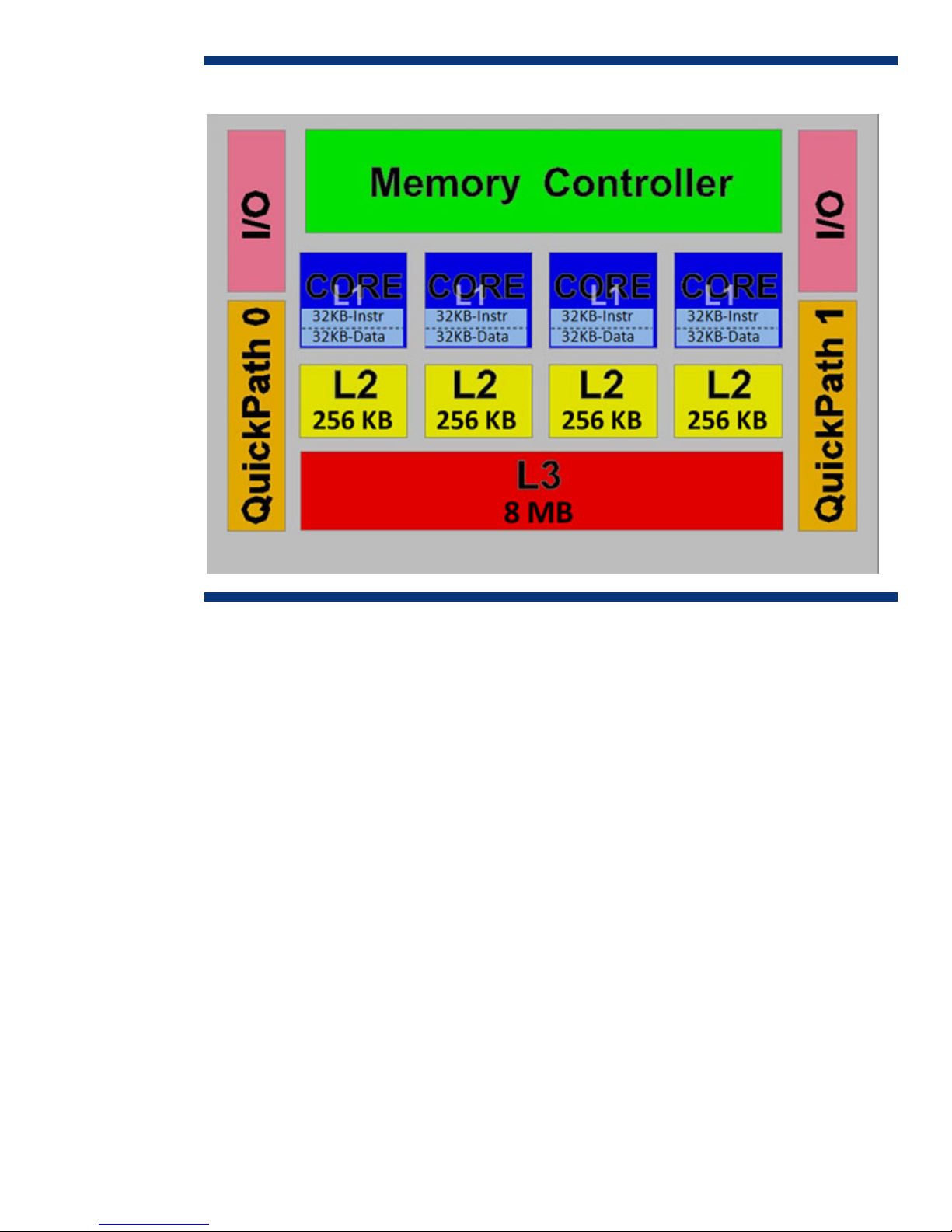

QuickPath Interconnect controller

Xeon 5500 Series processors attain their performance potential through the Intel QuickPath

Architecture (Figure 2): high-speed, point-to-point interconnects directly connect the processors. The

Intel QuickPath Architecture also connects each processor to distributed shared memory and to the

I/O chipset.

Each QuickPath Interconnect consists of two unidirectional links that operate simultaneously in each

direction using differential signaling. Unlike a typical serial bus, the QuickPath interconnects transmit

data packets in parallel across multiple lanes and packets are broken into multiple parallel transfers.

4

Each link is comprised of twenty 1-bit lanes. A maximum of 16 bits are used to transfer data; the

remaining 4 bits are used for the protocol and error correction. The interconnect performs a maximum

of 6.4 gigatransfers per second and has a bandwidth of 12.8-gigabytes per second in each

direction, for a total bandwidth of 25.6 gigabytes per second.

If an application requests data from the memory of another processor, the QuickPath interconnect

uses high-bandwidth inter-processor communication to retrieve the data.

Figure 2. Block diagram of QuickPath architecture

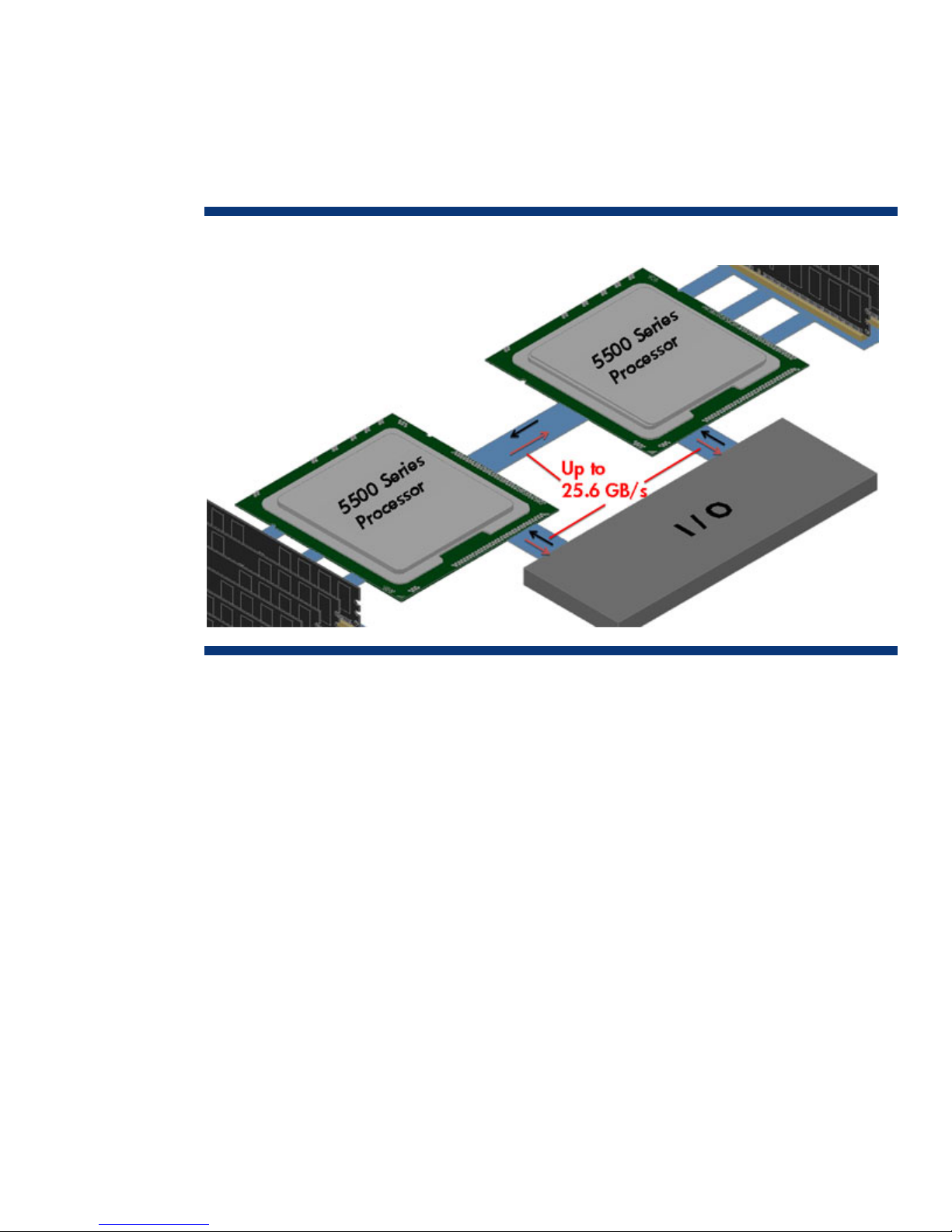

Hyper Threading

Simultaneous Multi-threading Technology, or SMT, is an enhanced version of Intel’s Hyper-Threading

Technology. SMT lets each core execute two computational threads at the same time. A single

processor can execute up to eight threads simultaneously (Figure 3). Compared to the previous Intel

core architecture, the high-bandwidth memory subsystem supplies data faster to the two computational

processes, and the low-latency cache hierarchy allows more instructions to be processed

simultaneously.

5

Figure 3. Diagram representing SMT technology in the 5500 Series processor

Incorporating simultaneous multithreading improves p

power cost, improving performance per watt (W), and allowing ProLiant G6 servers to do more using

the same—or less—power as previous-generation, Intel processor-based servers.

erformance at a proportionately small additional

Turbo Boost technology

Intel’s Turbo Boost technology complements Simultaneous Multi-threading Technology by increasing

the performance of both multi-threaded and single-threaded workloads. For workloads and

applications that do not benefit from multi-threading, Turbo Boost technology can provide better

performance. Turbo Boost is engaged by default and automatically increases the clock frequency of

active cores operating below power and thermal design points determined by the processor. The

maximum frequency depends on the number of active cores and varies based on the specific

configuration on a per-processor-number basis. Turbo Boost technology is operating system

independent and operating systems that are Advanced Configuration and Power Interface-aware

(ACPI) require no changes to support Turbo Boost technology.

Memory

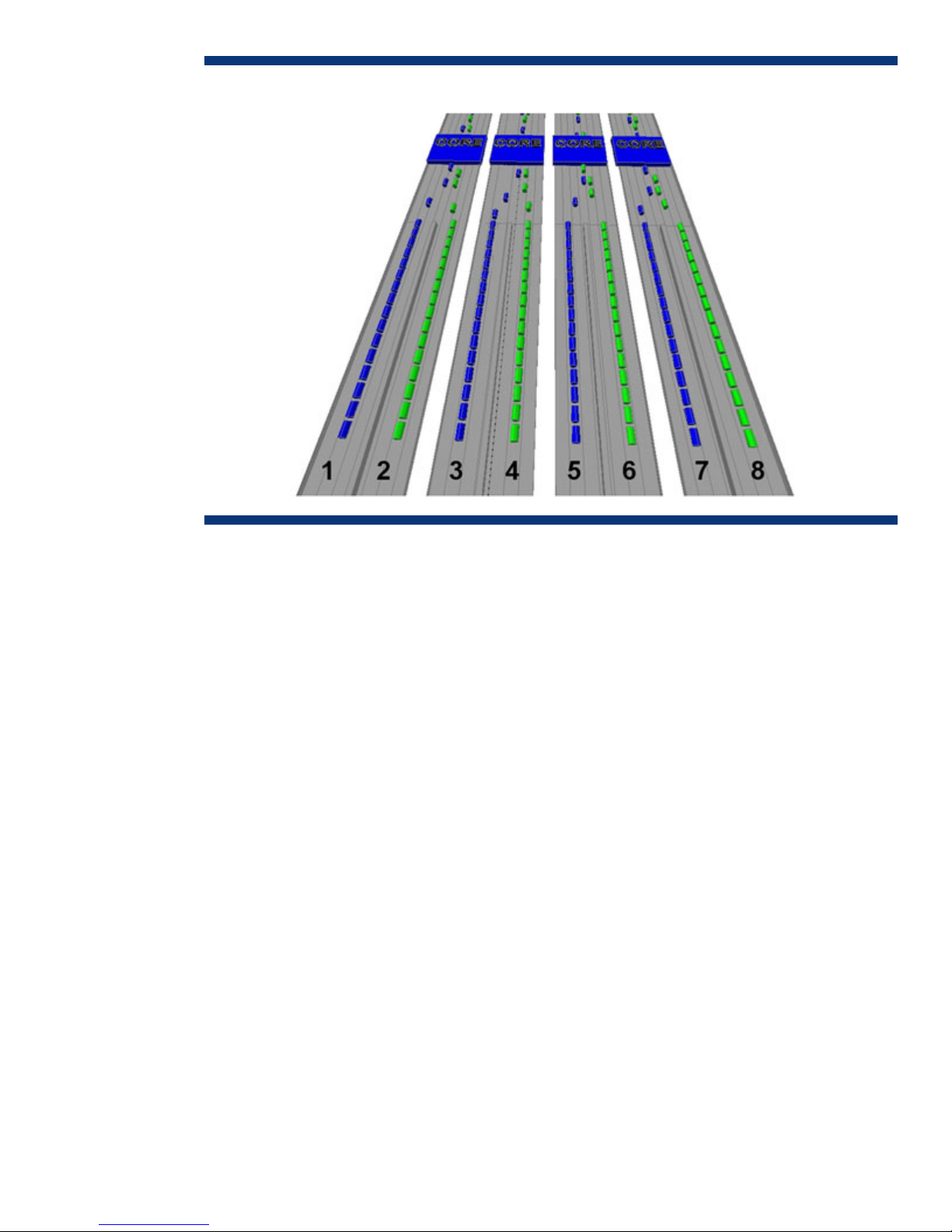

The Xeon 5500 Series processor connects directly to memory rather than through a chipset. The Xeon

5500 Series processor supports only DDR-3 dual inline memory modules (DIMMs). DDR-3 is part of

the synchronous dynamic random access memory (SDRAM) group of technologies. HP manages all

processor functionality options through the G6 server Basic Input/Output System (BIOS) and ROM

Based Setup Utility (RBSU). These options include Memory Mirroring and are discussed later in this

section.

DDR-3

DDR-3 has several key enhancements including an 8-bit prefetch buffer for storing data before it is

requested. By comparison, DDR-2 has a 4-bit buffer. For DDR-3, the data signal rate can increase to

6

1333 Megatransfers per second (MT/s). While this is commonly referred to as having a speed of

1333 MHz, the maximum clock speed for the DIMMs is actually 667 MHz and the signal is doublepumped to achieve the data rate of 1333 MT/s. DDR3-1333 DIMMs can operate at clock speeds of

667 MHz, 533 MHz and 400 MHz; with corresponding data rates of 1333, 1066, and 800 MT/s.

The three memory channels between the processor’s integrated memory controller and the dedicated

DDR-3 memory provide a total bandwidth of 32 gigabytes per second.

Energy efficiency is improved over previous generations. HP DDR-3 DIMM modules incorporate an

integrated thermal sensor that signals the chipset to throttle memory traffic to the DIMM if its

temperature exceeds a programmable critical trip point. By using the data from these thermal sensors,

the ProLiant G6 servers can reduce fan speed and therefore reduce power consumption when

memory is idle. Some third-party DIMMs may not include this DIMM thermal sensor. The BIOS in

ProLiant G6 servers verifies the presence of the thermal DIMM sensor during POST. If the thermal

sensor is absent, a POST message will warn that the DIMM does not have a thermal sensor, and the

fans will be forced to run at higher speed (requiring more power).

Operating voltage for DDR-3 has been reduced. DDR-2 operates at 1.8V, while DDR-3 currently

operates at 1.5V, consuming less power than DDR-2 DIMMs at the same capacity and speed. DDR-3

DIMMs have the same number of pins and are the same physical size as DDR-2 DIMMs, but they are

electrically incompatible and have a different key notch location.

DIMM Choices

DDR

-3 is available as both Unbuffered Dual In-line Memory Modules (UDIMMs) and Registered

(buffered) Dual In-line Memory Modules (RDIMMs). Both RDIMMs and UDIMMs support error

correcting code (ECC).

There are three types of DDR-3 available for ProLiant G6 servers:

• PC3-8500R (RDIMM, ECC compliant) —1066 or 800 MT/s data rate, depending on memory

configuration and processor installed.

• PC3-10600E (UDIMM, ECC compliant) —1333, 1066 or 800 MT/s data rate, depending on

memory configuration and processor installed

• PC3-10600R (RDIMM, ECC compliant) —1333, 1066 or 800 MT/s data rate, depending on

memory configuration and processor installed.

Administrators can configure ProLiant 300-series G6 servers using either RDIMMs or UDIMMs,

although RDIMM and UDIMM memory cannot be mixed within a single server. ProLiant 300-series

G6 servers have up to 18 DIMM slots, allowing larger memory capacities than with the platforms that

used DDR-2. ProLiant G6 servers optimize memory performance by operating DDR-3 memory at the

maximum rate possible, based on the memory configuration and processor installed.

When choosing memory configurations for 300-series G6 systems, the following guidelines should

prove helpful:

• UDIMM configurations are limited to a maximum of two UDIMMs per memory channel because the

memory controller must drive the address and command signals to each DRAM chip on a channel.

This results in a 24 GB maximum configuration in ProLiant 300-series G6 servers. Because they

require fewer components, UDIMMs are typically less expensive than RDIMMs.

• RDIMM configurations can provide larger memory capacity configuration because the memory

controller only drives the address and command signals to a single register chip, thereby reducing

the electrical load on the memory controller. Users requiring large memory footprints can install

three 8-GB RDIMMs per channel for a total of 144 GB.

• For smaller memory configurations, installing only one or two DIMMs per memory channel can

potentially increase memory performance. In many instances this allows administrators to clock the

memory channel at a higher data rate.

7

Loading...

Loading...