A

1 1

B

C D

E

Compal Confidential

2 2

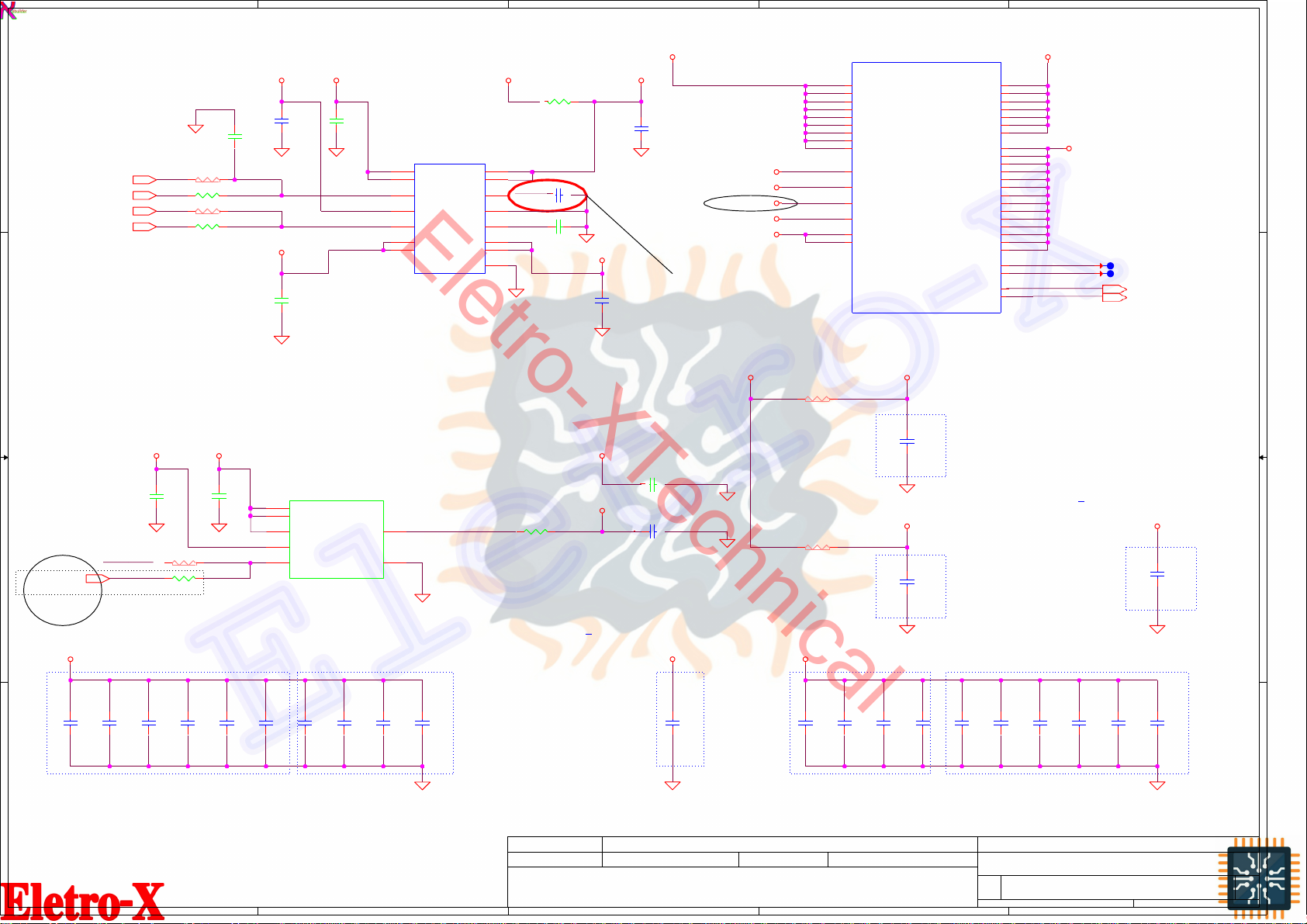

Intel M/B Schematics Document

Kabylake-U(2+2)-DDR4 SODIMMx2

nVidia N16 gDDR5-2GB

(N16S-GTR : GM108-670/770: GeForce MX130)

(N16V-GMR1 : GM108-626/726:GeForce MX110)

3 3

Project :2018OPP_Harry Potter(15.6")

EPK52 :LA-G07DP

Date : 2018-01-08

Version : 1.0

4 4

(Modified&Ref from:

01."NFLC_KBLR_LAE802PR10_MV_FINAL")

(02."Canadiens_LA-F035P-R10_KBL-UR_2017-06-23_CPU)

(02."CNL-U ORB_DDX02_LA-F152PR01_0822B")

A

B

Security Classification

Issued Date

THIS SHEET OF ENGI NEERING DRAW ING IS T HE PROPRI ET ARY PROPER TY OF C OMPAL ELECTRONIC S, INC. AND CONTAINS CONFIDENSTiIzAeL

AND TR ADE S EC RET INFORMATI ON. T HIS SHEET MAY NO T BE TR AN SFERE D FR OM TH E CU ST OD Y OF T HE COMPE TENT D IVISION OF R&D

DEPAR TM ENT EXCEPT A S AUTHORI ZED BY COMPA L ELE CTR ONI CS, INC . N EITHER T HIS S HEET NO R TH E INFOR MATION IT CO NTA INS

MAY BE U SE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PR IOR WRIT TE N C ON SENT OF CO MPAL ELECT RONICS, INC.

2015/10/22 2017/10/22

C D

Compal Secret Data

Deciphered Date

Custom

Date: Monday, January 08, 2018 Sheet

Title

DocumentNumber

Compal Electronics,Inc.

Cover Page

EPK52_LA-G07EP

E

1 of 59

Rev

v0.3

A

B

C

D

E

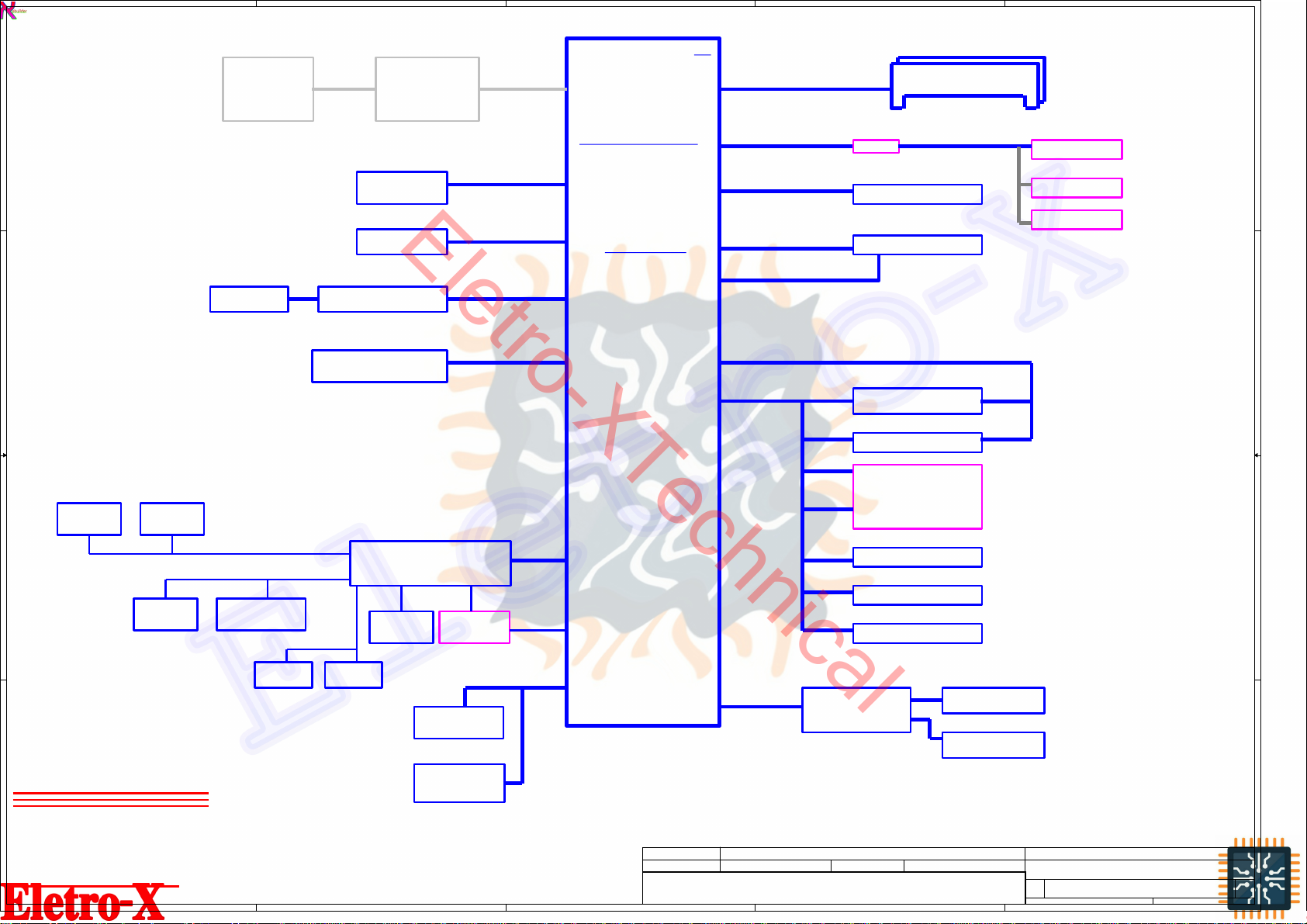

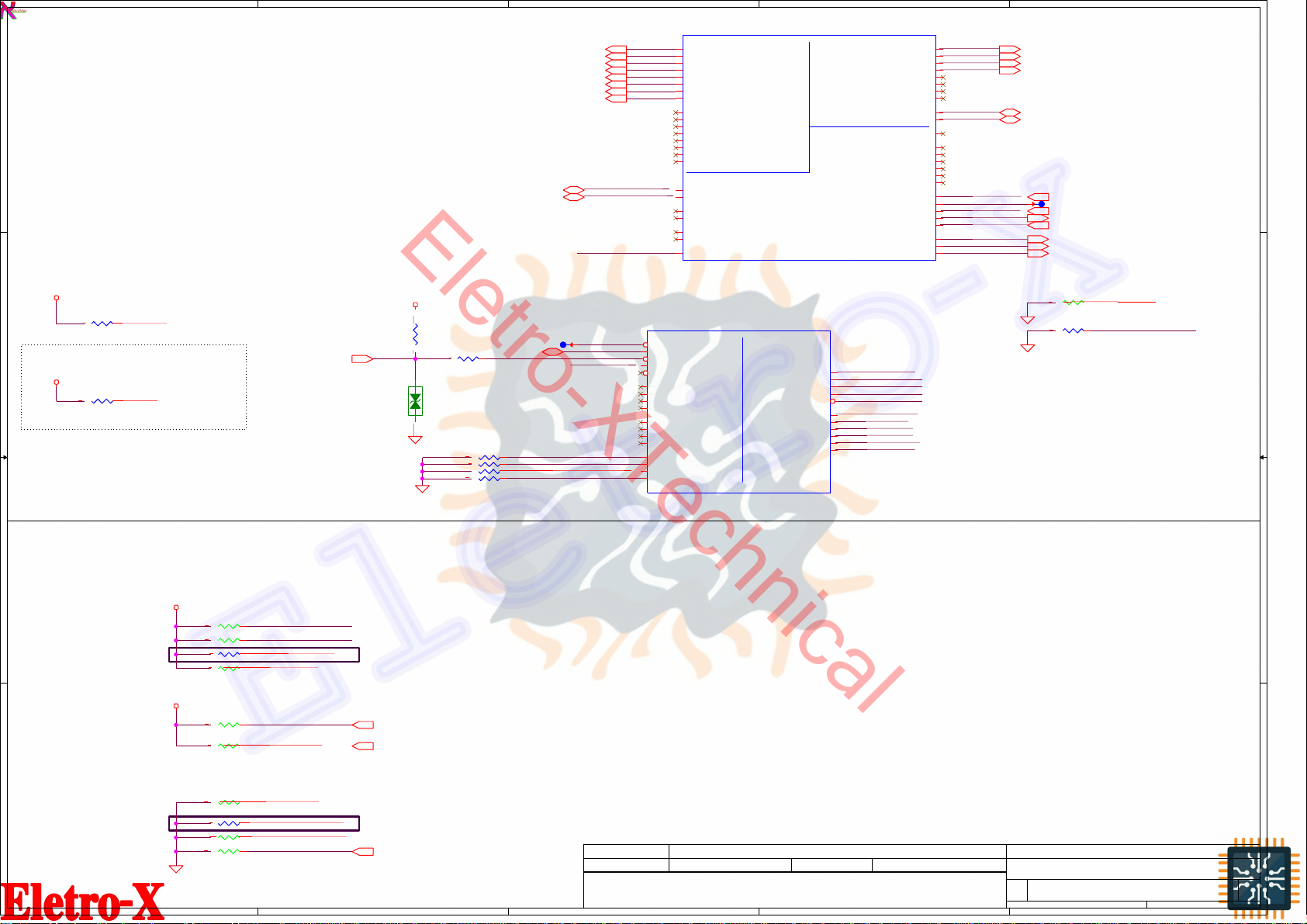

UV6 UV7

UV8 UV9(for 4GB)

VRAM

gDDR5x4pcs

256Mbx32

1 1

(8Gb)

P.25

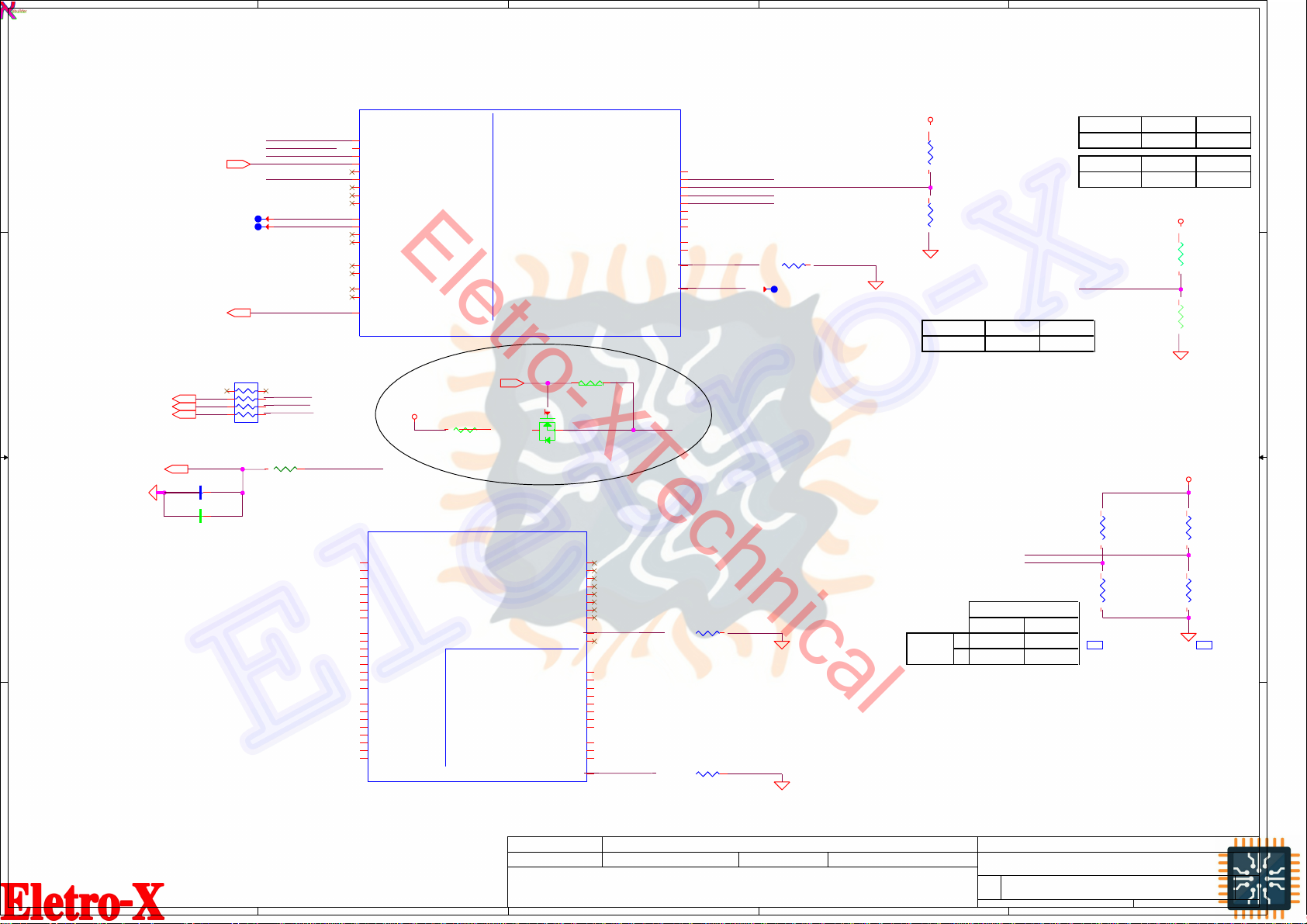

nVidia

N16S-GTR

N16V-GMR1

UV1 UC1

(MX110 )

PCIex4

Port#1~#4

PCIe3.0:8Gb/s

(MX130 )

P.19~26

Kaby Lake-RU42

Dual Channel Interleaved

DDR4 2133MHz1.2V

SATA 3.0

Port0

DDR4-SO-DIMM X 2

JHDD

P.30

JEDP

eDP CONN

P.27

eDPx2Lane

SATA 3.0

Port1

SATA ODD

JHDMI

HDMI CONN

P.28

JLAN

RJ45CONN

P.29

2 2

LAN

RTL8111HSH-CG

P.29

JWLAN

NGFF WLAN+BT

(Key E)

PUB1

Charger

P.47

3 3

Battery

dGPU

PJPB1

P.46

UV1

P.22

Thermalsensor

UC3

G753T11U

Fan

75x70

P.10

P.38

SMBus1

SMBus2

JFAN

KB light

JKBL

P.34

P.30

ECENE

KB9022QD

JKB

Int.KBD

P.34 P.34

DDI x4Lane Port 1

UL1

PCIex1 Port#5

PCIe Gen1 Only:2.5Gb/s

PCIex1 Port#6

PCIe Gen1 Only:2.5Gb/s

UK1

P.33

PS2

JTP

TouchPad

*sub board

LS-G073PR01

DA4002M0000

UC2

SPIROM

8MBytes

P.07

LPC

33MHz

SMBus

SPI

50MHz

1356P BGA

PCIe 3.0:8Gb/s

PCIe x2

Port#11~#12

SATA 3.0 Port2

USB3.0

5Gb/s

USB2.0

480Mb/s

Port1

Port2

Port3

Port4

Port5

Port6

Port7

HDA 24MHz

HDA Aduiocodec

M.2 SSD

USB3.0port

USB3.0port

USB2.0Port

CardReader

AK6485RB63-GLF-GR

(sub board)

Camera

Bluetooth

Touch Screen

ALC3247-CG

(KeyM)

NVMe

*need suppor ted Int el Opta ne (3D Xpoint )

UA1

P.32

UT1

TPM

B

SLB9670VQ2.0

P.35

Security Classification

IssuedDate

THI S S HE E T O F E NG IN EE RI NG DR AW IN G IS TH E P ROP RI ETA RY PR O PE RT Y OF C OM P AL E LE CTR ONI CS , I NC. A N D CON TA INS CONFIDENTSI

AN D TR AD E S EC RE T I NFO RM AT ION . THIS SH EE T MA Y N OT BE T RA NS F ER ED F RO M TH E C US TO DY OF T HE CO MP ET EN T DI VIS ION OF R &D

DE PA RTM EN T E XC EP T AS A UTH OR IZE D BY C OM P AL EL EC TRO NI CS , IN C. NE ITH ER THI S S HE E T NO R THE IN FO RM A TIO N I T CON TA INS

MA Y BE U S ED BY OR DI SCL OS ED TO A NY TH IR D PA R TY W IT HO UT P RI OR W R IT TE N CO NS E NT OF C OM PA L EL EC TRO NIC S, IN C.

C

2017/08/24 2018/08/24

Compal Secret Data

DecipheredDate

D

MB Board Information:

4 01.DA8001EG000, PCB 29I LA-G071P RE V0 MB 3(SKLU_4G)

02.DA6001WL000, PCB 29I LA-G072P REV0 MB 3(SKLU_2G)

03.DA8001EH000, PCB 29M LA-G079P REV0 MB 3(KBLU_4G)

4. DA6001WM000, PCB 29M LA-G07AP REV0 MB 3(KBLU_2G)

5. DA8001EI000, PCB 29L LA-G07BP REV0 MB 3(KBLR_4G)

6. DA6001WI000, PCB 29L LA-G07CP REV0 MB 3(KBLR_2G)

7. DA6001YA000, PCB 29M LA-G07DP REV0 MB 3(KBLU_UMA)

8. DA6001YB000, PCB 29L LA-G07EP REV0 MB 3(KBLR_UMA)

Sub Board Information:(EPK52)

01.DA6001WJ000, PCB 29L LS-G071P REV0 IOB(435OM832L01)

02.DA4002LZ000, PCB 29L LS-G072P REV0 HDDB(435OM932L01)

3. DA4002M0000, PCB 29L LS-G073P REV0 TOUCH PADB(435OMA32L01)

4. DA6001WR00S, PCB 29L LS-G074P REV0 SSDB(435OMB32L01)

5. DA6001WS00S, PCB 29L LS-G075P REV0 eMMCB

A

ChA:JDIIIIMM1(REV)

ChB:JDIIIIMM2(STD)

P.17~18

JODD

P.30

JSSD

P.19

JUSB1

Port1

P.30

JUSB2

P.31

Port2

JIO

P.31

*sub board

LS-G071PR01

DA6001WJ000

P.29

JEDP

P.27

JWLAN

P.30

JEDP

P.27

InternalSPK

Combo Jack

2.5" SATA HDD

(sub board)

M.2 SATA SSD

(sub board)

eMMC

(sub board)

JSPK

P.32

JHP

P.32

Title

iiiAzeL Document Number

Custom

*sub board

LS-G072P

DA4002LZ000

*sub board

LS-G074P

DA6001WR00S

*sub board

LS-G075P

DA6001WS00S

Compal Electronics, Inc.

Block Diagrams

EPK52_LA-G07EP

Sheet 2 of 59Date: Monday, January 08, 2018

E

Rev

v0.3

4

5

4

3

2

1

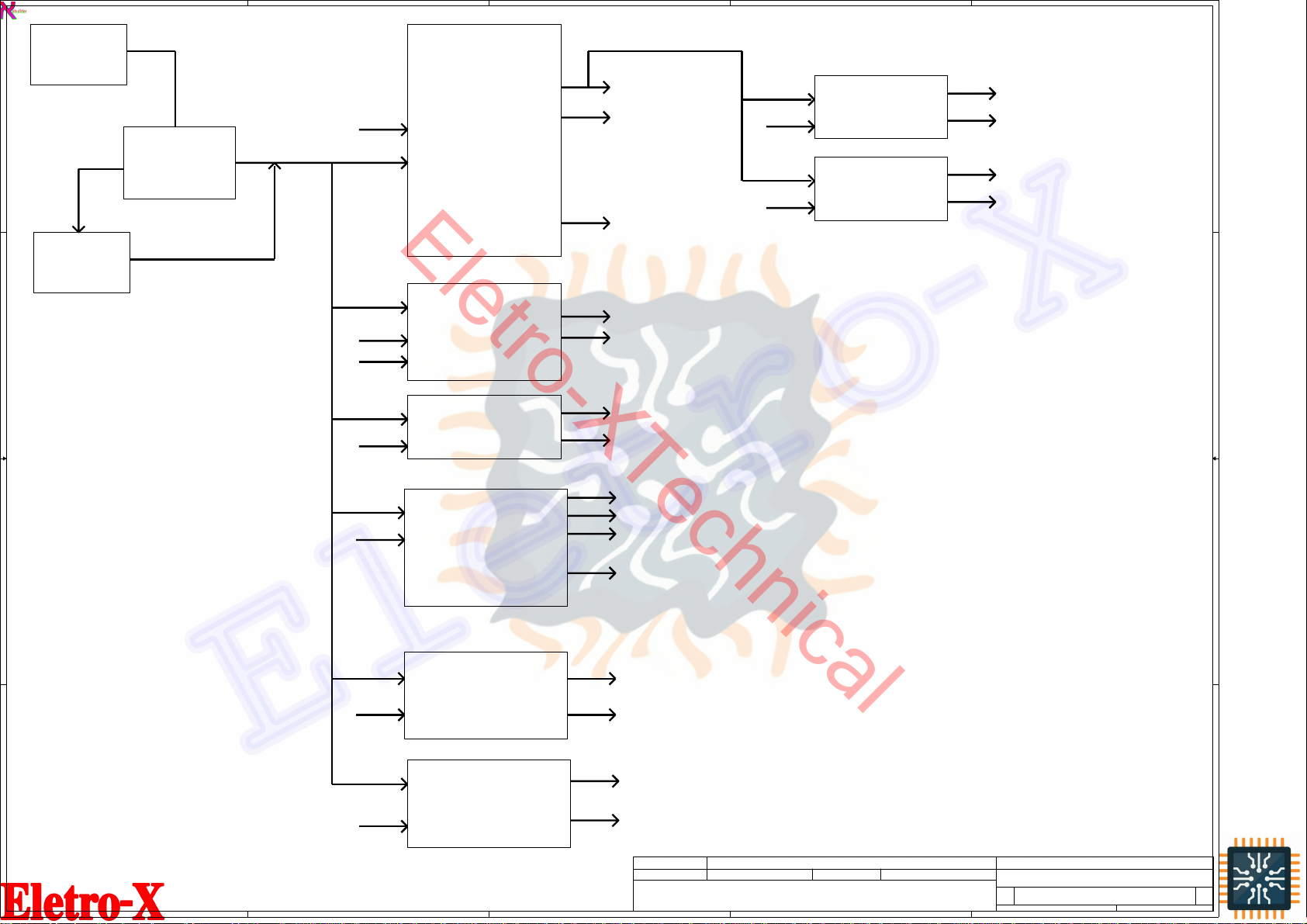

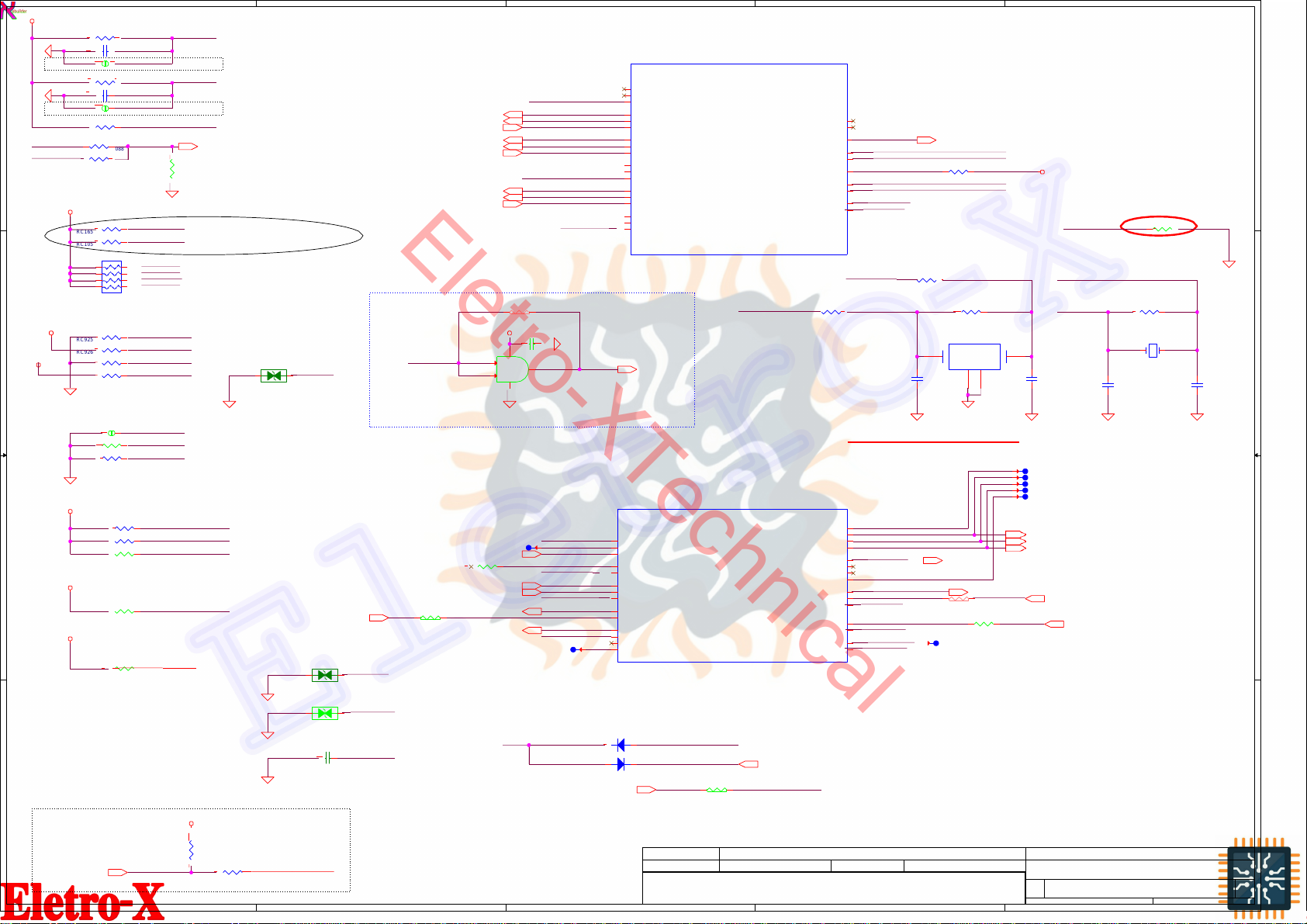

AC

Adapter 19.5V

P.45

D D

Charge

Charger

BQ24725

+19.5VB

EC_ON

P.47

DC

Battery

Discharge

P.46

+2.5V_PG

C C

SM_PG_CTRL

+1.8V_PG

+5VALW/+3VALW

(SY8288C/SY8286B)

Vout

EN

Vout

Vin

PGOOD

P.48

+1.2V/+0.6VS

(G5616B)

Vin

EN S5

EN S3

+1.0V_PRIM

Vin

(SY8286R)

EN

Vout

Vout

P.49

Vout

PGOOD

P.50

+3VALW

+5VALW

SPOK

+0.6V_0.6VS

+1.2V_VDDQ

+1.0V_PRIM

+1.0V_VS_PG_PWR

+3VALW

PCH_PWR_EN

+3VALW

PM_SLP_S4#

Vin

EN

Vin

EN

G5719

G5719

Vout

PGOOD

P.51

Vout

PGOOD

P.49

+1.8V_PRIM

+1.8V_PG

+2.5V

+2.5V_PG

CPU_CORE

Vin

(RT3602AE)

VR_ON

B B

EN

Vout

Vout

Vout

PGOOD

+VCC_CORE

+VCC_GT

+VCC_SA

VR_PWRGD

P.52,53

+VGA_CORE

VRAM_PG

(RT8812A)

Vin

EN

Vout

PGOOD

P.56

+1.35VS_VGA

Vin

A A

DGPU_PWR_EN

(SY8286R)

EN

Vout

PGOOD

P.55

5

4

+VGA_CORE

GPU_PGD

+1.35VS_VGA

VRAM_PG

Security Classification

Issued Date

THIS S HE ET OF ENG INEE RING D RA WIN G IS TH E PRO PR IET AR Y PR OPE RT Y OF C OM PA L ELEC TRONICS,,, INC . A ND CONT AINS CONFIDENTSIIiAzL

AN D TR AD E SE CR ET I NFO RM ATI ON. TH IS SH EE T MA Y N OT BE T RA NSF ER ED F ROM TH E C US TOD Y OF THE C OMP ET ENT DIV ISION OF R& D

DE PA RTME NT EX CEP T AS A UTH OR IZE D B Y C OMP AL EL ECT RON ICS , IN C. NEIIITHER THIS SHE ET NOR TH E INF ORM AT ION IIIT CON TAINS

MA Y BE US ED BY OR DIS CL OS ED TO AN Y TH IRD P ART Y W ITH OU T PR IOR W RI TTEN CO NS ENT OF C OM PA L ELE CTR ON ICS , IIINC...

3

2016/09/01

Compal SecretData

Deciphered Date

2

2019/09/01

Compal Electronics, Inc.

Title

Power Block Diagram

e Document Number

EPK52_LA-G07EP

Friday,,, January 05,,, 2018

Dattte:

Rev

58

Sheettt

1

v0.3

59

of

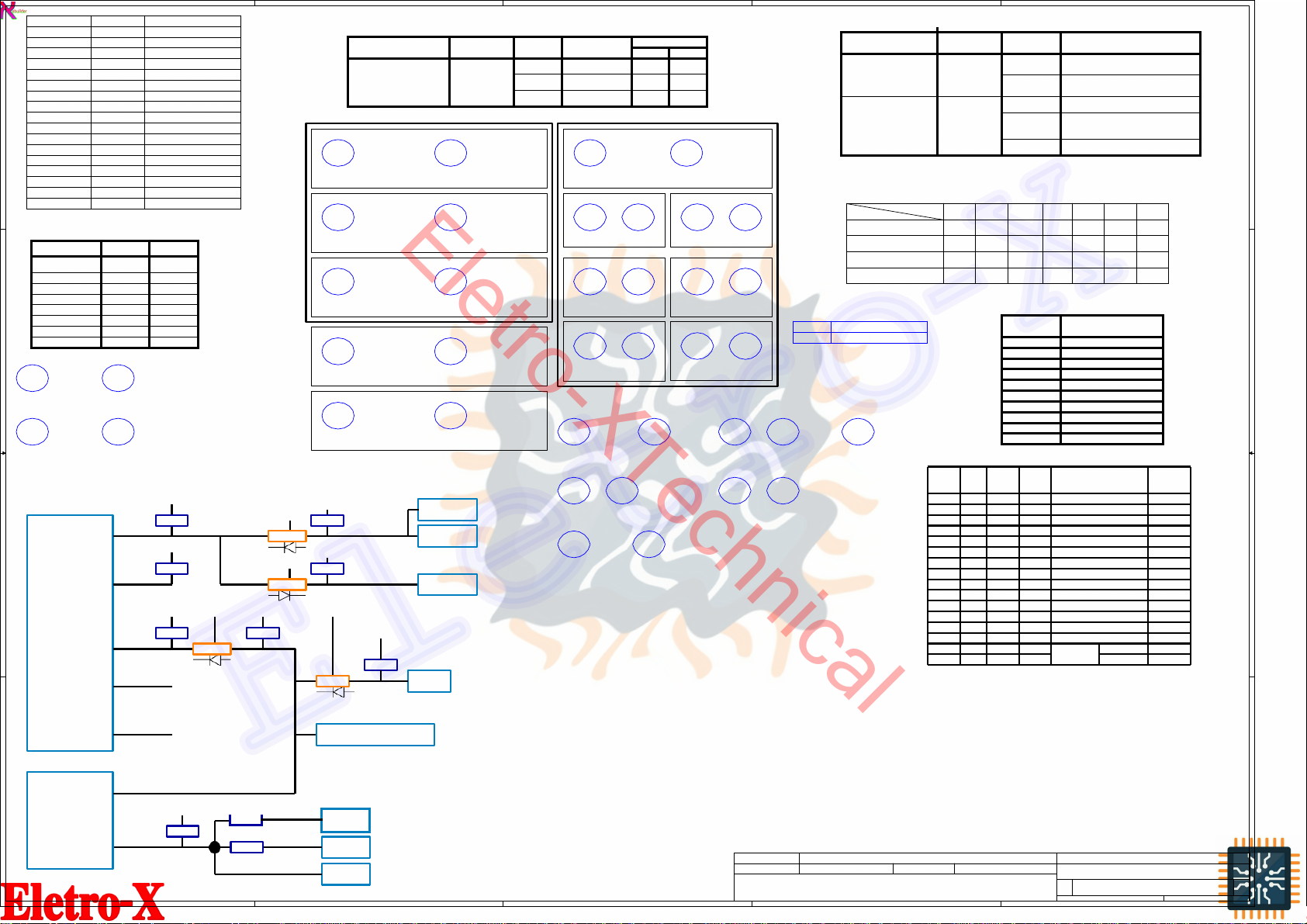

A

Power rail Control (EC) Source (CPU)

+RTCVCC X X

VIN X X

BATT+ X X

B+ X X

+VL X X

+3VL X X

+5VA LW EC_ON X

+3VA LW EC_ON X

+3VA LW_EC EC_ON X

1 1

+3V_PCH PCH_PWR_EN X

+1.2V_VDDQ SYSON PM_SLP_S5#/PM_SLP_S4#

+5VS SUSP# PM_SLP_S3#

+3VS SUSP# PM_SLP_S3#

+1.5VS SUSP# PM_SLP_S3#

+1.05VS SUSP# PM_SLP_S3#

+0.6V_0.6VS SUSP#

+VCC_CORE X VR12.5_VR_ON

BOM Structure Table(1/2)

Function

DGPU SKU

UMA SKU UMA@

TPM TPM@

2 2

R_i3_7020U_QN96@

UC1

R_SI_i3_7020U_QN96 Y0 2.3G R_SI_i3-8130U_QP8K Y02.2G

SA0000BLD00 SA0000BKN10

S IC A32 FJ8067703282620 QN96 Y0 2S.3GIC A32 FJ8067703282227 QP8K Y02.2G

R_i7_8550U_QNBF@ U_i3_7020U_QNZU@

UC1 UC1

R_SI_i7_8550U_QNBF Y0 1.8G

SA0000AWC10

S IC A32 FJ8067703281816 QNBF Y0 1S.8IGC A32 FJ8067702739769 QNZU H02.3G

UC1

3 3

CPU

Stuff Un-Stuff

PX@

R_i3_8130U_QP8K@

UC1

U_SI_i3-7020U_QNZU H0 2.3G

SA0000BLH00

SMBCLK

R7

SMBDATA

R8

SML0CLK

R9

SML0DATA

W2

SML1CLK

W3

SML1DATA

V3

U6

U7

+3V_PRIM

R=1K

+3V_PRIM

2N7002

+3V_PRIM

@

+3V_PRIM

2N7002

+3VS

EC_SMB_CK2

EC_SMB_DA2

R=499

+3V_PRIM+3VS +3VS_DGPU_AON

R=1K R=2.2K

2N7002

i3_7100U_R1@

i3_7100U

SA0000A38H0

S IC FJ8067702739738 SR343 H0 2.4G BGA

U_i5_7200U_SR342@

U_SI_i5-7200U_SR342 H0 2.5G

SA0000A37H0

S IC FJ8067702739739 SR342 H0 2.5G BGA

U_i7_7500U_SR341@ ZZZ

U_SI_i7-7500U_SR341 H0 2.7G

SA0000A34F0

S IC FJ8067702739740 SR341 H0 2.7G BGA

R_i5_8250U_QNEF@

R_SI_i5_8250U_QNEF Y0 1.6G

SA0000AWB10

S IC FJ8067703282221 SR3LA Y0 1.6G FCBGA S IC FJ8067703282221 SR3LA Y0 1.6GA32!

R_i7_8550U_SR3LC@

R_SI_i7-8550U_SR3LC Y0 1.8G i7_8550U

SA0000AWC20 SA0000AWC30

S IC FJ8067703281816 SR3LC Y0 1.8G FCBGA S IC FJ8067703281816 SR3LC Y0 1.8G A32!

+3VS

R=10K

+3VALW

R=10K

2N7002

B

SOC SMBUS Address Table

SOC_SMBUS Net Name Power Ra il Device Address (7 bit)

SMBCLK

SMBDATA

UC1

UC1

UC1

UC1

UC1

PCH_SMBCLK

PCH_SMBDATA

TP_SMBCLK

TP_SMBDAT

+3VS_DGPU_AON

R=2.2K

PX@

I2CS_SCL

I2CS_SDA

+3V_PRIM

i3_7100U_R3@

UC1

i3_7100U

SA0000A38J0

S IC FJ8067702739738 SR343 H0 2.4G A32!

i5_7200U_R3@

i5_7200U

SA0000A37J0

S IC FJ8067702739739 SR342 H0 2.5G A32!

i7_7500U_R3@

UC1

i7_7500U

SA0000A34H0

S IC FJ8067702739740 SR341 H0 2.7G A32!

i5_8250U_R3@

UC1

i5_8250U

SA0000AWB30

i7_8550U_R3@

UC1

SO-DIMM A

SO-DIMM B

Touch Pad

DGPU

DIMM1 0x50 0xA0 0xA1

DIMM2 0x52 0xA4 0xA5

Touch PAD

KBLU_2G@

DA6001WM000

PCB 29M LA-G07AP REV0 MB 3 PCB 29L LA-G07CP REV0 MB 3

DAZ_U2G@

DAZ23T00600

KBLU_UMA@

DA6001YA000 DA6001YB000

PCB 29M LA-G07DP REV0 M/B 3 PCB 29L LA-G07EP REV0 M/B 3

C

Address (8bit)

Write Read

0x2C 0x58 0x59

MX110@

UV1

N16V-GMR1-S-A2

SA00009IT00

S IC N16V-GMR1-S-A2 BGA595P

ZZZ

2G Mi cronUC1

M2G_R1@

X7674032L01

ZZZ

2G Hynix

H2G_R1@

X7674032L04

ZZZ

2G S ams ung

S2G_R1@

X7674032L05

DAX

KBLU -2G

ZZZ

DAZ_U2G

DAX

KBLU -UMA

M2G_R3@

X7674032L06

H2G_R3@

X7674032L07

2G S ams ung

S2G_R3@

X7674032L08

ZZZ

DAZ_R2G

DAZ_R2G@

DAZ23T00500

ZZZ

2G Mi cron

ZZZ

2G Hynix

ZZZ

KBLR_2G@

DA6001WI000

KBLR -UMA

KBLR_UMA@

KBLR -2G

DAX

MX130@

UV1

N16S-GTR-S-A2

SA00009FP00

S IC N16S-GTR-S-A2 BGA 595PGPU

ZZZ

4G Mi cron

M4G_R1@

X7674032L26

ZZZ

4G Hynix

H4G_R1@

X7674032L25

ZZZ

4G S ams ung

S4G_R1@

X7674032L27

DAX

ZZZ

4G Mi cron

M4G_R3@

X7674032L29

4G Hynix

H4G_R3@

X7674032L28

ZZZ

4G S ams ung

S4G_R3@

X7674032L30

DAX

KBLU -4G

KBLU_4G@

DA8001EH000

ZZZ

DAZ_U4G

DAZ_U4G@

DAZ23T00600

Part Number Description

RO0000002HM HDMI W/Logo:RO0000002HM

RO0000003HM

DAX

KBLR -4G

KBLR_4G@

DA8001EI000

ZZZ

DAZ_R4G

DAZ_R4G@

DAZ23T00500

D

EC SMBUS Address Table

(TBC)

EC_SMBUS Port Power Rail Device Address (7 bit)

SMBUS Port 1 +3VL_EC

BAT 0x16

CHGR 0x12

dGPU

SMBUS Port 2 +3VS

Thermal

Sensor

0x90

PCH

Power State

STATE

SIGNAL

SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

S0 (Full ON) HIGH HIGH HIGH ON ON ON ON

S3 (Suspend to RA M) LOW HIGH HIGH ON ON OFF OFF

S4 (Suspend to Disk)

S5 (Soft OFF)

ROYALTY HDMIW /LOGO45@

ZZZ

EMC for EE

X4E@

X4EABB32L01

SMT EMC FOR EE AG07C EPK52

LOW LOW HIGH ON OFF OFF OFF

LOW LOW LOW ON OFF OFF OFF

<USB2.0 port>

USB2.0port DESTINATION

1 USB3.0 Type-C

2 USB2.0/USB3.0

3 USB2.0/USB3.0

4 BT

5 HD/IR_1/IR_2Camera

6 IR_2 Camera

7 Card Reader

8 X

9 X

10 X

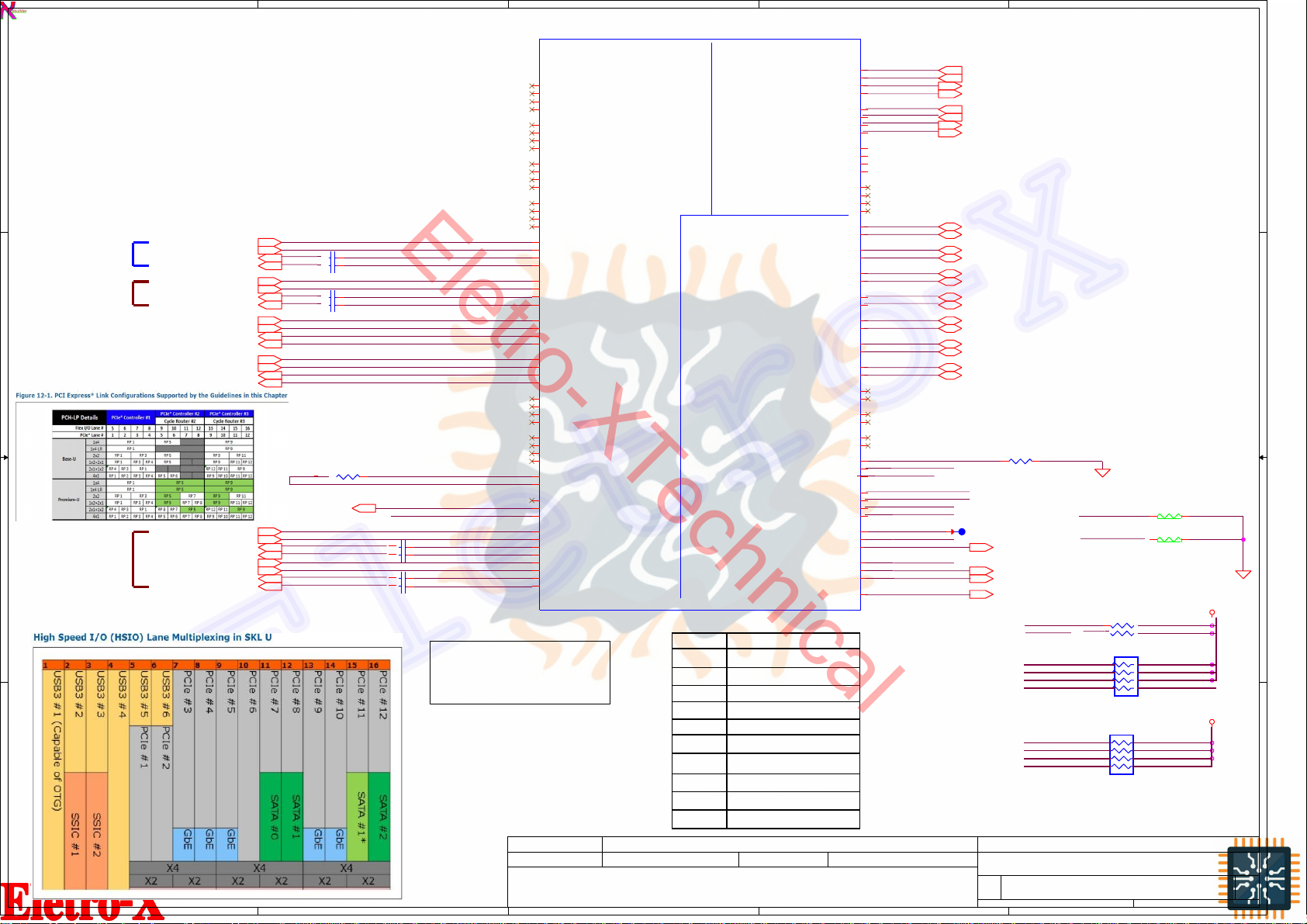

<PCI-E,SATA,USB3.0/CLK>

Lane# PCI-E SATA USB3.0

1 1

2 2

3 3

4 4

5 1 5

6

2 6

7

3

8

4

9

5

10

6

11

7

12 1a

13

14

15

16

0

8

10

1191b*

12

2

DESTINATION

USB3.0Type-C

USB3.0Type-C

USB2.0/USB3.0

USB2.0/USB3.0

GPU(DISonly)

GPU(DISonly)

GPU(DISonly)

GPU(DISonly)

LAN

WLAN

HDD

ODD CLK3

X

X

NVMex2

SATA SSD

E

CLK

X

X

X

X

CLK0

CLK1

CLK2

X

X

X

CLK4

X

X

U9

U8

UK1:+3VALW_EC(+3VL)

4 4

EC

EC_SMB_CK2

EC_SMB_DA2

79

80

EC_SMB_CK1

77

EC_SMB_DA1

78

A

+3V_SMBUS

R=2.2K

R=0

R=100

GSEN_I2DAT

GSEN_I2CLK

Thermal Sensor :G753T11U

Address : 0x48

G-Sensor

HP2DC

BAT

Charger

B

Securi ty C lassification

Issued Date

THI S S HE ET OF ENG IINE ERII NG D RAW IN G I S T HE PR OPR IE TAR Y P RO PER TY O F COM PA L E LE CTR ONI CS , INC . A ND CO NTA INS CONFIDENTSSIAizL

AND TR ADE SEC RE T IN FO RMA TIO N. TH IS SHE ET MAY N OT BE TR ANS FE RED F ROM T HE CUS TOD Y OF THE C OMP ET ENT D IVIS ION OF R &D

DE PAR TME NT EX CEP T A S AUTH ORI ZE D BY CO MPA L ELE CT RON ICS , INC . N EI THER THI S SHE ET NOR THE I NFO RMA TIO N IT CO NTA INS

C

MAY BE U SED BY OR DI SCL OSE D TO AN Y T HIR D PAR TY WI THO UT PR IO R W RIT TEN CO NSE NT OF CO MPA L EL ECT RO NIC S, I NC.

2016/12/15 2019/12/15

Compal Secret Data

Deciphered Date

D

Title

e Document Number

Custom

Compal Electronics,Inc.

Notes List

LA-G07DP(KBL-U_UMA_vv60.L3)

Sheet 3 of 59Date: Friday, January 05,2018

E

Rev

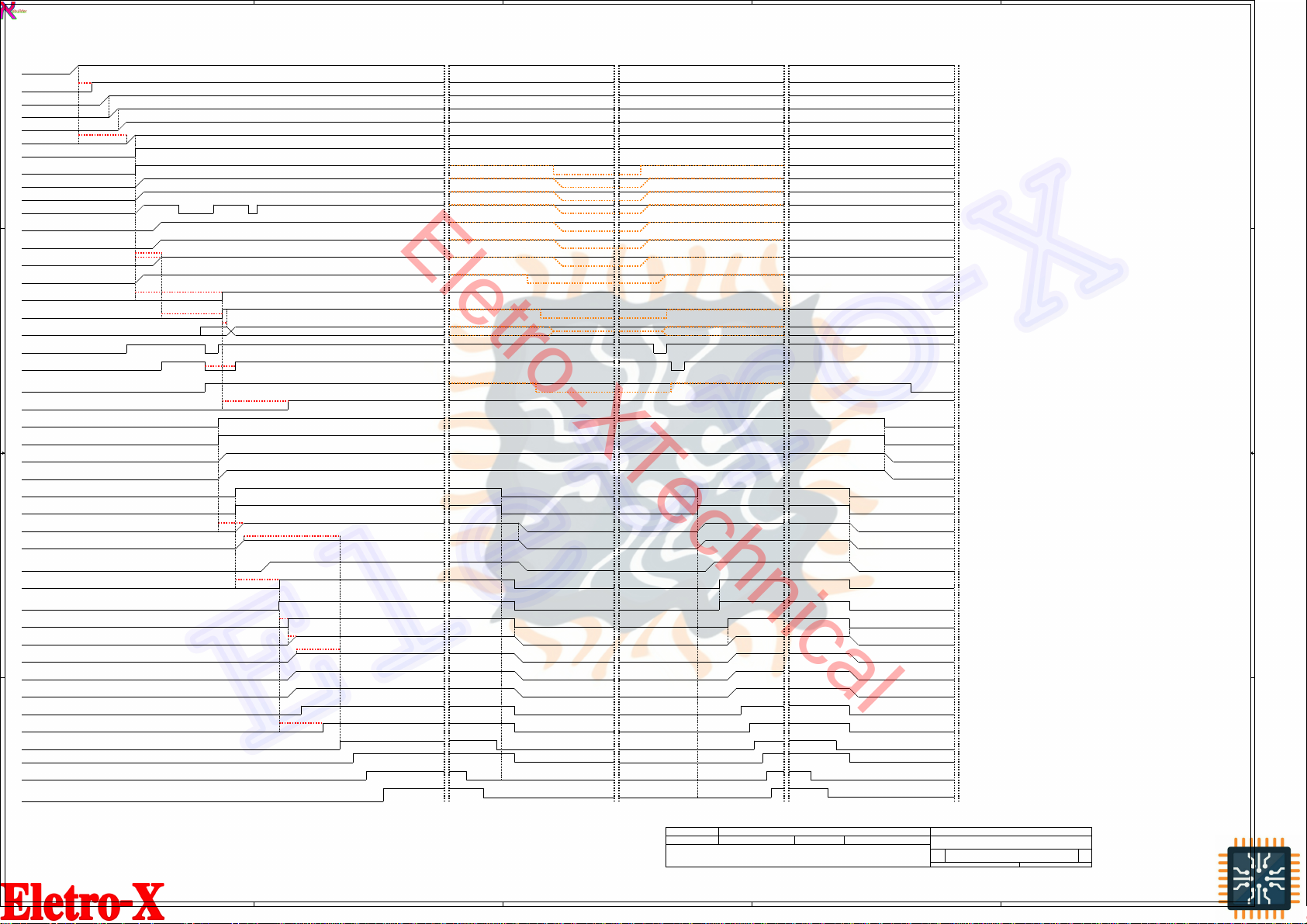

[Diner-PWR Sequence_SKL-U22_DDR3L_Volume_NON CS]

5

4

3

2

1

+3VL_RT C

SOC_RTCRST#

G3->S0

tPCH01_ Min : 9 ms

S0->S3/DS3

S0/DS3 ->S0

+19VB

+3VLP/+5VLP

D D

EC_ON

+5VALW /+3VALW /+3VALW_DSW

PM_BATLOW#

tPCH04_ Min : 9 ms

Pull-up to DSW well if not implemente d.

PCH_PWR_EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PW R_GAT E#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

tPCH06_ Min : 200 us

tPCH34_ Max : 20 ms

SUSACK#

PCH_DPW ROK

EC_RSMRST#

AC_PRESENT

C C

ON/OFF

PBTN_O UT#

Mini mum du rat ion of PW RBTN# assertion = 16mS. PWRBTN # can a ssert before or after RSMRST#

PM_SLP_S5 #

ESPI_RST#

If EXT _PWR_ GATE# T off min is too smal l, Pwr

gate may ch oos e to complete ly ignore it

tPCH02_ Min : 10 ms

tPCH03_ Min : 10 ms

tPLT02 _Min : 0 ms Max : 90 ms

tPCH18_ Min : 90 us

PM_SLP_S4 #

SYSON

+1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSFR_OC

PM_SLP_S3 #

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

+5VS/+3VS/+1.5VS/+1.05VS

B B

EC_VCCST_PG

VR_ON

SM_PG_CT RL

+0.675VS_VTT

+VCC_SA

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

T4 = Mi n : 20ms Max : 3 0ms(EC Control)

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

+VCC_CORE

+VCC_GT

VR_PW RGD

PCH_PW ROK

tCPU16 Min : 0 ns

H_CPUPWRGD

SYS_PW ROK

SUS_STAT#

A A

SOC_PLT RST#

S0->S5

+3VL_RT C

SOC_RTCRST#

+19VB

+3VLP/+5VLP

EC_ON

+5VALW /+3VALW /+3VALW_DSW

PM_BATLOW#

PCH_PWR_EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

SUSACK#

PCH_DPW ROK

EC_RSMRST#

AC_PRESENT

ON/OFF

PBTN_O UT#

PM_SLP_S5 #

ESPI_RST#

PM_SLP_S4 #

SYSON

+1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSFR_OC

PM_SLP_S3 #

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

+5VS/+3VS/+1.5VS/+1.05VS

EC_VCCST_PG

VR_ON

SM_PG_CT RL

+0.675VS_VTT

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PW RGD

PCH_PW ROK

H_CPUPWRGD

SYS_PW ROK

SUS_STAT#

SOC_PLT RST#

Security Classification

IssuedDate

THI S S HEE T OF EN GIN EER ING DR AWI NG IS TH E PRO PRI ETA RY PRO PER TY O F COMP AL EL ECT RONI CS , I NC. AND C ONTAIN S CON FID EN

AND TRA DE S ECR ET I NFO RMA TIO N. THI S SH EET MA Y NOT BE TRA NSF ER ED F ROM THE CUS TOD Y OF TH E C OMPE TEN T DI VISI ON OFR &

DEP ART MEN T E XCE PT AS A UTHO RIZ ED BY C OMP AL ELE CTR ONIC S, INC . NE ITHER THI S S HEE T NOR TH E IN FORM ATI ON IT C ONTA INS

MAY BE US ED BY OR D ISCL OSED TO AN Y THI RD PAR TY WI THO UT P RIO R WR ITTE N CON SEN T OF CO MPA L ELE CTR ONI CS, INC .

5

4

3

Compal Secret Data

DecipheredDate

Compal Electronics, Inc.

Title

TSSIAizL

e

D

m

Custo

Date: Friday, January 05,2018 Sheet 4 of 59

2

Document Number

HWReserve

EPK52_LA-G07EP

Rev

v0.3

1

A

B

C D

E

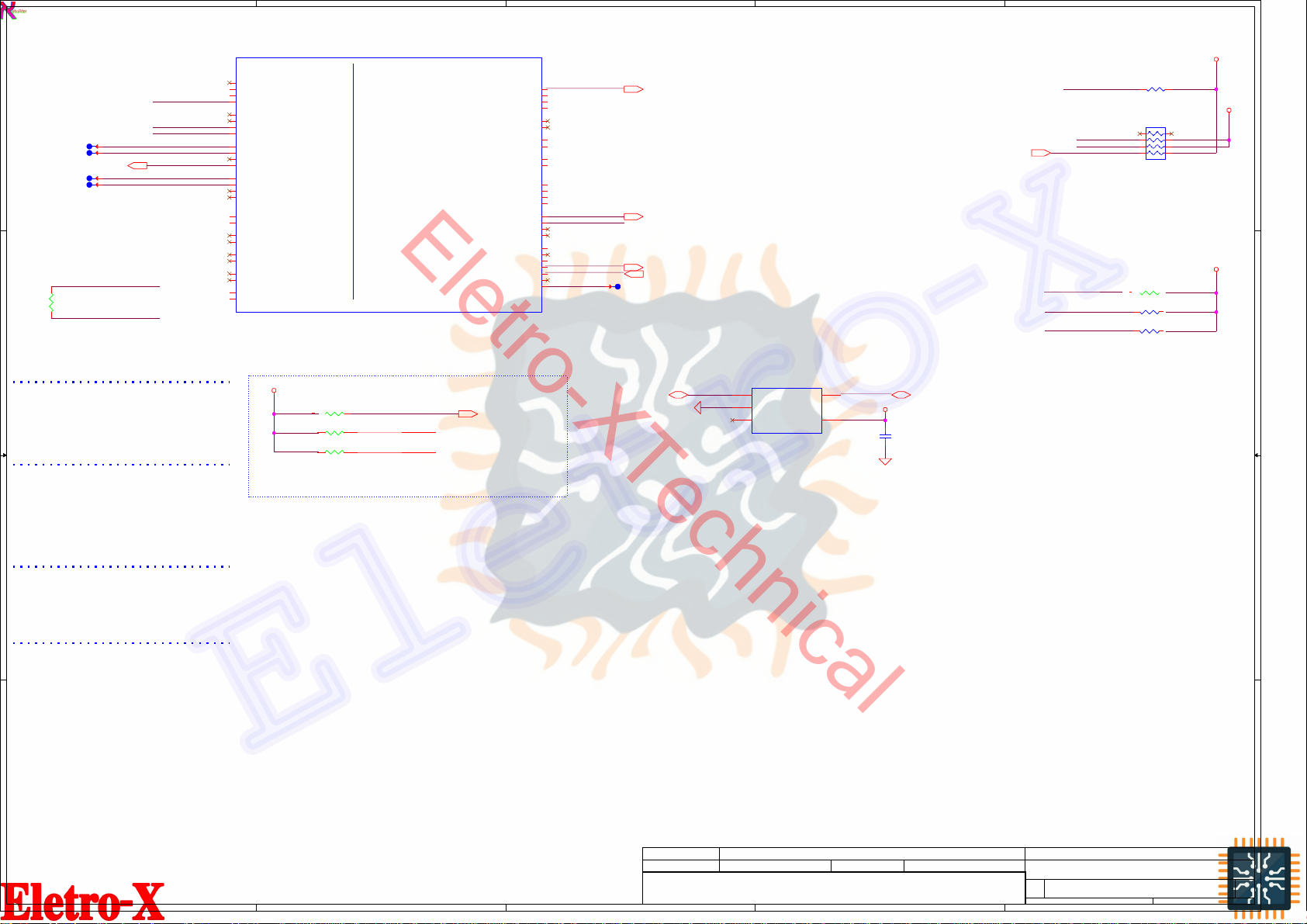

UC1A

UC1D

D63

CATERR#

A54

PECI

PROCHOT#

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

OPCE_RCOMP

H65

OPC_RCOMP

SKL-U_BGA1356

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-U_BGA1356

SKL-U

CPU MISC

4 OF20

<28> HOST_DP1_N0

<28> HOST_DP1_P0

SOC_DP1_CTRL_DATA(Internal Pull Down):

<HDMI>

Display Port B Detected

1 1

0 = Port B is not detected.

1 = Port Bis detected.

<28> HOST_DP1_N1

<28> HOST_DP1_P1

<28> HOST_DP1_N2

<28> HOST_DP1_P2

<28> HOST_DP1_N3

<28> HOST_DP1_P3

SOC_DP2_CTRL_DATA(Internal Pull Down):

Display Port C Detected

0 = Port C is not detected.

HDMI DDC (Port B)

<28> HOST_DP1_CTRL_CLK

<28> HOST_DP1_CTRL_DATA

HOST_DP1_CTRL_CLK L13

HOST_DP1_CTRL_DATA L12

1 = Port C isdetected.

EDP_COMP

+1.0V_VCCST

1

RC2

2 2

COMPENSATION PU FOReDP

+1.0V_PRIM

RC1 1

CAD note:

Trace width=20 mils,Spacing=25mil,Maxlength=100mils

2 H_THERMTRIP#

1K_0402_5%

2 EDP_COMP

24.9_0402_1%

<33> PROCHOT#

+1.0V_PRIM

12

RC3

1K_0402_5%

1 2

RC4 499_0402_1%

12

DS11

CK0402101V05_0402-2

ESD@

SCV00001K00

RC5 2

RC6 2

RC7 2

RC8 2

T248 TP@

<33> H_PECI

1 49.9_0402_1% CPU_POPIRCOMP AT16

1 49.9_0402_1%PCH_OPIRCOMP

1 49.9_0402_1% EDRAM_OPIO_RCOMP H66

1 49.9_0402_1%EOPIO_RCOMP

CATERR#

H_PECI

H_PROCHOT#_R C65

H_THERMTRIP# C63

SKL-U

DDI

DISPLA YSIDE BANDS

JTAG

PROC_TCK

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

1 OF20

Rev_0.53

PROC_TDI

JTAGX

EDP

EDP_DISP_UTIL

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

CPU_XDP_TCK0

B61

SOC_XDP_TDI

D60

A61

SOC_XDP_TDO

C60

SOC_XDP_TMS

SOC_XDP_TRST#

B59

B56 PCH_JTAG_TCK1

D59 SOC_XDP_TDI

A56 SOC_XDP_TDO

C59 SOC_XDP_TMS

C61 SOC_XDP_TRST#

A59 CPU_XDP_TCK0

Rev_0.53

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9 HOST_DP1_HPD

DDI2_HPD

L7

L6 NMI_DBG#_CPU

N9 EC_SCI#

L10 EDP_HPD

R12

ENBKL

R11

ENVDD_CPU

U13

EDP_TXN0 <27>

EDP_TXP0 <27>

EDP_TXN1 <27>

EDP_TXP1 <27>

EDP_AUXN <27>

EDP_AUXP <27>

HOST_DP1_HPD <28>

TP@ T408

NMI_DBG#_CPU <10,33>

EC_SCI# <33>

EDP_HPD <27>

ENBKL <33>

BKL_PWM_CPU <27>

ENVDD_CPU <27>

RC123 1 @ 2 100K_0402_5% ENVDD_CPU

RC124 1

<eDP>

From HDMI

2 100K_0402_5% ENBKL

From eDP

XDP CONN

3 3

+1.0V_PRIM

RC11 2 @

RC13 2 @

RC15 2 1 51 +-1% 0402 SOC_XDP_TDO

RC364 2 @ 1 51_0402_5% CPU_XDP_TCK0

+1.0V_PRIM

RC14 2 @ 1 51_0402_5% XDP_PREQ#

RC31 1 @ 2 1K_0402_5% XDP_ITP_PMODE

4 4

A

RC365 2 @ 1 51_0402_1% SOC_XDP_TRST#

RC35 2 1 51_0402_1% CPU_XDP_TCK0

RC37 2 @ 1 51_0402_5% PCH_JTAG_TCK1

RC366 1 @ 2 0_0402_5% CFG3

1 51_0402_5% SOC_XDP_TMS

1 51_0402_5% SOC_XDP_TDI

SD000008H80

XDP_PREQ# <11>

XDP_ITP_PMODE <16>

SD000008H80

CFG3 <16>

B

Security Classification

IssuedDate

THI S SHE ET O F ENGIN EERIN G DRAW IN G IS TH E P ROPRI ET ARY PRO PE RT Y OF C OMP AL E LECTRON ICS, INC . AND CONTAIN S CONFIDENTSSIAizL

AND TR ADE S ECRET INF OR MAT IO N. T HIS SHE ET M AY N OT BE T RANSF ER ED FROM TH E C US TO DY OF TH E C OM PET EN T DIVISION OF R &D

DEPAR TMENT E XCEPT AS AU TH OR IZED BY CO MP AL ELEC TR ON ICS , INC. NEIT HER THIS SHE ET N OR TH E INF OR MAT IO N IT CON TAINS

MAY BE U SED BY OR DISC LOS ED TO A NY T HI RD PA RT Y WI TH OUT P RIO R W R ITTEN CO NS ENT OF CO MPAL E LEC TR ON ICS , INC .

C D

2017/04/10 2019/12/15

Compal Secret Data

DecipheredDate

Custom

Title

Compal Electronics, Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

e Document Number

EPK52_LA-G07EP

Rev

Sheet 5 of 59Date: Friday, January 05, 2018

E

v0.3

5

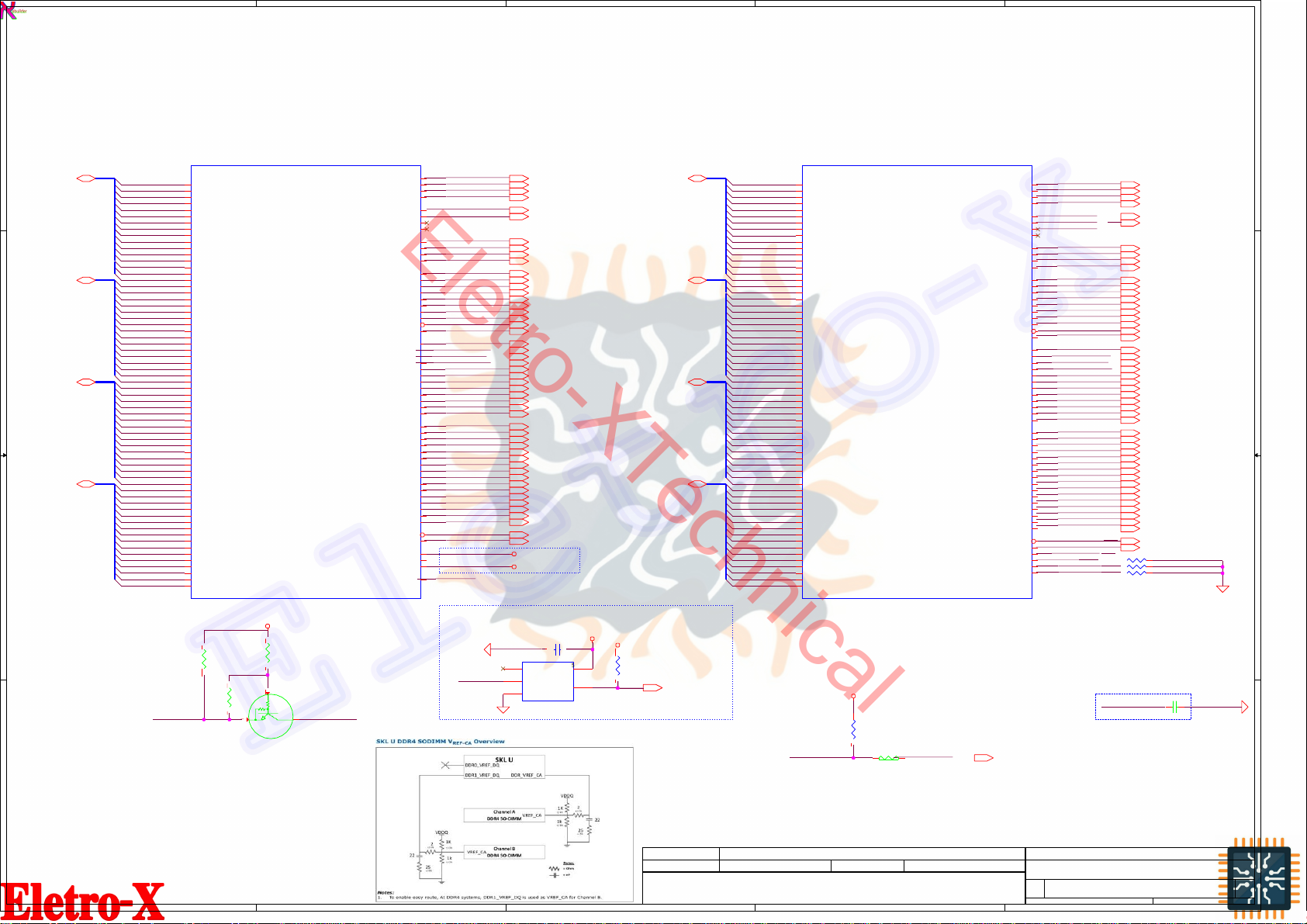

Interleaved Memory

4

3

2

1

Interleaved Memory

D D

<Cocoa_1020>

PDG#543016, ODT: CPU side no connect, DRAM side connect to VDDQ(Memory down); FET+R(SO-DIMM)

UC1B

<17> DDR_M0_D[0..15]

<17> DDR_M0_D[16..3 1]

C C

<17> DDR_M0_D[32..4 7]

<17> DDR_M0_D[48..6 3]

B B

A A

AL71

DDR_M0_D0

DDR_M0_D1

DDR_M0_D2

DDR_M0_D3

DDR_M0_D4

DDR_M0_D5

DDR_M0_D6

DDR_M0_D7

DDR_M0_D8

DDR_M0_D9

DDR_M0_D10AU71

DDR_M0_D11AU68

DDR_M0_D12AR71

DDR_M0_D13AR69

DDR_M0_D14AU70

DDR_M0_D15AU69

DDR_M0_D16BB65

DDR_M0_D17AW65

DDR_M0_D18AW63

DDR_M0_D19AY63

DDR_M0_D20BA65

DDR_M0_D21AY65

DDR_M0_D22BA63

DDR_M0_D23BB63

DDR_M0_D24BA61

DDR_M0_D25AW61

DDR_M0_D26BB59

DDR_M0_D27AW59

DDR_M0_D28BB61

DDR_M0_D29AY61

DDR_M0_D30BA59

DDR_M0_D31AY59

DDR_M0_D32AY39

DDR_M0_D33AW39

DDR_M0_D34AY37

DDR_M0_D35AW37

DDR_M0_D36BB39

DDR_M0_D37BA39

DDR_M0_D38BA37

DDR_M0_D39BB37

DDR_M0_D40AY35

DDR_M0_D41AW35

DDR_M0_D42AY33

DDR_M0_D43AW33

DDR_M0_D44BB35

DDR_M0_D45BA35

DDR_M0_D46BA33

DDR_M0_D47BB33

DDR_M0_D48AY31

DDR_M0_D49AW31

DDR_M0_D50AY29

DDR_M0_D51AW29

DDR_M0_D52BB31

DDR_M0_D53BA31

DDR_M0_D54BA29

DDR_M0_D55BB29

DDR_M0_D56AY27

DDR_M0_D57AW27

DDR_M0_D58AY25

DDR_M0_D59AW25

DDR_M0_D60BB27

DDR_M0_D61BA27

DDR_M0_D62BA25

DDR_M0_D63BB25

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

RC905

100K_0402_5% @

2 1

RC906

100K_0402_5% @

DDR_PG_CTRL

SB00000QJ00,S TR DRC5115E0L NPN

SOT323-3

+1.2V_VDDQ

12

@

3

UC9

MMBT3904WH NPN SOT323- 3

SKL-U

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_ BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_M A[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_M A[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_ BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_ BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDRCH -A

2 OF 20

12 2

RC904

@ 100K_0402 _5%

1 SM_PG_CT RL

SB000008 E10

Rev_0.53 Rev_0.53

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0 _DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0 _DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1 _DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1 _DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1 _DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1 _DQSP[5]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VR EF_DQ

DDR1_VR EF_DQ

DDR_VTT_CNTL

AU53 DDR_M0_CLK#0

AT53 DDR_M0_CLK0

AU55 DDR_M0_CLK#1

AT55 DDR_M0_CLK1

DDR_M0_CKE0

BA56

DDR_M0_CKE1

BB56

AW56

AY56

DDR_M0_CS#0

AU45AR68

AU43 DDR_M0_CS#1

AT45 DDR_M0_ODT0

AT43 DDR_M0_ODT1

BA51 DDR_M0_MA5

BB54 DDR_M0_MA9

BA52 DDR_M0_MA6

AY52 DDR_M0_MA8

AW52 DDR_M0_MA7

AY55 DDR_M0_BG0

AW54 DDR_M0_MA12

BA54 DDR_M0_MA11

BA55 DDR_M0_ACT #

AY54 DDR_M0_BG1

AU46 DDR_M0_MA13

AU48 DDR_M0_MA15_C AS#

AT46 DDR_M0_MA14_WE#

AU50 DDR_M0_MA16_R AS#

AU52 DDR_M0_BA 0

AY51 DDR_M0_MA2

AT48 DDR_M0_BA1

AT50 DDR_M0_MA10

BB50 DDR_M0_MA1

AY50 DDR_M0_MA0

BA50 DDR_M0_MA3

BB52 DDR_M0_MA4

AM70 DDR_M0_DQS#0

AM69 DDR_M0_DQS0

AT69 DDR_M0_DQS#1

AT70 DDR_M0_DQS1

BA64 DDR_M0_DQS#2

AY64 DDR_M0_DQS2

AY60 DDR_M0_DQS#3

BA60 DDR_M0_DQS3

BA38 DDR_M0_DQS#4

AY38 DDR_M0_DQS4

AY34 DDR_M0_DQS#5

BA34 DDR_M0_DQS5

BA30 DDR_M0_DQS#6

AY30 DDR_M0_DQS6

AY26 DDR_M0_DQS#7

BA26 DDR_M0_DQS7

AW50 DDR_M0_ALERT#

AT52 DDR_M0_PAR

AY67 +0.6V_ VREFCA

AY68

BA67 +0.6V_B_VREFD Q

AW67 DDR_PG_CTRL

For VTT power control

DDR_PG_CTRL 2

DDR_M0_CLK#0 < 17>

DDR_M0_CLK0 <1 7>

DDR_M0_CLK#1 < 17>

DDR_M0_CLK1 <1 7>

DDR_M0_CKE0 <17>

DDR_M0_CKE1 <17>

DDR_M0_CS#0 <17>

DDR_M0_CS#1 <17>

DDR_M0_O DT0 < 17>

DDR_M0_O DT1 < 17>

DDR_M0_MA5 <17>

DDR_M0_MA9 <17>

DDR_M0_MA6 <17>

DDR_M0_MA8 <17>

DDR_M0_MA7 <17>

DDR_M0_B G0 <17>

DDR_M0_MA12 <17>

DDR_M0_MA11 <17>

DDR_M0_A CT# < 17>

DDR_M0_B G1 <17>

DDR_M0_MA13 <17>

DDR_M0_MA15_CAS# <17>

DDR_M0_MA14_WE# <17>

DDR_M0_MA16_RAS# <17>

DDR_M0_B A0 <17>

DDR_M0_MA2 <17>

DDR_M0_B A1 <17>

DDR_M0_MA10 <17>

DDR_M0_MA1 < 17>

DDR_M0_MA0 <17>

DDR_M0_MA3 <17>

DDR_M0_MA4 <17>

DDR_M0_DQS#0 <17>

DDR_M0_DQS0 <17>

DDR_M0_DQS#1 <17>

DDR_M0_DQS1 <17>

DDR_M0_DQS#2 <17>

DDR_M0_DQS2 <17>

DDR_M0_DQS#3 <17>

DDR_M0_DQS3 <17>

DDR_M0_DQS#4 <17>

DDR_M0_DQS4 <17>

DDR_M0_DQS#5 <17>

DDR_M0_DQS5 <17>

DDR_M0_DQS#6 <17>

DDR_M0_DQS6 <17>

DDR_M0_DQS#7 <17>

DDR_M0_DQS7 <17>

DDR_M0_A LERT# <17>

DDR_M0_P AR <17>

+0.6V_VREFCA

+0.6V_B_VREFDQ

0.1U_0201_10V6K 2 1 CC57

UC7

1

NC

A

3

GND

74AUP1G07SE-7_SOT353-5

SA00007W E00

VCC

+1.2V_VDDQ

5

4

Y

<18> DDR_M1_D[0..15]

<18> DDR_M1_D[16..3 1]

<18> DDR_M1_D[32..4 7]

<18> DDR_M1_D[48..6 3]

+3VS

12

RC394

100K_0402_5%

SM_PG_CT RL <49>

AF65

DDR_M1_D0

DDR_M1_D1

AF64

DDR_M1_D2

AK65

DDR_M1_D3

AK64

DDR_M1_D4

AF66

DDR_M1_D5

AF67

DDR_M1_D6 AK67

DDR_M1_D7 AK66

DDR_M1_D8 A F70

DDR_M1_D9 AF68

DDR_M1_D10AH71

DDR_M1_D11AH68

DDR_M1_D 12AF71

DDR_M1_D 13AF69

DDR_M1_D14AH70

DDR_M1_D15AH69

DDR_M1_D16AT 66

DDR_M1_D17AU66

DDR_M1_D18AP65

DDR_M1_D19AN65

DDR_M1_D20AN66

DDR_M1_D21AP66

DDR_M1_D 22AT65

DDR_M1_D23AU65

DDR_M1_D 24AT61

DDR_M1_D25AU61

DDR_M1_D26AP60

DDR_M1_D27AN60

DDR_M1_D28AN61

DDR_M1_D29AP61

DDR_M1_D30AT 60

DDR_M1_D31AU60

DDR_M1_D32AU40

DDR_M1_D 33AT40

DDR_M1_D34AT 37

DDR_M1_D35AU37

DDR_M1_D36AR40

DDR_M1_D37AP40

DDR_M1_D38AP37

DDR_M1_D39AR37

DDR_M1_D 40AT33

DDR_M1_D41AU33

DDR_M1_D42AU30

DDR_M1_D 43AT30

DDR_M1_D44AR33

DDR_M1_D45AP33

DDR_M1_D46AR30

DDR_M1_D47AP30

DDR_M1_D48AU27

DDR_M1_D49AT 27

DDR_M1_D 50AT25

DDR_M1_D51AU25

DDR_M1_D52AP27

DDR_M1_D53AN27

DDR_M1_D54AN25

DDR_M1_D55AP25

DDR_M1_D56AT 22

DDR_M1_D57AU22

DDR_M1_D58AU21

DDR_M1_D59AT 21

DDR_M1_D60AN22

DDR_M1_D61AP22

DDR_M1_D62AP21

DDR_M1_D63AN21

UC1C

DDR1_DQ[0]/DDR0_DQ [16]

DDR1_DQ[1]/DDR0_DQ [17]

DDR1_DQ[2]/DDR0_DQ [18]

DDR1_DQ[3]/DDR0_DQ [19]

DDR1_DQ[4]/DDR0_DQ [20]

DDR1_DQ[5]/DDR0_DQ [21]

DDR1_DQ[6]/DDR0_DQ [22]

DDR1_DQ[7]/DDR0_DQ [23]

DDR1_DQ[8]/DDR0_DQ [24]

DDR1_DQ[9]/DDR0_DQ [25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

SKL-U_BGA1356

+1.2V_VDDQ

DDR_DRAMRST#

12

SKL-U

DDR1_MA[5]/DD R1_CAA[0 ]/DDR1_MA[5]

DDR1_MA[9]/DD R1_CAA[1 ]/DDR1_MA[9]

DDR1_MA[6]/DD R1_CAA[2 ]/DDR1_MA[6]

DDR1_MA[8]/DD R1_CAA[3 ]/DDR1_MA[8]

DDR1_MA[7]/DD R1_CAA[4 ]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5] /DDR1_BG [0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_M A[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[ 14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_M A[16]

DDR1_BA[0]/DDR1_CAB[4] /DDR1_BA[0]

DDR1_MA[2]/DD R1_CAB[5 ]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6] /DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DD R1_CAB[8 ]/DDR1_MA[1]

DDR1_MA[0]/DD R1_CAB[9 ]/DDR1_MA[0]

DDRCH -B

3 OF 20

RC32

470_0402_5%

1 Rshort@2 DDR_DRAMRST#_R RC33

0_0402_5%

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0 ]

DDR1_CS#[1 ]

DDR1_ODT [0]

DDR1_ODT[1 ]

DDR1_MA[3]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6 ]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR_DRAMRST#_R <17,18>

AN45 DDR_M1_CLK#0

AN46 DDR_M1_CLK#1

AP45 DDR_M1_CLK0

AP46 DDR_M1_CLK1

AN56

DDR_M1_CKE1 AN55

AP53

BB42 DDR_M1_CS#0

AY42 DDR_M1_CS#1

BA42 DDR_M1_ODT0

AW42 DDR_M1_ODT 1

AY48 DDR_M1_MA5

AP50 DDR_M1_MA9

BA48 DDR_M1_MA6

BB48 DDR_M1_MA8

AP48 DDR_M1_MA7

AP52 DDR_M1_BG0

AN50 DD R_M1_MA12

AN48 DD R_M1_MA11

AN53 DDR_M1_ACT#

AN52 DD R_M1_BG1

BA43 DDR_M1_MA13

AY43 DDR_M1_MA15_CAS#

AY44 DDR_M1_MA14_WE#

AW44 DDR_M1_MA16_RAS#

BB44 DDR_M1_BA0

AY47 DDR_M1_MA2

BA44 DDR_M1_BA1

AW46 DDR_M1_MA10

AY46 DDR_M1_MA1

BA46 DDR_M1_MA0

BB46 DDR_M1_MA3

BA47 DDR_M1_MA4

AH66 DDR_M1_DQS#0

AH65 DDR_M1_DQS0

AG69 DDR_M1_DQS#1

AG70 DDR_M1_DQS1

AR66 DDR_M1_DQS#2

AR65 DDR_M1_DQS2

AR61 DDR_M1_DQS#3

AR60 DDR_M1_DQS3

AT38 DDR_M1_DQS #4

AR38 DDR_M1_DQS4

AT32 DDR_M1_DQS #5

AR32 DDR_M1_DQS5

AR25 DDR_M1_DQS#6

AR27 DDR_M1_DQS6

AR22 DDR_M1_DQS#7

AR21 DDR_M1_DQS7

AN43 D DR_M1_ALERT# AP43

DDR_M1_P AR

AT13 DDR_DRAMR ST# AR18

SM_RCOMP0 RC38 1

AT18 SM_RCOMP1 RC39 1

AU18 SM_RC OMP2 RC40 1

0CKER_M1_DD AP55

DDR_PG_CTRL 1

From ESD Team Request

DDR_M1_CLK#0 <18>

DDR_M1_CLK#1 <18>

DDR_M1_CLK0 <18>

DDR_M1_CLK1 <18>

DDR_M1_CKE0 <18>

DDR_M1_CKE1 <18>

DDR_M1_CS#0 <18>

DDR_M1_CS#1 <18>

DDR_M1_O DT0 < 18>

DDR_M1_O DT1 < 18>

DDR_M1_MA5 <18>

DDR_M1_MA9 <18>

DDR_M1_MA6 <18>

DDR_M1_MA8 <18>

DDR_M1_MA7 <18>

DDR_M1_B G0 <18>

DDR_M1_MA12 <18>

DDR_M1_MA11 <18>

DDR_M1_A CT# <1 8>

DDR_M1_B G1 <18>

DDR_M1_MA13 <18>

DDR_M1_MA15_CAS# <18>

DDR_M1_MA14_WE# <18>

DDR_M1_MA16_RAS# <18>

DDR_M1_B A0 <18>

DDR_M1_MA2 <18>

DDR_M1_B A1 <18>

DDR_M1_MA10 <18>

DDR_M1_MA1 <18>

DDR_M1_MA0 <18>

DDR_M1_MA3 <18>

DDR_M1_MA4 <18>

DDR_M1_DQS#0 <18>

DDR_M1_DQS0 <18>

DDR_M1_DQS#1 <18>

DDR_M1_DQS1 <18>

DDR_M1_DQS#2 <18>

DDR_M1_DQS2 <18>

DDR_M1_DQS#3 <18>

DDR_M1_DQS3 <18>

DDR_M1_DQS#4 <18>

DDR_M1_DQS4 <18>

DDR_M1_DQS#5 <18>

DDR_M1_DQS5 <18>

DDR_M1_DQS#6 <18>

DDR_M1_DQS6 <18>

DDR_M1_DQS#7 <18>

DDR_M1_DQS7 <18>

DDR_M1_A LERT# <18>

DDR_M1_P AR <18>

2 121_0402_1%

2 80.6_0402_1%

2 100_0402_1%

@ESD@

2

CC70 100P_0402_50V8J

Security Classification

IssuedDate

THI S S HE E T O F E NG IN EE RI NG DR AW IN G IS TH E P ROP RI ETA RY PR O PE RT Y OF C OM P AL E LE CTR ONI CS , I NC. A N D CON TA INS CONFIDENTSI

AN D TR AD E S EC RE T I NFO RM AT ION . THIS SH EE T MA Y N OT BE T RA NS FE R ED FR OM TH E CU S TOD Y OF T HE C OM P ET EN T DIV IS ION OF R & D

DE PA RTM EN T E XC EP T AS A UT HOR IZ ED BY C OM PA L EL EC TRO NIC S, IN C. NE ITH ER T HIS S HE ET N OR TH E I NF OR MA TI ON IT C ONT AIN S

5

4

MA Y BE U S ED BY OR DI SCL OS ED TO A NY TH IR D P AR TY W IT HO UT P RI OR W R IT TE N CO NS E NT OF C OM PA L EL EC TRO NIC S, IN C.

3

2017/04/10 2019/12/15

Compal Secret Data

DecipheredDate

Compal Electronics,Inc.

Title

iiiAzeLDocument Number

Custom

2

Date: Friday, January 05, 2018

SKL-U(2/12)DDRIII

EPK52_LA-G07EP

1

Sheet 6 of

Rev

v0.3

59

5

HOST_SPI_0_CLK AV2

<35> HOST_SPI_0_SO

<35> HOST_SPI_0_SI

D D

to SPI ROM UC2

C C

HOST_SPI_0_CS0#_R 1

HOST_SPI_0_CS0#_R 2

HOST_SPI_0_SO_R 3

HOST_SPI_0_SO_R 4

HOST_SPI_0_HOLD# 1

HOST_SPI_0_SI_R 2

HOST_SPI_0_SI_R 3

HOST_SPI_0_WP# 2 1 HOST_SPI_0_SIO2

SPI ROM ( 8MByteOnly)

HOST_SPI_0_CS0#_R 1

HOST_SPI_0_SO_R 2

HOST_SPI_0_WP# 3

ACES_91960-0084L_8P-T

Use socket footprint

B B

<35> HOST_SPI_0_CS2#

<33> EC_KBRST#

To TPM

<33,35> SERIRQ

RPH11

15_0804_8P4R_5%

RPH12

4

15_0804_8P4R_5%

RC388 15_0402_5%

UC2

CS# VCC

DO(IO1) HOLD#(IO3)

WP#(IO2) CLK

4

GND DI(IO0)

XM25QH64AHIG SOP 8P

SPI ROM Part:

SA0000B8300

Main:SA0000B8300, S IC FL 64M XM25QH64AHIG SOP 8P(XMC)

Source From

8 EC_SPI_CS0#

7 HOST_SPI_0_CS0#

6 EC_SPI_SO

5 HOST_SPI_0_SO

8 HOST_SPI_0_SIO3

7 HOST_SPI_0_SI

6 EC_SPI_SI

5

+3V_SPI

8

HOST_SPI_0_HOLD#

7

6

HOST_SPI_0_CLK_R

5

HOST_SPI_0_SI_R

2nd: SA000039A40, S IC FL 64M W25Q64JVSSIQ SOIC 8P SPI ROM(Winbond)

3th: SA00008SL00, S IC FL 64M MX25L6473FM2I-08G SOP 8P(MXIC)

4rd: SA00007LA10, S IC FL 64M GD25B64CSIGR SOP 8P SPI ROM(GigaDevice)

HOST_SPI_0_SO AW3

HOST_SPI_0_SI

HOST_SPI_0_SIO2 AW2

HOST_SPI_0_SIO3 AU4

HOST_SPI_0_CS0# AU3

HOST_SPI_0_CS2#

EC_KBRST#

SERIRQ

LPC Mode

EC_SPI_CS0# <33>

EC_SPI_SO <33>

EC_SPI_SI <33>

CC8

1 2 0.1U_0201_10V6K

AW13

AY11

AV3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

UC1E

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

CL INK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

4

SKL-U

LPC

2

QC1A

SMBCLK 6

L2N7002SDW1T1G 2N SC88-6

SMBDATA

SML1CLK 6 1

L2N7002SDW1T1G 2N SC88-6

SML1DATA 3 4

1

SB00001FF00

QC1B

3 4

L2N7002SDW1T1G 2N SC88-6

SB00001FF00

2

@

QC2A

SB00001FF00 @

QC2B

L2N7002SDW1T1G 2N SC88-6

SB00001FF00

SMBUS ,S MLINK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

5 OF20

+3VS +3VS

RC216

10K_0402_5%

5

+3VS

5

+3V_PRIM +3VALW

3 2

Rev_0.53

R7

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

RC215

10K_0402_5%

1 2

1 2

PCH_SMBCLK <17,18>

PCH_SMBDATA <17,18>

SMBCLK

R8

SMBDATA

SMBALERT#

R10

R9

SML0CLK

W2

SML0DATA

W1

SML0ALERT#

W3

SML1CLK

V3

SML1DATA

AM7 GPP_B23 1

AY13 LPC_AD0

LPC_AD1

BA13

LPC_AD2

BB13

LPC_AD3

AY12

LPC_FRAME#

BA12

SUS_STAT#

BA11

AW9 CLK_PCI0

AY9

PM_CLKRUN#

AW11

RC902@

0_0201_5%

TP@ T234

RC387 1 2 22_0402_5%

<DB> Un-pop QC2 for new 0x90 thermal sensor

EC_SMB_CK2 <10,33>

EC_SMB_DA2 <10,33>

TP@ T239

2 SML1ALERT#

LPC_AD0 <33>

LPC_AD1 <33>

LPC_AD2 <33>

LPC_AD3 <33>

LPC_FRAME# <33>

TP@ T2402

PM_CLKRUN# <33>

CC182

22P 50V J NPO 0402

EMI@

SML0ALERT# (Internal Pull Down):

eSPI or LPC

0 = LPC is selected for EC --> For KB9022/9032 Use

1 = eSPI is selected f or EC --> For KB9032 Only.

SMB

(Link to XDP, DDR, TP)

SML1

(Link to EC,DGPU, LAN, Thermal Sensor)

CLK_PCI_LPC <33>

1

2

SML0ALERT#

SML1ALERT# RC903 2 @ 1 150K_0402_1%

SML0ALERT# RC360 2 @ 1 10K_0402_5%

SMBALERT#

EC_KBRST#

To EC

SML0CLK

SML0DATA

SML1CLK

SML1DATA

SMBCLK

SMBDATA

HOST_SPI_0_SIO2 RC3901 @ 2 1K_0402_1%

HOST_SPI_0_SIO3 RC3911 @ 2 1K_0402_1%

HOST_SPI_0_CS0#_R 1 @ 2

HOST_SPI_0_SIO3 RC51 1 ES@ 2 1K_0402_1%

RPC19 10K_0804_8P4R_5%

RC49 1 2 499_0402_1%

RC50 1 2 499_0402_1%

RPC7

1

2

3

4

1K_0804_8P4R_5%

RC357 1K_0402_5%

12

8

7

6

5

RC218

1K_0402_1%

8

7

6

5

1

2

3

4

+3V_SPI

1

+3V_PRIM

+3VS

+3V_PRIM

From WW36 MOW for SKL-U ES sample

RC82

RC81

1 2

1 2

10K_0402_5%

TP_SMBCLK <34>

TP_SMBDATA <34>

PM_CLKRUN#

SERIRQ

1

RC107

1 2

RC122 8.2K_0402_5%

Follow 543016_SKL_U_Y_PDG_0_9

2

8.2K_0402_5%

+3VS_PGPPA

CLK Source CPU to SPI ROM UC2&EC

HOST_SPI_0_CLK 2 1 HOST_SPI_0_CLK_R

15_0402_5%

RC368 EMI@

1 2

CC9

10P_0402_50V8J

@EMI@

HOST_SPI_0_CLK_R <33,35>

2

SMBCLK 1

L2N7002SDW1T1G 2N SC88-6

SMBDATA

SB00001FF00

10K_0402_5%

6

QC7A

5

4 3

QC7B SB00001FF00

L2N7002SDW1T1G 2N SC88-6

EON SA000046400 S IC FL 64M EN25Q64-104HIP SOP 8P MXIC

SA00006N100 S IC FL 64M MX25L6473EM2I-10G SOP 8P

WINBOND SA000039A30 S IC FL 64M W25Q64FVSSIQ SOIC 8P SPI ROM

Micron SA00005L100 S IC FL 64M N25Q064A13ESEC0F SO8W 8P

A A

Security Classification

IssuedDate

THI S SHE ET O F ENGIN EERIN G DRAW IN G IS TH E P ROPRI ET ARY PRO PE RT Y OF C OMP AL E LECTRON ICS, INC . AND CONTAIN S CONFIDENTSSIAizL

AND TR ADE S ECRET INF OR MAT IO N. T HIS S HEET MAY N OT BE T RAN SF ERED FR OM T HE C USTO DY OF T HE C OMPET EN T DIVISION OF R &D

DEPAR TMENT E XCEPT AS AU TH OR IZED BY CO MP AL ELEC TR ON ICS , INC. NEIT HER THIS SHE ET N OR TH E INF OR MAT IO N IT CON TAINS

5

4

MAY BE U SED BY OR DISC LOS ED TO A NY T HI RD PA RT Y WI TH OUT PR IO R WRIT TEN CONS EN T OF CO MPAL E LECTRON IC S, INC.

3 2

2017/04/10 2019/12/15

Compal Secret Data

DecipheredDate

Compal Electronics, Inc.

Title

SKL-U(3/12)SPI,ESPI,SMB,LPC

e Document Number

Custom

EPK52_LA-G07EP

1

Rev

Sheet 7 of 59Date: Friday, January 05, 2018

v0.3

5

4

3 2

1

1 @ 2 RC380 1

9 OF20

SKL-U

7 OF20

1K_0402_1%

@

D

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

SDIO/SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

RC367 1 Rshort@20_0402_5%

2

G

3 HDA_SDOUT

QC380

S

MESS138W-G_SOT323-3

Rev_0.53

C37

CSI2_CLKN0

D37

CSI2_CLKP0

C32

CSI2_CLKN1

D32

CSI2_CLKP1

C29

CSI2_CLKN2

D29

CSI2_CLKP2

B26

CSI2_CLKN3

A26

CSI2_CLKP3

E13 CSI2_COMP RC80 2

CSI2_COMP

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1 EMMC_RCOMP2

Rev_0.53

GPP_G7/SD_WP

SD_RCOMP

GPP_F23

AB11

VRAMCLK_SEL

AB13

PROJECT_ID

AB12

PLAT_SEL0

W12

PLAT_SEL1

W11

W10

W8

W7

BA9

BB9

AB7 SD_RCOMP RC76 2

AF13 SOC_GPIOF17

1 200_0402_1%

T235 TP@

HDA_SDOUT:

ME Flash Descriptor Security Override

Low : Disabled(Default)

High : Enabled

1 100_0402_1%

1

RC89

200_0402_1%

+3V_PRIM

12

PX@ RC127

10K_0402_5%

12

RC128

UMA@ 10K_0402_5%

X76 BOM control RAM size

Net Name

VRAMCLK_SEL

PLAT_SEL0

4G 2G

1 0

PLAT_SEL0

PLAT_SEL1

PLAT_SEL1

0 1

0 KBL-U KBL-R

1 SKL-U NA

PROJECT_ID

VRAM Clock

VRAMCLK_SEL

KBLR@

1 2

KBLU@

1 2

SKYL@

RC918

10K_0402_5%

SD028100280

2G VRAM 4GVRA M

RC919

10K_0402_5%

RC918

10K_0402_5%

UMA DIS

0

0

+3V_PRIM

RC900

X76@

10K_0402_5%

1 2

RC901

X76@

10K_0402_5%

1 2

+3V_PRIM

SKYL@

RC916

10K_0402_5%

1 2

KBLU@

RC917

10K_0402_5%

1 2

KBLR@

RC917

10K_0402_5%

SD028100280

1

1

UC1G

D D

<32> HDA_SDIN0

T38 TP@

T39 TP@

<10,32> HDA_SPKR

C C

HDA forAUDIO

1 8

EMI@

22P 50V J NPO0402

@R

F@

22P 50V J NPO0402

2

3

4

<32> HDA_SYNC_R

<32> HDA_RST#_R

<32> HDA_SDOUT_R

<32> HDA_BIT_CLK_R

CC143

EMI request

B B

A A

CC183

HDA_SYNC

HDA_BIT_CLK AY22

HDA_SDOUT

HDA_SDIN0

HDA_RST#

SOC_GPIOF1

SOC_GPIOF0

HDA_SPKR

RPC9

7 HDA_SYNC

6 HDA_RST#

5 HDA_SDOUT

33_0804_8P4R_5%

2 EMI@ 1 HDA_BIT_CLK

RC383 33_0402_5%

BA22

HDA_BLK/I2S0_SCLK

BB22

BA21

AY21

AW22

J5

AY20

AW20

AK7

AK6

AK9

AK10

H5

D7

D8

C8

AW5

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C2

D2

A27

B27

C27

D27

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356

+3V_HDA

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

8

CSI2_DN9

8

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL-U_BGA1356

<33> ME_FLASH_EN

SKL_ULT

Security Classification

Issued Date

THIS SHEET OF ENG IN EERIN G DRAWING IS TH E P RO PRIET AR Y P RO PERTY O F COMPA L ELECTRONICS, INC . AND CO NTAINS CONFIDENSSTiIzAeL

AND TR ADE S EC RET INFORMATI ON. T HIS SHEET MAY NO T BE TR ANSFE RED FROM TH E CU ST ODY OF T HE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AU TH OR IZED BY COMP AL EL ECTRON ICS , IN C. NEITHER THI S SHEET N OR THE INFORMA TION IT CONTAINS

MAY BE U SED BY OR DISCLOSED TO A NY T HIRD PA RT Y WITHOU T PRIOR W RITTEN CONSEN T OF COMPA L ELECTRONI CS, IN C.

5

4

2017/04/10 2019/12/15

3 2

Compal Secret Data

Deciphered Date

Compal Electronics,Inc.

Title

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

DocumentNumber

Custom

EPK52_LA-G07EP

Date: Friday, January 05, 2018 Sheet

1

Rev

v0.3

59

of

8

+RTCVCC

RC91 1

CC10 1 2 1U_0402_6.3V6K

CLRP1 1 2 SHORT PADS

RC93 1 2 20K_0402_5% PCH_RTCRST#

CC11 1 2 1U_040 2_6.3V6K

CLRP2 1 2 SHORT PADS

D D

C C

B B

A A

RC941 2 1M_0402 _5% SM_INTRUDER#

PCH_RT CRST# 2

0_0402_5%

PCH_SRT CRST# 2

0_0402_5%

+3VS

RC165

RC105

+3VALW _DSW

RC925

RC926

+3V_PRIM

RC927

RC928

CLRP3 SHORT PADS

RC100 1K_0402_5%

RC101

+3VALW _DSW

+3V_PRIM

+3VALW _DSW

RC111 2 @ 1 100K_0402_5% PBTN_O UT#

From EC(open -dra in)

<33,40> EC_VCCST_PG_R

5

2 20K_0402_5% PCH_SRTCRST #

CLR ME

CLR CMOS

1

R1088

1

R1089

1

1

RPC10

8

7

6

5

10K_0804_8P4R_5%

1

1

1

1

2 1 SYS_RESET#

1 @ 2 SUSCLK

2

1

RC103

1

RC104

1 @ 2 AC_PRESENT_R

RC106

12

Clear CMOS close to RAM door

@

JCMOS1

0_0603_5%

CLKREQ_PCIE#4

2

10K_0402_5%

2 CLKREQ_PCIE#5

10K_0402_5%

1 CLKREQ_PCIE#1

2 CLKREQ_PCIE#2

3 CLKREQ_P EG#0

4 CLKREQ_PCIE#3

PCH_PW ROK

2

10K_0402_5%

2 LAN_WAKE#

10K_0402_5%

2 PCH_RSMRST#

10K_0402_5%

2 SYS_RESET #

10K_0402_5%

1 PCH_DPWROK

100K_0402_5%

2

8.2K_0402_5%

2 WAKE#

1K_0402_5%

10K_0402_5%

2 10K_0402_5% SO C_VRALERT#RC1151 @

+1.0V_VCCST

5

PM_BATLOW#

CLR_CMOS# <33>

From 545659_SKL_PCH_U_Y_EDS_R0_7

<Cocoa_1027>

check u n-use G PIO for termi nation guidance

DS12

2

1 PCH_PWROK

CK0402101V05_0402-2

ESD@

SCV00001K00

Only Fo r Power Sequen ce Debug

<33> SUSACK#

ESD@

DS13

SCV00001K00

1

CK0402101V05_0402-2

DS14

1

CK0402101V05_0402-2

ESD@

C5229 1 2

0.1U_0402_25V6

12

RC113

1K_0402_5%

RC1161

2 60.4_0402_ 1% EC_VCCST _PG

2 H_CPUPW RGD

@ESD@

SCV00001K00

2 SUSACK#

SYS_PW ROK

4

LAN

WLAN

PCIe SSD

PCH

PLTRST

Buffer

PLT_RST#_PCH

2 Rshort@

RC110 0_0402_5%

4

<29> CLK_PCIE_N1

<29> CLK_PCIE_P1

<29> CLKREQ_PCIE#1

<30> CLK_PCIE_N2

<30> CLK_PCIE_P2

<30> CLKREQ_PCIE#2

<31> CLK_PCIE_N4

<31> CLK_PCIE_P4

<31> CLKREQ_PCIE#4

RC99 1 2 0_0402_5%

+3VS

5

@ UC8 0.1U_0201_ 10V6K

1

IN1

2

IN2

G P

SN74AHC1G08DCKR_SC70-5

3

T296 TP@

<33> PCH_ RSMRST#

RC102 1 @ 2 1K_0402_5% H_CPUPW RGD A68

<33> SYS_PWROK

<33> PCH_PW ROK

<33> PCH_SUSW ARN#

1

<30> WAKE#

3

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKREQ_PEG#0

CLK_PCIE_N1

CLK_PCIE_P1

CLKREQ_PCIE#1

CLK_PCIE_N2

CLK_PCIE_P2

CLKREQ_PCIE#2

CLKREQ_PCIE#3

CLK_PCIE_N4

CLK_PCIE_P4

CLKREQ_PCIE#4

CLKREQ_PCIE#5 AU7

@

CC145

1 2

4

O

PLT_RST#_PCH

SYS_RESET#

PCH_RSMR ST#

EC_VCCST_PG B65

SYS_PW ROK

PCH_PW ROK

PCH_DPW ROK_R BB20

PCH_SUSWARN#

SUSACK#_ R

WAKE#

LAN_WAKE#

T94 TP@

PCH_RSMR ST# PCH_PW ROK

<33> PCH_DP WROK

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

PLT_RST#

PLT_RST# <29,30,31,33,35>

UC1K

AN10

GPP_B13/PLTRST #

B5

SYS_RESET#

AY17

RSMRST#

PROCPW RGD

VCCST_PWRGD

B6

SYS_PW ROK

BA20

PCH_PW ROK

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

DC3 SCS00000Z00

RB751V-40 SOD-323

1 2

2

DC41SCS00000Z00

RB751V-40 SOD-323

Security Classification

THI S S HE E T O F E NG IN EE RI NG DR AW IN G IS TH E P ROP RI ETA RY PR O PE RT Y OF C OM P AL E LE CTR ONI CS , I NC. A N D CON TA INS CONFIDENTSI

AN D TR AD E S EC RE T I NFO RM AT ION . THIS SH EE T MA Y N OT BE T RA NS FE R ED FR OM TH E CU S TOD Y OF T HE C OM P ET EN T D IV ISI ON OF R &D

DE PA RTM EN T E XC EP T AS A UT HOR IZ ED BY C OM PA L EL EC TRO NIC S, IN C. NE ITH ER T HIS S HE ET N OR TH E I NF OR MA TI ON IT C ONT AIN S

MA Y BE U S ED BY OR DIS CL OS ED TO A NY TH IRD PA R TY W IT HO UT P RI OR W R IT TE N C ON S EN T OF CO MP A L E LE CTR ONI CS , I NC.

3

SYSTEM POWERMANAGEMENT

RC112 0_0402_5%

IssuedDate

2

SKL_ULT

CLOCKSIGNALS

10 OF 20

PCH_KBLU24_OUT RX2 2 1 33_0402_1% PCH_XTAL24U_OUT 1 2

SKL-U

GPP_B11/EXT_PW R_GAT E#

11 OF 20

SPOK <48>

2 Rshort@1 PCH_DPW ROK_R

2017/04/10 2019/12/15

Rev_0.53

CLKOUT _ITPXDP _N

CLKOUT _ITPXDP _P

GPP_B12/SLP_S0#

GPD9/SL P_WLAN#

GPD1/AC PRESENT

GPP_B2/VRALERT#

F43

E43

GPD8/SU SCLK

XCLK_BIASREF

GPD4/SL P_S3#

GPD5/SL P_S4#

GPD10/SLP_S5#

GPD3/PW RBTN#

GPD0/BATLOW #

GPP_A11/PME#

BA17 SUSCLK

E37 PCH_KBLU24_IN

XTAL24_IN

E35 PCH_KBLU24_OUT

XTAL24_OUT

E42 XCLK_BIASREF RC96 1 2 2.7K_0402_1%

AM18 PCH_RTCX1

RTCX1

AM20 PCH_RTCX2

RTCX2

AN18 PC H_SRTCRST#

SRTCRST#

AM16 PCH_RTCRST#

RTCRST#

<DB> Add RX1~4 for KBL U/R Colay

Change XTAL(YC1) to 2016 Type

PCH_KBLU24_IN RX1 2 1 33_0402_1% PCH_XTAL24U_IN

KBLU@ KBLU@

KBLU@

CC12

24MHzPa rrrrrrtttttt::::::

Maiiiiiin::::::SJ10000X700,,,,,, S CRYSTAL 24MHZ 18PF

+--20PPM8Y24000033((((((TXC))))))::::::2......0x1......6mm

2nd:::::: SJ10000TK00,,,,,, SCRYSTAL 24MH Z 18PF

+--20PPM7M24000027((((((TXC))))))::::::3......2x2......5mm

Rev_0.53

AT11 PM_SLP_S0#

AP15 PM_SLP_S3#

BA16 PM_SLP_S4#

AY16 PM_SLP_S5#

AN15 PM_SLP_SUS#

SLP_SUS#

AW15

SLP_LAN#

BB17

AN16 PM_SLP_A#

GPD6/SL P_A#

BA15 PBTN_O UT#

AY15 AC_PRESENT_R 2

AU13 PM_BATLO W# RC108

AU11 EC_ PCIE_WAKE#_CPU

AP16 SM_INT RUDER#

INTRUD ER#

AM10 EXT_PW R_GATE#

AM11 SOC _VRALERT #

Compal Secret Data

DecipheredDate

2

SUSCLK <30>

KBLU@

RC92 1M_0402_5%

YC1 KBLU@

24MHZ 18PF XRCGB2 4M000F2P5 1R0

3

3

SJ10000UJ00

27P_0402_50V8

J

PM_SLP_SUS# <33>

RC922 0_0402_5%

TP@T 298

NC NC

4 2

PBTN_O UT# <33>

1

0_0402_5%

2 @ 1

1

1

PM_SLP_S3 # <12,33,4 0>

PM_SLP_S4 # <12,33,4 0,49>

PM_SLP_S5 # <33>

Title

iiiAzeLDocument Number

Custom

1

+1.0V_CLK5_F24NS

KBLU@

CC13

27P_0402_50V8

J

XCLK_BIASREF

PCH_RTCX2

PCH_RTCX1

RC97 1 @ 2 60.4_0402_1%

RC98 10M_0402_5%

32.768KHZ 9PF 10PPM 9H03200055

SJ10000Q800

6.8P 50V C NPO 0402

CC15

1

SE07168AC80

2

<SI> CC15/CC16 SI change 3.9p=>6.8p

TP@T254

TP@T255

TP@T256

TP@T257

TP@T 258

ACIN <33>

EC_PCIE_WAKE# <30,33>

Compal Electronics,Inc.

SKL-U(5/12)CLK,GPIO

EPK52_LA-G07EP

1

1 2

YC2

1 2

Sheet 9 of 59Date: Friday, January 05, 2018

6.8P 50V C NP O0402

1

SE07168AC80

2

CC16

Rev

v0.3

5

4

3

2

1

UC1F

LPSS ISH

AN8

GPP_B15/GSPI0_C S#

AP7

GPP_B16/GSPI0_CLK

AP8

GSPI0_MOSI

D D

TP@T129

TP@T128

<30> WL_ OFF#

TP@T133

TP@T132

UART_2_CTXD_DRXD

12

R5194

@

0_0402_5%

UART_2_CRXD_DTXD

C C

SOC_GPIOB21

GSPI1_MOSI

UART_0_CRXD_DTXD

UART_0_CTXD_DRXD

WL_O FF#

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

Functional Strap Definitions

SPKR (Internal Pul l Down):

TOP Swap Override

0 = Disable TOP Swap mode.--->AAX05 Use

1 = Enable TOP Swap Mode.

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_C S#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/ UART0_RXD

AB2

GPP_C9/ UART0_TXD

W4

GPP_C10 /UART0_RTS#

AB3

GPP_C11 /UART0_CTS#

AD1

GPP_C20 /UART2_RXD

AD2

GPP_C21 /UART2_TXD

AD3

GPP_C22 /UART2_RTS#

AD4

GPP_C23 /UART2_CTS#

U7

GPP_C16 /I2C0_SD A

U6

GPP_C17 /I2C0_SC L

U8

GPP_C18 /I2C1_SD A

U9

GPP_C19 /I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKL-U_BGA1356

Strap Pin

+3VS

RC117 1 @ 2 100K_0402_5% HDA_SPKR

RC118 1 @ 2 4.7K_0402_5% GSPI0_MO SI

RC201 1 @ 2 150K_0402_1% GSPI1_MO SI

GSPI0_MOSI (Internal Pull Down):

SKL-U

GPP_D5/ ISH_I2C0_ SDA

GPP_D6/ ISH_I2C0_ SCL

GPP_D7/ ISH_I2C1_ SDA

GPP_D8/ ISH_I2C1_ SCL

GPP_F10/I2C5_SDA /ISH_ I2C2_SD A

GPP_F11/I2C5_SCL /ISH_I2C2_SC L

GPP_D13 /ISH_UART 0_RXD/SML0BDAT A/I2C4 B_SDA

GPP_D14 /ISH_UART 0_TXD/SML0BCL K/I2C4B_SCL

6 OF 20

GPP_D15 /ISH_UART 0_RTS#

GPP_D16 /ISH_UART 0_CTS#/SML0BALERT#

GPP_C12 /UART1_RXD/ISH_UART1_R XD

GPP_C13 /UART1_TXD/ISH _UART1_TXD

GPP_C14 /UART1_RTS#/ISH_UART1_RTS#

GPP_C15 /UART1_CTS#/ISH_UART1_CTS#

GPP_A12/BM_BUSY#/ISH_G P6

HDA_SPKR <8,32 >

Rev_0.53

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

DGPU_HOLD_RST#

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13 SOC_GPIOA12

TS_GPIO_CPU <27>

DGPU_PWR_EN <33>

ODD_PW R <37>

ODD_DA# <37>

T122 TP@

CPU THERMAL SENSOR

Address : 0x48

UC3

<7,33> EC _SMB_CK2 EC_SMB_DA 2 <7 ,33>

1

SMBCLK SMBDATA

2

GND

ALERT#

G753T 11U_SOT 23-5

SA00008C H00

<DB> Change Thermal Sensor IC

5

43

+Vs

+3VS

1

CC127

0.1U_0201_10V6K

2

<5,33> NMI_DBG#_CPU

DGPU_PWR_EN RC382 1

RPC14

WL_O FF# 2

SOC_GPIOB21 3

NMI_DBG#_CPU 4

DGPU_HOLD_RST# RC923 1 @ 2 10K_0402_5%

ODD_PW R

ODD_DA#

1

10K_0804_8P4R_5%

RC929 1 2 10K_0402_5%

RC930 1 2 10K_0402_5%

2 10K_0402_5%

8

7

6

5

+3VS

+3V_PRIM

+3VS

No Reboot

0 = Disable No Reboot mode. --> AAX05 Use

1 = Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This function is useful

when running ITP/XDP.

B B

GSPI1_MOSI (Internal PullDown):

Boot BIOS StrapBit

0 = SPI Mode --> AAX05 Use

1 = LPC Mode

A A

Security Classification

Issued Date

THI S S HE E T O F E NG IN EE RI NG DRA W ING I S THE PR OP RI ET AR Y P RO PE R TY OF CO MP AL E LE CTR ON ICS , INC . AN D C ONT AIN S CONFIDENTSIiiAzeL

AN D TR AD E S EC RE T I NFO RM AT ION . THIS S HE ET M AY N OT BE TR AN SF E RE D F RO M TH E C US TO DY OF TH E CO MP E TE NT D IVI SIO N OF R &D

DE PA RTM EN T EX C EP T AS A UT HO RI ZE D BY C OM PA L EL ECT RON IC S, IN C. NE ITH ER THI S S HE ET N OR TH E I NF OR MA TI ON IT CO NTA IN S

5

4

MA Y BE U S ED BY OR DIS CL OS ED TO A NY TH IRD PA R TY W IT HO UT P RI OR W R IT TE N C ON SE N T OF CO MP A L E LEC TR ONI CS , IN C.

3

2017/04/10 2019/12/15

Compal Secret Data

DecipheredDate

Compal Electronics,Inc.

Title

SKL-U(6/12)GPIO

Document Number

Custom

2

EPK52_LA-G07EP

Sheet 10 of 59Date: Friday, J anuary 05, 2018

1

Rev

v0.3

5

4

3 2

1

UC1H

PCIE/USB3/SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

D D

<29> PCIE_CRX_DTX_N5

*PCIe for DeviceDown

Place AC coupling capacitors very close toeither

the transmitter or the receiver.

*TX/RX with Cap

LAN

*PCI Express* Connector

Place AC caps closer to the PCIe*connector.

*Only TX with Cap, RX Cap on Add inCard

WLAN

HDD

C C

ODD

M.2 SSD

*For PCIe* Gen 3/ SATA multiplexedconfiguration,

motherboard Tx requires a 220 nF

AC capacitor and NO AC capacitor is requiredfor

motherboard Rx channel. This option DOES NOT

support DC coupled ODDs / Devices.

*Place AC caps closer to the M.2connector.

*Only TX with Cap, RX Cap on Add in Card

B

A A

<29> PCIE_CRX_DTX_P5

<29> PCIE_CTX_C_DRX_N5

<29> PCIE_CTX_C_DRX_P5

<30> PCIE_CRX_DTX_N6

<30> PCIE_CRX_DTX_P6

<30> PCIE_CTX_C_DRX_N6

<30> PCIE_CTX_C_DRX_P6

<37> SATA_CRX_DTX_N0

<37> SATA_CRX_DTX_P0

<37> SATA_CTX_DRX_N0

<37> SATA_CTX_DRX_P0

<37> SATA_CRX_DTX_N1

<37> SATA_CRX_DTX_P1

<37> SATA_CTX_DRX_N1

<37> SATA_CTX_DRX_P1

<31> PCIE_CRX_DTX_N11

<31> PCIE_CRX_DTX_P11

<31> PCIE_CTX_C_DRX_N11

<31> PCIE_CTX_C_DRX_P11

<31> PCIE_CRX_DTX_N12

<31> PCIE_CRX_DTX_P12

<31> PCIE_CTX_C_DRX_N12

<31> PCIE_CTX_C_DRX_P12

CC177 2

CC176 2

CC175 2

CC174 2

RC120 1

<5> XDP_PREQ#

CC178 0.22U 6.3V K X5R 0402 2 1

CC179 0.22U 6.3V K X5R 0402 2 1

CC180 0.22U 6.3V K X5R 0402 2 1

CC181 0.22U 6.3V K X5R 0402 2 1

1 0.1U_0402_16V7K

1 0.1U_0402_16V7K

1 0.1U_0402_16V7K

1 0.1U_0402_16V7K

2 100_0402_1% PCIE_RCOMPN

XDP_PREQ#

SOC_GPIOA7

PCIE_CRX_DTX_N5 F16

PCIE_CRX_DTX_P5 E16

PCIE_CTX_DRX_N5 C19

PCIE_CTX_DRX_P5 D19

PCIE_CRX_DTX_N6 G18

PCIE_CRX_DTX_P6 F18

PCIE_CTX_DRX_N6 D20

PCIE_CTX_DRX_P6 C20

PCIE_RCOMPP

PCIE_CRX_DTX_N11 E28

PCIE_CRX_DTX_P11 E27

PCIE_CTX_DRX_N11 D24

PCIE_CTX_DRX_P11 C24

PCIE_CRX_DTX_N12 E30

PCIE_CRX_DTX_P12 F30

PCIE_CTX_DRX_N12 A25

PCIE_CTX_DRX_P12 B25

When PCIE8/SATA1A is used

as SATA Port 1 (ODD), then

PCIE11/SATA1B (M.2 SSD)

cannot be used as SATA

Port 1.

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

PCIE5_RXN

PCIE5_RXP

PCIE5_TXN

PCIE5_TXP

PCIE6_RXN

PCIE6_RXP

PCIE6_TXN

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

PCIE11_RXN/SATA1B_RXN

PCIE11_RXP/SATA1B_RXP

PCIE11_TXN/SATA1B_TXN

PCIE11_TXP/SATA1B_TXP

PCIE12_RXN/SATA2_RXN

PCIE12_RXP/SATA2_RXP

PCIE12_TXN/SATA2_TXN

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

Security Classification

Issued Date

THIS SHEET OF ENG IN EERIN G DRAWING IS TH E P RO PRIET AR Y P RO PERTY O F COMPA L ELECTRONICS, INC . AND CO NTAINS CONFIDENSSTiiIzzAeL

AND TR ADE S EC RET INFORMATI ON. T HIS SHEET MAY NO T BE TR ANSFE RED FROM TH E CU ST ODY OF T HE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AU TH OR IZED BY COMP AL EL ECTRON ICS , IN C. NEITHER THI S SHEET N OR THE INFORMA TION IT CONTAINS

MAY BE U SED BY OR DISCLOSED TO A NY T HIRD PA RT Y WITHOU T PRIOR W RITTEN CONSEN T OF COMPA L ELECTRONI CS, IN C.

5

4

3 2

SKL-U

8 OF20

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

Rev_0.53

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6 USB2_COMP

AG3 USB2_ID

AG4 USB2_VBUSSENSE

A9 USB_OC0#

C9 USB_OC1#

D9 USB_OC2#

B9 USB_OC3#

J1

J2 DEVSLP1

J3

H2 SATA_GP0

H3 ODD_PLUG#

G4 SSD1_IF

H1

GPIO DEVICE CONTROL

USB_OC0#

USB_OC1#

USB_OC2#

USB2 Port 1 and Port 2

USB2 Port 3

N/A

USB_OC3# N/A

DEVSLP0

DEVSLP1

DEVSLP2

SATA_GP0

SATA_GP1

SATA_GP2

2017/04/10 2019/12/15

N/A

N/A

NGFF SSD KEY- M

N/A

ODD_PLUG#

PCIE/SATA

Compal Secret Data

Deciphered Date

DEVSLP0

USB3_CRX_DTX_N1 <38>

USB3_CRX_DTX_P1 <38>

USB3_CTX_DRX_N1 <38>

USB3_CTX_DRX_P1 <38>

USB3_CRX_DTX_N2 <38>

USB3_CRX_DTX_P2 <38>

USB3_CTX_DRX_N2 <38>

USB3_CTX_DRX_P2 <38>

USB20_N1 <38>

USB20_P1 <38>

USB20_N2 <38>

USB20_P2 <38>

USB20_N3 <39>

USB20_P3 <39>

USB20_N4 <39>

USB20_P4 <39>

USB20_N5 <27>

USB20_P5 <27>

USB20_N6 <30>

USB20_P6 <30>

USB20_N7 <27>

USB20_P7 <27>

RC119 1 2 113_0402_1%

T241 TP@

Title

DocumentNumber

Custom

USB2.0/USB3.0

USB2.0/USB3.0

USB2.0

CardReader

Camera

BT

TS

USB2_ID

DEVSLP2 <31>

ODD_PLUG# <37>

SSD1_IF <31>

SATA_LED# <39>

DEVSLP1

SOC_GPIOA7

SATA_LED# 1 8

SATA_GP0 2 7

SSD1_IF 3 6

ODD_PLUG# 4 5

USB_OC1# 1 8

USB_OC3# 2 7

USB_OC0# 3 6

USB_OC2# 4 5

USB2_VBUSSENSE1

RC3621

RC361 10K_0402_5%

Compal Electronics,Inc.

SKL-U(7/12)PCIE,USB,SATA

EPK52_LA-G07EP

USB2.0/USB3.0

USB2.0/USB3.0

RC20 1 Rshort@20_0402_5%

Rshort@2

RC21 0_0402_5%

2

1

2 10K_0402_5%

RPC13

10K_0804_8P4R_5%

RPC20

10K_0804_8P4R_5%

Sheet

11 of 59Date: Friday, January 05,2018

1

+3VS

+3V_PRIM

Rev

v0.3

B

5

4

3 2

1

+1.0V_PRIM TO +1.0V_VCCSTU

+1.2V_VDDQ

+5VALW

1U_0402_6.3V6K

1

CC98

0.1U_0402_25V6

D D

<33,40,49> SYSON

<9,33,40,49>PM_SLP_S4#

<33,40,49> SUSP#

<9,33,40> PM_SLP_S3#

C C

RC142 1 2 0_0402_5%

RC144 1 @ 2 0_0402_5%

RC168 1 2 0_0402_5%

RC194 1 @ 2 0_0402_5%

1

2

@

CC151

2

+1.8V_PRIM

1

@

2

1U_0402_6.3V6K

CC99

1U_0402_6.3V6K

1

CC97

I (Max) : 0.04 A(+1.0V_VCCSTU)

@

RON(Max) : 25 mohm

2

V drop : 0.001 V

UC5

1

VIN1

2

EN_1.0V_VCCSTU 3

4

EN_1.8VS

5

ON2

6

VIN2

7

EM5209VF_DFN14_2X3

SA00007PM00

I (Max) : 0.536 A(+1.8VS)

RON(Max) : 25 mohm

V drop : 0.013 V

VIN1

ON1

VBIAS

VIN2

+1.0V_PRIM

14

VOUT1

13

VOUT1

VOUT2

VOUT2

12 1.0V_VCCSTU_CT1 1 2

CT1

11 10P_0402_50V8J

GND

10

CT2

9

8

15

GPAD

@ 2 0_0603_5%

R51881

CC95

1.8VS_CT2 1 2

@CC94