Page 1

Page 2

TM 11-6625-2941-14&P

TECHNICAL MANUAL

OPERATOR’S, ORGANIZATIONAL, DIRECT SUPPORT,

AND GENERAL SUPPORT MAINTENANCE MANUAL

INCLUDING REPAIR PARTS AND SPECIAL TOOLS LIST

FOR

COUNTER, ELECTRONIC, DIGITAL READOUT

AN/USM-459

(HEWLETT-PACKARD MODEL 5328A/E42)

(NSN 6625-01-061-8928)

HEADQUARTERS, DEPARTMENT OF THE ARMY

MARCH 1979

Page 3

Page 4

This manual contains copyright material reproduced by permission of the

Hewlett-Packard Company.

TM 11-6625-2941-14 + P

Technical Manual

No. 11-6625-2941-14 + P

OPERATOR’S, ORGANIZATIONAL, DIRECT SUPPORT, AND

GENERAL SUPPORT MAINTENANCE MANUAL INCLUDING

REPAIR PARTS AND SPECIAL TOOLS LIST

COUNTER, ELECTRONIC, DIGITAL READOUT

You can improve this manual by recommending improvements using

DA Form 2028-2

tear out the self-addressed form, fill it out as shown on the

sample, fold it where shown, and drop it in the mail.

If there are no blank DA Forms 2028-2

your manual, use the standard DA Form 2028 (Recommended Changes to

Publications and Blank Forms) and forward to the Commander, US

Army Communications and Electronics Materiel Readiness Command,

ATTN:

DRSEL-ME-MQ, Fort Monmouth, New Jersey 07703.

HEADQUARTERS,

DEPARTMENT OF THE ARMY

Washington, DC 28 March 1979

FOR

AN/USM-459

(HEWLETT-PACKARD MODEL 5328A/E42)

(NSN 6625-01-061-8928)

REPORTING OF ERRORS

located in the back of the manual.

simply

in the back of

In either case a reply will be furnished direct to you.

s

This manual is an authentication of the manufacturer

commercial literature

which, through usage, has been found to cover the data required to operate

and maintain this equipment.

The manual was not prepared in accordance with

military specifications; therefore, the format has not been structured to

consider categories of maintenance.

TABLE OF CONTENTS

Section

0

INTRODUCTION

Page

0-1 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0-1

0-2 Indexes of Publications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0-1

0-3 Forms and Records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0-1

0-4 Reporting Equipment Improvement Recommendations (EIR) . . 0-1

0-5 Administrative Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0-1

0-6 Destruction of Army Electronics Material . . . . . . . . . . . . . . . . . . . . . . . 0-1

i/ii (blank)

Page 5

Page 6

TABLE OF CONTENTS

Model 5328A

Table of Contents

Section

I

II INSTALLATION

Ill

GENERAL INFORMATION

1-1.

1-4.

1-6.

1-8.

1-16. Equipment Supplied and Accessories Available

1-18. Specifications

2-1.

2-3.

2-5.

2-6.

2-8.

2-10.

2-13.

2-15.

2-17.

2-19. Packaging for Shipment

2-20.

2-24.

2-26. Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OPERATION (OPERATORS INSTRUCTIONS)

3-1.

3-3.

3-9.

3-13. Time Interval Measurements

3-20. Ratio Measurements

3-23. Operating Controls

3-26. Function of Controls, Indicators, Inputs, and Outputs

3-27.

3-29.

3-31.

3-33.

3-35.

3-37.

3-41.

3-44.

3-49.

3-51.

3-53.

3-57.

3-59.

3-61.

3-63.

3-65.

3-68. Programming Operation

3-71. Setting Add dress Switches

3-75. Measurement Output Format

3-77. Bus Commands

3-79. Programming Examples

Scope of Manual . .

Description

Instrument Identification

Applications

Introduction

Unpacking and Inspection

Preparation for Use

Introduction

Frequency Measurements

Period Measurements

Trigger Lights

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Requirements

Fuse Replacement and Installation

Power Cables . .

Operating Environment

Bench Operation

Rack Mounting

Original Packaging

Other Packaging Methods

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Display

Power (Line)

Reset

Sample Rate Control

Arming

Frequency Resoluton, N Switch

Input Channel Section

A and B Channel Signal Conditioning

Channel C Input

“C’’ Channel Overload Indicator . . . . . . . . . . . . . . . . . . . . . . . .

Hysteresis Band of Trigger Levels

External Frequency Standard Input. . . . . . . . . . . . . . . . . . . . . . . .

Marker Outputs

Gate/Marker Out . .

1 MHz and 10 MHz Frequency Standard Outputs

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page

1-1

1-1

1-1

1-1

1-2

1-2

1-2

2-1

2-1

2-1

2-1

2-1

2-1

2-1

2-2

2-2

2-2

2-2

2-2

2-3

2-3

3-1

3-1

3-1

3-2

3-3

3-4

3-4

3-8

3-8

3-8

3-8

3-8

3-8

3-9

3-10

3-10

3-12

3-12

3-12

3-12

3-13

3-13

3-13

3-13

3-13

3-13

3-16

3-16

3-18

iii

Page 7

Model 5328A

Table of Contents

TABLE OF CONTENTS (Continued)

Section

IV

Page

THEORY OF OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4-1.

4-3.

4-5.

4-7.

4-15.

4-18.

4-20.

4-22.

4-24.

4-27.

4-34.

4-36.

4-41.

4-43.

4-48.

4-52.

4-57.

4-60.

4-62.

4-64.

4-67.

4-69.

4-17.

4-73.

4-75.

4-79.

4-83.

4-85.

4-89.

4-91.

4-94.

4-96.

4-99.

4-103. A16 Display Assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

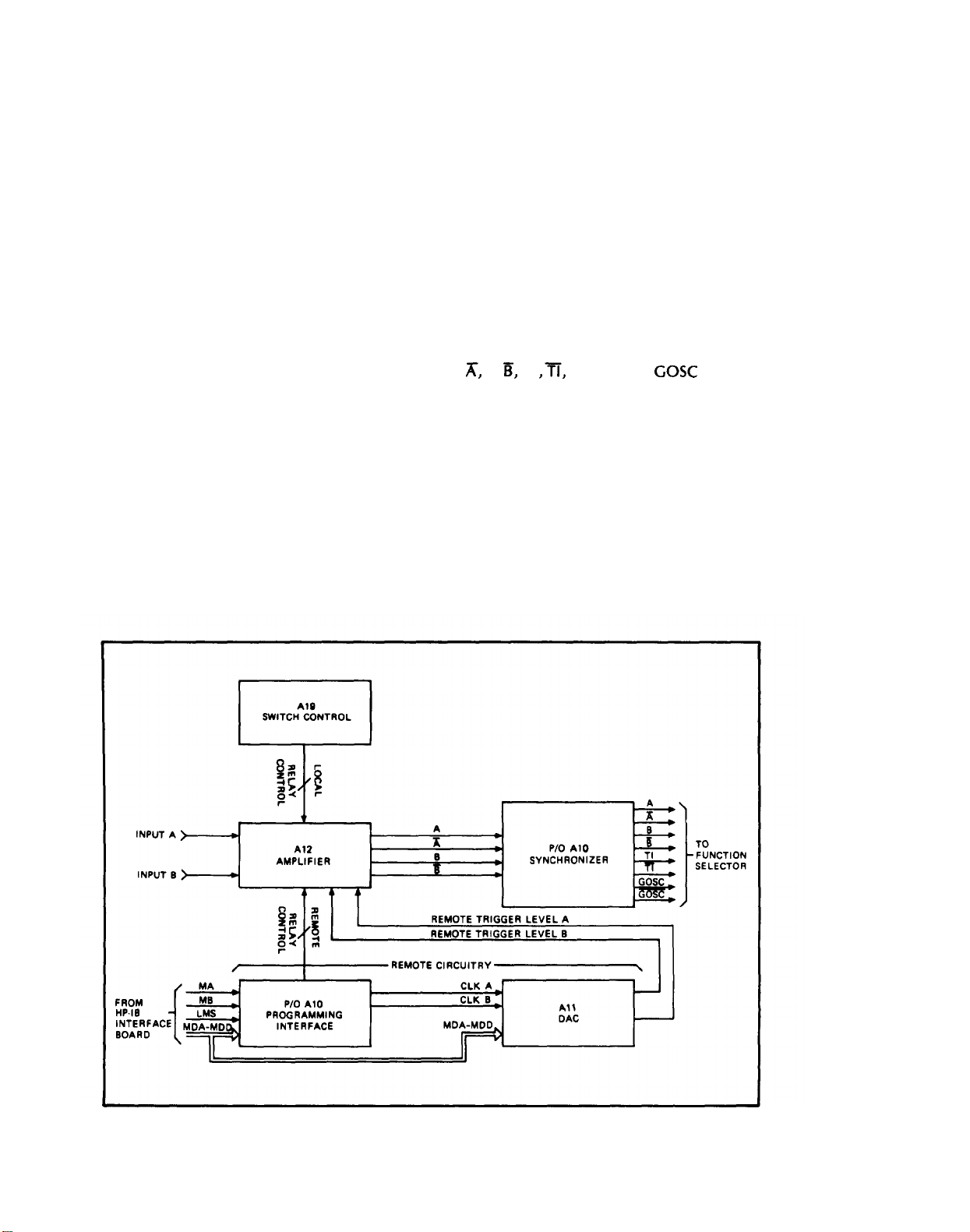

4-107. Remote Controllable (Programmable) Input Block

4-115. Remote Controllable (Programmable) Input

4-117.

4-122.

4-127.

4-147.

4-156.

4-162. HP interface Bus Theory

4-173. HP-lB A15 Interface Operation

4-178.

4-181.

4-183.

4-185.

4-187.

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Overall Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

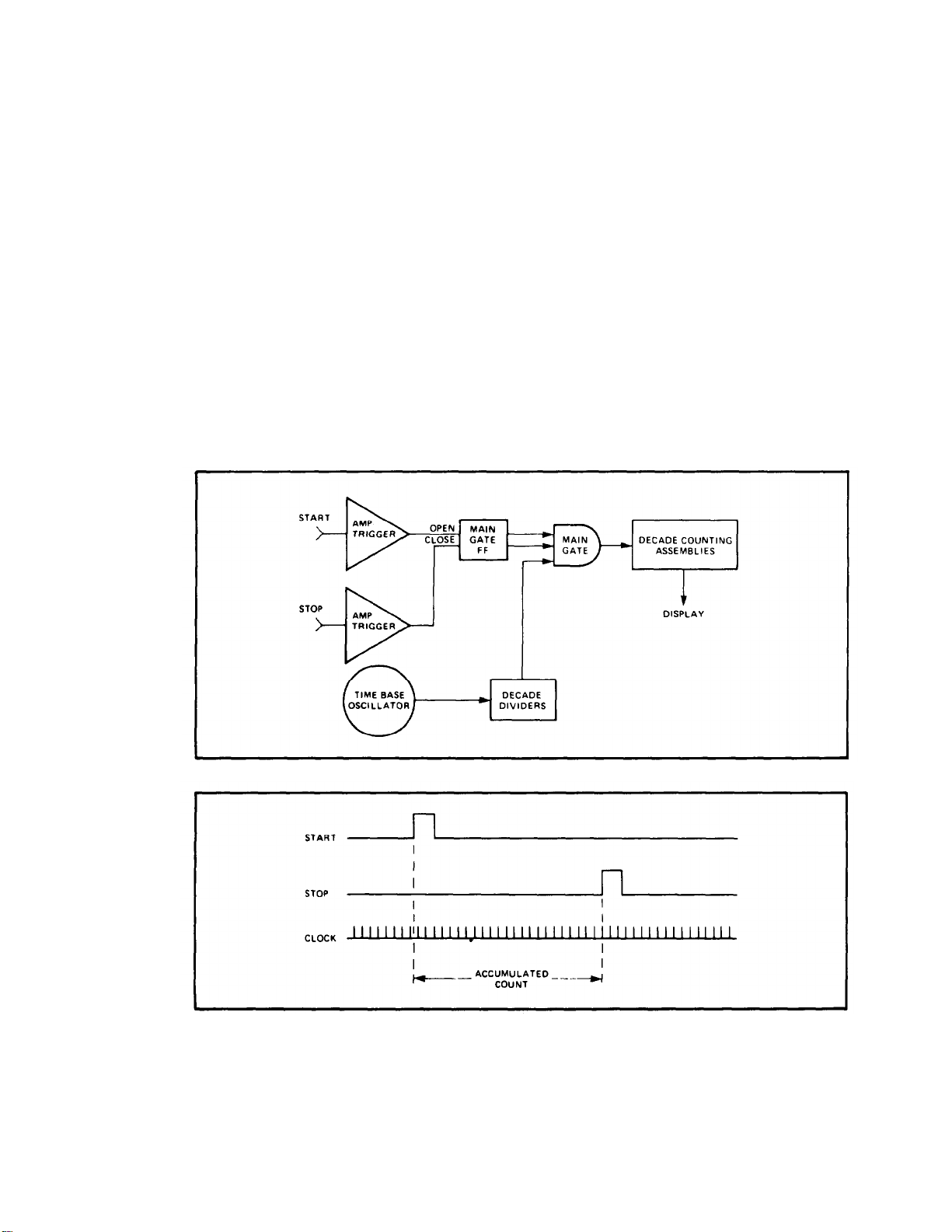

Basic Counter Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Period . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Time Interval . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Time interval, Resolution, and Averaging Techniques . . . . . . .

Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Time Interval Averaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Sources of Measurement Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

±1 Count Ambiguity . . . . . .

Time Base Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Trigger Error

5328A Principles of Operation

Main Counter Section

Input Section

Hewlett-Packard Interface Bus (HP-lB) Section . . . . . . . . . . . . 4-9

Al Motherboard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Display Control

State Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A3 Oscillator Support . . . .

A3 Oscillator Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A3A1 Oscillator (HP 10544A) . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Decade Counting Assembly (DCA) . . . . . . . . . . . . . . . . . . . . . . . . .

Time Base . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A2 Power Supply

+5V Supply

A4 Function Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

High Speed Multiplexer, Main Gate, and 1st Decade . . . . . .

Arming Multiplexer and Arming FF

Time Base Multiplexer and Main Gate FF . . . . . . . . . . . . . . . . .

An Example of Operation

Diagram Description . . . . . .

Schematic Theory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A19 Switch Control Board . . . .

A12 Amplifier Board

A10 Synchronizer Board . . . .

A11 DAC Board . . . . . . . . . . . . .

A8 Channel C lnput

Overall Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bus Command Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Listen Mode . . . . . . . . . . . . . . . .

Talk Mode . . . . . . . . . . . . . . . . .

A15 Circuit Operation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

4-1

4-2

4-3

4-5

4-6

4-7

4-7

4-9

4-10

4-10

4-10

4-10

4-10

4-10

4-11

4-11

4-11

4-12

4-12

4-12

4-13

4-13

4-13

4-14

4-16

4-16

4-16

4-17

4-20

4-20

4-21

4-22

4-22

Page 8

TABLE OF CONTENTS (Continued)

Model 5328A

Table of Contents

Section

V

MAINTENANCE

Introduction . . .

5-1.

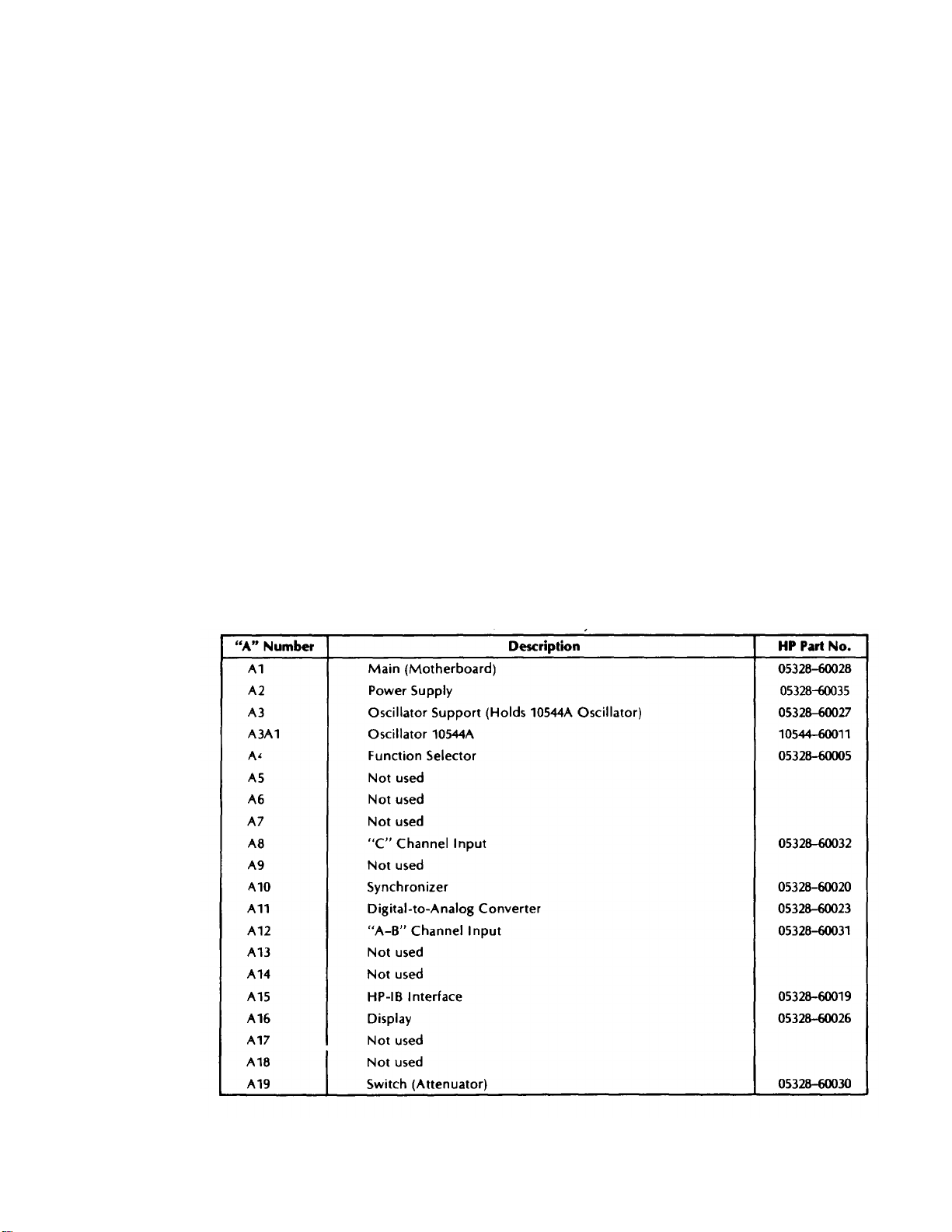

Assembly Designations . . . . . . . . . .

5-3.

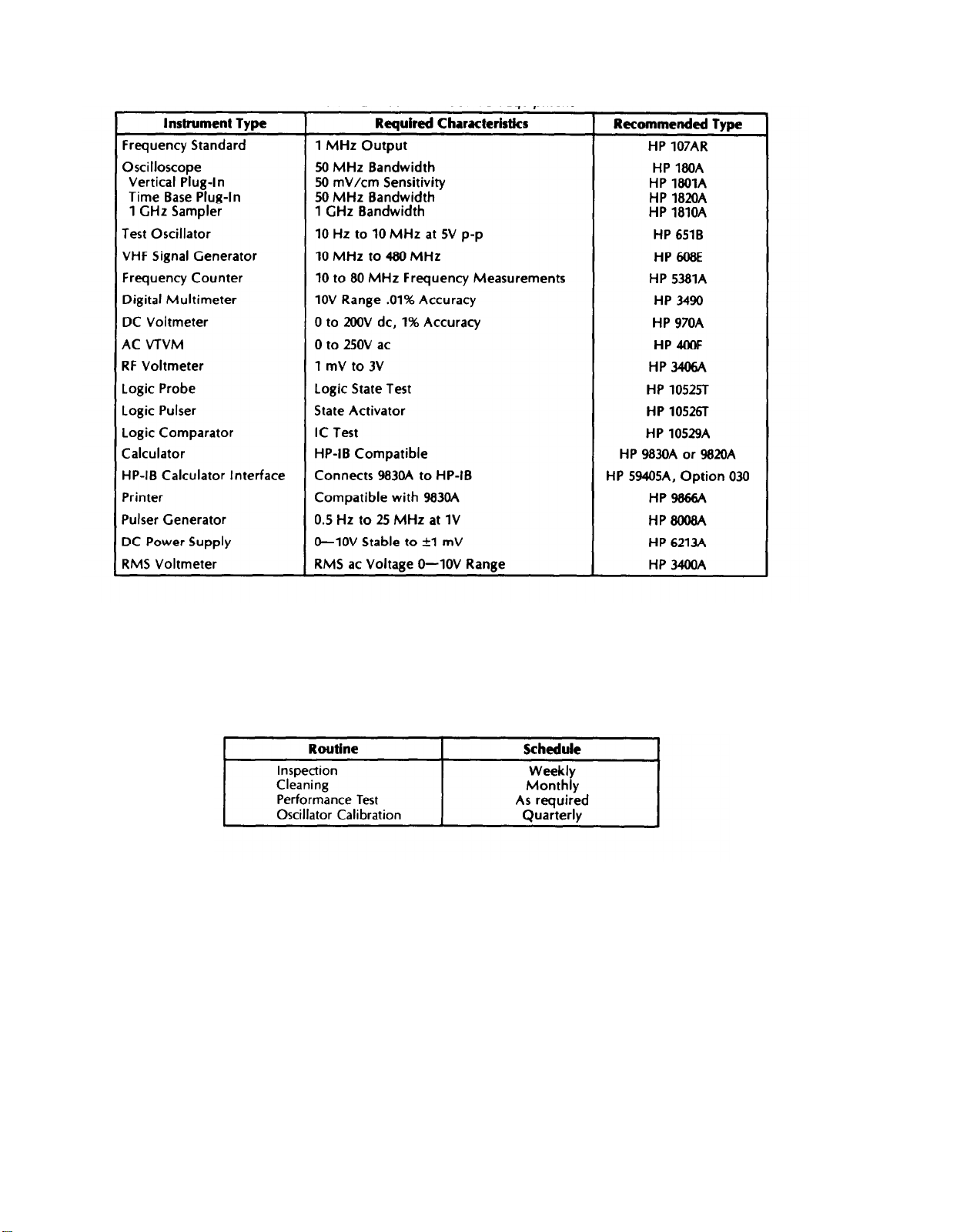

Test Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-5.

Assembly Connection Identification

5-7.

Preventive Maintenance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-9.

5-11.

5-13.

5-15.

5-17. Repair . . . . . . . .

5-18.

5-20.

5-22. Adjustments . . . . . . . . . . . . .

5-25.

5-26.

5-27. Troubleshooting . . . . . . . . . . .

5-29. Troubleshooting Aids . .

5-31.

5-33.

5-35.

5-43. Troubleshooting Input Channels

5-45.

5-54. Removal and Replacement Instructions

5-56.

5-58.

5-60.

Time Interval Module (Assemblies A10 and A19)

A16 Display Assembly Removal and Replacement . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

Inspection . . .

Cleaning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Performance Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Printed Circuit Component Replacement . . . . . . . . . . . . . . . . . .

Replacing Integrated Circuits

Sensitivity Adjustments

Adjustment of A3 Oscillator Support . . . . . . . . . . . . . . . . . . . . . .

Extender Board (05328-62016) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

lC Troubleshooting . . . .

Function Signals . . . . . . .

Local Mode Troubleshooting

Instrument Cover Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Removal Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

Page

5-1

5-1

5-1

5-1

5-1

5-2

5-3

5-3

5-3

5-3

5-3

5-3

5-19

5-19

5-24

5-24

5-24

5-24

5-26

5-26

5-41

5-41

5-45

5-45

5-45

5-45

VI

Vll

Vlll

APPENDIX A. REFERENCES

REPLACEABLE PARTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-1.

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-3.

HP Part Number Organization . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-5.

6-7.

6-10.

6-12.

6-14. Factory Selected Parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-16. Part Number to NSN Cross Reference Index . . . . . . . . . . . . . . . . .

MANUAL CHANGES

7-1.

7-3.

SCHEMATIC DIAGRAMS

8-1.

8-3.

8-5.

8-7.

8-9.

8-14. Assembly Locations and Component Locators

8-16. Factor Selected Components

B. COMPONENTS OF END ITEM LIST . . . . . . . . . . . . . . . . . . . .

C.

D.

E.

Component Parts and Materials . . . . . . . . . . . . . . . . . . . . . . . . . .

General Usage Parts

Specific Instrument Parts

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Manual Changes Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Schematic Diagrams SymboIs and Reference Designators . . . . .

Reference Designators

Signal Mnemonics

Identification Markings o Printed-Circuit Boards

ADDITIONAL AUTHORIZATION LIST (not applicable)

MAINTENANCE ALLOCATION

EXPENDABLE SUPPLIES AND MATERIALS LIST (not applicable)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..

. . . . . . . . . . . . . . . . . . . .

6-1

6-1

6-1

6-3

6-3

6-4

6-4

6-4

6-4

7-1

7-1

7-1

8-1

8-1

8-1

8-1

8-1

8-1

8-2

8-2

A-1

B-1

D-1

v

Page 9

Model 5328A

List of Tables

LIST OF TABLES

Table

1-1.

1-2.

1-3.

3-1.

3-2.

3-3.

3-4.

3-5.

3-6.

4-1.

5-1.

5-2.

5-3.

5-4.

5-5.

5-6.

5-7.

5-8.

5-9.

5-1o.

5-11.

5-12.

5-13.

5-14.

5-15.

5-16.

Page

Equipment Supplied . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Accessories Available . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5328A Counter Specifications

Arming Status . .

Frequency Resolution, N Switch Settings and Gate Times

Functions and Resolution Switch Settings

Addressing . .

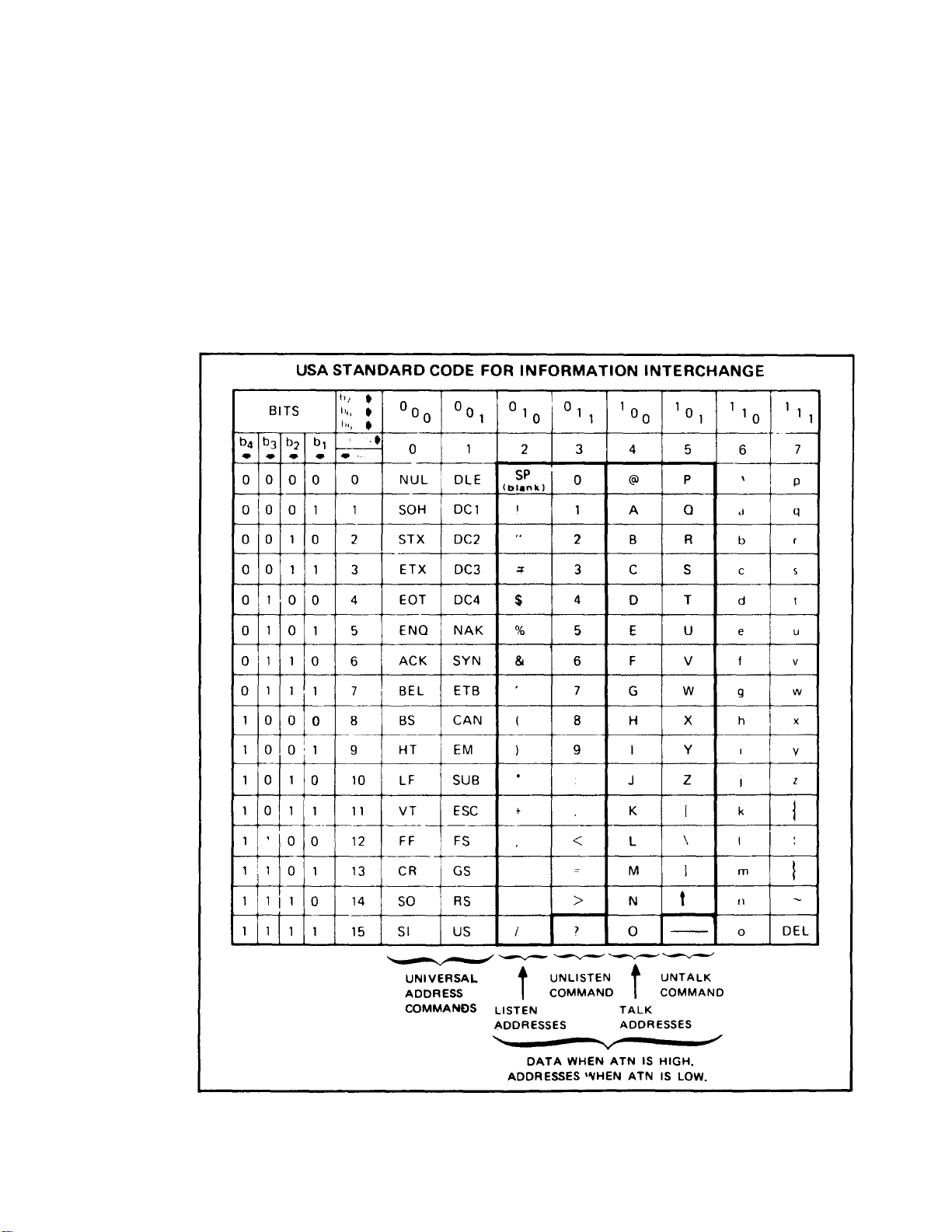

Program Code Set

American Standard Code for Information interchange (ASCII) . . . . . . .

5328A input Circuit Program Code Set . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5328A Assembly identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Recommended Test Equipment . .

Preventive Maintenance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Performance Test

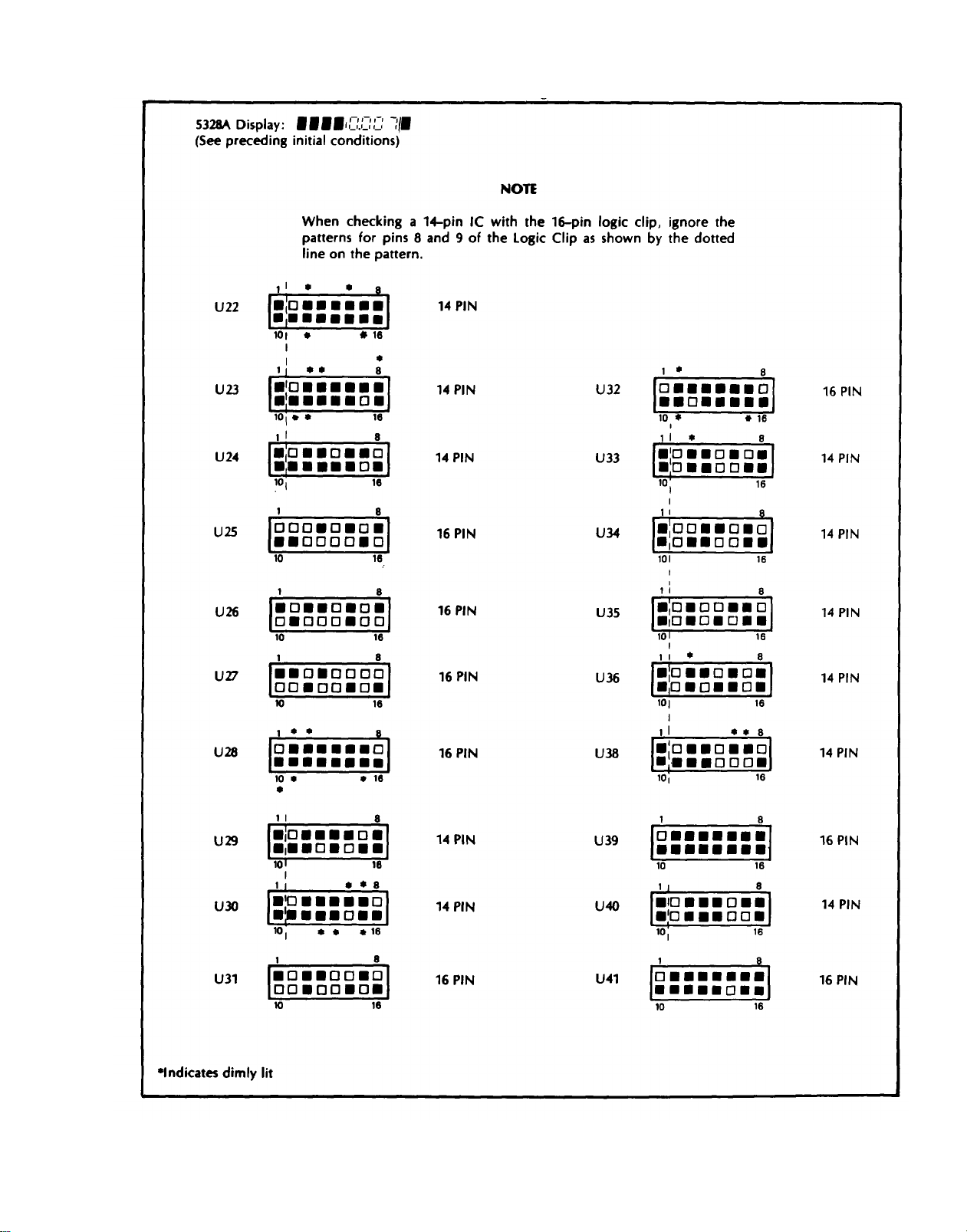

lC Troubleshooting, A1 Motherboard . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5328A Functional Signals

Program Listing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Program Description . . . . . .

5328A A15 Qualifiers and Signal Mnemonics

A12 Relay Operation . . . .

Relay Control Logic

Program interface Operation

ROM (A10U7) Input/Output Mode

A11 DAC Logic Levels

A11 DAC Signals

A11 DAC Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . 3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-2

1-3

3-9

3-9

3-14

3-15

3-17

4-15

5-1

5-2

5-4

5-27

5-30

5-33

5-36

5-39

5-41

5-41

5-43

5-43

5-44

5-44

6-1.

6-2.

6-3.

Figure

1-1.

3-1.

3-2.

3-3.

3-4.

3-5.

3-6.

3-7.

3-8.

3-9.

3-10.

3-11.

3-13.

Replaceable Parts

Manufacturers Code List . . . .

Part Number-NSN Cross Reference Index . . . . . . . . . . . . . .

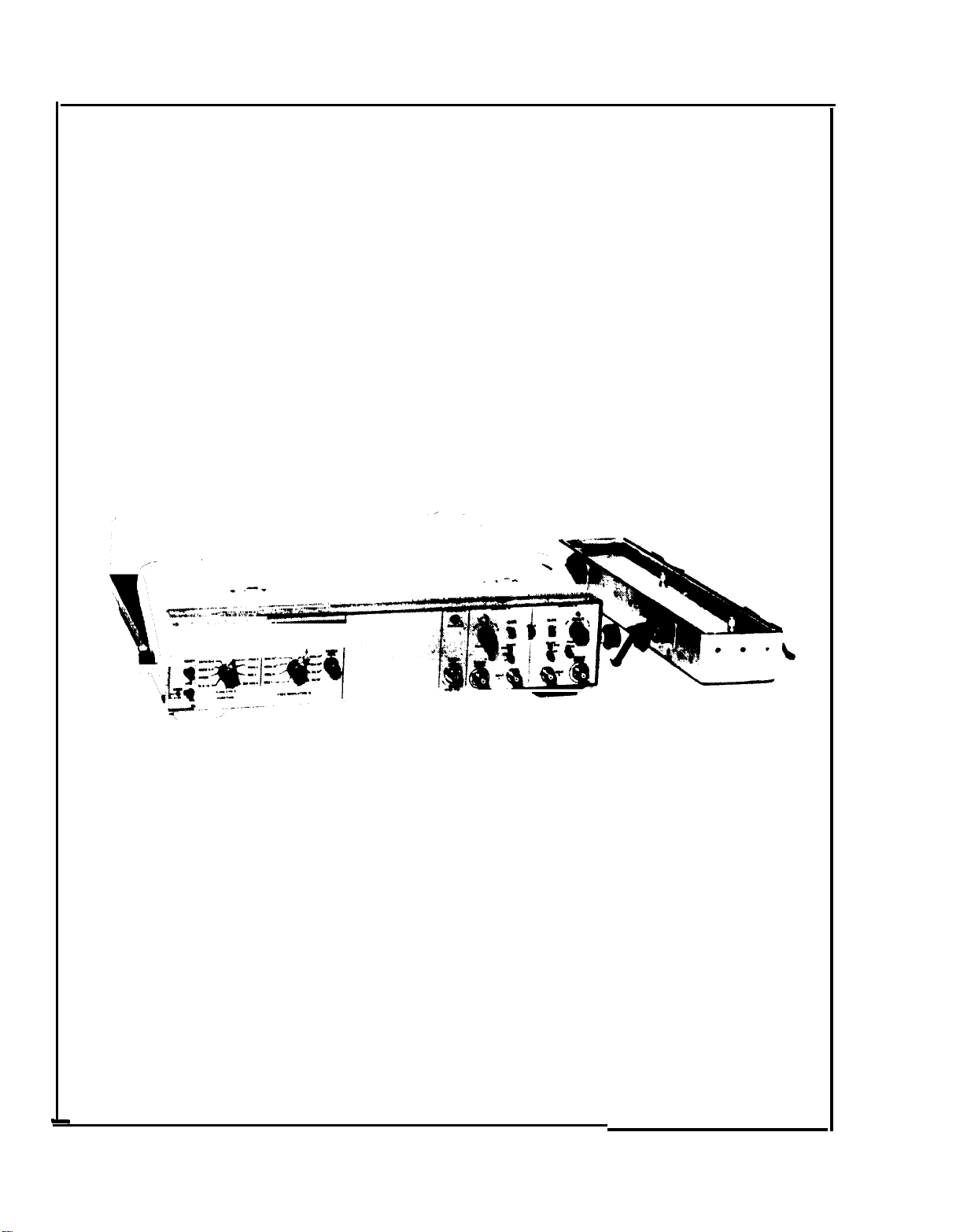

Model 5328A 500 MHz Universal Frequency Counter . . . . . . . . . . . . . . . 1-0

Measuring Linearity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Tone Burst Measurements . . . . .

Deadtime

Multiple STOP Pulses

Monitoring Marker Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

5328A Front Panel Operation Summary . . . . . . . . . . . .

5328A Rear Panel Controls and Connectors

Programmable Input Switch Configuration for COM A

Slope Switch Settings

Level Control Settings . . . . . . . . .

Hysteresis Band

5328A Measurement Cycle

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LIST OF FIGURES

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-5

6-24

6-25

Page

3-2

3-3

3-5

3-7

3-10

3-11

3-11

3-12

3-18

Page 10

LIST OF FIGURES

Model 5328A

List of Figures

4-1.

4-2.

4-3.

4-4.

4-5.

4-6.

4-7.

4-8.

4-9.

4-10.

5-1.

5-2.

5-3.

5-4.

5-5.

5-6.

5-7.

5-8.

5-8.

5-9.

5-10.

5-10.

5-10.

5-11.

5-11.

5-12.

Basic Elements of the Frequency Counter

Measuring Period . .

Basic Elements of a Time interval Counter . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock Pulses

Synchronizer Operation with Time Interval Averaging

±1 Count Ambiguity

Trigger Error

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Remote Controllable (Programmable) Input Block Diagram

ASM Oscillator Timing Diagram . .

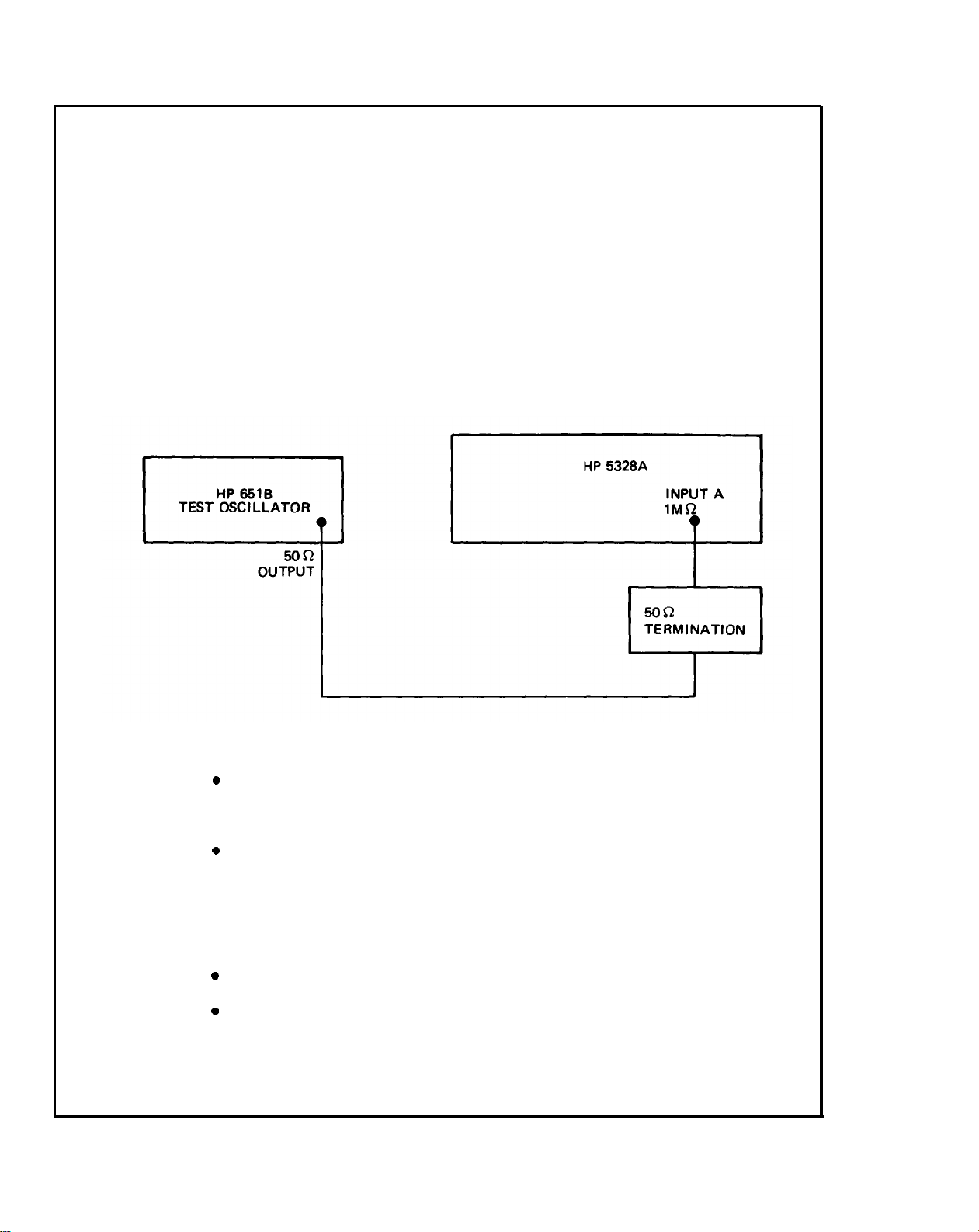

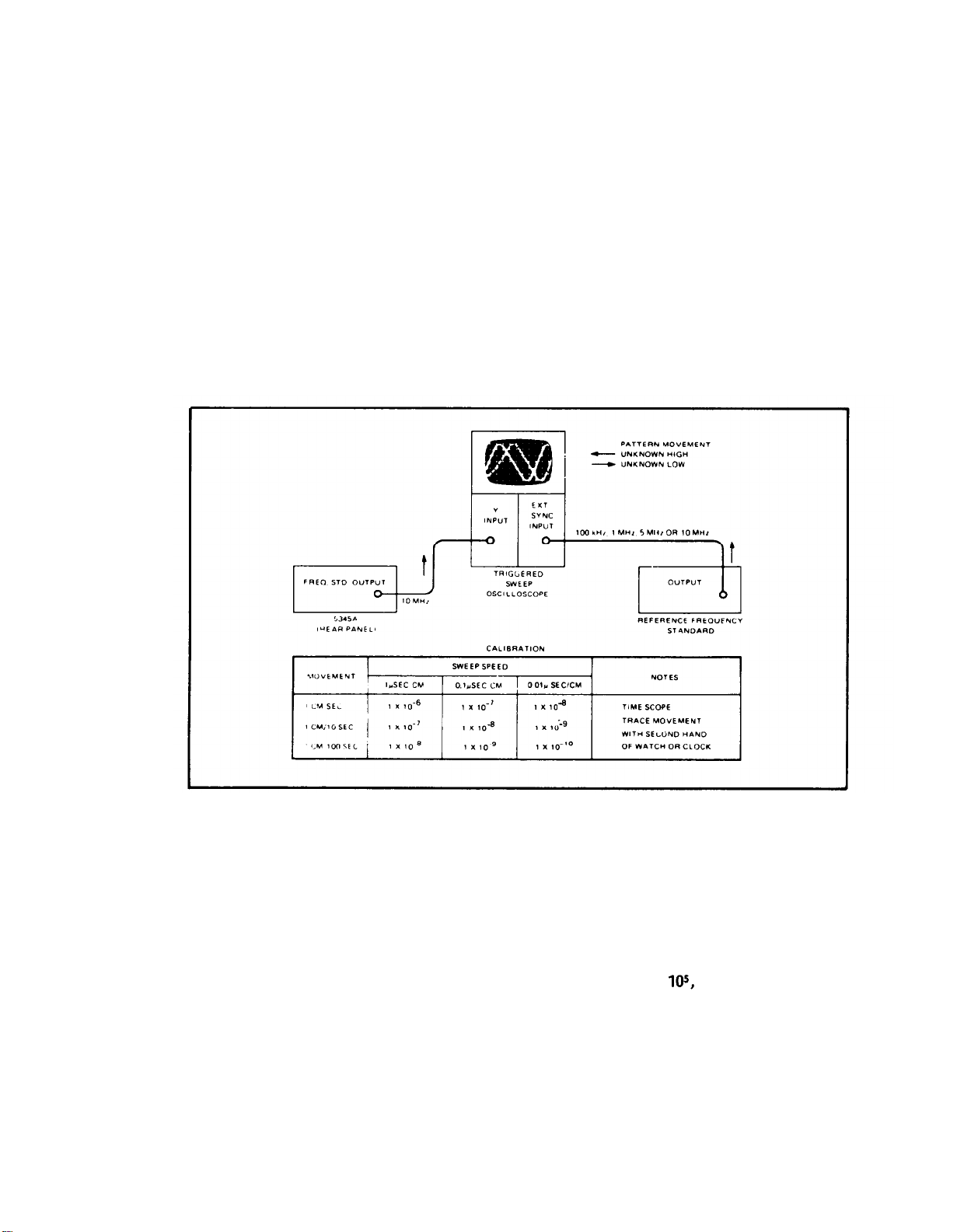

10 MHz Oscillator Frequency Check

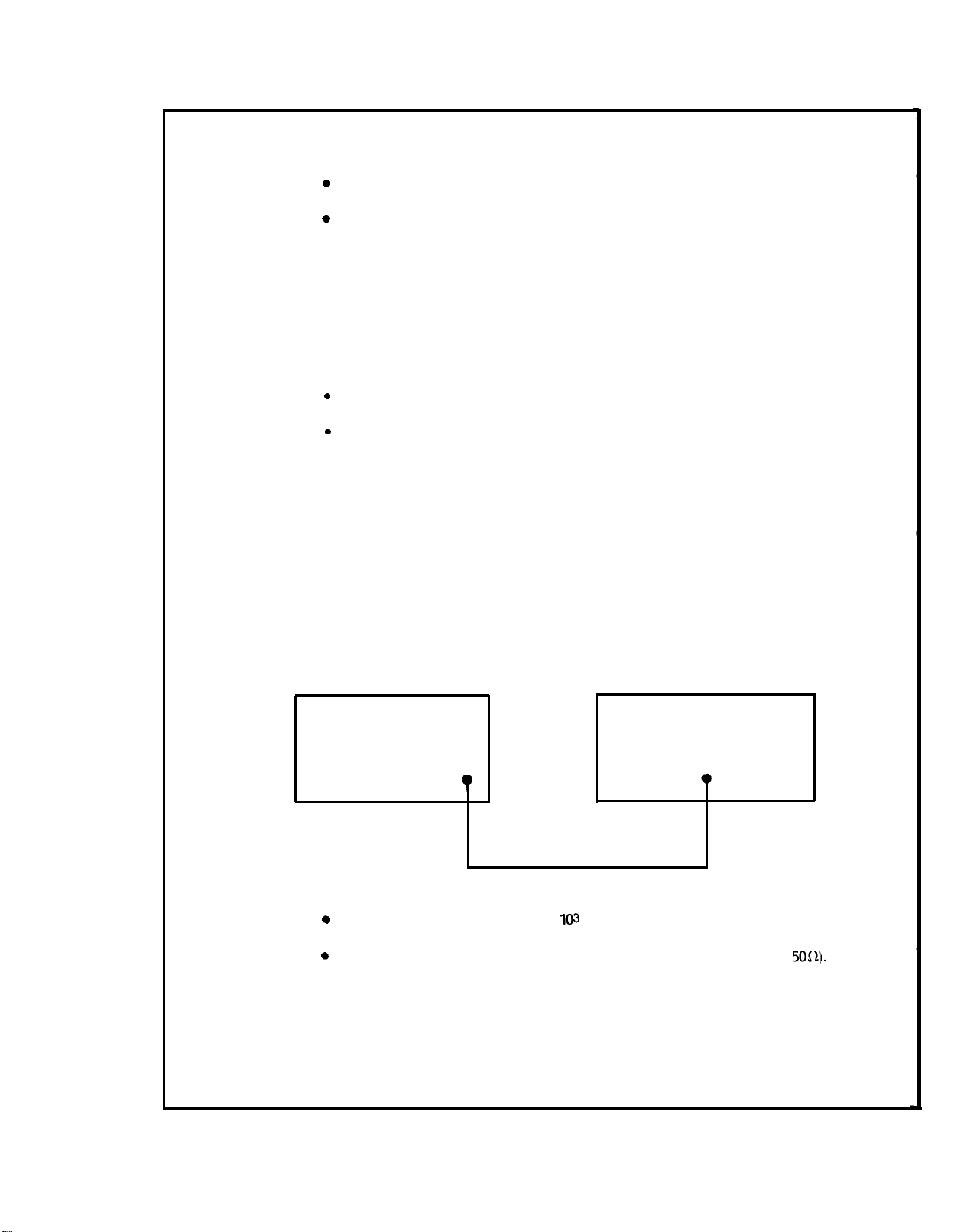

DAC Adjustment Equipment Connectors

DAC Adjustment Oscilloscope Readout and Adjustment Locations . .

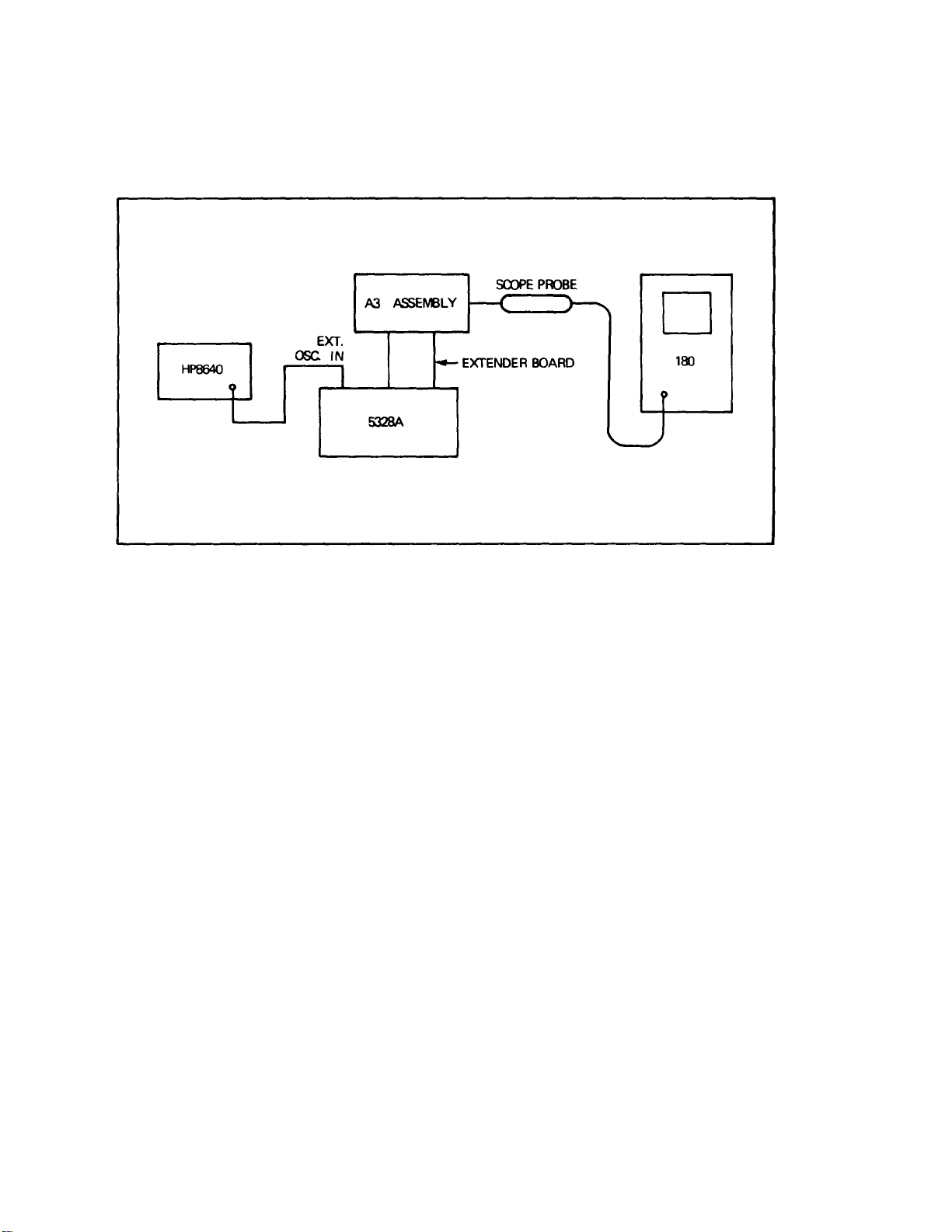

Hookup for A3 Oscillator Support Adjustment

A3 Jitter Adjustment . . . .

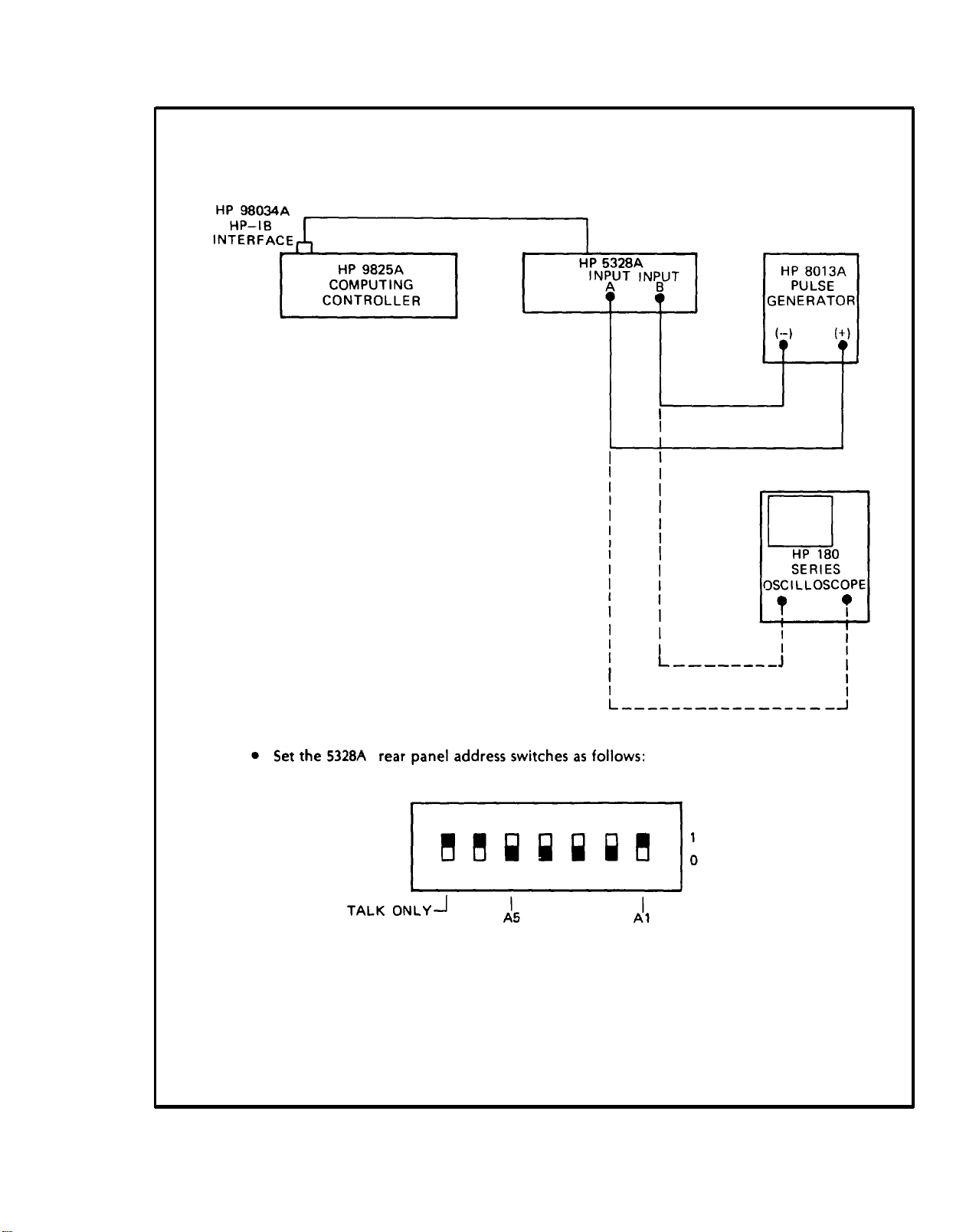

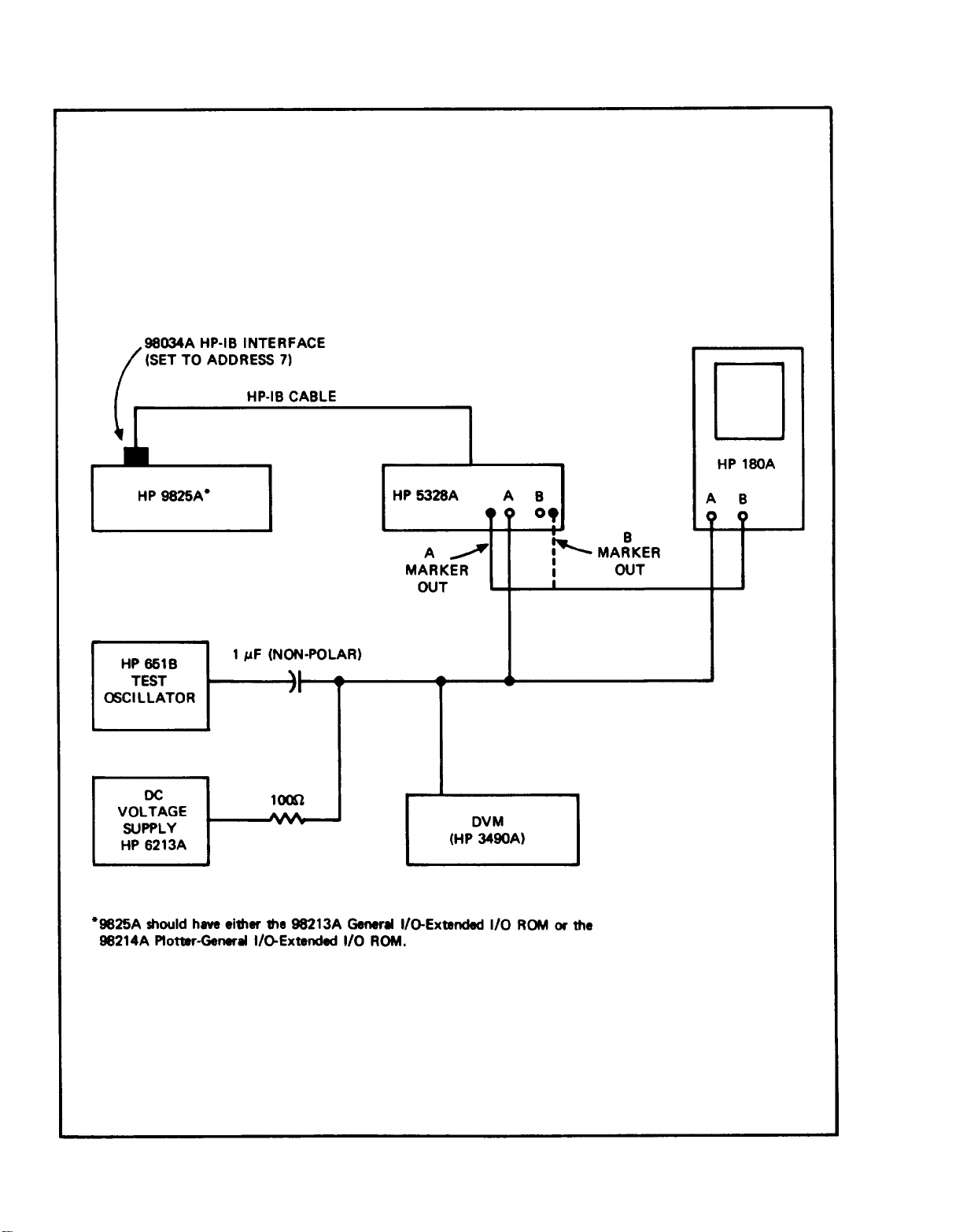

System Configuration

Sample Printout

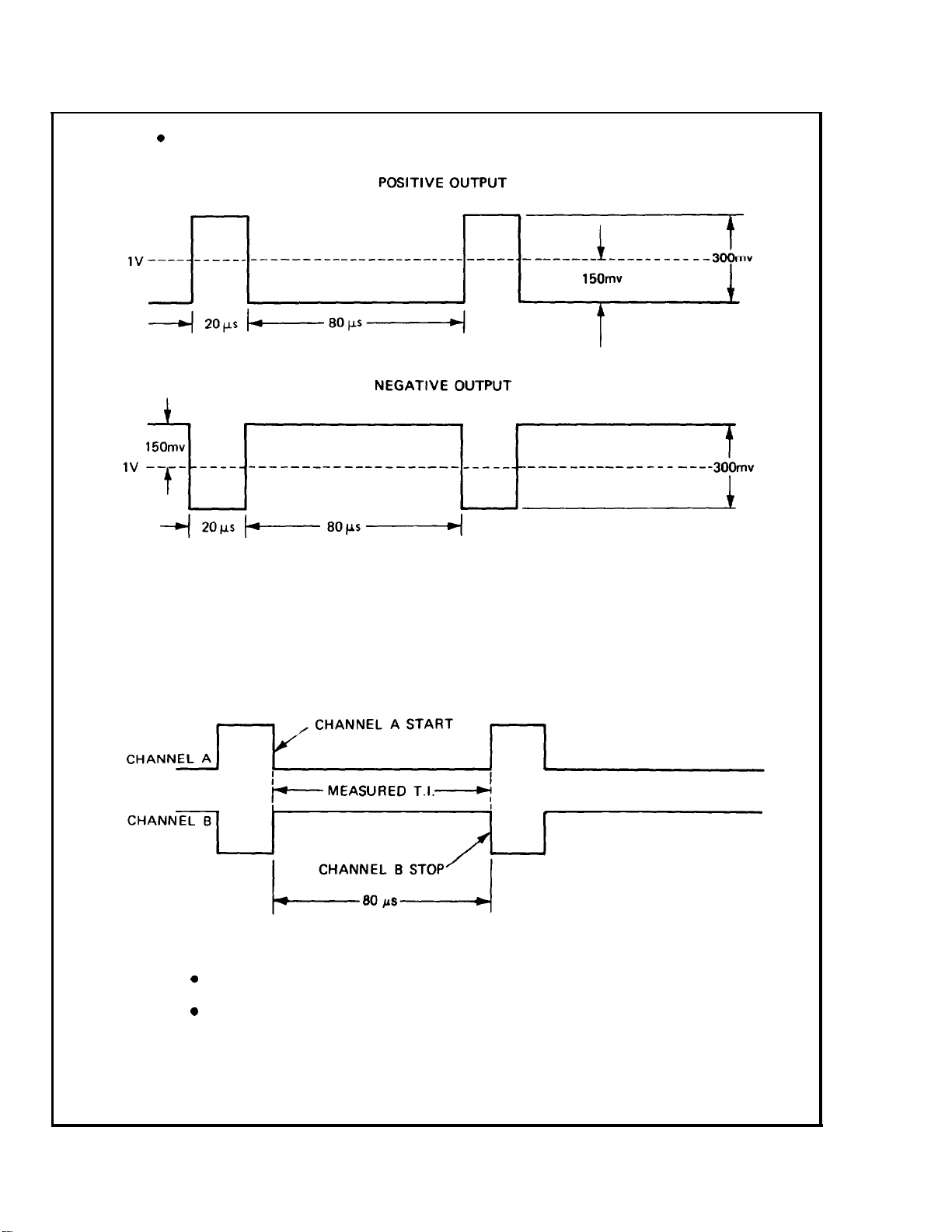

Hookup for

Hookup for Test Described in Table 5-8B and C . . . . . . . . . . . . . . . . . . . .

Triangular Pulse Observed in Steps 5 and 7, Table 5-8B

Assembly Flowchart (Sheet 1 of 3) . .

Assembly Flowchart (Sheet 2 of 3)

Assembly Flowchart (Sheet 3 of 3) . .

Local Troubleshooting Flowchart (Sheet 1 of 2) . . . . . . . . . . . . . . . . . . . . .

Local Troubleshooting Flowchart (Sheet 2 of 2) . . . . . . . . . . . . . . . . . . . . .

Address Switch Troubleshooting Flowchart

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . .

. . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

4-1

4-2

4-3

4-3

4-5

4-5

4-7

4-8

4-14

4-24

5-19

5-22

5-23

5-24

5-25

5-31

5-32

5-36

5-38

5-47

5-49

5-51

5-52

5-53

5-54

8-1.

8-2.

8-3.

8-4.

8-5.

8-6.

8-7.

8-7.

8-8.

8-9.

8-10.

8-11.

8-12.

8-13.

8-14.

8-15.

8-16.

8-17.

8-18.

8-19.

8-20.

8-21.

8-22.

8-23.

8-24.

8-25.

Schematic Diagram Notes . .

5328A Front View

5328A Rear View

5328A Top View

5328A Bottom View

A1 Motherboard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A1 Motherboard Schematic and Components (Sheet 1 of 2) . . . . . . . . .

A1 Motherboard Schematic and Components (Sheet 2 of 2)

A2 Power Supply Block Diagram . .

A2 Power Supply Schematic and Components . . . . . . . . . . . . . . . . . . . . . .

A3/A3A1 Oscillator Support Schematic and Components . . . . . . . . . . . . . 8-21

A4 Function Selector Block Diagram

A4 Function Selector Schematic and Components . . . . . . . . . . . . . . . . . .

A8 Channel “C” Block Diagram . . . . . . .

A8 Channel “C” Schematic and Components

A10 Synchronizer Block Diagram

A10 Synchronizer Schematic and Components

A11 Digital-to-Analog Converter Block Diagram . . . . . . . . . . . . . . . . . . . .

A11 Digital-to-Analog Converter Schematic and Components

A12 “A-B” Channel Block Diagram

A12 “A-B” Channel Schematic and Components . . . . . . . . . . . . . . . . . . .

A15 HP-IB Interface Block Diagram

A15 HP-IB Interface Schematic and Components

A16 Display Block Diagram . . . . . . . . . . .

A16 Display Schematic and Components

A19 Switch/Attenuator Schematic and Components

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

. . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

8-3

8-7

8-7

8-8

8-9

8-11

8-17

8-19

8-18

8-19

8-23

8-25

8-26

8-27

8-28

8-29

8-30

8-31

8-32

8-33

8-35

8-37

8-39

8-41

8-43

vii

Page 11

Model 5328A

Safety Considerations

GENERAL

This is a Safety Class I instrument. This instrument has been designed and tested according to

IEC Publication 348, “Safety Requirements for Electronic Measuring Apparatus.”

OPERATION

BEFORE APPLYING POWER verify that the power transformer primary is matched to the

available line voltage and the correct fuse is installed (see Section II). Make sure that only

fuses with the required rated current and of the specified type (normal blow, time delay, etc.) are

used for replacement. The use of repaired fuses and the short-circuiting of fuseholders must

be avoided.

SERVICE

Although this instrument has been designed in accordance with international safety standards,

this manual contains information, cautions, and warnings which must be followed to ensure

safe operation and to retain the instrument in safe condition. Service and adjustments should

be performed only by qualified service personnel.

SAFETY CONSIDERATIONS

Any adjustment, maintenance, and repair of the opened instrument under voltage should be

avoided as much as possible and, when inevitable, should be carried out only by a skilled person

who is aware of the hazard involved.

Capacitors inside the instrument may still be charged even if the instrument has been discon-

nected from its source of supply.

Whenever it is likely that the protection has been impaired, the instrument must be made in-

operative and be secured against any unintended operation.

viii

Page 12

Safety Considerations

WARNING

IF THIS INSTRUMENT IS TO BE ENERGIZED VIA AN AUTOTRANS-

FORMER (FOR VOLTAGE REDUCTION] MAKE SURE THE COMMON

TERMINAL IS CONNECTED TO THE EARTHED POLE OF THE POWER

SOURCE.

WARNING

BEFORE SWITCHING ON THE INSTRUMENT, THE PROTECTIVE EARTH

TERMINALS OF THE INSTRUMENT MUST BE CONNECTED TO THE

PROTECTIVE CONDUCTOR OF THE (MAINS) POWER CORD. THE

MAINS PLUG SHALL ONLY BE INSERTED IN A SOCKET OUTLET PROVIDED WITH A PROTECTIVE EARTH CONTACT. THE PROTECTIVE

ACTION MUST NOT BE NEGATED BY THE USE OF AN EXTENSION

CORD (POWER CABLE) WITHOUT A PROTECTIVE CONDUCTOR

(GROUNDING).

WARNING

Model 5328A

THE SERVICE INFORMATION FOUND IN THIS MANUAL IS OFTEN

USED WITH POWER SUPPLIED AND PROTECTIVE COVERS REMOVED

FROM THE INSTRUMENT. ENERGY AVAILABLE AT MANY POINTS

MAY, IF CONTACTED, RESULT IN PERSONAL INJURY.

CAUTION

BEFORE SWITCHING ON THIS INSTRUMENT:

1.

MAKE SURE THE INSTRUMENT IS SET

THE POWER SOURCE.

2.

ENSURE THAT ALL DEVICES CONNECTED TO THIS INSTRUMENT ARE CONNECTED TO THE PROTECTIVE (EARTH) GROUND.

ENSURE THAT THE LINE POWER (MAINS) PLUG IS CONNEC-

3.

TED TO A THREE-CONDUCTOR LINE POWER OUTLET THAT HAS

A PROTECTIVE (EARTH) GROUND. (GROUNDING ONE CONDUCTOR OF A TWO-CONDUCTOR OUTLET IS NOT SUFFICIENT.)

4.

MAKE SURE THAT ONLY FUSES WITH THE REQUIRED RATED

CURRENT AND OF THE SPECIFIED TYPE (NORMAL BLOW,

TIME DELAY, ETC.) ARE USED FOR REPLACEMENT. THE USE

OF REPAIRED FUSES AND THE SHORT-CIRCUITING OF FUSE

HOLDERS MUST BE AVOIDED.

TO THE VOLTAGE OF

ix

Page 13

Model 5328A

General Information

Figure 1-1. Model 5328A 500 MHz Universal Frequency Counter

0

Page 14

TM 11-6625-2941-14&P

SECTION O

INTRODUCTION

0-1. SCOPE

This manual describes Counter, Electronic, Digital Readout AN/USM-459 and

provides instructions for operation and maintenance. Throughout this manual,

the AN/USM-459 is referred to as Hewlett-Packard Model 5328A Counter.

0-2.

whether there are new editions,

ing to the equipment.

modification work orders (MWO's) pertaining to the equipment.

0-3.

forms, records,

all maintenance levels are listed in and prescribed by TM 38-750.

DD Form 6 (Packaging Improvement Report) as prescribed in AR 700-58/NAVSUPINST

4030.29/AFR 71-13/MCO P4030.29A and DLAR 4145.8.

ward Discrepancy in Shipment Report (DISREP) (SF 361) as prescribed in AR

55-38/NAVSUPINST 4610.33B/AFR 75-18/MCO P4610.19C and DLAR 4500.15.

0-4.

INDEXES OF PUBLICATIONS

DA Pam 310-4. Refer to the latest issue of DA Pam 310-4 to determine

a.

changes, or additional publications pertain-

DA Pam 310-7.

b.

FORMS AND RECORDS

a. Reports of Maintenance and Unsatisfactory Equipment. Maintenance

and reports which are to be used by maintenance personnel at

Report of Packaging and Handling Deficiencies. Fill out and forward

b.

Discrepancy in Shipment Report (DISREP) (SF 361). Fill out and for-

c.

REPORTING EQUIPMENT IMPROVEMENT RECOMMENDATIONS (EIR)

Refer to DA Pam 310-7 to determine whether there are

EIR’s will be prepared using Standard Form 368 (Quality Deficiency Report).

Instructions for preparing EIR’s are provided in TM 38-750, The Army Maintenance Management System. EIR’s should be mailed direct to Commander, US Army

Communications and Electronics Materiel Readiness Command, ATTN: DRSEL-ME-MQ,

Fort Monmouth, NJ 07703.

0-5.

shall be in accordance with paragraph 2-26.

0-6.

accordance with TM 750-244-2

ADMINISTRATIVE STORAGE

Administrative storage of equipment issued to and used by Army activities

DESTRUCTION OF ARMY ELECTRONICS MATERIEL

Destruction of Army electronics materiel to prevent enemy use shall be in

A reply will be furnished direct to you.

0-1

Page 15

Page 16

Model 5320A

General Information

SECTION I

GENERAL INFORMATION

1-1. SCOPE OF MANUAL

1-2. This manual provides operating and service information for the Hewlett-Packard Model

5328A/H42 500 MHz Universal Frequency Counter. (In this manual its name will be abbreviated

to “5328A” or “counter”.) A separate operators booklet contains condensed operator instructions.

1-3. This manual is divided into eight sections as listed and described below:

Section I

GENERAL INFORMATION —

items supplied, lists items required, but not supplied, describes applications,

and lists recommended maintenance and test equipment.

Describes the counter, lists specifications, lists

Section II

Section Ill

Section IV

Section V

Section VI

Section VII

Section Vlll

1-4. DESCRIPTION

1-5. The 5328A counter can be used to measure frequency, period, period average, time

interval, time interval average, and ratio. The 5328A provides a 9-digit LED display, display

storage, and leading zero blanking. Decimal point and unit readouts are displayed automatically.

Two independent selectable input channels are provided for time interval measurements. Each

input channel has an attenuator, trigger slope selector, level control, ac or dc coupling, and an

oscilloscope marker output. Rear panel connectors provide a gate output, one- and 10-megahertz output, and an input for an external frequency standard. An ARM switch on the rear panel

allows arming by the signal being measured (switch OFF) or by another input signal (switch ON).

INSTALLATION —

ation for use, preparation for reshipment, and preparation for storage.

OPERATION —

ment of input signal: time period, time period average, time interval, time

interval average, and ratio between frequencies of two input signals.

THEORY OF OPERATION —

principles of the counter with reference to block and schematic diagrams

of each assembly.

MAINTENANCE — Contains maintenance and service information, including

a list of assemblies, recommended test equipment, performance checks, and

adjustment. Troubleshooting procedures and flowcharts are included in this

section.

REPLACEABLE PARTS —

parts ordering information.

MANUAL CHANGES —

CIRCUIT DIAGRAMS —

cating illustrations.

Provides instructions for unpacking, inspection, prepar-

Provides operator instructions including frequency, measure-

Covers a. description of the general operating

Provides a complete list of replaceable parts and

Contains information on manual changes.

Contains schematic diagrams and component lo-

1-6. INSTRUMENT IDENTIFICATION

1-7. Hewlett-Packard instruments have a 2-section, 10-character serial number (0000A00000),

which is located on the rear panel. The 4-digit serial prefix identifies instrument changes. If

the serial prefix of your instrument differs from that listed on the title page of this manual, there

are differences between this manual and your instrument. Instruments having higher serial

prefixes are covered with a “Manual Changes” sheet included with this manual.

1-1

Page 17

Model 5328A

General Information

1-8. APPLICATIONS

1-9. Specific applications information is provided in Section III of this manual. The general

application features of the 5328A are described in the following paragraphs.

1-10. The high sensitivity, frequency range, and signal conditioning controls (see Table 7-3)

make the 5328A suited for a wide range of applications.

1-11. The rear panel controlled “ARM” feature of the 5328A is useful in applications such as

burst frequency measurements, and pulse ampltiude measurements.

1-12. The 5328A single-shot resolution of 100 ns meets the requirements for applications

such as mechanical and electromechanical device (relays) timing, time of flight measurements

(ballistics), sonar ranging, radio ranging, and navigation.

1-13. Using time interval averaging, time intervals as short as 100 picosecond, with resolution

to 10 picosecond may be measured. Applications include coaxial cable length measurements,

phase measurements, logic timing measurements, and integrated circuit propagation delay

measurement.

1-14. Full bandwidth, sensitivity, and signal conditioning of the Channel A, B, and C input

amplifiers is provided for ratio and totalizing measurements.

1-15. The 5328A HP-IB Interface is able to output measurement data and be controlled (fully

programmed) via the Hewlett-Packard Interface Bus (HP-16). The 5328A may be interfaced

to HP-IB compatible instruments, calculators, or computers by interconnecting with an HP-IB

cable.

1-16. EQUIPMENT SUPPLIED AND ACCESSORIES AVAILABLE

1-17. Table 7-7 lists equipment supplied with the 5328A and Table 7-2 lists accessories available, The Service Kits listed in Table 1-2 are described in Section III.

Table 1-1. Equipment Supplied

DESCRIPTION

Detachable Power Cord 231 cm (71/2 ft.) long

Extender Board, 18 pin

Table 1-2. Accessories Available

DESCRIPTION HP PART NUMBER

HP Interface Bus Interconnect Cable 10631A, 914 mm (3 ft. long)

Front Handle Kit

Rack Flange Kit (for instruments without handles)

Rack and Handle Kit (installation instructions included

with above kits)

Service Kit:

Function Selector and ROM Kit

HP PART NUMBER

8120-1348

05328-62016

10631B, 1828 mm (6 ft. long)

10631C, 3656 mm (12 ft. long)

10631D, 0.5 m (11/2 ft. long)

5061-0088

5061-0076

5061-0082

05328-82004

1-2

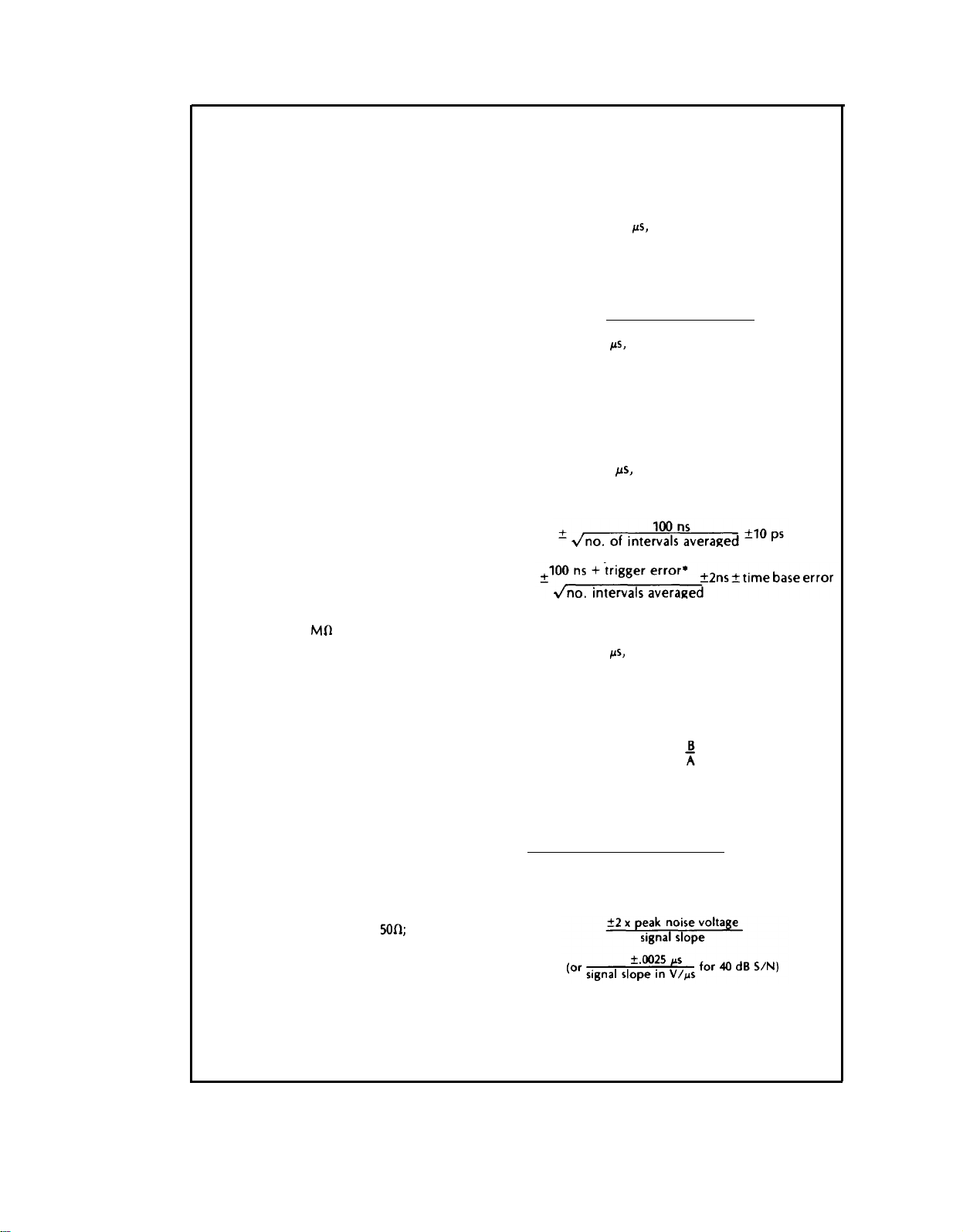

1-18. SPECIFICATIONS

1-19. Table 1-3 lists detailed specifications for the 5328AF/096.

Page 18

Table 1-3. 5328A Counter Specifications

Model 5328A

General Information

Power Requirements:

400 Hz ac.

Display:

Sample Rate:

seconds to HOLD.

Arming:

Refer to operation for details.

Blanking:

significant-digit are suppressed.

Hold:

HOLDS count between samples.

Trigger Light:

level.

PROGRAMMABLE OPERATION

Includes independent selection of coupling,

trigger slope, trigger level, and attenuator for

each channel. Separate/Common A switch is

programmable. Also, an invert feature switches

Channels A and B; useful in all functions except

Ratio B/A.

Trigger level is programmable in 10 mV steps

in X1; 100 mV in X10; IV in X100.

Trigger level accuracy under remote control:

X1:

±35 mV

X10:

±350 mV +2% of trigger level

X100:

±3.5V +2% of trigger level

Input Characteristics

Sensitivity:

20 Hz—35 MHz (ac coupled)

50 mV rms, 35 MHz—100 MHz

Minimum pulse width 5 ns, 140 mV p-p.

Coupling:

Impedance: 1 MO

Trigger Level:

attenuator setting with 0 volt preset position.

Trigger Slope:

- slope.

Attenuators:

Dynamic Range:

attenuator setting, 0—35 MHz; 50 mV rms

times attenuator setting, 35 MHz to 100 MHz

Maximum Input:

dc coupled, X1:

1.25 x 107V rms/freq., 50 kHz—2.5 MHz

5V rms, 2.5 MHz—100 MHz.

dc coupled, X10 and X100:

MHz 1.25 x 109V rms/freq., 5—100 MHz

ac coupled:

0-20 Hz; same as dc coupled above 20 Hz.

Channel Input:

Marker Outputs:

trigger outputs available on front panel;

0 to 300 mV levels into

Frequency Measurements

Frequency A

Range:

Resolution:

Accuracy:

Display: Hz, kHz, MHz.

GENERAL

Nine-digit LED.

Variable from less than 2 milli-

Rear panel ARM (ON-OFF) switch.

Unwanted zeros to left of most-

Indicates input is above trigger

(CHANNELS A AND B)

15 mV rms, 0—35 MHz (decoupled

ac or dc switch selectable.

X1, X10, X100.

0—100 MHz direct count.

1 MHz to 0.1 Hz in decade steps.

±1 count ± time base error.

115 or 230 volts 60 or

II <70 pF.

Variable over ±2.5 volts times

Independent selection of + or

25 mV to 1V rms times

250V rms, dc — SO kHz

250V rms, dc 5

200V (peak ac + dc),

Separate or Common A.

A and B channel Schmidt

50Q;

<20 ns delay.

Period Measurements

Time Interval Measurements

Ratio Measurement

Period A

Range:

Resolution:

Accuracy:

Display:

Period Average A

Range:

Resolution:

Accuracy:

error

Display:

Time Interval A to B

Range:

Resolution:

Accuracy:

Display:

Time Interval Average A to B

Range:

Resolution:

Accuracy:

Minimum Dead Time:

Maximum Repetition Rate:

Display:

Ratio B/A, or C/A

Range:

Range:

Range:

Resolution:

Accuracy: ±1 count of B or C ± trigger

* Trigger error is <0.3% of one period for sine waves

of 40 dB S/N or better and amplitude equal to

sensitivity of counter. For any wave shape, trigger

error is than then:

0—10 MHz

10 ns to 0.1s in decade steps.

±trigger error*

steps.

± trigger error*

STOP to next START

error* of A times frequency of B or C (N>1)

For N=1, add 12 ns times frequency of

B or C.

±1 count ± time base error

ns,

ps,

ms.

0—10 MHz

100 ns—.01 ps in decade steps.

±1 count displayed ± time base

trigger error*

±

no. of periods averaged

Ps,

ns

100 ns to 108 seconds

100 ns to 1-second in decade

±1 count ± time base error

ps,

ms, s.

0.1 ns to 10 seconds

150 ns from one

Ps,

ns.

A: 0—10 MHz

B: 0—100 MHz

C: 30—500 MHz

1 part in ~ x N

10 MHz.

1-3

Page 19

Model 5328A

General Information

Table 7-3. 5328A Counter Specifications (Continued)

CHANNEL C

Input Characteristics

Range:

Sensitivity:

Trigger level:

Impedance:

Maximum Input:

Input protection:

overload Indicator:

Resolution:

Accuracy:

Display: Hz, kHz, MHz

30 MHz to 500 MHz direct count

15 mV rms, 30 MHz—500 MHz

0 volts

50fl

nominal

5 volts rms

from front panel. protected to 200 volts peak.

of potential overload conditions.

Input BNC fused; accessible

flashing indicator warns

1 MHz to 0.1 Hz in decade steps

±1 count ± time base error

TIME BASE

Outputs:

Output level:

External Input:

Oscillator Aging Rate:

1 MHz and 10 MHz available at rear

panel BNC in standby and operate modes

1 volts rms into

Operates from 1, 2.5, 5, and 10

MHz inputs at 1V rms.

Input impedance 1

Counter automatically switches to

external mode when external input is

present.

24-hour warmup. Oscillator oven is

energized when power cable is connected

to line voltage.

50f)

K~l<30

pF

<5x1010/day after

1-4

Page 20

Model 5328A

Installation

SECTION II

INSTALLATION

2-1. INTRODUCTION

2-2. This section provides instructions for unpacking, inspection, preparation for use, shipment, and storage.

2-3. UNPACKING AND INSPECTION

2-4. If the shipping carton is damaged, inspect the counter for visible damage (scratches,

dents, etc.). If the counter is damaged, notify the carrier and the nearest Hewlett-Packard

Sales and Service Office immediately (offices are listed at the back of this manual). Keep the ship-

ping carton and packing material for the carrier’s inspection.

2-5. PREPARATION FOR USE

CAUTION

Before connecting this instrument to an ac power line, be sure that

the 115—230-volt line selector switch on the rear panel is set to the

proper position and proper line fuse is installed (see below).

2-6. Power Requirements

2-7. This instrument can be operated on single phase 115 or 230 (-10%. +5%) volts ac. Power

required is approximately 100 VA maximum. To avoid instrument damage, the rear panel line

selector switch must be set to the correct position and the correct fuse (as labeled on the rear

panel) must be installed. See Section

III for rear panel features photograph. When shipped, the

switch is set to 115-volt ac operation.

2-8. Fuse Replacement and Installation

2-9. Two fuses are supplied with the instrument. The instrument is shipped with a 2.0 ampere

fuse installed for 115- volt operation. To change the instrument for 230-volt operation disconnect the ac power cable, set the line selector switch and install the 1.0 ampere fuse.

2-10. Power Cables

WARNING

TO PROTECT OPERATING AND SERVICING PERSONNEL, THIS

INSTRUMENT IS EQUIPPED WITH A THREE-PIN POWER RECEP-

TACLE. THE CENTER PIN OF THE RECEPTACLE CONNECTS THE

INSTRUMENT CHASSIS AND PANELS TO EARTH GROUND WHEN

USED WITH A PROPERLY WIRED THREE CONDUCTOR OUTLET

AND POWER CABLE. IMPROPERLY GROUNDED EQUIPMENT CAN

RESULT IN HAZARDOUS POTENTIALS BETWEEN EQUIPMENTS.

2-1

Page 21

Model 5328A

Installation

2-11. To accommodate the different power receptacles used throughout the world, this instrument is supplied with one of the power cables shown in Figure 2-7. The cable supplied for use

in the United States meets the specifications established by the International Electrotechnical

Commission (lEC). The male connector of this cable is a NEMA type and the female connector

is a C.E.E. type.

2-12. Connect the power cable to a power source receptacle that has a grounded third con-

ductor. If the line power receptacle is a two-pin type instead of a three-pin receptacle, use a

two- to three-pin adapter (HP Part No. 1251-0048 for USA applications) and connect the green

lead on the adapter to earth ground. See warning above. If counter is to be operated with 230V ac

line power, an Underwriters Laboratories listed connector should be used to connect power.

2-13. Operating Environment

2-14. Maximum and minimum allowable operating temperatures are listed in Table 1-3. If

these limits are exceeded at the installation site, auxiliary cooling or heating should be used to

keep the environment within limits. A l-inch space above the counter should be clear to allow

cooling air circulation. The cooling fan exhaust port at rear is to be kept clear.

2-15. Bench Operation

2-16. The instrument cabinet has plastic feet and the large tilt carrying handle will fold under

for convenient bench operation. The tilt handle permits inclining the instrument for ease in

using front-panel controls and indicators.

NOTE

The tilt carrying handle may be secured in any position by tightening

the knurled side screws.

2-17. Rack Mounting

2-18. The counter is ready for bench operation as shipped from the factory. To mount the

counter in a rack, it is necessary to order and install the rack flange kit listed in Table 7-2.

CAUTION

Ambient temperature in rack during operation should not exceed 112°F

(50°C). Be sure instrument position in rack permits adequate air circulation and that nearby equipment does not discharge hot air directly on

the instrument.

2-19. PACKAGING FOR RESHIPMENT

2-20. Original Packaging

2-21. The same containers and materials used in factory packaging can be obtained through

the Hewlett-Packard Sales and Service Offices listed at the rear of this manual.

2-22. If the counter is being returned to Hewlett-Packard for service, attach a tag indicating

the type of service required, return address, model number, and full serial number. Mark the

container FRAGILE to assure careful handling.

2-2

2-23. In any correspondence refer to the counter by model number and full serial number.

Page 22

Model 5328A

Installation

2-24. Other Packaging Methods

2-25. If factory packaging is not available, good commercial packing should be used. Contract

packaging companies in many cities can provide dependable custom packaging on short notice.

The following general instructions should be followed when repackaging with commercially

available materials.

a.

If shipping to a Hewlett-Packard Service Office or Service Center, attach a tag indi-

cating the type of service required, return address, model number, and full serial number.

b. Wrap the counter in heavy paper or plastic.

c.

Use a strong shipping container. A double-wall carton made of 350-pound test material

is normally adequate for shipments inside the U.S.

d. Use enough shock-absorbing material (3-to 4-inch layer) around all sides of the counter

to provide a firm cushion and prevent movement inside the container. Protect the con-

trol panel with cardboard.

e.

Seal the shipping container securely.

2-26. STORAGE

2-27. If the counter is to be stored for an extended period of time, it should be enclosed in a

clean, dry, sealed container. See specifications in Section I for storage environmental limitations.

2-3

Page 23

Page 24

Model 5328A

SECTION Ill

OPERATION

(OPERATORS INSTRUCTIONS)

3-1. INTRODUCTION

3-2. This section contains information necessary to understand how to control and use the

counter. Specific details and examples are provided for making measurements of frequency,

period, period average, time interval and time interval average, and ratio. How to use the external frequency standard input is described. Programming information for use with the HP-IB

Interface and the Programmable Input Module is provided. Front and rear panel controls, connectors, and indicators are described.

3-3. FREQUENCY MEASUREMENTS

3-4. To make a frequency measurement on a CW signal below 100 MHz, select FREQ A function, select the appropriate input signal conditioning, and apply the signal to A input. The

RESOLUTION switch determines the resolution of the measurement. Since the 5328A is a conventional counter, 1 Hz resolution is obtained in 1-second of measurement time (e.g., .1Hz

10 seconds). The .1 Hz best case frequency resolution limits the low frequency measurement

accuracy. In practice, low frequencies are measured by making a period or period average

measurement and inverting the result to obtain frequency.

Operation

3-5. To make a frequency measurement on a CW signal in the range of 30 to 500 MHz, select

FREQ C function and apply the signal to the Channel C input. Make sure that the amplitude

does not exceed 5V rms. The trigger level for the Channel C is fixed at 0V dc. If pulse waveforms are being measured, they must cross through 0 volts dc by at least 25 mV. Pulse widths

down to 1 ns can be counted.

CAUTION

DO NOT exceed 5 volts rms at “C” channel input. Circuits in this

channel may be damaged by higher voltages.

3-6. The A, B, and C input modules are direct count modules. Direct count allows greater resolution per-second of measurement time than prescaling techniques and is important in making

frequency measurements on pulse bursts since the allowable measurement time is fixed (it

must be less than the width of the burst).

3-7. When the 5328A is in FREQ A or FREQ C function and the rear panel ARM switch is OFF,

a measurement cycle is initiated (i.e., arms the counter) upon the first trigger level crossing at

the A (or C) input. This means that pulsed signals are measured as easily as CW if the measurement time (determined by the RESOLUTION switch) is less than the width of the pulse.

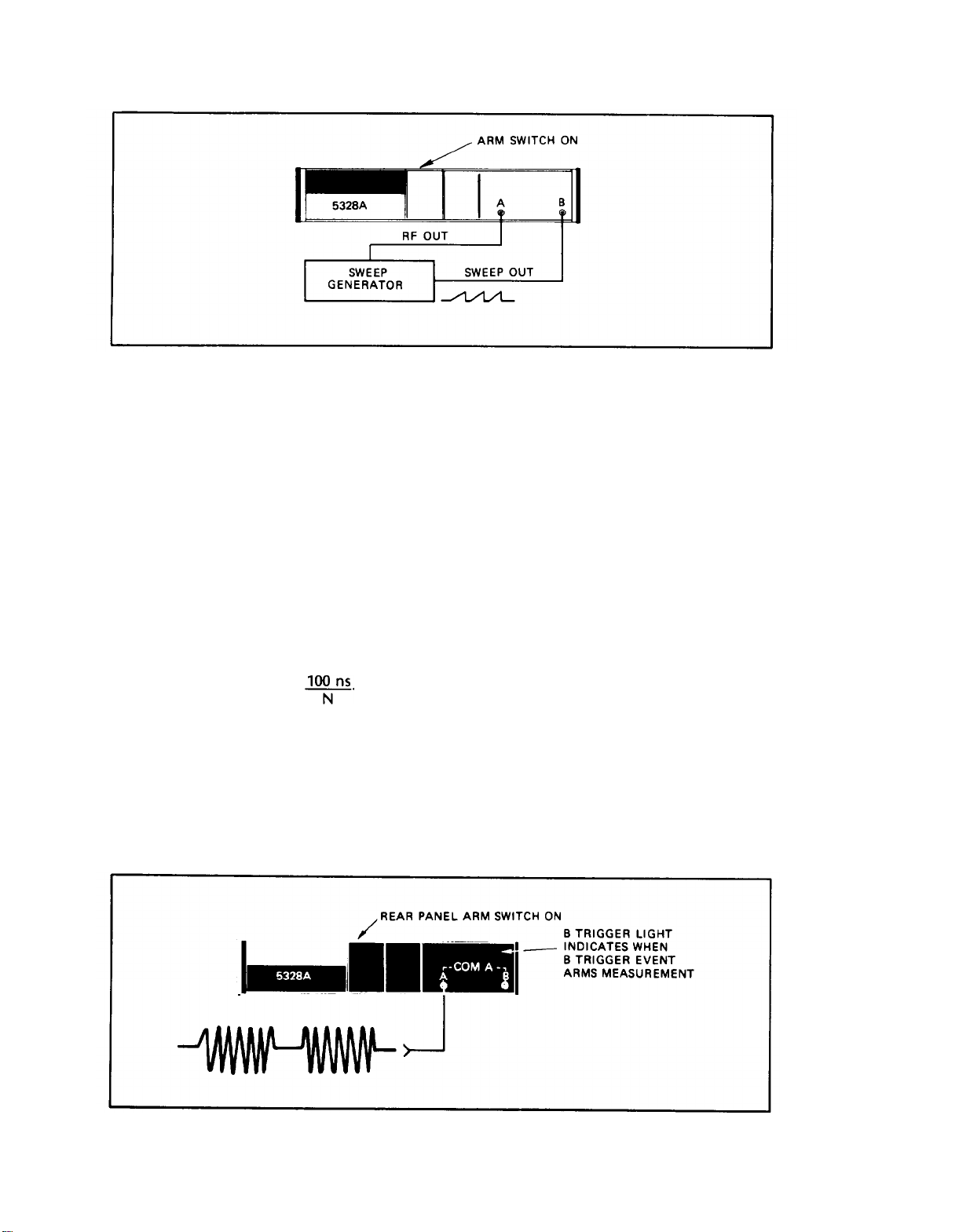

3-8. With the ARM switch ON, FREQ A and FREQ C are armed by a trigger event at the B input. This mode is useful whenever it is desired to have real time control over when a measurement is to begin. Useful applications include measuring frequency variations along a frequency

burst and linearity testing of sweep generators. Figure 3-7 illustrates the setup for measuring

the linearity of a sweep generator. The Channel B Trigger level is adjusted to trigger (and thereby arm the counter) at various points along the sweep out waveform. By plotting the B trigger

levels and the corresponding frequency measurements made at those levels, the linearity of the

generator may be determined.

3-1

Page 25

Model 5328A

Operation

3-9. PERIOD MEASUREMENTS

3-10. The PERIOD and PERIOD AVG functions allow single period measurement or multiple

period averages to be made on input signals into Channel A for frequencies up to 10 MHz. These

modes are useful for making low frequency measurements where maximum resolution is

desired.

Figure 3-1. Measuring Linearity

3-11. To make a PERIOD or PERIOD AVG measurement, select the desired function, select

appropriate input signal conditioning, and apply the signal to the A input. For single period

measurements, the RESOLUTION switch scales the time base frequency which determines the

resolution of the measurement. For optimum resolution, select N=1. Other N values may be

desirable to prevent display overflow or to get rid of unstable digits. For PERIOD AVG measurements, the RESOLUTION switch selects the number of periods over which the period average

measurement is made (the time base is 10 MHz for this case). the PERIOD AVG mode gives

increased resolution and accuracy. Trigger error is decreased by N and the resolution is in-

creased by N (resolution =

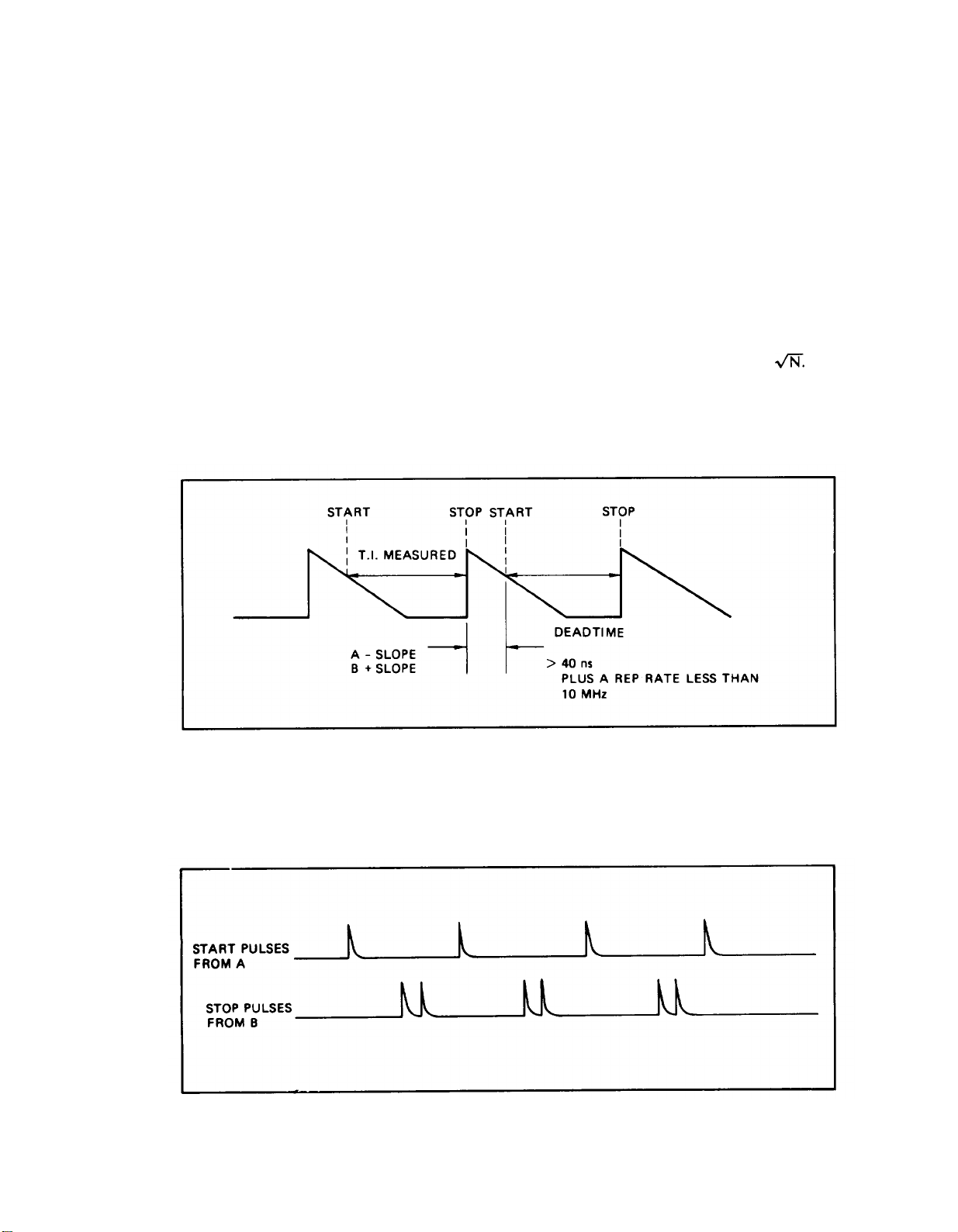

3-12. In PERIOD and PERIOD AVG with the rear panel ARM switch OFF, the measurement

cycle is initiated by the SAMPLE RATE control and the input signal. With the ARM switch ON,

PERIOD and PERIOD AVG are armed by a trigger event at the B input. To measure the frequency of a tone burst signal, use arming and the PERIOD AVG (for increased resolution over

a low frequency measurement) as shown in Figure 3-2. Select N equal to or less than the

number of periods in the tone burst and adjust Channel B trigger level to trigger on the first

cycle of the input signal.

~.

The measurement time is equal to the period times N.

3-2

Figure 3-2. Tone Burst Measurement

Page 26

Model 5328A

Operation

3-13. TIME INTERVAL MEASUREMENTS

3-14. One of two time interval functions can be selected, time interval or time interval average.

These functions measure the time interval between a START signal at the Channel A input and

STOP signal at the Channel B input. If both the START and the STOP signals are derived from

the same signal, place the COM A-SEP in COM A position. Separate slope and level controls

for each channel allow variable triggering on either positive or negative going slope.

3–15. In single-shot time interval measurements, Channel A opens the main gate and Channel

B closes the main gate. While the main gate is open, 10 MHz is divided by the setting of the

RESOLUTION switch and totalized by the counter. For optimum resolution, select N=1. Other N

values may be chosen to prevent display overflow (e.g., long time intervals) or to get rid of

unstable digits. In time interval average measurements, the main gate is open for the number

of time intervals selected by the RESOLUTION switch. The 5328A 10 MHz clock is totalized only

during the individual time intervals. The resolution of the measurement is improved by the

3-16. In order to allow the synchronizers time to reset during time interval averaging, there

must be at least 40 ns deadtime (and the additional constraint that the repetition rate be less

than 10 MHz). Deadtime is the time between the preceding time interval stop event and the

current time interval start event as shown in Figure 3-3.

fi.

Figure 3-3. Deadtime

3-17. During a time interval average, there must be only one stop pulse for each start pulse.

Extraneous stop pulses which occur before the next start pulse are accumulated and give erroneous readings. For example, the case illustrated in Figure 3-4 would result in a reading equal

to one-half of the desired time interval.

Figure 3-4. Multiple STOP Pukes

3-3

Page 27

Model 5328A

Operation

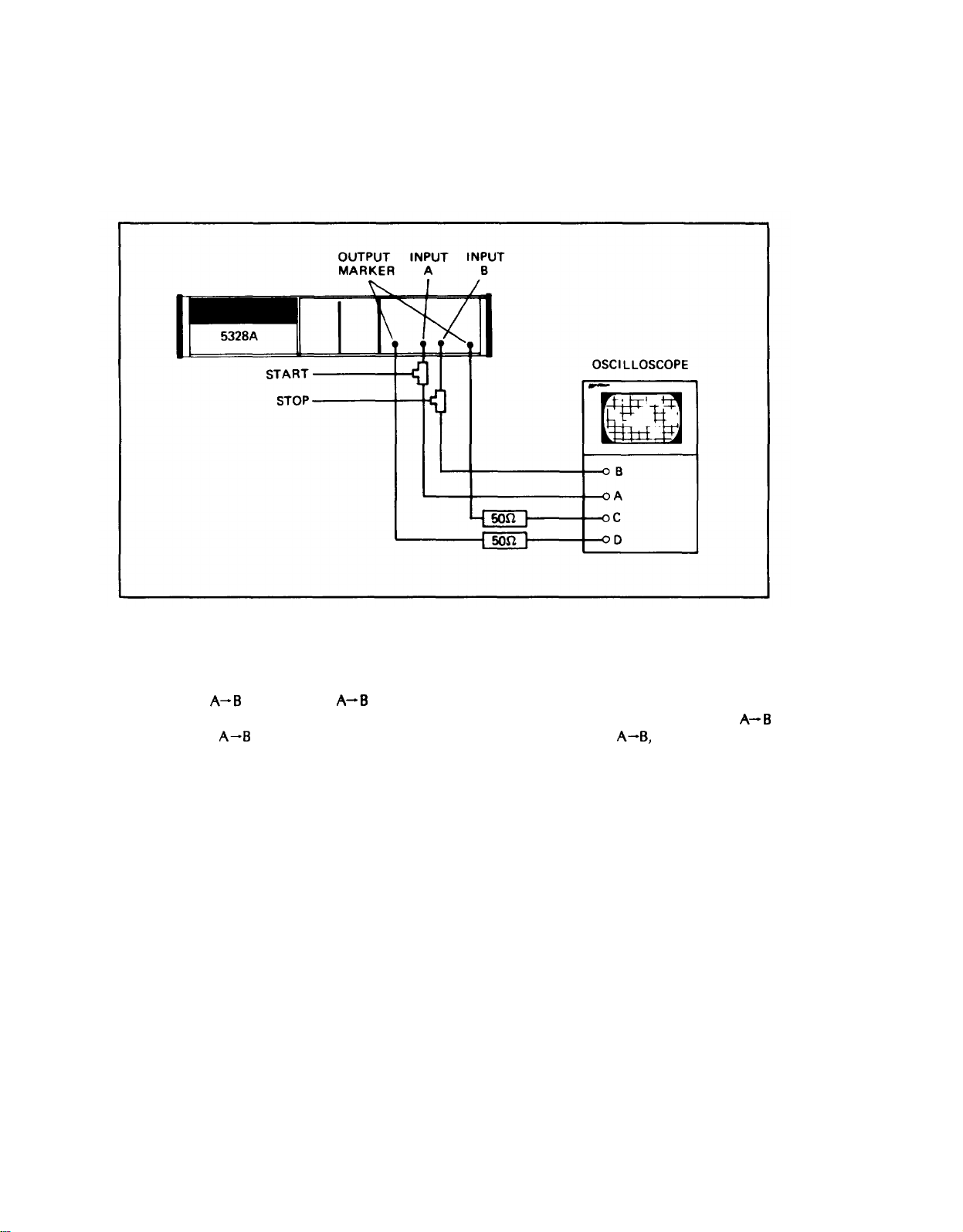

3–18. To set up a time interval measurement, the marker outputs may be monitored on an

oscilloscope (see Figure 3-5) to indicate where the channels are triggering with relation to the time

interval of interest. The GATE/MARKER OUT is high during the time interval being measured.

Figure 3-5. Monitoring Marker Outputs

A-B

3–19. In T.I.

by the run down of the SAMPLE RATE control. With the rear panel ARM switch ON, T.I.

and T.I. AVG

signal is required per average measurement (i.e., the counter doesn’t need to be armed prior

to each individual time interval in the time interval measurement).

3-20. RATIO MEASUREMENTS

3-21. For ratio measurements, the 5328A has wide bandwidth, good sensitivity, and complete

signal conditioning of the Channel A, B, and C input amplifiers.

3–22. Two ratio functions are available: B/A and C/A. The ratio of the frequency at B (or C)

to the frequency at A is measured for N counts of A where N is selected by the RESOLUTION

switch. The resolution of the measurement improves with increasing N and is given by 1 part

in B/A x N (or C/A x N). Since the range of A is 0-10 MHz while B is 0-100 MHz, the lower

frequency is normally applied to the A input although there is no restriction that this be the

case (i.e., ratios less than 1 may be measured). If B/A is greater than 1, the measurement reso-

lution is better than switching the inputs for a ratio <1, provided the value of N remains the same.

3-23. OPERATING CONTROLS

and T.I. AVG

A-B

are armed by an event at the C input. For T.I. AVG

A-B

with the rear panel ARM switch OFF, the counter is armed

A-B,

only one arming

A-B

3-4

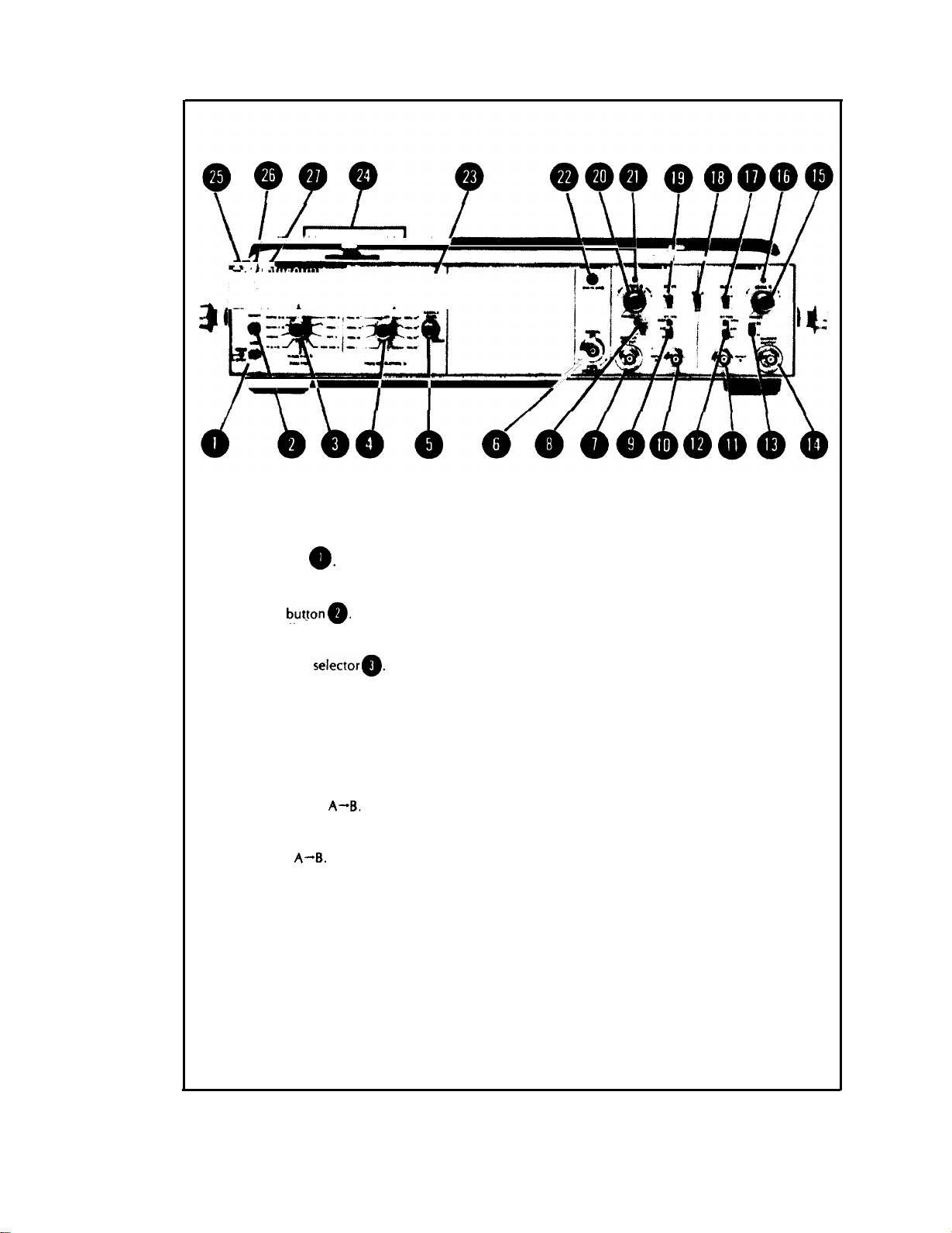

3–24. All of the front and rear panel operating controls are shown and described in Figures

3-6 and 3-7.

Page 28

Model 5328A

Operation

1.

LINE switch0.In STBY position with light on, supplies power to oven of the high stability

time base to maintain a constant temperature for the crystal. In OPER position, supplies normal

operating power to the instrument.

2.

RESET

lights all segments of the LED display and all annunciator LED’s for LED test. Returns 5328A

to LOCAL CONTROL when HP-IB Interface is in use.

3.

FUNCTION

a.

b.

c.

d.

e.

f.

g.

h.

i.

j.

button~.

FREQ A. Sets counter to measure frequency at Channel A.

FREQ C. Sets counter to measure the frequency of the signal at the Channel C input.

PER A. Sets counter to measure period at Channel A.

PER AVG A. Sets counter to make a period average measurement of the signal at Chan-

nel A. The number of periods over which the average measurement is made is determined by N, selected by the RESOLUTION switch.

T.I. AVG

interval from A to B. The number of time intervals over which the average measurement

is made is determined by N, selected by the RESOLUTION switch.

T.I.

A-B.

Channel A and the stop signal is applied to Channel B.

CHECK. Applies 10 MHz to decade counting assemblies. Verifies operation of SAMPLE

RATE control, RESOLUTION switch, and RESET.

RATIO C/A. Sets counter to measure the ratio of the signal frequency at Channel C to

the signal frequency at Channel A.

RATlO B/A. Sets counter to measure the ratio of the frequency at Channel B to the fre-

quency at Channel A.

Top blank position has no function.

Resets display and internal count to zero. When continuously depressed,

selector~.

A-B.

Sets counter to make a time interval measurement. Start signal is applied to

Selects mode of operation.

Sets counter to make a time interval average measurement of the time

Figure 3-6. 5328A Front Panel Operation Summary

3-5

Page 29

Model 5328A

Operation

3-6

Figure 3-6. 5328A Front Panel Operation Summary (Continued)

Page 30

Model 5328A

Operation

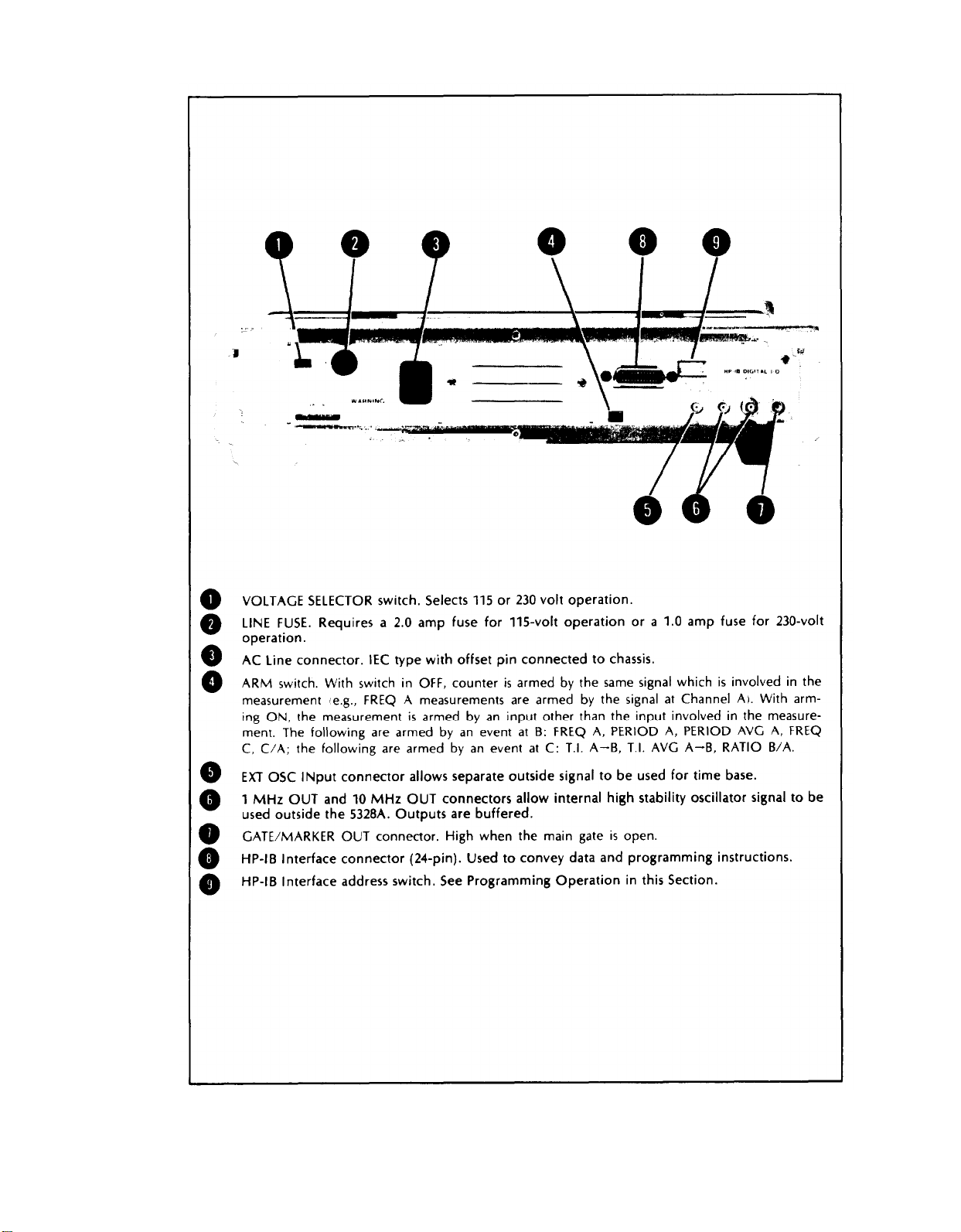

Figure 3-7. 5328A Rear Panel Controls and Connectors

3-7

Page 31

Model 5328A

Operation

3-25. FUNCTION OF CONTROLS, INDICATORS, INPUTS, AND OUTPUTS

3-26. The following paragraphs provide a detailed description of the function of controls, indi-

cators, and connectors.

3-27. Display

3-28. The 5328A counter display consists of nine-digit, seven-segment LED display and annun-

ciators for indicating the measurement units of Hz, s, as well as multiplier indicators (K, m,

n). These display units and multipliers are automatically displayed along with the correct decimal point location. Overflow (OVFL) indicates that left-most-significant digits have overflowed

the display. Remote (RMT) indicates that the counter (HP-IB interface) is under remote program

control. A GATE lamp indicates that the counter has been armed and that a measurement is

in process.

3-29. Power (Line)

3-30. The LINE switch puts the counter in OPER (operate) or STBY (standby). The STBY

position with STBY light on turns off some but not all the power supply voltages. This circuit

arrangement allows the high stability oscillator to operate continuously. Therfore, the input

to main power transformer (T1) plus the unregulated dc voltage to the oscillator oven is always

energized whenever power is connected even with the line switch in STBY.

~,

3-31. Reset

3–32. The RESET pushbutton resets the display and internal count to zero and also initiates

single measurements when the SAMPLE RATE control is in the HOLD mode, The HP-IB interface,

provides remote control capability, pushing the RESET button restores the counter to local control (when not remotely locked out by the HP-IB Local Lockout universal command). Refer to

programming in this section.

3-33. Sample Rate Control

3–34. The SAMPLE RATE control sets the minimum time between samples, The time is con-

tinuously variable from less than 2 milliseconds between measurements to HOLD, which holds

the display indefinitely.

NOTE

The counter will internally (self) arm (via the SAMPLE RATE control)

only when ARMing is OFF and the FUNCTION selected is at other

than FREQ A, FREQ C, and RATlO C/A.

3-35. Arming

3-36. The counter may be armed internally (i.e., made ready to start a measurement) by the

SAMPLE RATE control, or externally by the input signal itself, (arming off) or by a signal not

directly involved in the measurement (arming on). Table 3-7 is an arming status table. A rear

ps

panel switch turns ARMing either ON or OFF. The counter is armed within 1

ps

at the B arming input and is armed within 10

after the event of the C arming input.

after the event

3-8

Page 32

Model 5328A

Table 3-1. Arming Status

3-37. Frequency Resolution, N Switch

3-38. The FREQUENCY RESOLUTION, N switch determines the amount of time that the

counter’s main gate is open for a particular measurement when the Main Gate FF (refer to

Section IV) determines the gate time. Depending on the measurement, this time results in a

certain measurement resolution (e.g., frequency measurements), a number of intervals averaged (e.g., T.1. AVG measurements), or a scaling factor by which the time base is divided (e. g.,

period measurements). Table 3-2 shows the setting of the RESOLUTION switch and the corresponding time the main gate is open.

Operation

Table 3-2. Frequency Resolution, N Switch Settings and Gate Times

3-39. Table 3-3 summarizes the FUNCTIONS

FREQUENCY RESOLUTION, N switch setting.

Table 3-3. Functions and Resolution Switch Settings

and the corresponding interpretation of the

3-9

Page 33

Model 5328A

Operation

3-40. Input Channel Section

3-41. Two separate inputs are provided on the right side of the panel. The A and B inputs are

identical in specification and identical controls are provided for each input to allow maximum

versatility and accuracy.

3-42. HP-IB PROGRAMMABLE INPUT CONTROLS. In COM A position, the output of the

Channel B attenutor is disconnected. The output of the Channel A attenuator is routed to the A

and B input amplifiers as shown in Figure 3-8. In COM A the Channel B AC-DC, X1, X10, X100

Attenuator relays are disabled. The Channel A AC-DC, X1, X10, X100 Attenuator determine the

coupling for the Channel B amplifier.

3-10

Figure 3-8. Programmable Input Switch Configuration for COM A

3-43. The A and B input amplifiers have independent LEVEL and SLOPE controls regardless

of the mode of operation (SEP or COM A).

3-44. A and B Channel Signal Conditioning

3-45. AC-DC SWITCH. The AC-DC switch controls the coupling of the external signal to the

attenuator-amplifier by switching a capacitor in series in the AC position or by direct coupling

in the DC position. The advantage of AC coupling is to provide a DC block for signals with a

DC component. DC has the disadvantage of being unable to pass low frequency signals. A

distinct advantage of having DC coupling cover the full bandwidth (DC-100 MHz) is that

extremely accurate time interval or pulse measurements can be achieved even though pulse

widths or repetition rates vary since the trigger point is independent of the duty cycle of the input

signal.

3-46. ATTENUATOR. The attenuator (ATTEN) connects the input signal directly to the

amplifier (in X1) or through a 10:1 attenuator (X10) or a 100:1 attenuator (X100) to increase the

voltage range by 10 or 100 times to allow measurement of high level signals that would otherwise be impossible without external attenuation.

Page 34

Model 5328A

Operation

3-47. SLOPE SWITCH. The ±SLOPE switch (provided for each channel) determines which slope

of the input signal will trigger the counter. As a simple example, (Figure 3-9) if the pulse width of a

positive pulse is to be measured, the A channel slope switch would be set to “+” and the B channel would be set to “-” (for time interval measurements the A channel always begins the measurement and the B channel ends the measurement).

NOTE

A simple pulse width measurement is achieved with the use of the

+SLOPE setting for Channel A and the -SLOPE setting for Channel B.

Figure 3–9. Slope Switch Settings

3-48. LEVEL CONTROL. The LEVEL control for each channel is adjustable over the range of

±2.5V dc with the attenuator for that channel in the X1 position. A typical use of the LEVEL controls is shown in Figure 3-10.

NOTE

Simple measurement of a time interval, the LEVEL control of the A

and B input channels were used to set the trigger LEVEL of A and B.

Figure 3-10. Level Control Settings

3-11

Page 35

Model 5328A

Operation

3-49. Channel C Input

3-50. The CHANNEL C 500 MHz

A and B input channel range (0 to 100 MHz).

3-51. “C” Channel Overload lndicator

3-52. The OVERLOAD (CHANNEL C) indicator will flash on and off if the voltage maximum

is exceeded at the “C” channel input.

3-53. Hysteresis Band of Trigger Levels

3-54. The width of the trigger level hysteresis band, shown in Figure 3-77 is determined by the

sensitivity of the counter. For frequencies below 40 MHz, it is typically less than 25 mV peak-topeak. At frequencies from 40 MHz to 100 MHz, it is typically less than 70 MHz peak-to-peak. The

signal must pass through the entire hysteresis band before a trigger pulse is generated. If the

SLOPE switch is set to “+”, the trigger pulse occurs at the top of the hysteresis band. If the SLOPE

switch is set to “-”, the trigger pulse “occurs at the bottom” of the hysteresis band.

500

input is useful for higher frequency signals out of the

CAUTION

The “C” channel input signal should be limited to 5 volts maximum.

If this limit is exceeded the inline fuse may open (blow).

3-12

Figure 3–11 Hysteresis Band

3-55. Since trigger level measurements indicate the center of the hysteresis band, a better

value for the actual trigger level may be obtained by subtracting one-half the hysteresis band

(“-” slope) or adding one-half the hysteresis band (“+” slope). A typical value for the width of

the hysteresis band is 30 mv peak-to-peak.

3-56 The value to use for the hysteresis band depends on the frequency; or, for pulses, it de-

pends on the rise time.

3-57. External Frequency Standard Input

3-58. The rear panel external frequency standard (EXT OSC IN) input is useful for locking

the counter to a high stability external frequency standard. This external standard must be 1,

2.5,5, or 10 MHz, with an amplitude of >1V rms into 1

kfl

(maximum input of 5 volts peak-to-peak).

Page 36

Model 5320A

Operation

3-59. Marker Outputs

3-60. Two marker output connectors are mounted on the front panel. These outputs represent

the Channel A and Channel B Schmitt triggers. The outputs provide 0 to 300 mV levels into

50Q

delayed by less than 20 ns. These outputs are useful for oscilloscope monitoring, Time

interval measurement setups are simplified if the time interval of interest and the marker outputs can be simultaneously displayed on oscilloscope traces. Frequency measurements on noisy

signals can be made with more confidence since the markers can indicate the presence of noise

triggering. These outputs are protected from inadvertently applied voltage to ±5V dc.

3-61. Gate/Maker Out

3-62. the GATE/MARKER OUT rear panel connector supplies a TTL level which is high when

the counter’s main gate is open and low when it is closed. Monitoring the GATE OUT on an

oscilloscope can provide this information for applications where the markers do not give the

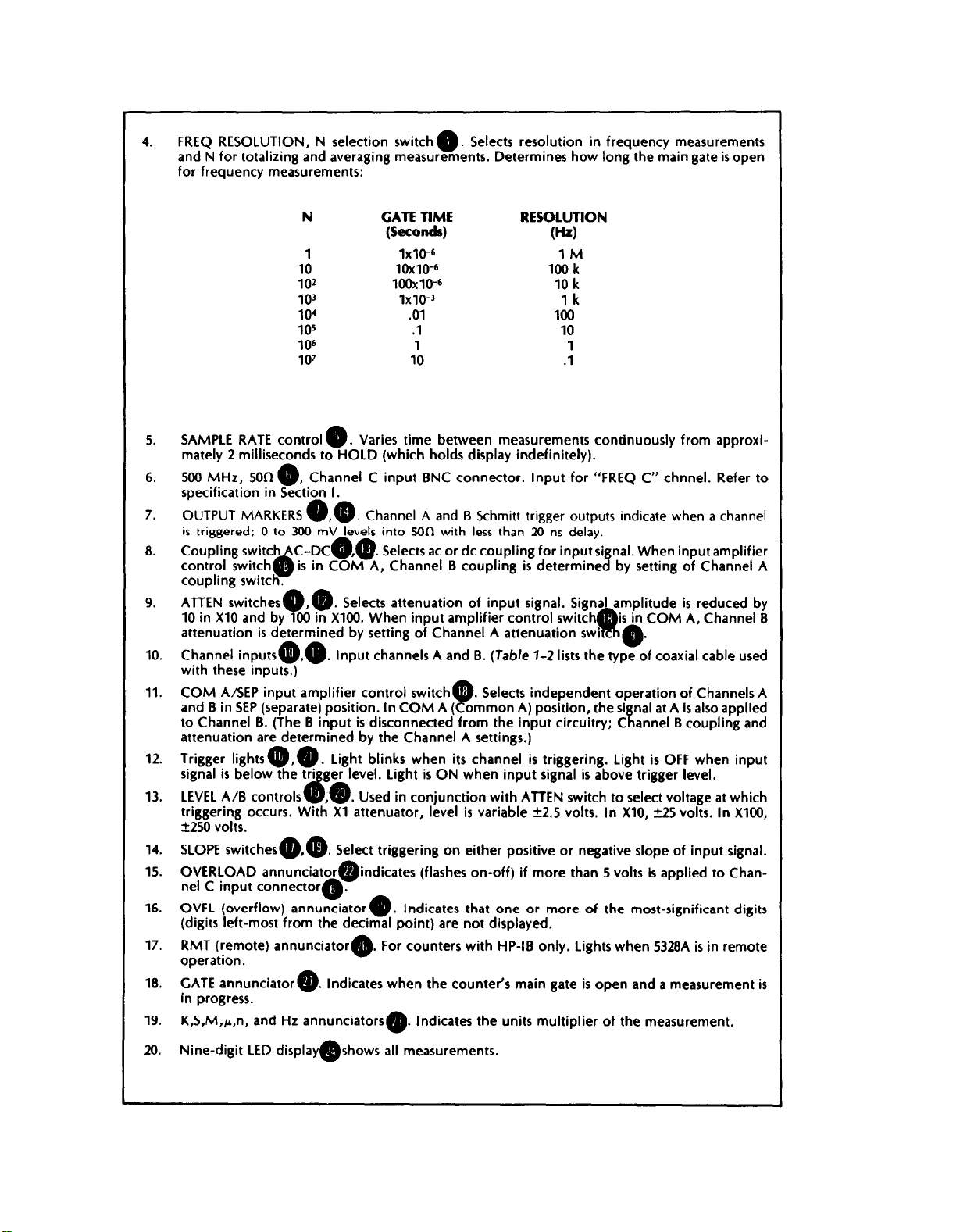

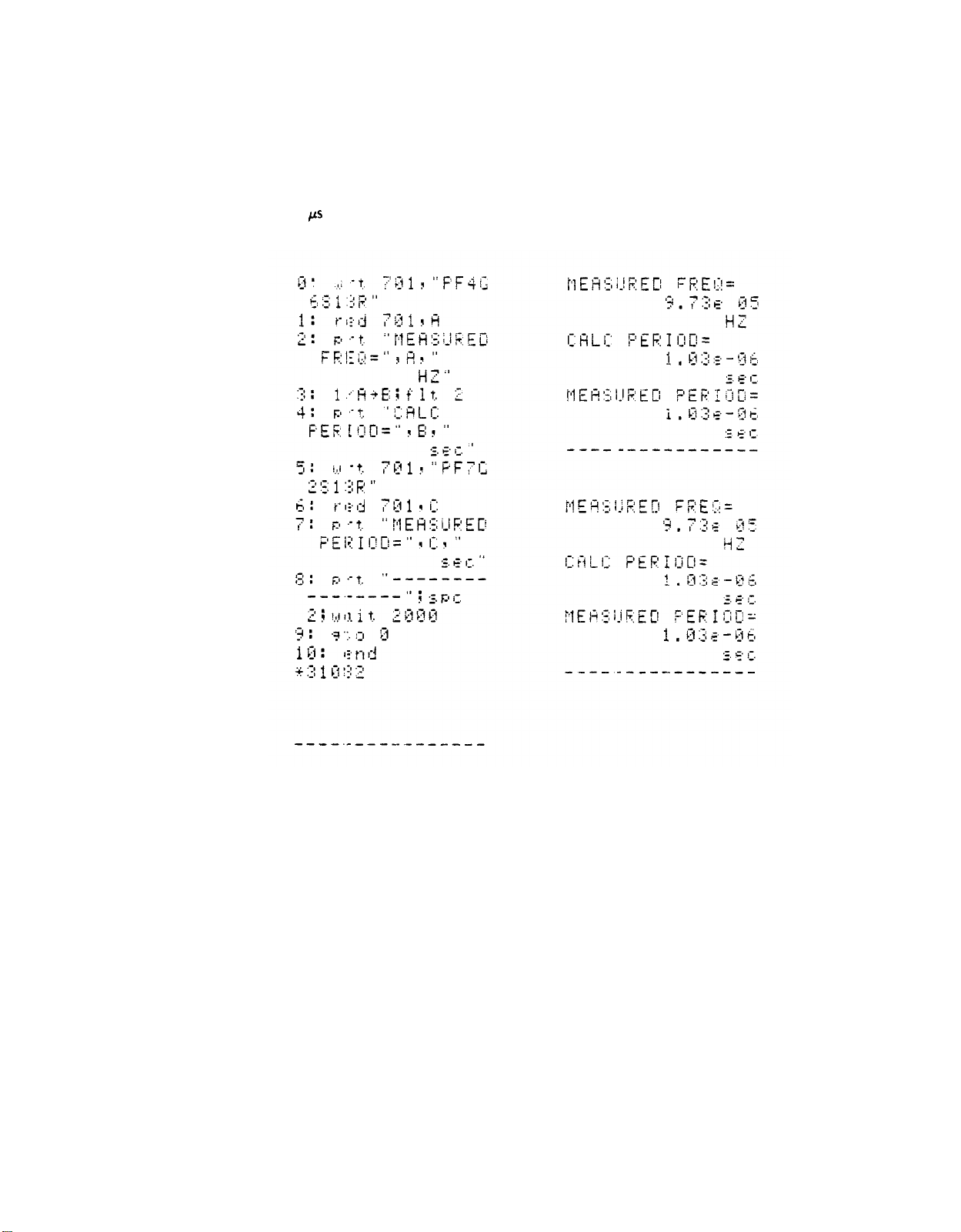

desired information.