Page 1

A

B

C

D

E

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

1 1

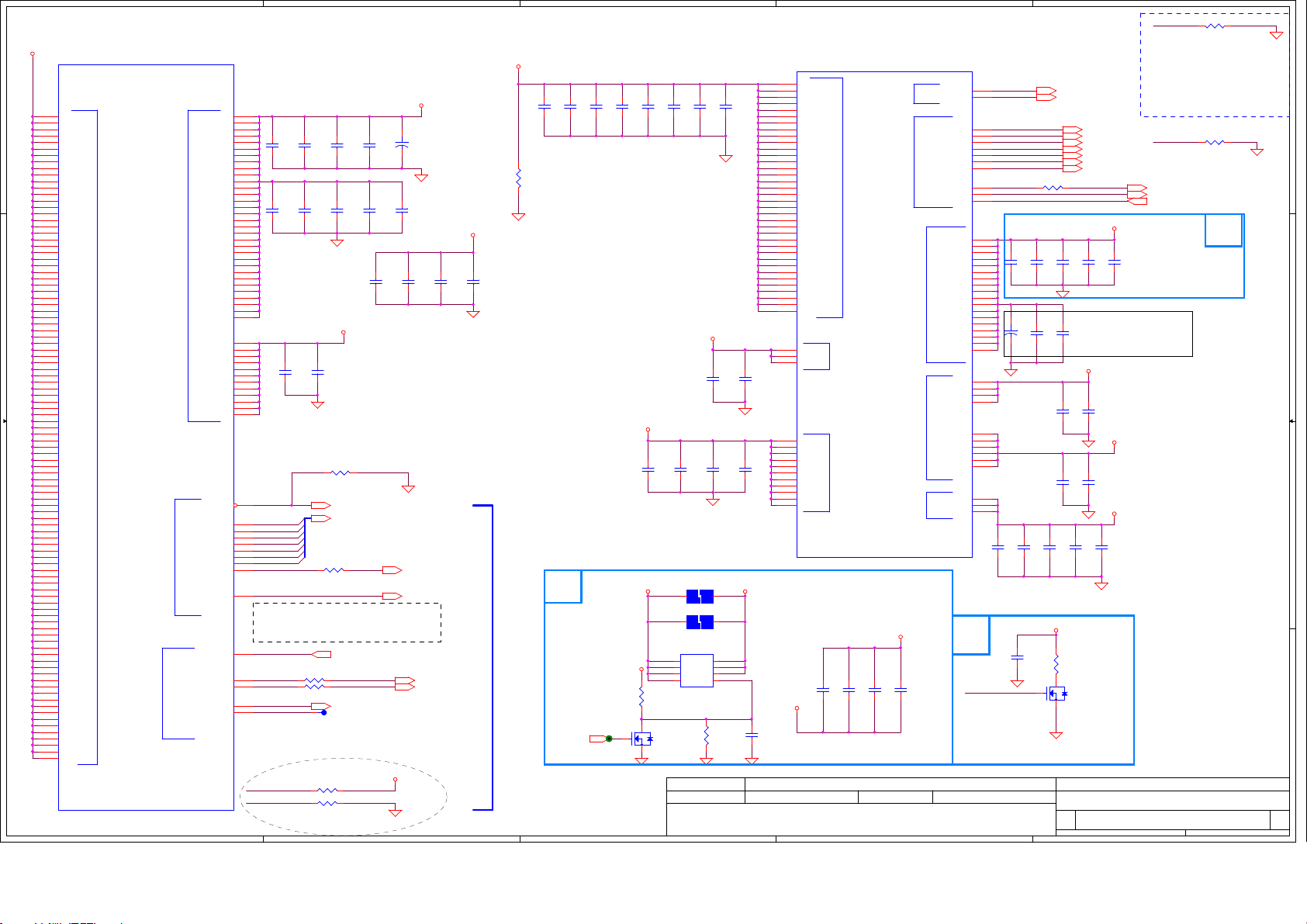

Compal Confidential

NIWE2

2 2

Schematics Document

Arrandale

with Intel IBEX PEAK-M core logic

3 3

REV:0.3

4 4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/03/25 2008/04/

C

Compal Secret Data

Deciphered Date

Compal Electronics,Ltd.

Title

Cover Sheet

Size Docu ment Numb er R ev

Cus tom

LA-5752P

D

Dat e: Sheet o f

1 51Thur sday, Octobe r 29, 2009

E

0.3

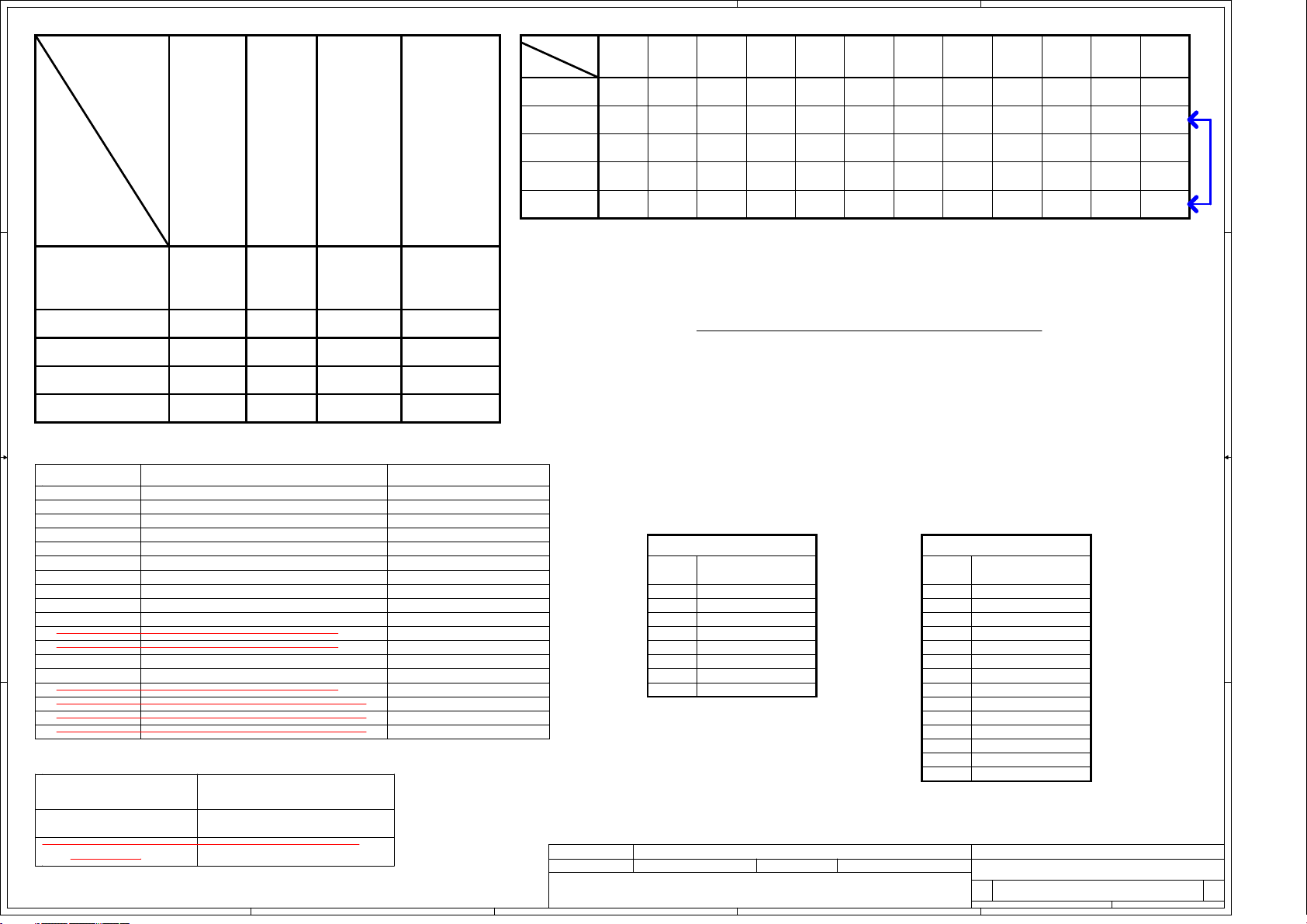

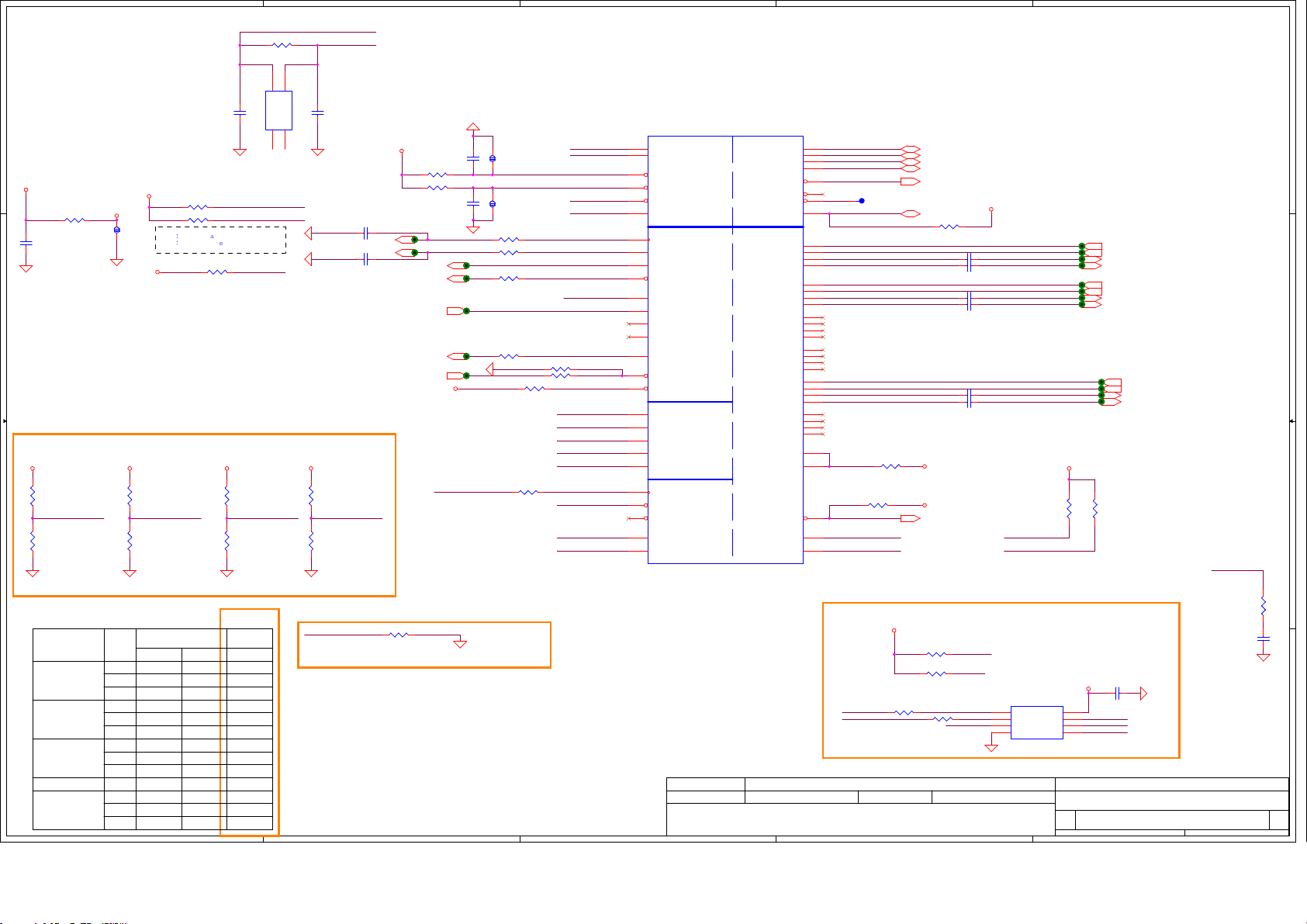

Page 2

A

Compal confidential

File Name :

ZZ Z

15.6W_PCB_LA5752P

1 1

HDMI

CO NN

page24

VR AM 6 4*16

DD R3*4

page20

NVidia N11M-GE1

page19~ 23

level shift IC

ASM 1 4 42

page25

PCI-E X16

B

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

intel

Arrandale

(UMA/DIS)

C

POWER BD: LS-5754P

POWER BT

NOVO BT

POWER MANAGE BT

D

CAP SENSOR BD:LS-5752P

VOLUME UP

VOLUME DOWN

MUTE

AUDIO ENHANCE

E

CARD READER BD:

LS-5753P

RTS5138

HP JACK

MIC JACK

BUTTON & LED

Clock Generator

ICS9LRS3199AKLFT

page12

Socket-rPGA989

37.5mm*37.5mm

page5~9

DDR3-SO-DIMM X2

BANK 0, 1, 2, 3

page 10,11

Dual Channel

100MHz

2.7GT/s

FDI *8

DMI *4

DDR3-800(1.5V)

DDR3-1067(1.5V)

UP TO 8G

2Channel Speaker

page33

CRT Connector

page26

2 2

LVDS

Co nnector

page27

PCI Express

Mini card Slot 1

page28

6*PCI-E B US

PCI Express

Mini card Slot 2

SIM Card

3 3

page28

page28

USB(WWAN)

SPI ROM

BIOS

page13

RTL8111DL-VB-GR

10/100/1G LAN

RJ45 CONN

page29

page30

Intel Ibex Peak M

FCBGA 951

25mm*25mm

LPC BUS

EC

ENE KB926D

Touch Pad

page35

page 13 ~18

page34

Int.KBD

SPI ROM

AZALIA

14*USB2.0

6*SATA serial

page35

page36

Audio Codec

Conexant

CX20671

page33

CMOS Camera

BlueTooth CONN

USB CONN X1(Right)

USB PORT X1(Left)

New Card X1

WWAN

SATA HDD CONN

page32

page27

page37

page28

page28

Analog MIC_Int

page37

page37

Card Reader/Audio Jack SB

CONN

Realtek 5138

MS/MS

pro/SD/SD

pro/mmc/XD

page33

HP X 1+

MIC_Ext X1

ESATA HDD AND USB CONN

page38

page37

4 4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/03/24 2008/04/

SATA ODD CONN

Compal Secret Data

Deciphered Date

page32

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

MB Block Diagram

LA-5752P

2 51Thurs day, October 29, 2009

E

0.3

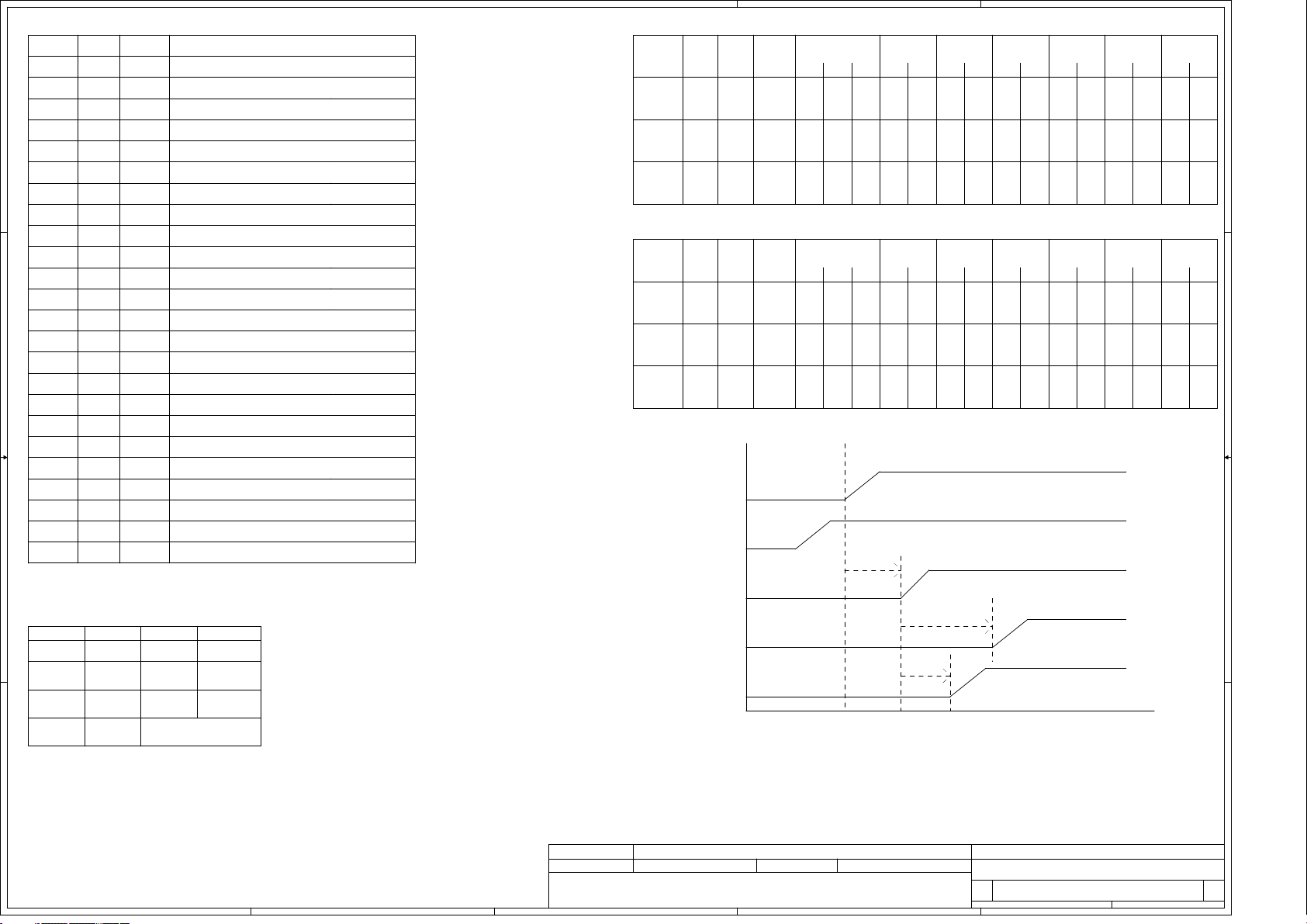

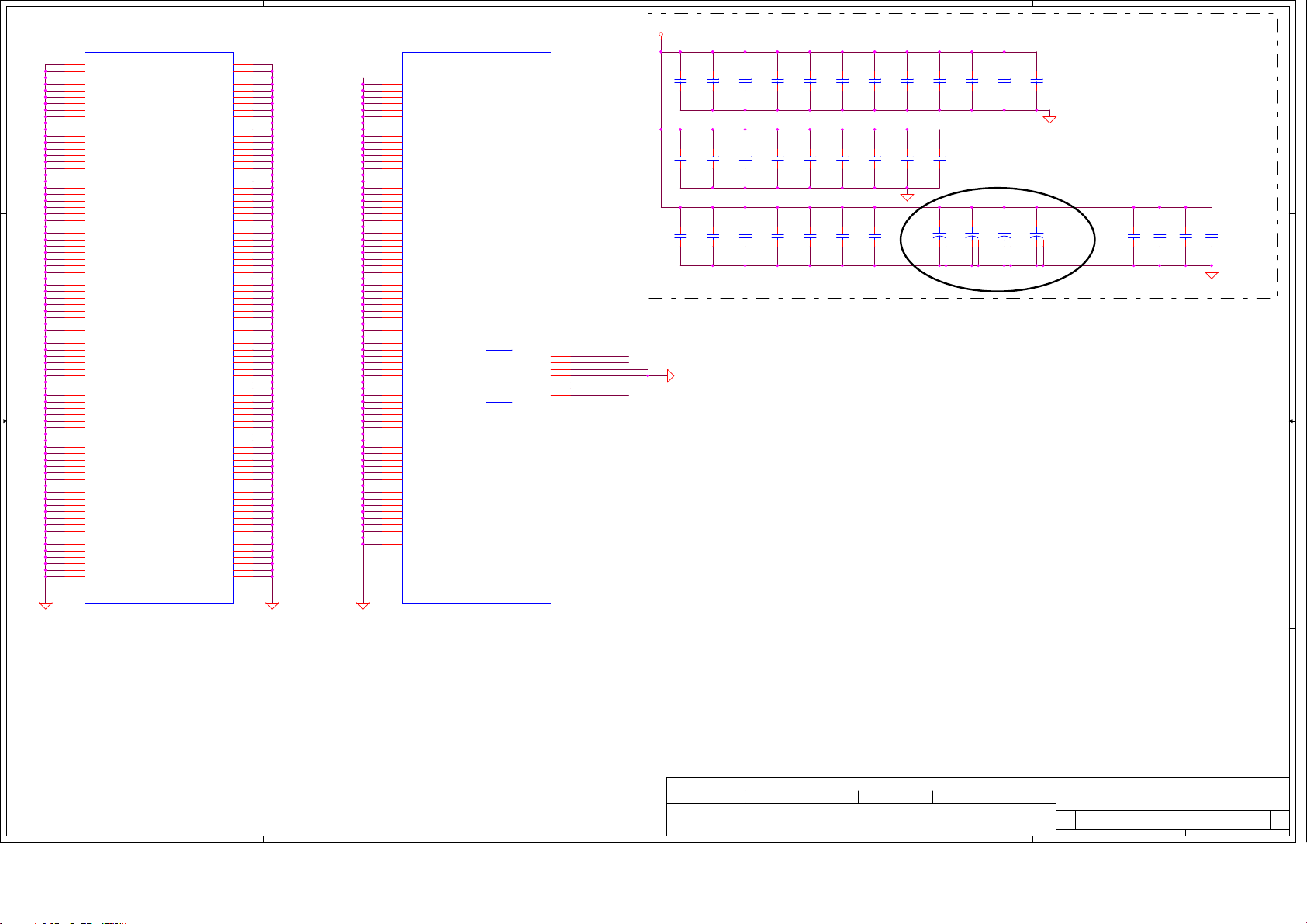

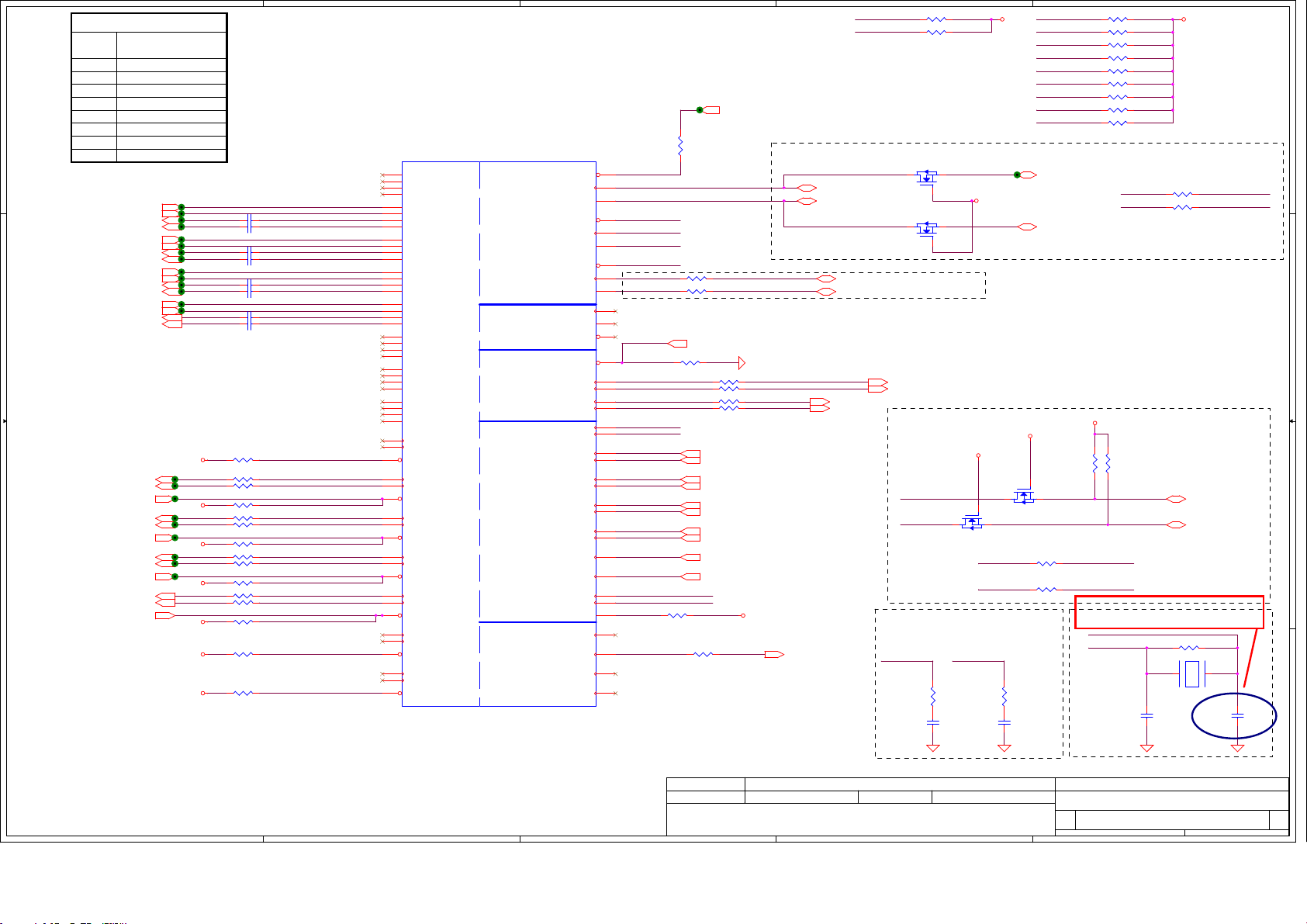

Page 3

A

DDR3 Voltage Rails

power

plane

1 1

+B

State

+5VALW

+3VALW

+1.5V

B

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

SMBUS Control Table

+5VS

+3VS

+1.5VS

+VCCP

+CPU_CO RE

+VGA_CO RE

+1.8VS

+0.75VS

+1.05VS

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

C

SOURCE

KB926

+3VALW

KB926

+3VALW

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

RAM

M2

X V

X

V

+3VALW

X

D

BATT KE926 SODIMM CLK CHIP

+3VALW

X

X

X

X

X

X

V

+3VALW

X

X

V V

+3VS

X

X

X

+3VS

X

WLAN

WWAN

N10x

Thermal

Sensor

X

X

X

X X

X

X X

X

X

V

+3VS

N10x

X

X

X

Cap sensor

bo ard

X

XX

X

X

V

+3VS

E

NEW

CARD

X X

X

V

+3VS

XXX X X X X X

PCH

V

+3VALW

X

X

S0

S3

2 2

S5 S4/AC

S5 S 4/ Batter y only

S5 S 4/AC & Ba ttery

don't e xist

O

O

O

O

X

O

O

O

X

O

X X

X

X X X

OO

I2C / SMBUS ADDRESSING

X

DEVICE

DDR SO-DIMM 0

X

DDR SO-DIMM 1

CLOCK GENERATOR (EXT.)

HEX

A0

D2

ADDRESS

1 0 1 0 0 0 0 0

1 0 1 0 0 1 0 0A4

1 1 0 1 0 0 1 0

@ FUNCTION

EVT NON-USE

45@

100@ 10/100 LAN

GIGA@

UMA_HDMI@

HDMI@

3 3

3G@

X76@

ESATA@

CMOS@

BT@ Blue Tooth

10M@

11M@

UMA@

DIS@

VGA@ FOR NVIDIA PART

HYBRID@ FOR SWITCHABLE

HU@

HD@

SKU

Arrandale(dGPU)

4 4

DIS only

Arrandale(iGPU)

UMA only

Arrandale(iGPU+dGPU)

SWITCHABLE

A

(45 BOM)

GIGA LAN

FOR UMA HDMI components

FOR HDMI components

3G(WWAN) function

(X76 BOM)

ESATA function

Camera function

FOR 10M CHIP

FOR 11M CHIP

UMA only (Arranddale)

DIS only (Arranddale)

SWITCHABLE or UMA only

SWITCHABLE or DIS only

DIS@ / 100@ for EVT

UMA@ / 100@ for EVT

VGA@+HD@+HU@+HYBRID@

PCIE PORT LIST

DEVICEPORT

1

2

LAN

3

3G

4

NEW CARD

5

6

7

8

USB PORT LIST

DEVICEPORT

RIGHT SIDE0

1WLAN

LEFT SIDE

CMOS

2

3

LEFT SIDE

4

RIGHT SIDE

5

CARD READER

6

7

WIRELESS8

9

NEW CARD

10

BT

11

12

3G

13

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/03/24 2008/04/

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

B

D

Date: Sheet of

Compal Electronics, Inc.

MB Notes List

LA-5752P

3 51Thurs day, October 29, 2009

E

0.3

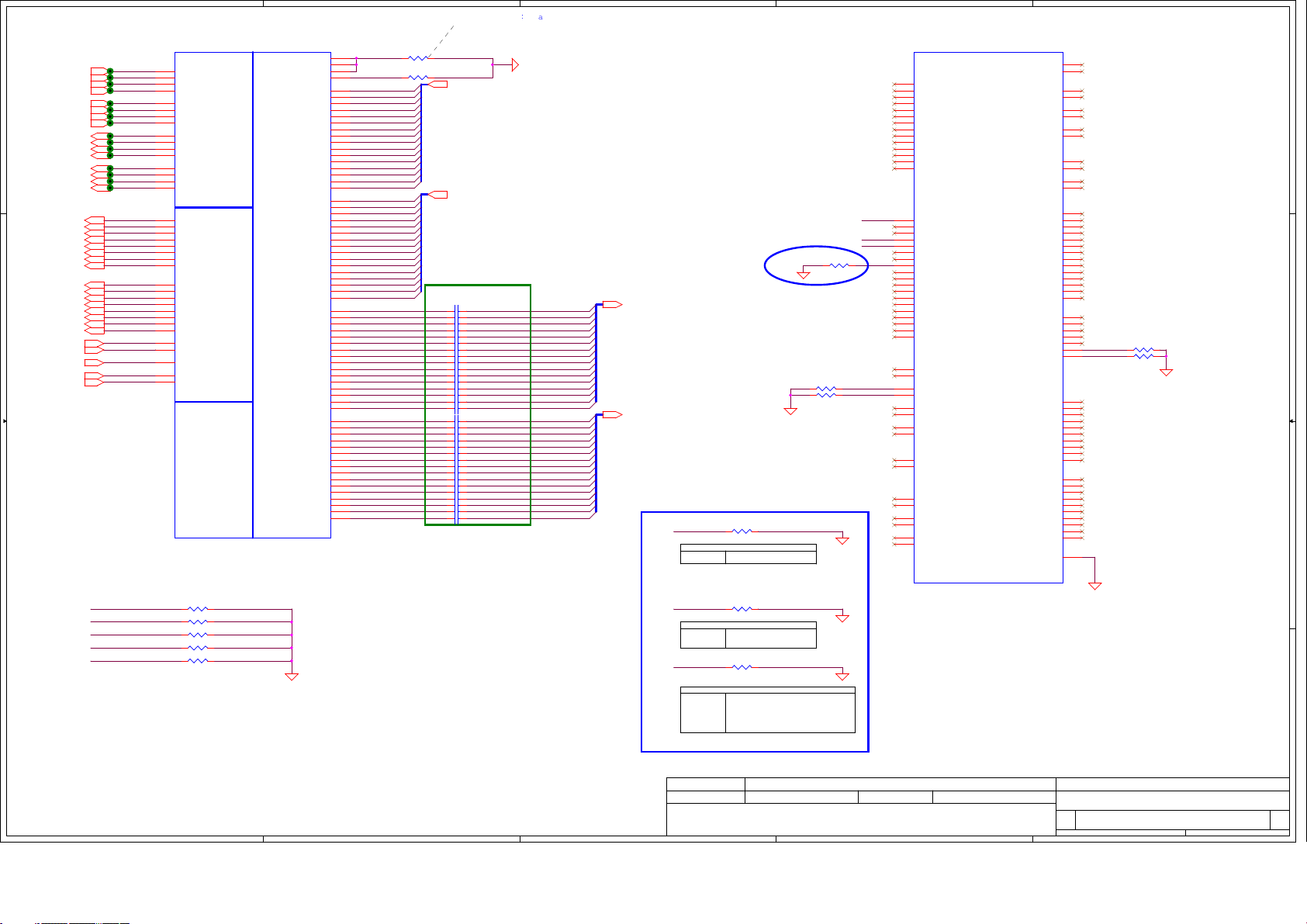

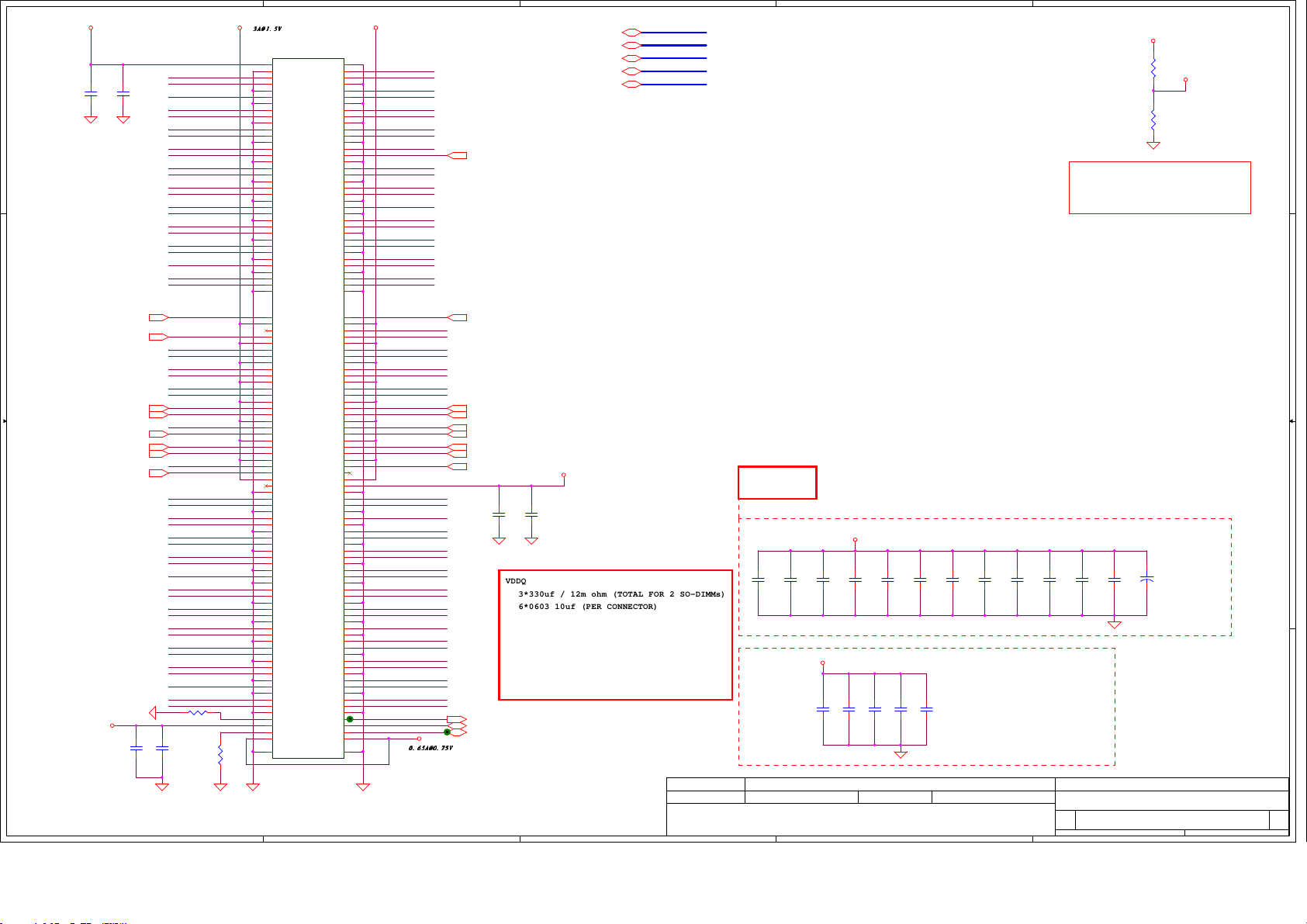

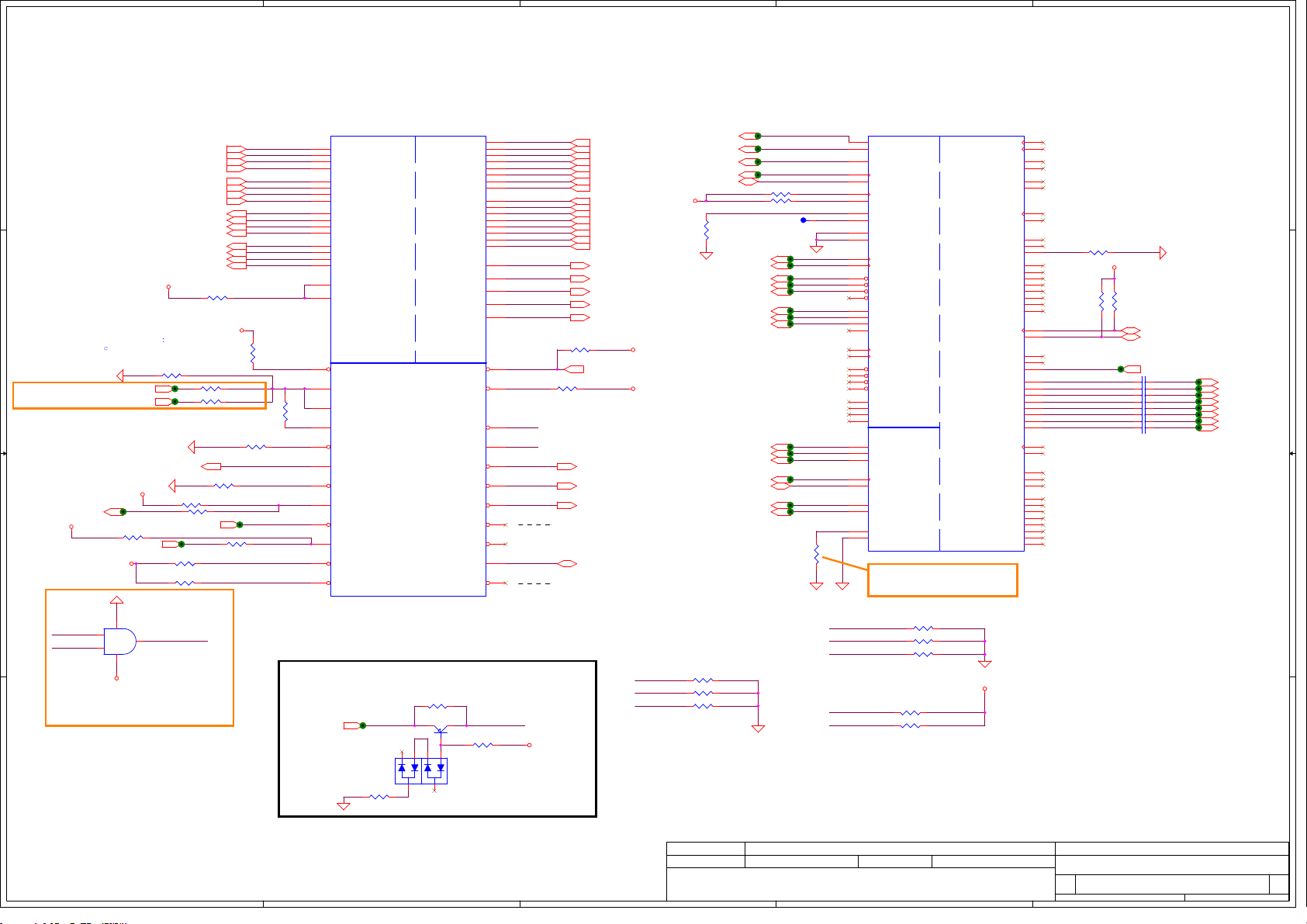

Page 4

A

GPIO I/O ACTIVE Function Description

GPIO0

GPIO1

GPIO2

1 1

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

2 2

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

GPIO22

GPIO23

3 3

GPIO6

GPU_VID 1 G PU_VID0 VGA _CORE

0 1

1 0

1 1

N/A

N/A

IN

-

Hot pl ug detect for IFP link C

OUT

OUT

OUT

OUT

OUT

OUT

I/O

OUT

OUT

I/O

IN

OUT

OUT

IN

OUT

IN

IN

IN

IN

IN

IN

Panel Back-Li ght b rightness(PWM capable)

H

Pan el Powe r Enab le

H

Panel Back-Li ght On/Off (PWM)

H

GPU VID0

-

GPU VID1

-

GPU VID2

-

Thermal Catast rophic Overtemp

L

Therma l Alert

L

Memory VREF switch

SLI raster sync

L

AC pow er det ect pin

-

MEM_VID orPower supply control

-

- Powe r supply control

-

Hot pl ug detect for IFP Link E

-

Progra mmable Fan Co ntrol

-

-

-

Hot pl ug detect for IFP Link D

-

-

Hot pl ug detect for IFP link F

-

SLI sw ap ready signal

I/O

GPIO5 N10M-GS N10P-GS

00

0.8V

0.85V 12

0.9V

P-State

12

0,10

1.0V (N10M-G S)

0.92 5V (N10P- GS)

B

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

C

D

E

Performance Mode P0 TDP at Tj = 102 C* (DDR3)VGA and DDR3 Voltage Rails (N10x GPIO)

Products

N10P-GS

128bit

1024MB

DDR3

N10P-GE

128bit

1024MB

DDR3

N10P-LP

128bit

1024MB

DDR3

GPU Mem NVCLK

(4) (1,5) (6)

(W) (W)

21.07

20.97

15.48

/MCLK NVVDD

(MHz)

6.67

TBD

6.73

TBD

6.44

TBD

(V) (A) (W ) (A) (W) (A) (W) (W)(mA) (W) (W) (W)(mA) (mA) (mA)

TBD

18.25

TBD

19.17

TBD

13.95

17.34

17.25

11.86

FBVDD

2.06

2.03

1.90

FBVDDQ PCI Express I/O and

(GPU+Mem)

(1.5V)(1.5V)

3.09

4.09

6.14

3.05

4.09 6. 14

2.85

3.99

5.99

0.89

0.88840

0.85

PLLVDD

75 0.14

75 0.14

(1.05V)

850 75 0.14

810

I/O and

PLLVDD

63 0.07

63 0.07

63 0.07

Other

(3.3V)(1.05V)(1.8V)

55 0.18

55 0.18

55 0.18

Performance Mode P0 TDP at Tj = 102 C* (DDR3)

Products

N10M-GE

64bit

512MB

DDR3

N10M-GS

64bit

512MB

DDR3

N10M-LP

64bit

512MB

DDR3

Power Sequence

(+3VS)

(1. 05VS)

(+V GA_CORE)

GPU Mem NVCLK

(4) (1,5) (6)

(W) (W)

13.36

14.29

8.28

/MCLK NVVDD

(MHz)

2.93

TBD

3.10

TBD

2.91

TBD

(V) (A) (W ) (A) (W)

TBD

11.89

TBD

11.53

TBD

6.60

10.70

11.53

5.61

FBVDD

0.66

0.70

0.62

FBVDDQ PCI Express I/O and

(GPU+Mem)

(1.5V)(1.5V)

(A) (W) (W)(mA) (W) (W) (W)(mA) (mA) (mA)

0.99

2.16

1.05

2.28 3. 42

0.93

2.20

The ramp ti me for a ny rail mu st be more than 40us

VDD33

PEX_ VDD can ramp u p any time

PEX_VDD

tNVVDD

NVVDD

tNV- IFPAB_IOV DD

(1.05V)

3.24

792 75 0.14

0.83

0.86817

3.3

782

0.82

PLLVDD

75 0.14

75 0.14

I/O and

PLLVDD

63 0.07

63 0.07

63 0.07

Other

(3.3V)(1.05V)(1.8V)

100 0.33

100 0.33

100 0.33

(1.8VS)IFPAB_IOVDD

tNV-F BVDDQ

(1.5VS)

FBVDDQ

4 4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009/03/16 2010/03/15

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

B

D

Date: Sheet of

Compal Electronics, Inc.

VGA Notes List

LA-5752P

4 51Thurs day, October 29, 2009

E

0.3

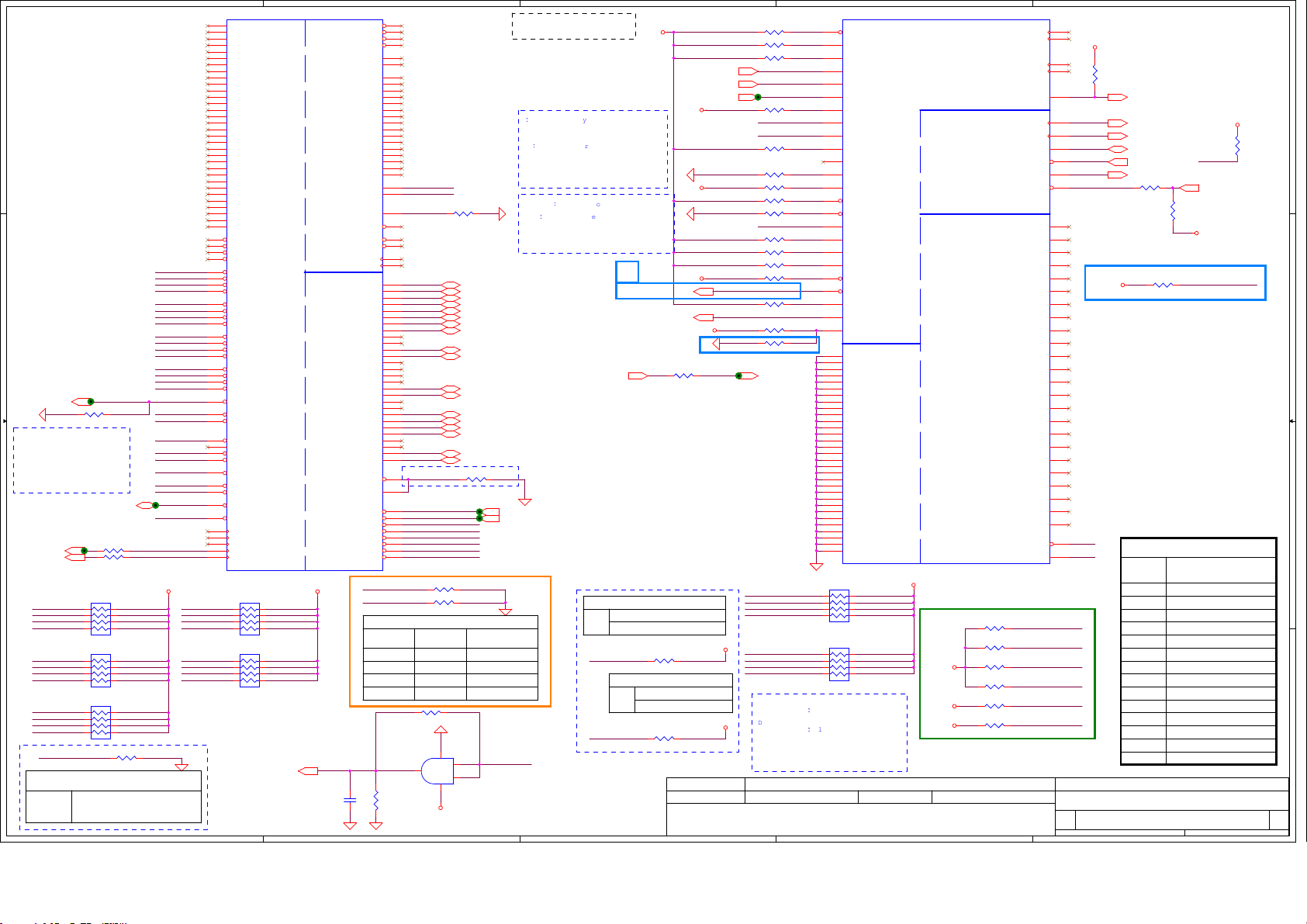

Page 5

5

4

3

2

1

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

DDR3 C ompensation Signals

SM_ RCOMP0

SM_ RCOMP1

SM_ RCOMP2

D D

C C

VCC P_POK<46>

FROM P OWER VTT

POWER GOOD S IGNAL

B B

R1 84

1K_ 0402_1%

12

Layout rule 10m il wid th :trace

length < 0.5 ", spa cing 20mil

+V CCP

H_ PROCH OT#<34, 48>

H_T HERM TRIP#<16>

+V CCP

H_ PM_S YNC<15>

H_ CPU PW RGD< 16>

PM_ DRAM _PWR GD<15>

R1 83

560_ 0402_5%

1 2

BUF _PLT_RS T#<16, 19,28, 29>

1 2

R5 5820_040 2_1%

1 2

R5 4849.9_ 0402_1%

1 2

R5 5749.9_ 0402_1%

1 2

TP_ SKTOCC#

12

R1 6349. 9_04 02_1%

R5 64 0_04 02_5%

H_ PECI<16>

+V CCP

1.5K _0402_5 %

H_P ECI_I SO

1 2

R5 69 68_0 402_5%

12

H_ PROC HOT#

H_T HERM TRIP#

H_ CPUR ST#_ R

12

R1 3568_0 402_5%

H_ PM_ SYNC _R

R1 87

1 2

0_04 02_5%

VC CPW RGOO D_1

R1 90

1 2

0_04 02_5%

VC CPW RGOO D_0

R1 39

1 2

0_04 02_5%

VD DPW RGO OD_R

R1 91

1 2

0_04 02_5%

R1 85

PLT _RST#_R

1 2

12

COM P2

COM P1

COM P0

H_ CATE RR#

VTT_POK

R1 86

750_ 0402_1%

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC ,AUB _CFD_ rPGA ,R1P 0

ME@

CL K_CP U_BC LK

MISC THERMAL

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

DDR3

MISC

PWR MANAGEMENT

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

TCK

AP28

TMS

AT27

AT29

TDI

AR27

TDO

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

CLK _CPU_ BCLK #

CLK _CPU_ ITP

CLK _CPU_ ITP#

CLK_EX P

CLK_ EXP#

SM_ DRAMR ST#

SM_ RCOMP0

SM_ RCOMP1

SM_ RCOMP2

PM_EXTTS#0

PM_EXTTS#1

XDP _PRD Y#

XDP _PREQ#

XDP _TCK

XDP_TMS

XDP_TR ST#

XDP _TDI

XDP _TDO

R5 55 0_04 02_5%

XDP _DBRES ET#

XDP_B PM#0

XDP_B PM#1

XDP_B PM#2

XDP_B PM#3

XDP_B PM#4

XDP_B PM#5

XDP_B PM#6

XDP_B PM#7

T17 PA D

T18 PA D

3

1 2

R5 63 0_04 02_5%

T19 PA D

12

CL K_CPU _BCL K <16>

CLK _CPU_ BCLK # <16>

CLK_EX P <14>

pins u nused by

Clarks field on the

rPGA98 9 Pack age

CLK_E XP# <14>

PM_EX TTS#1_R <1 0,11>

PM_EXTTS#0

PM_EXTTS#1

XDP _PREQ#

XDP_TMS

XDP _TDI

XDP _TDO

XDP _TCK

XDP_TR ST#

XDP _DBRES ET#

CHECK INTEL DOCUMENT #385422

Debug Port Design Guide Rev1.3

JC PU1B

COM P3

R5 6020_040 2_1%

1 2

R5 67 100_ 0402_1%

1 2

R5 66 24.9 _0402_1 %

1 2

R5 65 130_ 0402_1%

Layout Note:Please these

resist ors near Processor

1 2

R5 61 10K _0402_5%

1 2

R5 62 10K _0402_5%

R1 36 51_0 402_1%@

1 2

R1 38 51_0 402_1%@

1 2

R5 56 51_0 402_1%@

1 2

R1 34 51_0 402_5%

1 2

R5 7 51_0 402_1%@

1 2

R1 33 51_0 402_5%

1 2

R1 37

1K_ 0402_5%@

1 2

+V CCP

+3VS

+1.5V

For In tel S3 Power Reduc tion.

5

+3V ALW

5

U8

2

P

B

DR AM_ PWRG D

VCC P_POK<46>

A A

VCC P_PO K

2N70 02_SOT2 3

5

4

Y

1

A

G

MC7 4VHC1 G08D FT2G SC70 5P

3

+5V ALW

12

R6 10

10K _0402_5%

S3_ 0.75V _EN

13

D

2

G

Q42

S

4

R1 95

1 2

1.5K _0402 _1%

750_ 0402_1%

S3_ 0.75V _EN <44>

R1 94

12

+1.5 V

12

R1 93

1.1K _0402_1 %

@

VD DPW RGO OD_R

12

R1 92

3K_ 0402_1%

@

R3 01

DDR3 CONN ECT ER

DRA MRST#<10, 11>

PCH GPIO CON TROL

DRA MRST _CNTR L_PC H<16>

DRA MRST _CNTR L_EC<34>

EC GPIO C ONT ROL

1K_ 0402_1%

1 2

1 2

R2 81 0_04 02_5%

1 2

R2 82 0_04 02_5%@

1 2

DRA MRST# SM_ DRAMR ST#

2N70 02_SOT 23

DRA MRST _CNTR L_R

C3 38

6

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/10/31 2009/10/31

Compal Secret Data

Deciphered Date

For In tel S3 Power Reduc tion.

@

R3 000 _0402_ 5%

D

S

1 3

Q27

G

2

1

0.01 U_040 2_16V7K

2

2

12

R2 83 100K _0402_5 %

Size D ocum ent N umber Re v

Cu stom

Da te: She et o f

3

Title

Compal Electronics, Inc.

Arrandale(1/5)-Thermal/XDP

LA-5752P

1

5 5 1Thur sday , Oc tobe r 29, 2009

0. 3

Page 6

5

JC PU1A

DMI _CRX_PTX _N0<15>

DMI _CRX_PTX _N1<15>

DMI _CRX_PTX _N2<15>

DMI _CRX_PTX _N3<15>

DMI_C RX_PTX_P 0<15>

DMI_C RX_PTX_P 1<15>

D D

DMI_C RX_PTX_P 2<15>

DMI_C RX_PTX_P 3<15>

DMI _CTX_PRX _N0<15>

DMI _CTX_PRX _N1<15>

DMI _CTX_PRX _N2<15>

DMI _CTX_PRX _N3<15>

DMI_C TX_PRX_P 0<15>

DMI_C TX_PRX_P 1<15>

DMI_C TX_PRX_P 2<15>

DMI_C TX_PRX_P 3<15>

FDI _CTX_ PRX_N0<15>

FDI _CTX_ PRX_N1<15>

FDI _CTX_ PRX_N2<15>

FDI _CTX_ PRX_N3<15>

FDI _CTX_ PRX_N4<15>

FDI _CTX_ PRX_N5<15>

FDI _CTX_ PRX_N6<15>

FDI _CTX_ PRX_N7<15>

FDI _CTX_PRX _P0<15 >

FDI _CTX_PRX _P1<15 >

FDI _CTX_PRX _P2<15 >

FDI _CTX_PRX _P3<15 >

FDI _CTX_PRX _P4<15 >

FDI _CTX_PRX _P5<15 >

C C

FDI _CTX_PRX _P6<15 >

FDI _CTX_PRX _P7<15 >

FD I_F SYN C0<15>

FD I_F SYN C1<15>

FD I_I NT< 15>

FD I_L SYN C0<15>

FD I_L SYN C1<15>

FDI _CTX_ PRX_N0

FDI _CTX_ PRX_N1

FDI _CTX_ PRX_N2

FDI _CTX_ PRX_N3

FDI _CTX_ PRX_N4

FDI _CTX_ PRX_N5

FDI _CTX_ PRX_N6

FDI _CTX_ PRX_N7

FDI _CTX_PR X_P0

FDI _CTX_PR X_P1

FDI _CTX_PR X_P2

FDI _CTX_PR X_P3

FDI _CTX_PR X_P4

FDI _CTX_PR X_P5

FDI _CTX_PR X_P6

FDI _CTX_PR X_P7

FD I_F SYN C0

FD I_F SYN C1

FD I_I NT

FD I_L SY NC0

FD I_L SY NC1

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

PEG_RCOMPO

DMI Intel(R) FDI

PCI EXPRESS -- GRAPHICS

B B

FD I_F SYN C0

FD I_F SYN C1

FD I_I NT

FD I_L SY NC0

FD I_L SY NC1

A A

IC ,AUB _CFD_ rPGA ,R1P 0

ME@

R5 32 1K_ 0402_5%DI S@

1 2

R5 36 1K_ 0402_5%DI S@

1 2

R5 34 1K_ 0402_5%DI S@

1 2

R5 33 1K_ 0402_5%DI S@

1 2

R5 35 1K_ 0402_5%DI S@

1 2

PEG_ICOMPI

PEG_ICOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

4

EXP _ICOMPI

1 2

EXP _RBIAS

1 2

PCI E_CRX _GTX_N15

PCI E_CRX _GTX_N14

PCI E_CRX _GTX_N13

PCI E_CRX _GTX_N12

PCI E_CRX _GTX_N11

PCI E_CRX _GTX_N10

PCI E_CRX _GTX_N9

PCI E_CRX _GTX_N8

PCI E_CRX _GTX_N7

PCI E_CRX _GTX_N6

PCI E_CRX _GTX_N5

PCI E_CRX _GTX_N4

PCI E_CRX _GTX_N3

PCI E_CRX _GTX_N2

PCI E_CRX _GTX_N1

PCI E_CRX _GTX_N0

PCI E_CRX_GT X_P15

PCI E_CRX_GT X_P14

PCI E_CRX_GT X_P13

PCI E_CRX_GT X_P12

PCI E_CRX_GT X_P11

PCI E_CRX_GT X_P10

PCI E_CRX_GTX _P9

PCI E_CRX_GTX _P8

PCI E_CRX_GTX _P7

PCI E_CRX_GTX _P6

PCI E_CRX_GTX _P5

PCI E_CRX_GTX _P4

PCI E_CRX_GTX _P3

PCI E_CRX_GTX _P2

PCI E_CRX_GTX _P1

PCI E_CRX_GTX _P0

PCI E_CT X_GRX_C _N15

PCI E_CT X_GRX_C _N14

PCI E_CT X_GRX_C _N13

PCI E_CT X_GRX_C _N12

PCI E_CT X_GRX_C _N11

PCI E_CT X_GRX_C _N10

PCI E_CT X_GRX_C _N9

PCI E_CT X_GRX_C _N8

PCI E_CT X_GRX_C _N7

PCI E_CT X_GRX_C _N6

PCI E_CT X_GRX_C _N5

PCI E_CT X_GRX_C _N4

PCI E_CT X_GRX_C _N3

PCI E_CT X_GRX_C _N2

PCI E_CT X_GRX_C _N1

PCI E_CT X_GRX_C _N0

PCI E_CTX _GRX_C_P1 5

PCI E_CTX _GRX_C_P1 4

PCI E_CTX _GRX_C_P1 3

PCI E_CTX _GRX_C_P1 2

PCI E_CTX _GRX_C_P1 1

PCI E_CTX _GRX_C_P1 0

PCI E_CTX _GRX_C_P9

PCI E_CTX _GRX_C_P8

PCI E_CTX _GRX_C_P7

PCI E_CTX _GRX_C_P6

PCI E_CTX _GRX_C_P5

PCI E_CTX _GRX_C_P4

PCI E_CTX _GRX_C_P3

PCI E_CTX _GRX_C_P2

PCI E_CTX _GRX_C_P1

PCI E_CTX _GRX_C_P0

Layout rule tr:ace

length < 0.5"

R5 44 49.9 _0402_1 %

R5 45 750_ 0402_1%

PCI E_CRX _GTX _N[0..15] <19>

PCI E_CRX _GTX_P [0..15] <19>

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

PCIE Lane Numbers Reversed

CFG3-PCI Express Static Lane Reversal

VGA@

C5 27 0.1U _0402 _10V6K

1 2

C5 40 0.1U _0402 _10V6K

1 2

C5 29 0.1U _0402 _10V6K

1 2

C5 42 0.1U _0402 _10V6K

1 2

C5 31 0.1U _0402 _10V6K

1 2

C5 44 0.1U _0402 _10V6K

1 2

C5 33 0.1U _0402 _10V6K

1 2

C5 46 0.1U _0402 _10V6K

1 2

C5 35 0.1U _0402 _10V6K

1 2

C5 62 0.1U _0402 _10V6K

1 2

C5 64 0.1U _0402 _10V6K

1 2

C5 55 0.1U _0402 _10V6K

1 2

C5 57 0.1U _0402 _10V6K

1 2

C5 61 0.1U _0402 _10V6K

1 2

C5 48 0.1U _0402 _10V6K

1 2

C5 59 0.1U _0402 _10V6K

1 2

C5 28 0.1U _0402 _10V6K

1 2

C5 41 0.1U _0402 _10V6K

1 2

C5 30 0.1U _0402 _10V6K

1 2

C5 43 0.1U _0402 _10V6K

1 2

C5 32 0.1U _0402 _10V6K

1 2

C5 45 0.1U _0402 _10V6K

1 2

C5 34 0.1U _0402 _10V6K

1 2

C5 47 0.1U _0402 _10V6K

1 2

C5 36 0.1U _0402 _10V6K

1 2

C5 63 0.1U _0402 _10V6K

1 2

C5 65 0.1U _0402 _10V6K

1 2

C5 56 0.1U _0402 _10V6K

1 2

C5 58 0.1U _0402 _10V6K

1 2

C5 60 0.1U _0402 _10V6K

1 2

C5 49 0.1U _0402 _10V6K

1 2

C5 50 0.1U _0402 _10V6K

1 2

PCI E_CTX _GRX_N15

PCI E_CTX _GRX_N14

PCI E_CTX _GRX_N13

PCI E_CTX _GRX_N12

PCI E_CTX _GRX_N11

PCI E_CTX _GRX_N10

PCI E_CTX _GRX_N9

PCI E_CTX _GRX_N8

PCI E_CTX _GRX_N7

PCI E_CTX _GRX_N6

PCI E_CTX _GRX_N5

PCI E_CTX _GRX_N4

PCI E_CTX _GRX_N3

PCI E_CTX _GRX_N2

PCI E_CTX _GRX_N1

PCI E_CTX _GRX_N0

PCI E_CTX_G RX_P15

PCI E_CTX_G RX_P14

PCI E_CTX_G RX_P13

PCI E_CTX_G RX_P12

PCI E_CTX_G RX_P11

PCI E_CTX_G RX_P10

PCI E_CTX_GRX _P9

PCI E_CTX_GRX _P8

PCI E_CTX_GRX _P7

PCI E_CTX_GRX _P6

PCI E_CTX_GRX _P5

PCI E_CTX_GRX _P4

PCI E_CTX_GRX _P3

PCI E_CTX_GRX _P2

PCI E_CTX_GRX _P1

PCI E_CTX_GRX _P0

PCI E_CT X_GRX _N[0..15] <19>

PCI E_CT X_GRX_P [0..15] <19>

3

R5 9

@

1 2

3.01 K_040 2_1%

FOR ES1 S AMP LE ONLY

R5 47

0_04 02_5%

@

1 2

@

1 2

R5 46

0_04 02_5%

CFG Straps for PROCESSOR

CF G0

PCI-Ex press Configuration Select

CFG0

Not ap plica ble f or Clarksfield Processor

CFG[1:0] 11 =1*16 PEG

CF G3

CFG3-P CI Ex press Static Lane Reversal

CF G4

CFG4-D isplay Port Presence

CFG4

@

1 2

R5 8 3. 01K_0 402_1%

1: Single PEG

0: Bif urcation enabled

10=2*8 PEG

1 2

R6 1 3. 01K_0 402_1%

1: Nor mal Operation

0: Lan e Numbers Reversed

CFG3

15 -> 0, 14 ->1, .....

@

1 2

R6 0 3. 01K_0 402_1%

1: Dis abled ; No Physical Display Port

attach ed to Embedded Display Port

0: Ena bled; An external Display Port

device is c onnected to the Embedded

Display Port

CF G0

CF G3

CF G4

CF G7

H_ RSV D17_R

H_ RSV D18_R

2

JC PU1E

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

SA_DIMM_VREF

H17

SB_DIMM_VREF

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

IC ,AUB _CFD_ rPGA ,R1P 0

ME@

RESERVED

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD_NCTF_37

RSVD38

RSVD39

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD58

RSVD_TP_59

RSVD_TP_60

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

1

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

KEY

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS

RS VD6 4_R

RS VD6 5_R

R1 89

0_04 02_5%

R1 88

0_04 02_5%

@

12

@

12

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/10/31 2009/10/31

Compal Secret Data

Deciphered Date

2

Title

Size D ocum ent N umber Re v

Cu stom

Da te: She et o f

Compal Electronics, Inc.

Arrandale(2/5)-DMI/PEG/FDI

LA-5752P

1

6 5 1Thur sday , Oc tobe r 29, 2009

0. 3

Page 7

5

4

3

2

1

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

AR10

AT10

JC PU1 D

W8

SB_CK[0]

W9

SB_CK#[0]

B5

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

DDR SYSTEM MEMORY - B

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

DD R_B_ DM0

DD R_B_ DM1

DD R_B_ DM2

DD R_B_ DM3

DD R_B_ DM4

DD R_B_ DM5

DD R_B_ DM6

DD R_B_ DM7

DD R_B_ DQS# 0

DD R_B_ DQS# 1

DD R_B_ DQS# 2

DD R_B_ DQS# 3

DD R_B_ DQS# 4

DD R_B_ DQS# 5

DD R_B_ DQS# 6

DD R_B_ DQS# 7

DD R_B _DQS 0

DD R_B _DQS 1

DD R_B _DQS 2

DD R_B _DQS 3

DD R_B _DQS 4

DD R_B _DQS 5

DD R_B _DQS 6

DD R_B _DQS 7

DDR_ B_M A0

DDR_ B_M A1

DDR_ B_M A2

DDR_ B_M A3

DDR_ B_M A4

DDR_ B_M A5

DDR_ B_M A6

DDR_ B_M A7

DDR_ B_M A8

DDR_ B_M A9

DDR_ B_MA 10

DDR_ B_MA 11

DDR_ B_MA 12

DDR_ B_MA 13

DDR_ B_MA 14

DDR_ B_MA 15

M_ CLK_D DR2 < 11>

M_ CLK_D DR#2 <11>

DDR_ CKE2 _DIM MB <11>

M_ CLK_D DR3 < 11>

M_ CLK_D DR#3 <11>

DDR_ CKE3 _DIM MB <11>

DDR_ CS2_ DIMM B# <11>

DDR_ CS3_ DIMM B# <11>

M_ODT 2 <11>

M_ODT 3 <11>

DD R_B_ DM[0 ..7] < 11>

DD R_B_ DQS# [0..7 ] <11>

DD R_B _DQS [0..7 ] <11>

DDR_ B_MA [0.. 15] <1 1>

JC PU1 C

D D

DD R_A _D[0 ..63]<10>

C C

B B

DD R_A_B S0<10>

DD R_A_B S1<10>

DD R_A_B S2<10>

DD R_A_ CAS#<10>

DD R_A_ RAS#<10>

DD R_A _WE#<10>

DD R_A _D0

DD R_A _D1

DD R_A _D2

DD R_A _D3

DD R_A _D4

DD R_A _D5

DD R_A _D6

DD R_A _D7

DD R_A _D8

DD R_A _D9

DD R_A _D10

DD R_A _D11

DD R_A _D12

DD R_A _D13

DD R_A _D14

DD R_A _D15

DD R_A _D16

DD R_A _D17

DD R_A _D18

DD R_A _D19

DD R_A _D20

DD R_A _D21

DD R_A _D22

DD R_A _D23

DD R_A _D24

DD R_A _D25

DD R_A _D26

DD R_A _D27

DD R_A _D28

DD R_A _D29

DD R_A _D30

DD R_A _D31

DD R_A _D32

DD R_A _D33

DD R_A _D34

DD R_A _D35

DD R_A _D36

DD R_A _D37

DD R_A _D38

DD R_A _D39

DD R_A _D40

DD R_A _D41

DD R_A _D42

DD R_A _D43

DD R_A _D44

DD R_A _D45

DD R_A _D46

DD R_A _D47

DD R_A _D48

DD R_A _D49

DD R_A _D50

DD R_A _D51

DD R_A _D52

DD R_A _D53

DD R_A _D54

DD R_A _D55

DD R_A _D56

DD R_A _D57

DD R_A _D58

DD R_A _D59

DD R_A _D60

DD R_A _D61

DD R_A _D62

DD R_A _D63

AJ10

AL10

AK12

AK11

AM10

AR11

AL11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

A10

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

DD R_A_ DM0

DD R_A_ DM1

DD R_A_ DM2

DD R_A_ DM3

DD R_A_ DM4

DD R_A_ DM5

DD R_A_ DM6

DD R_A_ DM7

DD R_A_ DQS# 0

DD R_A_ DQS# 1

DD R_A_ DQS# 2

DD R_A_ DQS# 3

DD R_A_ DQS# 4

DD R_A_ DQS# 5

DD R_A_ DQS# 6

DD R_A_ DQS# 7

DD R_A _DQS 0

DD R_A _DQS 1

DD R_A _DQS 2

DD R_A _DQS 3

DD R_A _DQS 4

DD R_A _DQS 5

DD R_A _DQS 6

DD R_A _DQS 7

DDR_ A_M A0

DDR_ A_M A1

DDR_ A_M A2

DDR_ A_M A3

DDR_ A_M A4

DDR_ A_M A5

DDR_ A_M A6

DDR_ A_M A7

DDR_ A_M A8

DDR_ A_M A9

DDR_ A_MA 10

DDR_ A_MA 11

DDR_ A_MA 12

DDR_ A_MA 13

DDR_ A_MA 14

DDR_ A_MA 15

M_ CLK_D DR0 <1 0>

M_C LK_DD R#0 < 10>

DDR_ CKE0 _DIMM A <10>

M_ CLK_D DR1 <1 0>

M_C LK_DD R#1 < 10>

DDR_ CKE1 _DIMM A <10>

DDR_ CS0_ DIMM A# <10>

DDR_ CS1_ DIMM A# <10>

M_ODT 0 <10>

M_ODT 1 <10>

DD R_A_ DM[0 ..7] < 10>

DD R_A_ DQS# [0..7 ] <10>

DD R_A_ DQS[ 0..7] <10>

DDR_ A_MA [0.. 15] <10 >

DD R_B _D[0 ..63]<11>

DD R_B_B S0<11>

DD R_B_B S1<11>

DD R_B_B S2<11>

DD R_B_ CAS#<11>

DD R_B_ RAS#<11>

DD R_B_ WE#<11>

DD R_B _D0

DD R_B _D1

DD R_B _D2

DD R_B _D3

DD R_B _D4

DD R_B _D5

DD R_B _D6

DD R_B _D7

DD R_B _D8

DD R_B _D9

DD R_B _D10

DD R_B _D11

DD R_B _D12

DD R_B _D13

DD R_B _D14

DD R_B _D15

DD R_B _D16

DD R_B _D17

DD R_B _D18

DD R_B _D19

DD R_B _D20

DD R_B _D21

DD R_B _D22

DD R_B _D23

DD R_B _D24

DD R_B _D25

DD R_B _D26

DD R_B _D27

DD R_B _D28

DD R_B _D29

DD R_B _D30

DD R_B _D31

DD R_B _D32

DD R_B _D33

DD R_B _D34

DD R_B _D35

DD R_B _D36

DD R_B _D37

DD R_B _D38

DD R_B _D39

DD R_B _D40

DD R_B _D41

DD R_B _D42

DD R_B _D43

DD R_B _D44

DD R_B _D45

DD R_B _D46

DD R_B _D47

DD R_B _D48

DD R_B _D49

DD R_B _D50

DD R_B _D51

DD R_B _D52

DD R_B _D53

DD R_B _D54

DD R_B _D55

DD R_B _D56

DD R_B _D57

DD R_B _D58

DD R_B _D59

DD R_B _D60

DD R_B _D61

DD R_B _D62

DD R_B _D63

IC ,AUB _CFD_ rPGA ,R1P 0

ME@

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

IC ,AUB _CFD_ rPGA ,R1P 0

ME@

2008/10/31 2009/10/31

Compal Secret Data

Deciphered Date

Title

Size D ocum ent N umber R ev

Cu sto m

2

Da te: She et o f

Compal Electronics, Inc.

Arrandale(3/5)-DDR III

LA-5752P

1

7 5 1Thur sday , Oc tobe r 29, 2009

0. 3

Page 8

5

+C PU_C ORE

JC PU1 F

D D

C C

B B

A A

48A 15A18A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

IC ,AUB _CFD_ rPGA ,R1P 0

ME@

CPU CO RE SUP PLY

5

POWER

1.1V R AIL PO WER

CPU VI DS

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

PSI#

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

PROC_DPRSLPVR

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

AH14

10U_ 0805_10 V4K

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

VTT_S ELECT

H_ VID 0

H_ VID 1

H_ VID 2

H_ VID 3

H_ VID 4

H_ VID 5

H_ VID 6

PM_ DPRS LPVR _R

10U_ 0805_10 V4K

C2 01

1

1

2

2

10U_ 0805_10 V4K

10U_ 0805_10 V4K

C2 71

1

1

@

2

2

10U_ 0805_10 V4K

C2 08

1

1

2

2

R6 08 1K_ 0402_5%

1 2

R5 6 0_ 0402_5%

C1 99

1

2

C2 70

1

@

2

+V CCP

10U_ 0805_10 V4K

C2 09

1 2

PSI # <48>

H_ VID [0..6 ] <48>

H_VTTVID1 = Low, 1.1V FOR Clarksfiel

H_VTTVID1 = High, 1.05V FOR Auburndale

AN35

AJ34

AJ35

B15

A15

VCC _SEN SE

VSS _SENS E

IMV P_IMON <48>

0_04 02_5%

R5 54

1 2

1 2

R5 53 0_04 02_5%

VTT_S ENSE <4 6>

@

T15PA D

Clo se to CP U

VCC SENS E

VSS SENSE

1 2

R5 52 10 0_0402_ 1%

1 2

R5 51 10 0_0402_ 1%

10U_ 0805_10 V4K

C1 98

10U_ 0805_10 V4K

C2 16

10U_ 0805_10 V4K

1

2

10U_ 0805_10 V4K

1

2

1

2

VCC SENS E

VSS SENSE

4

C1 81

1

+

2

C1 82

1

2

10U_ 0805_ 10V4K

C2 19

+C PU_C ORE

4

+V CCP

330U _D2_2 .5VY _R9M

C5 54

10U_ 0805_10 V4K

C2 00

10U_ 0805_ 10V4K

10U_ 0805_ 10V4K

C2 74

C2 17

1

1

2

2

PR OC_DP RSLP VR <48 >

VTT_S ELECT <46 >

VC CSEN SE <48>

VSS SENSE <48>

+V CCP

3

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

+GF X_CORE

22U_ 0805_ 6.3V6M

1

C1 60

C1 61

@

2

22U_ 0805_6. 3V6M

12

R5 59

0_04 02_5%

DI S@

10U_ 0805_ 10V4K

C2 07

1

2

CPU

1

C1 91

@

2

22U_ 0805_6. 3V6M

1

SUS P<39, 44,45>

22U_ 0805_6. 3V6M

1

C1 90

@

2

22U_ 0805_ 6.3V6M

1

1

C1 89

@

UMA @

2

2

22U_ 0805_6. 3V6M

+V CCP

1

2

+1.5 V + 1.5V_ DDR3

+5V ALW

R2 68

20K _0402_5%

1.5V _DDR 3_GAT E

13

D

2

G

S

3

1

1

C5 91

C1 59

UMA @

UMA @

2

2

10U_ 0805_ 6.3V6M

10U_ 0805_10 V4K

10U_ 0805_10 V4K

C2 15

C2 14

1

2

J3

2

JUM P_43X118

@

J2

2

JUM P_43X118

@

U1 1

8

D

7

D

6

D

5

D

SI4 800BD Y-T1-E 3_SO8

Q23

2N70 02_SOT2 3

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

10U_ 0805_ 6.3V6M

1

C5 92

UMA @

2

+V CCP

10U_ 0805_ 10V4K

C2 10

1

2

10U_ 0805_10 V4K

C2 72

1

2

112

112

1

S

2

S

3

S

4

G

R2 67

0_04 02_5%

@

1 2

1

2

1

2

JC PU1G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

10U_ 0805_ 10V4K

C2 11

10U_ 0805_10 V4K

C2 40

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

IC, AUB_C FD_r PGA, R1P0

ME@

GRAPHI CS

FDI PEG & DMI

For In tel S3 Power Reduc tion.

0.1U _0402 _10V6K

0.1U _0402 _10V6K

C2 89

1

1

2

+1 .5V_D DR3

1

C3 25

0.1U _0603 _25V7K

2

2008/10/31 2009/10/31

2

Compal Secret Data

POWER

+1.5 V

0.1U _0402 _10V6K

C2 88

C2 87

1

2

Deciphered Date

2

SENSE

3A

0.6A

1

2

2

LINES

GRA PHI CS VIDs

0.1U _0402 _10V6K

VAXG_SENSE

VSSAXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

DDR3 - 1.5V RAILS

1.1V1.8V

VCCPLL1

VCCPLL2

VCCPLL3

C2 86

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

AN24

GFX _VR_E N

AR25

AT25

GFX _IMON

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

2

SUS P

UMA @

1 2

1U_0 603_1 0V4Z

1U_0 603_1 0V4Z

C2 54

1

1

2

2

22U_ 0805_6. 3V6M

220U _B2_ 2.5VM_R3 5

C2 68

1

1

+

@

2

2

1U_0 603_1 0V4Z

1U_0 603_1 0V4Z

C1 67

C1 49

1

2

1

1

2

2

+1 .5V_ DDR3

0.1U _0402 _10V6K

C2 69

1

@

2

2

G

For In tel S3 Power Reduc tion.

1

GFX _IMON

R1 32

DI S@

1K_ 0402_5%

12

AS NO CONNECT

BUT A SMALL AMOUNT OF POWER

VCC _AXG_S ENSE < 47>

VSS_A XG_SENS E <47>

GFX VR_V ID_0 <47>

GFX VR_V ID_1 <47>

GFX VR_V ID_2 <47>

GFX VR_V ID_3 <47>

GFX VR_V ID_4 <47>

GFX VR_V ID_5 <47>

GFX VR_V ID_6 <47>

R1 41 0_04 02_5%

1U_0 603_1 0V4Z

1U_0 603_1 0V4Z

C2 53

C2 56

1

1

2

2

22U_ 0805_6. 3V6M

Modify for cost revew.

C2 58

C2 52

1

09/16/2009

2

+V CCP

10U_ 0805_ 10V4K

10U_ 0805_ 10V4K

C2 73

1

1

2

2

10U_ 0805_ 10V4K

10U_ 0805_ 10V4K

C2 18

1

1

2

2

2.2U _0603 _6.3V 4Z

10U_ 0805_ 10V4K

C1 68

C1 69

1

2

12

R2 33

220_ 0402_5%

13

D

Q19

BSS 138_NL_ SOT23-3

S

Title

Size D ocum ent N umber Re v

Cu stom

Da te: She et o f

(~15MW ) MAYB E WASTED

DESIGN GU IDE RE V1.1

R1 40

1 2

UMA @

1

+1 .5V_D DR3

1U_0 603_1 0V4Z

C2 55

1

2

C2 12

+VC CP

C2 13

+1.8V S

4.7U _0603 _6.3V6K

C1 70

1

2

GFX _VR_E N

GFX VR_EN <47>

GFX VR_D PRSLPV R <47>

GFX VR_IMO N <47>

C2 57

Compal Electronics, Inc.

Arrandale(4/5)-PWR

LA-5752P

1

8 5 1Thur sday , Oc tobe r 29, 2009

4.7K _0402 _5%

0. 3

Page 9

5

JC PU1 H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

D D

C C

B B

AR17

AR15

AR12

AP20

AP17

AP13

AP10

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AG10

AE35

VSS8

VSS9

VSS10

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

VSS15

VSS16

VSS17

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

VSS80

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

4

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

JC PU1 I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

VSS

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

NCTF

AT1

AR34

B34

B2

B1

A35

VSS _NCT F2_R

VSS _NCT F3_R

VSS _NCT F4_R

VSS _NCT F5_R

VSS _NCT F6_R

VSS _NCT F7_R

VSS _NCT F1_R

AT35

3

+C PU_C ORE

2

1

CPU CORE

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C5 85

C5 68

1

1

2

2

10U_ 0805_ 6.3V6M

10U_ 0805_ 6.3V6M

C1 63

C1 47

1

1

2

2

10U_ 0805_6. 3V6M

10U_ 0805_6. 3V6M

C1 92

C1 95

1

1

2

2

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C5 80

1

2

10U_ 0805_ 6.3V6M

C1 62

1

2

10U_ 0805_6. 3V6M

C8 8

1

2

22U_ 0805_6. 3V6M

C5 79

1

2

1

2

1

2

C5 74

1

2

10U_ 0805_ 6.3V6M

10U_ 0805_ 6.3V6M

C1 93

C1 79

1

2

10U_ 0805_6. 3V6M

10U_ 0805_6. 3V6M

C1 96

C1 80

1

2

Under cavity

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C5 84

C5 73

1

1

2

2

10U_ 0805_ 6.3V6M

C1 66

1

1

2

2

10U_ 0805_6. 3V6M

C8 9

1

1

2

2

C5 78

1

2

10U_ 0805_ 6.3V6M

10U_ 0805_ 6.3V6M

C1 48

C1 65

1

2

10U_ 0805_6. 3V6M

C1 97

22U_ 0805_6. 3V6M

C5 83

1

2

1

2

1

2 3

C5 77

1

2

10U_ 0805_ 6.3V6M

C1 94

between Inductor and socket

470U _D2T_2VM

470U _D2T_2VM

C7 6

C7 5

1

+

+

2 3

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C5 71

C5 72

1

1

2

470U _D2T_2VM

1

+

2 3

2

C9 2

1

+

2 3

Inside cavity

470U _D2T_2VM

C1 64

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C9 1

1

1

2

2

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C9 0

C1 29

C8 7

1

1

2

2

470uF 4.5mohm

IC, AUB_C FD_r PGA, R1P0

ME@

A A

5

IC ,AUB _CFD_ rPGA ,R1P 0

ME@

4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/10/31 2009/10/31

Compal Secret Data

Deciphered Date

2

Title

Size D ocum ent N umber Re v

Cu stom

Da te: She et o f

Compal Electronics, Inc.

Arrandale(5/5)-GND/Bypass

LA-5752P

1

9 5 1Thur sday , Oc tobe r 29, 2009

0. 3

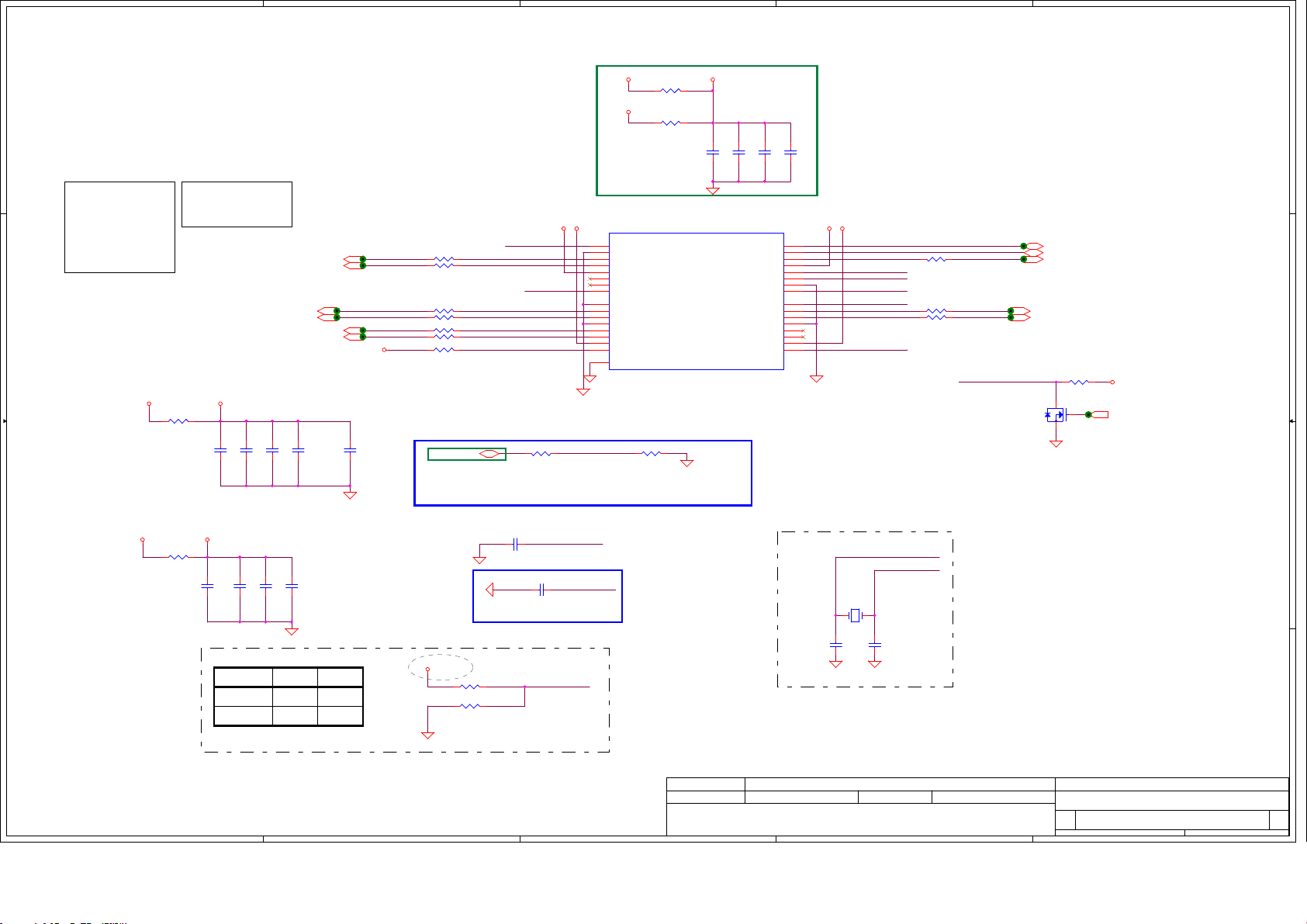

Page 10

5

+VR EF_D Q_DIMM A

+VR EF_D Q_DIMM A

2.2U _0603 _6.3V 4Z

0.1U _0402 _10V6K

C3 03

1

1

2

D D

C C

B B

A A

2

DDR_ CKE0 _DIMM A<7>

DDR_ A_BS 2<7>

M_ CLK_D DR0<7>

M_C LK_DD R#0< 7>

DDR_ A_BS 0<7>

DD R_A_ WE#<7>

DD R_A_ CAS#< 7>

DDR_ CS1_ DIMM A#<7>

+3VS

1

2

5

DD R_A _D0

C3 47

DD R_A _D1

DD R_A_ DM0

DD R_A _D2

DD R_A _D3

DD R_A _D8

DD R_A _D9

DD R_A_ DQS# 1

DD R_A _DQS 1

DD R_A _D10

DD R_A _D11

DD R_A _D16

DD R_A _D17

DD R_A_ DQS# 2

DD R_A _DQS 2

DD R_A _D18

DD R_A _D19

DD R_A _D24

DD R_A _D25

DD R_A_ DM3

DD R_A _D26

DD R_A _D27

DDR_ CKE0 _DIM MA

DD R_A_ BS2

DDR_ A_MA 12

DDR_ A_M A9

DDR_A_MA8

DDR_ A_M A5

DDR_ A_M A3

DDR_ A_M A1

M _CLK_ DDR0

M _CLK_ DDR#0

DDR_ A_MA 10

DD R_A_ BS0

DD R_A _WE#

DD R_A_ CAS# M_OD T0

DDR_ A_MA 13

DDR_ CS1_ DIMM A#

DD R_A _D32

DD R_A _D33

DD R_A_ DQS# 4

DD R_A _DQS 4

DD R_A _D34

DD R_A _D35

DD R_A _D40

DD R_A _D41

DD R_A_ DM5

DD R_A _D42

DD R_A _D43

DD R_A _D48

DD R_A _D49

DD R_A_ DQS# 6

DD R_A _DQS 6

DD R_A _D50

DD R_A _D51

DD R_A _D56

DD R_A _D57

DD R_A_ DM7

DD R_A _D58

DD R_A _D59

1 2

10K _0402_5%

2.2U _0603 _6.3V 4Z

0.1U _0402 _10V6K

C6 08

C6 17

1

2

+1.5 V + 1.5V

3A @

3A @ 1. 5 V

1. 5 V

3A @3A @

1. 5 V1. 5 V

DDR3 SO-DIMM A

JDI MM1

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

R5 70

10K _0402_5%

12

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

R5 71

VTT1

205

G1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

DQ14

DQ15

DQ20

DQ21

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

FOX _AS0 A626-U4S N-7F

ME@

G2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

4

DD R_A _D4

DD R_A _D5

DD R_A_ DQS# 0

DD R_A _DQS 0

DD R_A _D6

DD R_A _D7

DD R_A _D12

DD R_A _D13

DD R_A_ DM1

DRA MRST#

DD R_A _D14

DD R_A _D15

DD R_A _D20

DD R_A _D21

DD R_A_ DM2

DD R_A _D22

DD R_A _D23

DD R_A _D28

DD R_A _D29

DD R_A_ DQS# 3

DD R_A _DQS 3

DD R_A _D30

DD R_A _D31

DDR_ CKE1 _DIM MA

DDR_ A_MA 15

DDR_ A_MA 14

DDR_A_MA 11

DDR_ A_M A7

DDR_A_MA6

DDR_ A_M A4

DDR_ A_M A2

DDR_ A_M A0

M _CLK_ DDR1

M _CLK_ DDR#1

DD R_A_ BS1

DD R_A_ RAS#

DDR_ CS0_ DIMM A#

M_OD T1

DD R_A _D36

DD R_A _D37

DD R_A_ DM4

DD R_A _D38

DD R_A _D39

DD R_A _D44

DD R_A _D45

DD R_A_ DQS# 5

DD R_A _DQS 5

DD R_A _D46

DD R_A _D47

DD R_A _D52

DD R_A _D53

DD R_A_ DM6

DD R_A _D54

DD R_A _D55

DD R_A _D60

DD R_A _D61

DD R_A_ DQS# 7

DD R_A _DQS 7

DD R_A _D62

DD R_A _D63

PM_EX TTS#1_R

SMB _DATA_S3

SMB _CLK_S 3

+0.7 5VS

0.

0. 65 A @0 . 75 V

65 A @0 . 75 V

0.0.

65 A @0 . 75 V6 5A @ 0. 7 5V

4

DRA MRST# <5,11>

DDR_ CKE1 _DIMM A <7>

M_ CLK_D DR1 <7>

M_C LK_DD R#1 <7>

DDR_ A_BS 1 <7>

DD R_A_ RAS# <7>

DDR_ CS0_ DIMM A# <7>

M_ODT 0 <7>

M_ODT 1 <7>

0.1U _0402 _10V6K

C3 46

1

1

2

2

VDDQ(1 .5V) =

3*330u f / 12 m ohm (TOTAL FOR 2 SO-DIMMs)

6*0603 10uf (PER C ONNECTOR)

VTT(0. 75V) =

3*0805 10uf

VREF =

1*0402 0.1uf

VDDSPD (3.3V )=

1*0402 0.1uf 1*0402 2.2uf

PM_EX TTS#1_R <5 ,11>

SMB_D ATA_S3 <11,1 2,14,28 >

SMB _CLK_S3 <11, 12,14, 28>

《笔记本电脑故障检修100例》 《笔记本电脑电路分析与故障诊断》更多图纸请登录:qiumanliang.com网站免费下载

DD R_A _D[0 ..63]<7>

DD R_A_ DM[0 ..7]<7>

DD R_A _DQS [0..7 ]<7>

DD R_A_ DQS# [0..7 ]<7>

DDR_ A_MA [0.. 15]<7>

+VR EF_D Q_DIMM A

2.2U _0603 _6.3V 4Z

C3 55

4*0402 1uf

1*0402 2.2uf

3

Lay ou t N ote:

Pl ace near DIM M

+1.5 V

10U_ 0603_ 6.3V6M

10U_ 0603_ 6.3V6M

10U_ 0603_ 6.3V6M

C5 88

C5 89

1

1

@

@

2

2

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/10/31 2009/10/31

C5 81

C5 86

1

2

+0.7 5VS

C6 07

C6 05

1U_0 603_1 0V4Z

1

1

2

2

Compal Secret Data

1

2

1U_0 603_1 0V4Z

10U_ 0603_ 6.3V6M

10U_ 0603_ 6.3V6M

C3 10

1

2

C6 06

C3 00

1U_0 603_1 0V4Z

1

2

Deciphered Date

2

10U_ 0603_ 6.3V6M

C5 70

C3 09

1

1

2

2

C3 01