Page 1

5

4

3

2

1

2010.04.07 MV SChematic

D D

TABLE OF CONTENTS

MB

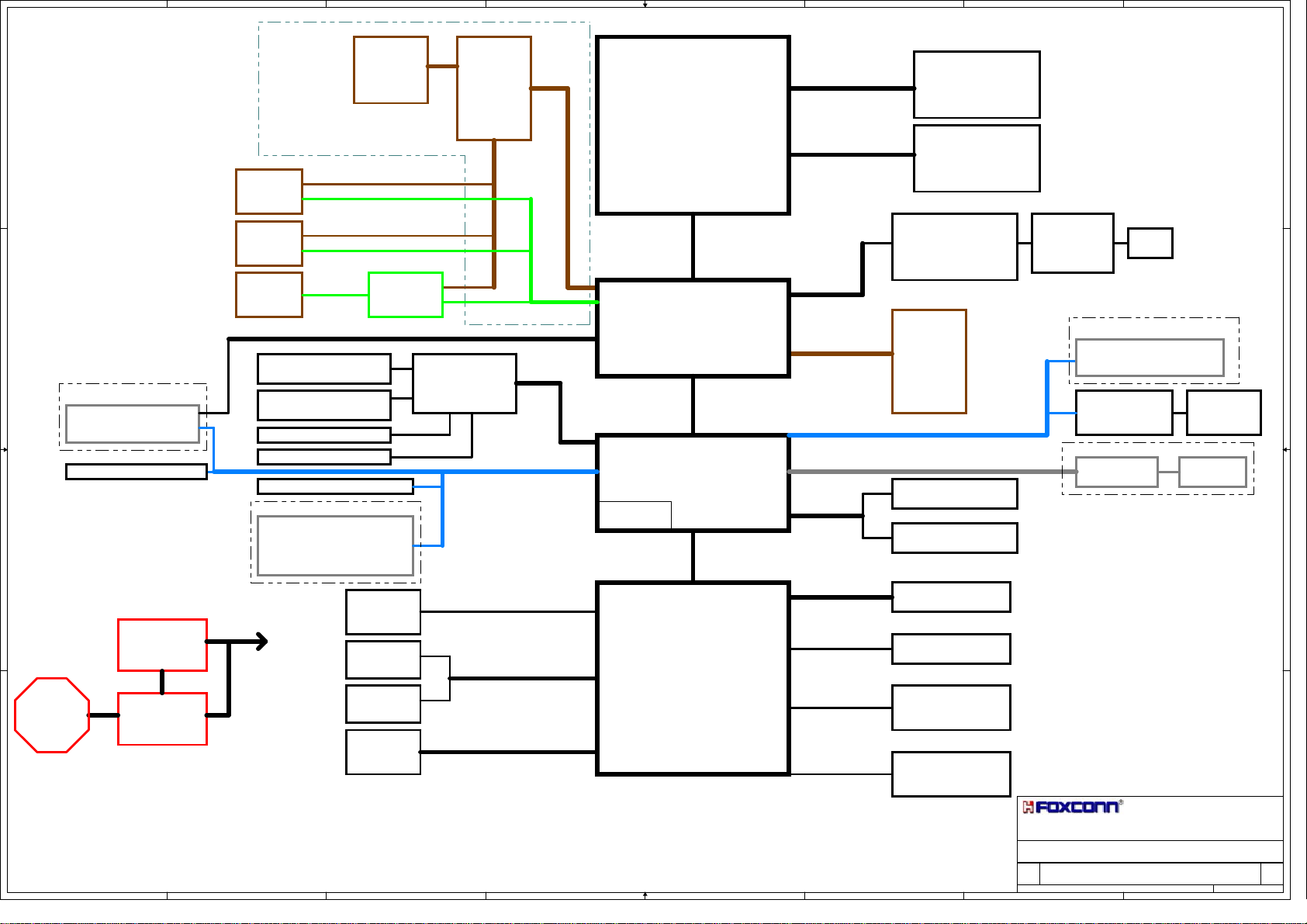

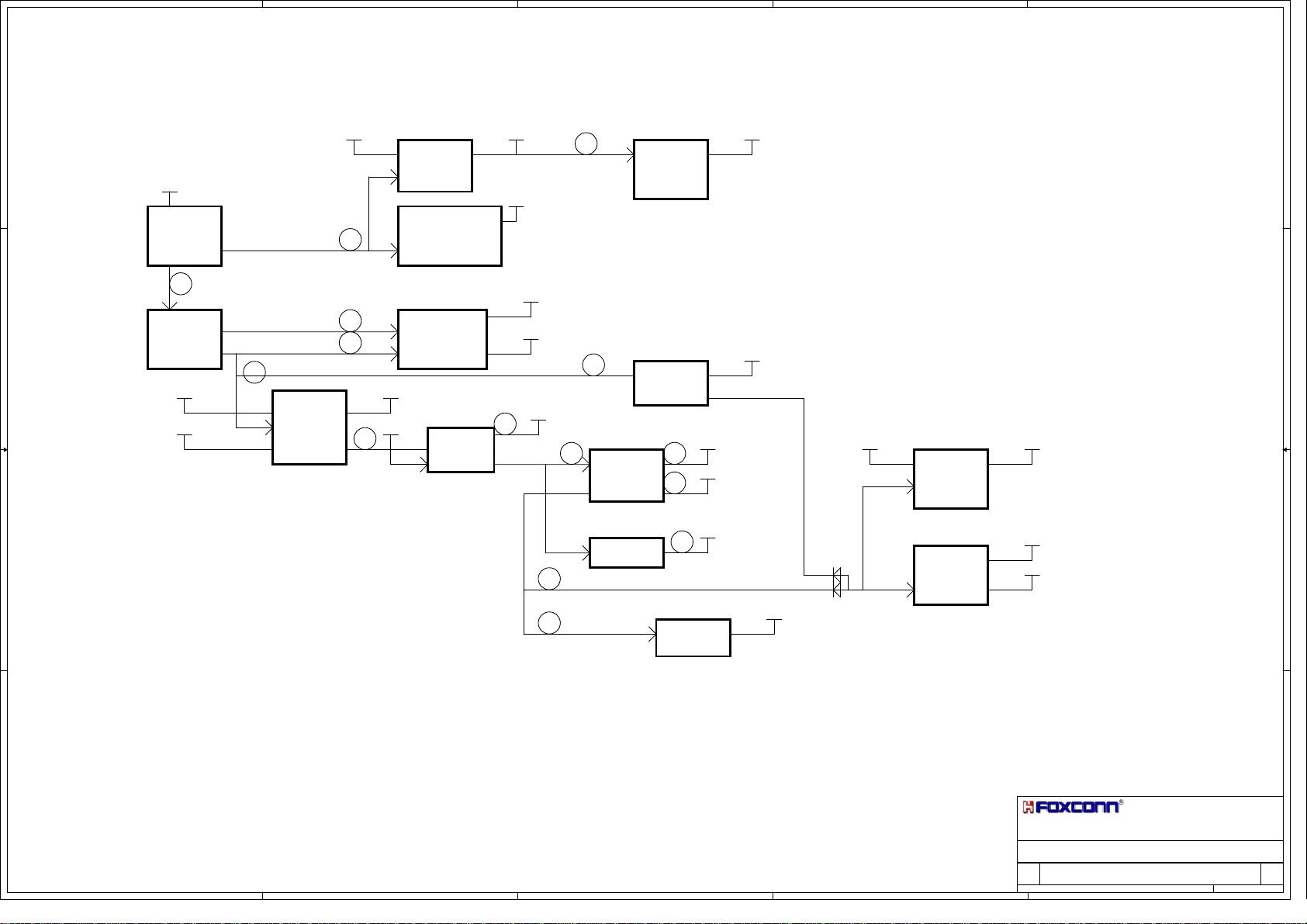

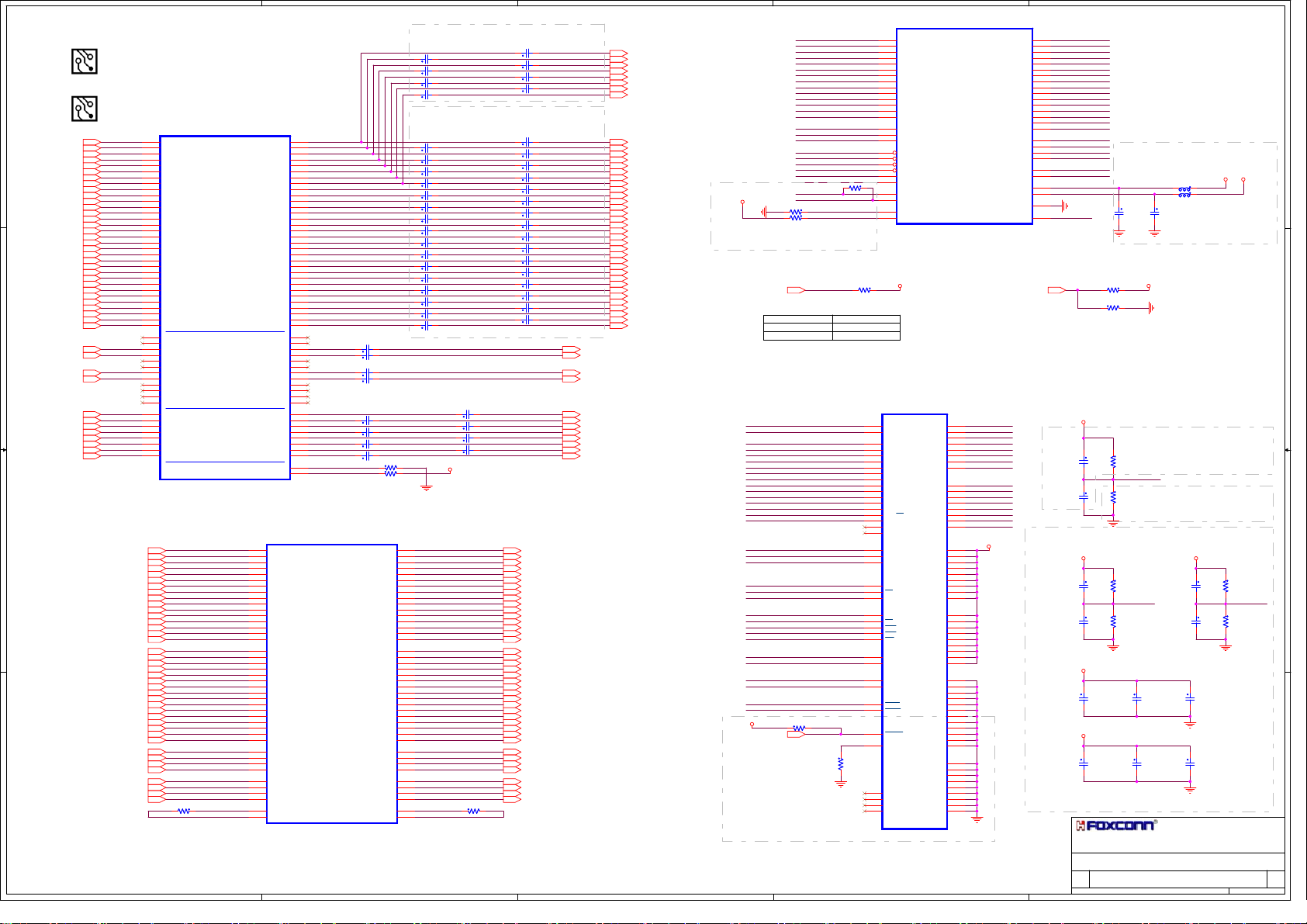

P02 : SYSTEM BLOCK DIAGRAM

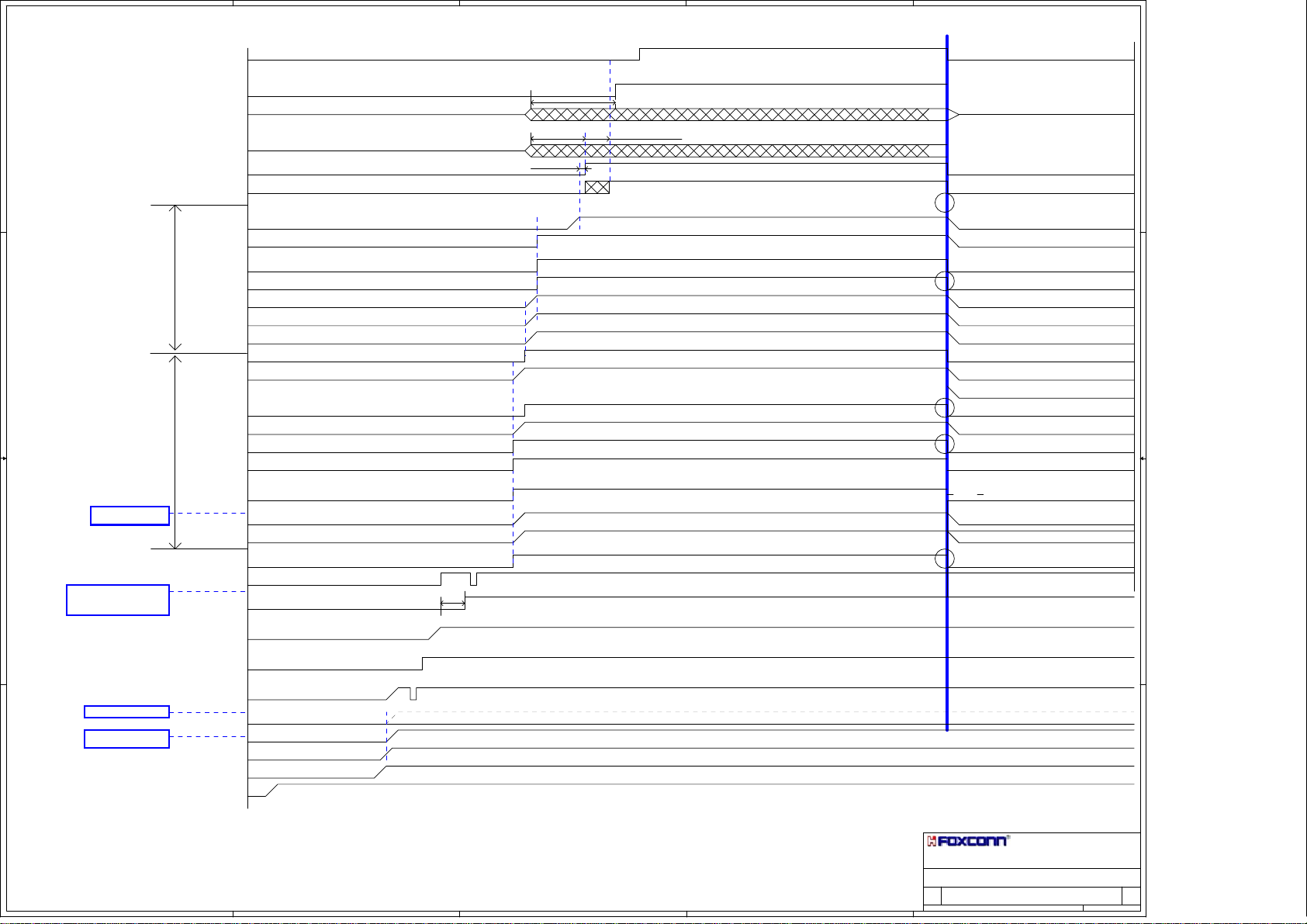

P03 : CLOCK MAP

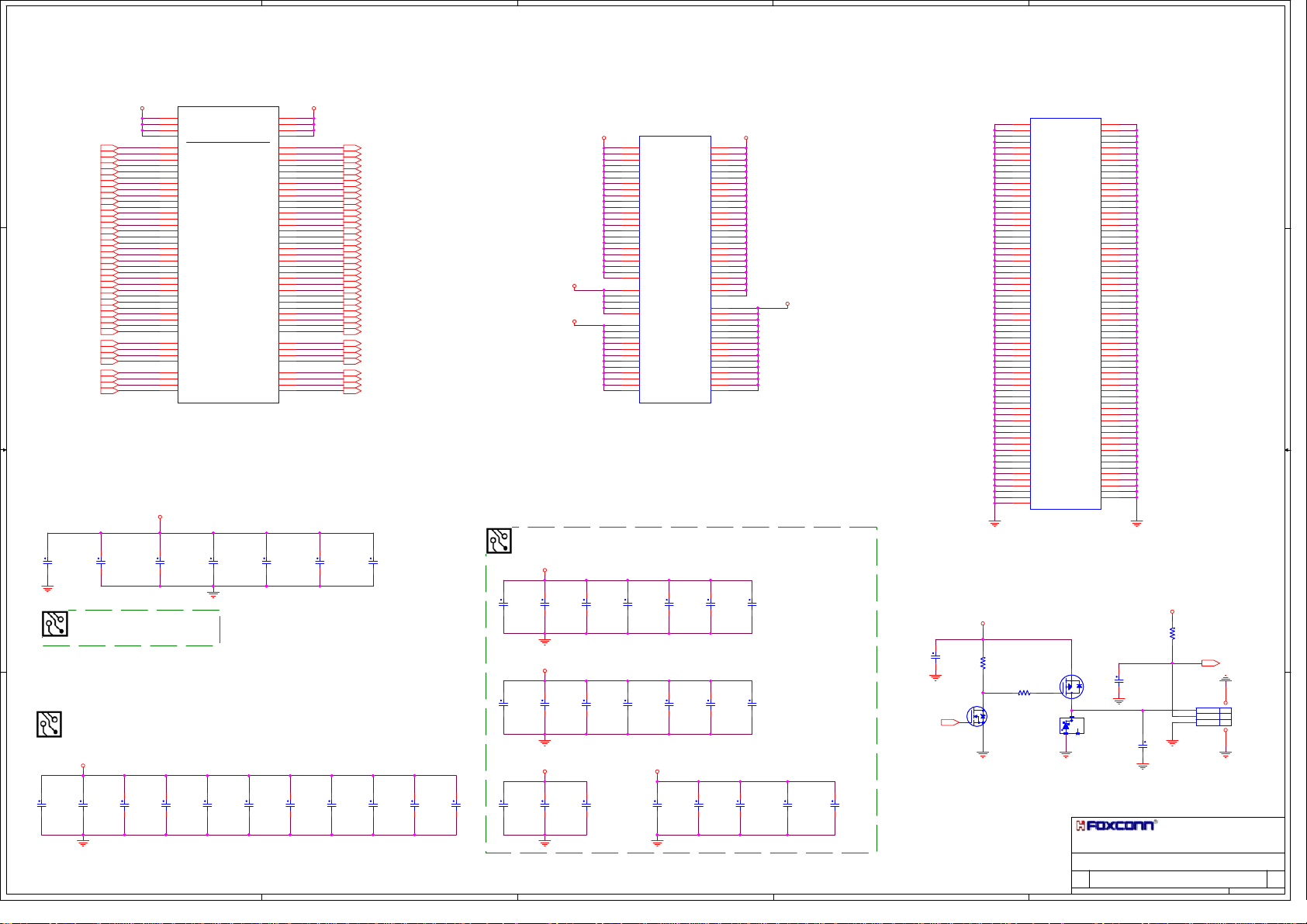

P04 : POWER DELIVERY CHART

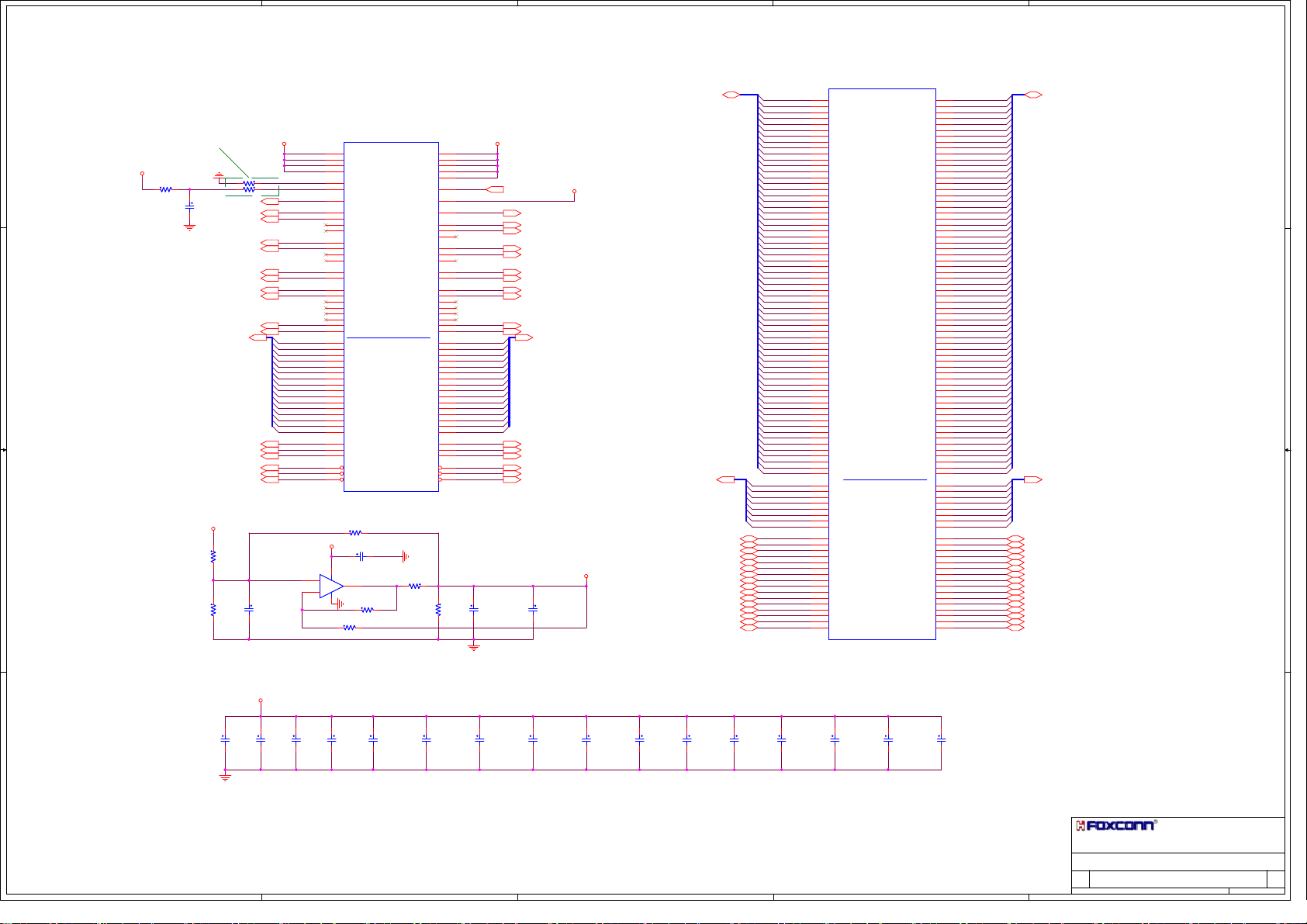

P05 : POWER SEQUENCY DIAGRAM

P06 : POWER SEQUENCE CHART

P07 : SMBUS&I2C MAP

P08 : S1G4 HT I/F & PWR

P09 : S1G4 CTRL & DEBUG

P10 : S1G4 DDRIII MEMORY I/F

P11 : RS880M-PCIE/HT LINK/SPMEM

C C

P12 : RS880M-SYSTEM I/F

P13 : RS880M-POWER

P14 : SB820M-PCIE/CPU/LPC/STRAP

P15 : SB820M-GPIO/USB/AZ//SATA

P16 : SB820M-POWER & DECOUPLING

P17 : DDR3(SO-DIMM_0/1)

P18 : VGA_S3 (PCI-E) 1/3

P19 : VGA (IO)/(STRAP) 2/3

P20 : VGA_S3 (POWER) 3/3

P21 : VRAM (DDR3)

P22 : EC+KBC (IT8502E) & ROM

P23 : Audio (CODEC_ALC270A)

P24 : Audio (JACK+AMP+SPK+Mute)

P25 : LAN(RTL8103EL)

P26 : Mini PCIe & RJ11 & BT

P27 : USBX2/USB DB/SATA CONN.

P28 : Card Reader

P29 : HDMI & CRT

P30 : LVDS&Webcam

P31 : PWR_Charger MAX8731AETI

P32 : 5V/3.3V SN0608098RHBT

P33 : Vcore MAX17480

P34 : +V1.1S TPS51117 & VDDR

P35 : +V1.8S RT8253ALGS & VDDA

P36 : PWR_Others power plane

P37 : +VCCNB & 1.5VDDR3 +0_75V

P38 : ATVDD TPS51217 & +VPCIE

P39 : Stitch CAP

Daughter Board

P40 -- Power Board / USB Board / SW Board

B B

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

Design byP. Leader Check by

Sheet of

Sheet of

Sheet of

MV

MV

MV

139

139

139

A A

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 19:11:12

Page Modified:

Wednesday, April 07, 2010 19:11:12

Page Modified:

5

4

3

2

Wednesday, April 07, 2010 19:11:12

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

1

Page 2

1

2

3

4

5

6

7

8

VRAMx4

64Mx16

DDR3

P21

A A

Discrete GPU Option

HDMI

Conn.

LVDS

Conn.

CRT

Conn.

B B

HDMI

P29

LVDS

P30

CRT

P29

Int. Speaker x2

Option

WLAN or WLAN+BT

Half Size Mini-Card

Analog Mic x1

With Pre-Amp

Ext. Mic In Jack

Headphone Jack

P29

Buffer

Level Shifter

ESD

P24

P23

P24

P24

P29

CODEC

RealTek

ALC270A-GR

USB 2.0 (2 amp) x2

P27

USB 2.0 (2 amp) x1

P27

Option

VGA Webcam (F2.8 lens)

GPU

ATI

PCIe X16

800/1066/1333 MHZ

Park XT

64bit

P18-20

AMD

S1G4

800/1066/1333 MHZ

P8-10

HT

PCIe

North Bridge

P23

PCIe

HDA

USB2.0

RS880M

P11-13

A-Link

South Bridge

Side Port

USB2.0

HDA

SB820M

Int CLK Gen

P14-16

SATA

Seti 100B;

C C

OmniVision OV7670;

Micron MI-366;

P30

LPC

KBMX

FAN

Battery Pack

System

P31

Adapter

19V

P31

D D

1

Charger

MAX8731AETI

P31

2

Lid

Switch

Power

Button

KBC ROM

2MB

P8

P40

P40

P27

3

PWM

GPIO

SPI

Embedded

Controller

ITE IT8502E

P27

4

5

PS/2

SMBus

SMBus

SO-DIMM 0

800/1066/1333 MHZ

DDR(III)

SO-DIMM 1

800/1066/1333 MHZ

DDR(III)

LAN

RealTek

RTL8103EL (10/100)

DDR3

128MB

P11

SATA : HDD

SATA : ODD

Keyboard

Touch PAD

CPU Thermal Sensor

GMT G786P81U

GPU Thermal Sensor

GMT G781_1

6

P17

P17

Transformer

DELTA

RJ45

LFE8456A-R

P25

Option

BlueTooth Module

Card Reader

RealTek

RTS5159

P28

Option

MDC Modem

P26

P27

P27

P22

P22

P9

P20

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

7

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

P26

5-IN-1

Combo

Connector

RJ11

Sheet of

239

Sheet of

239

Sheet of

239

8

MV

MV

MV

Page 3

5

4

3

2

1

D D

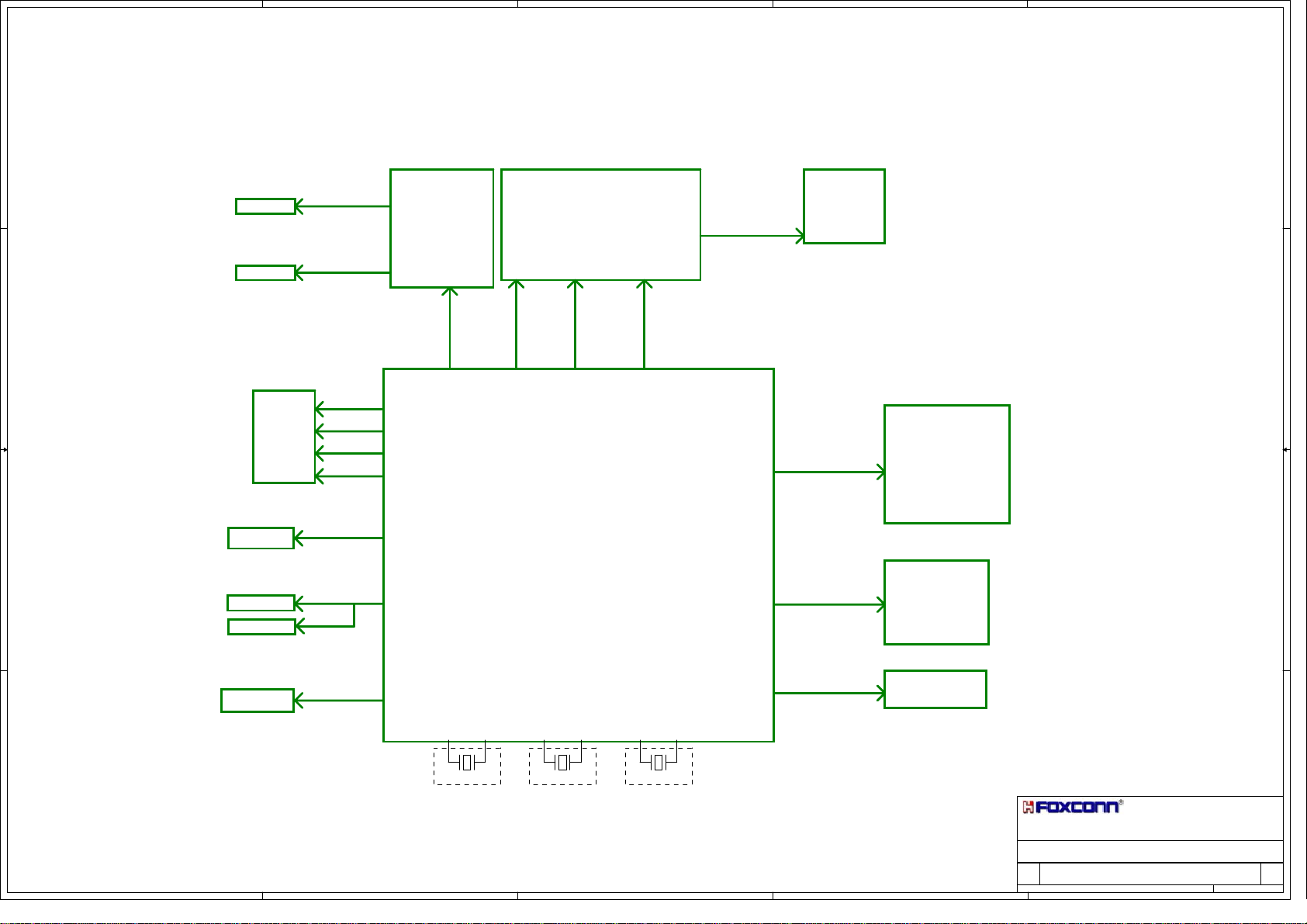

SDDR_A_CLK_DDR0

SDDR_A_CLK_DDR#0

SDDR_A_CLK_DDR1

STRAPS

SETTING,

UNUSED

CLOCKS

SDDR_A_CLK_DDR#1

800/1066/1333MHZ

SDDR_B_CLK_DDR0

SDDR_B_CLK_DDR#0

SDDR_B_CLK_DDR1

SDDR_B_CLK_DDR#1

800/1066/1333MHZ

PCI_CLK1

Stopped CLK

PCI_CLK2

Stopped CLK

PCI_CLK3

Stopped CLK

PCI_CLK4

Stopped CLK

CLK_PCI_KBC

33MHZ

HDA_BITCLK

24MHZ

A_SODIMM

B_SODIMM

C C

KBC

B B

HD AUDIO

HD MDC

INTERNAL CLOCK MODE

SPM_CLKP

SPM_CLKN

AMD

SIG4 CPU

CLK_CPU_R

CLK_CPU#_R

PCICLK1

PCICLK2

PCICLK3

PCICLK4

LPCCLK0

AZ_BITCLK

CPU_HT_CLKP/N

RS880M

A-LINK

200MHZ

CLK_NBLINK_R

CLK_NBLINK#_R

PCIE_RCLKP/N

REFCLKP/N

CLK_NB_REF_R

100MHZ

CLK_NB_REF#_R

NB_DISP_CLKP/N

100MHZ

GPP_REFCLK

100MHZ

CLK_HT_REF#_R

CLK_HT_REF_R

NB_HT_CLKP/N

AMD SB820M

CLOCK GENERATOR

400MHZ

SLT_GFX_CLKP/N

GPP_CLK1P/N

CLK_PEG_REF_R

CLK_PEG_REF#_R

CLK_PCIE_MINI_R

CLK_PCIE_MINI#_R

SIDE PORT

MEMORY CHIP

100MHZ

100MHZ

Park_XT or M93_XT

CLK_REQG# in SB

WLAN

CLK_REQ1 in SB

CLK_PCIE_LAN_R

Card Reader

A A

5

CLK_48M_CARD_R

48MHZ

14M_25M_48M_OSC

FOR MASTER FOR RTC FOR SATA

25M Hz

4

32.768K Hz

25M Hz

3

GPP_CLK3P/N

DNI

CLK_PCIE_LAN#_R

100MHZ

LAN

CLK_REQ3 in SB

2

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

CLOCK MAP

CLOCK MAP

CLOCK MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:17

Page Modified:

Wednesday, April 07, 2010 18:49:17

Page Modified:

Wednesday, April 07, 2010 18:49:17

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

1

Sheet of

339

Sheet of

339

Sheet of

339

MV

MV

MV

Page 4

5

4

3

2

1

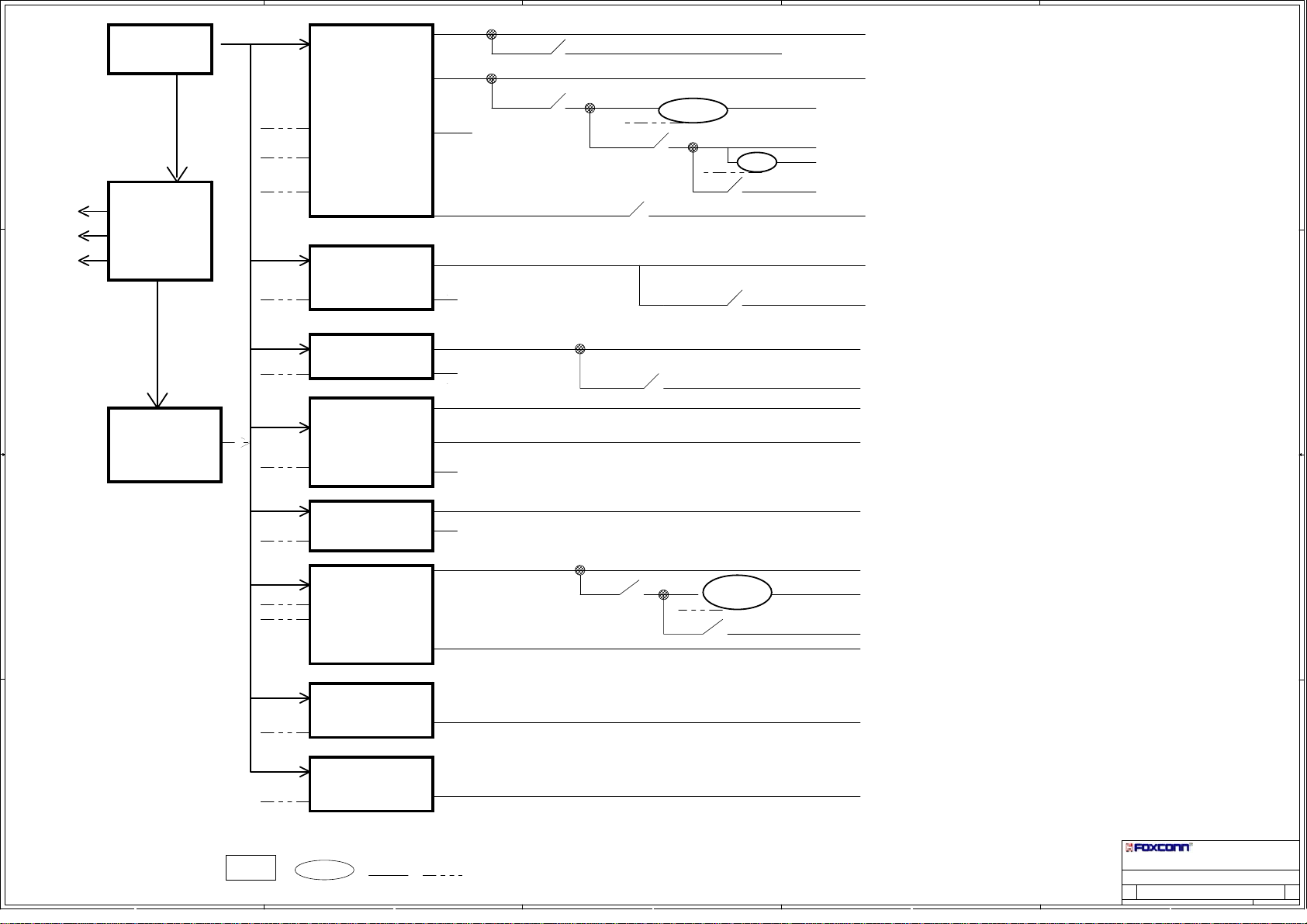

+V5A/7A/5.6A

+V5S/4A/4A

+V3.3A/6A/4.8A

SI7716ADN-T1-GE3

RUN_ON_LOAD

+V3.3A

APL5930

+V1.1A/600mA/600mA

+V3.3S/4A/4A+V3.3A

APL5930

+V3.3S

+V3.3S_DELAY/0.5A/0.5A

SI7716ADN-T1-GE3

+V12A +V12S

FDN340P_NL

SLP_S3#_3R

+V1.1S/10A/8A

For system power enable.

PAD

+VLDT/4A/3.2A

SI7716ADN-T1-GE3

+V3.3AL/6A/4.8A

VDDA_CPU/600mA/600mA

+V1.1A/10A/8A

+VLDT/4A/3.2A

+V1.8S/3A/2.4A

+V1.8S_GPU

+VCC_CORE/38A/30A

+VDDNB_CPU/4A/4A

in S0~S5

in S0~S1

in S0~S5

in S0~S5

in S0~S1

in S0~S1

in S0~S1

in S0~S5

in S0~S1

in S0~S1

in S0~S1

in S0~S1

in S0~S1

PGOOD

PGOOD

PWRGD

+V5A

+V3.3AL

+V5AL

CHARGE BUMP

V1.8S_PWRGD

VRM_PWRGD

+V5A

SI7716ADN-T1-GE3

RUN_ON_LOAD

+V3.3AL

SI7716ADN-T1-GE3

EC_ALW_EN

Adaptor

19.5V

90W/65W

D D

3.3A/4.7A

ACPRES

ADAPT_OC_IINP

ENDCHG

C C

PWR_Charger

Battery Charger

Switch Mode

MAX8731AETI

BT+

Battery Pack

3S2P/3S3P

47/55/62/93W

+VBAT

EC_ALW_EN

+V5AL

+V3.3A_RTC

VRM&V1.8S_PWRGD

SLP_S3#_3R

VDDA_PWRGD

TI SN0608098

+V5A/+V3.3AL

For System Power

EN1(+V5A)

EN2(+V3.3AL)

ENLDO(5V LDO)

TI

TPS51117

For +V1.1S

EN

MPS NB634

For +V1.8S

EN

MAXIM

MAX17480

FOR +VCC_CORE

SHDN#

MPS NB634

For +VDDR_NB

VDDA_PWRGD

B B

SLP_S3#_3R

SLP_S5#_3R

EN

TI

TPS51117RGYRG4

For +V1.5 DDR3

S3

G2997F6U

S5

For +V0.75S

PGOOD

+V1.5

SI7716ADN-T1-GE3

+V1.8S_PWRGD

+V1.5S/5A/4A

SLP_S3#_3R

APL5930

SI7716ADN-T1-GE3

TI

TPS51217DSCR

VRM_PWRGD

A A

Switching

5

For +VCCNB

TI

TPS51217DSCR

For +VDD_CORE

Linear Control signal

Power Rail

4

3

+VDDR_NB/2A/2A

+V1.5/10A/8A

+VPCIE/2.5A/2A

1.1V 1.0V

+V1.5S_GPU

+V0.75S/1A/1A

+VCC_NB/10A/8A

+VDD_CORE/10A/8A

in S0~S1

in S0~S3

in S0~S1

in S0~S1

in S0~S1

in S0~S1

in S0~S1

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

1

Hon Hai Precision Industry Co. Ltd.

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

Sheet of

439

Sheet of

439

Sheet of

439

MV

MV

MV

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

POWER DELIVERY CHART

POWER DELIVERY CHART

POWER DELIVERY CHART

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

2

Wednesday, April 07, 2010 18:49:16

Page 5

5

D D

+V3.3AL

+V3.3AL

4

SWITCH

PQ31

+V3.3A

+V5A

3

2

+1.1VEN

+V1.1A

2

1

APL5930

EC

ITE8502

EC_PWRBTN#

C C

3

SB820M

EC_ALW_EN

SLP_S5#

SLP_S3#

1

4

4

4

+V5A

+V3.3A

SLP_S3#

SWITCH

PQ42

PQ39

Power on Sequence required:

SB820M:

1, +V3.3A ramp before +V1.1A

2, +V3.3S ramp before +V1.8S

3, +V1.8S ramp before +V1.1S

B B

4, +V3.3S ramp before +V1.1S

RS880M:

1, 0 <(+V3.3S) - (+V1.8S) < 2.1

2, +V1.8S ramp before +V1.1S

3. +V1.1S ramp before VCC_NB

SN0608098RHBT

TPS51117

& G2997F6U

+V5S

+V3.3S

5

APL5930

LDO

EN

+V1.5

+V0.75S

CPU_VDDA_RUN

6

VDDA_PWRGD

VRM_PWRGD

+VDDR_CPU

VRM_PWRGD

+V1.8S

V1.8S_PWRGD

VCC_NB

+V1.5

SWITCH

PQ17

TPS51117

+V1.5S

+V1.1S

VLDT

4

7

PWRGD

NB634

MAX 17480

NB634

PWRGD

+VCC_CORE

8

+VDDNB_CPU

8

8

9

9

VRM_PWRGD

TPS51217

A A

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

POWER SEQUENCY DIAGRAM

POWER SEQUENCY DIAGRAM

POWER SEQUENCY DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

5

4

3

2

Wednesday, April 07, 2010 18:49:16

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

1

Sheet of

539

Sheet of

539

Sheet of

539

MV

MV

MV

Page 6

5

LDT_RST#

(SB to CPU)

4

3

2

1

LDT_PG

(SB to CPU)

D D

C C

CPU MEM CTL &

DDR3 SODIMM PWRS

B B

CPU_THM/SB/SB_SCL1/2

SB_KB/SPI/LPC ROM PWRS

CPU_CLKP/N running

NB_PWRGD

(SB to NB)

SB_PWRGD

(VRM_PWRGD to SB)

0.95V - 1.1V

1.1V

+VLDT

+V1.1S

0.9V(DDR3-1066) 1.05V(DDR3-1333)

0.8V - 1.1V

0.9V

2.5V

+V1.8S

+V12S

+V0.75S only will be shut down in S3 mode

+V0.75S

M_VREF

+V1.5

RC=0

Power button from EC to SB

20mS

delay

+V12A/+V5A/+V3.3A/+V1.1A

When IMC, always on at all time( always PWR)

VRM_PWRGD

(from +VCC_CORE IC)

+VDDR_CPU

+VCC_CORE

+VDDNB_CPU

VDDA_PWRGD

+VDDA_CPU

V1.8S_PWRGD

GROUP A GROUP B

+V5S/+V3.3S

SLP_S3#_3R (SB to EC)

SLP_S5#_3R (SB to EC)

EC_PWRBTN#

RSMRST# (EC to SB)

ALW RAILS

+VCC_NB

Req.

>1 mS

>1 mS Req.

running

>1 mS Req.

RC=~22ms

VRM_PWRGD AND V1.8S_PWRGD

RC=0

RC=0

RC=0

VCC_NB(all NB power) valid before NB_PWRGD.

VCC_NB should not ramp before +V1.1S

SLP_S3#_3R

V1.8S_PWRGD

V1.1A_PWRGD

VRM_PWRGD

to S3

EC_ALW_EN (from EC)

KBC is ready

KBC is powered by

+V3.3AL

Power on Sequence required:

SB820:

A A

1, +V3.3A ramp before +V1.1A

2, +V3.3S ramp before +V1.8S

3, +V1.8S ramp before +V1.1S

5, +V3.3A ramping down time > 300us

6, 50uS <= All power rails except +V3.3A <= 40mS

7, 100uS <= +V3.3A <= 40mS

RS880M:

1, 0 <(+V3.3S) - (+V1.8S) < 2.1

2, +V1.8S ramp before +V1.1S

3. +V1.1S ramp before +VCC_NB

5

PWR_SWIN#

ACPRES

(ACIN detect)

+V5AL/+V3.3AL

M31ALDO

(from DCIN)

+VBAT

+VCC_RTC

4

Power button pressed

AC not present scenario = LOW AC present= high

Battery inserted/AC IN

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

POWER SEQUENCY TIMING

POWER SEQUENCY TIMING

POWER SEQUENCY TIMING

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

3

2

Wednesday, April 07, 2010 18:49:16

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

1

Sheet of

639

Sheet of

639

Sheet of

639

MV

MV

MV

Page 7

5

4

3

2

1

+V3.3S_DELAY

+V3.3S_DELAY

D D

2N7002

+V3.3S_DELAY

+V3.3S_DELAY

2.2K ohm

DHDMI_DDC_DATA

DHDMI_DDC_CLK

2.2K ohm

DLVDS_DDC_DATA

DLVDS_DDC_CLK

2.2K ohm

DCRT_DDC_DATA

DCRT_DDC_CLK

DDCDATA

DDCCLK

GPU

Park XT

S3 Package

SDA

SCL

DDC1DATA

SMBUS&I2C MAP

+V3.3S

2.2K ohm

SMB0DATA

SMB0CLK

SB_SMB0_DAT_3S

SB_SMB0_CLK_3S

DIMM0

DIMM1

DDC1CLK

C C

CRT

+V5S_SYNC

2.2K ohm

CRT_DDC_DATA_5S

CRT_DDC_CLK_5S

Buffer

Level Shift

CRT_DDC_DATA

CRT_DDC_CLK

+V3.3S

4.7K ohm

UCRT_DDC_DATA

UCRT_DDC_CLK

ESD

+V3.3S

LVDS_DDC_DATA

LVDS

B B

+V5S

LVDS_DDC_CLK

2.2K ohm

+V3.3S

HDMI_DDC_DATA

HDMI

A A

HDMI_DDC_CLK

2N7002

4.7K ohm

+V3.3S

4.7K ohm

ULVDS_DDC_DATA

ULVDS_DDC_CLK

UTMDS_DDC_DATA

UTMDS_DDC_CLK

SB820M

CRT_DDC_DATA

CRT_DDC_CLK

L_DDC_DATA

L_DDC_CLK

DDPD_CTRLDATA

DDPD_CTRLCLK

CPU

Temp Sensor

GPU

Temp Sensor

SML1DATA

SML1CLK

SML2DATA

SML2CLK

+V3.3S

4.7K ohm

EC_SMB0_DAT_3S

EC_SMB0_CLK_3S

SB_SMB2_DAT_3A

SB_SMB2_CLK_3A

Charger

Battery

+V3.3A

+V3.3S

2N7002

2.2K ohm

+V3.3A

2N7002

+V3.3AL

+V3.3AL

+V3.3AL

2.2K ohm

EC_SMB2_DAT_3AL

EC_SMB2_CLK_3AL

2.2K ohm

EC_SMB1_DAT_3AL

EC_SMB1_CLK_3AL

2.2K ohm

EC_SMB0_DAT_3AL

EC_SMB0_CLK_3AL

WLAN

SMDAT2

SMCLK2

SMDAT1

SMCLK1

EC

ITE8502

SMDAT0

SMCLK0

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

1

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

Sheet of

739

Sheet of

739

Sheet of

739

MV

MV

MV

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

SMBUS&I2C MAP

SMBUS&I2C MAP

SMBUS&I2C MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

5

4

3

2

Wednesday, April 07, 2010 18:49:16

Page 8

5

UX4A

UX4A

+VLDT

D1

D2

D3

D4

E3

E2

E1

F1

G3

G2

G1

H1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

K5

N1

P1

P3

P4

D D

HT_NB_CPU_CAD_H011

HT_NB_CPU_CAD_L011

HT_NB_CPU_CAD_H111

HT_NB_CPU_CAD_L111

HT_NB_CPU_CAD_H211

HT_NB_CPU_CAD_L211

HT_NB_CPU_CAD_H311

HT_NB_CPU_CAD_L311

HT_NB_CPU_CAD_H411

HT_NB_CPU_CAD_L411

HT_NB_CPU_CAD_H511

HT_NB_CPU_CAD_L511

HT_NB_CPU_CAD_H611

HT_NB_CPU_CAD_L611

HT_NB_CPU_CAD_H711

HT_NB_CPU_CAD_L711

HT_NB_CPU_CAD_H811

HT_NB_CPU_CAD_L811

HT_NB_CPU_CAD_H911

HT_NB_CPU_CAD_L911

HT_NB_CPU_CAD_H1011

HT_NB_CPU_CAD_L1011

HT_NB_CPU_CAD_H1111

HT_NB_CPU_CAD_L1111

HT_NB_CPU_CAD_H1211

HT_NB_CPU_CAD_L1211

HT_NB_CPU_CAD_H1311

HT_NB_CPU_CAD_L1311

HT_NB_CPU_CAD_H1411

HT_NB_CPU_CAD_L1411

HT_NB_CPU_CAD_H1511

HT_NB_CPU_CAD_L1511

C C

HT_NB_CPU_CLK_H011

HT_NB_CPU_CLK_L011

HT_NB_CPU_CLK_H111

HT_NB_CPU_CLK_L111

HT_NB_CPU_CTL_H011

HT_NB_CPU_CTL_L011

HT_NB_CPU_CTL_H111

HT_NB_CPU_CTL_L111

4.7uF_X5R_6.3V

CX59

CX59

0603

0603

I

I

4.7uF_X5R_6.3V

CX68

CX68

0603

0603

I

I

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

B B

*

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

J1

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

SOCKET_638_PIN

SOCKET_638_PIN

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

CX60

CX60

0603

0603

I

I

HT LINK

HT LINK

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_H1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

CX67

CX67

220nF_Y5V_10V

220nF_Y5V_10V

0402

0402

I

I

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CLKOUT_L0

L0_CLKOUT_L1

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

CX66

CX66

220nF_Y5V_10V

220nF_Y5V_10V

0402

0402

I

I

+VLDT+VLDT

CX54

CX54

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

Place close to socket

* If VLDT is connected only on one side,

one 4.7uF cap should be added to

the island side

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+V1.5

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

A A

CX49

CX49

0603

0603

I

I

4.7uF_X5R_6.3V

CX50

CX50

0603

0603

I

I

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

5

CX17

CX17

0603

0603

I

I

4.7uF_X5R_6.3V

CX18

CX18

0603

0603

I

I

220nF_Y5V_10V

220nF_Y5V_10V

CX39

CX39

0402

0402

I

I

220nF_Y5V_10V

220nF_Y5V_10V

CX26

CX26

0402

0402

I

I

220nF_Y5V_10V

220nF_Y5V_10V

CX32

CX32

0402

0402

I

I

220nF_Y5V_10V

220nF_Y5V_10V

HT_CPU_NB_CAD_H0 11

HT_CPU_NB_CAD_L0 11

HT_CPU_NB_CAD_H1 11

HT_CPU_NB_CAD_L1 11

HT_CPU_NB_CAD_H2 11

HT_CPU_NB_CAD_L2 11

HT_CPU_NB_CAD_H3 11

HT_CPU_NB_CAD_L3 11

HT_CPU_NB_CAD_H4 11

HT_CPU_NB_CAD_L4 11

HT_CPU_NB_CAD_H5 11

HT_CPU_NB_CAD_L5 11

HT_CPU_NB_CAD_H6 11

HT_CPU_NB_CAD_L6 11

HT_CPU_NB_CAD_H7 11

HT_CPU_NB_CAD_L7 11

HT_CPU_NB_CAD_H8 11

HT_CPU_NB_CAD_L8 11

HT_CPU_NB_CAD_H9 11

HT_CPU_NB_CAD_L9 11

HT_CPU_NB_CAD_H10 11

HT_CPU_NB_CAD_L10 11

HT_CPU_NB_CAD_H11 11

HT_CPU_NB_CAD_L11 11

HT_CPU_NB_CAD_H12 11

HT_CPU_NB_CAD_L12 11

HT_CPU_NB_CAD_H13 11

HT_CPU_NB_CAD_L13 11

HT_CPU_NB_CAD_H14 11

HT_CPU_NB_CAD_L14 11

HT_CPU_NB_CAD_H15 11

HT_CPU_NB_CAD_L15 11

HT_CPU_NB_CLK_H0 11

HT_CPU_NB_CLK_L0 11

HT_CPU_NB_CLK_H1 11

HT_CPU_NB_CLK_L1 11

HT_CPU_NB_CTL_H0 11

HT_CPU_NB_CTL_L0 11

HT_CPU_NB_CTL_H1 11

HT_CPU_NB_CTL_L1 11

CX48

CX48

0402

0402

I

I

4

CX53

CX53

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

100nF_Y5V_10V

100nF_Y5V_10V

CX43

CX43

0402

0402

I

I

4

100nF_Y5V_10V

100nF_Y5V_10V

CX27

CX27

0402

0402

I

I

10nF_X7R_16V

10nF_X7R_16V

CX31

CX31

0402

0402

I

I

M10

+VDDNB_CPU

+V1.5

N11

K16

M16

P16

V16

H25

K18

K21

K23

K25

M18

M21

M23

M25

N17

BOTTOM SIDE DECOUPLING

+VCC_CORE

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

CX33

CX33

0805

0805

I

I

+VCC_CORE

22uF_X5R_6.3V

22uF_X5R_6.3V

CX41

CX41

0805

0805

I

I

+VDDNB_CPU +V1.5

22uF_X5R_6.3V

22uF_X5R_6.3V

CX21

CX21

0805

0805

I

I

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

CX30

CX30

0805

0805

I

I

CX38

CX38

0805

0805

I

I

CX40

CX40

0805

0805

I

I

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

CX19

CX19

0805

0805

I

I

CX42

CX42

0805

0805

I

I

CX35

CX35

0805

0805

I

I

G4

VDD_1

H2

VDD_2

J9

VDD_3

J11

VDD_4

J13

VDD_5

J15

VDD_6

K6

VDD_7

K10

VDD_8

K12

VDD_9

K14

VDD_10

L4

VDD_11

L7

VDD_12

L9

VDD_13

L11

VDD_14

L13

VDD_15

L15

VDD_16

M2

VDD_17

M6

VDD_18

M8

VDD_19

VDD_20

N7

VDD_21

N9

VDD_22

VDD_23

VDDNB_1

VDDNB_2

VDDNB_3

T16

VDDNB_4

VDDNB_5

VDDIO1

J17

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

L17

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

22uF_X5R_6.3V

3

UX4E

UX4E

SOCKET_638_PIN

SOCKET_638_PIN

CX36

CX36

0805

0805

I

I

CX29

CX29

0805

0805

I

I

22uF_X5R_6.3V

22uF_X5R_6.3V

CX22

CX22

0805

0805

I

I

3

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

220nF_Y5V_10V

220nF_Y5V_10V

CX25

CX25

0402

0402

I

I

220nF_Y5V_10V

220nF_Y5V_10V

CX45

CX45

0402

0402

I

I

22uF_X5R_6.3V

22uF_X5R_6.3V

2

UX4F

UX4F

AA4

VSS1

AA11

RH3

RH3

1K_5%

1K_5%

0402

0402

I

I

RH19 1K_5%

RH19 1K_5%

0402

0402

QH1

QH1

2N7002-7-F

2N7002-7-F

SOT23-3

SOT23-3

I

I

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AB2

AB7

AB9

AD6

AD8

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

SOCKET_638_PIN

SOCKET_638_PIN

G

I

I

+VCC_CORE+VCC_CORE

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

10nF_X7R_16V

10nF_X7R_16V

CX23

CX23

0402

0402

I

I

10nF_X7R_16V

10nF_X7R_16V

CX24

CX24

0402

0402

I

I

CX47

CX47

0805

0805

I

I

180pF_NPO_50V

180pF_NPO_50V

CX46

CX46

0402

0402

I

I

180pF_NPO_50V

180pF_NPO_50V

CX44

CX44

0402

0402

I

I

220nF_Y5V_10V

220nF_Y5V_10V

CX37

CX37

0402

0402

I

I

+V1.5

220nF_Y5V_10V

220nF_Y5V_10V

CX34

CX34

0402

0402

I

I

180pF_NPO_50V

180pF_NPO_50V

CX28

CX28

0402

0402

I

I

+V5S

CH4

CH4

10uF_X5R_10V

10uF_X5R_10V

0805

0805

I

I

A4405

D

EC_FAN1_PWM22

2

D

S

S

G

G

J6

VSS66

J8

VSS67

J10

VSS68

J12

VSS69

J14

VSS70

J16

VSS71

J18

VSS72

K2

VSS73

K7

VSS74

K9

VSS75

K11

VSS76

K13

VSS77

K15

VSS78

K17

VSS79

L6

VSS80

L8

VSS81

L10

VSS82

L12

VSS83

L14

VSS84

L16

VSS85

L18

VSS86

M7

VSS87

M9

VSS88

AC6

VSS89

M17

VSS90

N4

VSS91

N8

VSS92

N10

VSS93

N16

VSS94

N18

VSS95

P2

VSS96

P7

VSS97

P9

VSS98

P11

VSS99

P17

VSS100

R8

VSS101

R10

VSS102

R16

VSS103

R18

VSS104

T7

VSS105

T9

VSS106

T11

VSS107

T13

VSS108

T15

VSS109

T17

VSS110

U4

VSS111

U6

VSS112

U8

VSS113

U10

VSS114

U12

VSS115

U14

VSS116

U16

VSS117

U18

VSS118

V2

VSS119

V7

VSS120

V9

VSS121

V11

VSS122

V13

VSS123

V15

VSS124

V17

VSS125

W6

VSS126

Y21

VSS127

Y23

VSS128

N6

VSS129

SD

S

S

QH2

QH2

G

G

PMV65XP

PMV65XP

D

D

VCCFAN1

3

BAT54_200mA

BAT54_200mA

DH1

DH1

1

2

100nF_Y5V_10V

100nF_Y5V_10V

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

S1G4 HT I/F & PWR

S1G4 HT I/F & PWR

S1G4 HT I/F & PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

CH5

CH5

47nF_Y5V_16V

47nF_Y5V_16V

0402

0402

I

I

CX76

CX76

0402

0402

I

I

1

+V3.3S

RH8

RH8

4.7K_5%

4.7K_5%

0402

0402

I

I

EC_FAN1_TACH 22

FAN

1

2

3

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

1

1

1

HEADER3

HEADER3

2

2

Header_1X3_3u

Header_1X3_3u

3

3

4 5

Sheet of

Sheet of

Sheet of

MV

MV

MV

839

839

839

Page 9

5

4

3

2

1

LAYOUT: ROUTE VDDA TRACE APPROX.

D D

+VDDA_CPU

CX74

CX74

+

+

100uF_SP_6.3V

100uF_SP_6.3V

7.3X4.3

7.3X4.3

I

I

FBX1 26_0.6A

FBX1 26_0.6A

0805 I

0805 I

CX70

CX70

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

CX75

CX75

0603

0603

I

I

CX69

CX69

220nF_Y5V_10V

220nF_Y5V_10V

0402

0402

I

I

Keep net PWRGD, LDT_STOP#, LDT_RST# no stub

+V1.5S

RX23

RX23

300_5%

300_5%

0402

0402

I

I

+V1.5S

5

RX55

RX55

0_5%

0_5%

+V1.5S

RX27

RX27

300_5%

300_5%

0402

0402

I

I

RX22

RX22

300_5%

300_5%

0402

0402

I

I

LDT_RST#

CX61

CX61

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

RX53

RX53

4.7K_5%

4.7K_5%

0402

0402

LDT_PG

0402

0402

I

I

LDT_STOP#

I

I

RX4

RX4

0402

0402

1K_5%

1K_5%

I

I

+V3.3S

+V1.5S

+V1.8S

2 4

+V1.5

RX3

RX3

0402

0402

1K_5%

1K_5%

I

I

RX54

RX54

4.7K_5%

4.7K_5%

0402

0402

I

I

RX21

RX21

300_5%

300_5%

0402

0402

NI

NI

CPU_LDT_REQ#

100nF_Y5V_10V

100nF_Y5V_10V

CX62

CX62

0402 I

0402 I

53

1

74LVC1G07GW

74LVC1G07GW

CPU_ALERT

CPU_SID

G2

G

G

S

S

QX5B

QX5B

2N7002DW-7-F

2N7002DW-7-F

UX3

UX3

RX7

RX7

0402

0402

1K_5%

1K_5%

I

I

+V3.3S

S

S

D

D

CPU_SIC

G1

D2S2

LDT_PG14

17480_PGD_IN33

C C

B B

A A

LDT_STOP#12,14

LDT_RST#14

EC_SMB0_DAT_3S

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

CX71

CX71

3.3nF_X7R_50V

3.3nF_X7R_50V

0402

0402

CLK_CPU_R14

I

I

CLK_CPU#_R14

+V3.3S

RX29

RX29

4.7K_5%

4.7K_5%

0402

0402

I

I

CPU_LDT_RST_HTPA#

CPU_SIC 15

CPU_SID 15

G

G

D1S1

D

D

QX5A

QX5A

2N7002DW-7-F

2N7002DW-7-F

CX72 3.9nF_X7R_50V

CX72 3.9nF_X7R_50V

0402 I

0402 I

CX73 3.9nF_X7R_50V

CX73 3.9nF_X7R_50V

0402 I

0402 I

Keep trace from resisor to CPU within 0.6"

keep trace from caps to CPU within 1.2"

place them to CPU within 1.5"

RX19 44.2_1%

RX20 44.2_1%

+VLDT

+V1.5

RX44

RX44

510_5%

510_5%

0402

0402

I

I

RX43

RX43

510_5%

510_5%

0402

0402

I

I

EC_SMB0_CLK_3AL 20,22EC_SMB0_CLK_3S

EC_SMB0_DAT_3AL 20,22

4

VCC_CORE0_FB_H33

VCC_CORE0_FB_L33

RX46

RX46

169_1%

169_1%

0402

0402

I

I

UX4D

CPU_VDDA_RUN

CLK_CPU_C

CLK_CPU#_C

LDT_RST#

LDT_PG

LDT_STOP#

CPU_LDT_REQ#

CPU_SIC

CPU_SID

CPU_ALERT

CPU_HTREF0

IRX19 44.2_1%

I

0402

0402

CPU_HTREF1

IRX20 44.2_1%

I

0402

0402

VCC_CORE1_FB_H

1

TP92TP92

VCC_CORE1_FB_L

1

TP93TP93

CPU_DBRDY

1

TP7TP7

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

TEST23

1

TP1TP1

RX52

RX52

TEST18

1K_5%

1K_5%

TEST19

0402

0402

I

I

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TP20TP20

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

1

TEST6

+V1.5

RX45

RX45

0_5%

0_5%

0402

0402

I

I

F8

F9

A9

A8

B7

A7

F10

C6

AF4

AF5

AE6

R6

P6

F6

E6

Y6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

G9

E9

E8

AB8

AF7

AE7

AE8

AC8

AF8

C2

AA6

A3

A5

B3

B5

C1

1

3

5

7

9

11

13

15

17

19

21

23

UX4D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SIC

SID

ALERT_L

HT_REF0

HT_REF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

SOCKET_638_PIN

SOCKET_638_PIN

HEADER1

HEADER1

KEY

KEY

Header_2x13_S_3u

Header_2x13_S_3u

RSVD11

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

VSS

SVC

SVD

TDO

2

4

6

8

10

12

14

16

18

20

22

24

26

M11

W18

CPU_SVC_R

A6

CPU_SVD_R

A4

THERMTRIP#

AF6

PROCHOT#

AC7

AA8

1

H_THRMDC

W7

H_THRMDA

W8

W9

VDDIO_FB_L

Y9

H6

VDDNB_FB_L

G6

CPU_DBREQ#

E10

CPU_TDO

AE9

TEST28_H_

J7

TEST28_L

H8

TEST17

D7

TEST16

E7

TEST15

F7

TEST14

C7

TEST7

C3

TEST10

K8

C4

TEST29_H

C9

C8

TEST29_L

H18

H19

AA7

D5

C5

CPU_LDT_RST_HTPA#

TP3TP3

1

TP2TP2

1

TP8TP8

1

TP22TP22

1

TP25TP25

1

TP26TP26

1

TP23TP23

1

TP9TP9

1

TP10TP10

1

TP24TP24

1

TP5TP5

RX47

RX47

80.6_1%

80.6_1%

0402

0402

I

I

Route as 80ohm, diff

+V1.5_RUN_FB_H 37

VDDNB_CPU_FB_H 33

route as differential

as short as possible

testpoint under package

HDT Connector

+V3.3S

CX5

CX5

100nF_Y5V_10V

100nF_Y5V_10V

0402

0402

I

I

CX4

2.2nF_X7R_50V

2.2nF_X7R_50V

THER_SD#20,32

CX4

0402

0402

H_THRMDA

NI

NI

H_THRMDC

UX1

UX1

1

VDD

2

DP

3

DN

SYS_SHDN#4GND

G786P81U

G786P81U

SMCLK

SMDATA

ALERT#

I

I

8

EC_SMB0_CLK_3S

7

EC_SMB0_DAT_3S

6

5

+V1.5

RX9

RX9

RX11

RX11

1K_5%

1K_5%

300_5%

300_5%

0402

0402

0402

0402

I

I

I

I

Thermdc and Thermda should be routed away to VRM,

crystal, etc. Customer should follow the MBDG.

However, Guam is using TSI so this does not applies to Guam.

RX25

RX25

1K_5%

1K_5%

0402

0402

NI

NI

CPU_SVC_R

CPU_SVD_R

VID Override Circuit

Note:

To override VID,

Remove RX24, RX48 set VID

SMBus Address: ?H

Place Thermal-Sensor near CPU.

3

2

+V1.5

RX8

RX8

10K_5%

10K_5%

0402

0402

I

I

QX4

QX4

MMBT3904_NL

MMBT3904_NL

SOT23-3

SOT23-3

I

I

B

B

C

E

C

E

E

E

+V1.5+V1.5S

RX50

RX50

1K_5%

1K_5%

0402

0402

NI

NI

RX24 0_5%

0402

0402

RX48 0_5%

0402

0402

RX10

RX10

10K_5%

10K_5%

0402

0402

QX3

QX3

MMBT3904_NL

MMBT3904_NL

SOT23-3

SOT23-3

I

I

B

B

C

C

I

I

CPU_DBREQ#

TEST27

TEST21

TEST20

TEST24

TEST22

TEST12

TEST18

TEST19

RX51

RX51

1K_5%

1K_5%

0402

0402

I

I

IRX24 0_5%

I

IRX48 0_5%

I

RX28

RX49

RX49

220_5%

220_5%

0402

0402

RX28

220_5%

220_5%

0402

0402

NI

NI

N$325219

SVC

SVD

0 0 1.1 1.1

0 1 1.0 1.2

1 0 0.9 1.0

1 1 0.8 0.8

VID OVERIDE TABLE (VDD)

place them under CPU

CPU_PROCHOT# 14

PM_THRMTRIP# 15

+V1.5

RX42 300_5%

RX42 300_5%

I

I

0402

0402

RX33 1K_5%

RX33 1K_5%

I

I

0402

0402

RX39 1K_5%

RX39 1K_5%

I

I

0402

0402

RX35 1K_5%

RX35 1K_5%

I

I

0402

0402

RX37 1K_5%

RX37 1K_5%

I

I

0402

0402

RX32 1K_5%

RX32 1K_5%

I

I

0402

0402

RX38 1K_5%

RX38 1K_5%

I

I

0402

0402

RX40 1K_5%

RX40 1K_5%

I

I

0402

0402

RX41 1K_5%

RX41 1K_5%

I

I

0402

0402

+V1.5S

RX26

RX26

1K_5%

1K_5%

0402

0402

I

I

CPU_SVC 33

CPU_SVD 33

NI

NI

N$325218

BOOT VOLTAGE(VDD)

(CPUVRM_PRO#

(CPUVRM_PRO#

= OPEN)

= VCC/GND)

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

S1G4 CTRL & DEBUG

S1G4 CTRL & DEBUG

S1G4 CTRL & DEBUG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Page Modified:

Wednesday, April 07, 2010 18:49:16

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

1

Sheet of

Sheet of

Sheet of

MV

MV

MV

939

939

939

Page 10

A

B

C

D

E

Processor Memory Interface

UX4C

UX4C

MEM:DATA

SDDR_B_DQ[63:0]17

4 4

UX4B

PLACE THEM CLOSE TO

CPU WITHIN 1"

+V1.5

RX34 0_5%

RX34 0_5%

0402

0402

CX65

CX65

10uF_X5R_10V

10uF_X5R_10V

0805

0805

3 3

2 2

I

I

I

I

RX31 39.2_1%

RX36 39.2_1%

SDDR_A_RST#17

SDDR_A_ODT017

SDDR_A_ODT117

SDDR_A_CS#017

SDDR_A_CS#117

SDDR_A_CKE017

SDDR_A_CKE117

SDDR_A_CLK_DDR017

SDDR_A_CLK_DDR#017

SDDR_A_CLK_DDR117

SDDR_A_CLK_DDR#117

SDDR_A_A[15:0]17

SDDR_A_BS017

SDDR_A_BS117

SDDR_A_BS217

SDDR_A_RAS#17

SDDR_A_CAS#17

SDDR_A_WE#17

+V1.5

RX13

RX13

1K_1%

1K_1%

0402

0402

I

I

RX12

RX12

1K_1%

1K_1%

0402

0402

I

I

CX7

CX7

470nF_X5R_6.3V

470nF_X5R_6.3V

0402

0402

I

I

IRX31 39.2_1%

I

0402

0402

IRX36 39.2_1%

I

0402

0402

SDDR_A_A0

SDDR_A_A1

SDDR_A_A2

SDDR_A_A3

SDDR_A_A4

SDDR_A_A5

SDDR_A_A6

SDDR_A_A7

SDDR_A_A8

SDDR_A_A9

SDDR_A_A10

SDDR_A_A11

SDDR_A_A12

SDDR_A_A13

SDDR_A_A14

SDDR_A_A15

AD10

M_ZP

AF10

M_ZN

AE10

AA16

RX14 0_5%

+V3.3A

3

+

+

4

-

-

RX17 0_5%

M20

M19

M22

M24

D10

VDDR1

C10

VDDR2

B10

VDDR3

VDDR4

MEMZP

MEMZN

H16

MA_RESET_L

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L0

U19

MA0_CS_L1

U20

MA1_CS_L0

V20

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H5

N20

MA_CLK_L5

E16

MA_CLK_H1

F16

MA_CLK_L1

Y16

MA_CLK_H7

MA_CLK_L7

P19

MA_CLK_H4

P20

MA_CLK_L4

N21

MA_ADD0

MA_ADD1

N22

MA_ADD2

MA_ADD3

MA_ADD4

L20

MA_ADD5

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_L

SOCKET_638_PIN

SOCKET_638_PIN

100nF_Y5V_10V

100nF_Y5V_10V

CX6

CX6

0402 I

0402 I

UX2

UX2

+

MCP6001RT-E/OT

+

MCP6001RT-E/OT

1

-

-

5 2

RX15 0_5%

RX15 0_5%

0402

0402

UX4B

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

NIRX14 0_5%

NI

0402

0402

I

I

NIRX17 0_5%

NI

0402

0402

VDDR5

VDDR6

VDDR7

VDDR8

VDDR9

VDDR_SENSE

MEMVREF

MB_RESET_L

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

RX18 10_5%

RX18 10_5%

I

I

0402

0402

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

RX16

RX16

10K_5%

10K_5%

0402

0402

I

I

SDDR_B_A0

SDDR_B_A1

SDDR_B_A2

SDDR_B_A3

SDDR_B_A4

SDDR_B_A5

SDDR_B_A6

SDDR_B_A7

SDDR_B_A8

SDDR_B_A9

SDDR_B_A10

SDDR_B_A11

SDDR_B_A12

SDDR_B_A13

SDDR_B_A14

SDDR_B_A15

CX9

CX9

100nF_Y5V_10V

100nF_Y5V_10V

0402

0402

I

I

+VDDR_CPU+VDDR_CPU

VDDR_CPU_SENSE 34

CPU_M_VREF_SUS

SDDR_B_RST# 17

SDDR_B_ODT0 17

SDDR_B_ODT1 17

SDDR_B_CS#0 17

SDDR_B_CS#1 17

SDDR_B_CKE0 17

SDDR_B_CKE1 17

SDDR_B_CLK_DDR0 17

SDDR_B_CLK_DDR#0 17

SDDR_B_CLK_DDR1 17

SDDR_B_CLK_DDR#1 17

SDDR_B_A[15:0] 17

SDDR_B_BS0 17

SDDR_B_BS1 17

SDDR_B_BS2 17

SDDR_B_RAS# 17

SDDR_B_CAS# 17

SDDR_B_WE# 17

CX8

CX8

1nF_X7R_16V

1nF_X7R_16V

0402

0402

I

I

CPU_M_VREF_SUS

SDDR_B_DM[7:0]17

SDDR_B_DQS017

SDDR_B_DQS#017

SDDR_B_DQS117

SDDR_B_DQS#117

SDDR_B_DQS217

SDDR_B_DQS#217

SDDR_B_DQS317

SDDR_B_DQS#317

SDDR_B_DQS417

SDDR_B_DQS#417

SDDR_B_DQS517

SDDR_B_DQS#517

SDDR_B_DQS617

SDDR_B_DQS#617

SDDR_B_DQS717

SDDR_B_DQS#717

SDDR_B_DQ0

SDDR_B_DQ1

SDDR_B_DQ2

SDDR_B_DQ3

SDDR_B_DQ4

SDDR_B_DQ5

SDDR_B_DQ6

SDDR_B_DQ7

SDDR_B_DQ8

SDDR_B_DQ9

SDDR_B_DQ10

SDDR_B_DQ11

SDDR_B_DQ12

SDDR_B_DQ13

SDDR_B_DQ14

SDDR_B_DQ15

SDDR_B_DQ16

SDDR_B_DQ17

SDDR_B_DQ18

SDDR_B_DQ19

SDDR_B_DQ20

SDDR_B_DQ21

SDDR_B_DQ22

SDDR_B_DQ23

SDDR_B_DQ24

SDDR_B_DQ25

SDDR_B_DQ26

SDDR_B_DQ27

SDDR_B_DQ28

SDDR_B_DQ29

SDDR_B_DQ30

SDDR_B_DQ31

SDDR_B_DQ32

SDDR_B_DQ33

SDDR_B_DQ34

SDDR_B_DQ35

SDDR_B_DQ36

SDDR_B_DQ37

SDDR_B_DQ38

SDDR_B_DQ39

SDDR_B_DQ40

SDDR_B_DQ41

SDDR_B_DQ42

SDDR_B_DQ43

SDDR_B_DQ44

SDDR_B_DQ45

SDDR_B_DQ46

SDDR_B_DQ47

SDDR_B_DQ48

SDDR_B_DQ49

SDDR_B_DQ50

SDDR_B_DQ51

SDDR_B_DQ52

SDDR_B_DQ53

SDDR_B_DQ54

SDDR_B_DQ55

SDDR_B_DQ56

SDDR_B_DQ57

SDDR_B_DQ58

SDDR_B_DQ59

SDDR_B_DQ60

SDDR_B_DQ61

SDDR_B_DQ62

SDDR_B_DQ63

SDDR_B_DM0

SDDR_B_DM1

SDDR_B_DM2

SDDR_B_DM3

SDDR_B_DM4

SDDR_B_DM5

SDDR_B_DM6

SDDR_B_DM7

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

AB26

AE22

AC16

AD12

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

Y11

A12

B16

A22

E25

C12

B12

D16

C16

A24

A23

F26

E26

PLACE CLOSE TO CPU

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

SOCKET_638_PIN

SOCKET_638_PIN

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

SDDR_A_DQ0

SDDR_A_DQ1

SDDR_A_DQ2

SDDR_A_DQ3

SDDR_A_DQ4

SDDR_A_DQ5

SDDR_A_DQ6

SDDR_A_DQ7

SDDR_A_DQ8

SDDR_A_DQ9

SDDR_A_DQ10

SDDR_A_DQ11

SDDR_A_DQ12

SDDR_A_DQ13

SDDR_A_DQ14

SDDR_A_DQ15

SDDR_A_DQ16

SDDR_A_DQ17

SDDR_A_DQ18

SDDR_A_DQ19

SDDR_A_DQ20

SDDR_A_DQ21

SDDR_A_DQ22

SDDR_A_DQ23

SDDR_A_DQ24

SDDR_A_DQ25

SDDR_A_DQ26

SDDR_A_DQ27

SDDR_A_DQ28

SDDR_A_DQ29

SDDR_A_DQ30

SDDR_A_DQ31

SDDR_A_DQ32

SDDR_A_DQ33

SDDR_A_DQ34

SDDR_A_DQ35

SDDR_A_DQ36

SDDR_A_DQ37

SDDR_A_DQ38

SDDR_A_DQ39

SDDR_A_DQ40

SDDR_A_DQ41

SDDR_A_DQ42

SDDR_A_DQ43

SDDR_A_DQ44

SDDR_A_DQ45

SDDR_A_DQ46

SDDR_A_DQ47

SDDR_A_DQ48

SDDR_A_DQ49

SDDR_A_DQ50

SDDR_A_DQ51

SDDR_A_DQ52

SDDR_A_DQ53

SDDR_A_DQ54

SDDR_A_DQ55

SDDR_A_DQ56

SDDR_A_DQ57

SDDR_A_DQ58

SDDR_A_DQ59

SDDR_A_DQ60

SDDR_A_DQ61

SDDR_A_DQ62

SDDR_A_DQ63

SDDR_A_DM0

SDDR_A_DM1

SDDR_A_DM2

SDDR_A_DM3

SDDR_A_DM4

SDDR_A_DM5

SDDR_A_DM6

SDDR_A_DM7

SDDR_A_DQ[63:0] 17

SDDR_A_DM[7:0] 17

SDDR_A_DQS0 17

SDDR_A_DQS#0 17

SDDR_A_DQS1 17

SDDR_A_DQS#1 17

SDDR_A_DQS2 17

SDDR_A_DQS#2 17

SDDR_A_DQS3 17

SDDR_A_DQS#3 17

SDDR_A_DQS4 17

SDDR_A_DQS#4 17

SDDR_A_DQS5 17

SDDR_A_DQS#5 17

SDDR_A_DQS6 17

SDDR_A_DQS#6 17

SDDR_A_DQS7 17

SDDR_A_DQS#7 17

+VDDR_CPU

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

CX64

CX64

0603

0603

I

I

4.7uF_X5R_6.3V

CX20

CX20

0603

0603

I

I

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

CX16

CX16

0603

0603

I

I

4.7uF_X5R_6.3V

4.7uF_X5R_6.3V

CX63

CX63

0603

0603

I

I

1 1

A

Place close to socket

CX58

CX58

220nF_Y5V_10V

220nF_Y5V_10V

0402

0402

I

I

CX57

CX57

220nF_Y5V_10V

220nF_Y5V_10V

0402

0402

I

I

B

CX15

CX15

220nF_Y5V_10V

220nF_Y5V_10V

0402

0402

I

I

CX14

CX14

220nF_Y5V_10V

220nF_Y5V_10V

0402

0402

I

I

CX55

CX55

1nF_X7R_16V

1nF_X7R_16V

0402

0402

I

I

CX56

CX56

1nF_X7R_16V

1nF_X7R_16V

0402

0402

I

I

C

CX12

CX12

1nF_X7R_16V

1nF_X7R_16V

0402

0402

I

I

CX13

CX13

1nF_X7R_16V

1nF_X7R_16V

0402

0402

I

I

CX52

CX52

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

CX51

CX51

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

CX11

CX11

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

D

CX10

CX10

180pF_NPO_50V

180pF_NPO_50V

0402

0402

I

I

Hon Hai Precision Industry Co. Ltd.

Hon Hai Precision Industry Co. Ltd.

Foxconn eMS Inc.

Foxconn eMS Inc.

Foxconn eMS Inc.

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

HNBD R&D phone: +886-2-2799-6111

Title

Title

Title

S1G4 DDRIII MEMORY I/F

S1G4 DDRIII MEMORY I/F

S1G4 DDRIII MEMORY I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Page Modified:

Wednesday, April 07, 2010 18:49:17

Page Modified:

Wednesday, April 07, 2010 18:49:17

Page Modified:

Wednesday, April 07, 2010 18:49:17

Hon Hai Precision Industry Co. Ltd.

Safina

Safina

Safina

(UTC/GMT)

(UTC/GMT)

(UTC/GMT)

E

Sheet of

10 39

Sheet of

10 39

Sheet of

10 39

MV

MV

MV

Page 11

5

Keep the impendance of PCIE lane to 85ohm +/-15%

Including the A-link

All PCIe lane shou route 8" max for Gen2 connector

D D

PEG_RXN1518

PEG_RXP1518

PEG_RXN1418

PEG_RXP1418

PEG_RXN1318

PEG_RXP1318

PEG_RXN1218

PEG_RXP1218

PEG_RXN1118

PEG_RXP1118

PEG_RXN1018

PEG_RXP1018

PEG_RXN918

PEG_RXP918

PEG_RXN818

PEG_RXP818

PEG_RXN718

PEG_RXP718

PEG_RXN618

PEG_RXP618

PEG_RXN518

PEG_RXP518

PEG_RXN418

PEG_RXP418

PEG_RXN318

PEG_RXP318

PEG_RXN218

PEG_RXP218

PEG_RXN118

PEG_RXP118

PEG_RXN018

C C

B B

A A

PEG_RXP018

PCIE_RXP125

PCIE_RXN125

PCIE_RXP326

PCIE_RXN326

A_Link_RXP014

A_Link_RXN014

A_Link_RXP114

A_Link_RXN114

A_Link_RXP214

A_Link_RXN214

A_Link_RXP314

A_Link_RXN314

and max 12" for Gen2 on board devices

UN3B

UN3B

D4

GFX_RX0P

C4

GFX_RX0N

A3

GFX_RX1P

B3

GFX_RX1N

C2

GFX_RX2P

C1

GFX_RX2N

E5

GFX_RX3P

F5

GFX_RX3N

G5

GFX_RX4P

G6

GFX_RX4N

H5

GFX_RX5P

H6

GFX_RX5N

J6

GFX_RX6P

J5

GFX_RX6N

J7

GFX_RX7P

J8

GFX_RX7N

L5

GFX_RX8P

L6

GFX_RX8N

M8

GFX_RX9P

L8

GFX_RX9N

P7

GFX_RX10P

M7

GFX_RX10N

P5

GFX_RX11P

M5

GFX_RX11N

R8

GFX_RX12P

P8

GFX_RX12N

R6

GFX_RX13P

R5

GFX_RX13N

P4

GFX_RX14P

P3

GFX_RX14N

T4

GFX_RX15P

T3

GFX_RX15N

AE3

GPP_RX0P

AD4

GPP_RX0N

AE2

GPP_RX1P

AD3

GPP_RX1N

AD1

GPP_RX2P

AD2

GPP_RX2N

V5

GPP_RX3P

W6

GPP_RX3N

U5

GPP_RX4P

U6

GPP_RX4N

U8

GPP_RX5P

U7

GPP_RX5N

AA8

SB_RX0P

Y8

SB_RX0N

AA7

SB_RX1P

Y7

SB_RX1N

AA5

SB_RX2P

AA6

SB_RX2N

W5

SB_RX3P

Y5

SB_RX3N

RS880M

RS880M

HT_CPU_NB_CAD_H08

HT_CPU_NB_CAD_L08

HT_CPU_NB_CAD_H18

HT_CPU_NB_CAD_L18

HT_CPU_NB_CAD_H28

HT_CPU_NB_CAD_L28

HT_CPU_NB_CAD_H38

HT_CPU_NB_CAD_L38

HT_CPU_NB_CAD_H48

HT_CPU_NB_CAD_L48

HT_CPU_NB_CAD_H58

HT_CPU_NB_CAD_L58

HT_CPU_NB_CAD_H68

HT_CPU_NB_CAD_L68

HT_CPU_NB_CAD_H78

HT_CPU_NB_CAD_L78

HT_CPU_NB_CAD_H88

HT_CPU_NB_CAD_L88

HT_CPU_NB_CAD_H98

HT_CPU_NB_CAD_L98

HT_CPU_NB_CAD_H108

HT_CPU_NB_CAD_L108

HT_CPU_NB_CAD_H118

HT_CPU_NB_CAD_L118

HT_CPU_NB_CAD_H128

HT_CPU_NB_CAD_L128

HT_CPU_NB_CAD_H138

HT_CPU_NB_CAD_L138

HT_CPU_NB_CAD_H148

HT_CPU_NB_CAD_L148

HT_CPU_NB_CAD_H158

HT_CPU_NB_CAD_L158

HT_CPU_NB_CLK_H08

HT_CPU_NB_CLK_L08

HT_CPU_NB_CLK_H18

HT_CPU_NB_CLK_L18

HT_CPU_NB_CTL_H08

HT_CPU_NB_CTL_L08

HT_CPU_NB_CTL_H18

HT_CPU_NB_CTL_L18

RN25 301_1%

RN25 301_1%

0402

0402

5

PART 2 OF 6

PART 2 OF 6

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

I

I

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

PCIE I/F GFX

PCIE I/F GFX

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

SB_TX3N

UN3A

UN3A

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

AC24

AC25

AB25

AB24

AA24

AA25

Y22

Y23

W21

W20

V21

V20

U20

U21

U19

U18

T22

T23

AB23

AA22

M22

M23

R21

R20

HT_RXCALP HT_TXCALP

C23

HT_RXCALN

A24

RS880M

RS880M

B5

A4

B4

C3

B2

D1

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

AC1

AC2

AB4

AB3

AA2

AA1

Y1

Y2

Y4

Y3

V1

V2

AD7

AE7

AE6

AD6

AB6

AC6

AD5

AE5

AC8

AB8

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

PEG_TXP15

PEG_TXN14

PEG_TXP14

PEG_TXN13

PEG_TXP13

PEG_TXN12

PEG_TXP12

PEG_TXN11

PEG_TXP11

PEG_TXN10

PEG_TXP10

PEG_TXN9

PEG_TXP9

PEG_TXN8

PEG_TXP8

PEG_TXN7

PEG_TXP7

PEG_TXN6

PEG_TXP6

PEG_TXN5

PEG_TXP5

PEG_TXN4

PEG_TXP4

PEG_TXN3

PEG_TXP3

PEG_TXN2

PEG_TXP2

PEG_TXN1

PEG_TXP1

PEG_TXN0

PEG_TXP0

PCIE_TXP1

PCIE_TXN1

PCIE_TXP3

PCIE_TXN3

A_Link_TXP0

A_Link_TXN0

A_Link_TXP1

A_Link_TXN1

A_Link_TXP2

A_Link_TXN2

A_Link_TXP3

A_Link_TXN3

PCE_CALRP

PCE_CALRN

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

PEG_TXN15

A5

4

Dis GPU(M93 XT):Not Install

PX;UMA:Install

CN62 100nF_X5R_10V 0402 ICN62 100nF_X5R_10V 0402 I

CN59 100nF_X5R_10V 0402 ICN59 100nF_X5R_10V 0402 I

CN58 100nF_X5R_10V 0402 ICN58 100nF_X5R_10V 0402 I

CN54 100nF_X5R_10V 0402 ICN54 100nF_X5R_10V 0402 I

CN111 100nF_X5R_10V 0402 NICN111 100nF_X5R_10V 0402 NI

CN109 100nF_X5R_10V 0402 NICN109 100nF_X5R_10V 0402 NI

CN107 100nF_X5R_10V 0402 NICN107 100nF_X5R_10V 0402 NI

CN105 100nF_X5R_10V 0402 NICN105 100nF_X5R_10V 0402 NI

CN103 100nF_X5R_10V 0402 NICN103 100nF_X5R_10V 0402 NI

CN101 100nF_X5R_10V 0402 NICN101 100nF_X5R_10V 0402 NI

CN99 100nF_X5R_10V 0402 NICN99 100nF_X5R_10V 0402 NI

CN97 100nF_X5R_10V 0402 NICN97 100nF_X5R_10V 0402 NI

CN95 100nF_X5R_10V 0402 ICN95 100nF_X5R_10V 0402 I

CN93 100nF_X5R_10V 0402 ICN93 100nF_X5R_10V 0402 I

CN91 100nF_X5R_10V 0402 ICN91 100nF_X5R_10V 0402 I

CN89 100nF_X5R_10V 0402 ICN89 100nF_X5R_10V 0402 I

CN87 100nF_X5R_10V 0402 ICN87 100nF_X5R_10V 0402 I

CN85 100nF_X5R_10V 0402 ICN85 100nF_X5R_10V 0402 I

CN83 100nF_X5R_10V 0402 ICN83 100nF_X5R_10V 0402 I

CN81 100nF_X5R_10V 0402 ICN81 100nF_X5R_10V 0402 I

CN80 100nF_X5R_10V 0402 ICN80 100nF_X5R_10V 0402 I

CN79 100nF_X5R_10V 0402 ICN79 100nF_X5R_10V 0402 I

CN12 100nF_X5R_10V 0402 ICN12 100nF_X5R_10V 0402 I

CN14 100nF_X5R_10V 0402 ICN14 100nF_X5R_10V 0402 I

CN72 100nF_X5R_10V 0402 ICN72 100nF_X5R_10V 0402 I

CN73 100nF_X5R_10V 0402 ICN73 100nF_X5R_10V 0402 I

CN75 100nF_X5R_10V 0402 ICN75 100nF_X5R_10V 0402 I

CN77 100nF_X5R_10V 0402 ICN77 100nF_X5R_10V 0402 I

RN11 1.27K_1%

0402

0402

RN12

RN12

0402

0402

2K_1%

I

2K_1%

I

D24

HT_TXCAD0P

D25

HT_TXCAD0N

E24

HT_TXCAD1P

E25

HT_TXCAD1N

F24

HT_TXCAD2P

F25

HT_TXCAD2N

F23

HT_TXCAD3P

F22

HT_TXCAD3N

H23

HT_TXCAD4P

H22

HT_TXCAD4N

J25

HT_TXCAD5P

J24

HT_TXCAD5N

K24

HT_TXCAD6P

K25

HT_TXCAD6N

K23

HT_TXCAD7P

K22

HT_TXCAD7N

F21

HT_TXCAD8P

G21

HT_TXCAD8N

G20

HT_TXCAD9P

H21

HT_TXCAD9N

J20

HT_TXCAD10P

J21

HT_TXCAD10N

J18

HT_TXCAD11P

K17

HT_TXCAD11N

L19

HT_TXCAD12P

J19

HT_TXCAD12N

M19

HT_TXCAD13P

L18

HT_TXCAD13N

M21

HT_TXCAD14P

P21

HT_TXCAD14N

P18

HT_TXCAD15P

M18

HT_TXCAD15N

H24

HT_TXCLK0P

H25

HT_TXCLK0N

L21

HT_TXCLK1P

L20

HT_TXCLK1N

M24

HT_TXCTL0P

M25

HT_TXCTL0N

P19

HT_TXCTL1P

R18

HT_TXCTL1N

B24

HT_TXCALP

HT_TXCALN

HT_TXCALN

B25

4

CN63 100nF_X5R_10V 0402 ICN63 100nF_X5R_10V 0402 I

CN61 100nF_X5R_10V 0402 ICN61 100nF_X5R_10V 0402 I

CN60 100nF_X5R_10V 0402 ICN60 100nF_X5R_10V 0402 I

CN56 100nF_X5R_10V 0402 ICN56 100nF_X5R_10V 0402 I

Dis GPU(M93 XT):Install

PX:CN81-CN96 Install

UMA:CN81-CN96 Not Install

CN71 100nF_X5R_10V 0402 ICN71 100nF_X5R_10V 0402 I

CN74 100nF_X5R_10V 0402 ICN74 100nF_X5R_10V 0402 I

CN76 100nF_X5R_10V 0402 ICN76 100nF_X5R_10V 0402 I

CN78 100nF_X5R_10V 0402 ICN78 100nF_X5R_10V 0402 I

+V1.1S

IRN11 1.27K_1%

I

RN27 301_1%

RN27 301_1%

0402

0402

CN112 100nF_X5R_10V 0402 NICN112 100nF_X5R_10V 0402 NI

CN110 100nF_X5R_10V 0402 NICN110 100nF_X5R_10V 0402 NI

CN108 100nF_X5R_10V 0402 NICN108 100nF_X5R_10V 0402 NI

CN106 100nF_X5R_10V 0402 NICN106 100nF_X5R_10V 0402 NI

CN104 100nF_X5R_10V 0402 NICN104 100nF_X5R_10V 0402 NI

CN102 100nF_X5R_10V 0402 NICN102 100nF_X5R_10V 0402 NI

CN100 100nF_X5R_10V 0402 NICN100 100nF_X5R_10V 0402 NI

CN98 100nF_X5R_10V 0402 NICN98 100nF_X5R_10V 0402 NI

CN96 100nF_X5R_10V 0402 ICN96 100nF_X5R_10V 0402 I

CN94 100nF_X5R_10V 0402 ICN94 100nF_X5R_10V 0402 I

CN92 100nF_X5R_10V 0402 ICN92 100nF_X5R_10V 0402 I

CN90 100nF_X5R_10V 0402 ICN90 100nF_X5R_10V 0402 I

CN88 100nF_X5R_10V 0402 ICN88 100nF_X5R_10V 0402 I

CN86 100nF_X5R_10V 0402 ICN86 100nF_X5R_10V 0402 I

CN84 100nF_X5R_10V 0402 ICN84 100nF_X5R_10V 0402 I

CN82 100nF_X5R_10V 0402 ICN82 100nF_X5R_10V 0402 I

HT_NB_CPU_CAD_H0 8

HT_NB_CPU_CAD_L0 8

HT_NB_CPU_CAD_H1 8

HT_NB_CPU_CAD_L1 8

HT_NB_CPU_CAD_H2 8

HT_NB_CPU_CAD_L2 8

HT_NB_CPU_CAD_H3 8

HT_NB_CPU_CAD_L3 8

HT_NB_CPU_CAD_H4 8

HT_NB_CPU_CAD_L4 8

HT_NB_CPU_CAD_H5 8

HT_NB_CPU_CAD_L5 8

HT_NB_CPU_CAD_H6 8

HT_NB_CPU_CAD_L6 8

HT_NB_CPU_CAD_H7 8

HT_NB_CPU_CAD_L7 8

HT_NB_CPU_CAD_H8 8

HT_NB_CPU_CAD_L8 8

HT_NB_CPU_CAD_H9 8

HT_NB_CPU_CAD_L9 8

HT_NB_CPU_CAD_H10 8

HT_NB_CPU_CAD_L10 8

HT_NB_CPU_CAD_H11 8

HT_NB_CPU_CAD_L11 8

HT_NB_CPU_CAD_H12 8

HT_NB_CPU_CAD_L12 8

HT_NB_CPU_CAD_H13 8

HT_NB_CPU_CAD_L13 8

HT_NB_CPU_CAD_H14 8

HT_NB_CPU_CAD_L14 8

HT_NB_CPU_CAD_H15 8

HT_NB_CPU_CAD_L15 8

HT_NB_CPU_CLK_H0 8

HT_NB_CPU_CLK_L0 8

HT_NB_CPU_CLK_H1 8

HT_NB_CPU_CLK_L1 8