Page 1

A

1 1

2 2

B

C

D

E

Compal confidential

Schematics Docu ment

Mobile Auburndale rPGA989 with

3 3

4 4

A

Intel PCH(Ibex Peak-M) core logic

2009-04-13

Secur i t y Classification

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

http://laptop-motherboard-schematic.blogspot.com/

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

C

2007/08/28 2006/03/10

Compal Secret Data

Dec iphered Date

Title

Size Document Number Re v

Custom

D

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

Cal p el la D I S L A4743P

0.1

of

149Monday, April 13, 2009

E

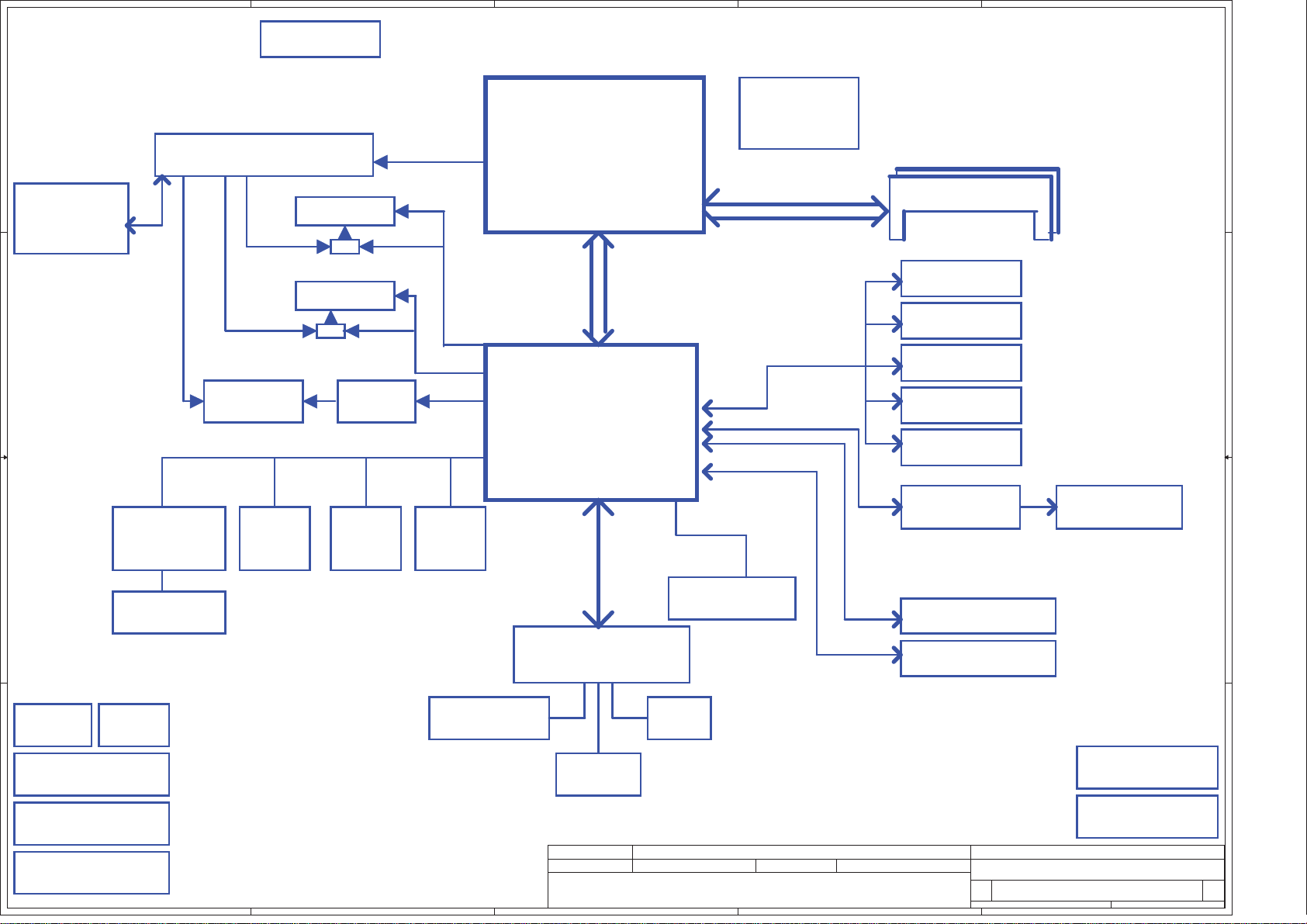

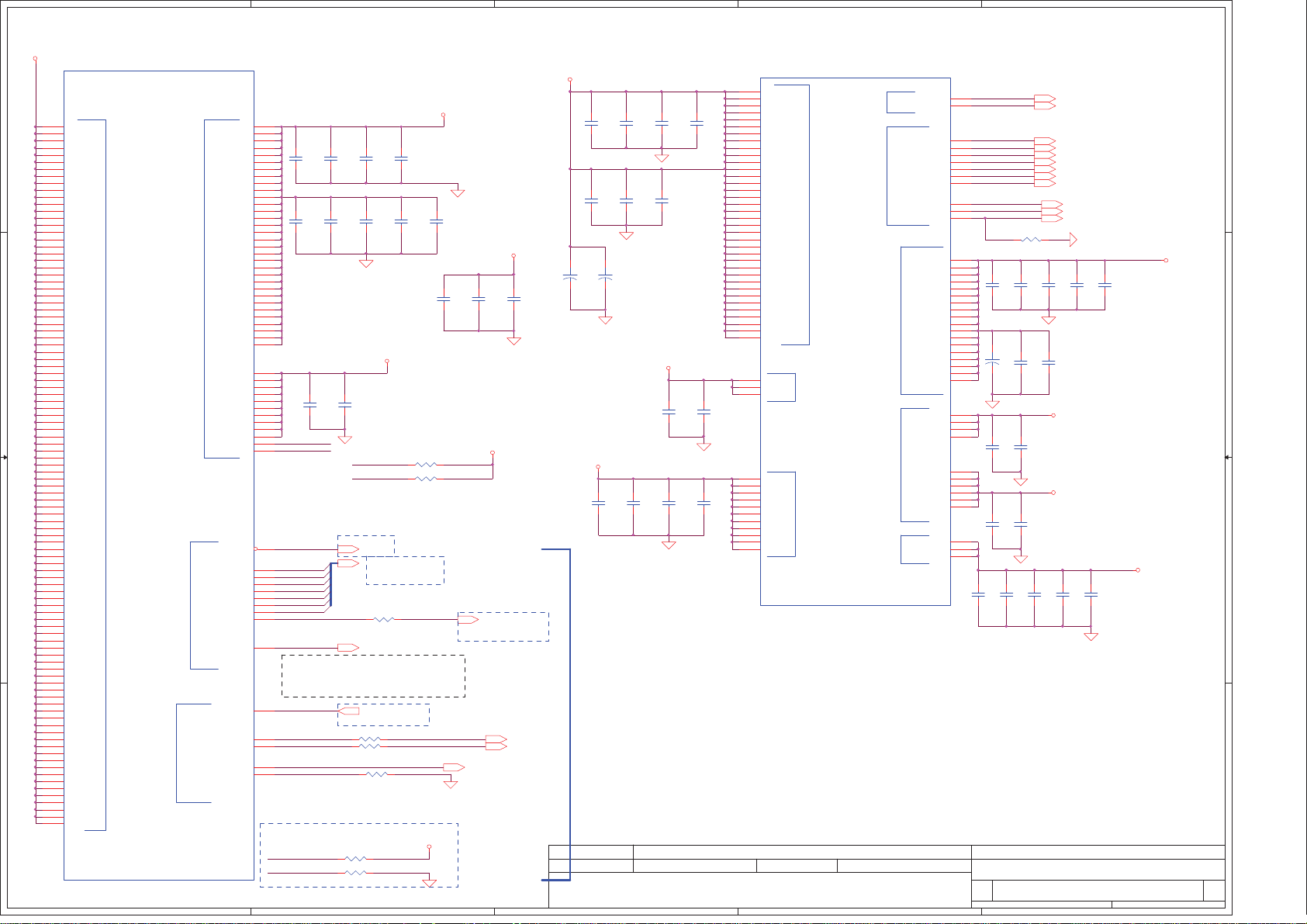

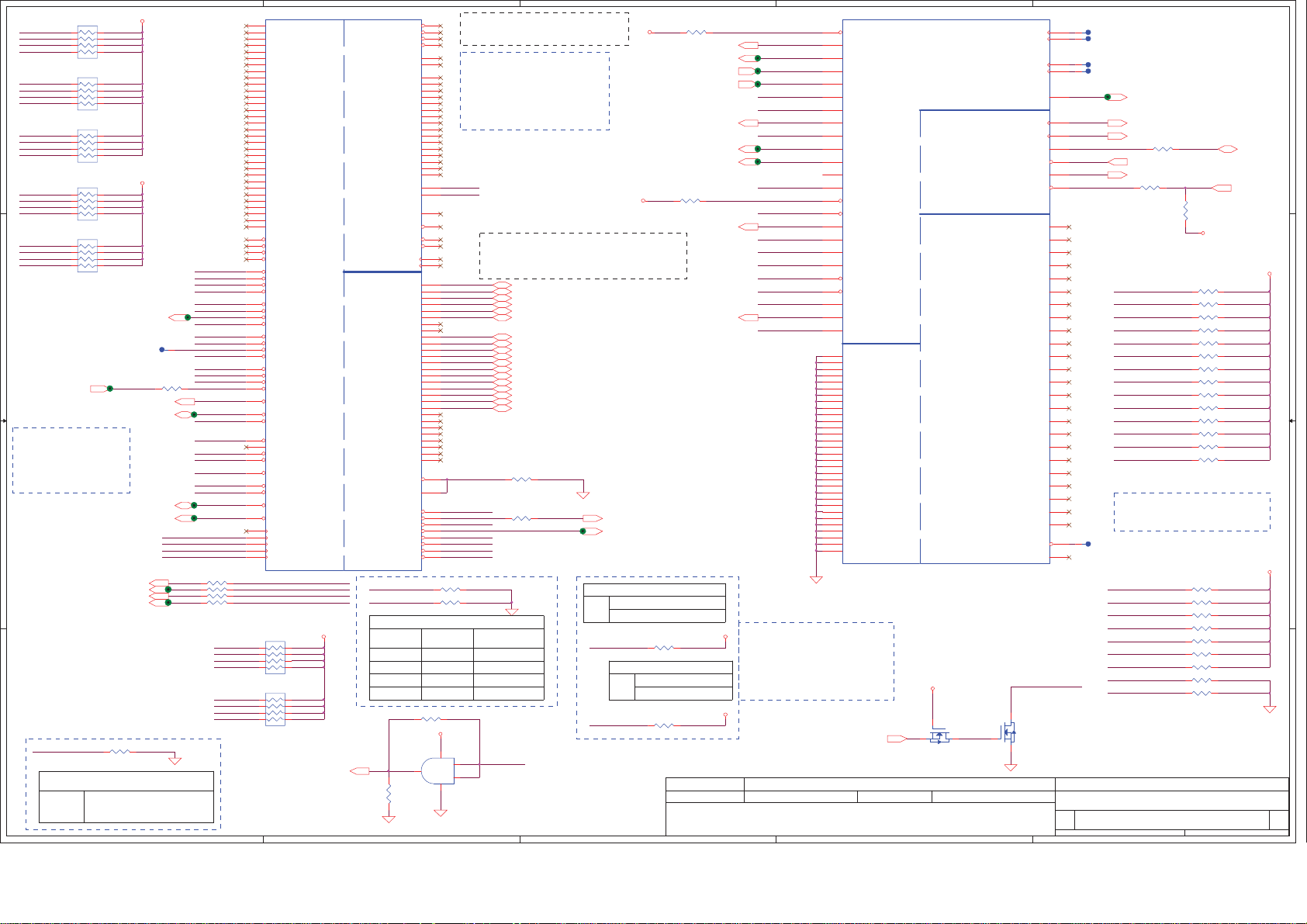

Page 2

A

B

C

D

E

Compal confidential

1 1

Nv id ia

NB10M-GE

VRAM DDR3

128/512MB

page 28,29

2 2

Dis

HDMI Conn.

PCI-E BUS*4

Fan conn

page 24,25,26,27

Dis Dis(UMA)

Page 6

LCD Conn.

page 21

MUX

CRT

page 20

MUX

Dis(UMA)Dis

Level Shifter

page 23

page 23

Calpella Consumer 13.3" UMA +Switchable

USB2.0 X12

32QFN

P19

DDR 3 S O- D IMM X2

BANK 0, 1, 2, 3

USB Card Reader

USB conn x3

BT Conn

USB Camera

Finger print

PCIE-Express 16X

UMA

UMA

UMA

Mobile Arrandale

2C CPU + GMCH

Socket-rPGA989

Page 6,7,8,9,10

DMI X4

Intel PCH

Ibex Peak-M

FCBGA 951

Page 11,12,13,14,15,16

CK505

Clock Generator

SLG8SP585VTR

DDR3 1066/1333 MHz 1.5V

Dual Channel

Azalia

SATA Master-1

SATA Slave

P17, 18

P33

P36

P36

P21

P36

Audio CKT

JMC261 (LAN

+Card reader)

3 3

Mini-Card

WLAN

P31

RJ45/11 CONN

P31

Mini-Card

WWAN

P32P32 P32

New Card

LPC BUS

SPI

SPI ROM 16M

P34

MX25L1605AM2C-15G

SATA HDD Connector

Codec_IDT92HD81

P34 P35

Audio Jack

P30

ENE

KB926

P38

SATA ODD Connector

P30

C

P37

Int.KBD

P38

2006/02/13 2006/03/10

Compal Secret Data

Dec iphered Date

D

USB B o ard Conn

USB conn x2

Capsense switch Conn

Title

Size Document Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Cal p el la D I S L A4743P

E

249Monday, April 13, 2009

P33

P36

of

0.1

RTC CKT.

P21

LED

P36

ACC E LEROMETER

ST

4 4

P27

Touch Pad CONN.

P39

SPI ROM

SST25VF080

K/B b ac k light Conn

P36

Secur i t y C lassification

DC/DC Interface CKT.

P38

A

http://laptop-motherboard-schematic.blogspot.com/

B

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

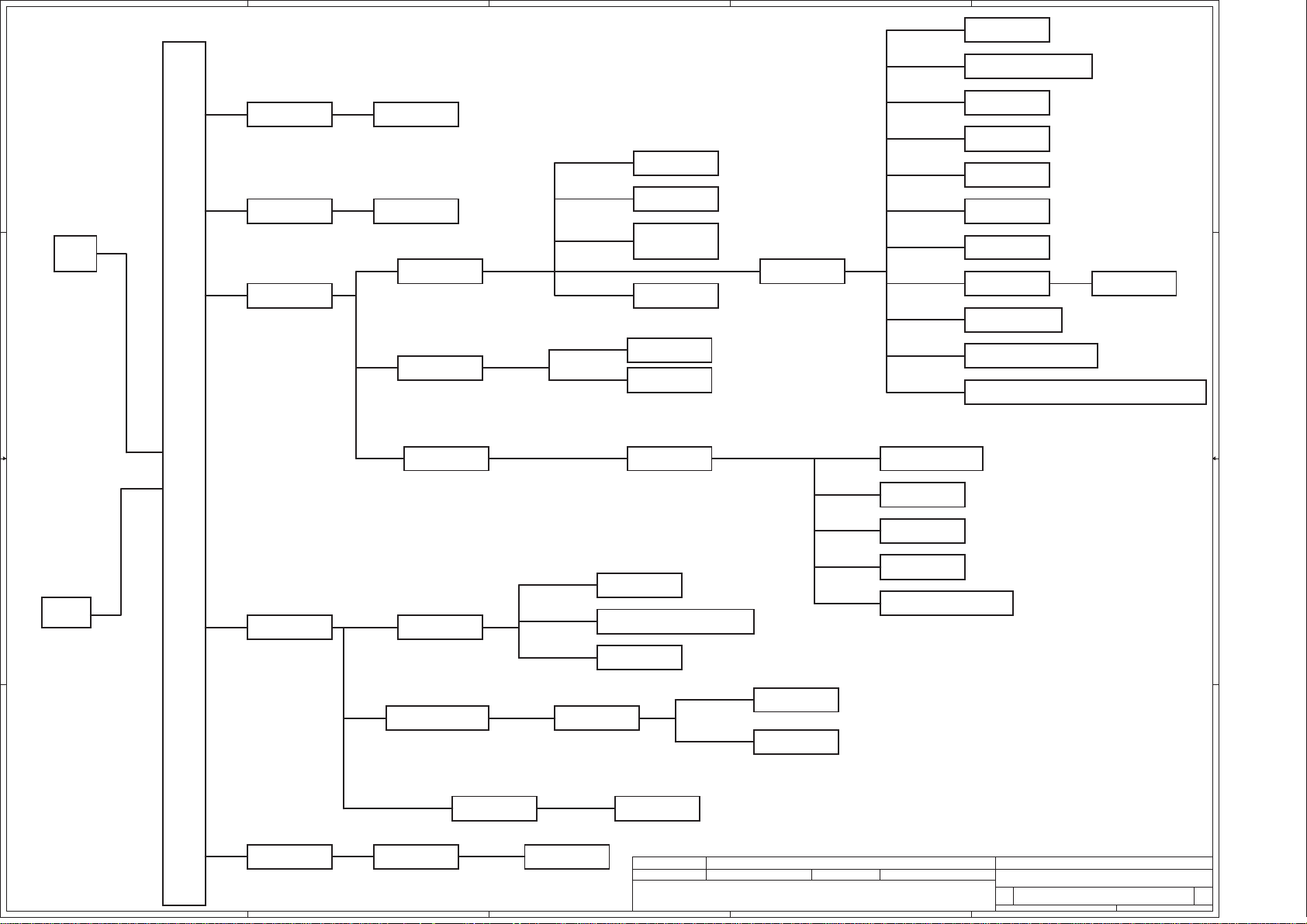

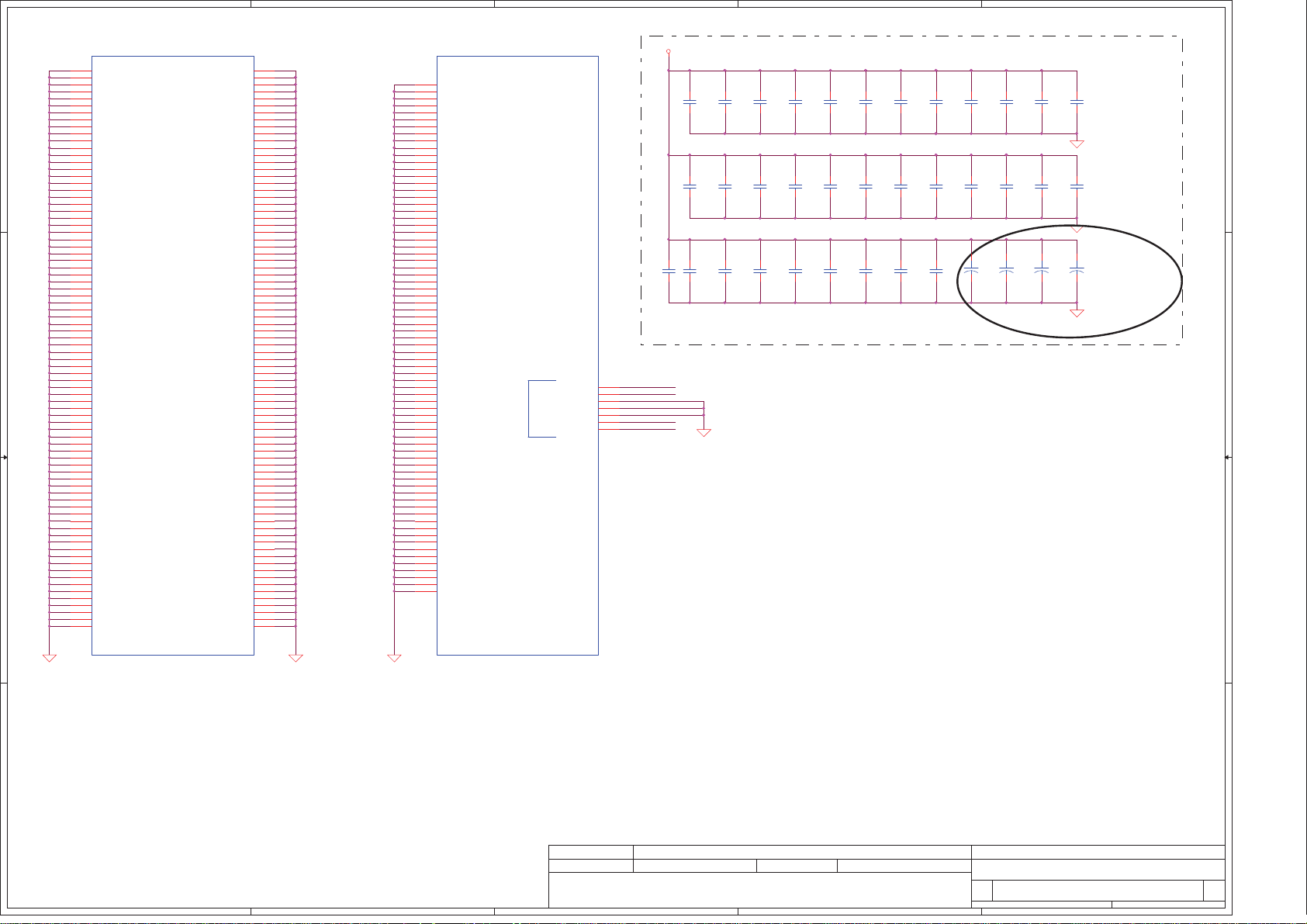

Page 3

A

Symbol Note :

Voltage Rails

power

plane

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Batt ery

don't exist

1 1

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

KB926

KB926

PCH

PCH

PCH

O MEANS ON X MEANS OFF

+B

O

O

O

O

O

+5VALW

+3VALW

O

O

O

O

X

XX

XDP BATT

X V

X

V

X

Thermal

Sensor

X

X

X

X

X

X

X

+1.8V

+5VS

+3VS

+1.5VS

+0.9V

+VCCP

+CPU_CORE

+2.5VS

+1.8VS

O

O

O

X

X

X

SODIMM CLK CHIP

X

X

WLAN

WWAN

X

X

X

X

VVV

X

X

X

+3VALW +3VALW+3VS+3VS+3VS +3VS+5VL +5VL

O

O

X

X

X

X

NB10M

Thermal

Sensor

X

XX

X

X

X

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

45@ : means need be mounted when 45 level assy or rework stage.

BATT @ : means need be mounted when 45 level assy or rework stage.

CONN@ : means ME part

SG@ : means stuff when Switchable graphic

UMA@ : means stuf f when UM A skus

VRAM@ : X76 level

8111DL@ : Only for Giga LAN

DE B UG@ : For debug

Cypress@ : Only For Cypress Capacito r sensor board

ENE@ : Only For ENE Capacitor sensor board

M3@ : Only For Intel DDR3 V RE F

PA@ : Only For PA

PR@ : Only For PR

NB10M-GE

X

X

X

Cap sensor

board

NEW

G sensor

CARD

V

X

X

X

XX

X

X

VV

X

X

XXXXXXXXX X

PCH I2C / SMBUS ADDRESSING

DEVICE

DDR SO-DIMM 0

DDR SO-DIMM 1

CLOCK GENERATOR (EXT.)

45172932L01ΚSwitchable graphic

45172932L02ΚUMA only

USB assignment:

USB-0 Right side

USB-1 Right side

USB-2 Left side(with ESATA)

USB-3 X

USB-4 Camera

USB-5 WLAN

USB-6 Bluetooth

USB-7 F i nger Printer

USB - 8 M iniCard (WW AN/T V)

USB-9 Express card

USB-10 X

USB-11 X

PCIe assignment:

PCIe-1 WWAN

PCIe- 2 WLAN

PCIe- 3 LAN

PCIe-4 New card

PCIe- 5 X

PCIe- 6 X

SATA assignment:

SATA0 HDD

SATA1 ODD

SATA2 X

SATA3 X

SAT A4 ESATA

SATA5 X

HEX

A0

D2

ADDRESS

1 0 1 0 0 0 0 0

1 0 1 0 0 1 0 0A4

1 1 0 1 0 0 1 0

NB10M -GE SMBUS Control Table

D_EDID_DATA

D_EDID_CLK

D_CRT_DDC_DATA

D_CRT_DDC_DATA

HDMIDAT_VGA

HDMICLK_VGA

SOURCE LVDS CRT

NB10M

NB10M

NB10M

V

X

X

HDMI

XX

X

V

X

V

Secur i t y C lassification

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

http://laptop-motherboard-schematic.blogspot.com/

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

A

2007/08/28 2006/03/10

Compal Secret Data

Dec iphered Date

Title

Size Do c ument Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Notes List

Cal p el la D I S L A4743P

of

349Monday, April 13, 2009

0.1

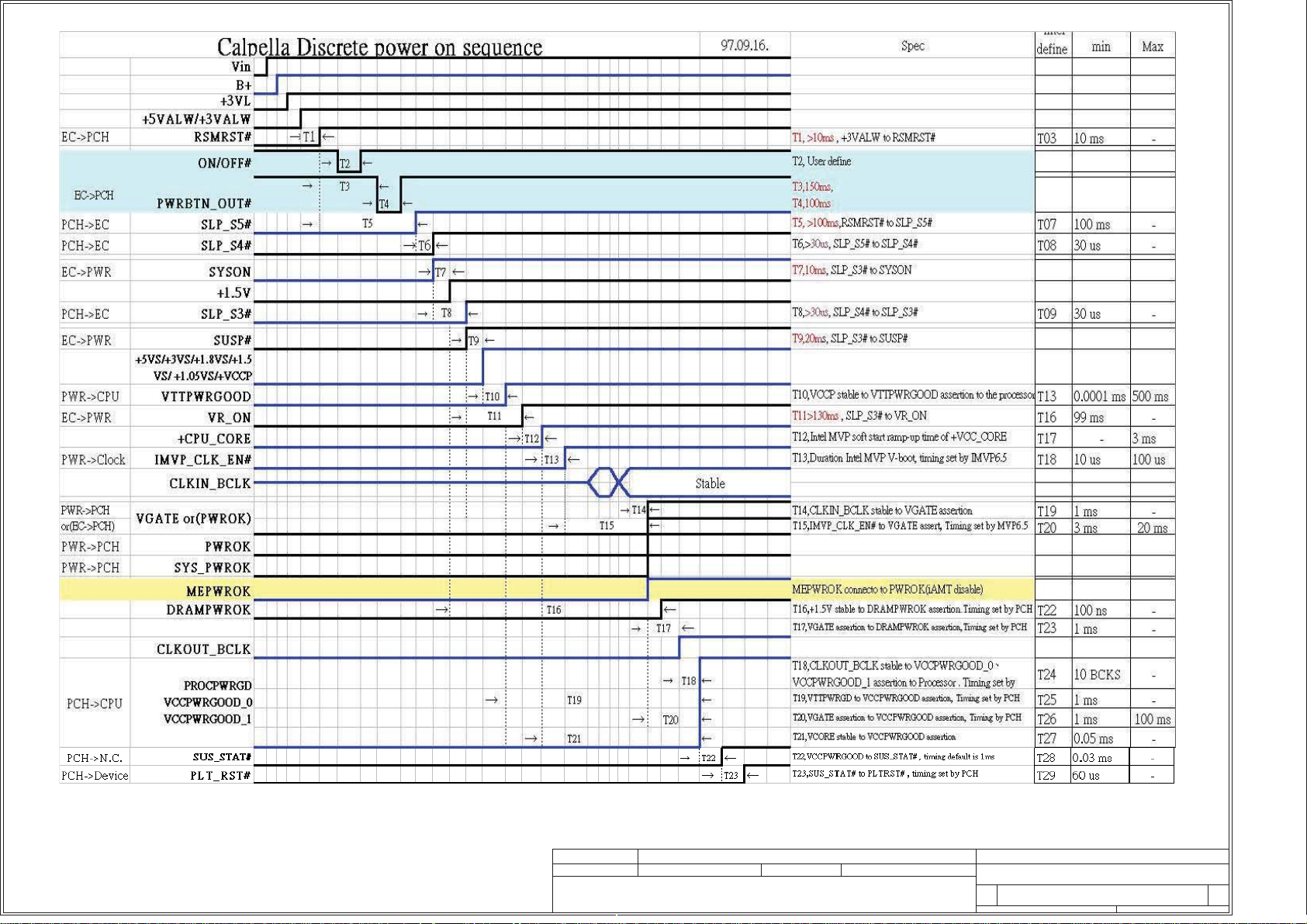

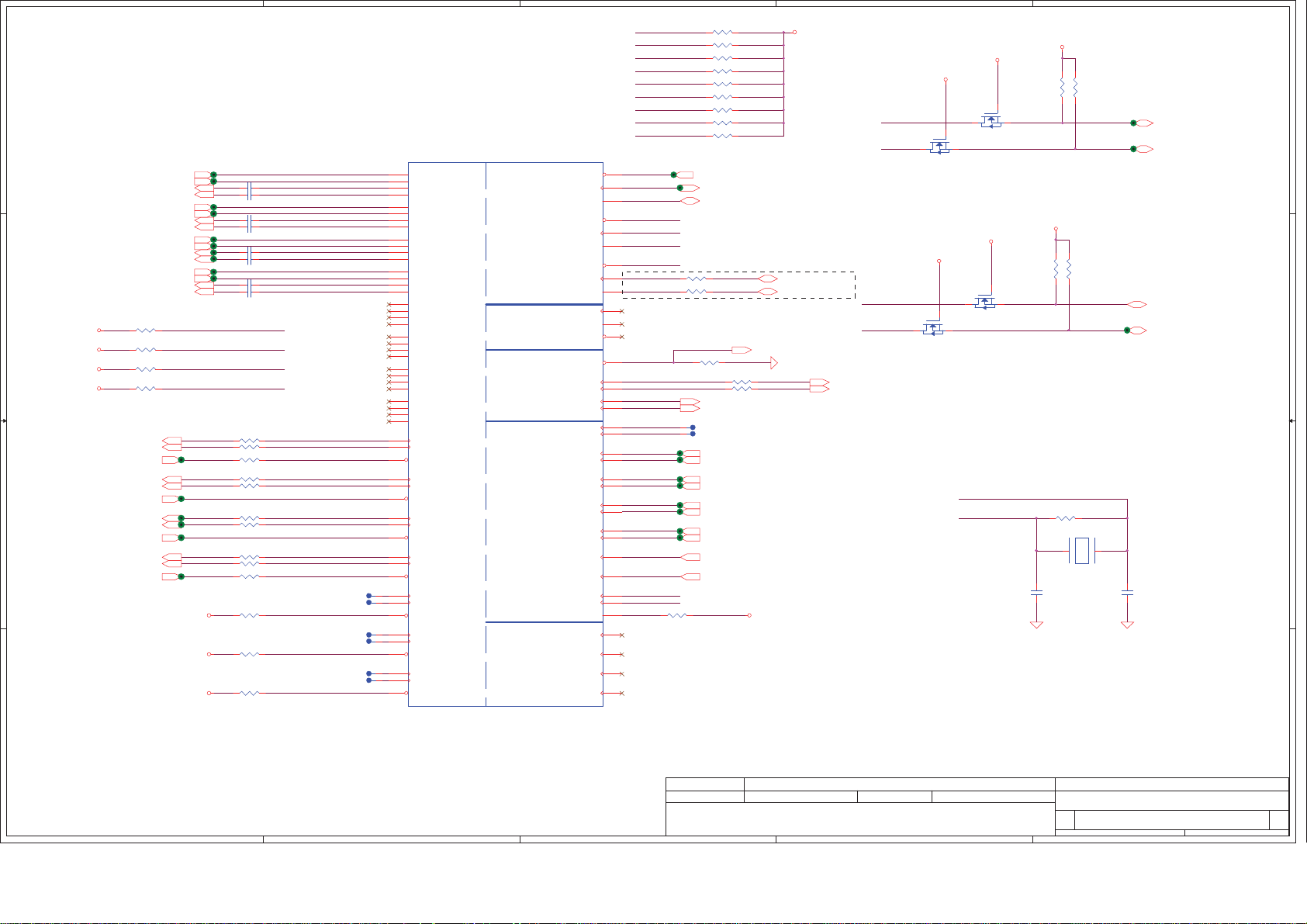

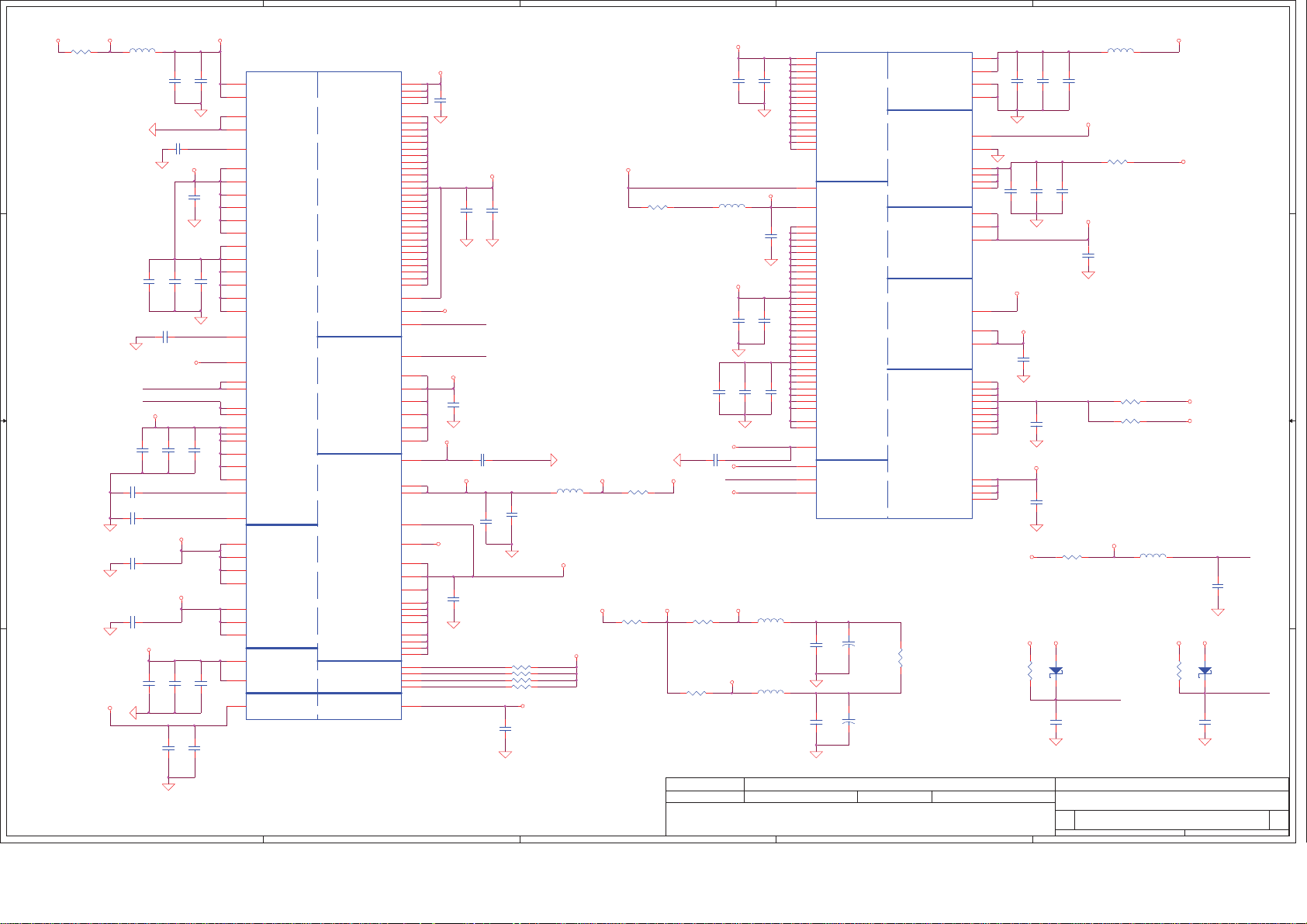

Page 4

5

4

3

2

60mA

+3VAUX_BT

1

50mA

1A

D D

VIN

AC

C C

B+

7A

+V_BATTERY Dock con

0.3A

INVPWR_B+

2A

B++

LVDS CON

1.7A

+3VALW

+1.5VS

+5VALW

35mA

169mA

300mA

MDC 1.5

ICH9

LAN

3.39A5.89A

+3VS

RT5158

??mA

???A

1.3A0.58A

Mini card

New card

+5VS

35mA

10mA

25mA

20mA

10mA

1A

811mA

1.5A

250mA

1A

1A

+VDDA

IDT 9271B7

+5VAMP

Finger printer

+3VS_DVDD

ALC268

+3VALW_EC

SPI ROM

New card

PCH

+LCDVDD

LVDS CON

+3VS_CK505

Mini card (WLAN)

Mini card (TV tu/WWAN/Robeson)

1.8A

B B

3.7 X 3=11.1V

DC

BATT

B+++

A A

CPU_B+ +VCC_CORE

5

11.05A1.9A

4.7A

+1.5V

1.05V_B+

+1.05VS PCH

10mA2A

http://laptop-motherboard-schematic.blogspot.com/

4

38A/1.05V

3A

8 A

50mA

+VCCP

2.59A

CPU

CPU

DDR3 800Mhz 4G x2

+0.75V

162mA

??A

Securi ty Classification

Issued Date

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPER TY OF COMPAL ELECTR ONI CS, INC . AN D C ONT AINS CO NFID ENTI AL

AND TRADE SECRET INFORMATION. THIS SH EET MAY NOT BE TRANSFERED FRO M TH E CU STO DY O F TH E CO MPET ENT DIVI SIO N O F R& D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHE R TH IS SHEE T NO R TH E I NFOR MATI ON IT C ONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CON SENT OF COM PAL ELEC TRO NIC S, I NC.

3

PCH

CPU

2007/08/28 2006/03/10

700mA

50mA

Compal Secret Data

Dec iphered Date

ODD

SATA

PC Camera(4.75V)

2

Compal Electronics, Inc.

Title

Size Document Number Re v

C

Calpella DIS LA4743P

Date: Sheet

Pow e r d elevry

1

449Mond ay, April 13, 2009

of

0.1

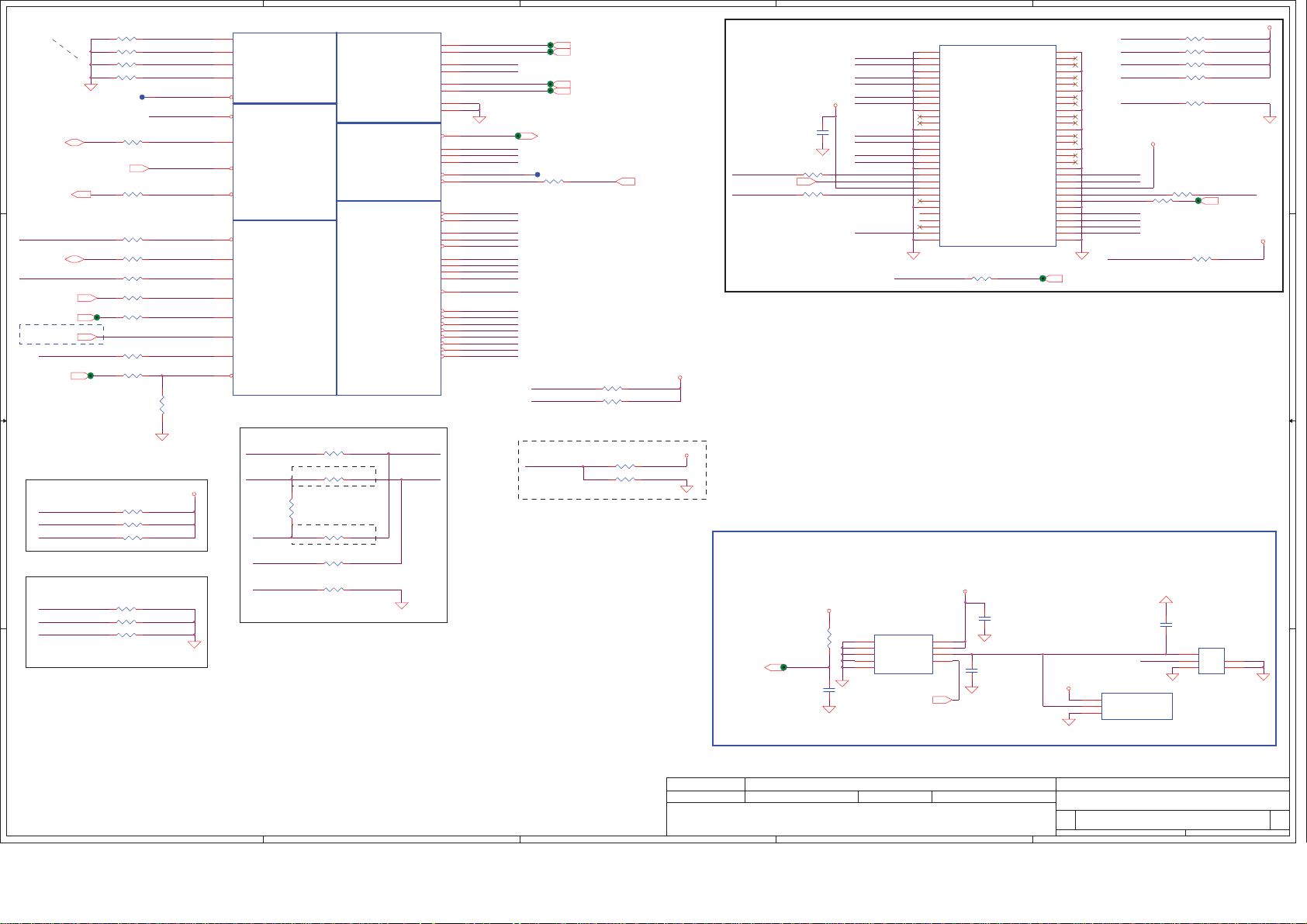

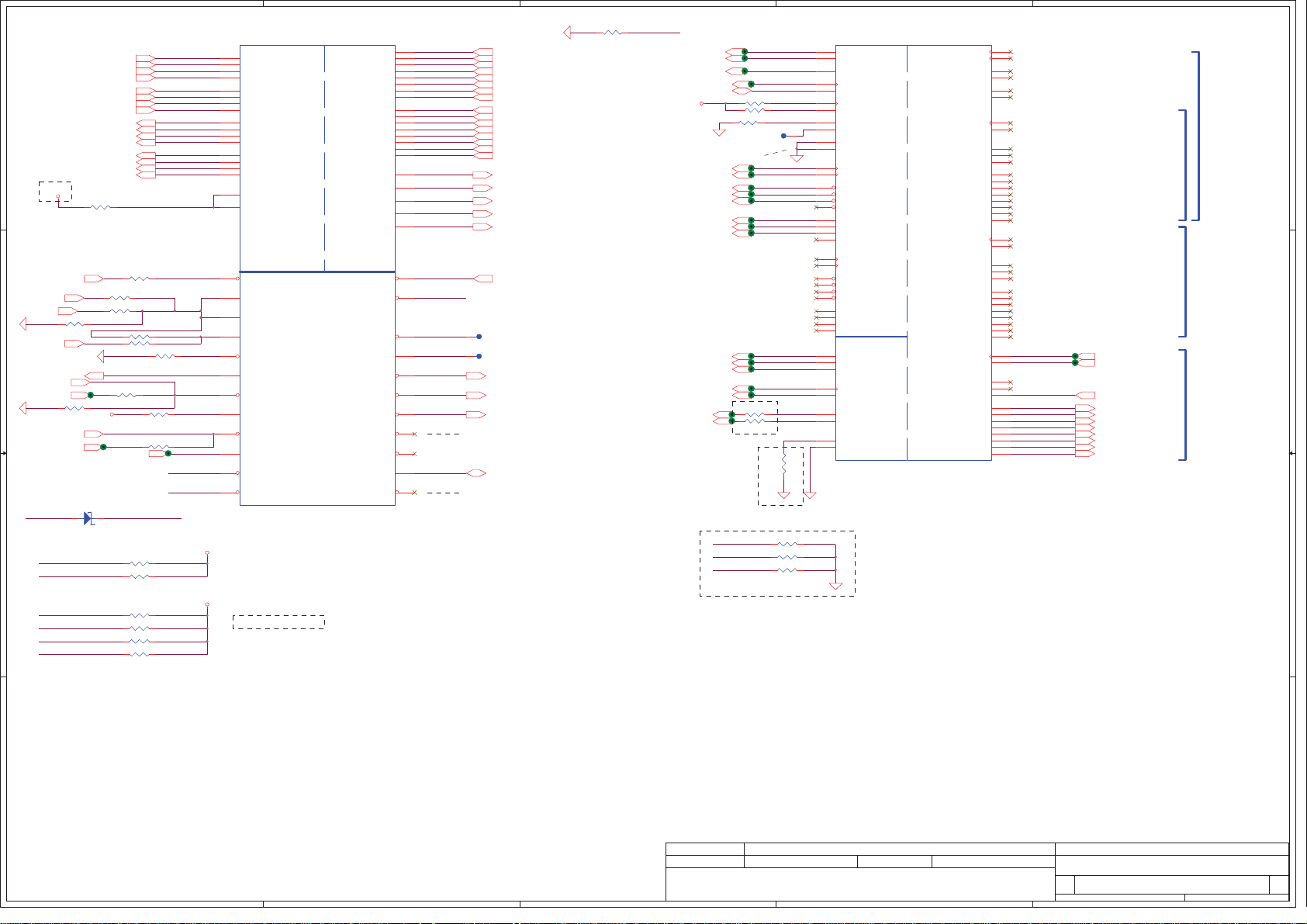

Page 5

A

1 1

Secur i t y C lassification

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

http://laptop-motherboard-schematic.blogspot.com/

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

A

2007/08/28 2006/03/10

Compa l Secret Data

Dec iphered Date

Title

Size Do c ument Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Notes List

Cal p el la D I S L A4743P

of

549Monday, April 13, 2009

0.1

Page 6

Layout rule 10mΚil

width trace length <

0.5", spacing 20mil

D D

H_PECI<14>

H_PROCHOT#<46>

H_THERMTRIP#<14>

H_CPURST#

H_PM_SYNC<13>

H_CPUPWRGD

H_CPUPWRGD<14>

PM_DRAM_PWRGD<13>

C C

From power

VTTPWR GOOD<44>

BU F _ PLT_ RS T#<14>

5

R1 20_0402_1%

1 2

R3 20_0402_1%

1 2

R5 49.9_0402_1%

1 2

R7 49.9_0402_1%

1 2

TP_ S KTOCC#

T1PAD

H_C A TE RR#

R10

1 2

R15

1 2

R19

1 2

R20

1 2

R21

1 2

R23

1 2

R24

1 2

R25

1 2

R26

1 2

1.5K_0402_1%

750_0402_1%

H_P EC I_ISO

0_0402_5%

H_PROCHOT#

H_THERMTRIP#_R

0_0402_5%

H_CPURST#_R

0_0402_5%

H_PM_SYNC_R

0_0402_5%

SYS_AGENT_PWROK

0_0402_5%

VCCPWRGOOD_0

0_0402_5%

VDDPWRGOOD_R

0_0402_5%

H_ P W R G D _ XDP_RH_PWRGD_XDP

0_0402_5%

PL T_RST# _ R

12

R28

COMP3

COMP2

COMP1

COMP0

JCPU1B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC , A U B _ CF D_r PGA, R1 P0

CONN@

MISC THERMAL

PWR MANAGEMENT

CLOCKS

DDR3

MISC

JTAG & BPM

4

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

3

CLK_CPU_BCLK

A16

CLK_CPU_BCLK#

B16

CLK_CPU_XDP

AR30

CL K _ C PU_XDP#

AT30

CL K_EXP

E16

CL K_EXP#

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

AP28

AT27

AT29

TDI

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

eDP

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PM_EXTTS#0

PM_EXTTS#1

XDP_PRDY#

XDP _PREQ#

XDP_TCK

XDP_TMS

XD P_ TRST#

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

XDP _ D BRESET#

XDP_ BPM#0

XDP_ BPM#1

XDP_ BPM#2

XDP_ BPM#3

XDP_ BPM#4

XDP_ BPM#5

XDP_ BPM#6

XDP_ BPM#7

R14 0_0402_5%

DRAMR ST# <17,18>

T63 P AD

1 2

PM_EXTTS#0

PM_EXTTS#1

CLK_ C PU_BCLK <14>

CLK_CPU_BCLK# <14>

CLK_EXP <12>

CLK_EXP# <12>

R27 10K_0402_5%

R29 10K_0402_5%

1 2

1 2

OK

PM_EXTTS#1_R <17,18>

from DDR

+VCCP

H_CPUPWRGD

PM_PW RB TN#_R<13>

H_PWRGD_XDP

+VCCP

1

C1

@

0.1U_0402_16V4Z

2

R13

1K_0402_5%

1 2

R16 0_0402_5%

1 2

XDP _PREQ#

XDP_PRDY#

XDP_ BPM#0

XDP_ BPM#1

XDP_ BPM#2

XDP_ BPM#3

XDP_ BPM#4

XDP_ BPM#5

XDP_ BPM#6

XDP_ BPM#7

H_CPUPWRGD_R

PM_PWRBTN#_R

2

XDP Connector

JP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030- 01 -L - D-A CO NN@

XDP_RST#_R

R22 0_0402_5%@

1 2

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

GND15

TRST#

GND17

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

TD0

54

56

TDI

58

TMS

60

CLK_CPU_XDP

CL K _ C PU_XDP#

XDP _RST#_R

XDP _ D BRESET#_ R

XDP_TDO

XD P_ TRST#

XDP_TDI

XDP_TMSXDP_TCK

XDP _ D BRESET#

PLT_RST# <14,31,32>

1

XDP_TDI

R2 51_0402_1%@

1 2

R4 51_0402_1%@

XDP_TMS

XDP _PREQ#

XDP_TDO

This shall place near CPU

XDP_TCK

1 2

R6 51_0402_1%@

1 2

R8 51_0402_1%

1 2

R9 51_0402_1%@

1 2

+VCCP

R17

1K_0402_5%

1 2

1 2

R18

0_0402_5%

R603 1K_0402_5%

1 2

H_CPURST#

XDP _ DBRESET# < 13 >

+VCCP

+3VS

JTAG MAPPING

+1.5V

Fan Voltage Control circuit

SI-1 Change to voltage control circuit

+5VS

+3VS

1 2

1

2

U32

9

Thermal P ad

8

GND

7

GND

6

5

VSET

GND

GND

G99 6 RD1U_TDFN8_3X3

FAN_SET<37>

VEN

1

2

VIN

3

VO

4

R678

10K_0402_5%

FAN_SPEED<3 7>

FAN_SPEED

C775

1000P_0402_50V7K

1

C2

2.2U_0603_6.3V4Z

2

1

C774

2.2U_0603_6.3V4Z

2

+5VS_FAN

+5VS

D1

3

Vcc

2

Line to be protect ed

1

GND

DLPT05-7-F_SOT23-3

FAN_SPEED

1

C3

0.1U_0402_16V4Z

2

1

2

3

CONN@

JFAN1

1

4

2

G1

5

3

G2

ACES_85204-03001

XDP_TDI_M

XDP_TDO_R

XD P_ TRST#

R30 0_0402_5%

1 2

R32 0_0402_5%@

1 2

R34

0_0402_5%

1 2

R37 0_0402_5%@

1 2

R38 0_0402_5%

1 2

R39 51_0402_1%

1 2

XDP_TDI

XDP_TDOXDP_TDO_M

VDDPWRGOOD_R

R31 4.75K_0402_1%

R33 12K_0402_1%

CRB 0.9 R38 change to 1K

1 2

1 2

XDP_TDI_R

Processor Pullups

H_CATERR#

H_CPURST#_R

B B

H_PROCHOT#

R35 49.9_0402_1%

1 2

R36 68_0402_5%@

1 2

R11 68_0402_5%

+VCCP

12

DDR3 Compensation Signals

SM_RCOMP0

R40 100_0402_1%

SM_RCOMP1

SM_RCOMP2

Layout Note:Please these

resistors near Processor

A A

1 2

R41 24.9_0402_1%

1 2

R42 130_0402_1%

1 2

Security Classification

Issued Date

THIS SHE E T OF E NGIN EE RI NG DR A W ING I S THE P RO P RIE TAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/03/13 2009/05/11

Compal Secret Data

Deciphered Date

2

Title

Size D o cu ment Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Auburndale(1/5)-Thermal/XDP

Calp ell a DI S L A4 743P

1

649Monday, April 13, 2009

of

0.1

http://laptop-motherboard-schematic.blogspot.com/

Page 7

5

JCPU1A

DMI_CRX_PTX_N0<13>

DMI_CRX_PTX_N1<13>

DMI_CRX_PTX_N2<13>

DMI_CRX_PTX_N3<13>

DMI_CRX_PTX_P0<13>

DMI_CRX_PTX_P1<13>

D D

DMI_CRX_PTX_P2<13>

DMI_CRX_PTX_P3<13>

DMI_CTX_PRX_N0<13>

DMI_CTX_PRX_N1<13>

DMI_CTX_PRX_N2<13>

DMI_CTX_PRX_N3<13>

DMI_CTX _PRX_P0<13>

DMI_CTX _PRX_P1<13>

DMI_CTX _PRX_P2<13>

DMI_CTX _PRX_P3<13>

FDI_CTX_PRX_N0<13>

FDI_CTX_PRX_N1<13>

FDI_CTX_PRX_N2<13>

FDI_CTX_PRX_N3<13>

FDI_CTX_PRX_N4<13>

FDI_CTX_PRX_N5<13>

FDI_CTX_PRX_N6<13>

FDI_CTX_PRX_N7<13>

FDI_CTX_PRX_P0<13>

FDI_CTX_PRX_P1<13>

FDI_CTX_PRX_P2<13>

FDI_CTX_PRX_P3<13>

FDI_CTX_PRX_P4<13>

FDI_CTX_PRX_P5<13>

C C

FDI_CTX_PRX_P6<13>

FDI_CTX_PRX_P7<13>

FD I_FSY NC0<13>

FD I_FSY NC1<13>

FDI_INT<13>

FD I_LSYNC0<13>

FD I_LSYNC1<13>

B B

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

IC,AUB_CFD_rPGA,R1P0

CONN@

DMI Intel(R) FDI

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

4

EXP_ICOMPI

B26

A26

B27

EXP_RBIAS

A25

PCIE_CRX_GTX_N0

K35

PCIE_CRX_GTX_N1

J34

PCIE_CRX_GTX_N2

J33

PCIE_CRX_GTX_N3

G35

PCIE_CRX_GTX_N4

G32

PCIE_CRX_GTX_N5

F34

PCIE_CRX_GTX_N6

F31

PCIE_CRX_GTX_N7

D35

PCIE_CRX_GTX_N8

E33

PCIE_CRX_GTX_N9

C33

PCIE_CRX_GTX_N10

D32

PCIE_CRX_GTX_N11

B32

PCIE_CRX_GTX_N12

C31

PCIE_CRX_GTX_N13

B28

PCIE_CRX_GTX_N14

B30

PCIE_CRX_GTX_N15

A31

PCIE_CRX_GTX_P0

J35

PCIE_CRX_GTX_P1

H34

PCIE_CRX_GTX_P2

H33

PCIE_CRX_GTX_P3

F35

PCIE_CRX_GTX_P4

G33

PCIE_CRX_GTX_P5

E34

PCIE_CRX_GTX_P6

F32

PCIE_CRX_GTX_P7

D34

PCIE_CRX_GTX_P8

F33

PCIE_CRX_GTX_P9

B33

PCIE_CRX_GTX_P10

D31

PCIE_CRX_GTX_P11

A32

PCIE_CRX_GTX_P12

C30

PCIE_CRX_GTX_P13

A28

PCIE_CRX_GTX_P14

B29

PCIE_CRX_GTX_P15

A30

PCIE_CTX_GRX_C_N0

L33

PCIE_CTX_GRX_C_N1

M35

PCIE_CTX_GRX_C_N2

M33

PCIE_CTX_GRX_C_N3

M30

PCIE_CTX_GRX_C_N4

L31

PCIE_CTX_GRX_C_N5

K32

PCIE_CTX_GRX_C_N6

M29

PCIE_CTX_GRX_C_N7

J31

PCIE_CTX_GRX_C_N8

K29

PCIE_CTX_GRX_C_N9

H30

PCIE_CTX_GRX_C_N10

H29

PCIE_CTX_GRX_C_N11

F29

PCIE_CTX_GRX_C_N12

E28

PCIE_CTX_GRX_C_N13

D29

PCIE_CTX_GRX_C_N14

D27

PCIE_CTX_GRX_C_N15

C26

PCIE_CTX_GRX_C_P0

L34

PCIE_CTX_GRX_C_P1

M34

PCIE_CTX_GRX_C_P2

M32

PCIE_CTX_GRX_C_P3

L30

PCIE_CTX_GRX_C_P4

M31

PCIE_CTX_GRX_C_P5

K31

PCIE_CTX_GRX_C_P6

M28

PCIE_CTX_GRX_C_P7

H31

PCIE_CTX_GRX_C_P8

K28

PCIE_CTX_GRX_C_P9

G30

PCIE_CTX _GRX_C_P10

G29

PCIE_CTX _GRX_C_P11

F28

PCIE_CTX _GRX_C_P12

E27

PCIE_CTX _GRX_C_P13

D28

PCIE_CTX _GRX_C_P14

C27

PCIE_CTX _GRX_C_P15

C25

R44 49.9_0402_1%

1 2

R45 750_04 02_1%

1 2

PCIE_CRX _GTX_N[0 ..15] <24>

PCIE_CRX_GTX_P[0..15] <24>

C4 0.1U_0402_16V4ZSG@

1 2

C5 0.1U_0402_16V4ZSG@

1 2

C6 0.1U_0402_16V4ZSG@

1 2

C7 0.1U_0402_16V4ZSG@

1 2

C8 0.1U_0402_16V4ZSG@

1 2

C9 0.1U_0402_16V4ZSG@

1 2

C10 0.1U_0402_16V4ZSG@

1 2

C11 0.1U_0402_16V4ZSG@

1 2

C12 0.1U_0402_16V4ZSG@

1 2

C13 0.1U_0402_16V4ZSG@

1 2

C14 0.1U_0402_16V4ZSG@

1 2

C15 0.1U_0402_16V4ZSG@

1 2

C16 0.1U_0402_16V4ZSG@

1 2

C17 0.1U_0402_16V4ZSG@

1 2

C18 0.1U_0402_16V4ZSG@

1 2

C19 0.1U_0402_16V4ZSG@

1 2

C20 0.1U_0402_16V4ZSG@

1 2

C21 0.1U_0402_16V4ZSG@

1 2

C22 0.1U_0402_16V4ZSG@

1 2

C23 0.1U_0402_16V4ZSG@

1 2

C24 0.1U_0402_16V4ZSG@

1 2

C25 0.1U_0402_16V4ZSG@

1 2

C26 0.1U_0402_16V4ZSG@

1 2

C27 0.1U_0402_16V4ZSG@

1 2

C28 0.1U_0402_16V4ZSG@

1 2

C29 0.1U_0402_16V4ZSG@

1 2

C30 0.1U_0402_16V4ZSG@

1 2

C31 0.1U_0402_16V4ZSG@

1 2

C32 0.1U_0402_16V4ZSG@

1 2

C33 0.1U_0402_16V4ZSG@

1 2

C34 0.1U_0402_16V4ZSG@

1 2

C35 0.1U_0402_16V4ZSG@

1 2

3

Lay out rule trace

length < 0.5"

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_P9

PCIE_CTX _GRX_P10

PCIE_CTX _GRX_P11

PCIE_CTX _GRX_P12

PCIE_CTX _GRX_P13

PCIE_CTX _GRX_P14

PCIE_CTX _GRX_P15

Κ

+V _ DDR_CPU_REF1

PCIE_CT X_GRX_N[0 ..15] <24>

PCIE_CTX_GRX_P[0..15] <24>

R50 0_0402_5%@

R51 0_0402_5%@

1 2

1 2

2

+V _ DDR_CPU_REF0

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

AP25

AL25

AL24

AL22

AJ33

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

AG9

M27

L28

J17

H17

G25

G17

E31

E30

H16

B19

A19

A20

B20

U9

T9

AC9

AB9

C1

A3

J29

J28

A34

A33

C35

B35

JCPU1E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

SA_DIMM_VREF

SB_DIMM_VREF

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD_TP_86

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD_NCT F_23

RSVD_NCT F_24

RSVD26

RSVD27

RSVD_NCT F_28

RSVD_NCT F_29

RSVD_NCT F_30

RSVD_NCT F_31

RESERVED

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD_NCT F_37

RSVD38

RSVD39

RSVD_NCT F_40

RSVD_NCT F_41

RSVD_NCT F_42

RSVD_NCT F_43

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD_NCT F_54

RSVD_NCT F_55

RSVD_NCT F_56

RSVD_NCT F_57

RSVD58

RSVD_TP_59

RSVD_TP_60

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

1

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

KEY

D15

C15

R48 0_0402_5%@

R49 0_0402_5%@

1 2

1 2

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS

IC,AUB_CFD_rPGA,R1P0

CONN@

CFG Straps for PROCESSOR

CFG0

R52 3.01K_0402_1%@

1 2

PCI-Express Configuration Select

1: Single PEG

CFG0

A A

Not applicable for Clarksfield Processor

CFG3

0: B ifurcation enabled

R54 3.01K_0402_1%

1 2

CFG3-PCI Express Static Lane Reversal

CFG3

1: N ormal Operation

0: Lane Numbers Reversed

15 -> 0, 14 ->1, .....

5

*

CFG4

R53 3.01 K_0402_1%@

1 2

CFG4-Display Port Presence

1: Disabled; No Physical

Display Port

attached to Embedded Display Port

0: Enabled; An external

CFG4

Display Port

device is connected to the

Embedded Display Port

CFG7

R55 3.01 K_0402_1%@

Only temporary for early

CFD samples (rPGA/BGA)

Only for pre ES1 sample

1 2

http://laptop-motherboard-schematic.blogspot.com/

4

**

CFG7

WW33GPD 3.01K on CFG7 for PCIE Jitter

Κ

WW41 don't staff

Secur i t y C lassification

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

3

2008/03/13 2009/05/11

Compa l Secret Data

Dec iphered Date

2

Title

Size Document Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Auburndale(2/5)-DMI/PEG/FDI

Cal p el la D I S L A4743P

CRB 0.9 change to GND

of

749Monday, April 13, 2009

1

0.1

Page 8

5

4

3

2

1

AR10

AT10

JCPU1D

W8

SB_CK[0]

W9

SB_CK#[0]

B5

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

DDR SYSTEM MEMORY - B

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_ B _ M A 0

DDR_ B _ M A 1

DDR_ B _ M A 2

DDR_ B _ M A 3

DDR_ B _ M A 4

DDR_ B _ M A 5

DDR_ B _ M A 6

DDR_ B _ M A 7

DDR_ B _ M A 8

DDR_ B _ M A 9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

M_ CLK_DDR2 <18>

M_ CL K_DDR#2 <18>

DDR_CKE2_DIMMB <18>

M_ CLK_DDR3 <18>

M_ CL K_DDR#3 <18>

DDR_CKE3_DIMMB <18>

DDR_CS2_DIMMB# <18>

DDR_CS3_DIMMB# <18>

M_ODT2 <18>

M_ODT3 <18>

DDR _ B_ DM [0 ..7 ] <18>

DDR _ B_ DQS # [0 ..7 ] <18>

DDR_B_DQS[0..7] <18>

DDR_B_MA[0..15] <18>

JCPU1C

D D

DDR_A_D[0..63]<17>

C C

B B

DDR_A_BS0<17>

DDR_A_BS1<17>

DDR_A_BS2<17>

DDR_A_CAS#<17>

DDR_A_RAS#<17>

DDR_A_WE#<17>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AJ10

AL10

AK12

AK11

AM10

AR11

AL11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

A10

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_ A _ M A 0

DDR_ A _ M A 1

DDR_ A _ M A 2

DDR_ A _ M A 3

DDR_ A _ M A 4

DDR_ A _ M A 5

DDR_ A _ M A 6

DDR_ A _ M A 7

DDR_ A _ M A 8

DDR_ A _ M A 9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_ CL K_DDR0 <17>

M_CLK _DDR#0 <17>

DDR_CKE0_DIMMA <17>

M_ CL K_DDR1 <17>

M_CLK _DDR#1 <17>

DDR_CKE1_DIMMA <17>

DDR_CS0_DIMMA# <17>

DDR_CS1_DIMMA# <17>

M_ODT0 <17>

M_ODT1 <17>

DDR_A_DM[0..7] <17>

DDR_A_DQS#[0..7] <17>

DDR_A_DQS[0..7] <17>

DDR_A_MA[0..15] <17>

DDR_B_D[0..63]<18>

DDR_B_BS0<18>

DDR_B_BS1<18>

DDR_B_BS2<18>

DDR_B_CAS#<18>

DDR_B_RAS#<18>

DDR_B_WE#<18>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

IC,AUB_CFD_rPGA,R1P0

CONN@

A A

Secur i t y C lassification

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

5

http://laptop-motherboard-schematic.blogspot.com/

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

3

2008/03/13 2009/05/11

Compa l Secret Data

IC,AUB_CFD_rPGA,R1P0

CONN@

Dec iphered Date

Title

Size Document Number Re v

Custom

2

Date: Sheet

Compal Electronics, Inc.

Cantiga(2/6)-DDR3 A/B CH

Cal p el la D I S L A4743P

1

0.1

of

849Monday, April 13, 2009

Page 9

5

+V C C_CORE

JCPU1F

D D

C C

B B

A A

48A 15A18A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

IC,AUB_CFD_rPGA,R1P0

CONN@

CPU CORE SUPPLY

5

1.1V RAIL POWER

POWER

PROC_DPR SLPVR

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

PSI#

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

AH14

AH12

AH11

AH10

1

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

C40

2

10U_0805_6.3V6M

1

C48

2

10U_0805_6.3V6M

1

C67

2

+VTT_43

+VTT_44

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

PM_DPRSLPVR_R

H_VTTVID1 = Low, 1.1V(Clarksfield)

H_VTTVID1 = High, 1.05V(Auburndale)

AN35

VCCSENSE_R

AJ34

VSSSENSE_R

AJ35

B15

VSS_SENSE_VTT

A15

Near Processor

VCCSENSE

VSSSENSE

R61 100_0402_1%

R62 100_0402_1%

4

+VGA_CORE

+V CCP

1

C41

2

10U_0805_6.3V6M

1

C49

2

@

10U_0805_6.3V6M

1

2

22U_0805_6.3V6M

+VTT_44

+VTT_43

to power

R58 0_0402_5%

to power

R59 0_0402_5%

1 2

R60 0_0402_5%

1 2

R203 0_0402_5%

1 2

1 2

http://laptop-motherboard-schematic.blogspot.com/

1

1

2

1

2

C68

22U_0805_6.3V6M

1 2

1 2

C43

C42

2

10U_0805_6.3V6M

1

C51

C50

2

@

10U_0805_6.3V6M

+V CCP

R56 0_0603_5%

1 2

R57 0_0603_5%

1 2

H_PSI# <46>

H_V ID[0 ..6 ] <46>

to power

VTT _SELECT <44>

IMVP_IMON <46>

+VCC_CORE

4

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C52

2

1

2

VCCSENSE

VSSSENSE

10U_0805_6.3V6M

1

C61

2

22U_0805_6.3V6M

+VCCP

to power

VTT _SENSE <44>

+V CCP

1

C63

C62

2

22U_0805_6.3V6M

22U_0805_6.3V6M

H_ DP RSLPVR <46>

VCCSENSE <46>

VSSSENSE <46>

CPU

Secur i t y C lassification

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

3

JCPU1G

AT21

22U_0805_6.3V6M

22U_0805_6.3V6M

C988

C987

1

1

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C993

C991

1

1

@

@

2

330U_D2_2VY_R7M

C995

1

1

+

+

2

2

+V CCP

1

2

@

2

330U_D2_2VY_R7M

C996

+V CCP

1

C74

C73

2

22U_0805_6.3V6M

22U_0805_6.3V6M

3

10U_0805_6.3V6M

10U_0805_6.3V6M

C990

C989

1

1

2

2

22U_0805_6.3V6M

C994

1

2

1

1

C69

2

2

22U_0805_6.3V6M

1

1

C75

2

2

22U_0805_6.3V6M

2008/03/13 2009/05/11

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

C70

22U_0805_6.3V6M

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

C76

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

22U_0805_6.3V6M

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

IC,AUB_CFD_rPGA,R1P0

CONN@

Compa l Secret Data

Dec iphered Date

2

GRAPHICS

FDI PEG & DMI

POWER

2

SENSE

LINES

GRAPHICS VIDs

3A

0.6A

VAXG_SENSE

VSSAXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

DDR3 - 1.5V RAILS

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

1.1V1.8V

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

1

VCC_A X G_SENSE

VSS_AXG_SENSE

GFXVR_VID_0

GFXVR_VID_1

GFXVR_VID_2

GFXVR_VID_3

GFXVR_VID_4

GFXVR_VID_5

GFXVR_VID_6

GFXVR_EN

GFXVR_DPRSLPVR

GFXVR_IMON

R128

@

1K_0402_5%

1

C56

2

1U_0603_10V4Z

1

+

C64

2

330U_D2_2VY_R7M

1

C71

2

10U_0805_6.3V6M

1

C77

2

22U_0805_6.3V6M

1

1

C79

2

2

1U_0603_10V4Z

Title

Size Document Number Re v

Custom

Cal p el la D I S L A4743P

Date: Sheet

VCC_A X G_SENSE <43>

VSS_AXG_SENSE <43>

GFXVR_VID_0 <43>

GFXVR_VID_1 <43>

GFXVR_VID_2 <43>

GFXVR_VID_3 <43>

GFXVR_VID_4 <43>

GFXVR_VID_5 <43>

GFXVR_VID_6 <43>

GFXVR_EN <43>

GFXVR_DPRSLPVR <43>

GFXVR_IMON <43>

12

1

2

1

2

1

2

1

2

C80

1U_0603_10V4Z

1

1

C57

2

1U_0603_10V4Z

1

C65

2

22U_0805_6.3V6M

+VCCP

C72

10U_0805_6.3V6M

+VCCP

C78

22U_0805_6.3V6M

1

C81

2

2.2U_0603_6.3V4Z

1

C59

C58

1U_0603_10V4Z

C66

22U_0805_6.3V6M

1

2

C60

2

2

1U_0603_10V4Z

1U_0603_10V4Z

1

C82

2

22U_0805_6.3V6M

+1.8VS

C83

4.7U_0603_6.3V6K

Compal Electronics, Inc.

Auburndale(4/5)-PWR

949Monday, April 13, 2009

1

+1.5V

of

0.1

Page 10

5

4

3

2

1

JCPU1H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

D D

C C

B B

AR17

AR15

AR12

AP20

AP17

AP13

AP10

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AG10

AE35

VSS8

VSS9

VSS10

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

VSS15

VSS16

VSS17

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

VSS80

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

JCPU1I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

VSS

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

+V C C_CORE

@

VSS_NCTF1_R

VSS_NCTF2_R

VSS_NCTF3_R

VSS_NCTF4_R

VSS_NCTF5_R

VSS_NCTF6_R

VSS_NCTF7_R

1

1

C84

2

1

2

1

1

C982

2

2

47P_0402_50V8J

C85

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C97

C96

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C114

C115

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C86

2

10U_0805_6.3V6M

1

C98

2

10U_0805_6.3V6M

1

C116

2

10U_0805_6.3V6M

CPU CORE

1

1

C87

2

1

2

1

2

C88

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C100

C99

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C117

C118

2

10U_0805_6.3V6M

22U_0805_6.3V6M

1

1

1

C89

2

1

2

1

2

C90

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C101

C102

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C119

C120

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C91

2

1

2

1

2

C92

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C104

C103

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

+

C121

C108

2

22U_0805_6.3V6M

470U_D2_2VM_ R4.5M

1

1

C93

2

10U_0805_6.3V6M

1

C105

2

10U_0805_6.3V6M

1

+

C109

2

470U_D2_2VM_ R4.5M

1

C94

2

10U_0805_6.3V6M

1

C106

2

10U_0805_6.3V6M

1

+

C110

2

470U_D2_2VM_ R4.5M

Inside cavity

C95

2

10U_0805_6.3V6M

1

bet ween

C107

Inductor and

2

10U_0805_6.3V6M

soc ket

1

+

C111

2

470U_D2_2VM_ R4.5M

470uF 4.5mohm

IC,AUB_CFD_rPGA,R1P0

CONN@

A A

5

http://laptop-motherboard-schematic.blogspot.com/

4

IC,AUB_CFD_rPGA,R1P0

CONN@

Secur i t y C lassification

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS TH E PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHOR IZED BY COM PAL ELECTRONICS, IN C. N EITHER THIS SHEET NOR THE INFORMATION IT CONTAIN S

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRON ICS, INC.

3

2008/03/13 2009/05/11

Compa l Secret Data

Dec iphered Date

2

Title

Size Document Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Auburndale(5/5)-GND/Bypass

Cal p el la D I S L A4743P

10 49Monday, April 13, 2009

1

of

0.1

Page 11

5

ICH _ RTCX1

Y1

32.768KHZ_12.5PF_Q13MC14610002

1

2

ICH _ RTCX2

C123

18P_0402_50V8J

SPI _ SB_CS#

SPI_SO_R

R63 10M_0402_5%

1 2

1

1

D D

2

C C

+3VS

R656 10K_0402_5%

R657 10K_0402_5%

B B

C122

18P_0402_50V8J

1 2

1 2

OSC4OSC

NC3NC

2

+RTCVCC

R65 1M_0402_5%

R66 330K_0402_5%

+RTCVCC

R69 20K_0402_1%

R70 20K_0402_1%

HDA_BITCLK_MDC<33>

HDA_BITCLK_CODEC<33>

HDA_SYNC_MDC<33>

HDA_SYNC_CODEC<33>

HDA_RST#_MDC<33>

HDA _ R ST # _CODEC<33,37>

HDA_SDOUT_MDC<33>

HDA_SDOUT_CODEC<33>

1U_0603_10V4Z

1 2

1 2

1U_0603_10V4Z

HDA_SDIN0<33>

HDA_SDIN1<33>

SPI _ CL K_ PCH<36>

SPI _ SB_CS#<36>

SPI_SI<36>

SPI_SO_R<36>

1 2

1 2

1

C124

2

1

C125

2

R72 33_0402_5%

1 2

R73 33_0402_5%

1 2

R74 33_0402_5%

1 2

R75 33_0402_5%

1 2

1 2

R77 33_0402_5%

1 2

R78 33_0402_5%

R81 33_0402_5%

1 2

R82 33_0402_5%

1 2

R670 100K_0402_5%@

1 2

SPI _ CL K_PCH

SPI _ SB_CS#

SPI_SI

SPI_SO_R

SM_ IN T R UDER#

PCH_INTVRMEN

INTVRMEN

HIn

Κ

LIn

Κ

12

CLRP1

SHORT PADS

12

CLRP2

SHORT PADS

SB_ SPKR<33>

R654 15_0402_5%

1 2

R655 15_0402_5%

1 2

4

tegrated VRM enable

tegrated VRM disable

ICH _ RTCX1

ICH _ RTCX2

ICH_RTCRST#

ICH_SRTCRST#

SM_ IN T R UDER#

PCH_INTVRMEN

HDA_BIT_CLK

H DA_SYNC

SB_ SPKR

HDA_RST#

HDA_SDIN0

HDA_SDIN1

HDA_SDOUT

HDA_DOCK_EN#

PCH_JTAG_TCK

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH _J TAG_RST#

B13

D13

C14

D17

A16

A14

A30

D29

P1

C30

G30

F30

E32

F32

B29

H32

J30

T16PAD

M3

K3

K1

J2

J4

BA2

AV3

AY3

AY1

AV1

*

U1A

RTCX1

RTCX2

RTCRST#

SRTCRST#

INTRUDER#

INTV RME N

HDA_BCLK

HDA_SYNC

SPKR

HDA_RS T#

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_SDIN3

HDA_SDO

HDA_DOCK_ EN# / GPIO33

HDA_DOCK_RST# / GPIO13

JTAG_TCK

JTAG_TMS

JTAG_TDI

JTAG_TDO

TRST#

SPI_CLK

SPI_CS0#

SPI_CS1#

SPI_MOSI

SPI_MISO

IBEXPEAK-M_FCBGA10 71

+3VS

R64 10K_0402_5%

1 2

R67 1K_0402_5%@

1 2

LOW=Default

HIGH=No Reboot

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

FWH4 / LFRAME#

LDRQ0#

LDRQ1# / GPIO23

RTCIHDA

LPC

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATALED#

SATA0GP / GPIO21

SATA1GP / GPIO19

SPI JTAG

3

SIRQ

SB_ SPKR

*

D33

B33

C32

A32

C34

LDRQ0#

A34

LDRQ1#

F34

SIRQ

AB9

AK7

AK6

SATA_TXN0_C

AK11

SATA_TXP0_C

AK9

AH6

AH5

SATA_TXN4_C

AH9

SATA_TXP4_C

AH8

AF11

AF9

AF7

AF6

AH3

AH1

AF3

AF1

AD9

AD8

SATA_TXN2_C

AD6

SATA_TXP2_C

AD5

AD3

AD1

AB3

AB1

AF16

R89 37.4_0402_1%

1 2

AF15

R91 10K_0402_1%

1 2

T3

GPIO21

Y9

HDDHALT_LED#

V1

LPC_AD0 <31,36,37>

LPC_AD1 <31,36,37>

LPC_AD2 <31,36,37>

LPC_AD3 <31,36,37>

LPC _F RAME# <31,36 ,3 7>

T13 P A D

T14 P A D

SIRQ <37>

C126 0.01U_0402_50V7K

1 2

C127 0.01U_0402_50V7K

1 2

C130 0.01U_0402_50V7K

1 2

C131 0.01U_0402_50V7K

1 2

C128 0.01U_0402_50V7K

1 2

C129 0.01U_0402_50V7K

1 2

+1.05VS

+3VS

SATA_LED# <38>

HDDHALT_LED# <38>

SATA_RXN0_C

SATA_RXP0_C

SATA_TXN0

SATA_TXP0

SATA_RXN4_C

SATA_RXP4_C

SATA_TXN4

SATA_TXP4

SATA_RXN2_C

SATA_RXP2_C

SATA_TXN2

SATA_TXP2

2

SATA_RXN0_C <30>

SATA_RXP0_C <30>

SATA_TXN0 <30>

SATA_TXP0 <30 >

SATA_RXN4_C <30>

SATA_RXP4_C <30>

SATA_TXN4 <30>

SATA_TXP4 <30 >

SATA_RXN2_C <35>

SATA_RXP2_C <35>

SATA_TXN2 <35>

SATA_TXP2 <35 >

HDD

ODD

E SATA

12

R86

@

200_0402_5%

12

R684

@

100_0402_1%

1

+3VALW+3VALW +3VALW +3VALW

12

R84

@

200_0402_5%

PCH_JTAG_TMS P C H_ J TAG_RST#PCH_JTAG_TDO PCH_J TAG_TDI

12

R683

@

100_0402_1%

R85

20K_0402_5%

1 2

R685

10K_0402_1%

1 2

@

1 2

12

@

R87

20K_0402_5%

R88

10K_0402_5%

HDA_SDO

HDA_SYNC

This signal has a weak internal pull down.

H=>On Die PLL is supplied by 1.5V

L=>On Die PLL is supplied by 1.8V

*

HDA_DOCK_EN#

ME debug mode , this signal has a weak internal PU

H=>security measures defined in the Flash

*

Descriptor will be in effect (default)

L=>Flash Descriptor Security will be overridden

A A

5

SPI_MOSI

This signal has a weak internal pull down.

Dis able iTPM=No Stuff

*

Enable iTPM=Stuff

iTPM ENABLE/DISABLE

+3VS

R68 1K_0402_5%@

1 2

SPI_SI

4

This signal has a weak internal pull down.

This signal can't PU

Dis able iTPM=No Stuff

*

Enable iTPM=Stuff

W=20milsW= 20mils

1

C132

2.2U_0603_6.3V4Z

2

Place near IBEX-M

+3VS

GPIO21

HDDHALT_LED#

R92 10K_0402_5%

R93 10K_0402_5%

12

12

Security Classification

THIS SHE E T OF E NGIN EE RI NG D RA W ING I S THE P RO P RIE TAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

D3

1

DAN202U_SC70

Issued Date

2

R94 1K_0402_5%

3

1 2

BATT1

@

BATT1.1+3VL+RTCVCC

CR2032 RTC BATTERY

JBATT1

1

W=20mils

2008/03/13 2009/05/11

1

2

2

3

GND

4

GND

ACES_85205-02001

CONN@

Com p a l S ecret Data

Deciphered Date

PCH _JTAG_TDO

PCH _JTAG_TMS

PCH _JTAG_TDI

PCH _JTAG_TCK

PCH _JTAG_RST#

2

1 2

R90 51_0402_5%

RefDesP CH Pin

R86

R684

R84

R683

R685

R90

R87

R88

PCH_JTAG_TCK

PCH JTAG Enable PCH JTAG Disable

ES1 ES1ES2 ES2

No Install

200ohm

200ohm

100ohm

200ohm

No Install

No Install

100ohm 100ohm

200ohm

200ohm

100ohm 100ohm

51ohm 51ohm 51ohm

20Kohm 20Kohm

10Kohm

10Kohm

Title

Size Do c u ment Numbe r R e v

Custom

Date: Sheet

Compal Electronics, Inc.

IBEX-M(1/6)- HDA/ JTAG/S ATA

Calp ell a DI S L A4 743P

No Install

No Install

No Install

20Kohm

10Kohm

No Install

1

No Install

No Install

No Install

No Install

No InstallR85

No Install

51ohm

No Install

No InstallNo Install

11 49Monday, April 13, 2009

of

0.1

http://laptop-motherboard-schematic.blogspot.com/

Page 12

5

D D

PCIE_RXN1<31>

WWAN

WLAN

LAN

New Card

C C

OK

OK

OK

B B

OK

A A

+3 VALW

+3VS

+3VS

+3 VALW

WWAN

WLAN

LAN

EXP

PCI E_RXP1<31>

PCIE_TXN1<31>

PCIE_TXP1<31>

PCIE_RXN2<31>

PCI E_RXP2<31>

PCIE_TXN2<31>

PCIE_TXP2<31>

PCIE_RXN3<32>

PCI E_RXP3<32>

PCIE_TXN3<32>

PCIE_TXP3<32>

PCIE_RXN4<31>

PCI E_RXP4<31>

PCIE_TXN4<31>

PCIE_TXP4<31>

R405 10K_0402_5%

1 2

R411 10K_0402_5%

1 2

R677 10K_0402_5%

1 2

R415 10K_0402_5%

1 2

CLK_PCIE_WWAN#<31>

CLK_PCIE_WWAN<31>

CLKREQ_WW AN#<31>

CLK_PCIE_WLAN#<31>

CLK_PCIE_WLAN<31>

CLKREQ_WLAN#<31>

CLK_PCIE_LAN#<32>

CLK_PCIE_LAN<32>

CLKREQ_LAN#<32>

CL K _PC IE_EXP#<31>

CL K _ PC IE_ EXP<31>

CL K REQ _EXP#<31>

C133 0.1U_0402_16V4Z

C134 0.1U_0402_16V4Z

C135 0.1U_0402_16V4Z

C136 0.1U_0402_16V4Z

C137 0.1U_0402_16V4Z

C138 0.1U_0402_16V4Z

C139 0.1U_0402_16V4Z

C140 0.1U_0402_16V4Z

CLKREQ_WW AN#_R

CLKREQ_ WLAN#

CLKREQ_LAN#

CL K R EQ_EXP#_ R

R107 0_0402_5%

1 2

R108 0_0402_5%

1 2

R80 100_0402_5%

1 2

R109 0_0402_5%

1 2

R110 0_0402_5%

1 2

R111 0_0402_5%

1 2

R112 0_0402_5%

1 2

R114 0_0402_5%

1 2

R115 0_0402_5%

1 2

R83 100_0402_5%

1 2

R756 10K_0402_5%

+3VALW

+3VALW

+3VALW

1 2

R757 10K_0402_5%

1 2

R606 10K_0402_5%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PCIE_RXN1

PCI E_RXP1

PCI E_C_TXN1

PCIE_C_TXP1

PCIE_RXN2

PCI E_RXP2

PCI E_C_TXN2

PCIE_C_TXP2

PCIE_RXN3

PCI E_RXP3

GLA N_C_TXN

GL AN_C_TXP

PCIE_RXN4

PCI E_RXP4

PCI E_C_TXN4

PCIE_C_TXP4

CLK_PCIE_W WAN#_R

CLK_PCIE_W WAN_R

CLKREQ_WW AN#_R

CLK_PCIE _WLAN#_R

CLK_PCIE _WLAN_R

CLK_PC IE_LAN#_R

CLK_PC IE_LAN_R

CL K _ PCIE_EXP# _R

CL K _ PCIE_EXP_ R

CL K R EQ_EXP#_ R

PCI ECL KREQ4 #

PCI ECL KREQ5 #

PEG _ B_CL KRQ #

4

U1B

BG30

PERN1

BJ30

PERP1

BF29

PETN1

BH29

PETP1

AW30

PERN2

BA30

PERP2

BC30

PETN2

BD30

PETP2

AU30

PERN3

AT30

PERP3

AU32

PETN3

AV32

PETP3

BA32

PERN4

BB32

PERP4

BD32

PETN4

BE32

PETP4

BF33

PERN5

BH33

PERP5

BG32

PETN5

BJ32

PETP5

BA34

PERN6

AW34

PERP6

BC34

PETN6

BD34

PETP6

AT34

PERN7

AU34

PERP7

AU36

PETN7

AV36

PETP7

BG34

PERN8

BJ34

PERP8

BG36

PETN8

BJ36

PETP8

AK48

CLKOUT_PCIE0N

AK47

CLKOUT_PCIE0P

P9

PCIECLKRQ0# / GPIO73

AM43

CLKOUT_PCIE1N

AM45

CLKOUT_PCIE1P

U4

PCIECLKRQ1# / GPIO18

AM47

CLKOUT_PCIE2N

AM48

CLKOUT_PCIE2P

N4

PCIECLKRQ2# / GPIO20

AH42

CLKOUT_PCIE3N

AH41

CLKOUT_PCIE3P

A8

PCIECLKRQ3# / GPIO25

AM51

T57PAD

T58PAD