Holtek Semiconductor Inc HT9200A, HT9200B Datasheet

Features

•

Operating voltage: 2.0V ~5.5V

•

Serial mode for the HT9200A

•

Serial/parallel mode for the HT9200B

General Description

The HT9200 A/B tone generators are d esigned

for

µC interfaces. They can be instru cted by a

µC to generate 16 dual tones and 8 single tones

from the DTMF p in. The HT9200A provides a

serial mode wh ereas the HT9200B conta ins a

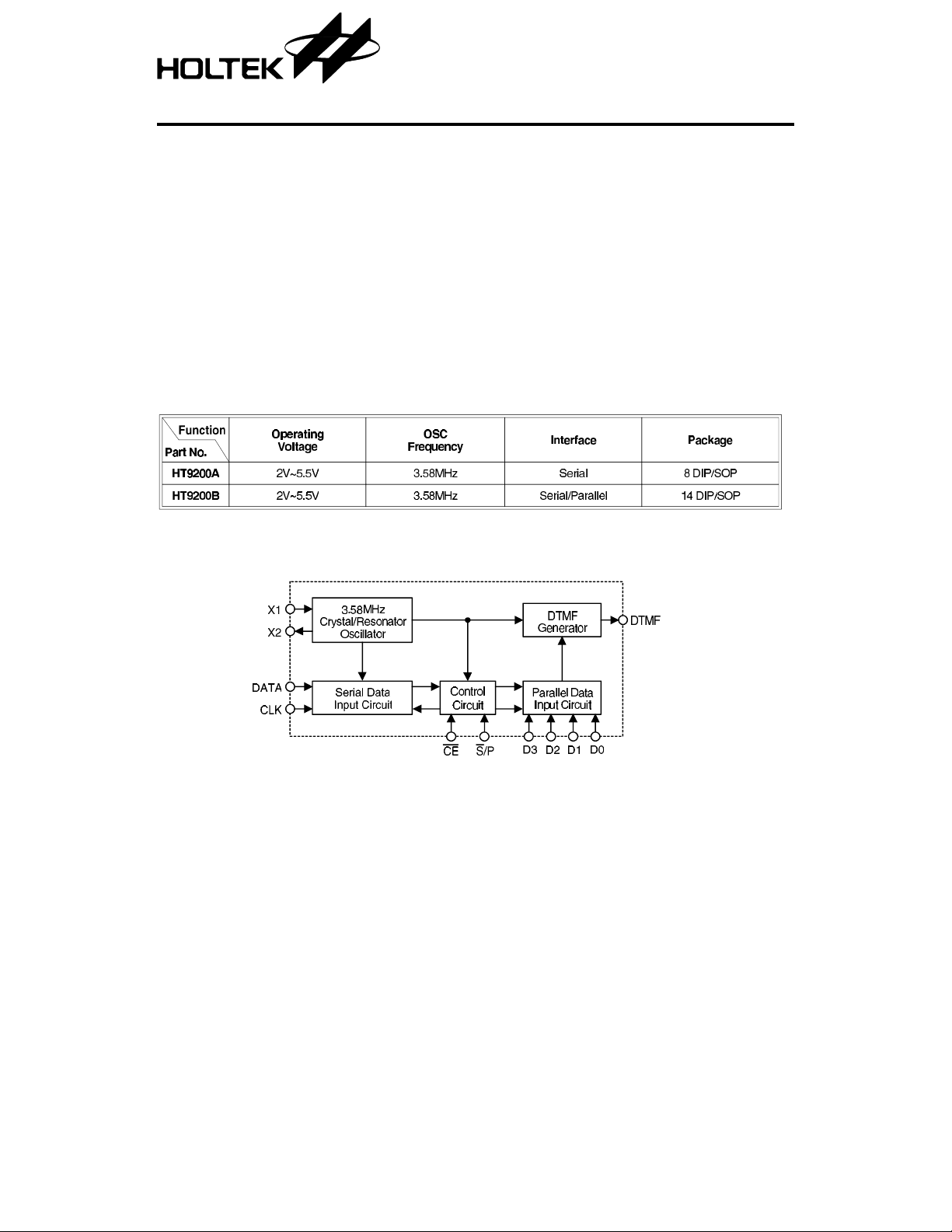

Selection Table

HT9200A/B

DTMF Generators

•

Low standby current

•

Low total harmonic distortion

•

3.58MHz crystal or ceramic resonator

selectable serial/parallel mode interface for

various appl ications such as security systems,

home automation , remote control thro ugh tele phone lines, communication systems, etc.

Block Diagram

1 21st Aug ’98

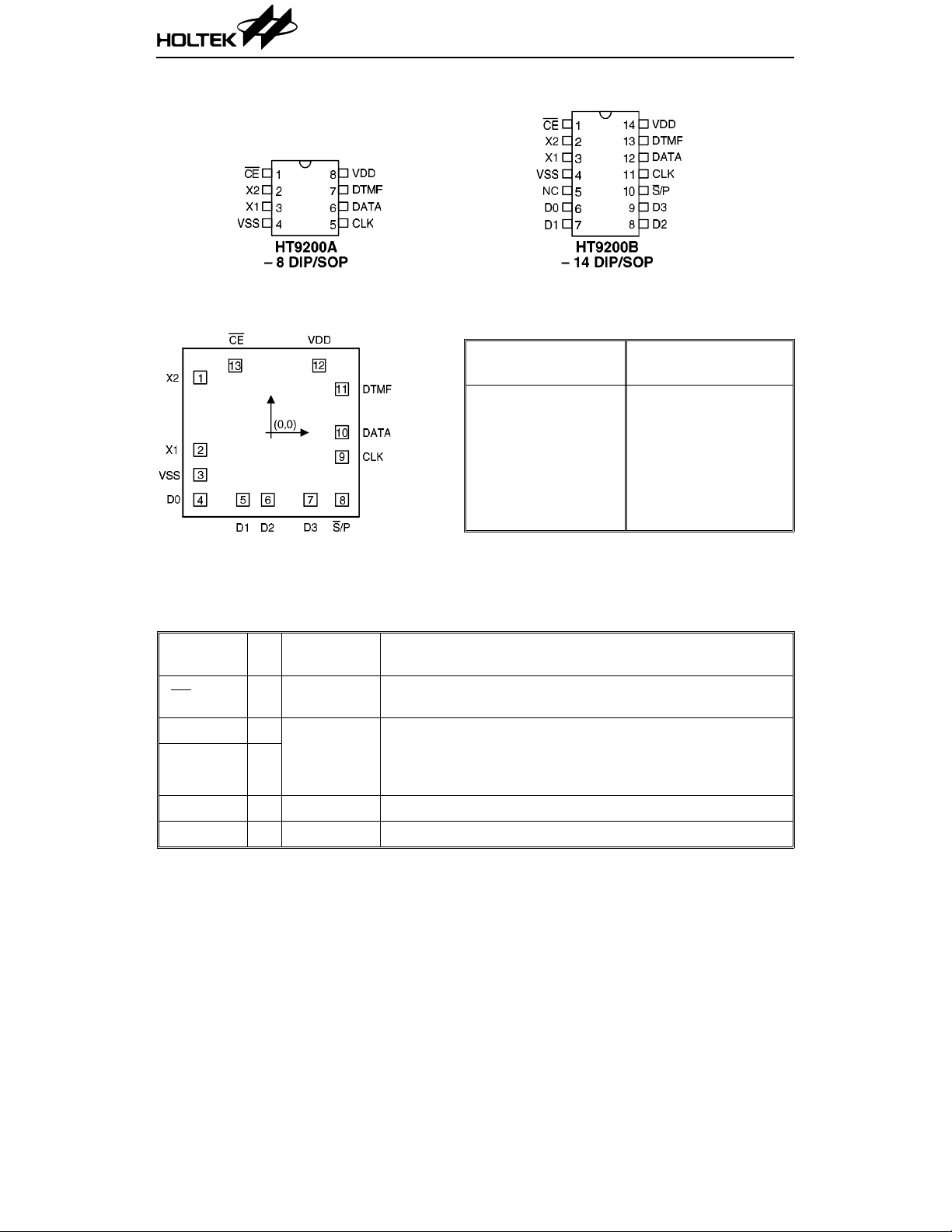

Pin Assignment

HT9200A/B

Pad Assignment Pad Coordinates

Pad

No.

1 –553.30 430.40 8 553.30 –523.50

2 –553.30 –133.50 9 553.30 –190.30

3 –553.30 –328.50 10 553.30 4.70

4 –553.30 –523.50 11 553.30 340.30

5 –220.10 –523.50 12 374.90 523.50

6 –25.10 –523.50 13 –279.30 523.50

7 308.10 –523.50

Chip size: 1460

* The IC substrate should be connected to VSS in the PCB layout artwork.

× 1470 (µm)

2

XY

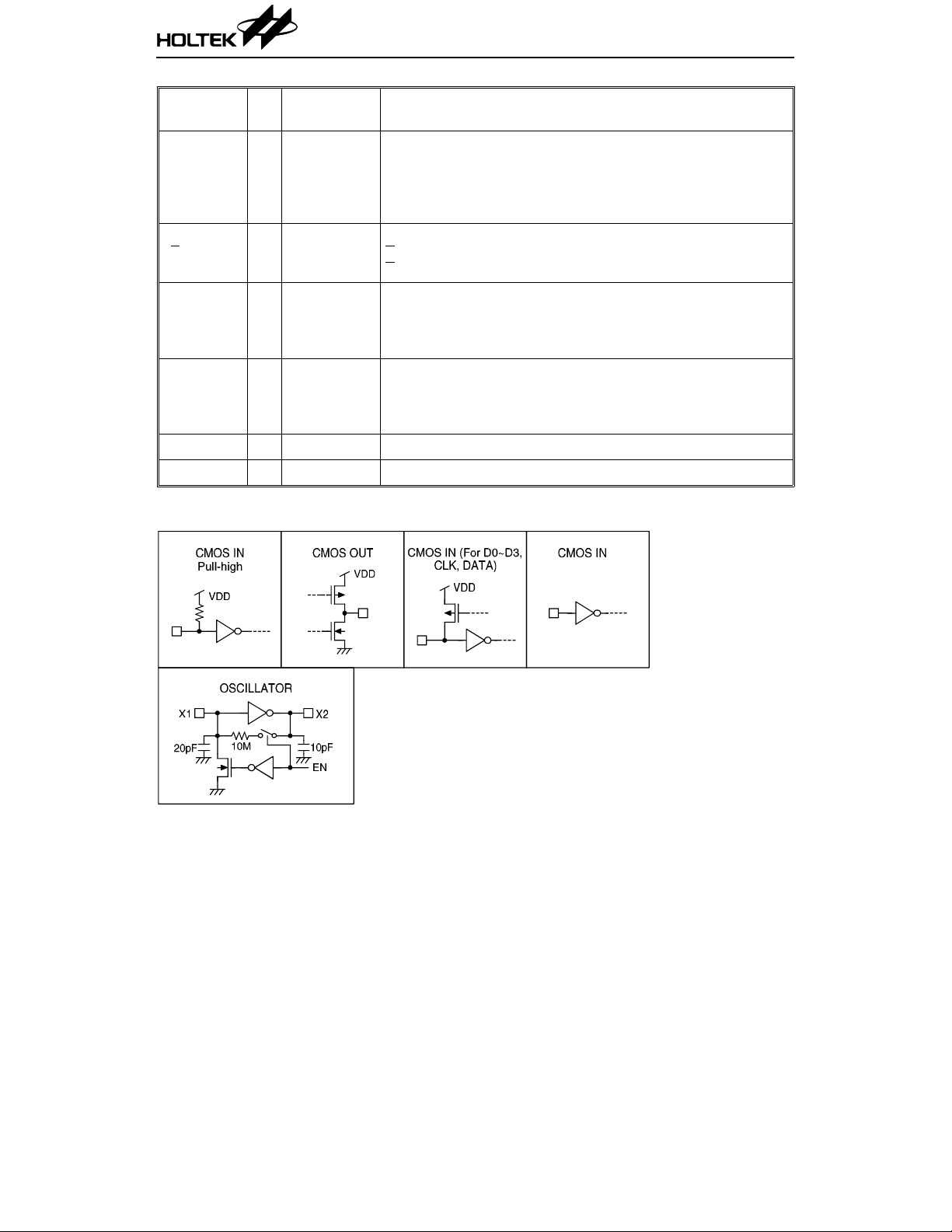

Pin Description

Pin Name I/O

CE I

X2 O

X1 I

Internal

Connection

CMOS IN

Pull-high

Oscillator

Description

Chip enable, active low

The system oscillator consists of an inverter, a bias resistor, and

the required load capacitor on chip.

The oscillator function can be implemented by Connect a

standard 3.579545MHz crystal to the X1 and X2 terminals.

Pad

No.

Unit: µm

XY

VSS — — Negative power supply

NC — — No connection

2 21st Aug ’98

HT9200A/B

Pin Name I/O

D0~D3 I

S/P I CMOS IN

CLK I

DATA I

DTMF O CMOS OUT Output terminal of the DTMF signal

VDD — — Positive power supply, 2.0V~5.5V for normal operation

Approximate internal connection circuits

Internal

Connection

CMOS IN

Pull-high

or floating

CMOS IN

Pull-high

or floating

CMOS IN

Pull-high

or floating

Description

Data inputs for the parallel mode

When the IC is operating in the serial mod e, the data input

terminals (D0~D3) are included with a pull-high resistor. When

the IC is operating in the parallel mode, these pins become

floating.

Operation mode selection input

S/P=“H”: Parallel mode

S/P=“L”: Serial mode

Data synchronous clock input for the serial mode

When the IC is operating in the parallel mode, the input

terminal (CLK) is included with a pull-high res istor. Whe n the

IC is operating in the serial mode, this pin becomes floating.

Data input terminal for the serial mode

When the IC is operating in the parallel mode, the input terminal

(DATA) is included with a pull-high resistor. When the IC is

operating in the serial mode, this pin becomes floating.

3 21st Aug ’98

Loading...

Loading...