HT9032

Calling Line Identification Receiver

1 April 6, 2000

Features

·

HT9032B/C/D operating voltage: 3.5V~5.5V

HT9032F operating voltage: 3.0V~5.5V

·

Bell 202 FSK and V.23 demodulation

·

Ring detection input and output

·

Carrier detection output

·

Power down mode

·

High input sensitivity

·

HT9032C: 16-pin DIP/SOP package

HT9032B/F-A: 8-pin DIP package

HT9032D/F-B: 8-pin SOP package

Applications

·

Feature phones

·

Caller ID adjunct boxes

·

Fax and answering machines

·

Computer telephony interface products

·

ADSI products

General Description

The HT9032 calling line identification receiver

is a low power CMOS integrated circuit de

signed for receiving physical layer signals transmitted according to Bellcore TR-NWT-000030

and ITU-T V.23 specifications. The primary ap

plication of this device is for products used to

receive and display the calling number, or mes

sage waiting indicator sent to subscribers from

the central office facilities. The device also pro

vides a carrier detection circuit and a ring de

tection circuit for easier system applications.

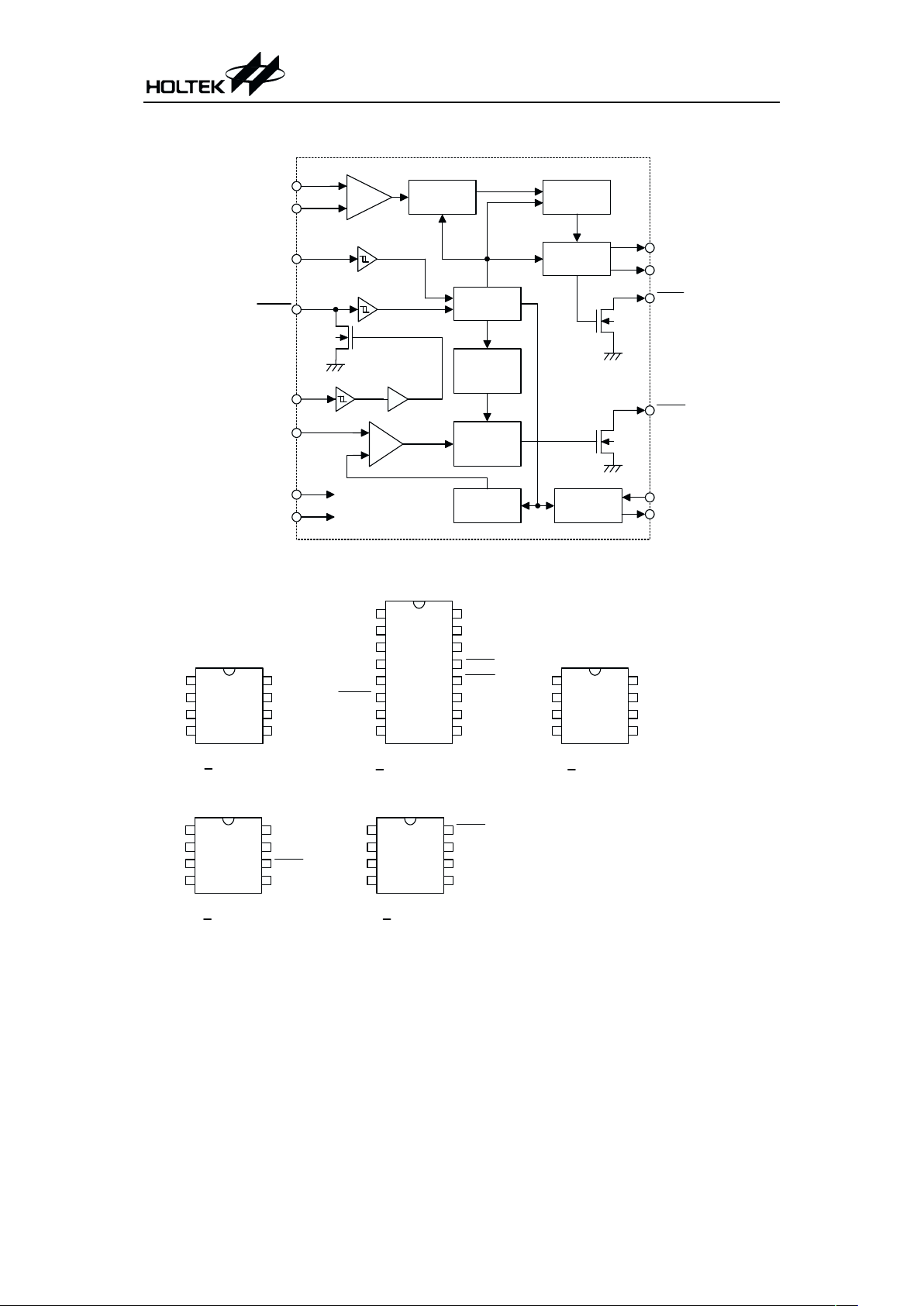

Block Diagram

Pin Assignment

HT9032

2 April 6, 2000

Band Pass

F ilte r

Power Up

Logic

D em odulator

Valid Data

Detection

DOUTC

DOUT

Internal

Power Up

Logic

Ring

Analysis

Circuit

R eference

Voltage

Clock

G enerator

CDET

RDET

VSS

VDD

RDET2

TIP

RING

PDW N

RTIM E

RDET1

X1

X2

H T9032B

8 D IP

TIP

PDW N

RING

VSS

X2

DOUT

X1

NC

NC

TIP

VDD

RTIM E

RDET1

X2

PDW N

VSS

RING

CDET

RDET

X1

RDET2

DOUTC

DOUT

H T9032C

16 D IP /S O P

VDD

1

2

3

4

8

7

6

5

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

H T9032D

8 S O P

DOUT

TIP

VDD

RING

PDW N

X2

VSS

X1

1

2

3

4

8

7

6

5

H T9032F-A

8 D IP

TIP

PDW N

RING

VSS

X1

DOUT

CDET

VDD

1

2

3

4

8

7

6

5

H T9032F-B

8 S O P

DOUT

TIP

VDD

RING

PDW N

X1

VSS

CDET

1

2

3

4

8

7

6

5

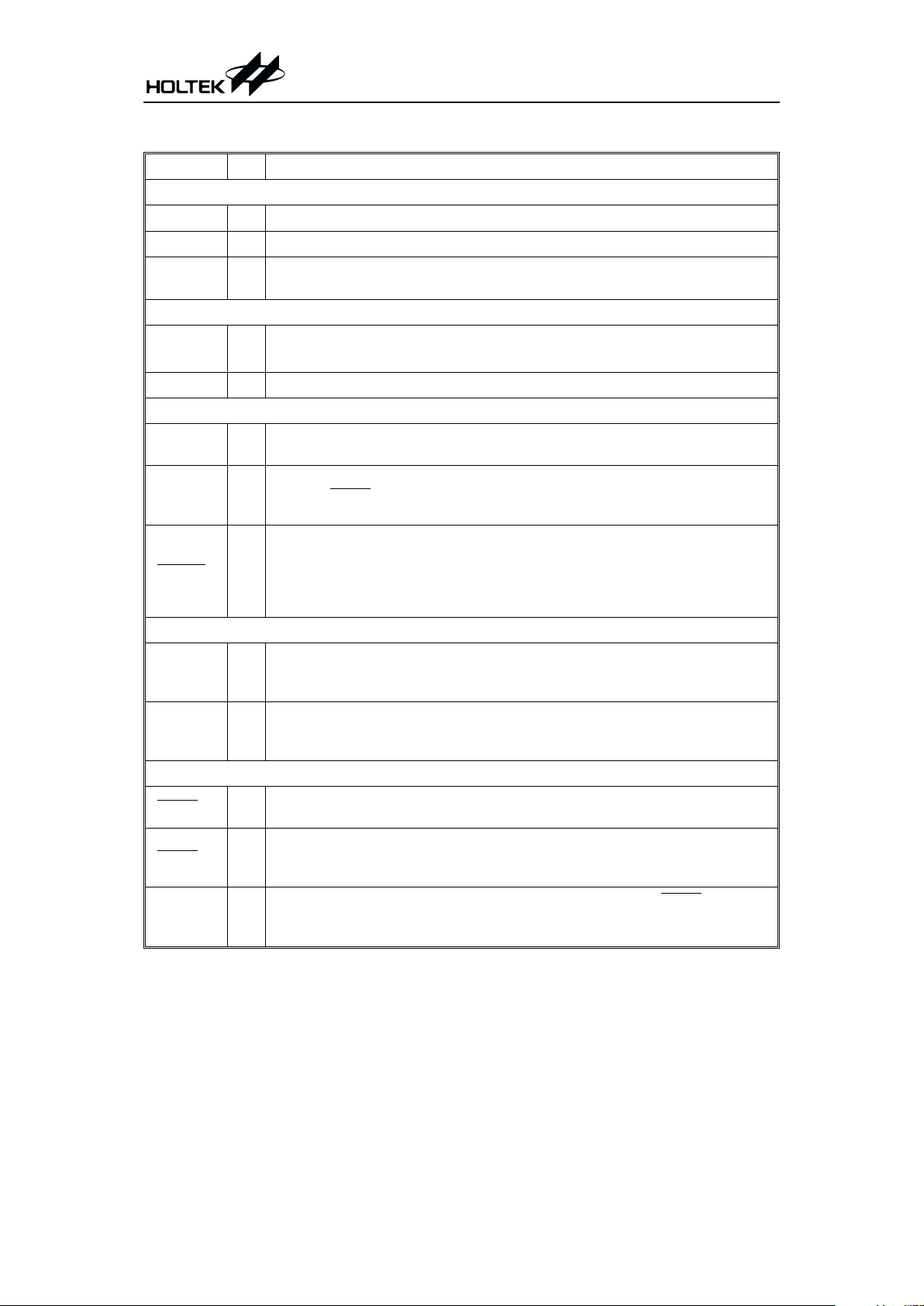

Pin Description

Pin Name I/O Description

Power Inputs

VDD

¾

Power-VDD is the input power for the internal logic.

VSS

¾

Ground-VSS is ground connection for the internal logic.

PDWN I

A logic ²1² on this pin puts the chip in power down mode. When a logic ²0² is on

this pin, the chip is activated. This is a schmitt trigger input.

Clock

X1 I

A crystal or ceramic resonator should be connected to this pin and X2.

This pin may be driven from an external clock source.

X2 O A crystal or ceramic resonator should be connected to this pin and X1.

Ring Detections

RDET1 I

It detects ring energy on the line through an attenuating network and enables

the oscillator and ring detection. This is a schmitt trigger input.

RDET2 I

It couples the ring signal to the precision ring detector through an attenuating

network. RDET

=²0² if a valid ring signal is detected. This is a schmitt trigger in

-

put.

RTIME

I/O

An RC network may be connected to this pin in order to hold the pin voltage be

low 2.2V between the peaks of the ringing signal. This pin controls internal

power up and activates the partial circuitry needed to determine whether the

incoming ring is valid or not. The input is a schmitt trigger input. The output

cell structure is an NMOS output.

FSK Signal Inputs

TIP I

This input pin is connected to the tip side of the twisted pair wires. It is internally biased to 1/2 V

DD

when the device is in power up mode. This pin must be

DC isolated from the line.

RING I

This input pin is connected to the ring side of the twisted pair wires. It is internally biased to 1/2 V

DD

when the device is in power up mode. This pin must be

DC isolated from the line.

Detection Results

RDET

O

This open drain output goes low when a valid ringing signal is detected. When

connected to PDWN pin, this pin can be used for auto power up.

CDET

O

This open drain output goes low indicating that a valid carrier is present on the

line. A hysteresis is built-in to allow for a momentary drop out of the carrier.

When connected to PDWN pin, this pin can be used for auto power up.

DOUT O

This pin presents the output of the demodulator whenever CDET

pin is low.

This data stream includes the alternate ²1² and ²0² pattern, the marking, and

the data. At all other times, this pin is held high.

HT9032

3 April 6, 2000