Holtek Semiconductor Inc HT82K68E Datasheet

HT82K68E

Preliminary

Multimedia Keyboard Encoder OTP

Features

Operating voltage: 2.8V~5.5V

·

34(42-pin)/32(40-pin) bidirectional I/O lines

·

One 8-bit programmable timer counter with

·

overflow interrupts

Crystal or RC oscillator

·

Watchdog Timer

·

3K´16 OTP EPROM

·

160´8 data RAM

·

General Description

The HT82K68E is an 8-bit high performance

peripheral interface IC, designed for multiple

I/O products and multimedia applications. It

supports interface to a low speed PC with

multimedia keyboard or wireless keyboard in

Windows 95, Windows 98 or Windows 2000 en

vironment. A HALT feature is included to re

duce power consumption.

HALT function and wake-up feature reduce

·

power consumption

Six-level subroutine nesting

·

Bit manipulation instructions

·

16-bit table read instructions

·

63 powerful instructions

·

All instructions in 1 or 2 machine cycles

·

40/42-pin DIP package

·

The program and option PROM can be electri

cally programmed making the HT82K68E suit

able for use in product development.

-

-

-

-

1 August 8, 2000

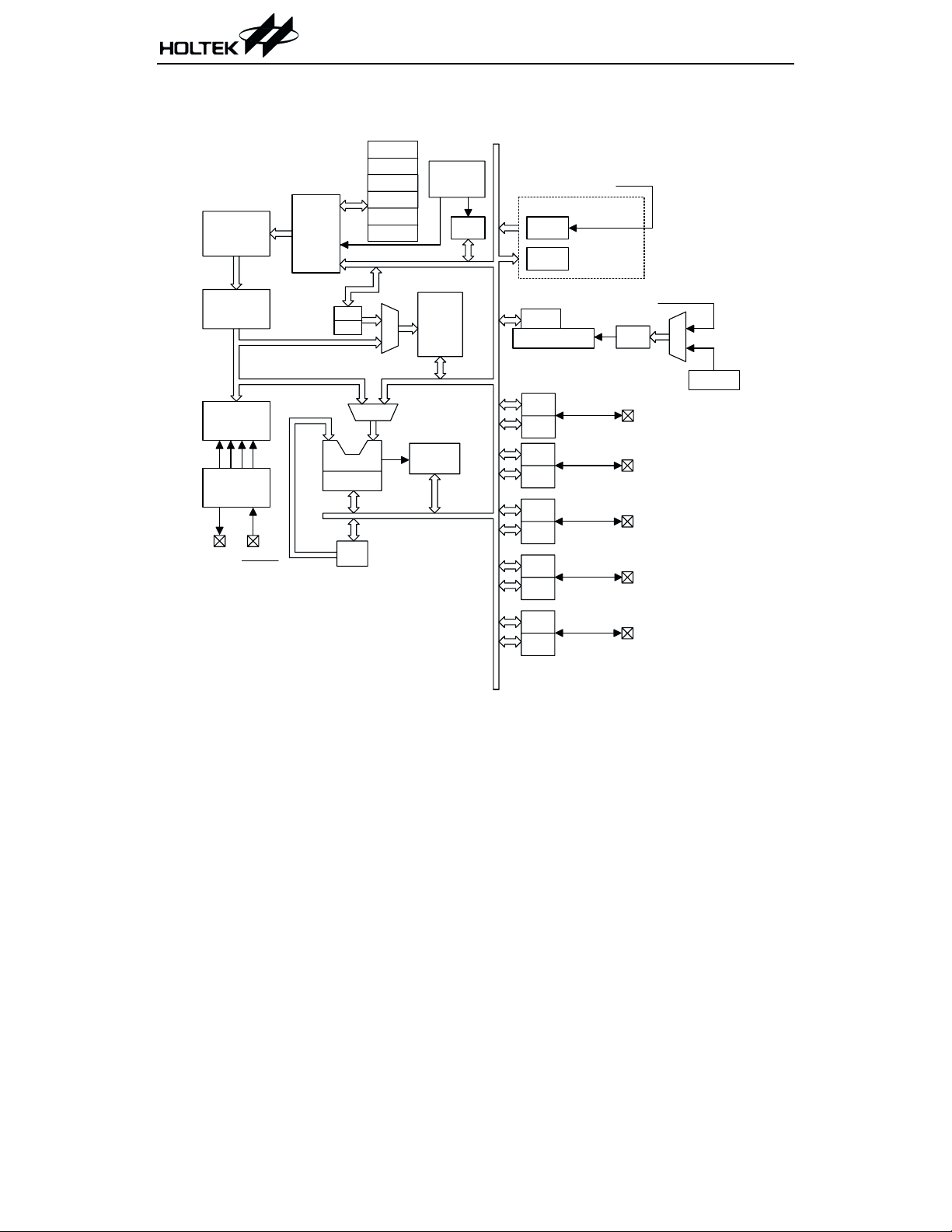

Block Diagram

Program

EPRO M

Program

C ounter

Preliminary

STACK0

STACK1

STACK2

STACK3

STACK4

STACK5

In te rru p t

Circuit

IN T C

HT82K68E

SYS C LK/4

TM R

TM RC

8 bit

Instruction

R egister

Instruction

D ecoder

Tim ing

G enerator

OSC2 OSC1

RESET

VDD

VSS

MP0

MP1

ALU

S h ifte r

ACC

MUX

M

U

X

DATA

Memory

STATUS

WDTS

WDT Prescaler

PORT E

PEC

PE

PDC

PORT D

PD

PCC

PORT C

PC

PBC

PORT B

PB

PAC

PORT A

PA

SYS C LK/4

WDT

PE0~PE4

PD0~PD 7

PC0~PC 7

PB0~PB7

PA0~PA7

M

U

X

RC OSC

2 August 8, 2000

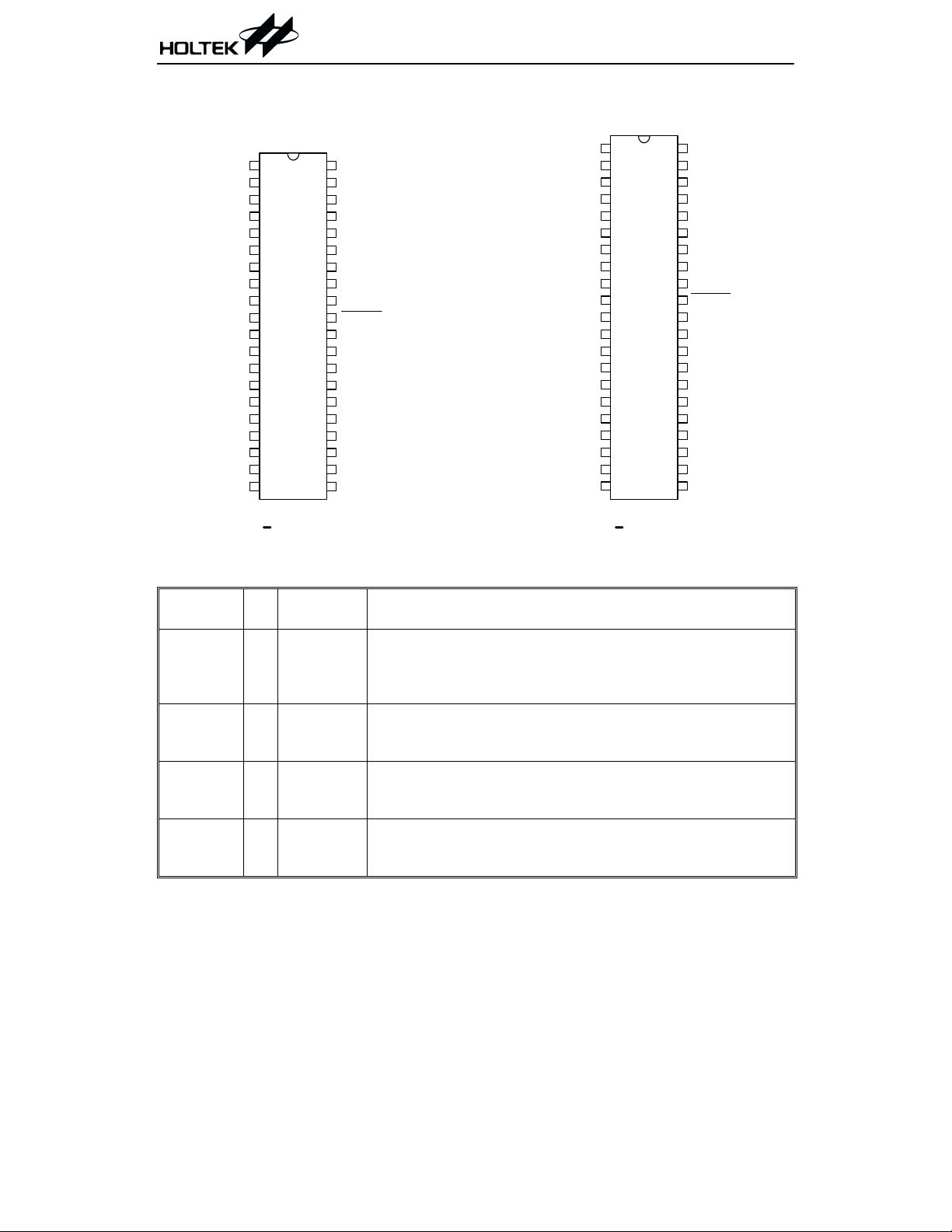

Pin Assignment

Preliminary

HT82K68E

1

PB5

2

PB4

3

PA3

4

PA2

5

PA1

6

PA0

7

PB3

8

PB2

9

PB1

10

PB0

11

PD7

12

PD6

13

PD5

14

PD4

15

VSS

PC0

PC1

PC2

16

17

18

19

20

PE2(LED)

PE3(LED)

H T82K 68E

4 0 D IP

Pin Description

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

PB6

PB7

PA4

PA5

PA6

PA7

OSC2

OSC1

VDD

RESET

PE4(LED)

PD3

PD2

PD1

PD0

PC7

PC6

PC5

PC4

PC3

PB5

PB4

PA3

PA2

PA1

PA0

PB3

PB2

PB1

PB0

PD7

PD6

PD5

PD4

VSS

PE2(LED)

PE3(LED)

PC0

PC1

PC2

PE0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

H T82K 68E

4 2 D IP

PB6

PB7

PA4

PA5

PA6

PA7

OSC2

OSC1

VDD

RESET

PE4(LED)

PD3

PD2

PD1

PD0

PC7

PC6

PC5

PC4

PC3

PE1

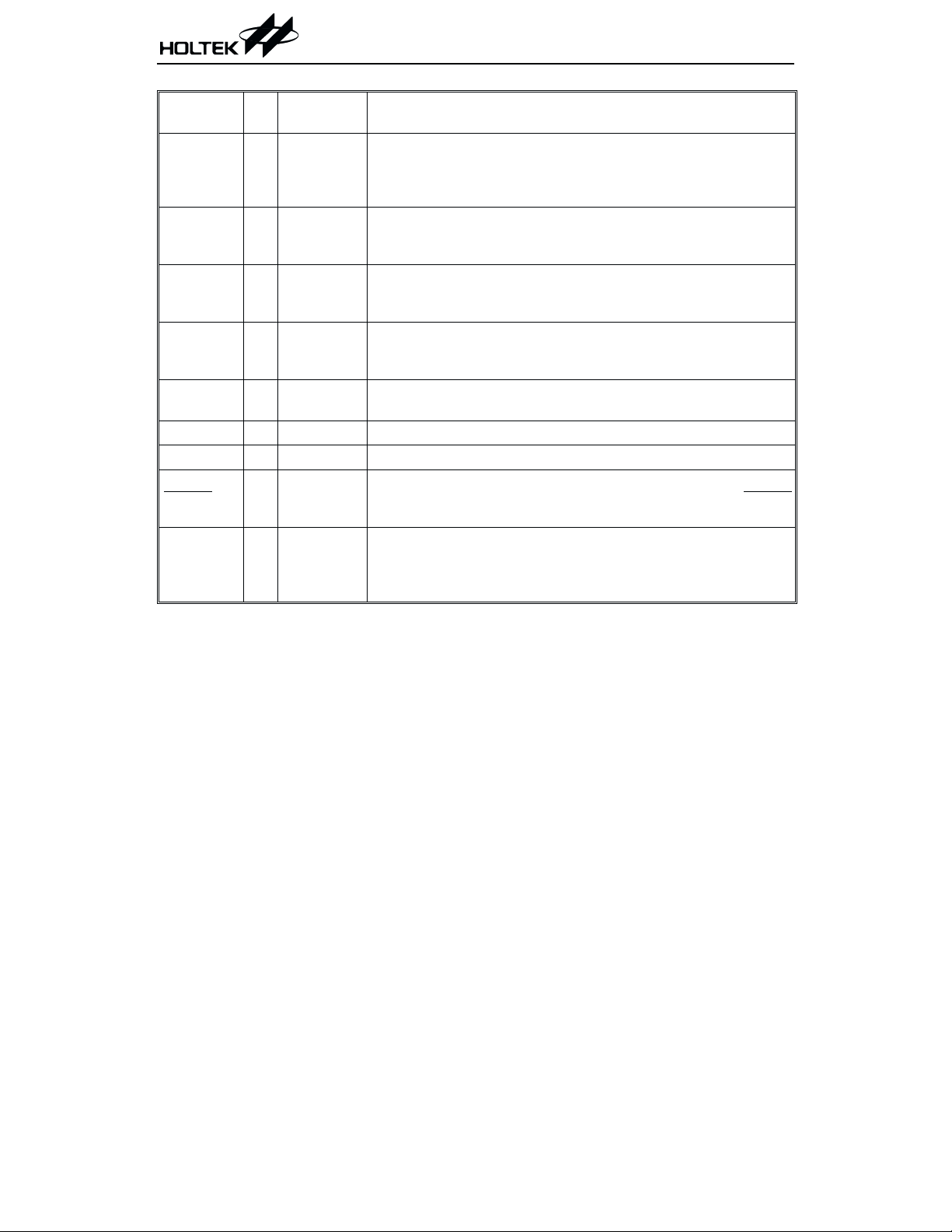

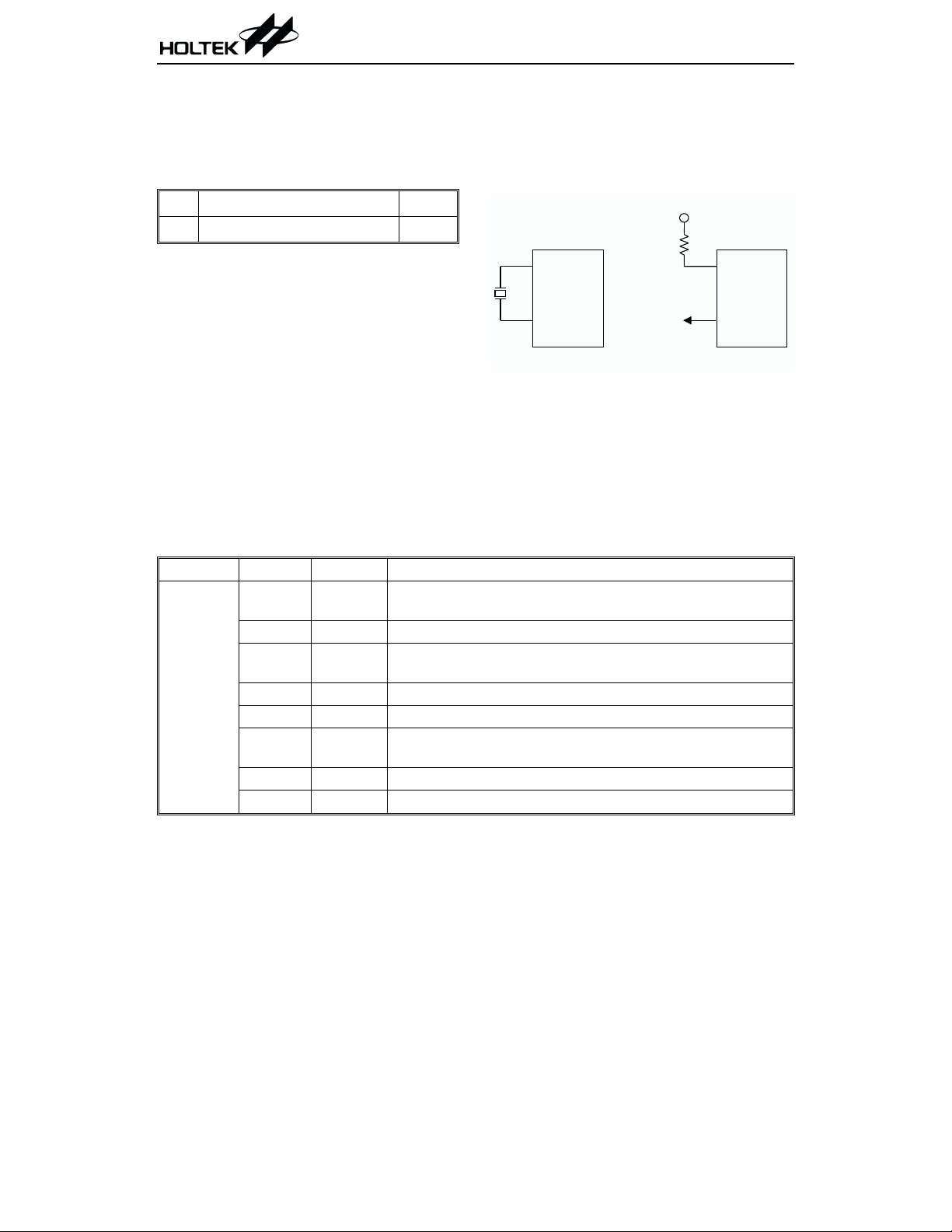

Pin Name I/O

PA0~PA7 I/O

PB0~PB7 I/O

PC0 I/O

PC1 I/O

ROM Code

Option

Wake-up

Pull-high

or None

Pull-high

or None

Wake-up

Pull-high

or None

Wake-up

Pull-high

or None

Description

Bidirectional 8-bit input/output port. Each bit can be configured

as a wake-up input by ROM code option. Software* instructions

determine the CMOS output or schmitt trigger input with or without pull-high resistor 12K.

Bidirectional 8-bit input/output port. Software* instructions de

termine the CMOS output or schmitt trigger input with or without

pull-high resistor.

This pin is an I/O port. Open drain output with pull-high resistor

and can be used as DATA or CLOCK line of PS2. This pin can be

configured as a wake-up input by ROM code option.

This pin is an I/O port. open drain output with pull-high resistor

and can be used as DATA or CLOCK line of . This pin can be con

figured as a wake-up input by ROM code option.

3 August 8, 2000

-

-

Preliminary

HT82K68E

Pin Name I/O

PC2~PC3 I/O

PC4~PC7 I/O

PD0~PD7 I/O

PE0~PE1 I/O

PE2~PE4 O

VDD

VSS

RESET

OSC1

OSC2

¾¾

¾¾

I

IOCrystal or

ROM Code

Option

Wake-up

Pull-high

or None

Pull-high

or None

Pull-high

or None

Pull-high

or None

¾

¾

RC

Description

Bidirectional 2-bit input/output port. Each bit can be configured

as a wake-up input by ROM code option. Software* instructions

determine the CMOS output or schmitt trigger input with or with

out pull-high resistor.

Bidirectional 4-bit input/output port. Software* instructions de

termine the CMOS output or schmitt trigger input with or without

pull-high resistor.

Bidirectional 8-bit input/output port. Software* instructions de

termine the CMOS output or schmitt trigger input with or without

pull-high resistor.

Bidirectional input/output port. Software* instructions determine

the CMOS output or schmitt trigger input with or without

pull-high resistor.

This pin is an NMOS output structure. The pad can function as

LED drivers for the keyboard. I

Positive power supply

Negative power supply, ground

Chip reset input. Active low. Built-in power-on reset circuit to re

set the entire chip. Chip can also be externally reset via RESET

pin

OSC1, OSC2 are connected to an RC network or a crystal for the

internal system clock. In the case of RC operation, OSC2 is the

output terminal for the 1/4 system clock; A 110kW resistor is connected to OSC1 to generate a 2MHZ frequency.

=14mA, @VOL=3.2V

OL

-

-

-

-

Note: *: Software means the ROM code option can be configured by HT-IDE (Holtek Integrated De-

velopment Environment).

Absolute Maximum Ratings

Supply Voltage .............................-0.3V to 5.5V

Input Voltage ................V

Note: These are stress ratings only. Stresses exceeding the range specified under ²Absolute Maxi

mum Ratings² may cause substantial damage to the device. Functional operation of this device

at other conditions beyond those listed in the specification is not implied and prolonged expo

sure to extreme conditions may affect device reliability.

3V to VDD+0.3V

SS-0.

Storage Temperature ................-50°Cto125°C

Operating Temperature .............-25°Cto70°C

4 August 8, 2000

-

-

Preliminary

HT82K68E

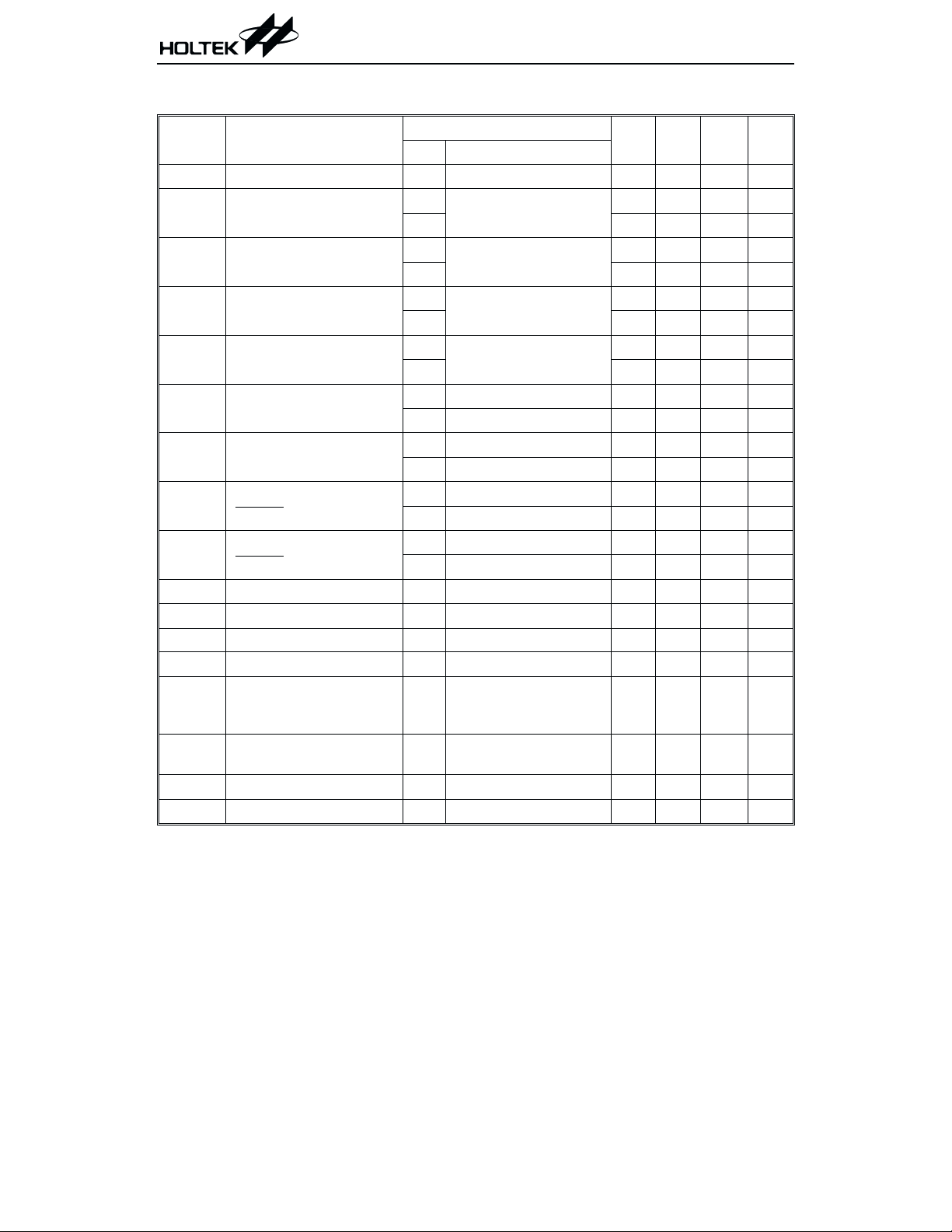

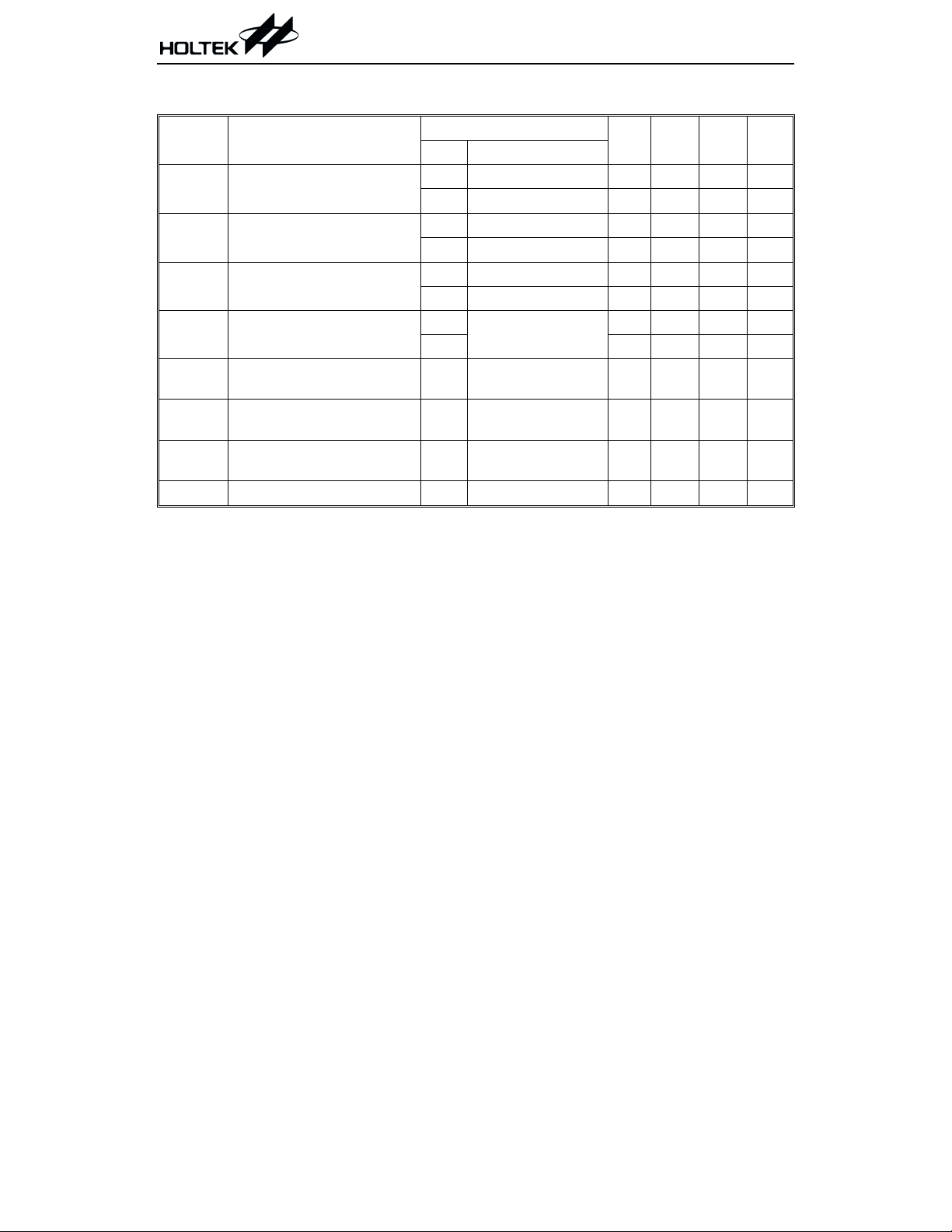

D.C. Characteristics

Symbol Parameter

V

DD

I

DD1

I

DD2

I

STB1

I

STB2

V

IL

V

IH

V

IL1

V

IH1

I

OL

I

OH

I

LED

t

POR

R

PH

R

PH1

Df/f

Df/f1

Operating Voltage

Operating Current

(Crystal OSC)

Operating Current

(RC OSC)

Standby Current

(WDT enabled)

Standby Current

(WDT Disabled)

Input Low Voltage for

I/O Ports

Input High Voltage for

I/O Ports

Input Low Voltage

(RESET

)

Input High Voltage

(RESET

)

I/O Port Sink Current 5V

I/O Port Source Current 5V

LED Sink Current 5V VOL=3.2V 10 14 18 mA

Power-on Reset Time 5V

Internal Pull-high

Resistance of PA, PB, PC,

PD, PE Port

Internal Pull-high

Resistance of DATA, CLK

Frequency Variation 5V Crystal

Frequency Variation 5V RC

Test Conditions

V

DD

Conditions

¾¾

3V

No load, f

5V

3V

No load, f

5V

3V

No load, system HALT

5V

3V

No load, system HALT

5V

3V

5V

3V

5V

3V

5V

3V

5V

V

= 0.5V

OL

V

= 4.5V

OH

SYS

SYS

¾

¾

¾

¾

¾

¾

¾

¾

= 2MHz

= 2MHz

¾

5V

5V

¾

¾

Ta=25°C

Min. Typ. Max. Unit

2.8

¾

¾

¾

¾

¾¾

¾¾

¾¾

¾¾

0

0

2.1

3.5

0

0

2.5

4.1

715

-2.5 -4.5 ¾

5.5 V

¾

0.7 1.5 mA

25mA

1 1.5 mA

25mA

8

mA

15

mA

3

mA

6

mA

¾

¾

¾

¾

¾

¾

¾

¾

1V

1.5 V

3V

5V

0.7 V

1.3 V

3V

5V

mA

¾

mA

120 150 180 ms

51220

25 8

¾¾±1

¾¾±10

kW

kW

%

%

5 August 8, 2000

Preliminary

HT82K68E

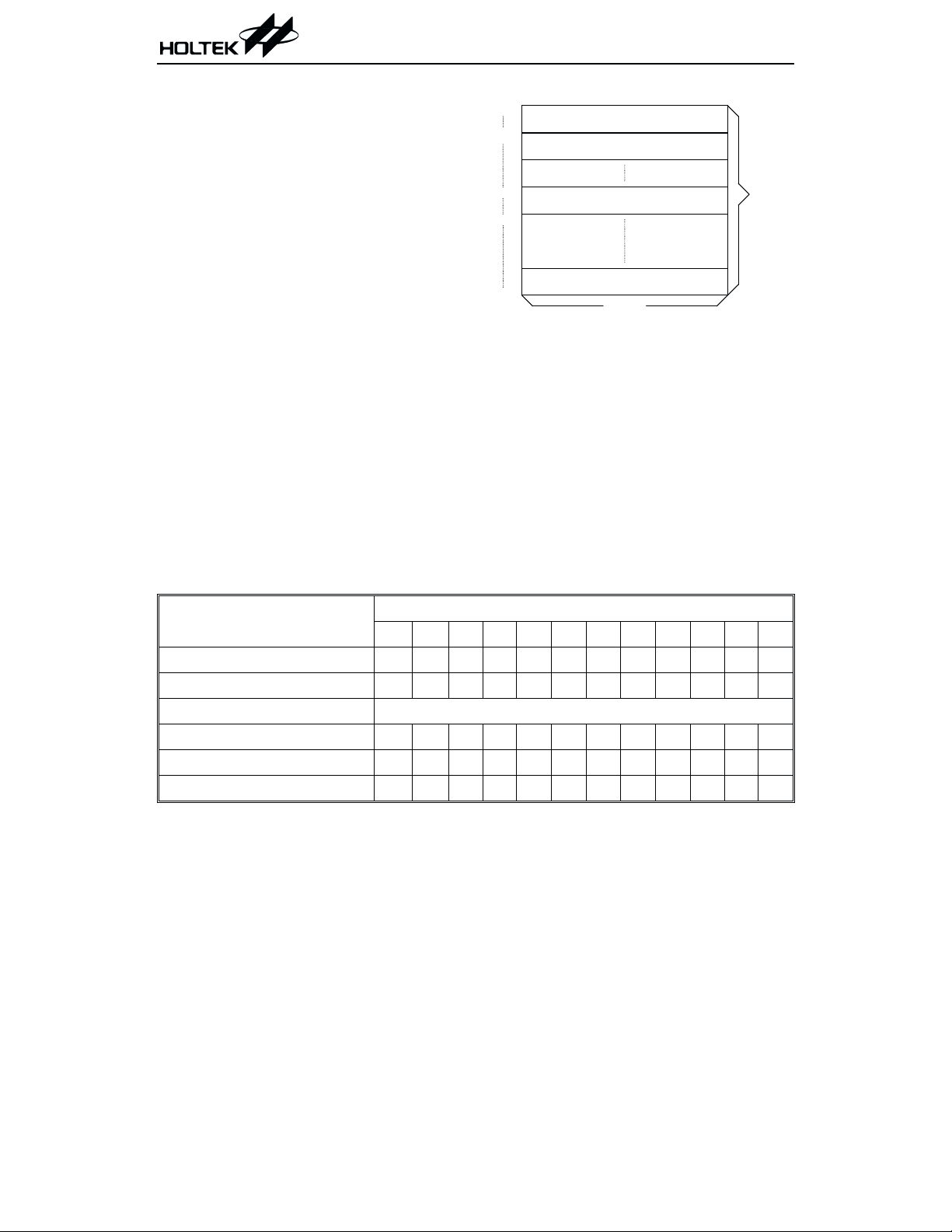

A.C. Characteristics

Symbol Parameter

f

SYS1

f

SYS2

t

WDTOSC

t

WDT1

t

WDT2

t

RES

t

SST

t

INT

Note: t

System Clock

(Crystal OSC)

System Clock (RC OSC)

Watchdog Oscillator

Watchdog Time-out

Period (RC)

Watchdog Time-out

Period (System Clock)

External Reset Low

Pulse Width

System Start-up Timer

Period

Interrupt Pulse Width

= 1/f

SYS

SYS

Ta=25°C

Test Conditions

V

DD

3V

5V

3V

5V

3V

5V

3V

5V 9 17 35 ms

¾

Conditions

¾¾2¾

¾¾

¾¾2¾

¾¾

¾

¾

Without WDT

prescaler

Without WDT

prescaler

¾¾

Power-up or

¾

wake-up from HALT

¾¾

Min. Typ. Max. Unit

MHz

2 20 MHz

MHz

2 20 MHz

45 90 180

35 65 130

12 23 45 ms

1024

¾

1

¾¾ms

1024

¾

1

¾¾ms

¾

¾

t

t

ms

ms

SYS

SYS

6 August 8, 2000

Preliminary

Functional Description

Execution flow

The HT82K68E system clock is derived from ei

ther a crystal or an RC oscillator. The system

clock is internally divided into four

non-overlapping clocks. One instruction cycle

consists of four system clock cycles.

Instruction fetching and execution are

pipelined in such a way that a fetch takes one

instruction cycle while decoding and execution

takes the next instruction cycle. However, the

pipelining scheme causes each instruction to

effectively execute within one cycle. If an in

struction changes the program counter, two cy

cles are required to complete the instruction.

Program counter - PC

The 12-bit program counter (PC) controls the

sequence in which the instructions stored in the

program ROM are executed and its contents

specify a maximum of 4096 addresses.

After accessing a program memory word to

fetch an instruction code, the contents of the

program counter are incremented by one. The

program counter then points to the memory

word containing the next instruction code.

When executing a jump instruction, conditional

skip execution, loading PCL register, subroutine call, initial reset, internal interrupt, exter-

HT82K68E

nal interrupt or return from subroutine, the PC

manipulates the program transfer by loading

-

the address corresponding to each instruction.

The conditional skip is activated by instruction.

Once the condition is met, the next instruction,

fetched during the current instruction execu

tion, is discarded and a dummy cycle replaces it

to get the proper instruction. Otherwise pro

ceed with the next instruction.

The lower byte of the program counter (PCL) is

a readable and writeable register (06H).Moving

data into the PCL performs a short jump. The

destination will be within 256locations.

Once a control transfer takes place, an addi

tional dummy cycle is required.

Program memory - PROM

The program memory is used to store the pro

gram instructions which are to be executed. It

also contains data, table, and interrupt entries,

and is organized with 3072 ´ 16 bits, addressed

by the program counter and table pointer.

Certain locations in the program memory are

reserved for special usage:

·

Location 000

This area is reserved for the initialization

program. After chip reset, the program always begins execution at location 000H.

-

-

-

-

S ystem C lock

OSC2 (RC only)

(N M O S open drain output)

PC

T1 T2 T3 T4 T1 T2 T3 T4 T1 T2 T3 T4

PC

F e tc h IN S T (P C )

Execute IN ST (PC -1)

PC+1 PC+2

F e tc h IN S T (P C + 1 )

Execute IN ST (PC )

F e tc h IN S T (P C + 2 )

Execute IN ST (PC +1)

Execution flow

7 August 8, 2000

Preliminary

m

·

Location 008H

This area is reserved for the timer counter in

terrupt service program. If timer interrupt re

sults from a timer counter overflow, and if the

interrupt is enabled and the stack is not full,

the program begins execution at location

008H.

·

Table location

Any location in the PROM space can be used

as look-up tables. The instructions TABRDC

[m] (the current page, 1 page=256 words) and

TABRDL [m] (the last page) transfer the con

tents of the lower-order byte to the specified

data memory, and the higher-order byte to

TBLH (08H). Only the destination of the

lower-order byte in the table is well-defined,

the other bits of the table word are trans

ferred to the lower portion of TBLH, the re

maining 1 bit is read as 0. The Table

Higher-order byte register (TBLH) is read

only. The TBLH is read only and cannot be re

stored. If the main routine and the ISR (Inter

rupt Service Routine) both employ the table

read instruction, the contents of the TBLH in

the main routine are likely to be changed by

the table read instruction used in the ISR. Errors can occur. In other words, using the table

read instruction in the main routine and the

ISR simultaneously should be avoided. How-

HT82K68E

000H

-

-

008H

n00H

nFFH

-

BFFH

-

-

ever, if the table read instruction has to be ap

plied in both the main routine and the ISR,

the interrupt is supposed to be disabled prior

-

-

to the table read instruction. It will not be en

abled until the TBLH has been backed up.

The table pointer (TBLP) is a read/write regis

ter (07H), which indicates the table location.

Before accessing the table, the location must be

placed in TBLP. All table related instructions

need 2 cycles to complete the operation. These

areas may function as normal program memory

depending upon the requirements.

D evice initialization program

Tim er/event counter interrupt subroutine

Look-up table (256 w ords)

Look-up table (256 w ords)

16 bits

N ote: n ranges from 0 to B

Program memory

Progra

PRO M

-

-

-

Mode

Program Counter

*11 *10 *9 *8 *7 *6 *5 *4 *3 *2 *1 *0

Initial reset 0 0 0 0 00000000

Timer counter overflow 0 0 0 0 00001000

Skip PC+2

Loading PCL

*11 *10 *9 *8

@7 @6 @5 @4 @3 @2 @1 @0

Jump, call branch #11 #10 #9 #8 #7 #6 #5 #4 #3 #2 #1 #0

Return from subroutine S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1 S0

Note: *11~*0: Program counter bits

#11~#0: Instruction code bits

S11~S0: Stack register bits

@7~@0: PCL bits

8 August 8, 2000

Preliminary

Stack register - STACK

This is a special part of the memory which is

used to save the contents of the program coun

ter (PC) only. The stack is organized into six lev

els and is neither part of the data nor part of the

program space, and is neither readable nor

writeable. The activated level is indexed by the

stack pointer (SP) and is neither readable nor

writeable. At a subroutine call or interrupt ac

knowledgement, the contents of the program

counter are pushed onto the stack. At the end of

a subroutine or an interrupt routine, signaled

by a return instruction (RET or RETI), the pro

gram counter is restored to its previous value

from the stack. After a chip reset, the SP will

point to the top of the stack.

If the stack is full and a non-masked interrupt

takes place, the interrupt request flag will be re

corded but the acknowledgement will be inhib

ited. When the stack pointer is decremented (by

RET or RETI), the interrupt will be serviced. This

feature prevents stack overflow allowing the pro

grammer to use the structure more easily. In a

similar case, if the stack is full and a ²CALL² is

subsequently executed, stack overflow occurs and

the first entry will be lost (only the most recent

four return addresses are stored).

HT82K68E

Indirect A ddressing R egister 0

00H

01H

Indirect A ddressing R egister 1

-

-

-

-

-

-

-

02H

03H

04H

05H

06H

07H

08H

09H

0AH

0BH

0C H

0D H

0EH

0FH

10H

11H

12H

13H

14H

15H

16H

17H

18H

19H

1AH

1BH

1C H

1D H

1EH

1FH

20H

MP0

MP1

ACC

PCL

TBLP

TBLH

WDTS

STATUS

IN T C

TM R

TM R C

PA

PAC

PB

PBC

PC

PCC

PD

PDC

PE

PEC

Special P urpose

DATA MEM ORY

: U nused.

R ead as ²00

²

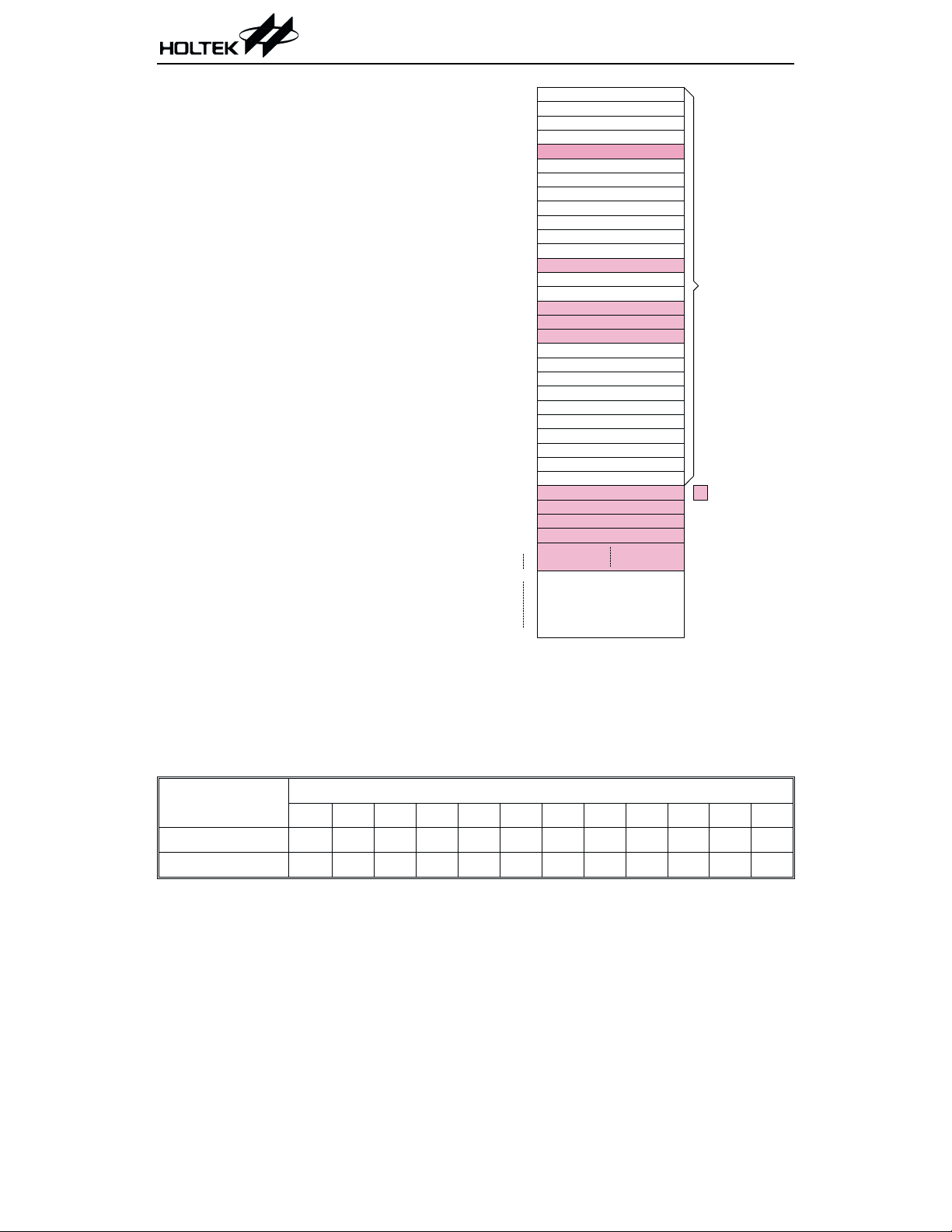

Data memory - RAM

The data memory is designed with 184 ´ 8 bits.

It is divided into two functional groups: special

function registers and general purpose data

memory (160´8). Most of them are read/write,

60H

G eneral P urpose

DATA MEM ORY

(160 B ytes)

FFH

RAM mapping

but some are read only.

The special function registers include the Indirect Addressing register 0 (00H), the Memory

Pointer register 0 (MP0;01H), the Indirect Ad

dressing register 1 (02H), the Memory Pointer

register 1 (MP1;03H), the Accumulator

Instruction(s)

*11 *10 *9 *8 *7 *6 *5 *4 *3 *2 *1 *0

(ACC;05H), the Program Counter Lower-byte

register (PCL;06H), the Table Pointer

(TBLP;07H), the Table Higher-order byte regis

ter (TBLH;08H), the Watchdog Timer option Set

ting register (WDTS;09H), the Status register

Table Location

TABRDC [m] P11 P10 P9 P8 @7 @6 @5 @4 @3 @2 @1 @0

TABRDL [m] 1 0 1 1 @7 @6 @5 @4 @3 @2 @1 @0

Note: *11~*0: Table location bits

P11~P8: Current program counter bits

@7~@0: Table location bits

9 August 8, 2000

-

-

Preliminary

HT82K68E

(STATUS;0AH), the Interrupt Control register

(INTC;0BH), the timer counter register

(TMR;0DH), the timer counter control register

(TMRC;0EH), the I/O registers (PA;12H,

PB;14H, PC;16H, PD;18H, PE;1AH) and the I/O

control registers (PAC;13H, PBC;15H, PCC;17H,

PDC;19H, PEC;1BH). The remaining space be

fore the 60H is reserved for future expanded us

age and reading these locations will get the result

00H. The general purpose data memory, ad

dressed from 60H to FFH, is used for data and

control information under instruction com

mand.

All data memory areas can handle arithmetic,

logic, increment, decrement and rotate opera

tions directly. Except for some dedicated bits,

each bit in the data memory can be set and re

set by the SET [m].i and CLR [m].i instructions,

respectively. They are also indirectly accessible

through Memory pointer registers (MP0;01H,

MP1;03H).

Indirect addressing register

Location 00H and 02H are indirect addressing

registers that are not physically implemented.

Any read/write operation of [00H] and [02H]

can access the data memory pointed to by MP0

(01H) and MP1 (03H) respectively. Reading location 00H or 02H indirectly will return the result 00H. Writing indirectly results in no

operation.

The function of data movement between two indirect addressing registers is not supported.

The memory pointer registers, MP0 and MP1,

are 8-bit registers which can be used to access

the data memory by combining corresponding

indirect addressing registers.

Accumulator

The accumulator is closely related to the ALU

operations. It is also mapped to location 05H of

the data memory and is capable of carrying out

immediate data operations. The data move

ment between two data memory locations must

pass through the accumulator.

Arithmetic and logic unit - ALU

This circuit performs 8-bit arithmetic and logic

operation. The ALU provides the following func

tions:

·

Arithmetic operations (ADD, ADC, SUB,

-

-

-

-

-

-

-

SBC, DAA)

·

Logic operations (AND, OR, XOR, CPL)

·

Rotation (RL, RR, RLC, RRC)

·

Increment and Decrement (INC, DEC)

·

Branch decision (SZ, SNZ, SIZ, SDZ ....)

The ALU not only saves the results of a data op

eration but also changes the status register.

Status register - Status

The 8-bit status register (0AH) contains the

zero flag (Z), carry flag (C), auxiliary carry flag

(AC), overflow flag (OV), power down flag (PD)

and watch dog time-out flag (TO). The status

register not only records the status information

but also controls the operation sequence.

With the exception of the TO and PD flags, bits

in the status register can be altered by instruc

tions like most other registers. Any data writ

ten into the status register will not change the

TO or PD flags. It should be noted that operations related to the status register may give different results from those intended. The TO and

PD flags can only be changed by system power

up, Watchdog Timer overflow, executing the

HALT instruction and clearing the Watchdog

Timer.

The Z, OV, AC and C flags generally reflect the

status of the latest operations.

In addition, on entering an interrupt sequence

or executing a subroutine call, the status regis

ter will not be automatically pushed onto the

stack. If the contents of status are important

and if the subroutine can corrupt the status

register, precaution must be taken to save it

properly.

-

-

-

-

-

10 August 8, 2000

Preliminary

HT82K68E

Interrupt

The HT82K68E provides an internal timer

counter interrupt. The interrupt control regis

ter (INTC;0BH) contains the interrupt control

bits to set not only the enable/disable status but

also the interrupt request flags.

Once an interrupt subroutine is serviced, all

other interrupts will be blocked (by clearing the

EMI bit). This scheme may prevent any further

interrupt nesting. Other interrupt requests may

occur during this interval but only the interrupt

request flag is recorded. If a certain interrupt re

quires servicing within the service routine, the

EMI bit and the corresponding bit of the INTC

may be set to allow interrupt nesting. If the

stack is full, the interrupt request will not be ac

knowledged, even if the related interrupt is en

abled, until the SP is decremented. If immediate

service is desired, the stack must be prevented

from becoming full.

All these kinds of interrupt have the wake-up

capability. As an interrupt is serviced, a control

transfer occurs by pushing the program counter

onto the stack followed by a branch to a subrou

tine at the specified location in the program

memory. Only the program counter is pushed

onto the stack. If the contents of the register and

Status register (STATUS) are altered by the in

terrupt service program which corrupt the de

sired control sequence, the contents should be

saved in advance.

The internal timer counter interrupt is initialized

by setting the timer counter interrupt request

flag (T0F; bit 5 of INTC), which is normally

caused by a timer counter overflow. When the in

terrupt is enabled, and the stack is not full and

the T0F bit is set, a subroutine call to location

08H will occur. The related interrupt request flag

(T0F) will be reset and the EMI bit cleared to dis

able further interrupts.

During the execution of an interrupt subroutine,

other interrupt acknowledgements are held un

til the RETI instruction is executed or the EMI

bit and the related interrupt control bit are set to

1 (if the stack is not full). To return from the in

terrupt subroutine, a RET or RETI instruction

may be invoked. RETI will set the EMI bit to en

able an interrupt service, but RET will not.

Interrupts occurring in the interval between

the rising edges of two consecutive T2 pulses,

-

-

-

-

-

-

-

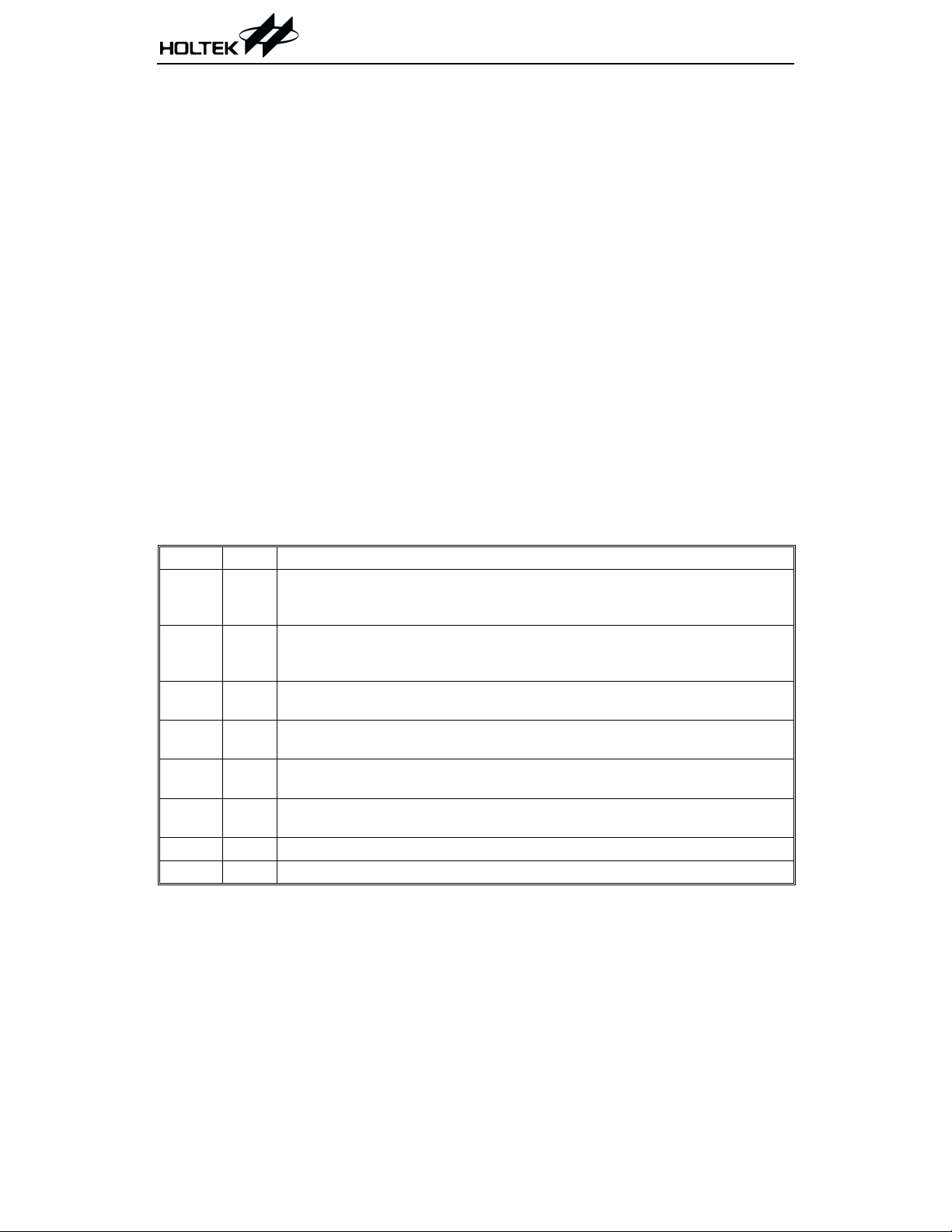

Labels Bits Function

C is set if the operation results in a carry during an addition operation or if a bor-

C0

AC 1

Z2

OV 3

PD 4

TO 5

¾

¾

row does not take place during a subtraction operation; otherwise C is cleared. C

is also affected by a rotate through carry instruction.

AC is set if the operation results in a carry out of the low nibbles in addition or if

no borrow from the high nibble into the low nibble in subtraction; otherwise AC

is cleared.

Z is set if the result of an arithmetic or logic operation is zero; otherwise Z is

cleared.

OV is set if the operation results in a carry into the highest-order bit but not a

carry out of the highest-order bit, or vice versa; otherwise OV is cleared.

PD is cleared when either a system power-up or executing the CLR WDT in

struction. PD is set by executing the HALT instruction.

TO is cleared by a system power-up or executing the CLR WDT or HALT in

struction. TO is set by a WDT time-out.

6 Undefined, read as "0"

7 Undefined, read as "0"

Status register

11 August 8, 2000

-

-

Preliminary

HT82K68E

will be serviced on the latter of the two T2

pulses, if the corresponding interrupts are en

abled. In the case of simultaneous requests, the

following table shows the priority that is ap

plied. These can be masked by resetting the

EMI bit.

No. Interrupt Source Vector

a Timer counter overflow 08H

The timer counter interrupt request flag (T0F),

enable timer counter bit (ET0I), and enable

master interrupt bit (EMI) constitute an inter

rupt control register (INTC) which is located at

0BH in the data memory. EMI, ET0I, are used

to control the enabling/disabling of interrupts.

These bits prevent the requested interrupt

from being serviced. Once the interrupt request

flags (T0F) are set, they will remain in the

INTC register until the interrupts are serviced

or cleared by a software instruction.

It is suggested that a program does not use the

²CALL subroutine² within the interrupt sub

routine. Because interrupts often occur in an un

predictable manner or need to be serviced

immediately in some applications, if only one

stack is left and enabling the interrupt is not well

controlled, once the ²CALL subroutine² operates in

-

the interrupt subroutine it will damage the original

control sequence.

-

Oscillator configuration

There are two oscillator circuits in HT82K68E.

V

DD

OSC1

-

f

OSC2

Crystal Oscillator RC Oscillator

(NMOS Open

Drain Output)

/4

SYS

System oscillator

Both are designed for system clocks; the RC os

cillator and the Crystal oscillator, which are de

termined by mask options. No matter what

-

oscillator type is selected, the signal provides

-

the system clock. The HALT mode stops the

system oscillator and resists the external signal

to conserve power.

OSC1

OSC2

-

-

Register Bit No. Label Function

Controls the master (global) interrupt

(1= enabled; 0= disabled)

Undefined, read as "0"; programming must be "0"

Controls the timer counter interrupt

(1= enabled; 0= disabled)

Undefined, read as "0"

Undefined, read as "0"; programming must be "0"

Internal timer counter request flag

(1= active; 0= inactive)

Undefined, read as "0"

Unused bit, read as "0"

INTC

(0BH)

0 EMI

1

¾

2 ET0I

3

4

¾

¾

5 T0F

6

7

¾

¾

INTC register

12 August 8, 2000

Loading...

Loading...