Holtek Semiconductor Inc HT48CA0 Datasheet

Features

•

Operating voltage: 2.2V ~3.6V

•

Ten bidirectional I/O lines

•

Six schmitt trigger input lines

•

One carrier output (1/2 or 1/3 duty)

•

On-chip crystal and RC oscillator

•

Watchdog timer

•

1K×14 program ROM

•

32×8 data RAM

•

Low voltage reset function

General Description

The HT48CA0 is an 8-bit high performance

RISC-like micro controller specifically d es igned

for multiple I/O prod uct applications. The device is particularly suita ble for use in prod ucts

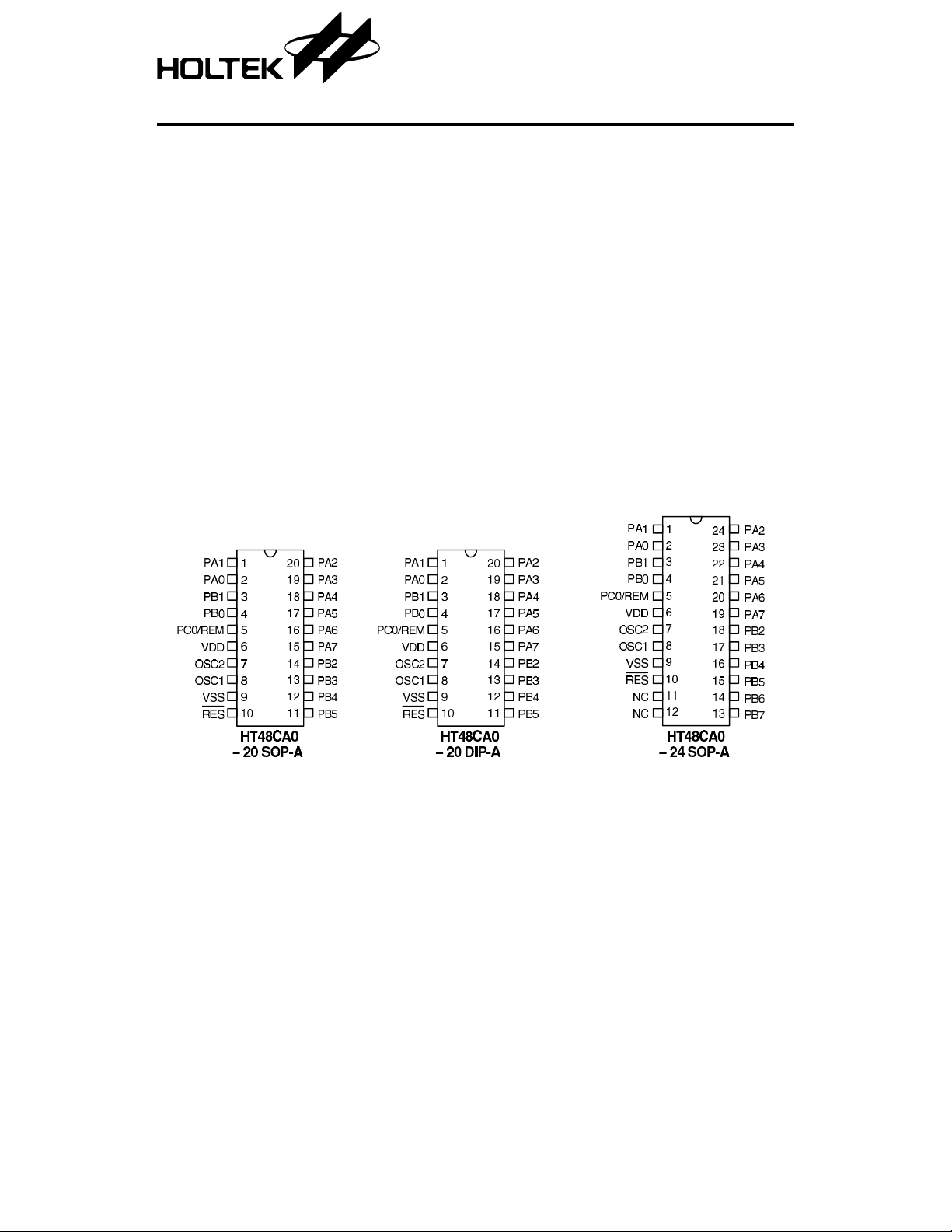

Pin Assignment

HT48CA0

8-bit Microcontroller

•

Halt function and wake-up feature reduce

power consumption

•

62 powerful instructions

•

Up to 1µs instruction cycle with 4MHz

system clock

•

All instructions in 1 or 2 machine cycles

•

14-bit table read instructions

•

One-level subroutine nesting

•

Bit manipulation instructions

such as remote controllers, fan/light controllers, washing machi ne controllers, sca les, toys

and various subsystem controllers. A halt feature is included to reduce power consumption.

1 23rd July ’98

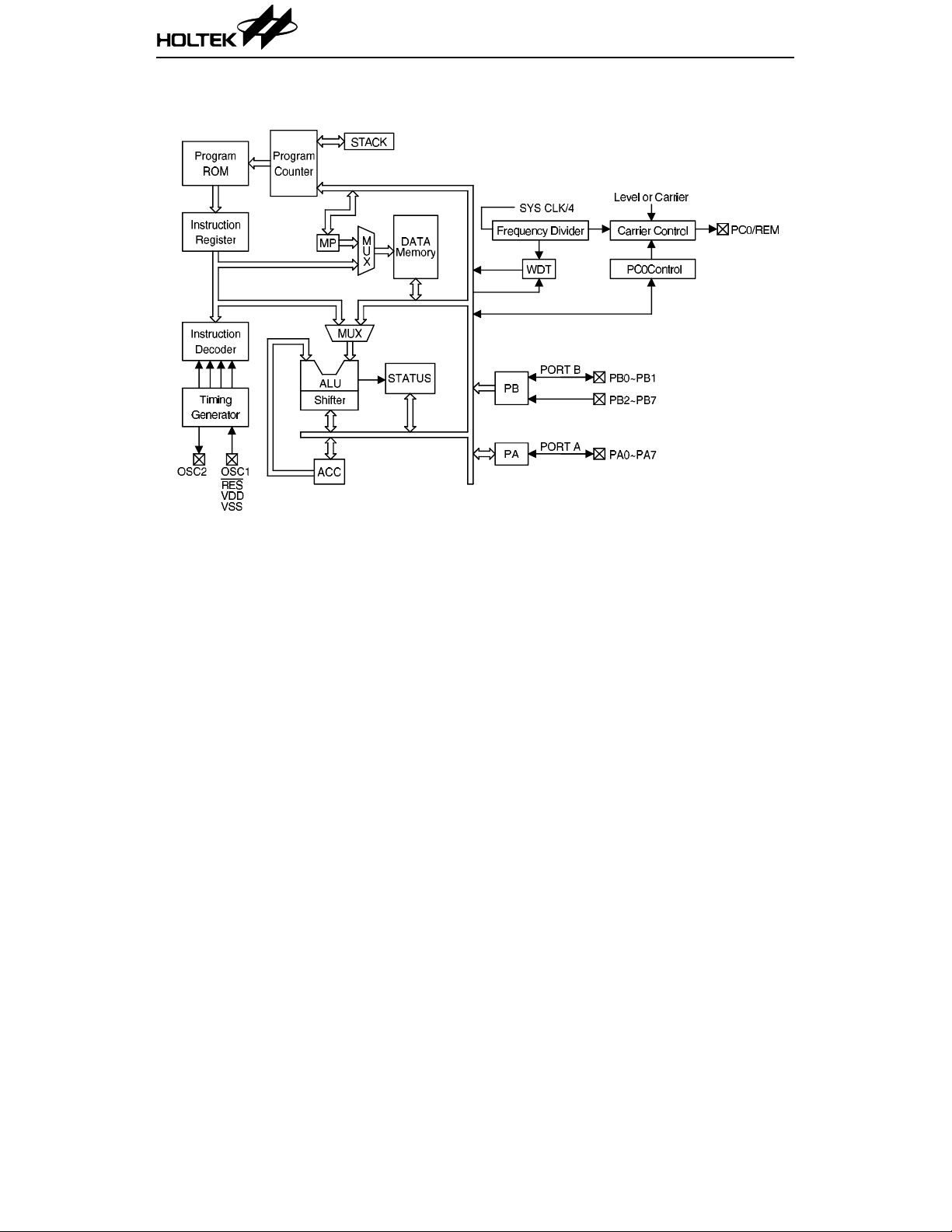

Block Diagram

HT48CA0

2 23rd July ’98

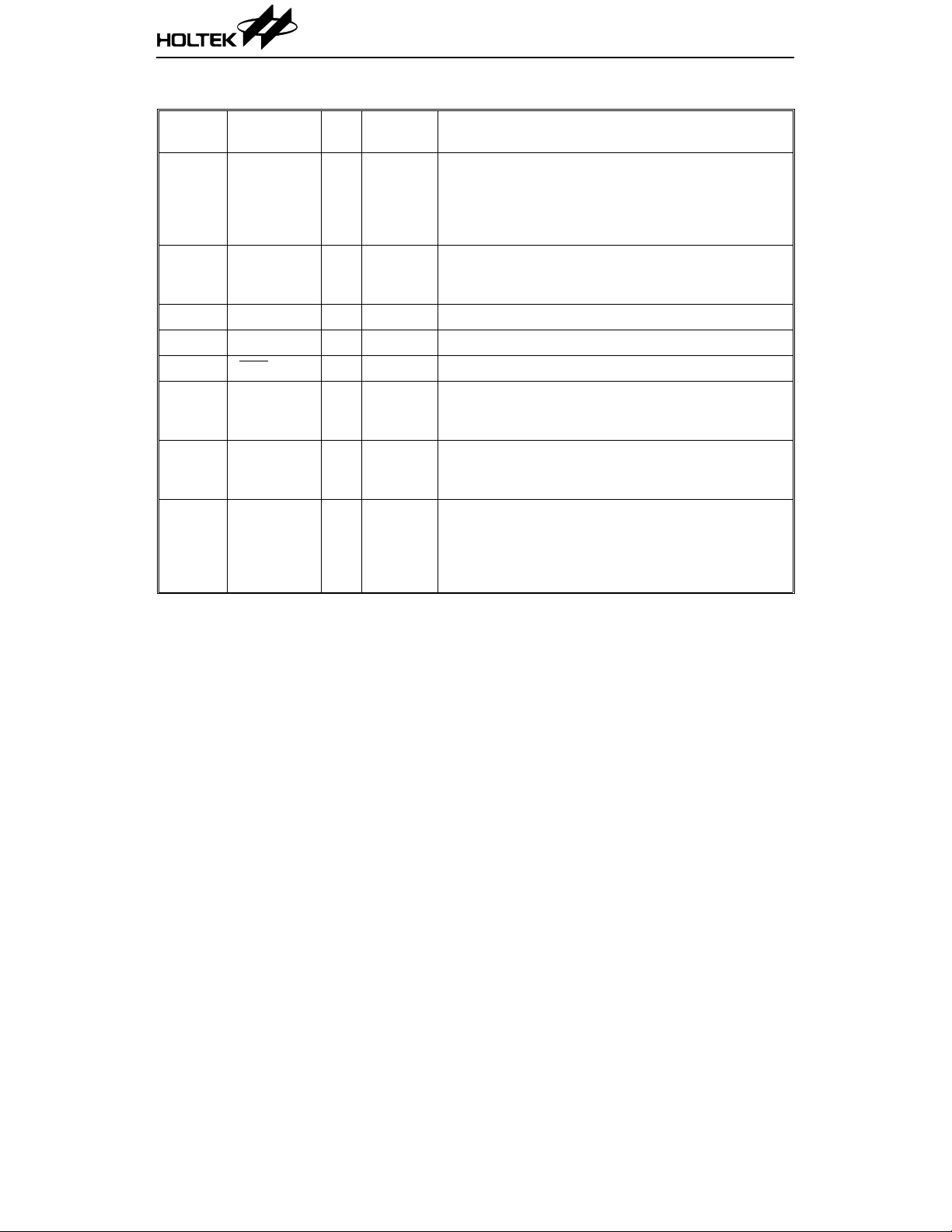

Pad Description

HT48CA0

Pad No. Pad Name I/O

1, 22 PB0, PB1 I/O

2 PC0/REM O

3 VDD — — Positive power supply

6 VSS — — Negative power supply, GND

7

13~8 PB2~PB7 I

21~14 PA0~PA7 I/O —

RES I — Schmitt trigger reset input. Active low.

OSC1

OSC2

Mask

Option

Wake-up

or None

Level or

Carrier

Wake-up

or None

IOCrystal or

RC

Function

2-bit bidirectional input/output lines with pull-high

resistors. Each bit can be determined as NMOS output

or schmitt trigger input by software instructions. Each

bit can also be configu red as wake-up i nput by mask

option.

Level or carrier output pin

PC0 can be set as C MO S outp ut pin o r carri er outp ut

pin by mask option.

6-bit schmitt trigger input lines with pull-high

resistors. Each bit can be configured as a wake-up

input by mask option .

Bidirectional 8-bit input/output port with pull-high

resistors. Each bit can be determined as NMOS output

or schmitt trigger input by software instructions.

OSC1, OSC2 are connected to an RC network or a

crystal (determined by mask option) for the internal

system clock. In the case of RC operation, OSC2 is the

output terminal for 1/4 system clock (NMOS open

drain output).

3 23rd July ’98

Pad Assignment

* The IC substrate should be connected to VSS in the PCB layout artwork.

* The TMR pad must be bonded to VDD or VSS if the TMR pad is not used.

HT48CA0

Absolu te Maxim um Ratings *

Supply Voltage.................................–0.3V to 4V Storage Temperature.................–50°C to 125°C

Input Voltage................. V

*Note: These are stress ra tings on ly. Stresses exceeding the range specified under “Ab solute Maxi -

mum Ratings” ma y cause substantial damage to the device. Functional operation of this

device at other conditions beyond those listed in the specification is not implied and prolonged

exposure to extreme condition s may affect device reliability.

–0.3V to VDD+0.3V Operating Temperature............... –25°C to 70°C

SS

4 23rd July ’98

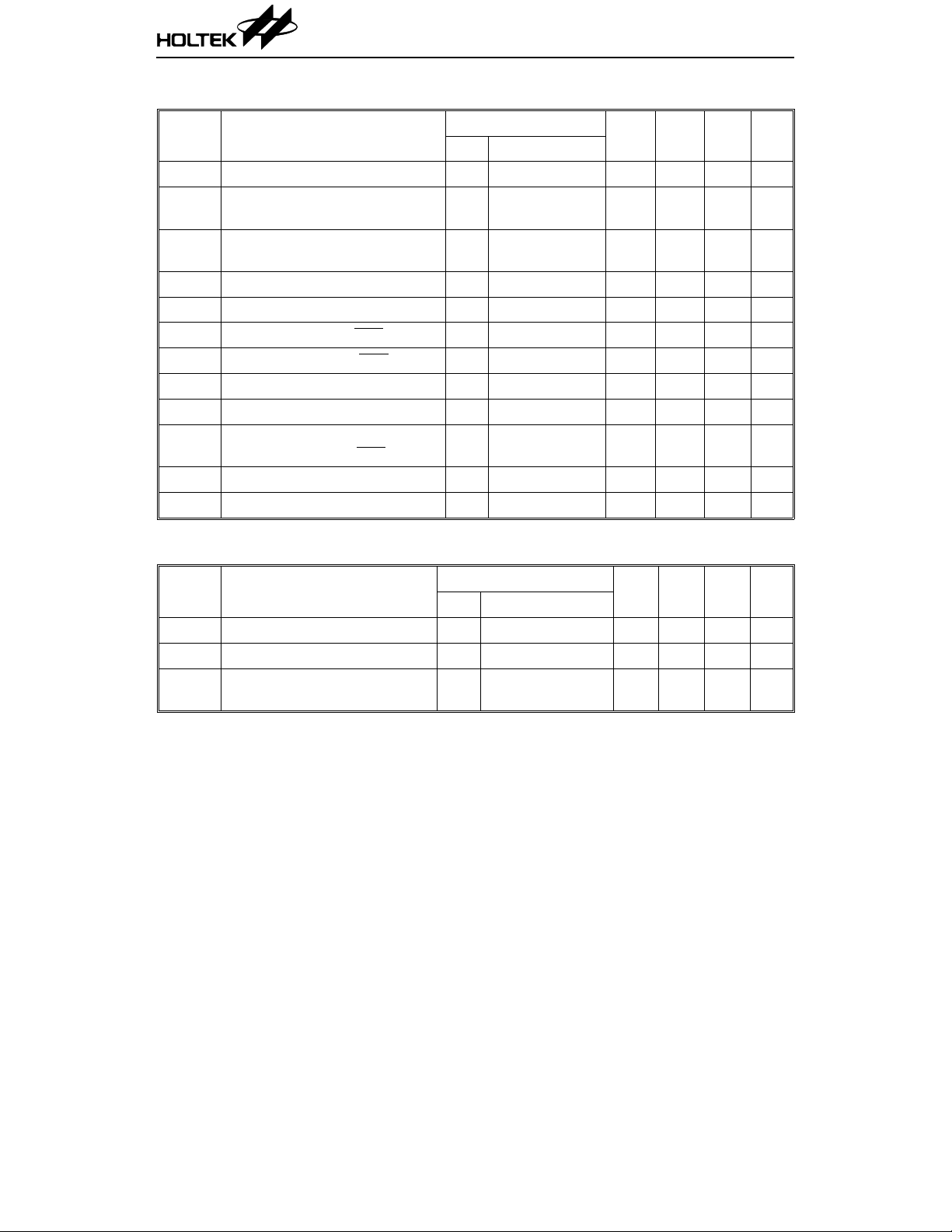

HT48CA0

D.C. Characteristics Ta=25°C

Symbol Parameter

V

I

DD

I

STB

V

V

V

V

I

OL

I

OH

R

R

V

Operating Voltage — — 2.2 — 3.6 V

DD

Operating Current 3V

Standby Current 3V

Input Low Voltage for I/O Ports 3V — 0 — 1.05 V

IL1

Input High Voltage for I/O Ports 3V — 1.95 — 3 V

IH1

Input Low Voltage (RES) 3V — — 1.5 — V

IL2

Input High Voltage (RES) 3V — — 2.4 — V

IH2

I/O Ports Sink Current 3V VOL=0.3V 1.5 2.5 — mA

I/O Ports Source Current 3V VOH=2.7V –1 –1.5 — mA

Pull-high Resistance of PA

PH1

Port, PB0~PB1 and

Pull-high Resistance of PB2~PB7 3V — — 60 — kΩ

PH2

Low Voltage Reset 3V — 1.8 2.0 2.2 V

LVR

RES

Test Conditions

V

DD

Conditions

No load,

f

=4MHz

SYS

No load,

system HALT

Min. Typ. Max. Unit

— 0.7 1.5 mA

——1µA

3V — — 60 — k

Ω

A.C. Characteristics Ta=25°C

Symbol Parameter

f

SYS

t

RES

t

SST

Note: t

System Clock 3V — 400 — 4000 kHz

External Reset Low Pulse Width — — 1 — — µs

System Start-up timer

Period

=1/f

SYS

SYS

Test Conditions

V

DD

—

Conditions

Power-up or

wake-up from halt

5 23rd July ’98

Min. Typ. Max. Unit

—1024—t

SYS

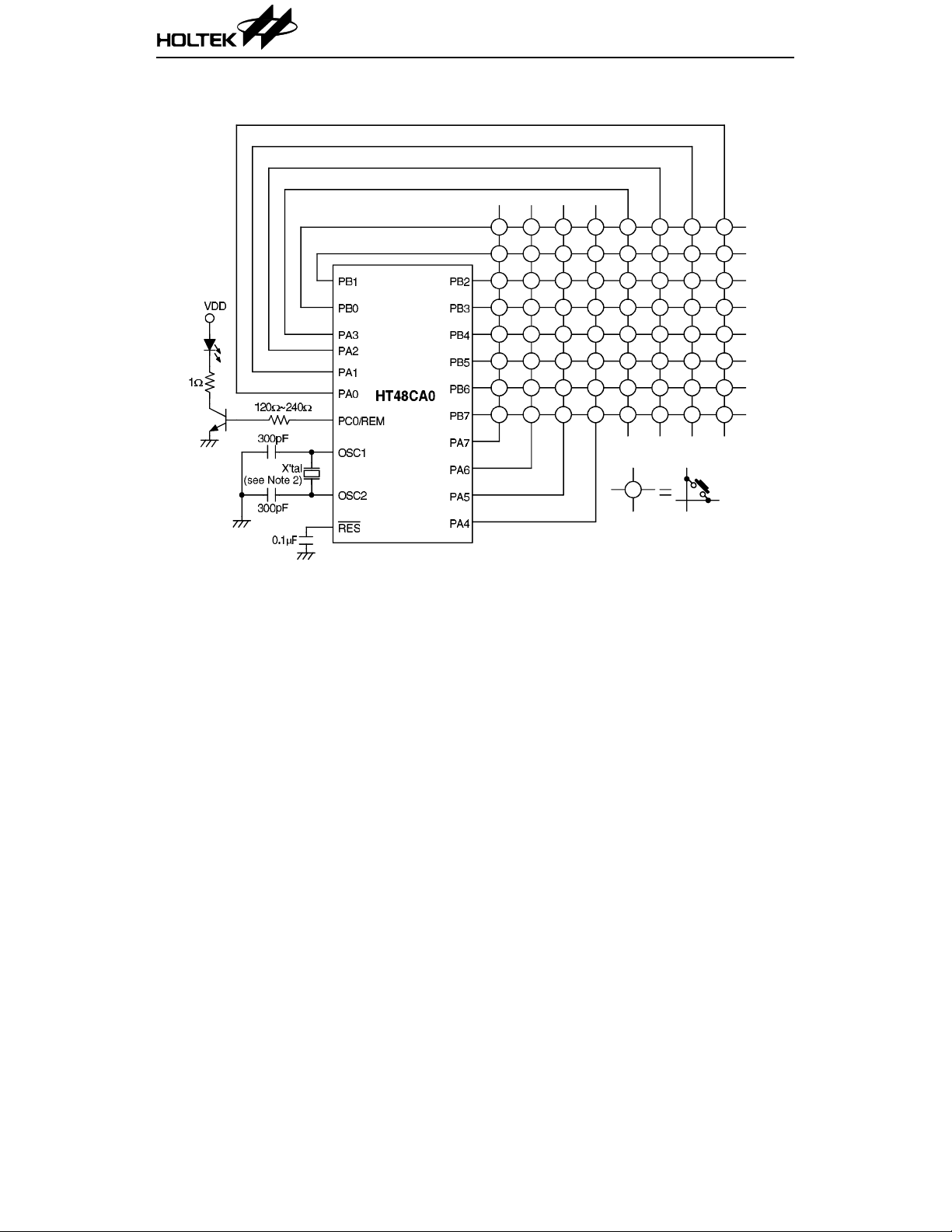

Application Circuit

HT48CA0

Notes: It is recommended tha t a 0.1µF decoupling capacitor is placed between VSS and VDD.

If the crystal has a value above 1MHz the capacitors are not required.

6 23rd July ’98

System Architect ure

Execution flow

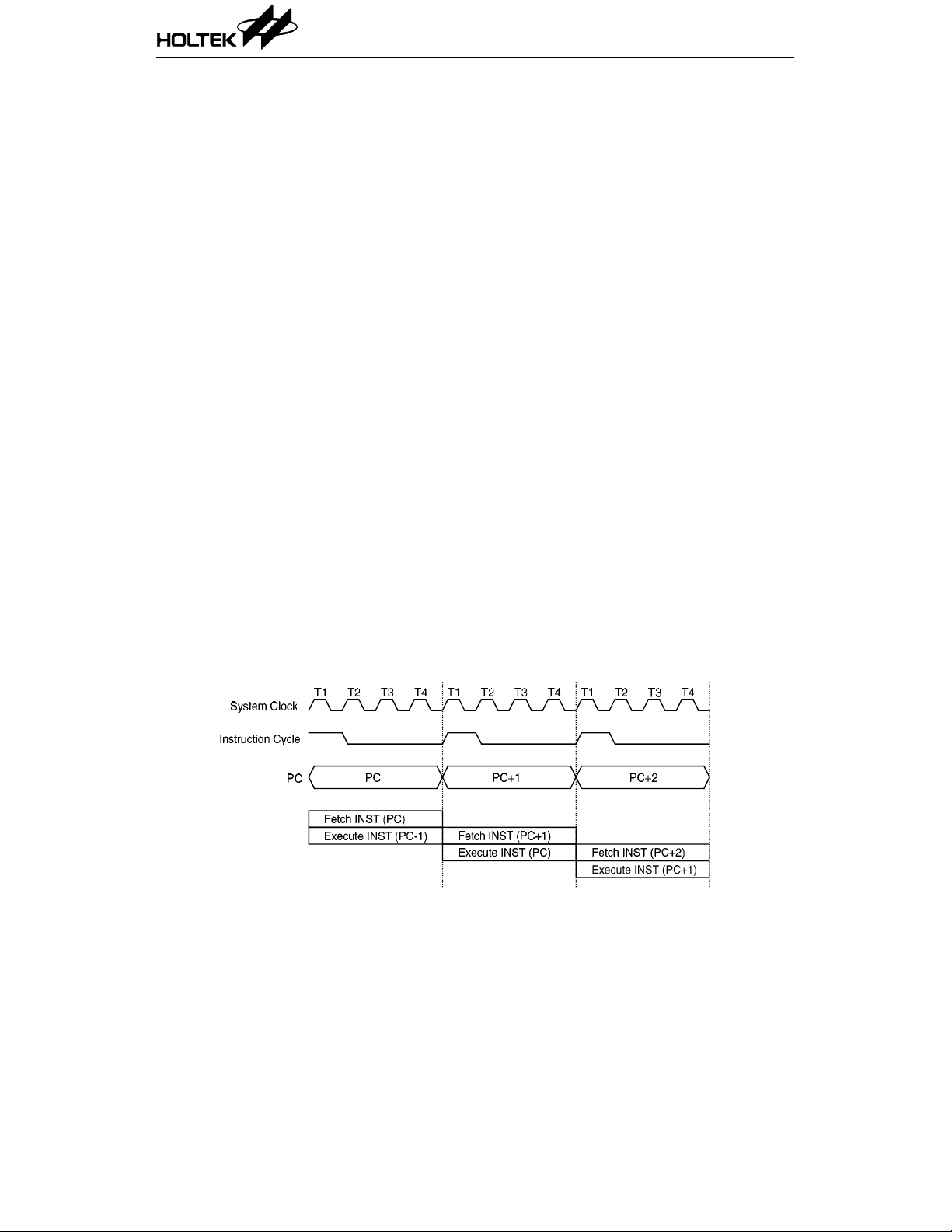

The HT48CA0 system clock can be derived from

a crystal/ceramic res onator oscillator. It is internally divided into four non-overlapping

clocks. One instruction cycle consists of four

system clock cycles.

Instruction fetching and execution are pipelined in such a wa y that a fetch takes one instruction cycle while decoding and execution

takes the next instructi on cycle. However, the

pipelining scheme causes each instruction to

effectively execute within one cycle. If an instruction changes the program cou nte r, two cycles are required to comp lete the instruction.

Program counter – PC

The 10-bit program co unter (PC) controls the

sequence in which the instructions stored in

program ROM are executed and its contents

specify a maximum of 10 24 addresses.

After accessing a program memory word to

fetch an instruction code, the contents of the

program counter are incremented by one. The

program counter then points to the memory

word containing the next instruction code.

When executing a jump instruction, conditional

skip execution, loading PCL register, subroutine call, initial reset or return from subroutine,

the PC manipulates the program transfer by

loading the addr ess corresponding to each instruction.

HT48CA0

The conditional skip is activated by instruction.

Once the condition is met, the next instruction,

fetched during the current instruction execution, is discarded and a dummy cycle replaces it

to get the proper instruction. Otherwise proceed with the next instruction.

The lower byte of the program counter (PCL) is

a readable and writeable re gister (06H). Moving data into the PCL performs a short jump.

The destination will be within 256 locations.

When a control tran sfer takes place, an additional dummy cycle is required.

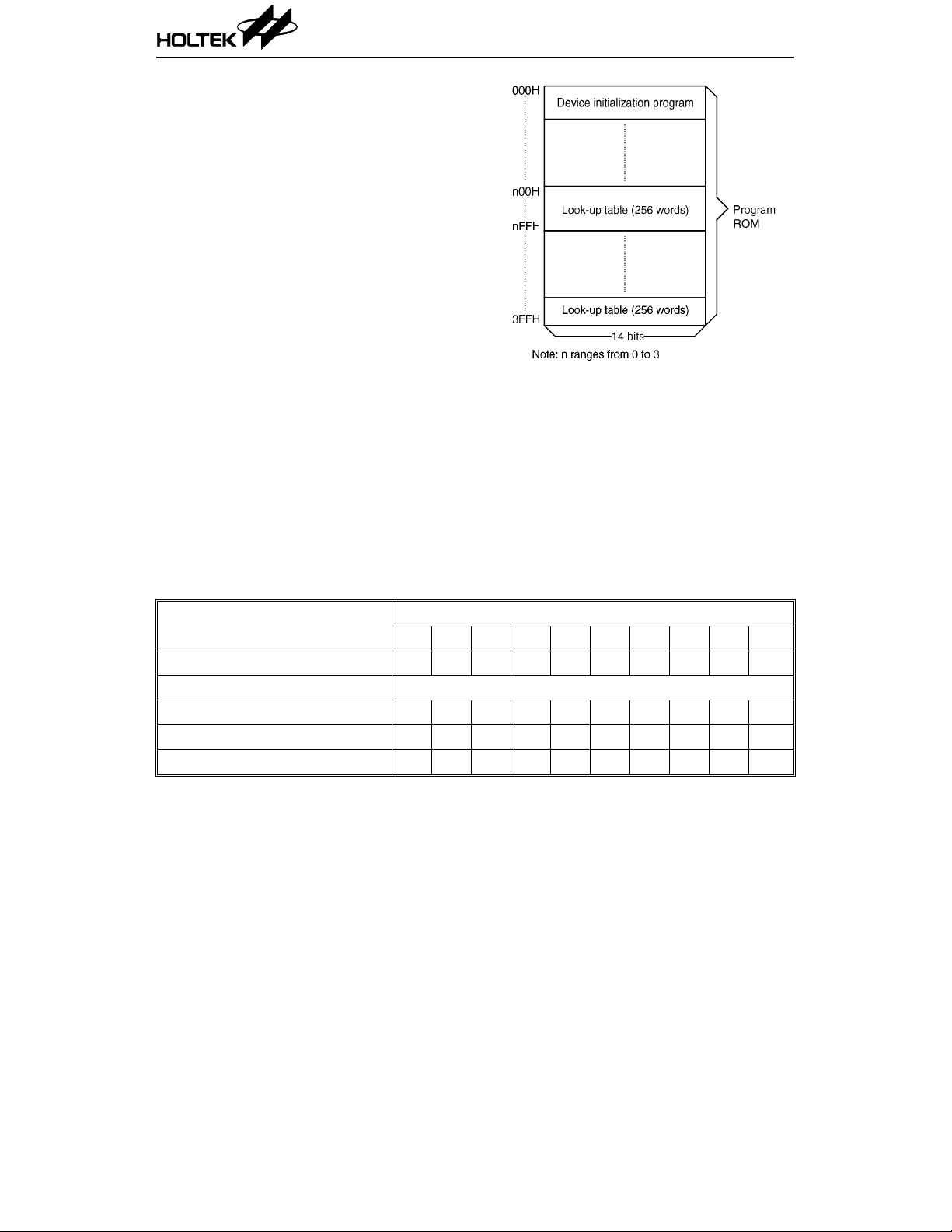

Program memory – ROM

The program memory is used to store the program instructions which are to be executed. It

also contains data and ta ble and is organized

into 1024

counter and table pointer.

Certain locations in the progra m memory are

reserved for special usage:

•

Location 000H

This area is reserved for the initialization

program. After chip reset, the program always

begins execution at location 000H.

•

Table location

Any location in the ROM space can be used as

look-up tables. The instructions TABRDC [m]

(the current page, 1 page=256 words) and

TABRDL [m] (the last page) transfer the contents of the lower-order byte to the specified

×14 bits, addressed by the program

Execution flow

7 23rd July ’98

data memory, and the higher-order byte to

TBLH (08H). Only the destination of the

lower-order byte in the table is well-defin ed,

the other bits of the table word are transferred

to the lower portion of TBLH, the remaining 2

bits are read as “0”. The Table Higher-order

byte register (TBLH) is read only. The tab le

pointer (TBLP) is a read/write regi ster (07H),

where P indicates the table location. Before

accessing the table, the location must be

placed in TBLP. The TBLH is read only and

cannot be restore d. All table related instructions need 2 cycles to com ple te the o pera tio n.

These areas may function as normal program

memory depending upon the requirements.

Stack register – STACK

This is a special part of the memory used to save

the contents of the progra m counter (PC) only.

The stack is organized into one level and is

neither part of the data nor part of the program

space, and is neither readable nor writeable.

The activated level is indexed by the stack

pointer (SP) and is neith er readable nor writeable. At a subroutine call the contents of the

program counter are pushed onto th e stack. At

the end of a subroutine signaled by a return

instruction (RET), the program counter is restored to its previous value from the stack. After

a chip reset, the SP will point to the top of the stack.

HT48CA0

Program memory

If the stack is full and a “CALL” is subsequently

executed, stack overflow occurs and the first

entry will be lost (o nly the most recent retu rn

address is stored).

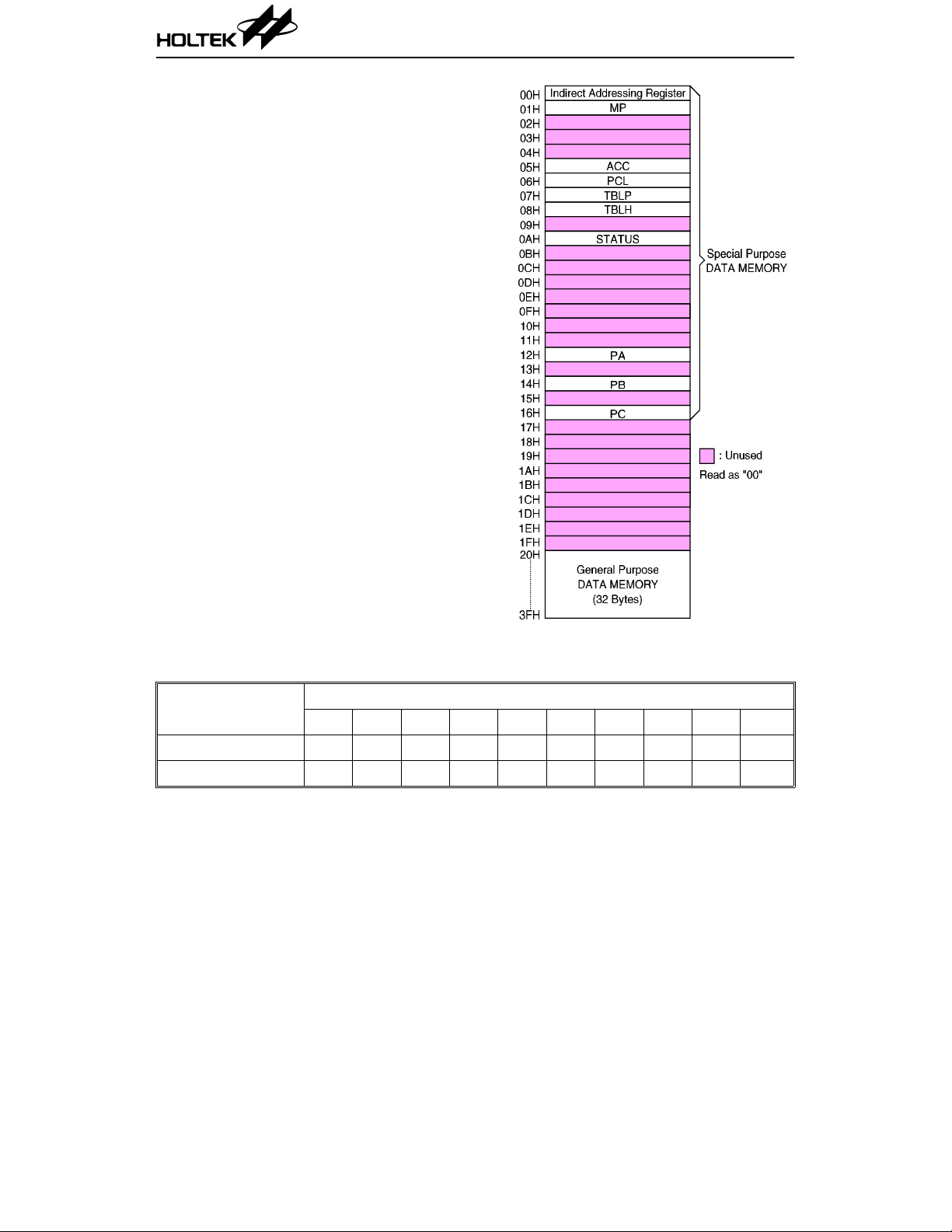

Data memory – RAM

The data memory is designed wi th 42×8 bits.

The data memory is divided into two functional

groups: special function re gisters and general

purpose data memory (32

read/write, but some are read only.

×8). Most of them are

Mode

Program Counter

*9 *8 *7 *6 *5 *4 *3 *2 *1 *0

Initial reset 0000000000

Skip

Loading PCL *9 *8@7@6@5@4@3@2@1 @0

Jump, call branch #9 #8 #7 #6 #5 #4 #3 #2 #1 #0

Return from subroutine S9 S8 S7 S6 S5 S4 S3 S2 S1 S0

Program counter

Notes: *9~*0: Program counter bits

#9~#0: Instruction code bits

8 23rd July ’98

PC+2

S9~S0: Stack register bits

@7~@0: PCL bits

The special function registers include the indirect

addressing register (00H), the memory pointer

register (MP;01H), the accumulator (ACC;05H)

the program counter lower-order byte register

(PCL;06H), the table pointer (TBLP;07H), the table higher-order byte register (TBLH;08H), the

status register (STATUS;0AH) and the I/O registers (PA;12H, PB;14H, PC;16H). The remaining

space before the 20H is reserved for future expanded usage and reading these locations will

return the result 00H. The general purpose data

memory, addressed from 20H to 3FH, is used for

data and control information under instruction

command.

All data memory areas can hand le arithmetic,

logic, increment, decrement and ro tate operations directly. Except for some ded icated bits,

each bit in the data memory can be set and reset

by the SET [m].i and CLR [m].i instructions,

respectively. They are also indirectly accessible

through memory pointer register (MP;01H).

Indirect addressing register

Location 00H is an indirect addressing register

that is not physically implemented. Any

read/write operation of [00H] accesses data

memory pointed to by MP (01H). Reading location 00H itself indire ctly will return th e result

00H. Writing indirectly results in no operation.

The memory pointer register MP (01H) is a 6-bit

register. The bit 7~6 of MP is undefined and

reading will return the result “1” . Any writing

operation to MP will only transfer the lower 6-bit

data to MP.

HT48CA0

RAM mapping

Instruction(s)

Ta ble Loc ation

*9 *8 *7 *6 *5 *4 *3 *2 *1 *0

TABRDC [m] P9 P8 @7 @6 @5 @4 @3 @2 @1 @0

TABRDL [m] 1 1 @7 @6 @5 @4 @3 @2 @1 @0

Table location

Notes: *9~*0: Table location bits

@7~@0: Table pointer bits

9 23rd July ’98

P9~P8: Current program counter bits

Accumulator

The accumulator clo sely relates to ALU opera tions. It is also mappe d to location 05H of the

data memory and is capable of carrying out

immediate data operations. Data movement between two data memory loca tions has to pass

through the accumulator.

Arithmetic and logic unit – ALU

This circuit performs 8-bit arithmetic and logic

operation. The ALU provides the following functions.

•

Arithmetic operations (ADD, ADC, SUB,

SBC, DAA)

•

Logic operations (AND, OR, XOR, CPL)

•

Rotation (RL, RR, RLC, RRC)

•

Increment and Decrement (INC, DEC)

•

Branch decision (SZ, SNZ, SIZ, SDZ ....)

The ALU not only saves the results of a data

operation but also changes the contents of the

status register.

Status register – STATUS

This 8-bit status register (0AH) contains the zero

flag (Z), carry flag (C), auxiliary carry flag (AC),

HT48CA0

overflow flag (OV), power down flag (PD) and

watchdog time -out flag (TO). It also recor ds the

status information and controls the operation

sequence.

With the exception of the TO and PD flags, bits

in the status register can be altered by instructions like most other register. Any data written

into the status register will not change the TO

or PD flags. I n a d diti on it sh ou ld be note d that

operations related to the status register may

give different results from th ose intende d. The

TO and PD flags can only be changed by the

W atchdog Timer overflow, chip power-up, clearing the Watchdog Timer and executing the

HALT instruction.

The Z, OV, AC and C flags generally reflect the

status of the latest operations.

In addition, on executing the subrouti ne call,

the status register will not be automatically

pushed onto the stack. If the contents of the

status are impo rtant and if the sub routine can

corrupt the status register, precautions must be

taken to save it properly.

Labels Bits Function

C is set if the operati on results in a carry during an addition op eration or if a

C0

borrow does not take place during a subtraction operation; otherwise C is

cleared. C is also affected by a rotate through carry instruction.

AC is set if the operation results in a carry ou t of the low nibbles in additio n or

AC 1

no borrow from the high nibble into the low nibble in subtraction; otherwise AC

is cleared.

Z2

OV 3

PD 4

TO 5

Z is set if the resul t of an arithmetic or logi c operation is zero; otherwise Z is

cleared.

OV is set if the operati on re sults in a carry in to the high est-order bi t but not a

carry out of the highest-order bit, or vice versa; otherwise OV is cleared.

PD is cleared when either a system power-up or executing the CLR WDT

instruction. PD is set by executing the HALT instruction.

TO is cleared by a system power-up or executing the CLR WDT or HALT

instruction. TO is set by a WDT time-out.

— 6 Undefined, read as “0”

— 7 Undefined, read as “0”

Status register

10 23rd July ’98

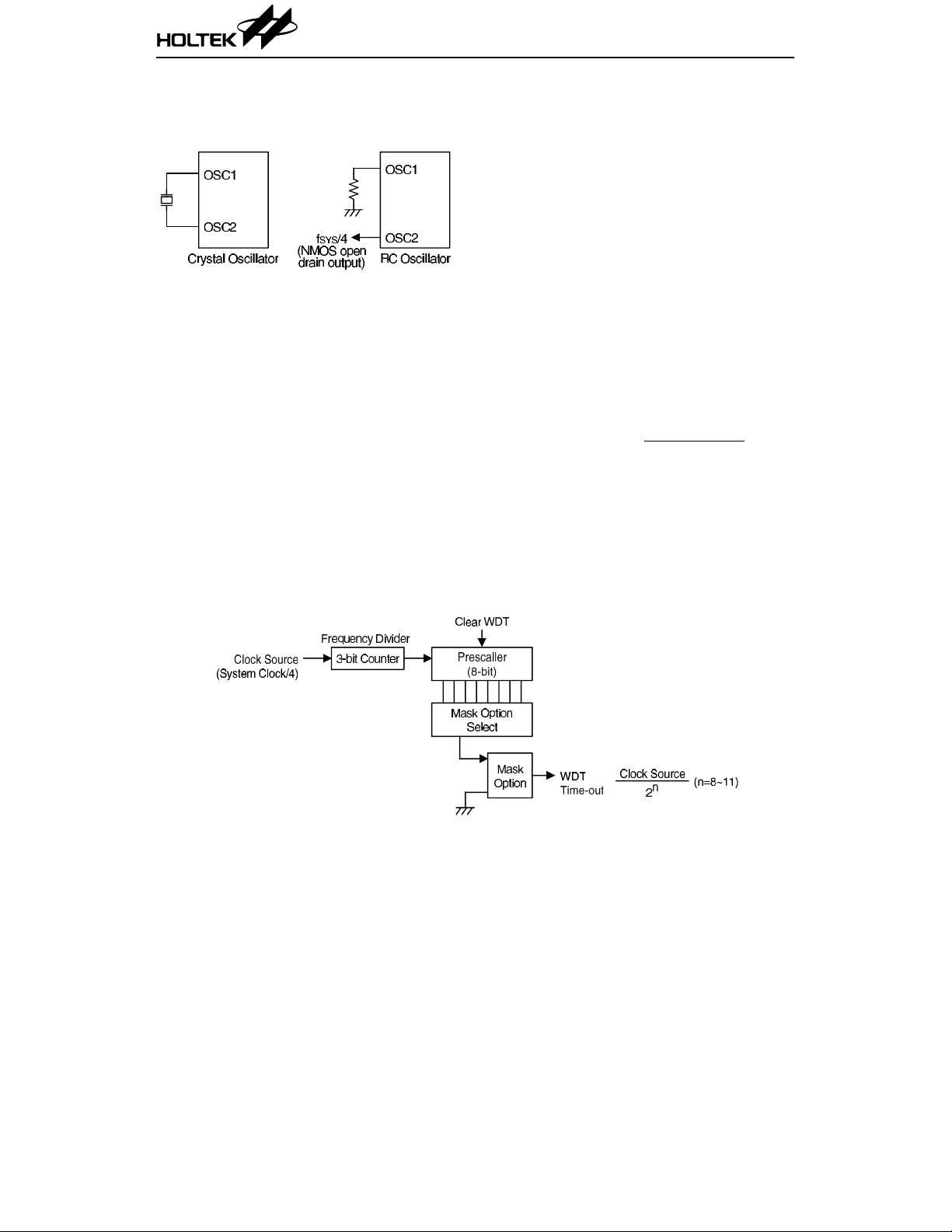

Oscillator configuration

There are two oscillator circuits in the HT48CA0.

System oscillator

Both are designed for system clocks; the RC

oscillator and the Crystal oscillator, which are

determined by mask options. No matter what

oscillator typ e is selected, the si gnal provides

the system clock. The HALT mode stops the

system oscillator and igno res the external signal to conserve power.

If an RC oscillator is u sed, an e xtern al res istor

between OSC1 and VSS in needed and the resistance must range from 51k

Ω to 1MΩ. The

system clock, divided by 4, is available on

OSC2, which can be u se d to synch ron ize exte rnal logic. The RC oscillator provides the most

cost effective solution. However, the frequency

of the oscillation may vary with VDD, temperature and the chip itself due to process vari-

HT48CA0

ations. It is, therefore, not suitable for timing

sensitive operations where accurate os cillator

frequency is desired.

If the Crystal oscillator is used, a crystal across

OSC1 and OSC2 is need ed to provi de the feedback and phase shift for the oscillator. No other

external compone nts are needed. Instead of a

crystal, the resonator can also be connected

between OSC1 and OSC2 to get a frequency

reference, but two external capacitors in OSC1

and OSC2 are required.

Watchdog timer – WDT

The clock source of the WDT is implemented by

instruction clock (system clock divided by 4).

The clock source is processed by a frequency

divider and a prescaller to yield various time

out periods.

WDT time out period =

Where n= 8~11 selected by mask option.

This timer is designed to prevent a software

malfunction or sequence jumping to an unknown location with unpredictable results. The

Watchdog Timer can be disabled by mask option. If t he Watchdog Timer i s di sabl ed , al l th e

executions related to the WDT result in no op-

Clock Source

n

2

Watchdog timer

11 23rd July ’98

Loading...

Loading...