Page 1

Standard 8051 8-Bit Flash MCU

HT85F2260

HT85F2270

HT85F2280

Revision: V1.00 Date: January 15, 2015January 15, 2015

Page 2

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

Table of Contents

1 Features ................................................................................................................. 14

CPU Features.................................................................................................................... 14

Peripheral Features ........................................................................................................... 15

2 General Description ............................................................................................. 16

Table of Contents

3 Selection Table

4 Block Diagram

5 Pin Assignment

6 Pin Descriptions

7 Absolute Maximum Ratings

8 D.C. Characteristics

9 A.C. Characteristics

10 ADC Electrical Characteristics

11 DAC Electrical Characteristics

12 Comparator Electrical Characteristics

...................................................................................................... 17

....................................................................................................... 18

..................................................................................................... 19

................................................................................................... 20

................................................................................. 23

.............................................................................................. 23

.............................................................................................. 25

......................................................................... 26

.......................................................................... 26

............................................................. 27

13 Power on Reset Electrical Characteristics

14 System Architecture

15 Program Counter

16 Stack

.................................................................................................................... 29

........................................................................................... 28

................................................................................................ 29

....................................................... 28

17 Arithmetic and Logic Unit – ALU

18 Flash Program Memory

Structure ............................................................................................................................ 31

Special Vectors.................................................................................................................. 31

In-Circuit Programming – ICP ........................................................................................... 32

On-Chip Debug Support – OCDS ..................................................................................... 32

In-Application Programming – IAP .................................................................................... 33

Flash Program Memory Resisters ..................................................................................... 33

Flash Memory Read/Write Operations .............................................................................. 37

Unlocking the Flash Memory ........................................................................................................ 37

Page Erase Operation .................................................................................................................. 38

Byte Read Operation .................................................................................................................... 39

Byte Write Operation .................................................................................................................... 40

Rev. 1.00 2 of 225 January 15, 2015

...................................................................................... 31

....................................................................... 30

Page 3

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

Program Memory Protection ............................................................................................. 42

Memory Protection Control Bytes ................................................................................................. 42

19 RAM Data Memory .............................................................................................. 46

Structure ............................................................................................................................ 46

Register Banks .................................................................................................................. 50

Bit Addressable Space ...................................................................................................... 50

Special Function Registers................................................................................................ 52

ACC Register – Accumulator ........................................................................................................ 53

B Register .................................................................................................................................... 53

SP Register – Stack Pointer ......................................................................................................... 53

DPL, DPH, DPL1, DPH1 Registers – Data Pointer Registers ...................................................... 53

Data Pointer Select Registers ...................................................................................................... 54

Data Pointer Control Register....................................................................................................... 54

Program Status Word ................................................................................................................... 56

Table of Contents

20 Oscillators ........................................................................................................... 57

System Oscillator Overview .............................................................................................. 57

System Clock Conguration .............................................................................................. 57

External High Speed Crystal Oscillator – HXT ............................................................................. 57

Internal High Speed RC Oscillator – HIRC ................................................................................... 58

External Low Speed Crystal Oscillator – LXT ............................................................................... 58

Internal Low Speed RC Oscillator – LIRC .................................................................................... 59

21 Operating Modes and System Clocks .............................................................. 60

System Clocks Description................................................................................................ 60

Phase Locked Loop – PLL

Changing the PLL Frequency ....................................................................................................... 64

................................................................................................ 64

Operation Modes ............................................................................................................... 66

NORMAL Mode ............................................................................................................................ 66

IDLE Mode.................................................................................................................................... 66

Power-Down Mode ....................................................................................................................... 66

Power Control Register ..................................................................................................... 67

Standby Current Considerations ....................................................................................... 67

Wake-up ............................................................................................................................ 68

22 Watchdog Timer .................................................................................................. 69

Watchdog Registers .......................................................................................................... 70

Watchdog Timer Clock Source .......................................................................................... 73

Watchdog Timer Operation ............................................................................................... 73

Rev. 1.00 3 of 225 January 15, 2015

Page 4

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

23 Low Voltage Detector – LVD .............................................................................. 75

LVD Register ..................................................................................................................... 75

LVD Operation ................................................................................................................... 75

24 Reset and Initialisation ....................................................................................... 76

Reset Overview ................................................................................................................. 76

Reset Operations .............................................................................................................. 77

Reset Source Register – RSTSRC............................................................................................... 77

Power-on Reset ............................................................................................................................ 78

RESET Pin Reset

Low Voltage Reset – LVR

Watchdog Reset

Comparator 0 Reset ..................................................................................................................... 82

Software Resets ........................................................................................................................... 83

SRST Register Software Reset .................................................................................................... 83

WDTCR Register Software Reset ................................................................................................ 84

LVRCR Register Software Reset ..................................................................................................84

ROM Code Check Reset

Reset Initial Conditions...................................................................................................... 85

......................................................................................................................... 79

............................................................................................................. 80

.......................................................................................................................... 81

.............................................................................................................. 85

Table of Contents

25 Interrupts ............................................................................................................. 91

Interrupt Registers ............................................................................................................. 91

Interrupt Operation .......................................................................................................... 103

Interrupt Priority ............................................................................................................... 106

Priority Levels ............................................................................................................................. 106

Priority Control Registers............................................................................................................ 108

External Interrupt ..............................................................................................................111

Comparator Interrupt ....................................................................................................... 112

A/D Converter Interrupt ................................................................................................... 11 3

Timer/Counter Interrupt ................................................................................................... 113

Time Base Interrupts ....................................................................................................... 113

2

I

C Interface Interrupt ...................................................................................................... 11 4

SPI Interface Interrupt ..................................................................................................... 11 5

UART Interface Interrupt ................................................................................................. 115

LVD Interrupt ................................................................................................................... 115

Interrupt Wake-up Function ............................................................................................. 11 6

Programming Considerations .......................................................................................... 116

Rev. 1.00 4 of 225 January 15, 2015

Page 5

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

26 Input/Output Ports ............................................................................................ 117

Input/Output Port Overview ............................................................................................. 117

Register Description ........................................................................................................ 118

PnM0/PnM1 Registers – Port Mode Registers ........................................................................... 120

P0WAKE Register – Port 0 Wake-up ......................................................................................... 122

SRCR Register – Slew Rate Control .......................................................................................... 122

I/O Pin Structures ............................................................................................................ 123

Quasi-bidirectional I/O – All Ports ............................................................................................... 123

Push-pull Output – Ports 0~3 Only ............................................................................................. 124

Open-drain Output – Ports 0~3 Only .......................................................................................... 124

Input Only – Ports 0~3 Only ....................................................................................................... 124

Programming Considerations .......................................................................................... 125

27 Timer/Event Counters ...................................................................................... 126

Timer/Event Counter Summary ....................................................................................... 126

Table of Contents

28 Timer/Event Counters 0, 1, 3 ........................................................................... 127

Introduction...................................................................................................................... 127

Timer 0/Timer 1/Timer 3 Register Description ................................................................. 128

Mode 0 – 13-bit Counter/Timer Mode Operation .............................................................135

Mode 1 – 16-bit Counter/Timer Mode Operation .............................................................135

Mode 2 – 8-bit Auto-reload Counter/Timer Mode Operation ........................................... 136

Mode 3 – Two 8-Bit Timers/Counters Mode Operation – Timer 0 Only ........................... 137

29 Timer 2 with Additional 4-channel PCA .......................................................... 138

Introduction...................................................................................................................... 138

Timer 2 ............................................................................................................................140

Timer function ............................................................................................................................. 140

Event Counter function ............................................................................................................... 140

Gated Timer function .................................................................................................................. 140

Timer 2 with PCA ............................................................................................................. 141

Timer 2 Register Description ........................................................................................... 142

Capture Modes ................................................................................................................ 145

Capture On Edge Mode.............................................................................................................. 145

Capture On Write Mode .............................................................................................................. 145

Compare Modes .............................................................................................................. 146

Compare Mode 0 ........................................................................................................................ 146

Compare Mode 1 ........................................................................................................................ 148

Reload Mode ................................................................................................................... 150

Programmable Clock Output Mode ................................................................................. 151

Rev. 1.00 5 of 225 January 15, 2015

Page 6

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

30 Analog to Digital Converter – ADC ................................................................. 152

A/D Overview .................................................................................................................. 152

A/D Converter Register Description ................................................................................ 153

A/D Converter Data Registers – ADRL, ADRH ...............................................................153

A/D Converter Control Registers – ADCR0, ADCR1, ADCR2, ADPGA .......................... 153

A/D Operation.................................................................................................................. 157

A/D Converter Clock Source ........................................................................................... 158

A/D Input Pins ................................................................................................................. 158

Temperature Sensor ........................................................................................................ 159

A/D Reference Voltage Source .......................................................................................159

Summary of A/D Conversion Steps ................................................................................. 160

A/D Conversion Timing....................................................................................................161

Programming Considerations .......................................................................................... 162

A/D Transfer Function ..................................................................................................... 162

Table of Contents

31 Digital to Analog Converter – DAC .................................................................. 163

DAC Register Description ............................................................................................... 163

DAC Operation ................................................................................................................ 165

DAC Reference Voltage Source ...................................................................................... 166

Programming Considerations .......................................................................................... 166

32 Voltage Reference Generator .......................................................................... 167

Voltage Reference Generator Operation ......................................................................... 167

33 Comparators ..................................................................................................... 169

Comparator Operation..................................................................................................... 169

Comparator Registers ..................................................................................................... 170

Comparator Interrupt ....................................................................................................... 175

Comparator Reset Function ............................................................................................ 175

Programming Considerations .......................................................................................... 175

34 I2C Serial Interface ............................................................................................ 176

I2C Interface Operation .................................................................................................... 176

2

I

C Registers ................................................................................................................... 177

2

I

C Bus Communication .................................................................................................. 181

I2C Bus Start Signal .................................................................................................................... 182

Slave Address............................................................................................................................. 182

I2C Bus Read/Write Signal .......................................................................................................... 182

I2C Bus Slave Address Acknowledge Signal .............................................................................. 182

I2C Bus Data and Acknowledge Signal ....................................................................................... 183

2

C Status Codes ........................................................................................................................ 184

I

Rev. 1.00 6 of 225 January 15, 2015

Page 7

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

35 Serial Interface – SPI ........................................................................................ 189

SPI Interface Operation ................................................................................................... 189

SPI Features............................................................................................................................... 190

SPI Registers .................................................................................................................. 191

SPI Communication......................................................................................................... 194

36 UART Serial Interfaces – UART0 and UART1 ................................................. 197

UART Overview ...............................................................................................................197

UART0 Features ......................................................................................................................... 197

UART1 Features ......................................................................................................................... 197

Basic UART Data Transfer Scheme ........................................................................................... 198

UART0 Operating Description ......................................................................................... 199

UART0 External Pin Interfacing .................................................................................................. 199

UART0 Register Description ...................................................................................................... 200

UART0 Operating Modes ........................................................................................................... 204

UART0 Multiprocessor Communication .................................................................................... 208

UART0 Baud Rate Setup ........................................................................................................... 208

UART1 Operating Description ......................................................................................... 209

UART1 External Pin Interfacing .................................................................................................. 209

UART1 Register Description ...................................................................................................... 210

UART1 Operating Modes ........................................................................................................... 213

UART1 Multiprocessor Communication ..................................................................................... 215

UART1 Baud Rate Setup ........................................................................................................... 215

Table of Contents

37 Instruction Set ................................................................................................... 216

Introduction...................................................................................................................... 216

Read-Modify-Write Instruction ......................................................................................... 221

38 Package Information ........................................................................................ 222

48-pin LQFP (7mm×7mm) Outline Dimensions .............................................................. 223

64-pin LQFP (7mm × 7mm) Outline Dimensions ............................................................ 224

Rev. 1.00 7 of 225 January 15, 2015

Page 8

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

List of Tables

Program Memory Register List ................................................................................................................ 33

FMAR0 Register – Flash Program Memory Address Register 0 ............................................................. 33

FMAR1 Register – Flash Program Memory Address Register 1 ............................................................. 34

FMAR2 Register – Flash Program Memory Address Register 2 ............................................................. 34

FMDR Register – Flash Program Memory Data Register ....................................................................... 34

FMCR Register – Flash Program Memory Control Register ................................................................... 35

FMKEY Register – Flash Program Memory Unlock Key Data Register .................................................. 36

FMSR Register – Flash Program Memory Status Register ..................................................................... 36

HT85F2260 Program Memory Contents .................................................................................................. 43

HT85F2270 Program Memory Contents .................................................................................................. 44

HT85F2280 Program Memory Contents .................................................................................................. 44

Security Bytes .......................................................................................................................................... 44

General Purpose Data RAM, 20H~2FH, Bit Address Map ...................................................................... 50

Special Function Register Bit Addresses Map ......................................................................................... 51

Special Function Register Map ................................................................................................................ 52

DPS Register – Data Pointer Select Register .......................................................................................... 54

DPC Register – Data Pointer Control Register ........................................................................................ 55

PSW Register – Program Status Word Register ..................................................................................... 56

Crystal Recommended Capacitor Values ................................................................................................ 58

32768Hz Crystal Recommended Capacitor Values ................................................................................. 59

System Clock Control Register – SCCR .................................................................................................. 62

High Speed Oscillator Control Register – HSOCR .................................................................................. 63

Low Speed Oscillator Control Register – LSOCR ................................................................................... 63

PLL Control Register – PLLCR ................................................................................................................ 65

PCON Register – Power Control Register ............................................................................................... 67

WDT Register Contents ........................................................................................................................... 70

IEN0 Register .......................................................................................................................................... 70

IEN1 Register .......................................................................................................................................... 71

WDTREL Register ................................................................................................................................... 71

WDTCR Register ..................................................................................................................................... 72

IP0 Register ............................................................................................................................................. 72

Watchdog Timer Enable/Disable Control ................................................................................................. 73

LVDCR Register....................................................................................................................................... 75

Reset Source Summary ........................................................................................................................... 76

RSTSRC Register .................................................................................................................................... 77

LVRCR Register....................................................................................................................................... 80

IP0 Register ............................................................................................................................................. 81

T2CON1 Register .................................................................................................................................... 82

CP0CR Register ...................................................................................................................................... 83

Software Reset Summary ........................................................................................................................ 84

SRST Register ......................................................................................................................................... 84

WDTCR Register ..................................................................................................................................... 85

LVRCR Register....................................................................................................................................... 85

List of Tables

Rev. 1.00 8 of 225 January 15, 2015

Page 9

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

Interrupt Register Bit Naming Conventions ............................................................................................. 92

Interrupt Register Contents ...................................................................................................................... 93

IEN0 Register .......................................................................................................................................... 93

IEN1 Register .......................................................................................................................................... 94

IEN2 Register .......................................................................................................................................... 94

IEN3 Register .......................................................................................................................................... 95

IRCON Register ....................................................................................................................................... 96

IRCON2 Register ..................................................................................................................................... 97

S0CON Register ...................................................................................................................................... 98

S1CON Register ...................................................................................................................................... 99

TCON Register ...................................................................................................................................... 100

T2CON Register .................................................................................................................................... 101

T3CON Register .................................................................................................................................... 101

SPSTA Register ..................................................................................................................................... 102

CPICR Register ..................................................................................................................................... 103

I2CCON Register ................................................................................................................................... 104

Low byte of Interrupt Priority Register 0: IP0 ......................................................................................... 109

High byte of Interrupt Priority Register 0: IP0H ...................................................................................... 109

Low byte of Interrupt Priority Register 1: IP1 ..........................................................................................110

High byte of Interrupt Priority Register 1: IP1H .......................................................................................110

Low byte of Interrupt Priority Register 2: IP2 ..........................................................................................111

High byte of Interrupt Priority Register 2: IP2H .......................................................................................111

Low byte of Interrupt Priority Register 3: IP3 ..........................................................................................111

How byte of Interrupt Priority Register 3: IP3H .......................................................................................112

External Interrupt Trigger Type ...............................................................................................................112

CPICR Register ......................................................................................................................................113

TBCR Register ........................................................................................................................................115

I/O Port Function Summary ....................................................................................................................118

I/O Register List ......................................................................................................................................119

P0 Register .............................................................................................................................................119

P1 Register .............................................................................................................................................119

P2 Register ............................................................................................................................................ 120

P3 Register ............................................................................................................................................ 120

P4 Register ............................................................................................................................................ 120

P5 Register ............................................................................................................................................ 120

Port 0 Mode Control ............................................................................................................................... 121

P0M0 Register ....................................................................................................................................... 121

P0M1 Register ....................................................................................................................................... 121

Port 1 Mode Control ............................................................................................................................... 121

P1M0 Register ....................................................................................................................................... 121

P1M1 Register ....................................................................................................................................... 121

Port 2 Mode Control ............................................................................................................................... 122

P2M0 Register ....................................................................................................................................... 122

P2M1 Register ....................................................................................................................................... 122

Port 3 Mode Control ............................................................................................................................... 122

P3M0 Register ....................................................................................................................................... 122

List of Tables

Rev. 1.00 9 of 225 January 15, 2015

Page 10

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

P3M1 Register ....................................................................................................................................... 122

P0WAKE Register .................................................................................................................................. 123

SRCR Register ...................................................................................................................................... 123

Timer Function Summary ....................................................................................................................... 127

Timer0/Timer1/Timer3 Register List ....................................................................................................... 129

TL0 Register ......................................................................................................................................... 129

TH0 Register ......................................................................................................................................... 130

TL1 Register .......................................................................................................................................... 130

TH1 Register .......................................................................................................................................... 131

TL3 Register .......................................................................................................................................... 131

TH3 Register .......................................................................................................................................... 132

TMOD Register ...................................................................................................................................... 132

TCON Register ...................................................................................................................................... 133

T3CON Register ................................................................................................................................... 134

TMPRE Register .................................................................................................................................... 135

13-bit Counter Data ............................................................................................................................... 136

Timer 2 with PCA Modules Operating Modes Summary ........................................................................ 139

Timer 2 with PCA Modules I/O Pins ....................................................................................................... 139

Timer 2 Register List .............................................................................................................................. 143

CCEN Register ..................................................................................................................................... 143

T2CON Register .................................................................................................................................... 144

T2CON1 Register ................................................................................................................................. 145

A/D Converter Register List ................................................................................................................... 154

A/D Data Registers ................................................................................................................................ 154

ADCR0 Register ................................................................................................................................... 155

ADCR1 Register .................................................................................................................................... 156

ADCR2 Register .................................................................................................................................... 157

ADPGA Register .................................................................................................................................... 158

A/D Clock Period Examples ................................................................................................................... 159

A/D Converter Voltage Reference Select .............................................................................................. 160

DAH Register ......................................................................................................................................... 164

DAL Register .......................................................................................................................................... 164

DACTRL Register .................................................................................................................................. 164

DAC Converter Voltage Reference Select ............................................................................................. 167

Internal Voltage Reference Enable/Disable Control .............................................................................. 168

Comparator Registers List ..................................................................................................................... 171

CP0CR Register .................................................................................................................................... 172

CP1CR Register .................................................................................................................................... 173

CPHCR Register .................................................................................................................................... 174

CPICR Register ..................................................................................................................................... 175

I2C Register List .................................................................................................................................... 178

I2CCON Register ................................................................................................................................... 178

I2CLK Register ...................................................................................................................................... 179

I2CSTA Register .................................................................................................................................... 180

I2CDAT Register .................................................................................................................................... 180

List of Tables

Rev. 1.00 10 of 225 January 15, 2015

Page 11

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

I2CADR Register ................................................................................................................................... 180

2

C Status in Master Transmitter Mode .................................................................................................. 185

I

I2C Status in Master Receiver Mode ..................................................................................................... 186

2

C Status in Slave Receiver Mode ........................................................................................................ 187

I

2

C Status in Slave Transmitter Mode .................................................................................................... 188

I

2

C Status: Miscellaneous States .......................................................................................................... 189

I

SPI Register List .................................................................................................................................... 192

SPDAT Register ..................................................................................................................................... 192

SPCON Register .................................................................................................................................... 193

SPSTA Register ..................................................................................................................................... 194

UART0 Register List .............................................................................................................................. 201

S0BUF Register – UART0 Data register................................................................................................ 201

S0CON Register – UART0 Control register ........................................................................................... 202

S0RELL Register – UART0 Reload Low Register ................................................................................. 203

S0RELH Register – UART0 Reload High Register................................................................................ 203

SPPRE Register – UART Clock Prescaler Register .............................................................................. 203

SBRCON Register ................................................................................................................................. 204

PCON Register ...................................................................................................................................... 204

UART0 Operating Modes....................................................................................................................... 205

Mode 0 ................................................................................................................................................... 205

UART1 Register List ...............................................................................................................................211

S1BUF Register – UART1 Data register.................................................................................................211

S1CON Register – UART1 Control register ........................................................................................... 212

S1RELL Register – UART1 Reload Low Register ................................................................................. 213

S1RELH Register – UART1 Reload High Register................................................................................ 213

SPPRE Register – UART Clock Prescaler Register .............................................................................. 213

UART1 Operating Modes....................................................................................................................... 214

Notes on Data Addressing Modes ......................................................................................................... 217

Notes on Program Addressing Modes ................................................................................................... 217

Arithmetic Operations ............................................................................................................................ 218

Logic Operations .................................................................................................................................... 219

Data transfer Operations ....................................................................................................................... 220

Program Branches ................................................................................................................................. 221

Boolean Manipulation ............................................................................................................................ 222

List of Tables

Rev. 1.00 11 of 225 January 15, 2015

Page 12

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

List of Figures

Stack Block Diagram ............................................................................................................................... 29

Program Memory Structure ..................................................................................................................... 31

Unlock Procedure Flowchart .................................................................................................................... 37

Page Erase Flowchart ............................................................................................................................. 38

Byte Read Flowchart ............................................................................................................................... 39

Byte Write Flowchart (FMCR.0=1, FMCR.6=0) ....................................................................................... 40

Byte Write Flowchart (FMCR.0=1, FMCR.6=1) ....................................................................................... 41

Internal Data Memory Structure ............................................................................................................... 47

HT85F2270/HT85F2280 XDATA .............................................................................................................. 48

HT85F2260 XDATA .................................................................................................................................. 49

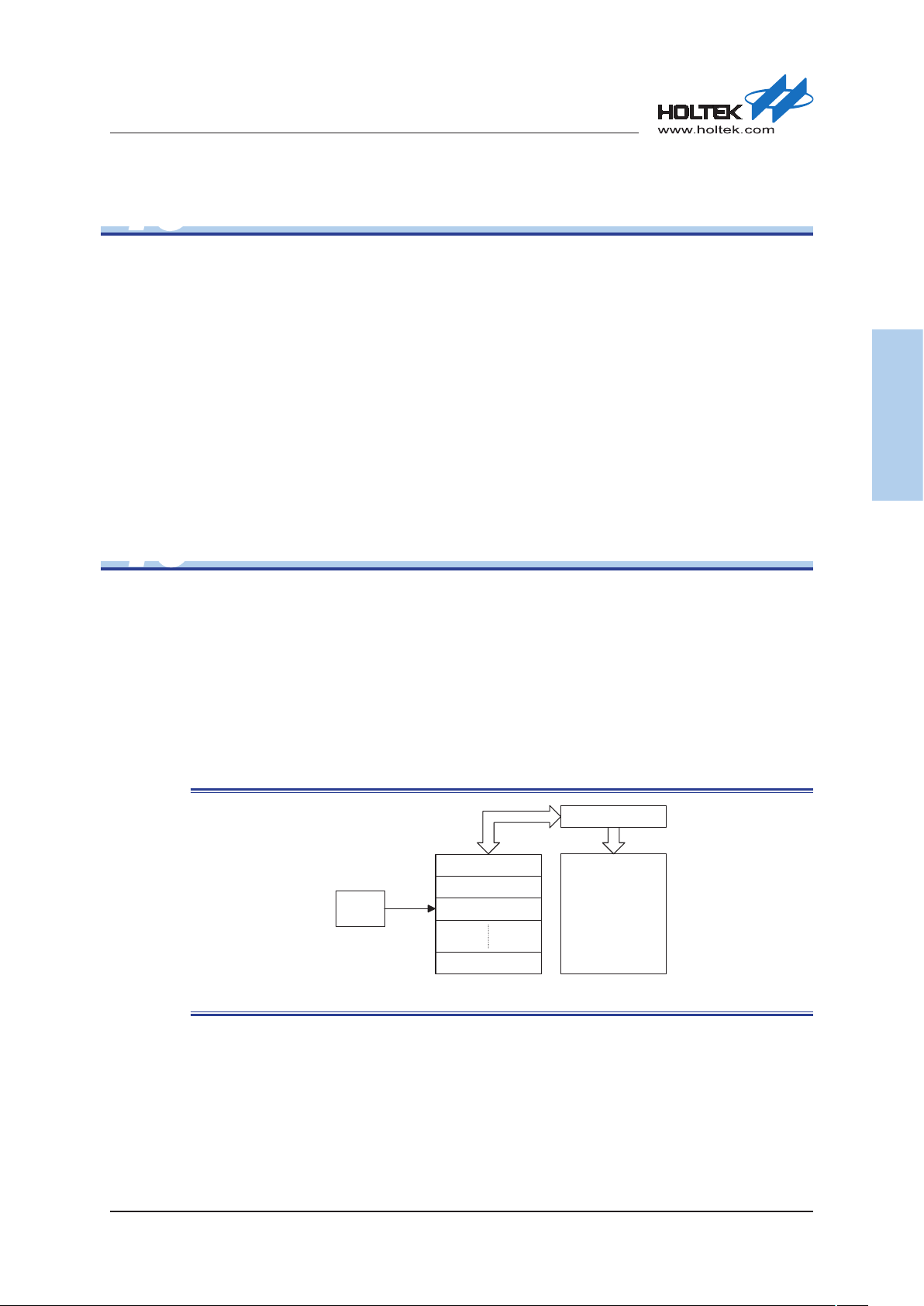

DPTRn Registers Control Block Diagram ................................................................................................ 53

Crystal/Resonator Oscillator – HXT ......................................................................................................... 58

External LXT Oscillator – LXT .................................................................................................................. 59

System Clock Congurations ................................................................................................................... 61

PLL Frequency Changing ........................................................................................................................ 64

Watchdog Timer ....................................................................................................................................... 69

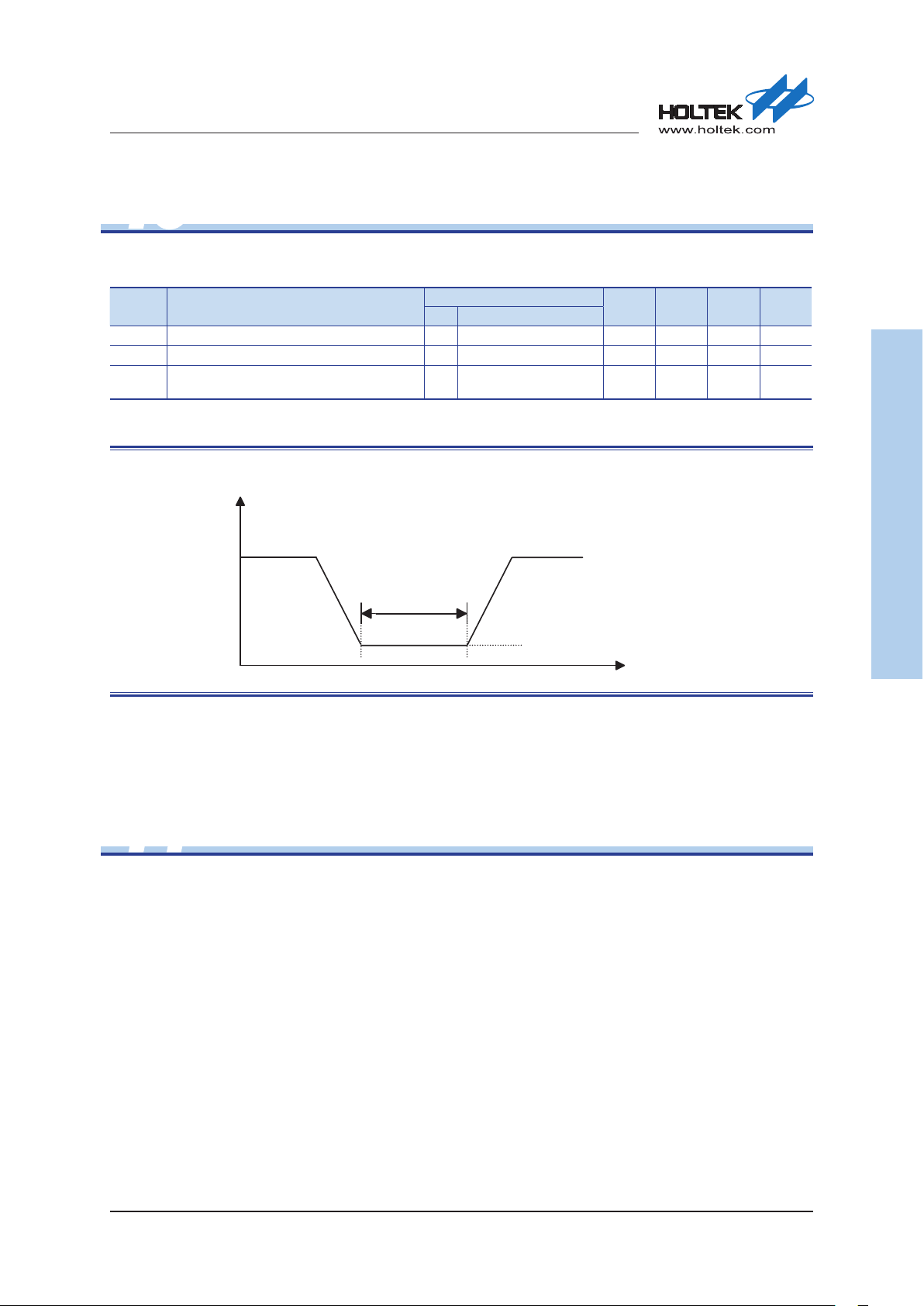

Watchdog Timer Refresh Operation ........................................................................................................ 74

Power-On Reset Timing .......................................................................................................................... 78

Interrupt Structure .................................................................................................................................. 105

Interrupt Flowchart ................................................................................................................................. 106

Time Base Clock Source Select .............................................................................................................114

Quasi-bidirectional I/O Structure ............................................................................................................ 124

Push-pull Output Structure .................................................................................................................... 125

Open-drain Output Structure ................................................................................................................. 125

Input Only Structure ............................................................................................................................... 125

Mode 0 and Mode 1 Block Diagram – Timer 0, 1, 3 .............................................................................. 136

Mode 2 Block Diagram – Timer 0, 1, 3 .................................................................................................. 137

Mode 3 Block Diagram – Timer 0 .......................................................................................................... 138

Timer 2 with PCA Modules Block Diagram ............................................................................................ 140

Capture Modes Block Diagram .............................................................................................................. 146

Compare Mode 0 – Module 1, Module 2, Module 3 ............................................................................... 147

Compare Mode 0 – Module 0 ................................................................................................................ 148

Compare Mode 0 Timing Diagram ......................................................................................................... 148

Compare Mode 1 – Module1, Module2, Module 3 ................................................................................. 149

Compare Mode 1 – Module 0 ................................................................................................................ 149

Compare Mode 1 Timing Diagram ......................................................................................................... 150

Reload Mode – Module 0 ....................................................................................................................... 151

Timer2 Clock Output Block Diagram ...................................................................................................... 152

Programmable Clock Output Timing Diagram – Module 0 .................................................................... 152

A/D Converter Structure ........................................................................................................................ 153

A/D Conversion Timing .......................................................................................................................... 162

Ideal A/D Transfer Function (PGA=1) .................................................................................................... 163

DAC Basic Operational Block Diagram ................................................................................................. 166

List of Figures

Rev. 1.00 12 of 225 January 15, 2015

Page 13

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

Voltage Reference Generator Block Diagram ........................................................................................ 169

Comparator 0 ......................................................................................................................................... 170

Comparator 1 ......................................................................................................................................... 171

2

C Master Slave Bus Connection .......................................................................................................... 177

I

2

C Interface Operation Flow .................................................................................................................. 177

I

2

C Block Diagram .................................................................................................................................. 181

I

2

C Bus Initialisation Flow Chart ............................................................................................................ 182

I

I2C Communication Timing Diagram ...................................................................................................... 184

Single SPI Master and single Slave Connection ................................................................................... 190

SPI Interface Block Diagram .................................................................................................................. 191

SPI Master Mode Timing ....................................................................................................................... 195

SPI Slave Mode Timing – CPHA=0 ....................................................................................................... 196

SPI Slave Mode Timing – CPHA=1

SPI Transfer Control Flowchart .............................................................................................................. 197

Basic UART Data Transfer Diagram ...................................................................................................... 199

UART 0 Block Diagram .......................................................................................................................... 200

UART0 Mode 0 Timing Diagram ............................................................................................................ 205

UART0 Mode 1 Timing Diagram ............................................................................................................ 206

UART0 Mode 2 Timing Diagram ............................................................................................................ 207

UART0 Mode 3 Timing Diagram ............................................................................................................ 208

UART0 Baud Rate Generator ................................................................................................................ 209

UART1 Block Diagram ........................................................................................................................... 210

UART1 Mode A Timing Diagram ............................................................................................................ 214

UART1 Mode B Timing Diagram............................................................................................................ 215

UART1 Baud Rate Generator ................................................................................................................ 216

....................................................................................................... 196

List of Figures

Rev. 1.00 13 of 225 January 15, 2015

Page 14

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

1

Features

CPU Features

Operating Voltage:

■

● f

● f

● f

● f

Program Memory Capacity: 16K×8~64K×8

■

Data Memory Capacity: 1280×8~2304×8

■

High performance 1-T architecture: 8051

■

Up to 32MIPS with 32MHz system clock at V

■

8051 compatible instruction set

■

Flexible Power-down and wake-up functions to reduce power consumption

■

Oscillator types:

■

● External high frequency crystal

● Internal high frequency RC

● External low frequency crystal

● Internal low frequency RC

=3.6864MHz: 2.2V~5.5V

SYS

=8MHz: 2.2V~5.5V

SYS

=12MHz: 2.7V~5.5V

SYS

=24MHz: 4.5V~5.5V

SYS

DD

Features

=5V

Multi-mode operation: Normal, Idle and Power-Down Modes

■

Fully integrated internal 3.6864MHz oscillator requires no external components

■

Internal PLL to multiply oscillator frequency up to 1~8 times for high speed system clock

■

Watchdog Timer function

■

Dual 16-bit data pointers with addition arithmetic operation

■

Rev. 1.00 14 of 225 January 15, 2015

Page 15

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

Peripheral Features

Multi-channel 12-bit resolution A/D converter

■

Single 12-bit D/A Converter

■

Serial SPI Interface

■

2

C Interface

I

■

Dual UART Interfaces

■

Dual Comparator functions

■

Up to 48 bidirectional I/O lines

■

16-bit Programmable Counter Array with 5 Capture/Compare Modules

■

16-bit Programmable Counter Array

■

Single Time-Base functions for generation of xed time interrupt signal

■

Internal Temperature Sensor

■

Low voltage reset function

■

Features

Low voltage detect function

■

Package types: 48-LQFP and 64-LQFP

■

Rev. 1.00 15 of 225 January 15, 2015

Page 16

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

2

General Description

The HT85F22x0 series of devices are Flash Memory A/D type high performance 1-T architecture

8051-Based microcontrollers. Offering users the convenience of Flash Memory multi-programming

features, these devices also include a wide range of functions and features.

Analog features include a multi-channel 12-bit A/D converter, a 12-bit D/A converter and dual

comparator functions. Multiple timers provide timing, capture, event counter and programmable

clock output functions. Communication with the outside world is catered for by including fully

integrated SPI, I

with a means of easy communication with external peripheral hardware. Protective features such

as an internal Watchdog Timer, Low Voltage Reset and Low Voltage Detector and excellent noise

immunity and ESD protection ensure that reliable operation is maintained in hostile electrical

environments.

A full choice of both internal and external high and low speed oscillators are provided with the

internal oscillators requiring no external components for its implementation. A fully internal Phase

Locked Loop and the ability to operate and switch dynamically between a range of operating

modes using different clock sources gives users the ability to optimise microcontroller operation

and minimize power consumption.

The inclusion of exible I/O programming features, Time-Base functions along with many other

features ensure that the device will nd excellent use in applications such as electronic metering,

environmental monitoring, handheld instruments, household appliances, electronically controlled

tools, motor driving in addition to many others.

2

C and UART interface functions, popular interfaces which provide designers

General Description

The HT85F22x0 series are Flash devices offering the advantages of easy and effective in-circuit

program updates. In addition, an EV chip, HT85V2280, includes an OCDS (On-Chip Debug

Support) interface for the In-Circuit Emulator.

Rev. 1.00 16 of 225 January 15, 2015

Page 17

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

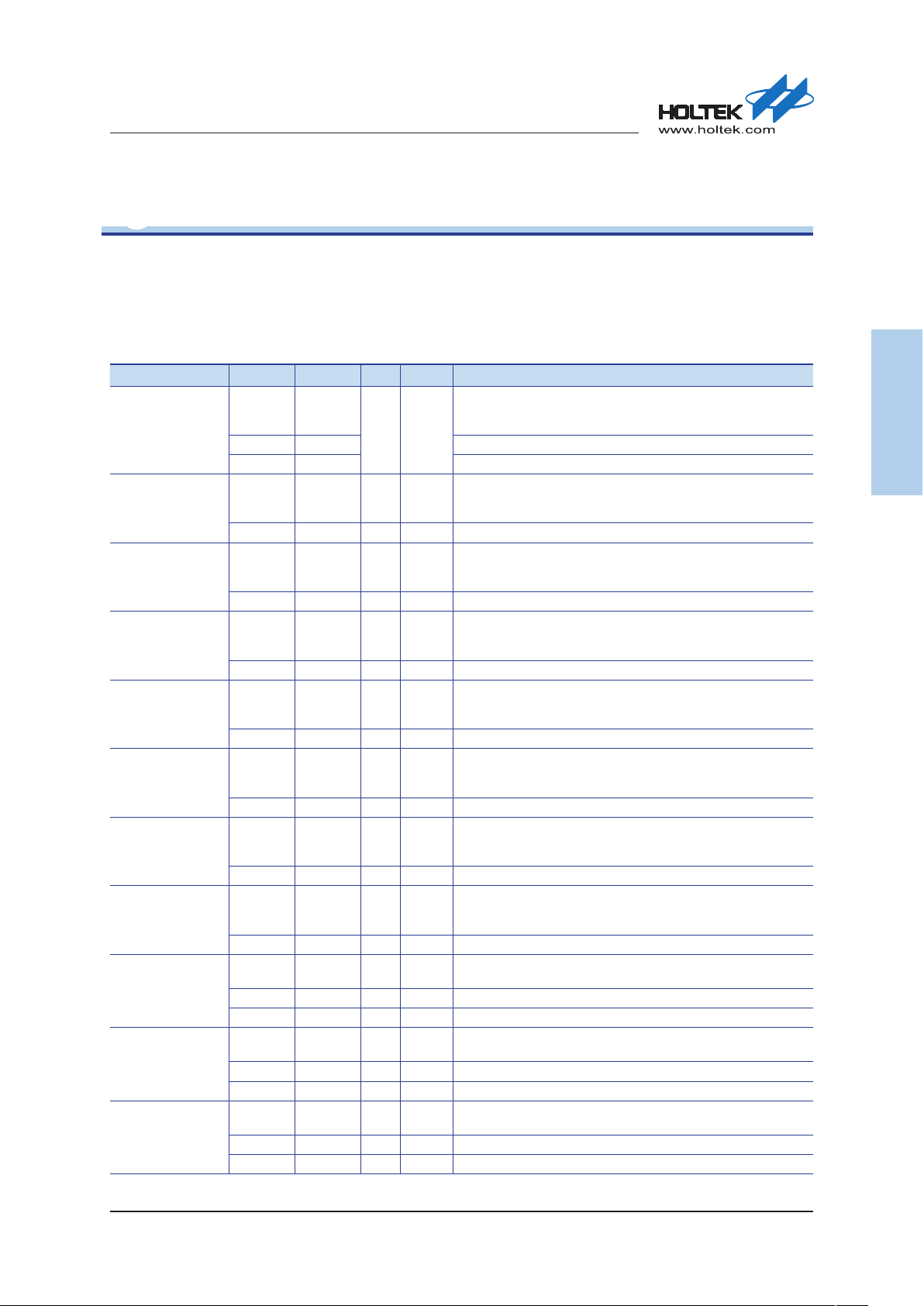

3

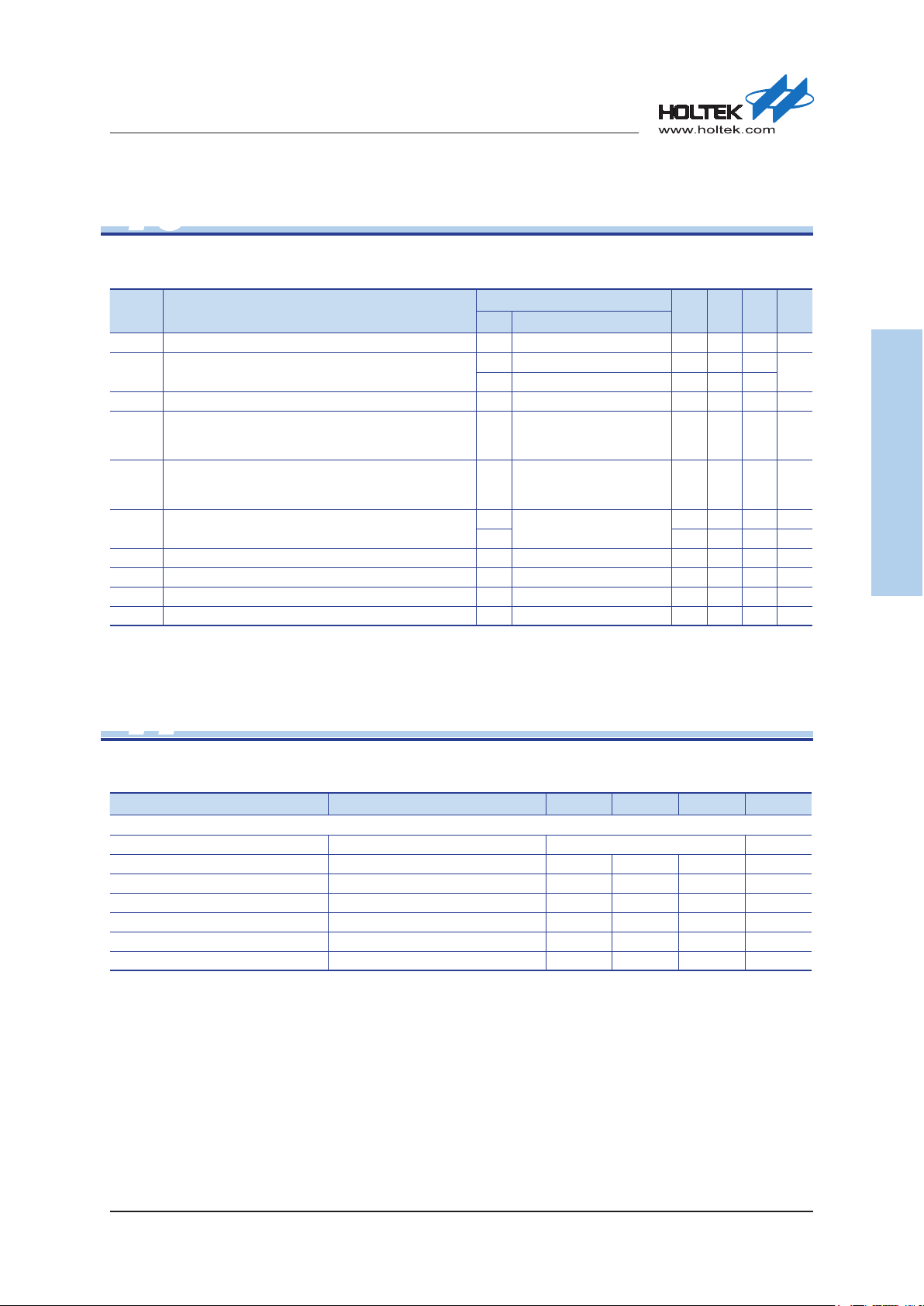

Selection Table

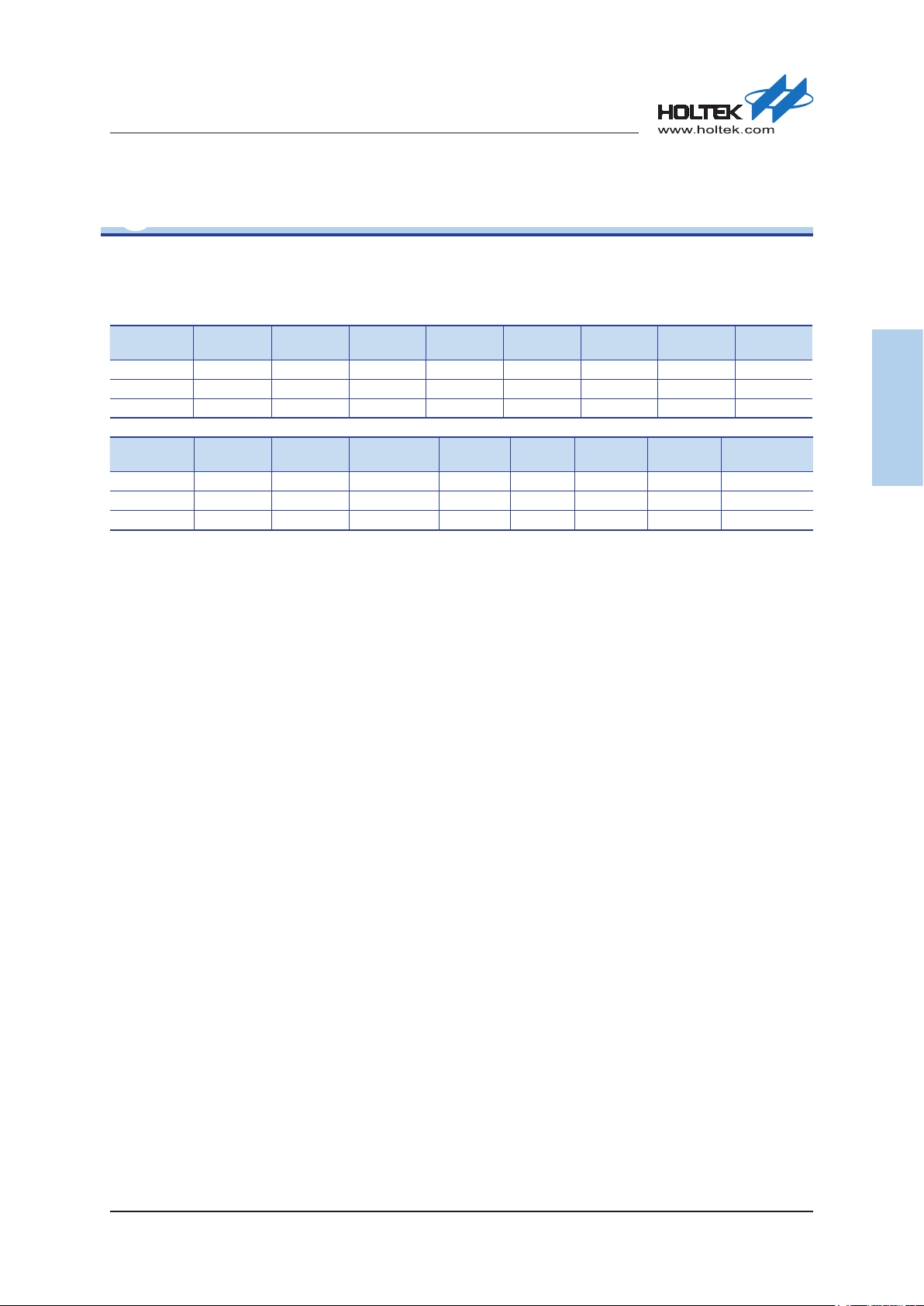

Most features are common to all devices, the main feature distinguishing them are Program

Memory and Data memory capacity, A/D channels, UART numbers and packages. The following

table summarises the main features of each device.

Part No. V

HT85F2260 2.2V~5.5V 16K×8 1280×8 32 7 4 CCU×4 1

HT85F2270 2.2V~5.5V 32K×8 2304×8 48 7 4 CCU×4 1

HT85F2280 2.2V~5.5V 64K×8 2304×8 48 7 4 CCU×4 1

Part No. A/D D/A Comparator I2C SPI UART

HT85F2260 12-bit×7 12-bit×1 2 √ √ 1 √ 48LQFP

HT85F2270 12-bit×9 12-bit×1 2 √ √ 2 √ 48/64LQFP

HT85F2280 12-bit×9 12-bit×1 2 √ √ 2 √ 48/64LQFP

Note:

CCU stands for Compare/Capture Unit.

DD

Program

Memory

Data

Memory

I/O

Ext.

Interrupt

16-bit Timer 16-bit PCA Time Base

Temp.

Sensor

package

Selection Table

Rev. 1.00 17 of 225 January 15, 2015

Page 18

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

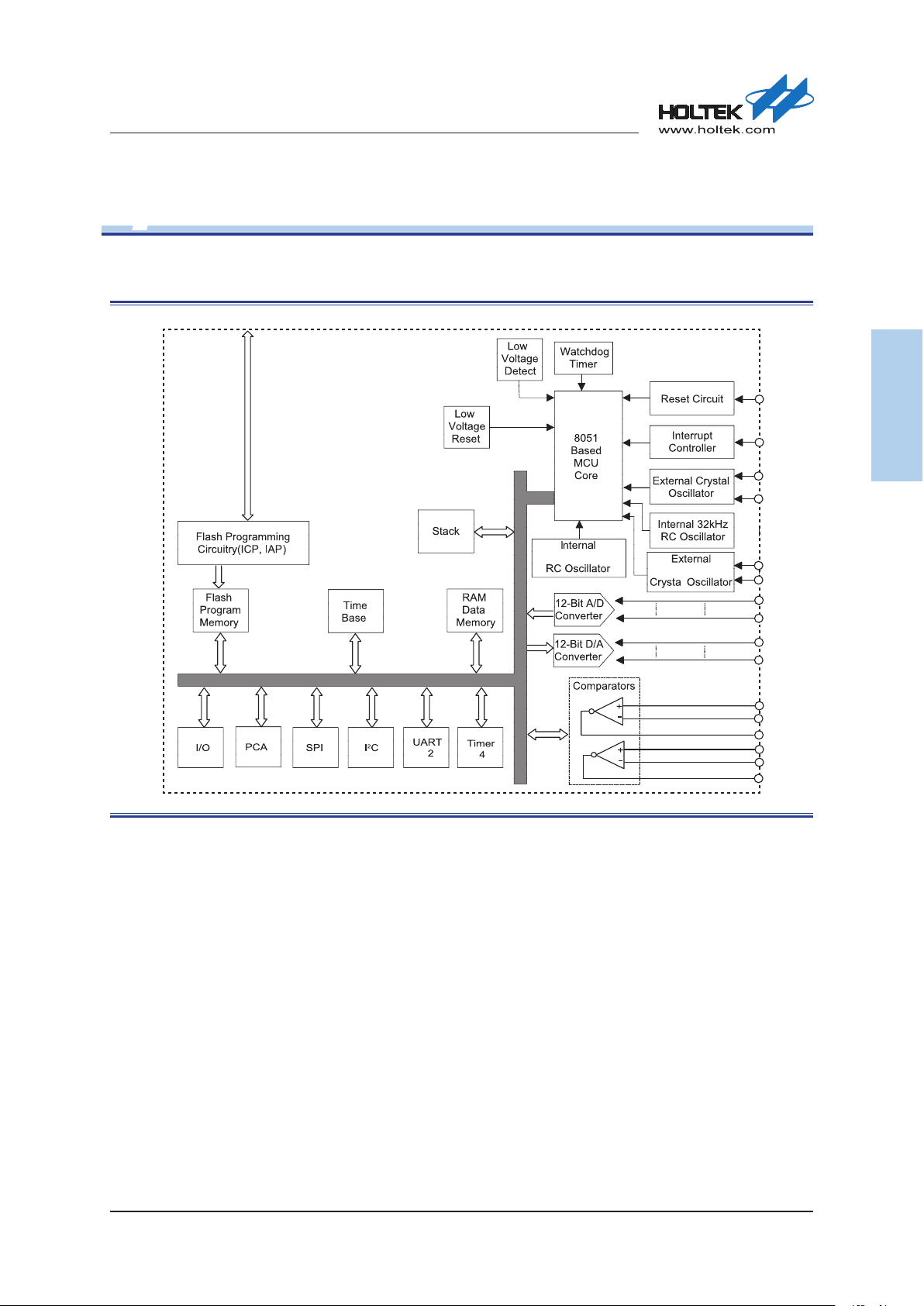

4

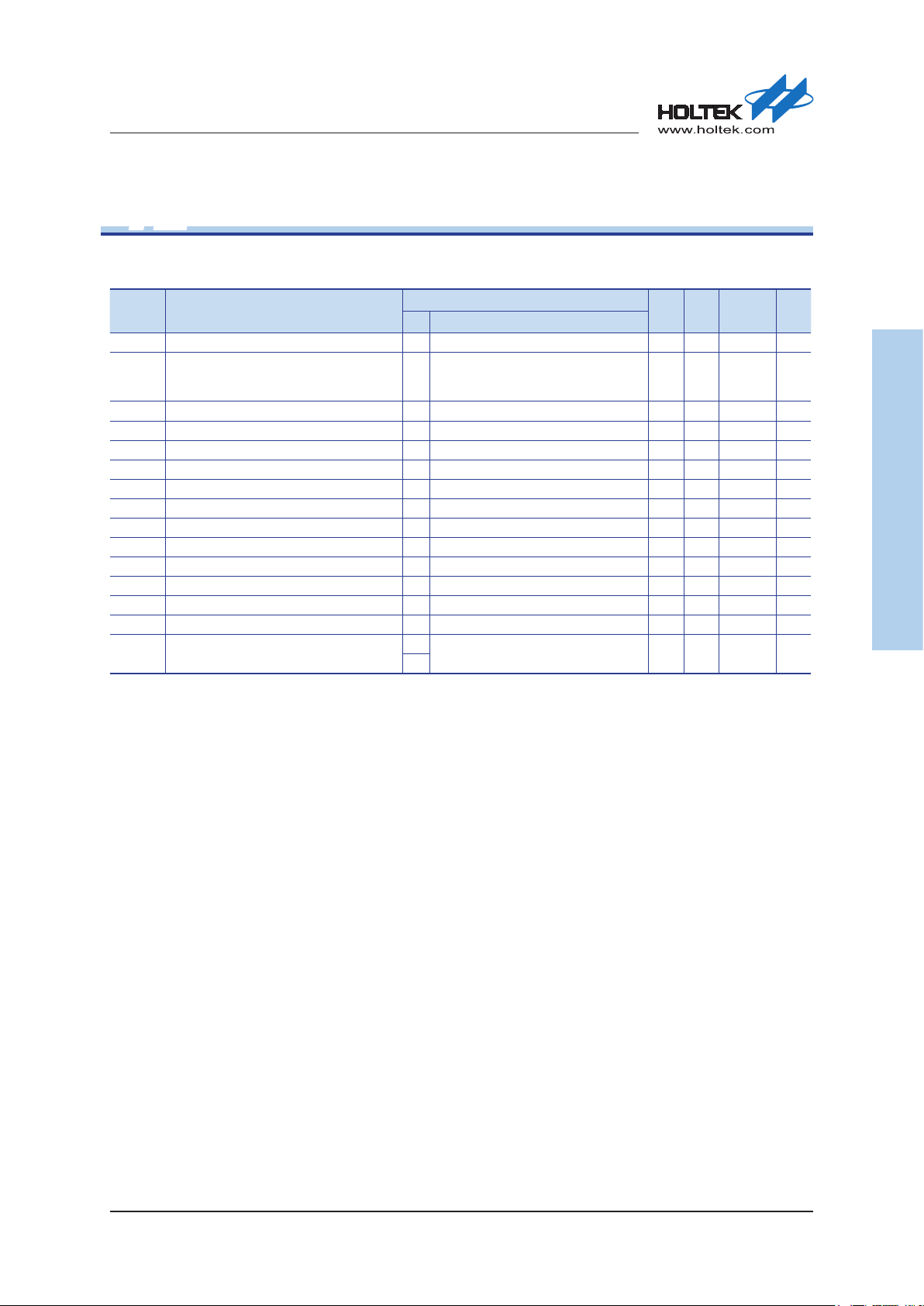

Block Diagram

The following block diagram illustrates the main functional blocks.

3.6864MHz

32768Hz

I

Block Diagram

× ×

Rev. 1.00 18 of 225 January 15, 2015

Page 19

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

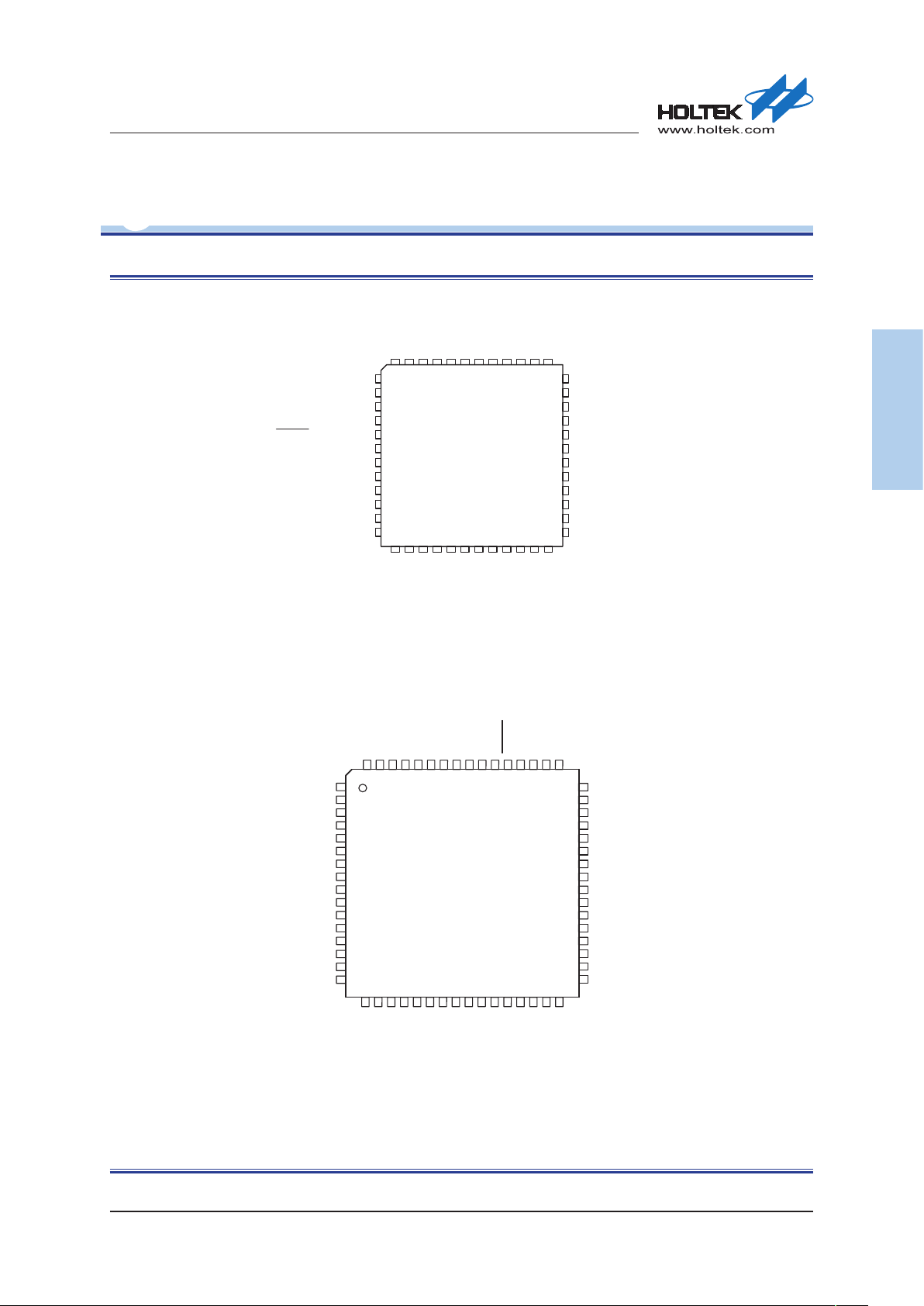

5

Pin Assignment

Pin Assignment

Note:

1. If the pin-shared pin functions have multiple outputs simultaneously, its pin names at the right side of the “/”

sign can be used for higher priority.

2. For both the 48 LQFP-A and 64 LQFP-A packages, both real IC and OCDS EV IC share the same

package.

Rev. 1.00 19 of 225 January 15, 2015

Page 20

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

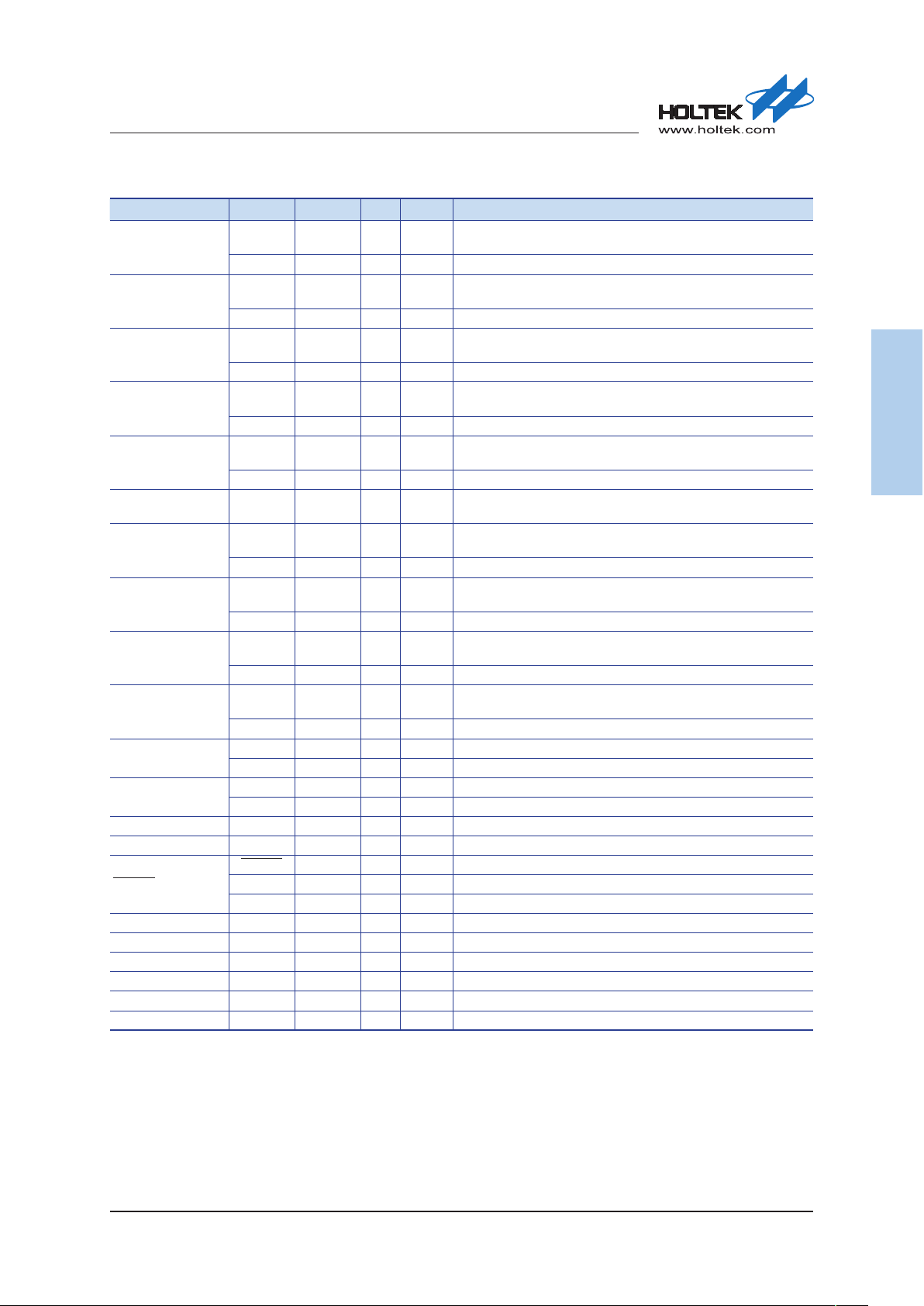

6

Pin Descriptions

With the exception of the power pins, all pins on these devices can be referenced by their Port

name, e.g. P0.0, P0.1 etc, which refer to the digital I/O function of the pins. However these Port

pins are also shared with other function such as the Analog to Digital Converter, Serial Port pins

etc. The function of each pin is listed in the following table, however the details behind how each

pin is congured is contained in other sections of the datasheet.

Pin Name Function OPT I/T O/T Description

P0.0/ICPDA/TDA

P0.1/C1OUT

P0.2/SSN

P0.3/SCK

P0.4/MISO

P0.5/MOSI

P0.6/SCL

P0.7/SDA

P1.0/INT3/CC0

P1.1/INT4/CC1

P1.2/INT5/CC2

P0.0

ICPDA — ICP Data Input/Output

TDA — Debug Data Input/Output

P0.1

C1OUT — — CMOS Comparator 1 Output

P0.2

SSN — ST — SPI Slave select Input

P0.3

SCK — ST CMOS SPI Clock

P0.4

MISO — ST CMOS SPI Master In Slave Out pin

P0.5

MOSI — ST CMOS SPI Master Out Slave In pin

P0.6

SCL — — NMOS I2C Clock

P0.7

SDA — — NMOS I2C Data

P1.0

INT3 — ST — External Interrupt 3 Input

CC0 — ST CMOS Compare/Capture input/output for PCA module 0

P1.1

INT4 — ST — External Interrupt 4 Input

CC1 — ST CMOS Compare/Capture input/output for PCA module 1

P1.2

INT5 — ST — External Interrupt 5 Input

CC2 — ST CMOS Compare/Capture input/output for PCA module 2

P0M0

P0M1

P0WAKE

P0M0

P0M1

P0WAKE

P0M0

P0M1

P0WAKE

P0M0

P0M1

P0WAKE

P0M0

P0M1

P0WAKE

P0M0

P0M1

P0WAKE

P0M0

P0M1

P0WAKE

P0M0

P0M1

P0WAKE

P1M0

P1M1

P1M0

P1M1

P1M0

P1M1

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode and wake-up

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode and wake-up

ST CMOS

ST CMOS

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode and wake-up

General purpose I/O. Register selected I/O mode and wake-up

General purpose I/O. Register selected I/O mode and wake-up

General purpose I/O. Register selected I/O mode and wake-up

General purpose I/O. Register selected I/O mode and wake-up

General purpose I/O. Register selected I/O mode and wake-up

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

Pin Descriptions

Rev. 1.00 20 of 225 January 15, 2015

Page 21

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

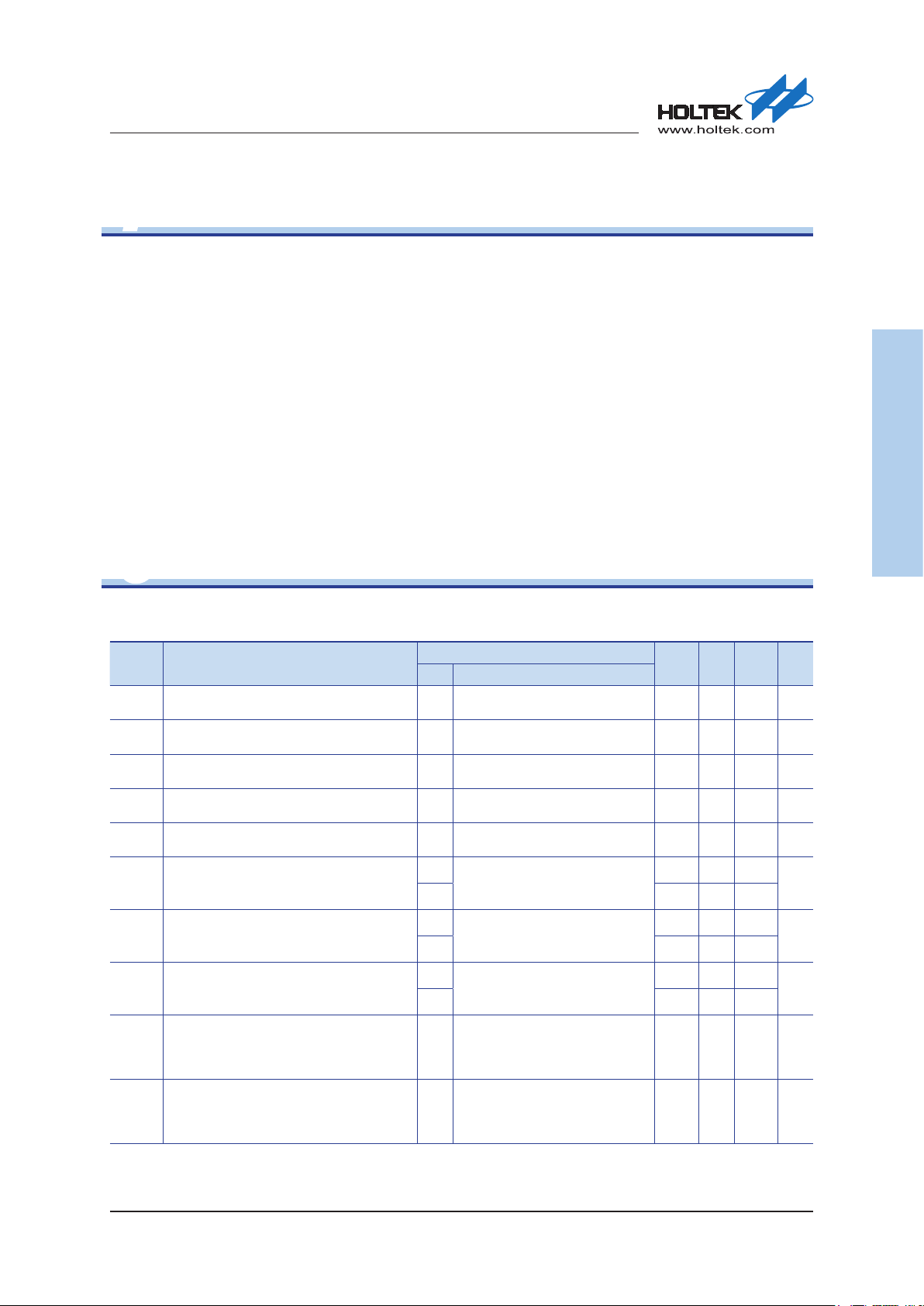

Pin Name Function OPT I/T O/T Description

P1.3

P1.3/INT6/CC3

P1.4/INT2

P1.5/T2EX

P1.6/T2

P1.7 P1.7

P2.0~P2.6 P2.0~P2.6

P2.7/T3

P3.0/RXD0

P3.1/TXD0

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

P3.6/RXD1

P3.7/TXD1

P4.0/AIN.0

P4.1/AIN.1

P4.2/AIN.2

INT6 — ST — External Interrupt 6 Input

CC3 — ST CMOS Compare/Capture input/output for PCA module 3

P1.4

INT2 — ST — External Interrupt 2 Input

P1.5

T2EX — ST — Timer 2 capture trigger

P1.6

T2 — ST CMOS Timer 2 external input or Timer 2 programmable clock output

P2.7

T3 — ST — Timer 3 External Input

P3.0

RXD0 — ST — UART0 Receive Data Input

P3.1

TXD0 — — CMOS UART0 Transmit Data Output

P3.2

INT0 — ST — External Interrupt 0 Input

P3.3

INT1 — ST — External Interrupt 1 Input

P3.4

T0 — ST — Timer 0 External Input

P3.5

T1 — ST — Timer 1 External Input

P3.6

RXD1 — ST — UART1 Receive Data Input

P3.7

TXD1 — — CMOS UART1 Transmit Data Output

P4.0

AIN.0 — AN — ADC Input Channel 0

P4.1

AIN.1 — AN — ADC Input Channel 1

P4.2

AIN.2 — AN — ADC Input Channel 2

P1M0

P1M1

P1M0

P1M1

P1M0

P1M1

P1M0

P1M1

P1M0

P1M1

P2M0

P2M1

P2M0

P2M1

P3M0

P3M1

P3M0

P3M1

P3M0

P3M1

P3M0

P3M1

P3M0

P3M1

P3M0

P3M1

P3M0

P3M1

P3M0

P3M1

P4M0

P4M1

P4M0

P4M1

P4M0

P4M1

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS

ST CMOS

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

Pin Descriptions

Rev. 1.00 21 of 225 January 15, 2015

Page 22

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

Pin Name Function OPT I/T O/T Description

P4.3/AIN.3

P4.4/AIN.4

P4.5/AIN.5

P4.6/AIN.6

P4.7/AIN.7

P5.0~P5.3 P5.0~P5.3

P5.4/C0OUT

P5.5/XT1

P5.6/XT2

P5.7/DAC

CP0-/CP0+

CP1-/CP1+

OSC1 OSC1 — HXT — High Frequency Crystal Oscillator

OSC2 OSC2 — — HXT High Frequency Crystal Oscillator

RESET/ICPCK/TCK

VREF VREF — AN — Reference Voltage for ADC/DAC

VDD VDD — PWR — Positive Power supply for CORE

VCCA1 VCCA1 — PWR — Positive Power supply for I/O pad

VCCA2 VCCA2 — PWR — Positive Power supply for DAC

VCCA3 VCCA3 — PWR — Positive Power supply for ADC

VSS VSS — PWR — Negative Power supply

P4.3

AIN.3 — AN — ADC Input Channel 3

P4.4

AIN.4 — AN — ADC Input Channel 4

P4.5

AIN.5 — AN — ADC Input Channel 5

P4.6

AIN.6 — AN — ADC Input Channel 6

P4.7

AIN.7 — AN — ADC Input Channel 7

P5.4

C0OUT — — CMOS Comparator 0 Output

P5.5

XT1 — LXT — Low Frequency Crystal Oscillator

P5.6

XT2 — — LXT Low Frequency Crystal Oscillator

P5.7

DAC — — CMOS DAC Output

CP0- — AN —

CP0+ — AN — Comparator 0 Non-Inverting Input

CP1- — AN —

CP1+ — AN — Comparator 1 Non-Inverting Input

RESET — ST — RESET pin

ICPCK — ST —

TCK — ST — Debug Clock Input

P4M0

P4M1

P4M0

P4M1

P4M0

P4M1

P4M0

P4M1

P4M0

P4M1

P5M0

P5M1

P5M0

P5M1

P5M0

P5M1

P5M0

P5M1

P5M0

P5M1

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS

ST CMOS

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS General purpose I/O. Register selected I/O mode

ST CMOS General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

General purpose I/O. Register selected I/O mode

Comparator 0 Inverting Input

Comparator 1 Inverting Input

ICP Clock Input

Pin Descriptions

Note:

I/T: Input type; O/T: Output type; ST: Schmitt Trigger input