Page 1

HT46R62, HT46R63,

HT46R64, HT46R65

A/D with LCD Type MCU

Handbook

October 2004

Copyright Ó 2004 by HOLTEK SEMICONDUCTOR INC. All rights reserved. Printed in Taiwan. No part of this publication

may be reproduced, stored in a retrieval system, or transmitted in any form by any means, electronic, mechanical photo

copying, recording or otherwise without the prior written permission of HOLTEK SEMICONDUCTOR INC.

-

Page 2

Contents

Part I Microcontroller Profile ................................................................... 1

Contents

Chapter 1 Hardware Structure ......................................................................................... 3

Introduction ....................................................................................................................3

Features ......................................................................................................................... 4

Technology Features ............................................................................................... 4

Kernel Features ....................................................................................................... 4

Peripheral Features ................................................................................................. 5

Selection Table .............................................................................................................. 5

Block Diagram ............................................................................................................... 6

Pin Assignment .............................................................................................................. 7

Pin Description ............................................................................................................... 9

Absolute Maximum Ratings ......................................................................................... 17

D.C. Characteristics ..................................................................................................... 17

A.C. Characteristics ..................................................................................................... 21

System Architecture ..................................................................................................... 23

Clocking and Pipelining ......................................................................................... 23

Program Counter ................................................................................................... 24

Stack ..................................................................................................................... 25

Arithmetic and Logic Unit - ALU ............................................................................ 26

Program Memory ......................................................................................................... 27

Organization .......................................................................................................... 27

Special Vectors ..................................................................................................... 28

Look-up Table ........................................................................................................ 29

Table Program Example ........................................................................................ 29

Data Memory ............................................................................................................... 31

Organization .......................................................................................................... 31

General Purpose Data Memory ............................................................................ 32

Special Purpose Data Memory ............................................................................. 32

LCD Memory ......................................................................................................... 33

i

Page 3

A/D with LCD Type MCU

Special Function Registers .......................................................................................... 34

Indirect Addressing Registers - IAR0, IAR1 .......................................................... 34

Memory Pointers - MP0, MP1 ............................................................................... 34

Bank Pointer - BP .................................................................................................. 35

Accumulator - ACC................................................................................................ 35

Program Counter Low Register - PCL ......................................................................... 35

Look-up Table Registers - TBLP, TBLH ................................................................ 35

Real Time Clock - RTCC ....................................................................................... 36

Status Register - STATUS ..................................................................................... 37

Interrupt Control Registers - INTC0, INTC1 ......................................................... 37

Timer/Event Counter Registers ............................................................................ 38

Input/Output Ports and Control Registers ............................................................. 38

Pulse Width Modulator Registers - PWM0, PWM1, PWM2, PWM3 ..................... 39

A/D Converter Registers - ADR, ADRL, ADRH, ADCR, ADSR ............................ 39

Input/Output Ports ........................................................................................................ 39

Pull-high Resistors ................................................................................................ 39

Port A Wake-up ..................................................................................................... 39

I/O Port Control Registers .................................................................................... 40

Pin-shared Functions ............................................................................................ 40

Programming Considerations ................................................................................ 43

Comparator .................................................................................................................. 44

Liquid Crystal Display (LCD) Driver ............................................................................. 44

LCD Memory ......................................................................................................... 44

LCD Clock ............................................................................................................. 46

LCD Driver Output ................................................................................................. 46

LCD Voltage Source and Biasing .......................................................................... 53

Programming Considerations ................................................................................ 55

Timer/Event Counters .................................................................................................. 57

Configuring the Timer/Event Counter Input Clock Source .................................... 57

Timer Registers - TMR, TMRL/TMRH, TMR0L/TMR0H, TMR1L/TMR1H ............ 59

Timer Control Registers - TMRC, TMR0C, TMR1C ............................................. 60

Configuring the Timer Mode .................................................................................. 62

Configuring the Event Counter Mode .................................................................... 63

Configuring the Pulse Width Measurement Mode ................................................ 63

Programmable Frequency Divider - PFD ............................................................. 64

Prescaler ................................................................................................................ 65

I/O Interfacing ........................................................................................................ 65

Programming Considerations ................................................................................ 65

Pulse Width Modulator ................................................................................................. 66

6+2 PWM Mode .................................................................................................... 67

7+1 PWM Mode .................................................................................................... 68

PWM Output Control ............................................................................................. 69

ii

Page 4

Contents

Analog to Digital Converter .......................................................................................... 70

A/D Converter Data Registers - ADR, ADRL/ADRH ............................................ 70

A/D Converter Control Register - ADCR .............................................................. 71

A/D Converter Clock Source Register - ACSR ..................................................... 73

A/D Input Pins ....................................................................................................... 74

Summary of A/D Conversion Steps ...................................................................... 74

A/D Transfer Function ........................................................................................... 77

Interrupts ......................................................................................................................78

External Interrupt ................................................................................................... 83

Timer/Event Counter Interrupt ............................................................................... 84

Time Base Interrupt ............................................................................................... 84

Real Time Clock Interrupt - RTC .......................................................................... 85

A/D Interrupt .......................................................................................................... 85

Interrupt Priority ..................................................................................................... 86

Programming Considerations ................................................................................ 87

Reset and Initialization ................................................................................................. 87

Reset ..................................................................................................................... 88

Oscillator ......................................................................................................................95

System Clock Configurations ................................................................................ 95

System Crystal/Ceramic Oscillator ........................................................................ 95

System RC Oscillator ............................................................................................ 96

RTC Oscillator........................................................................................................ 97

Watchdog Timer Oscillator .................................................................................... 98

Internal Clock Source............................................................................................. 99

HALT and Wake-up in Power Down Mode ................................................................ 100

Low Voltage Detector - LVD ...................................................................................... 100

Watchdog Timer ......................................................................................................... 101

Buzzer ........................................................................................................................ 103

Configuration Options ................................................................................................ 105

Application Circuits .....................................................................................................107

Part II Programming Language ........................................................... 111

Chapter 2 Instruction Set Introduction ........................................................................ 113

Instruction Set ............................................................................................................ 113

Instruction Timing ................................................................................................ 113

Moving and Transferring Data ............................................................................. 114

Arithmetic Operations .......................................................................................... 114

Logical and Rotate Operations ............................................................................ 114

Branches and Control Transfer ........................................................................... 114

Bit Operations ...................................................................................................... 114

Table Read Operations ........................................................................................ 115

Other Operations ................................................................................................. 115

iii

Page 5

A/D with LCD Type MCU

Instruction Set Summary ............................................................................................ 115

Convention .......................................................................................................... 115

Chapter 3 Instruction Definition ................................................................................... 119

Chapter 4 Assembly Language and Cross Assembler .............................................. 131

Notational Conventions .............................................................................................. 131

Statement Syntax ...................................................................................................... 132

Name ................................................................................................................... 132

Operation ............................................................................................................ 132

Operand .............................................................................................................. 132

Comment ............................................................................................................. 133

Assembly Directives .................................................................................................. 133

Conditional Assembly Directives ......................................................................... 133

File Control Directives ......................................................................................... 134

Program Directives .............................................................................................. 135

Data Definition Directives .................................................................................... 138

Macro Directives ................................................................................................. 140

Assembly Instructions ................................................................................................ 142

Name ................................................................................................................... 142

Mnemonic ............................................................................................................ 142

Operand, Operator and Expression .................................................................... 142

Miscellaneous ........................................................................................................... 144

Forward References ............................................................................................ 144

Local Labels ........................................................................................................ 144

Reserved Assembly Language Words ................................................................ 145

Cross Assembler Options .......................................................................................... 146

Assembly Listing File Format ..................................................................................... 146

Source Program Listing ....................................................................................... 146

Summary of Assembly ........................................................................................ 147

Miscellaneous ..................................................................................................... 147

Part III Development Tools .................................................................. 149

Chapter 5 MCU Programming Tools ............................................................................ 151

HT-IDE Development Environment ............................................................................ 151

Holtek In-Circuit Emulator - HT-ICE .......................................................................... 152

HT-ICE Interface Card ......................................................................................... 152

OTP Programmer ................................................................................................ 153

OTP Adapter Card .............................................................................................. 153

System Configuration ................................................................................................ 153

HT-ICE Interface Card Settings ........................................................................... 154

iv

Page 6

Contents

Installation .................................................................................................................. 155

System Requirement ........................................................................................... 155

Hardware Installation .......................................................................................... 155

Software Installation ............................................................................................ 155

Chapter 6 Quick Start ................................................................................................... 159

Step 1 - Create a New Project ........................................................................... 159

Step 2 - Add Source Program Files to the Project ............................................ 159

Step 3 - Build the Project ................................................................................... 159

Step 4 - Programming the OTP Device ............................................................. 159

Step 5 - Transmit Code to Holtek ...................................................................... 160

Chapter 7 LCD Simulator................................................................................................161

Introduction .................................................................................................................161

LCD Panel Configuration File .....................................................................................161

Relationship Between the Panel File and the Current Project .............................162

Selecting the HT-LCDS ........................................................................................162

LCD Panel Picture File ...............................................................................................163

Setup the LCD Panel Configuration File .....................................................................163

Setup the Panel Configurations ...........................................................................163

Select the Patterns and their Positions ................................................................164

Add a New Pattern ...............................................................................................164

Delete a Pattern ...................................................................................................165

Change the Pattern ..............................................................................................165

Change the Pattern Position ................................................................................165

How to Add a User-defined Matrix .......................................................................166

Define the Pattern Using the Panel Editor ...........................................................166

Add New Pattern Items Using a Batch File ..........................................................167

Selecting Color for an LCD Panel ........................................................................167

Simulating the LCD .....................................................................................................167

Stop the Simulation ..............................................................................................167

Appendix ................................................................................................. 169

Appendix A Device Characteristic Graphics .............................................................. 171

Appendix B Package Information ................................................................................ 181

v

Page 7

A/D with LCD Type MCU

vi

Page 8

Preface

Preface

Since the founding of the company, Holtek Semiconductor has concentrated much of its design ef

forts in the area of microcontroller development. Although supplying a wide range of semiconduc

tor devices,the microcontroller category has always been a key product category within the Holtek

range, and one which will continue to expand as their devices increase in functionality and matu

rity. By capitalizing on the substantial accumulated skills within its dedicated microcontroller devel

opment department, Holtek has been able to release a comprehensive range of high quality

low-cost microcontroller devices for a wide range of application areas. Many important application

areas have the need to digitize analog input signals, such as those which interface to external sen

sors, and to display the result on a Liquid Crystal Display. Applications that fall into this category

will all require an A/D converter to digitize the signals and an LCD driver function to display the re

sults. To address these needs, Holtek has developed its range of A/D with LCD microcontrollers,

which in addition to having all the features and functions of the A/D range of devices, also include

an LCD driver function that can directly interface to a custom Liquid Crystal Display, providing related users with a fully integrated solution with which to measure and display analog signals. This

high level of device integration and consequent reduction in need for external components therefore provide a high function low cost solution for any users with applications that require both analog signal processing and Liquid Crystal Display functions.

This handbook is divided into three parts for user convenience. Most details regarding general

datasheet information and device specification is located within Part I. Information related to

microcontroller programming such as device instruction set, instruction definition, and assembly

language directivesis found within Part II. Part III relates to the Holtek range ofDevelopment Tools

where information can be found on their installation and use.

By compiling all relevant data together in one handbook, we hope users of the Holtek range of A/D

with LCD Type microcontroller devices will have at their fingertips a useful, complete and simple

means to efficiently implement their microcontroller applications. Holtek's efforts to combine infor

mation on device specifications, programming and development tools into one publication have

produced a handbook which with careful use by the user should result in trouble free designs and

the maximum benefit being gained from the many features of Holtek microcontroller devices.

Holtek welcomes feedback and comments from our customers regarding further improvements.

-

-

-

-

-

-

-

vii

Page 9

A/D with LCD Type MCU

viii

Page 10

Part I

Part I Microcontroller Profile

Microcontroller Profile

1

Page 11

A/D with LCD Type MCU

2

Page 12

Chapter 1

Hardware Structure

This sectionis the main datasheet section of the A/D withLCD Type microcontrollerhandbook and

contains all the parameters and information related to the hardware. The information contained

provides designers with details on all the main hardware features of the A/D with LCD Type

microcontroller range which together with the programming section contains the information to en

able swift and successful implementation of user microcontroller applications. By proper consulta

tion of the relevant parts of this section, users can ensure that they make the most efficient use of

the flexible and multi-function features within the A/D with LCD Type microcontroller series.

Introduction

The HT46R62/HT46C62, HT46R63/HT46C63, HT46R64/HT46C64 and HT46R65/HT46C65

form the series of 8-bit high performance RISC architecture microcontrollers, designed especially

for product applications that interface directly to analog signals and which require to display the

measured dataon aLiquid Crystal Display. Device flexibility is enhanced with the usual features of

the other microcontroller range such as HALT and wake-up functions, integrated timer functions,

oscillator options, programmable frequency divider in addition to Pulse Width Modulator outputs

etc. These features combine to ensure applications require a minimum of external components

and therefore reduce overall product costs. Having the benefits of integrated analog to digital conversion functions which together with integrated LCD driver circuits and, in addition to the usual

Holtek advantages of low power consumption, high performance, I/O flexibility, as well as low cost,

these devices have the versatility to suit a wide range of application possibilities in areas such as

sensor signal processing and displaying, electronic metering, motor driving etc., for both industrial

and homeappliance application areas. Many features are common to all devices however, they dif

fer in areas such as I/O pin count, RAM and ROM capacity, timer number and size, A/D channels,

PWM outputs, LCD outputs etc.

Chapter 1 Hardware Structure

1

-

-

-

The HT46R62, HT46R63, HT46R64 and HT46R65 are OTP devices offering the advantages of

easy and effective program updates, using the Holtek range of development and programming

tools. These devices provide the designer with the means for fast and low cost product develop

ment cycles. However, for applications that are at a mature state in their design process, the

HT46C62, HT46C63, HT46C64 and HT46C65 mask version devices offer a complementary de

vice for products with high volume and low cost demands. Fully pin and functionally compatible

with their OTP sister devices, such mask version devices provide the ideal substitute for products

which have gone beyond their development cycle and are facing cost down demands.

-

-

3

Page 13

Features

A/D with LCD Type MCU

Technology Features

High-performance RISC Architecture

·

Low-power Fully Static CMOS Design

·

Operating Voltage:

·

f

=4MHz: 2.2V~5.5V

SYS

=8MHz: 3.3V~5.5V

f

SYS

Power Consumption:

·

3mA Typical at 5V 8MHz (for Crystal Oscillator with ADC Disabled)

Maximum of 1mA Standby Current at 3V with WDT Disabled

Cycle Time:

·

Up to 0.5ms Instruction Cycle with 8MHz System Clock

Temperature Range:

·

Operating Temperature -40°Cto85°C (Industrial Grade)

Storage Temperature -50°Cto125°C

Kernel Features

Program Memory:

·

2K´14 OTP/Mask ROM (HT46R62/HT46C62)

4K´15 OTP/Mask ROM (HT46R63/HT46C63, HT46R64/HT46C64)

8K´16 OTP/Mask ROM (HT46R65/HT46C65)

· Data Memory:

88´8 RAM (HT46R62/HT46C62)

192´8 RAM (HT46R64/HT46C64)

208´8 RAM (HT46R63/HT46C63)

384´8 RAM (HT46R65/HT46C65)

· LCD Driver:

20´2, 20´3or19´4 Segments (HT46R62/HT46C62)

20´3or19´4 Segments (HT46R63/HT46C63)

33´2, 33´3or32´4 Segments (HT46R64/HT46C64)

41´2, 41´3or40´4 Segments (HT46R65/HT46C65)

·

Table Read Function

·

Multi-level Hardware Stack:

6-level (HT46R62/HT46C62)

8-level (HT46R63/HT46C63, HT46R64/HT46C64)

16-level (HT46R65/HT46C65)

·

Direct and Indirect Data Addressing Mode

·

Bit Manipulation Instructions

·

63 Powerful Instructions

·

Most Instructions Implemented in 1 Machine Cycle

4

Page 14

Chapter 1 Hardware Structure

Peripheral Features

From 20 to 32 Bidirectional I/O with Pull-high Options

·

Port A Wake-up Options

·

Multi-channel 8, 9 or 10-bit A/D Converter

·

Internal LCD Driver

·

Internal Dedicated LCD Memory

·

Pulse Width Modulator Outputs

·

Comparator (HT46R63/HT46C63 only)

·

Two External Interrupt Inputs

·

Event Counter Input

·

Full Timer Functions with Prescaler and Interrupt

·

Watchdog Timer (WDT)

·

HALT and Wake-up Feature for Power Saving Operation

·

PFD Output (except HT46R63/HT46C63)

·

Buzzer Drivers Outputs (except HT46R63/HT46C63)

·

On-chip Crystal and RC Oscillator

·

32768Hz Real Time Clock (RTC) Function

·

Low Voltage Reset (LVR) Feature for Brown-out Protection (except HT46R63/HT46C63)

·

Low Voltage Detector (except HT46R63/HT46C63)

·

Programming Interface with Code Protection

·

Mask Version Devices Available for High Volume Production

·

Full Suite of Supported Hardware and Software Tools Available

·

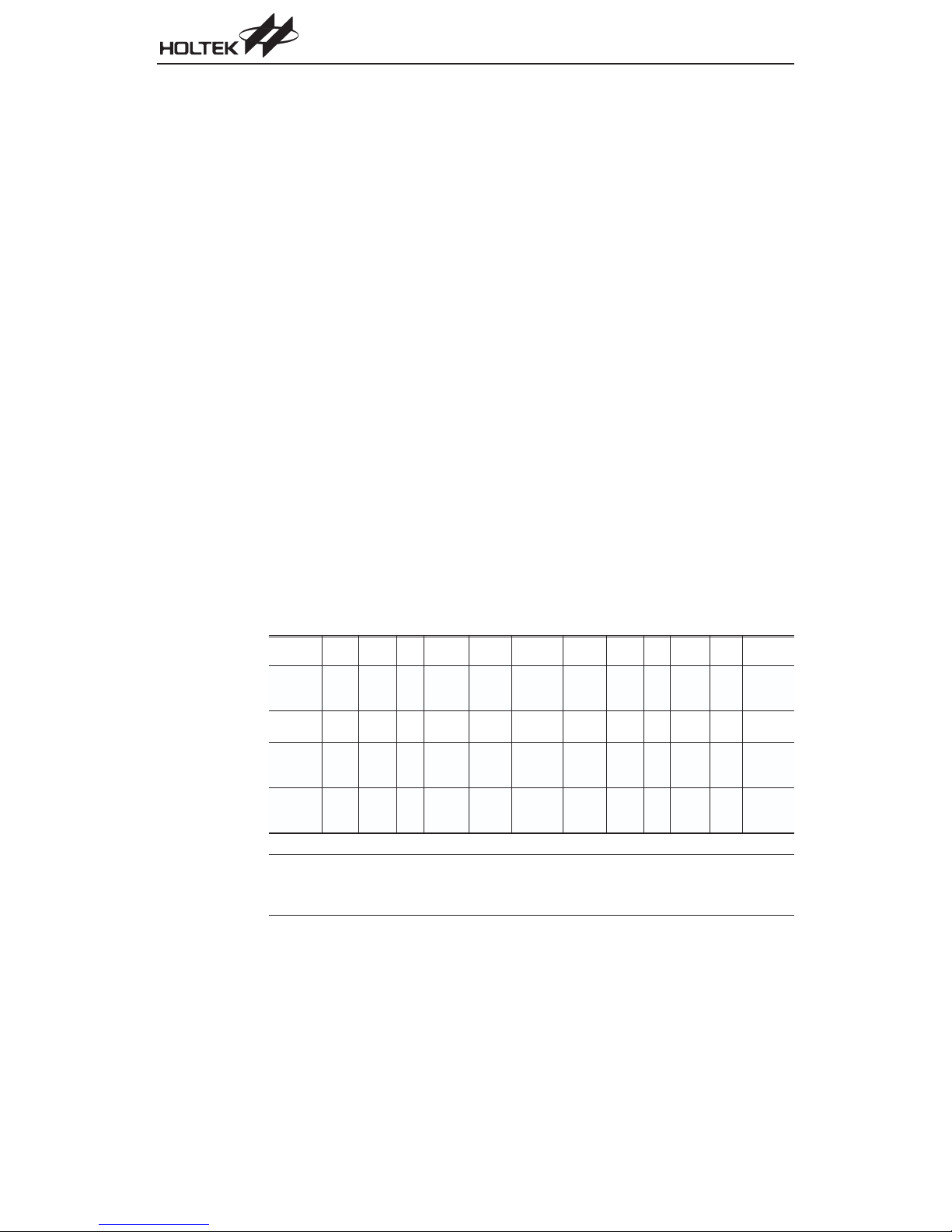

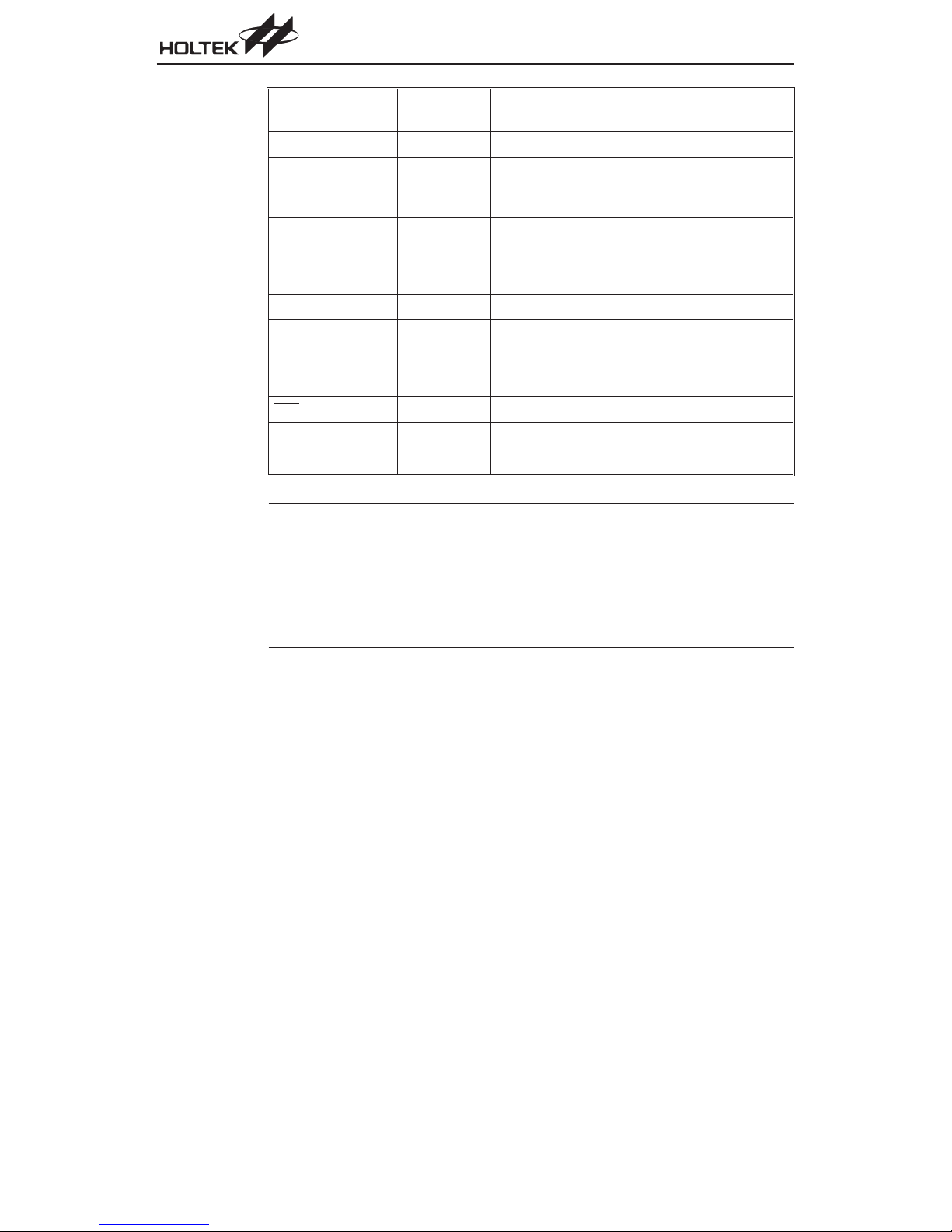

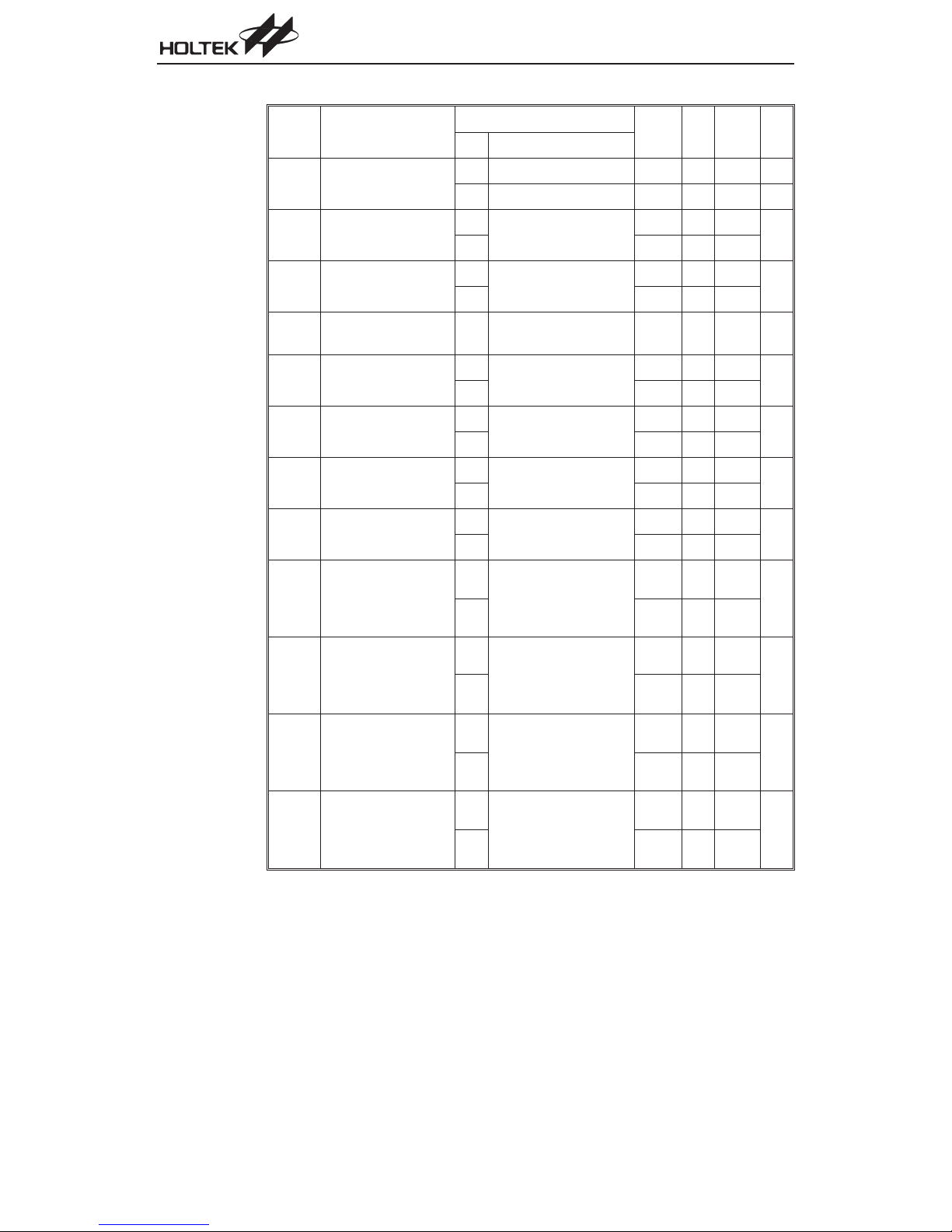

Selection Table

The series of A/D with LCD microcontrollers include a comprehensive range of features, some of

which are standard and some of which are device dependent. Most features are common to all devices, the main features distinguishing them are Program Memory, Data Memory capacity, I/O

count, timer functions, A/D channels, LCD outputs and PWM outputs. To assist users in their selection of the most appropriate device for their application, the following table, which summarizes the

main features of each device, is provided.

Part No.

HT46R62

HT46C62

HT46R63

HT46C63

HT46R64

HT46C64

HT46R65

HT46C65

Note

1. Part numbers including ²C² are mask version devices while ²R² are OTP devices.

2. For devices that exist in two package formats, the table reflects the situation for the larger

package.

Prog.

Data

Mem.

Mem.

2K´14 88´8

4K´15 208´8

4K´15 192´8

8K´16 384´8

I/O LCD Timer Interrupt A/D PWM PFD Buzzer Stack

20´2,

20

32

24

24

20´3or

19´4

20´3or

19´4

33´2,

33´3or

32´4

41´2,

41´3or

40´4

8-bit´1

16-bit´1

8-bit´1

16-bit´1

16-bit´2

6

9-bit´6 8-bit´3 ÖÖ

6

8-bit´8 8-bit´4

7

10-bit´8 8-bit´4 ÖÖ

7

10-bit´8 8-bit´4 ÖÖ

¾¾

6 56SSOP

8

8

16

5

Package

Types

56SSOP,

100QFP

56SSOP,

100QFP

56SSOP,

100QFP

Page 15

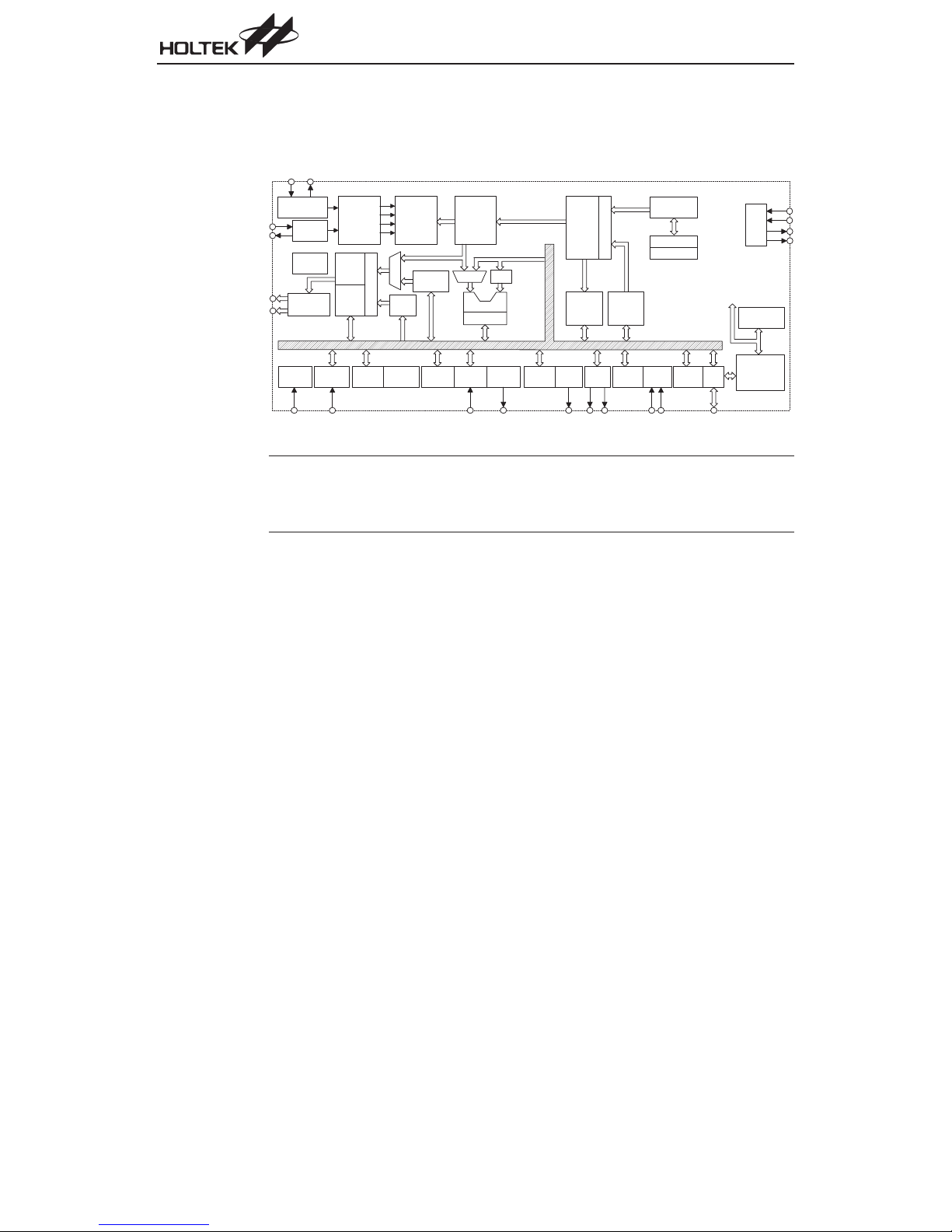

Block Diagram

The following block diagram illustrates the main functional blocks of the A/D with LCD Type

microcontroller series of devices.

A/D with LCD Type MCU

P W M

P r o g r a m

M e m o r y

L o o k - u p

T a b l e

R e g i s t e r

B u z z e r

D r i v e r

A d d r e s s D e c o d e r

L o o k - u p

T a b l e

P o i n t e r

C o n f i g .

R e g i s t e r

S t a c k P o i n t e r

I n t e r r u p t

C i r c u i t

S y s t e m R C /

X ' t a l O s c i l l a t o r

O s c i l l a t o r

L C D D r i v e r s

C O M

R e s e t &

L V R / L V D

1. This block diagram represents the OTP device, for the mask device there is no Device

Note

R T C

O S C

W D T

S E G

C o n v e r t e r

A / D

T i m i n g

G e n e r a t o r

L C D

M e m o r y

D a t a

M e m o r y

C o n f i g .

R e g i s t e r

A d d r e s s D e c o d e r

I n s t r u c t i o n

M

U

X

B a n k

P o i n t e r

W a t c h d o g

T i m e r

D e c o d e r

M e m o r y

P o i n t e r

C o n f i g .

R e g i s t e r

I n s t r u c t i o n

R e g i s t e r

M U X

T i m e r ( s ) /

C o u n t e r

A L U

S h i f t e r

A C C

C o n f i g .

P F D

R e g i s t e r

Programming Circuitry.

2. The Comparator function only exists in the HT46R63/HT46C63 devices.

3. The LVR/LVD, Buzzer driver and PFD do not exist in the HT46R63/HT46C63.

P r o g r a m

C o u n t e r

S t a c k

C o n f i g .

R e g i s t e r

P o r t s

I / O

T o P r o g r a m

M e m o r y

C o m p a r a t o r

C o n f i g u r a t i o n

O p t i o n

D e v ic e

P r o g r a m m i n g

C i r c u i t r y

6

Page 16

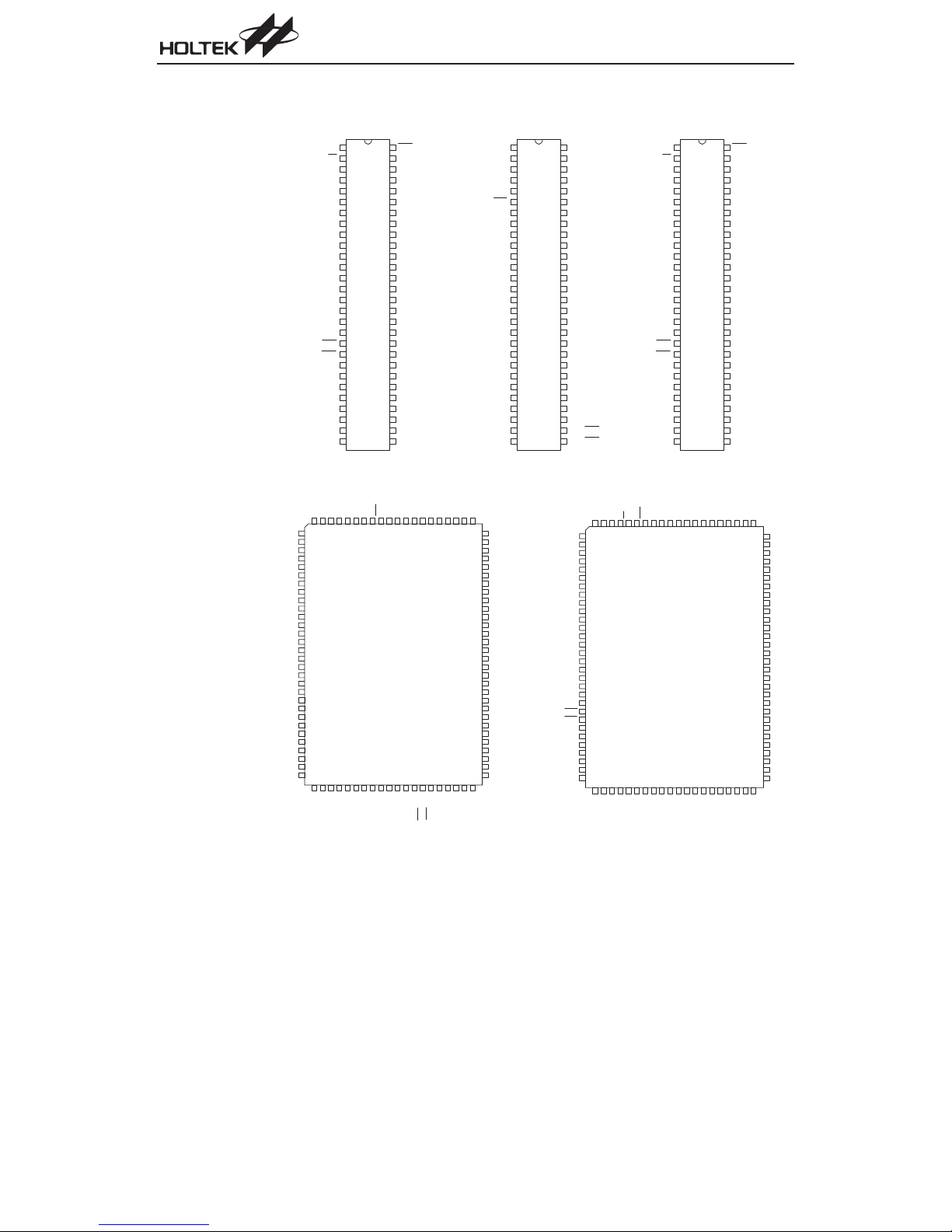

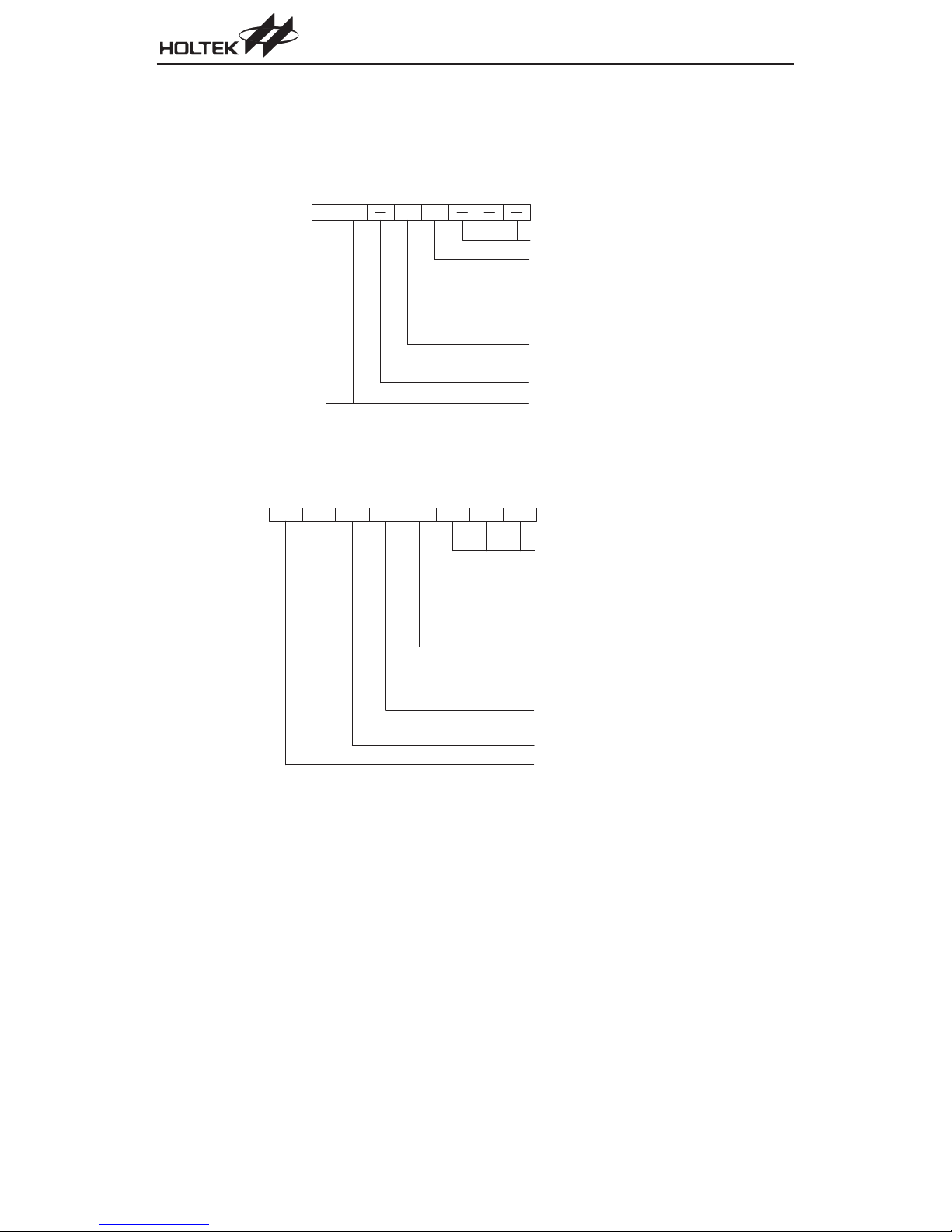

Pin Assignment

Chapter 1 Hardware Structure

P A 0 / B Z

1

P A 1 / B Z

2

P A 2

3

P A 3 / P F D

4

P A 4

5

P A 5

6

P A 6

7

P A 7

8

P B 0 / A N 0

9

P B 1 / A N 1

1 0

P B 2 / A N 2

1 1

P B 3 / A N 3

1 2

P B 4 / A N 4

1 3

P B 5 / A N 5

1 4

V S S

1 5

1 6

1 7

1 8

P D 4 / I N T 0

1 9

P D 5 / I N T 1

2 0

P D 6 / T M R

2 1

V L C D

2 2

V M A X

2 3

2 4

V 1

2 5

V 2

2 6

C 1

2 7

C 2

2 8

C O M 0

H T 4 6 R 6 2 / H T 4 6 C 6 2

5 6 S S O P - A

N C

N C

N C

N C

N C

N C

N C

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

H T 4 6 R 6 3 / H T 4 6 C 6 3

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

2 9

3 0

3 1

P C 0

1 0 0 Q F P - A

3 2 3 3 3 4 3 5 3 6 3 7 3 8 3 9 4 0 4 1 4 2 4 3 4 4 4 5 4 6 4 7 4 8 4 9 5 0

P C 6

P C 5

P C 4

P C 3

P C 2

P C 1

P B 0 / A N 0

P B 1 / A N 1

P B 2 / A N 2

P B 3 / A N 3

P B 4 / A N 4

P B 5 / A N 5

P B 6 / A N 6

P B 7 / A N 7

A V D D

N C

N C

N C

N C

P A 0

P A 1

P A 2

P A 3

P A 4

P A 5

P A 6

P A 7

V S S

N C

N C

N C

N C

N C

N C

N C

N C

P D 0 / P W M 0

P D 1 / P W M 1

P D 2 / P W M 2

5 6

5 5

5 4

5 3

5 2

5 1

5 0

4 9

4 8

4 7

4 6

4 5

4 4

4 3

4 2

4 1

4 0

3 9

3 8

3 7

3 6

3 5

3 4

3 3

3 2

3 1

3 0

2 9

R E S

O S C 1

O S C 2

V D D

O S C 3

O S C 4

S E G 0

S E G 1

S E G 2

S E G 3

S E G 4

S E G 5

S E G 6

S E G 7

S E G 8

S E G 9

S E G 1 0

S E G 1 1

S E G 1 2

S E G 1 3

S E G 1 4

S E G 1 5

S E G 1 6

S E G 1 7

S E G 1 8

C O M 3 / S E G 1 9

C O M 2

C O M 1

O S C 4

O S C 3

O S C 2

O S C 1

P B 0 / A N 0

P B 1 / A N 1

P B 2 / A N 2

P B 3 / A N 3

A V D D

P D 0 / P W M 0

P D 1 / P W M 1

P D 2 / P W M 2

P D 3 / P W M 3

V D D

R E S

P A 0

P A 1

P A 2

P A 3

P A 4

P A 5

P A 6

P A 7

V S S

P C 0

P C 1

P C 2

P C 3

H T 4 6 R 6 3 / H T 4 6 C 6 3

C M P O

C H G O

C M P N

C M P P

O S C 4

O S C 3

O S C 2

O S C 1

V D D

R E S

P D 3 / P W M 3

P D 2 / P W M 2

P D 2 / P W M 1

P D 0 / P W M 0

P C 7

V L C D

N C

N C

8 18 28 38 48 58 68 78 88 99 09 19 29 39 49 59 69 79 89 91 0 0

N C

8 0

N C

7 9

N C

7 8

N C

7 7

N C

7 6

N C

7 5

C O M 0

7 4

C O M 1

7 3

C O M 2

7 2

C O M 3 /S E G 1 9

7 1

S E G 1 8

7 0

S E G 1 7

6 9

S E G 1 6

6 8

S E G 1 5

6 7

S E G 1 4

6 6

S E G 1 3

6 5

S E G 1 2

6 4

S E G 1 1

6 3

S E G 1 0

6 2

S E G 9

6 1

S E G 8

6 0

S E G 7

5 9

S E G 6

5 8

S E G 5

5 7

S E G 4

5 6

S E G 3

5 5

S E G 2

5 4

S E G 1

5 3

S E G 0

5 2

N C

5 1

N C

N C

N C

N C

P D 7

P D 6 / T M R

P D 5 / I N T 1

P D 4 / I N T 0

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

5 6 S S O P - A

P D 0 / P W M 0

P D 1 / P W M 1

P D 2 / P W M 2

P D 3 / P W M 3

5 6

5 5

5 4

5 3

5 2

5 1

5 0

4 9

4 8

4 7

4 6

4 5

4 4

4 3

4 2

4 1

4 0

3 9

3 8

3 7

3 6

3 5

3 4

3 3

3 2

3 1

3 0

2 9

P B 0 / A N 0

P B 1 / A N 1

P B 2 / A N 2

P B 3 / A N 3

P B 4 / A N 4

P B 5 / A N 5

P B 6 / A N 6

P B 7 / A N 7

P D 4 / I N T 0

P D 5 / I N T 1

P D 6 / T M R 0

P D 7 / T M R 1

C H G O

C M P O

C M P P

C M P N

V L C D

C O M 0

C O M 1

C O M 2

C O M 3 / S E G 1 9

S E G 1 4

S E G 1 3

S E G 1 2

S E G 1 1

S E G 1 0

S E G 9

S E G 8

S E G 7

S E G 6

S E G 5

S E G 4

S E G 3

S E G 2

S E G 1

S E G 0

P D 7

P D 6 / T M R

P D 5 / I N T 1

P D 4 / I N T 0

P A 4

1

P A 5

2

N C

3

N C

4

N C

5

N C

6

N C

7

P A 6

8

P A 7

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

V S S

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

N C

2 7

N C

2 8

N C

2 9

N C

3 0

N C

3 2 3 3 3 4 3 5 3 6 3 7 3 8 3 9 4 0 4 1 4 2 4 3 4 4 4 5 4 6 4 7 4 8 4 9 5 0

3 1

V M A X

V L C D

P D 0 / P W M 0

P D 1 / P W M 1

P D 2 / P W M 2

P D 6 / T M R 0

P A 3 / P F D

P A 1 / B Z

P A 0 / B Z

R E S

P A 2

H T 4 6 R 6 4 / H T 4 6 C 6 4

C 2

C 1

V 2

V 1

P A 0 / B Z

P A 1 / B Z

P A 2

P A 3 / P F D

P A 4

P A 5

P A 6

P A 7

P B 0 / A N 0

P B 1 / A N 1

P B 2 / A N 2

P B 3 / A N 3

P B 4 / A N 4

P B 5 / A N 5

V S S

P D 4 / I N T 0

P D 5 / I N T 1

V L C D

V M A X

V 1

V 2

C 1

C 2

C O M 0

H T 4 6 R 6 4 / H T 4 6 C 6 4

5 6 S S O P - A

O S C 4

O S C 3

O S C 2

O S C 1

V D D

1 0 0 Q F P - A

C O M 2

C O M 1

C O M 0

C O M 3 /S E G 3 2

S E G 3 1

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

N C

S E G 3 0

R E S

5 6

O S C 1

5 5

O S C 2

5 4

V D D

5 3

O S C 3

5 2

O S C 4

5 1

S E G 8

5 0

S E G 9

4 9

S E G 1 0

4 8

S E G 1 1

4 7

S E G 1 2

4 6

S E G 1 3

4 5

S E G 1 4

4 4

S E G 1 5

4 3

S E G 1 6

4 2

S E G 1 7

4 1

S E G 1 8

4 0

S E G 1 9

3 9

S E G 2 0

3 8

S E G 2 1

3 7

S E G 2 2

3 6

S E G 2 3

3 5

S E G 2 4

3 4

S E G 2 5

3 3

S E G 2 6

3 2

C O M 3 / S E G 3 2

3 1

C O M 2

3 0

2 9

C O M 1

S E G 0

N C

N C

N C

N C

N C

N C

N C

8 18 28 38 48 58 68 78 88 99 09 19 29 39 49 59 69 79 89 91 0 0

S E G 1

8 0

S E G 2

7 9

S E G 3

7 8

N C

7 7

N C

7 6

N C

7 5

S E G 4

7 4

S E G 5

7 3

S E G 6

7 2

S E G 7

7 1

S E G 8

7 0

S E G 9

6 9

S E G 1 0

6 8

S E G 1 1

6 7

S E G 1 2

6 6

S E G 1 3

6 5

S E G 1 4

6 4

S E G 1 5

6 3

S E G 1 6

6 2

S E G 1 7

6 1

S E G 1 8

6 0

S E G 1 9

5 9

S E G 2 0

5 8

S E G 2 1

5 7

N C

5 6

N C

5 5

N C

5 4

N C

5 3

N C

5 2

N C

S E G 2 9

S E G 2 8

5 1

S E G 2 7

S E G 2 6

S E G 2 5

S E G 2 4

S E G 2 3

S E G 2 2

7

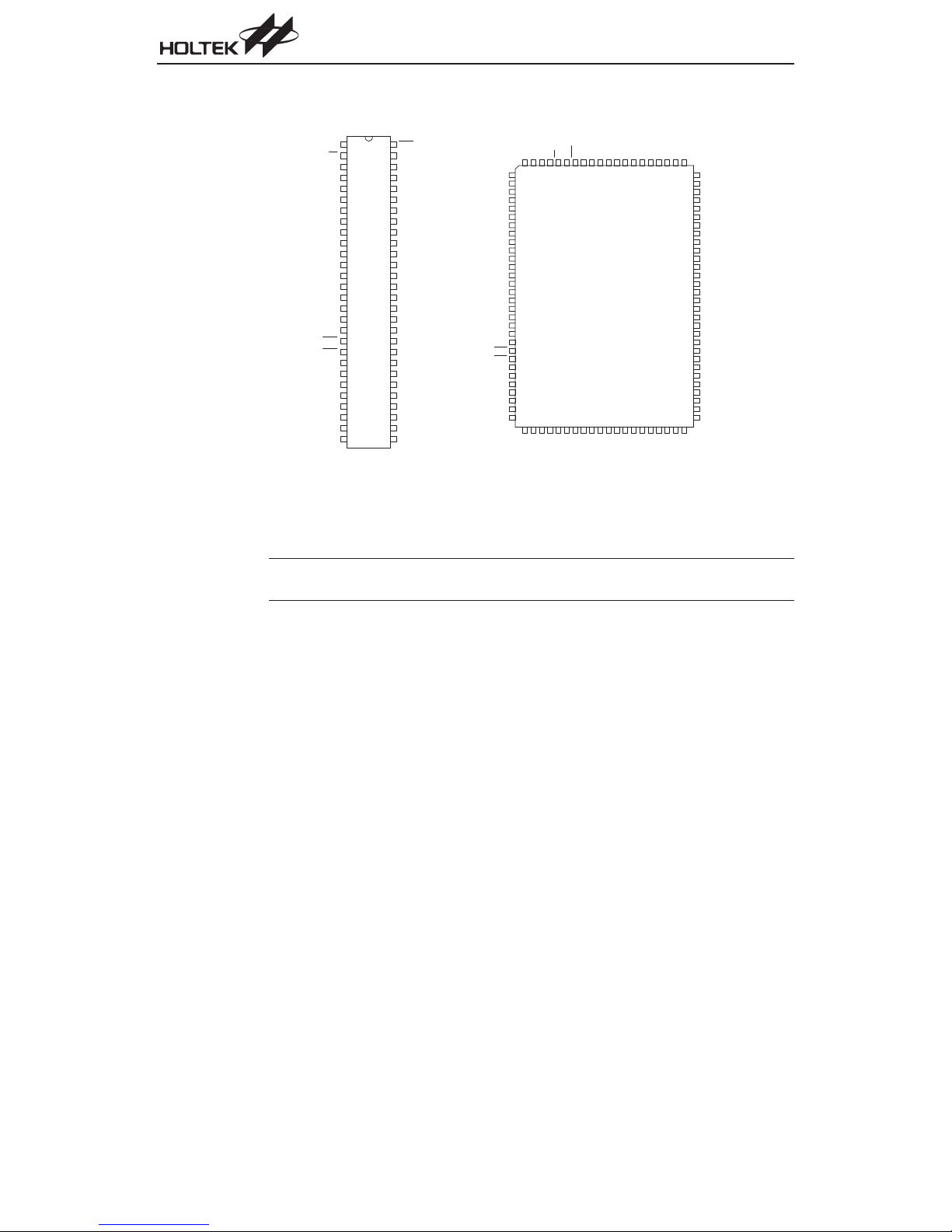

Page 17

P A 0 / B Z

P A 1 / B Z

P A 2

P A 3 / P F D

P A 4

P A 5

P A 6

P A 7

P B 0 / A N 0

P B 1 / A N 1

P B 2 / A N 2

P B 3 / A N 3

P B 4 / A N 4

P B 5 / A N 5

V S S

P D 0 / P W M 0

P D 1 / P W M 1

P D 2 / P W M 2

P D 4 / I N T 0

P D 5 / I N T 1

P D 6 / T M R 0

V L C D

V M A X

V 1

V 2

C 1

C 2

C O M 0

H T 4 6 R 6 5 / H T 4 6 C 6 5

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

5 6 S S O P - A

5 6

5 5

5 4

5 3

5 2

5 1

5 0

4 9

4 8

4 7

4 6

4 5

4 4

4 3

4 2

4 1

4 0

3 9

3 8

3 7

3 6

3 5

3 4

3 3

3 2

3 1

3 0

2 9

R E S

O S C 1

O S C 2

V D D

O S C 3

O S C 4

S E G 1 6

S E G 1 7

S E G 1 8

S E G 1 9

S E G 2 0

S E G 2 1

S E G 2 2

S E G 2 3

S E G 2 4

S E G 2 5

S E G 2 6

S E G 2 7

S E G 2 8

S E G 2 9

S E G 3 0

S E G 3 1

S E G 3 2

S E G 3 3

S E G 3 4

C O M 3 / S E G 4 0

C O M 2

C O M 1

P B 0 / A N 0

P B 1 / A N 1

P B 2 / A N 2

P B 3 / A N 3

P B 4 / A N 4

P B 5 / A N 5

P B 6 / A N 6

P B 7 / A N 7

P D 0 / P W M 0

P D 1 / P W M 1

P D 2 / P W M 2

P D 3 / P W M 3

P D 4 / I N T 0

P D 5 / I N T 1

P D 6 / T M R 0

P D 7 / T M R 1

A/D with LCD Type MCU

P A 3 / P F D

P A 1 / B Z

P A 0 / B Z

O S C 3

O S C 2

O S C 1

V D D

R E S

P A 4

P A 2

1

P A 5

2

N C

3

N C

4

N C

5

N C

6

N C

7

P A 6

8

P A 7

9

1 0

1 1

1 2

1 3

1 4

H T 4 6 R 6 5 / H T 4 6 C 6 5

1 5

1 6

1 7

V S S

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

N C

2 7

N C

2 8

N C

2 9

N C

3 0

N C

3 1

V L C D

1 0 0 Q F P - A

3 2 3 3 3 4 3 5 3 6 3 7 3 8 3 9 4 0 4 1 4 2 4 3 4 4 4 5 4 6 4 7 4 8 4 9 5 0

V 1

V M A X

C O M 2

C O M 1

C O M 0

C 2

C 1

V 2

C O M 3 /S E G 4 0

O S C 4

S E G 0

S E G 1

S E G 2

S E G 3

S E G 4

S E G 5

S E G 6

S E G 7

S E G 8

8 18 28 38 48 58 68 78 88 99 09 19 29 39 49 59 69 79 89 91 0 0

S E G 9

8 0

S E G 1 0

7 9

S E G 1 1

7 8

N C

7 7

N C

7 6

N C

7 5

S E G 1 2

7 4

S E G 1 3

7 3

S E G 1 4

7 2

S E G 1 5

7 1

S E G 1 6

7 0

S E G 1 7

6 9

S E G 1 8

6 8

S E G 1 9

6 7

S E G 2 0

6 6

S E G 2 1

6 5

S E G 2 2

6 4

S E G 2 3

6 3

S E G 2 4

6 2

S E G 2 5

6 1

S E G 2 6

6 0

S E G 2 7

5 9

S E G 2 8

5 8

S E G 2 9

5 7

N C

5 6

N C

5 5

N C

5 4

N C

5 3

N C

5 2

N C

5 1

S E G 3 0

S E G 3 1

S E G 3 2

S E G 3 3

S E G 3 4

S E G 3 5

S E G 3 6

S E G 3 7

S E G 3 8

S E G 3 9

Note The pin compatibility features of the microcontroller packages allow for straightforward upgrading

to devices of higher functionality with minimal changes to application hardware.

8

Page 18

Pin Description

HT46R62/HT46C62

PA0/BZ

PA1/BZ

PA2

PA3/PFD

PA4~PA7

PB0/AN0

PB1/AN1

PB2/AN2

PB3/AN3

PB4/AN4

PB5/AN5

PD0/PWM0

PD1/PWM1

PD2/PWM2

PD4/INT0

PD5/INT1

PD6/TMR

OSC1

OSC2

OSC3

OSC4

VLCD

Pin Name I/O

I/O

I/O Pull-high

I/O

O

O

¾¾

Configuration

Option

Pull-high

Wake-up

Buzzer

PFD

Pull-high

PWM

Interrupt

I

Crystal or RC

I

RTC or

System Clock

Chapter 1 Hardware Structure

Description

Bidirectional 8-bit input/output port. Each individual bit

on this port can be configured as a wake-up input by a

configuration option. Software instructions determine if

the pin is a CMOS output or Schmitt Trigger input. Con

figuration options determine which pins on the port

have pull-high resistors. Pins PA0, PA1 and PA3 are

pin-shared with BZ, BZ

tion of which is chosen via configuration options.

Bidirectional 6-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine which

pins on the port have pull-high resistors. PB is

pin-shared with the A/D input pins. The A/D inputs are

selected via software instructions. Once selected as an

A/D input, the I/O function and pull-high resistor func

tions are disabled automatically.

Bidirectional 6-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine which

pins on the port have pull-high resistors. PD0~PD2 are

pin-shared with PWM0~PWM2, the function of each pin

is selected via a configuration option. Pins PD4 and

PD5 are pin-shared with external interrupt input pins

INT0

and INT1 respectively. Configuration options determine the interrupt enable/disable and the interrupt

low/high trigger type. Pin PD6 is pin-shared with the external timer input pin TMR.

OSC1 and OSC2 are connected to an external RC net

work or external crystal (determined by configuration

option) for the internal system clock. For external RC

system clock operation, OSC2 is an output pin for 1/4

system clock. If an RTC oscillator on pins OSC3 and

OSC4 is used as a system clock, then the OSC1 and

OSC2 pins should be left floating.

OSC3 andOSC4 are connected to a 32768Hz crystal to

form a real time clock for timing purposes or to form a

system clock.

LCD power supply

and PFD respectively, the func

-

-

-

-

-

-

9

Page 19

A/D with LCD Type MCU

Pin Name I/O

VMAX

V1, V2, C1, C2 I

SEG0~SEG7 O

SEG8~SEG15 O

SEG16~SEG18 O

COM0~COM2

COM3/SEG19

RES I

VDD

VSS

Note 1. Each pin on Port A can be programmed through a configuration option to have a wake-up

function.

2. Individual pins can be selected to have a pull-high resistor.

Configuration

Option

¾¾

¾

SEG0~SEG7

CMOS Output

SEG8~SEG15

CMOS Output

¾

1/2, 1/3 or 1/4

O

¾¾

¾¾

Duty

¾

Description

IC maximum voltage, connect to VDD,V

LCD voltage pump

LCD driver outputs for LCD panel segments. A configu

ration option can select all pins to be used as segment

drivers or all pins to be used as CMOS outputs.

LCD driveroutputs for LCD panel segments. Configura

tion options can select each pin to be used as either a

segment driver or each pin to be used as a CMOS out

put.

LCD driver outputs for LCD panel segments

An LCD duty-cycle configuration option determines if

SEG19 is configured as a segment driver or as a com

mon output driver for the LCD panel. COM0~COM2 are

the LCD common outputs.

Schmitt Trigger reset input. Active low.

Positive power supply

Negative power supply, ground

LCD

or V1

-

-

-

-

10

Page 20

HT46R63/HT46C63

Pin Name I/O

PA0~PA7 I/O

PB0/AN0

PB1/AN1

PB2/AN2

PB3/AN3

PB4/AN4

PB5/AN5

PB6/AN6

PB7/AN7

PC0~PC7 I/O Pull-high

PD0/PWM0

PD1/PWM1

PD2/PWM2

PD3/PWM3

PD4/INT0

PD5/INT1

PD6/TMR

PD7

OSC1

OSC2

OSC3

OSC4

Configuration

Option

Pull-high

Wake-up

I/O Pull-high

Pull-high

I/O

I

O

I

O

PWM

Interrupt

Crystal or RC

¾

Chapter 1 Hardware Structure

Description

Bidirectional 8-bit input/output port. Each individual bit

on this port can be configured as a wake-up input by a

configuration option. Software instructions determine if

the pin is a CMOS output or Schmitt Trigger input. Con

figuration options determine whether the four pins

PA0~PA3 and PA4~PA7 have pull-high resistors. Indi

vidual pins cannot be selected to have pull-high resis

tors.

Bidirectional 8-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine whether

the four pins PB0~PB3 and PB4~PB7 have pull-high

resistors. Individual pins cannot be selected to have

pull-high resistors. PB is pin-shared with the A/D input

pins. The A/D inputs are selected via software instruc

tions. Once selected as an A/D input, the I/O function

and pull-high resistor functions are disabled automati

cally.

Bidirectional 8-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine whether

the four pins PC0~PC3 and PC4~PC7 have pull-high

resistors. Individual pins cannot be selected to have

pull-high resistors.

Bidirectional 8-bit input/output port. Software instructions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine whether

the four pins PD0~PD3 and PD4~PD7 have pull-high

resistors. Individual pins cannot be selected to have

pull-high resistors. PD0~PD3 are pin-shared with

PWM0~PWM3, the function of each pin is selected via

a configuration option. Pins PD4 and PD5 are

pin-shared with external interrupt input pins INT0

INT1

respectively. Configuration options determine the

interrupt enable/disable and the interrupt low/high trig

ger type. Pin PD6 is pin-shared with the external timer

input pin TMR.

OSC1 and OSC2 are connected to an external RC net

work or external crystal (determined by configuration

option) for the internal system clock. For external RC

system clock operation, OSC2 is an output pin for 1/4

system clock.

32768Hz crystal connections for RTC clock generation.

and

-

-

-

-

-

-

-

-

-

11

Page 21

A/D with LCD Type MCU

Pin Name I/O

CMPN I

CMPP I

CMPO O

CHGO O

AVDD

VLCD

SEG0~SEG6 O

SEG7~SEG10 O

SEG11~SEG14 O

SEG15~SEG18 O

COM0~COM2

COM3/SEG19

RES I

VDD

VSS

Configuration

Option

¾

¾

¾

¾

¾¾

¾¾

¾

SEG7~SEG10

CMOS Output

SEG11~SEG14

CMOS Output

SEG15~SEG18

CMOS Output

O 1/3 or 1/4 Duty

¾

¾¾

¾¾

Description

Negative input for comparator

Positive input for comparator

Comparator output

Comparator output with 32768Hz carrier

A/D converter reference voltage input. It should be ex

ternally connected to VDD.

LCD power supply

LCD driver outputs for LCD panel segments.

LCD driver outputs for LCD panel segments. A configu

ration option can select all pins to be used as segment

drivers or all pins to be used as CMOS outputs.

LCD driver outputs for LCD panel segments. A configu

ration option can select all pins to be used as segment

drivers or all pins to be used as CMOS outputs. If used

as CMOS outputs, these pins have a higher sink capa

bility than the SEG7~SEG10 CMOS outputs.

LCD driver outputs for LCD panel segments. A configu

ration option can select all pins to be used as segment

drivers or all pins to be used as CMOS outputs. If used

as CMOS outputs, these pins have a higher sink capa

bility than the SEG7~SEG10 CMOS outputs.

An LCD duty-cycle configuration option determines if

SEG19 is configured as a segment driver or as a common output driver for the LCD panel. COM0~COM2 are

the LCD common outputs.

Schmitt Trigger reset input. Active low.

Positive power supply

Negative power supply, ground

-

-

-

-

-

-

Note 1. Each pin on Port A can be programmed through a configuration option to have a wake-up

function.

2. Individual pins cannot beselected to have a pull-high resistor. Pull-high resistor configuration

options can only be selected in groups of four pins.

3. Pins PB4/AN4 ~ PB7/AN7 only exist on the 100-pin QFP package.

4. Pins PC4~PC7 only exist on the 100-pin QFP package.

5. Segment pins SEG15~SEG18 only exist on the 100-pin QFP package.

6. If the SEG11~SEG18 outputs are configured as CMOS outputs, note that their sink current

capacity is higher than the SEG7~SEG10 outputs.

12

Page 22

HT46R64/HT46C64

Pin Name I/O

PA0/BZ

PA1/BZ

PA2

PA3/PFD

PA4~PA7

PB0/AN0

PB1/AN1

PB2/AN2

PB3/AN3

PB4/AN4

PB5/AN5

PB6/AN6

PB7/AN7

PD0/PWM0

PD1/PWM1

PD2/PWM2

PD3/PWM3

PD4/INT0

PD5/INT1

PD6/TMR0

PD7/TMR1

OSC1

OSC2

OSC3

OSC4

VLCD

VMAX

Configuration

Option

Pull-high

Wake-up

I/O

I/O Pull-high

I/O

Buzzer

PFD

Pull-high

PWM

Interrupt

I

Crystal or RC

O

I

RTC or

O

System Clock

¾¾

¾¾

Chapter 1 Hardware Structure

Description

Bidirectional 8-bit input/output port. Each individual bit

on this port can be configured as a wake-up input by a

configuration option. Software instructions determine

if the pin is a CMOS output or Schmitt Trigger input.

Configuration optionsdetermine which pins on the port

have pull-high resistors. Pins PA0, PA1 and PA3 are

pin-shared with BZ, BZ

function of which is chosen via configuration options.

Bidirectional 8-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine which

pins on the port have pull-high resistors. PB is

pin-shared with the A/D input pins. The A/D inputs are

selected via software instructions. Once selected as

an A/D input, the I/O function and pull-high resistor

functions are disabled automatically.

Bidirectional 8-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine which

pins on the porthave pull-highresistors. PD0~PD3 are

pin-shared with PWM0~PWM3, the function of each

pin is selected via a configuration option. Pins PD4

and PD5 are pin-shared with external interrupt input

pins INT0

tions determinethe interrupt enable/disable and the interrupt low/high trigger type. Pins PD6 and PD7 are

pin-shared with the external timer input pins TMR0

and TMR1.

OSC1 andOSC2 are connected to an external RC network or external crystal (determined by configuration

option) for the internal system clock. For external RC

system clock operation, OSC2 is an output pin for 1/4

system clock. If an RTC oscillator on pins OSC3 and

OSC4 is used as a system clock, then the OSC1 and

OSC2 pins should be left floating.

OSC3 and OSC4 are connected to a 32768Hz crystal

to form a real time clock for timing purposes or to form

a system clock.

LCD power supply

IC maximum voltage, connect to VDD,V

and INT1 respectively. Configuration op-

and PFD respectively, the

or V1

LCD

-

-

13

Page 23

A/D with LCD Type MCU

Pin Name I/O

V1, V2, C1, C2 I

SEG0~SEG7 O

SEG8~SEG15 O

SEG16~SEG31 O

COM0~COM2

COM3/SEG32

RES I

VDD

VSS

Note 1. Each pin on Port A can be programmed through a configuration option to have a wake-up

function.

2. Individual pins can be selected to have a pull-high resistor.

3. Pins PB6/AN6 and PB7/AN7 only exist on the 100-pin QFP package.

4. Pin PD3/PWM3 only exists on the 100-pin QFP package.

5. Pin PD7/TMR1 only exists on the 100-pin QFP package. The 56-pin SSOP package has

only one external timer input TMR0.

6. Segment pins SEG0~SEG7 and SEG27~SEG31 only exist on the 100-pin QFP package.

Configuration

Option

¾

SEG0~SEG7

CMOS Output

SEG8~SEG15

CMOS Output

¾

1/2, 1/3 or 1/4

O

¾¾

¾¾

Duty

¾

Description

LCD voltage pump

LCD driver outputs for LCD panel segments. A config

uration option can select all pins to be used as seg

ment drivers or all pins to be used as CMOS outputs.

LCD driver outputs for LCD panel segments. Configu

ration options can select each pin to be used as either

a segment driver or each pin to be used as a CMOS

output.

LCD driver outputs for LCD panel segments

An LCD duty-cycle configuration option determines if

SEG32 is configured as a segment driver or as a com

mon output driver for the LCD panel. COM0~COM2

are the LCD common outputs.

Schmitt Trigger reset input. Active low.

Positive power supply

Negative power supply, ground

-

-

-

-

14

Page 24

HT46R65/HT46C65

Pin Name I/O

PA0/BZ

PA1/BZ

PA2

PA3/PFD

PA4~PA7

PB0/AN0

PB1/AN1

PB2/AN2

PB3/AN3

PB4/AN4

PB5/AN5

PB6/AN6

PB7/AN7

PD0/PWM0

PD1/PWM1

PD2/PWM2

PD3/PWM3

PD4/INT0

PD5/INT1

PD6/TMR0

PD7/TMR1

OSC1

OSC2

OSC3

OSC4

VLCD

VMAX

Configuration

Option

Pull-high

Wake-up

I/O

I/O Pull-high

I/O

¾¾

¾¾

I

Crystal or RC

O

I

O

System Clock

Buzzer

PFD

Pull-high

PWM

Interrupt

RTC or

Chapter 1 Hardware Structure

Description

Bidirectional 8-bit input/output port. Each individual bit

on this port can be configured as a wake-up input by a

configuration option. Software instructions determine

if the pin is a CMOS output or Schmitt Trigger input.

Configuration options determine which pins on the

port have pull-high resistors. Pins PA0, PA1 and PA3

are pin-shared with BZ, BZ

function of which is chosen via configuration options.

Bidirectional 8-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine which

pins on the port have pull-high resistors. PB is

pin-shared with the A/D input pins. The A/D inputs are

selected via software instructions. Once selected as

an A/D input, the I/O function and pull-high resistor

functions are disabled automatically.

Bidirectional 8-bit input/output port. Software instruc

tions determine if the pin is a CMOS output or Schmitt

Trigger input. Configuration options determine which

pins on the port have pull-high resistors. PD0~PD3

are pin-shared with PWM0~PWM3, the function of

each pin is selected via a configuration option. Pins

PD4 andPD5 are pin-shared with external interrupt input pins INT0

options determinethe interrupt enable/disable and the

interrupt low/high trigger type. Pins PD6 and PD7 are

pin-shared with the external timer input pins TMR0

and TMR1 respectively.

OSC1 and OSC2 are connected to an external RC

network or external crystal (determined by configura

tion option) for the internal system clock. For external

RC system clock operation, OSC2 is an output pin for

1/4 system clock. If an RTC oscillator on pins OSC3

and OSC4 is used as a system clock, then the OSC1

and OSC2 pins should be left floating.

OSC3 and OSC4 are connected to a 32768Hz crystal

to form a real time clock for timing purposes or to form

a system clock.

LCD power supply

IC maximum voltage, connect to VDD,V

and INT1 respectively. Configuration

and PFD respectively, the

or V1

LCD

-

-

-

15

Page 25

A/D with LCD Type MCU

Pin Name I/O

V1, V2, C1, C2 I

SEG0~SEG7 O

SEG8~SEG15 O

SEG16~SEG23 O

SEG24~SEG39 O

COM0~COM2

COM3/SEG40

RES I

VDD

VSS

Configuration

Option

¾

SEG0~SEG7

CMOS output

SEG8~SEG15

CMOS output

SEG16~SEG23

CMOS output

¾

1/2, 1/3 or 1/4

O

¾¾

¾¾

Duty

¾

Description

LCD voltage pump

LCD driver outputs for LCD panel segments. A config

uration option can select all pins to be used as seg

ment driversor all pins to be used asCMOS outputs.

LCD driver outputs for LCD panel segments. A config

uration option can select all pins to be used as seg

ment driversor all pins to be used asCMOS outputs.

LCD driver outputs for LCD panel segments. Configu

ration options can select each pin to be used as either

a segment driver or each pin to be used as a CMOS

output.

LCD driver outputs for LCD panel segments

An LCD duty-cycle configuration option determines if

SEG40 is configured as a segment driver or as a com

mon output driver for the LCD panel. COM0~COM2

are the LCD common outputs.

Schmitt Trigger reset input. Active low.

Positive power supply

Negative power supply, ground

-

-

-

-

-

-

Note 1. Each pin on Port A can be programmed through a configuration option to have a wake-up

function.

2. Individual pins can be selected to have a pull-high resistor.

3. Pins PB6/AN6 and PB7/AN7 only exist on the 100-pin QFP package.

4. Pin PD3/PWM3 only exists on the 100-pin QFP package.

5. Pin PD7/TMR1 only exists on the 100-pin QFP package. The 56-pin SSOP package has

only one external timer input TMR0.

6. Segment pins SEG0~SEG15 and SEG35~SEG39 only exist on the 100-pin QFP package.

16

Page 26

Absolute Maximum Ratings

Supply Voltage.............................................................................................VSS-0.3V to VSS+6.0V

Input Voltage ...............................................................................................V

Storage Temperature.............................................................................................-50°Cto125°C

Operating Temperature............................................................................................-40°Cto85°C

These are stress ratings only. Stresses exceeding the range specified under Absolute Maximum

Ratings may cause substantial damage to the device. Functional operation of this device at other

conditions beyond those listed in the specification is not implied and prolonged exposure to ex

treme conditions may affect device reliability.

D.C. Characteristics

Chapter 1 Hardware Structure

-0.3V to VDD+0.3V

SS

-

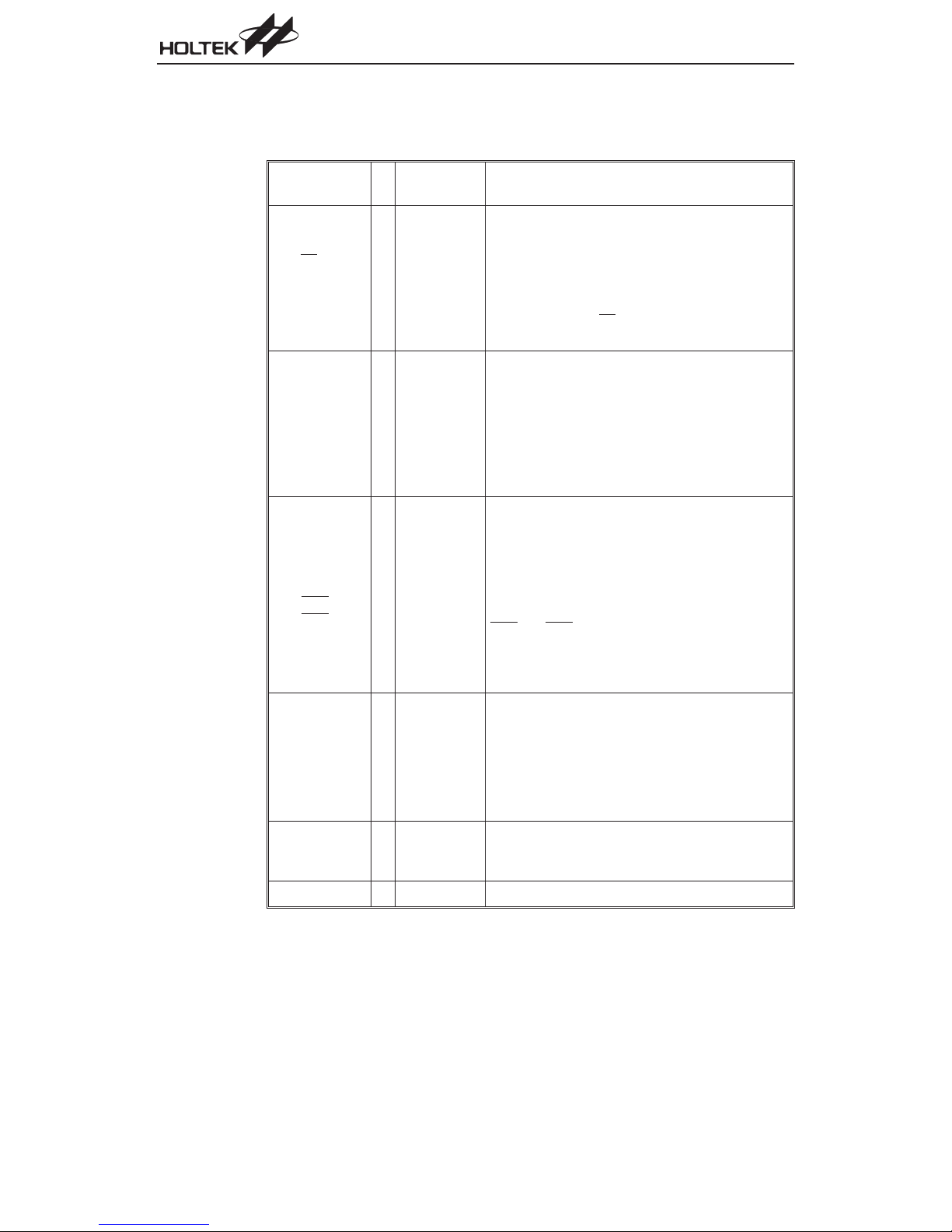

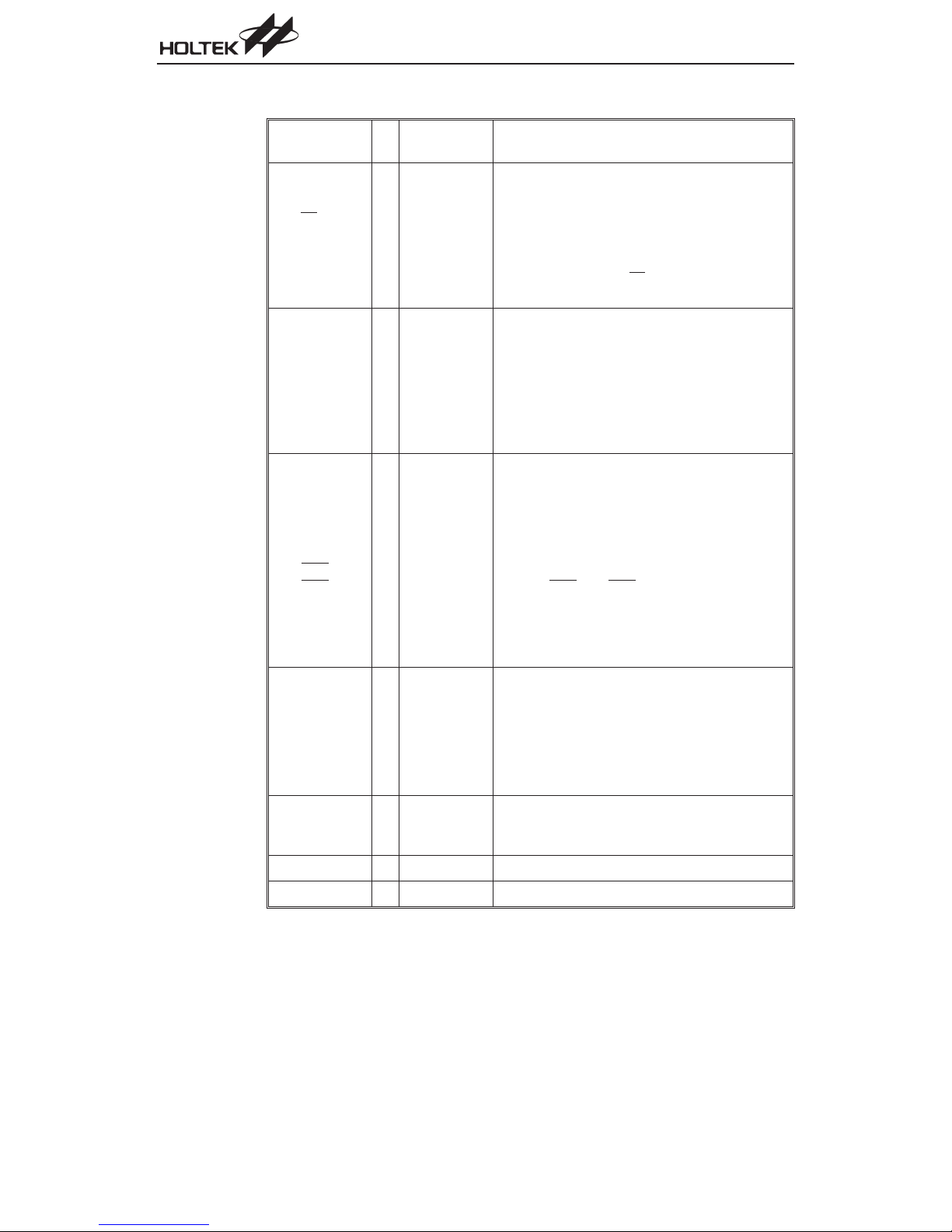

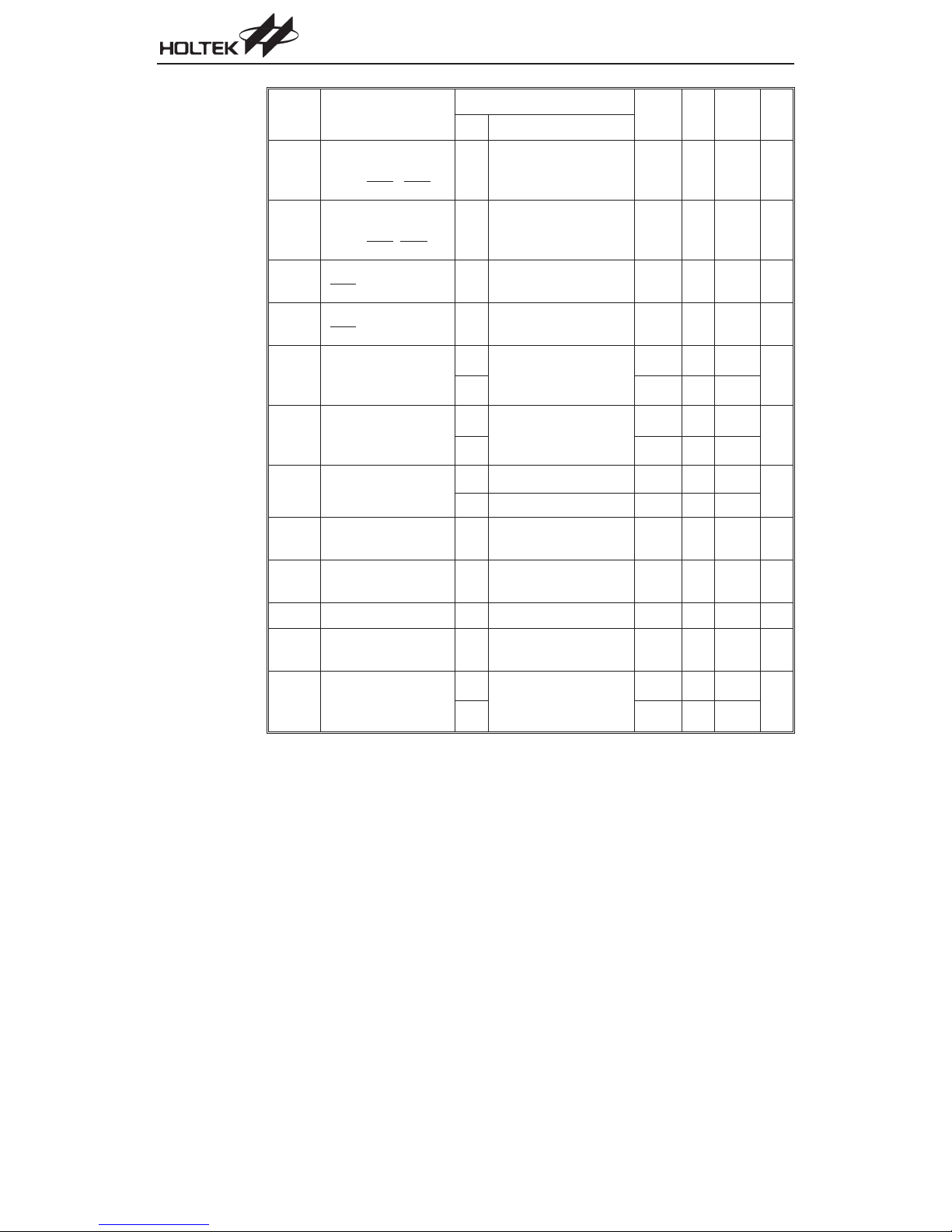

For HT46R63/HT46C63

Symbol Parameter

V

V

I

DD1

I

DD2

I

DD3

I

STB1

I

STB2

I

STB3

Operating Voltage

DD

LCD Highest Voltage

LCD

Operating Current (RC OSC,

Analog Circuit Disabled)

Operating Current (RC OSC)

Operating Current

(Crystal OSC, RC OSC)

Standby Current (WDT OSC On,

RTC Off, LCD Off)

Standby Current (WDT OSC Off,

RTC Off, LCD Off)

Standby Current (WDT OSC Off,

RTC On, LCD Off)

Standby Current (WDT OSC Off,

I

STB4

RTC On,LCD On with Low Current

Internal R Type Bias Option)

Standby Current (WDT OSC Off,

I

STB5

RTC On, LCD On with Middle Current Internal R Type Bias Option)

Test Conditions

Conditions

V

DD

¾

f

=4MHz 2.2

SYS

¾

f

=8MHz 3.3

SYS

¾¾

3V

No load,

f

=4MHz

SYS

5V

3V

No load,

f

=4MHz

SYS

5V

No load,

5V

f

=8MHz

SYS

3V

No load,

System HALT

5V

3V

System HALT

5V

3V

System HALT

5V

3V

System HALT

V

LCD=VDD

5V

3V

System HALT

V

LCD=VDD

5V

Ta=25°C

Min. Typ. Max. Unit

¾

5.5 V

¾

5.5 V

¾

0

¾

¾

¾

¾

¾

¾¾

¾¾

¾¾

¾¾

¾¾

¾¾

V

12

DD

V

mA

35

12

mA

35

48mA

5

mA

15

1

mA

1

5

mA

20

10 12 16

mA

20 24 32

16 20 26

mA

32 40 52

17

Page 27

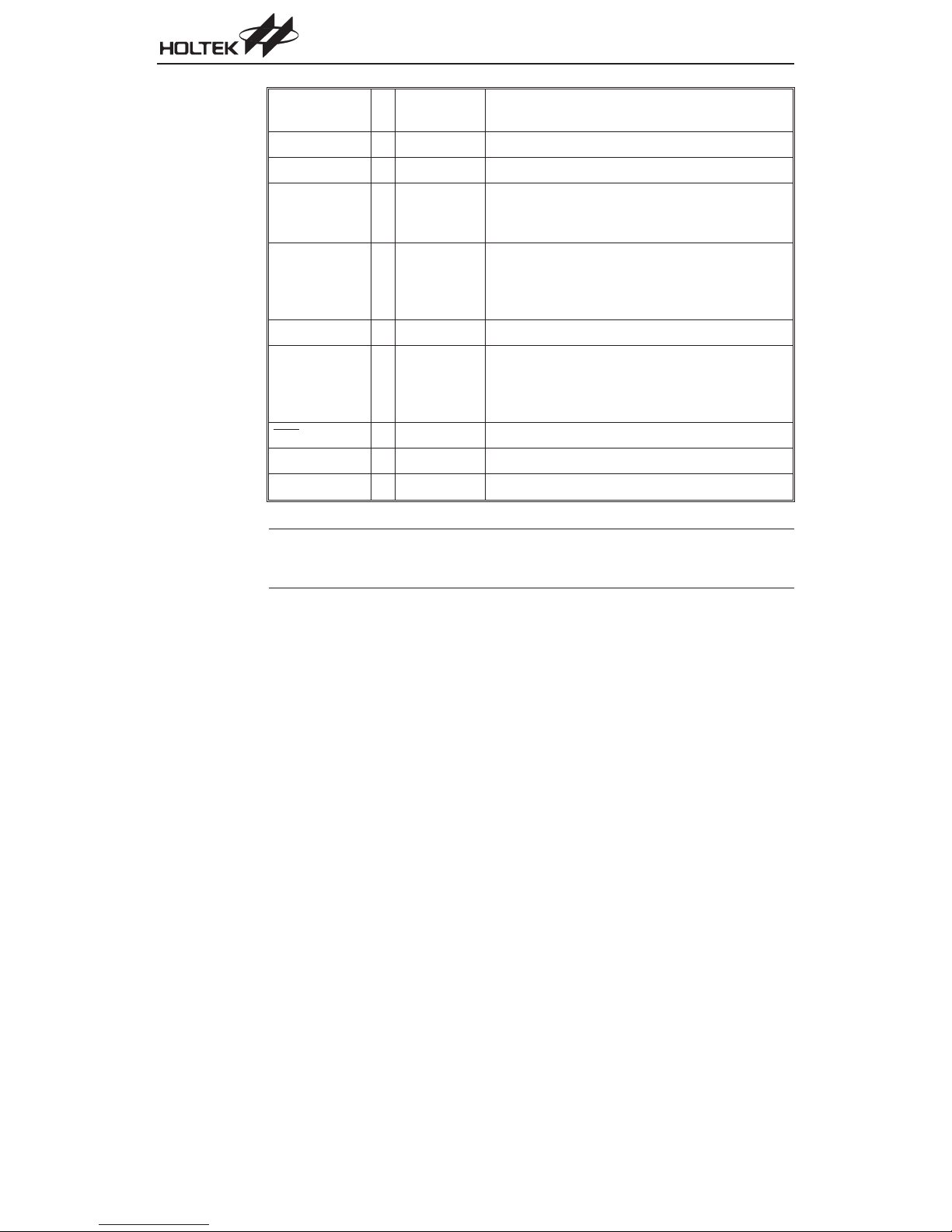

A/D with LCD Type MCU

Symbol Parameter

Standby Current (WDT OSC Off,

I

STB6

RTC On,LCD On with High Current

Internal R Type Bias Option)

V

V

V

V

I

OL1

I

OH1

I

OL2

I

OH2

I

OL3

I

OLTOTAL

I

OHTOTAL

R

V

V

V

E

I

ADC

Input Low Voltage for I/O Ports

IL1

Input High Voltage for I/O Ports

IH1

Input Low Voltage (RES)

IL2

Input High Voltage (RES)

IH2

I/O Port Sink Current

I/O Port Source Current

SEG7~SEG10 Logical Sink

Current

SEG7~SEG18 Logical Source

Current

SEG11~SEG18 Logical Sink

Current

I/O Port Total Sink Current

I/O Port Total Source Current

Pull-high Resistance

PH

Comparator Input Offset Voltage

OS

Comparator Input Voltage Range

1

A/D Input Voltage

AD

A/D Conversion Integral

AD

Nonlinearity Error

Additional Power Consumption

if A/D Converter is used

Test Conditions

Min. Typ. Max. Unit

V

Conditions

DD

3V

System HALT

V

LCD=VDD

5V 76 104 136

V

V

V

V

V

OL

OH

OL

OH

OL

¾

¾

¾

¾

=0.1V

=0.9V

=0.1V

=0.9V

=0.1V

DD

DD

DD

DD

DD

¾

¾

¾

¾

3V

5V 10 25

3V

5V

3V

5V 16

3V

5V

3V

5V 32

¾¾ ¾¾

38 52 68

¾

0

0.7V

0.9V

¾

DD

¾

0

¾

DD

612

-2 -4

-5 -8

¾¾

8

¾¾

-2 -4 ¾

-4 -8 ¾

¾¾

16

¾¾

0.3V

V

0.4V

V

100 mA

¾¾ ¾¾-100

3V

5V

¾

¾

¾

¾

3V

5V

¾

¾

¾

¾

¾

¾¾

¾

20 60 100

10 30 50

-10 ¾

0.2

¾ V

DD

¾

0

V

±0.5 ±1

¾

0.5 1

¾

1.5 3

10 mV

DD

DD

DD

DD

¾

¾

¾

¾

- 0.8

DD

mA

V

V

V

V

mA

mA

mA

mA

mA

mA

kW

V

V

LSB

mA

18

Page 28

Chapter 1 Hardware Structure

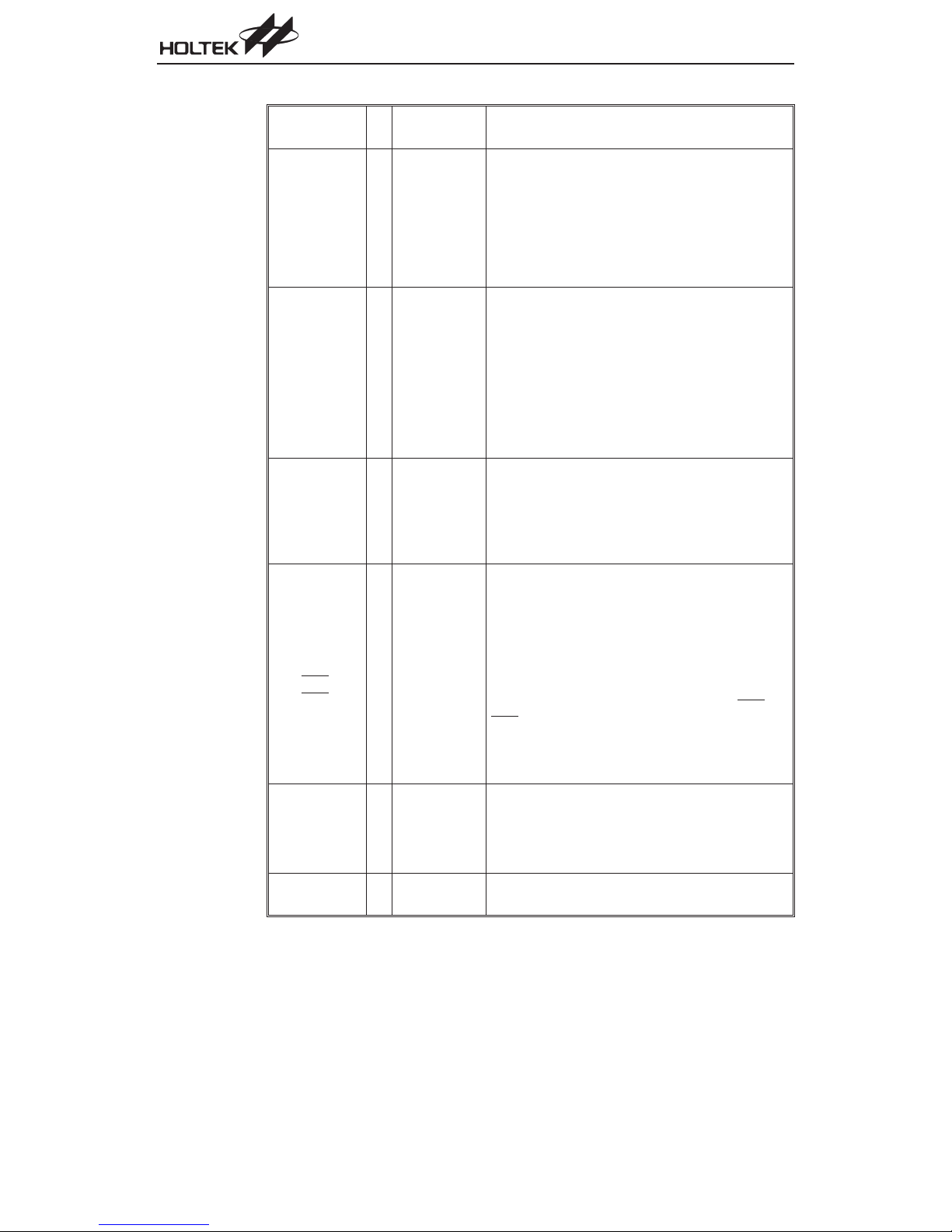

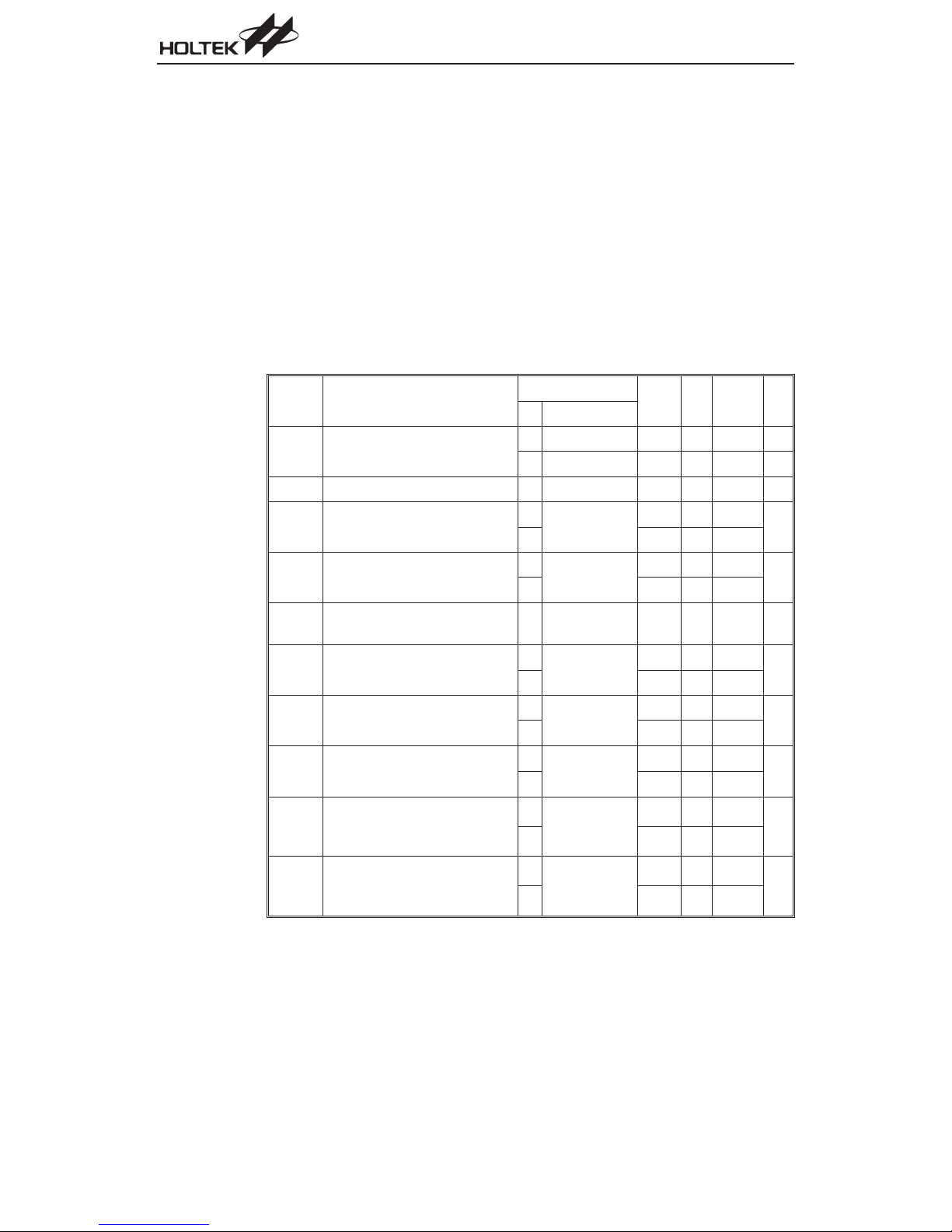

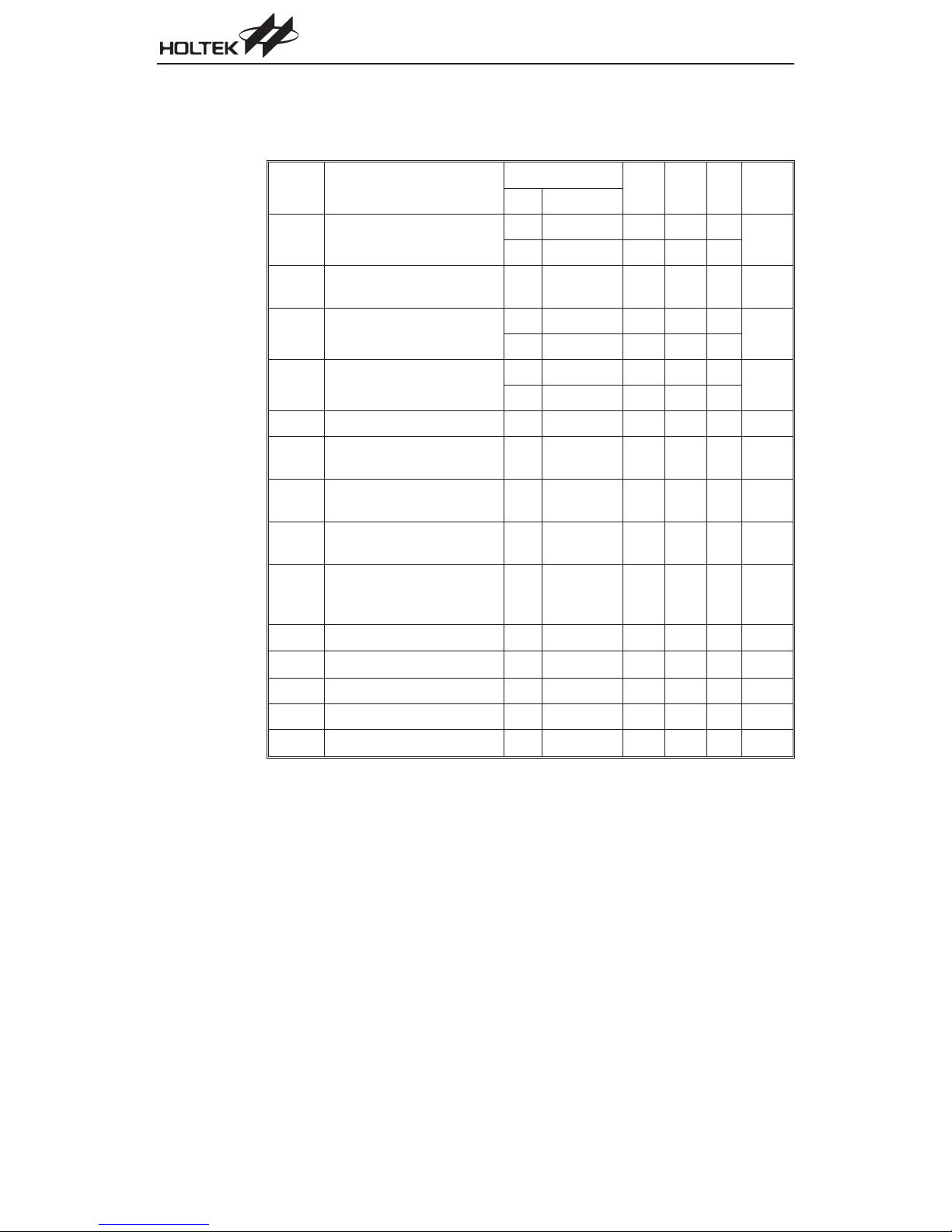

For HT46R62/HT46C62, HT46R64/HT46C64, HT46R65/HT46C65

Test Conditions

Symbol Parameter

V

DD

I

DD1

I

DD2

I

DD3

I

DD4

I

STB1

I

STB2

I

STB3

I

STB4

I

STB5

I

STB6

I

STB7

Operating Voltage

Operating Current

(Crystal OSC)

Operating Current

(RC OSC)

Operating Current

(Crystal OSC, RC OSC)

Operating Current

(f

=32768Hz)

SYS

Standby Current

(f

=T1)

S

Standby Current

(f

=32768Hz OSC)

S

Standby Current

(f

=WDT RC OSC)

S

Standby Current

(f

=32768Hz OSC)

S

Standby Current

(f

=32768Hz OSC)

S

Standby Current

(f

=WDT RC OSC)

S

Standby Current

(f

=WDT RC OSC)

S

V

DD

¾

¾

3V

5V

3V

5V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

Conditions

f

=4MHz 2.2

SYS

=8MHz 3.3

f

SYS

No load, f

SYS

=4MHz

ADC Off

No load, f

SYS

=4MHz

ADC Off

No load, f

SYS

=8MHz

ADC Off

No load, ADC Off

No load, system HALT

LCD Off

No load, system HALT

LCD On, C type

No load, system HALT

LCD On, C type

No load, system HALT,

LCD On,R type, 1/2 bias,

V

LCD=VDD

(Low bias current option)

No load, system HALT,

LCD On,R type, 1/3 bias,

V

LCD=VDD

(Low bias current option)

No load, system HALT,

LCD On,R type, 1/2 bias,

V

LCD=VDD

(Low bias current option)

No load, system HALT,

LCD On,R type, 1/3 bias,

V

LCD=VDD

(Low bias current option)

Ta=25°C

Min. Typ. Max. Unit

¾

5.5 V

¾

5.5 V

¾

12

¾

35

¾

12

¾

35

¾

48mA

¾

0.3 0.6

¾

0.6 1

¾¾

¾¾

¾

2.5 5

¾

10 20

¾

25

¾

610

¾

17 30

mA

mA

mA

1

mA

2

mA

mA

mA

¾

34 60

¾

13 25

mA

¾

28 50

¾

14 25

mA

¾

26 50

¾

10 20

mA

¾

19 40

19

Page 29

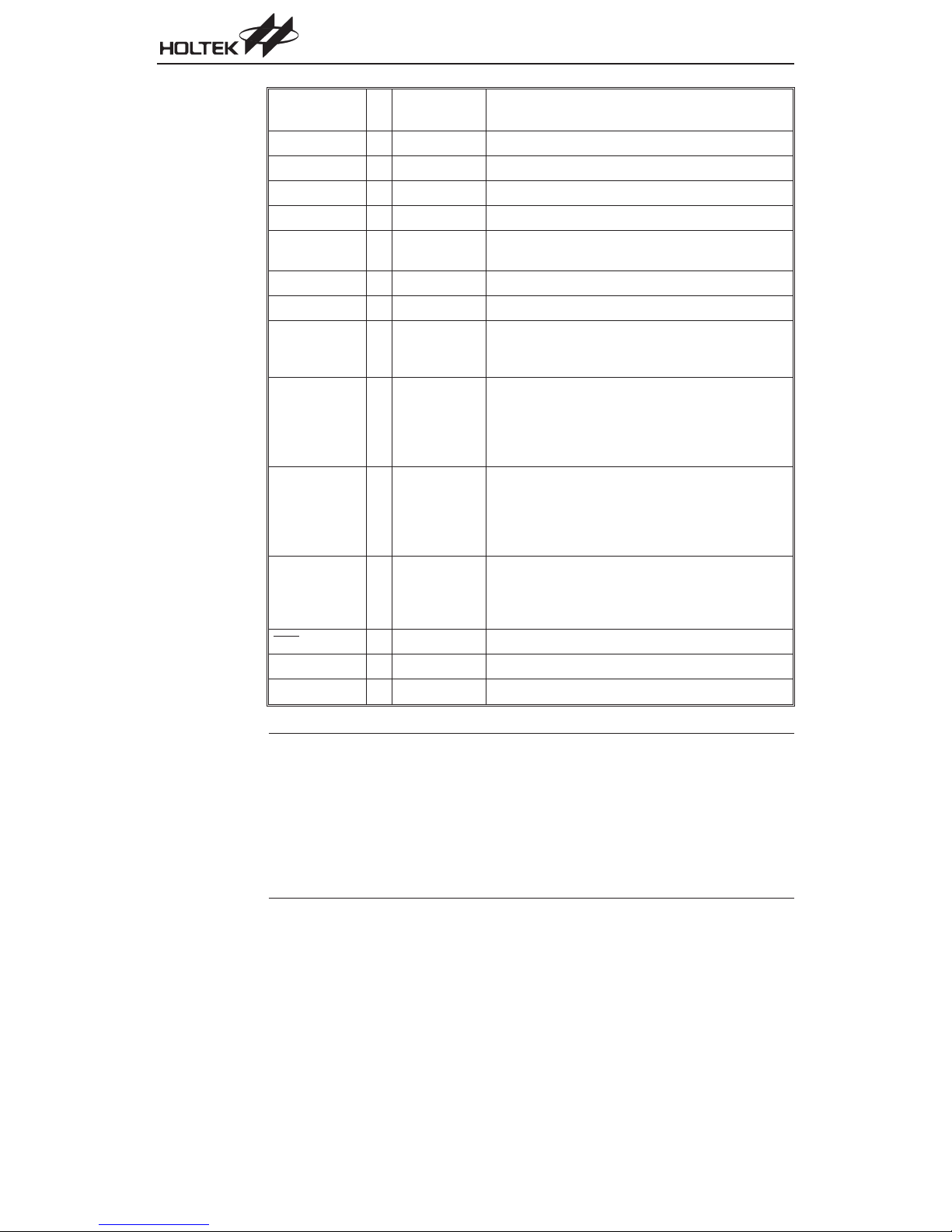

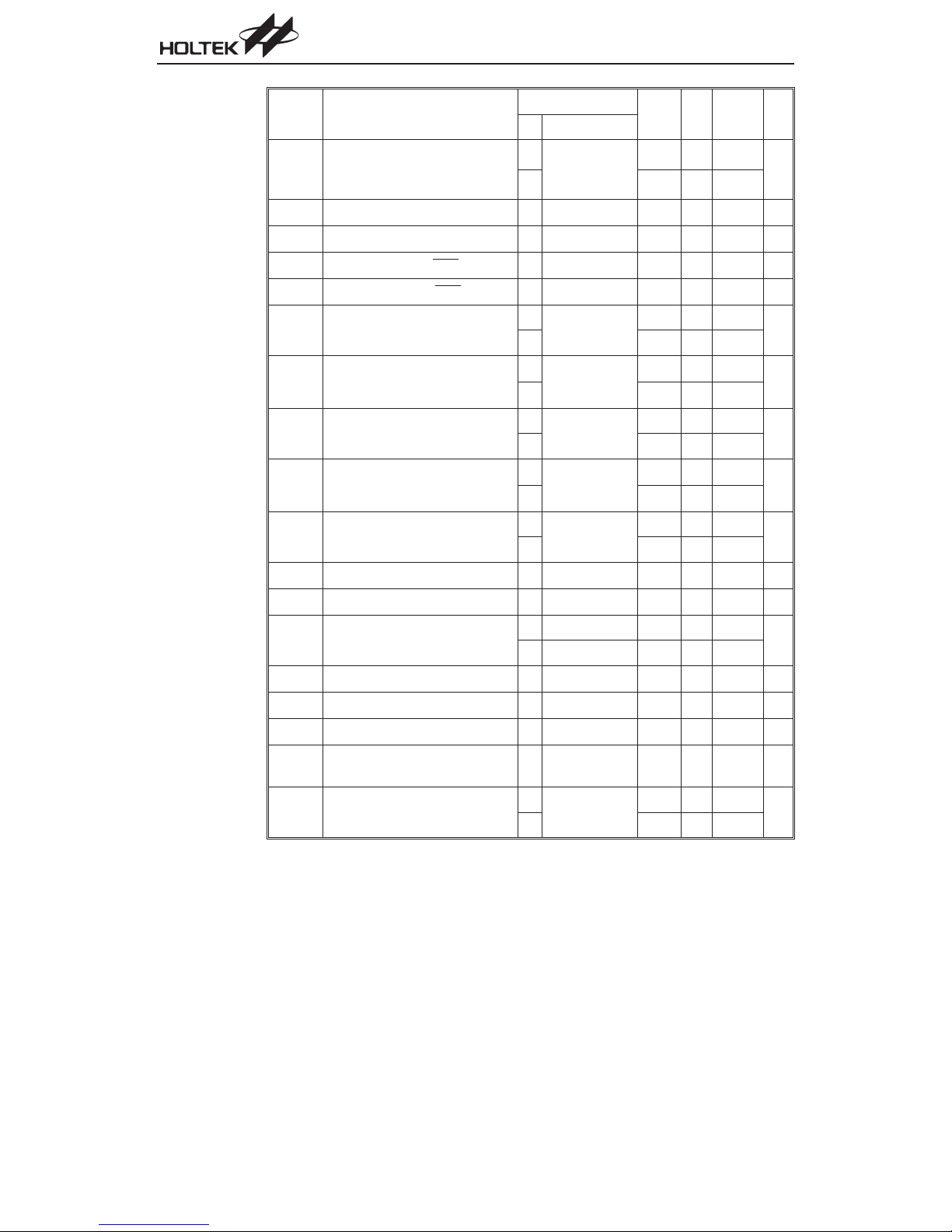

A/D with LCD Type MCU

Symbol Parameter

Input Low Voltage for

V

I/O Ports, TMR, TMR0

IL1

TMR1, INT0

, INT1

Input High Voltage for

V

V

V

I/O Ports, TMR, TMR0

IH1

TMR1, INT0

Input Low Voltage

IL2

(RES

Input High Voltage

IH2

(RES

, INT1

)

)

I/O Port Segment

I

OL

Logic Output Sink

Current

I/O Port Segment

I

OH

Logic Output Source

Current

R

V

V

V

E

Pull-high Resistance

PH

Low Voltage Reset

LVR

Voltage

Low Voltage Detector

LVD

Voltage

A/D Input Voltage

AD

A/D Conversion Inte-

AD

gral Nonlinearity Error

Additional Power

I

ADC

Consumption if A/D

Converter is used

Test Conditions

Min. Typ. Max. Unit

V

DD

¾¾

¾¾

¾¾

¾¾

3V

V

OL

Conditions

=0.1V

DD

0

0.7V

DD

0

0.9V

DD

612

¾

0.3V

¾

¾

0.4V

¾

5V 10 25

3V

V

=0.9V

OH

DD

5V

3V

5V

¾

¾

¾¾

¾¾

¾¾

¾¾ ¾

3V

-2 -4

-5 -8

20 60 100

10 30 50

2.7 3.0 3.3 V

3.0 3.3 3.6 V

¾

0

±0.5 ±1

¾

0.5 1

¾

5V

¾

1.5 3

V

DD

V

V

DD

V

DD

V

V

DD

¾

mA

¾

¾

mA

¾

kW

V

V

DD

LSB

mA

20

Page 30

A.C. Characteristics