HT46R23/HT46C23

A/D

型八位单片机

盛群知识产权政策

专利权

盛群半导体公司在全球各地区已核准和申请中之专利权至少有 160 件以上,享有绝对之合法权益。与盛群

公司 MCU 或其它产品有关的专利权并未被同意授权使用,任何经由不当手段侵害盛群公司专利权之公司、

组织或个人,盛群将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨盛群公司因侵权行为

所受之损失、或侵权者所得之不法利益。

商标权

盛群之名称和标识、Holtek 标识、HT-IDE、HT-ICE、Marvel Speech、 Music Micro、 Adlib Micro、 Magic

Vo i c e 、 Green Dialer、 PagerPro、 Q-Voice、 Turbo Voice、 EasyVoice 和 HandyWriter 都是盛群半导体公

司在台湾地区和其它国家的注册商标。

著作权

Copyright 2004 by HOLTEK SEMICONDUCTOR INC.

规格书中所出现的信息在出版当时相信是正确的,然而盛群对于规格内容的使用不负责任。文中提到的应

用其目的仅仅是用来做说明,盛群不保证或不表示这些应用没有更深入的修改就能适用,也不推荐它的产

品使用在会由于故障或其它原因可能会对人身造成危害的地方。盛群产品不授权使用于救生、维生器件或

系统中做为关键器件。盛群拥有不事先通知而修改产品的权利,对于最新的信息,请参考我们的网址

http://www.holtek.com.tw; http://www.holtek.com.cn

Rev. 1.70 1 2004-09-21

特性

• 工作电压:

=4MHz:2.2V~5.5V

f

SYS

f

=8MHz:3.3V~5.5V

SYS

• 最多可有 23 个双向输入/输出口

• 1 个与输入/输出口共用引脚的外部中断输入

• 16 位可编程定时/计数器,具有溢出中断和 7

级预分频器

• 内置晶体和 RC 振荡电路

• 看门狗定时器

• 4096×15 程序存储器 ROM

• 192×8 数据存储器 RAM

• 具有 PFD 功能,可用于发声

• HALT 和唤醒功能可降低功耗

HT46R23/HT46C23

• 在 V

为 0.5µs

• 8 层硬件堆栈

• 8 通道 10 位解析度的 A/D 转换器

• 2 通道 8 位的 PWM 输出,与输入/输出口共用

引脚

• 位操作指令

• 查表指令,表格内容字长 15 位

• 63 条指令

• 指令执行时间为 1 或 2 个指令周期

• 低电压复位功能

• I

• 24/28-pinSKDIP/SOP 封装

=5V,系统频率为 8MHz 时,指令周期

DD

2

C 总线(slave 模式)

概述

HT46R23/HT46C23 是 8 位高性能精简指令集单片机,专门为需要 A/D 转换的产品而设计,例如传感

器信号输入。掩膜版本 HT46C23 与 OTP 版本 HT46R23 引脚和功能完全相同。低功耗、I/O 使用灵活、可

编程分频器、计数器、振荡类型选择、多通道 A/D 转换、脉冲测量功能、I

这款单片机可以广泛应用于传感器的 A/D 转换、马达控制、工业控制、消费类产品等系统中。

2

I

C 为 Philips Semiconductors 的商标

2

C 通信、暂停和唤醒功能,使

Rev. 1.70 2 2004-09-21

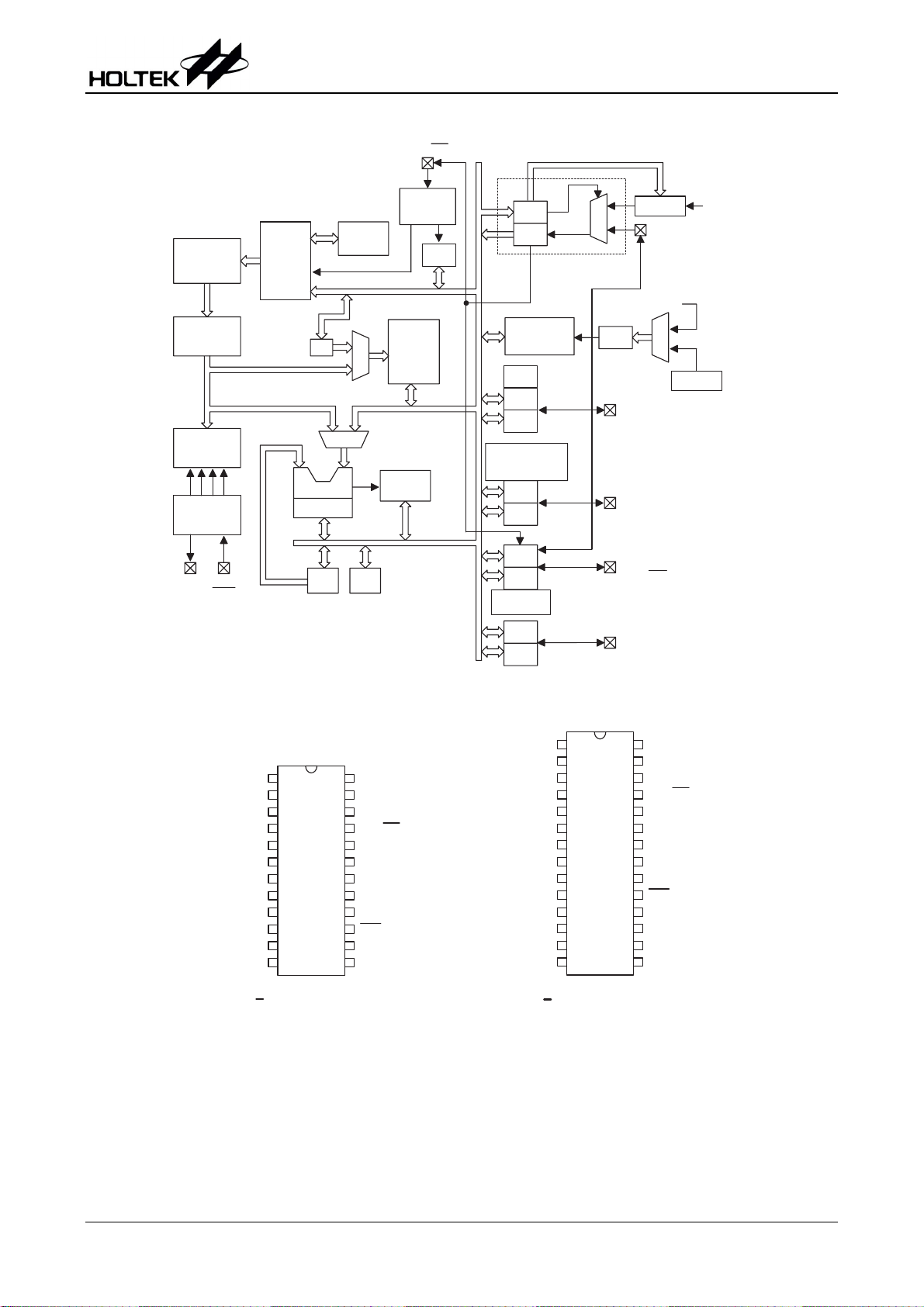

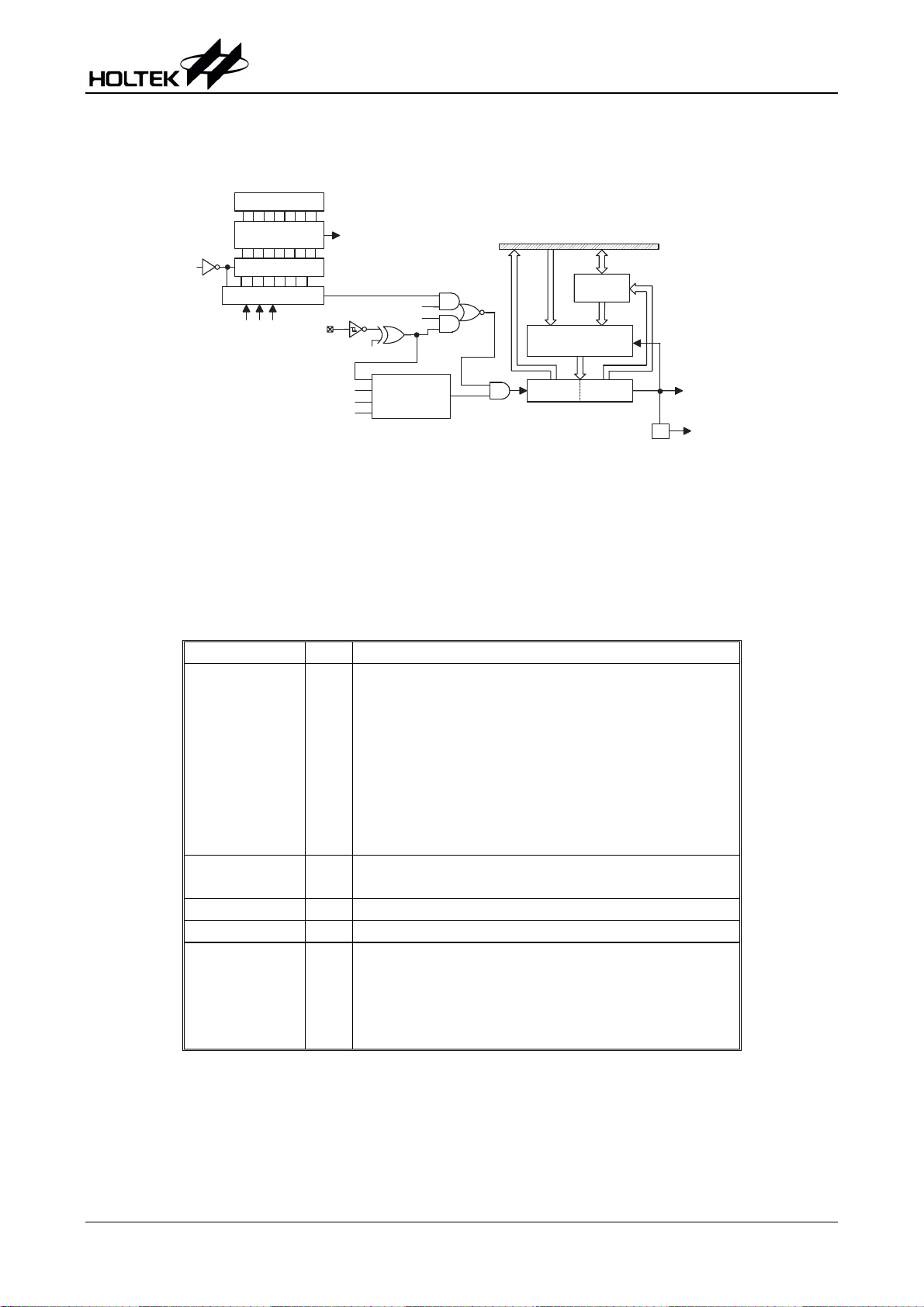

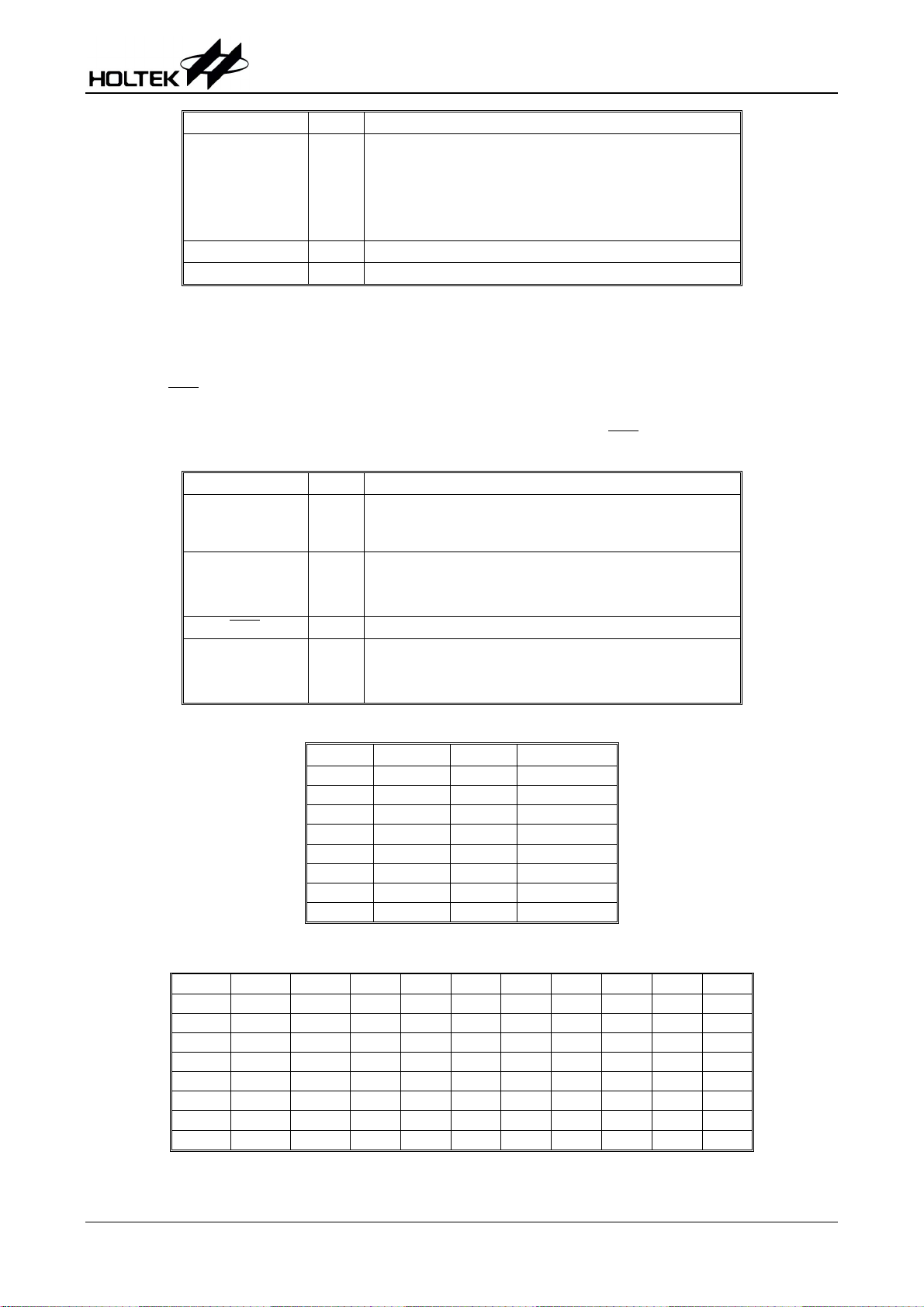

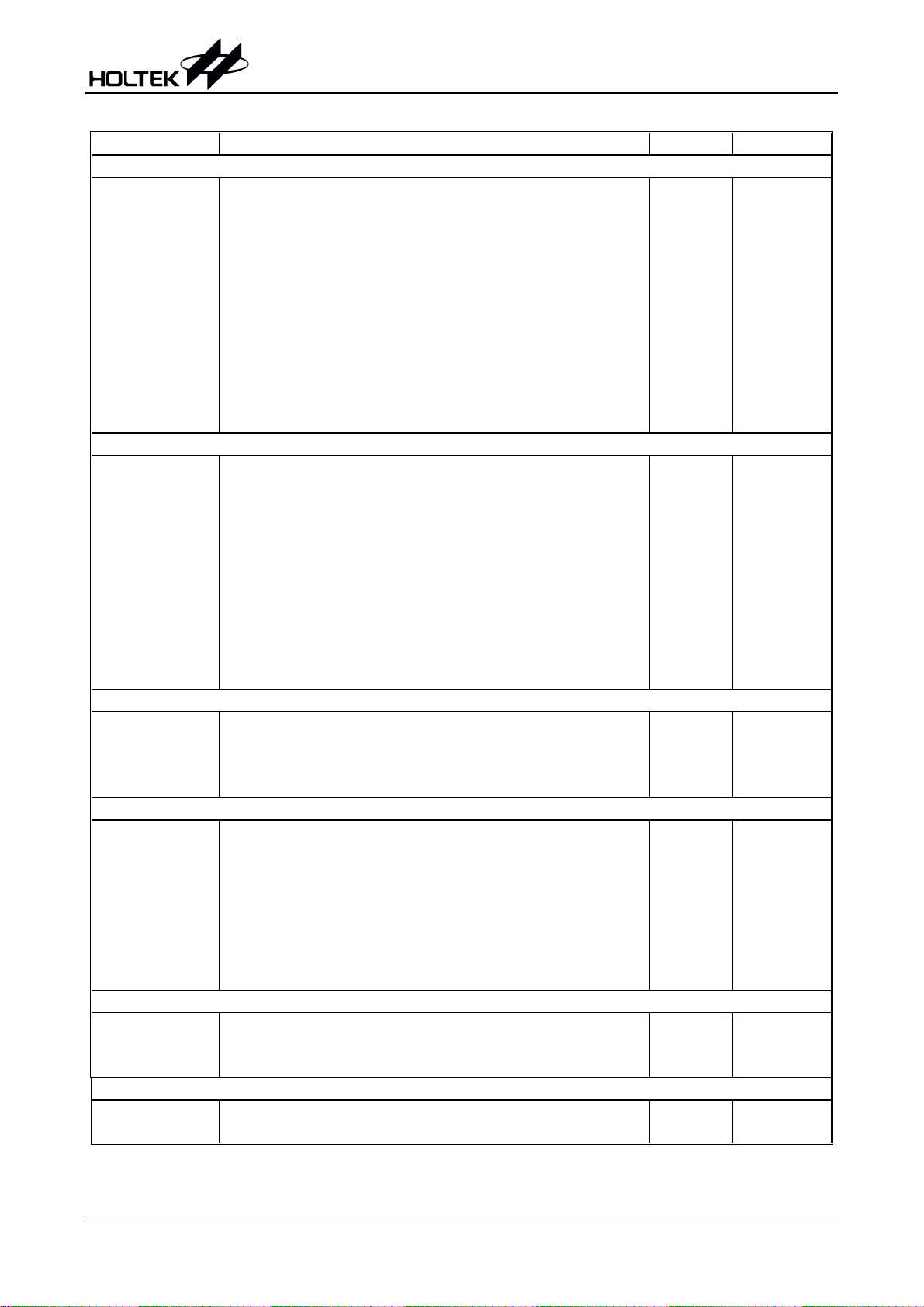

方框图

HT46R23/HT46C23

P A 5 / I N T

P r o g r a m

R O M

I n s t r u c t i o n

R e g i s t e r

I n s t r u c t i o n

D e c o d e r

T i m i n g

G e n e r a t o r

O S C 2 O S C 1

R E S

V D D

V S S

P r o g r a m

C o u n t e r

M P

A L U

S h i f t e r

A C C

M U X

S T A C K

M

U

X

L V R

D A T A

M e m o r y

S T A T U S

I n t e r r u p t

C i r c u i t

I N T C

P A 3 , P A 5

T M R C

T M R

P A 3 / P F D

W D T

P r e s c a l e r

P W M

P D C

P D

8 - C h a n n e l

A / D C o n v e r t e r

P B C

P B

P A C

P A

I2C B u s

S l a v e M o d e

P C

P C C

P o r t D

P o r t B

P o r t A

P o r t C

P r e s c a l e r f

M

U

X

P A 4 / T M R

P A 4

f

/ 4

S Y S

M

W D T

U

X

R C O S C

P D 0 / P W M 0 ~ P D 1 / P W M 1

P B 0 / A N 0 ~ P B 7 / A N 7

P A 0 ~ P A 2

P A 3 / P F D

P A 4 / T M R

P A 5 / I N T

P A 6 / S D A

P A 7 / S C L

P C 0 ~ P C 4

S Y S

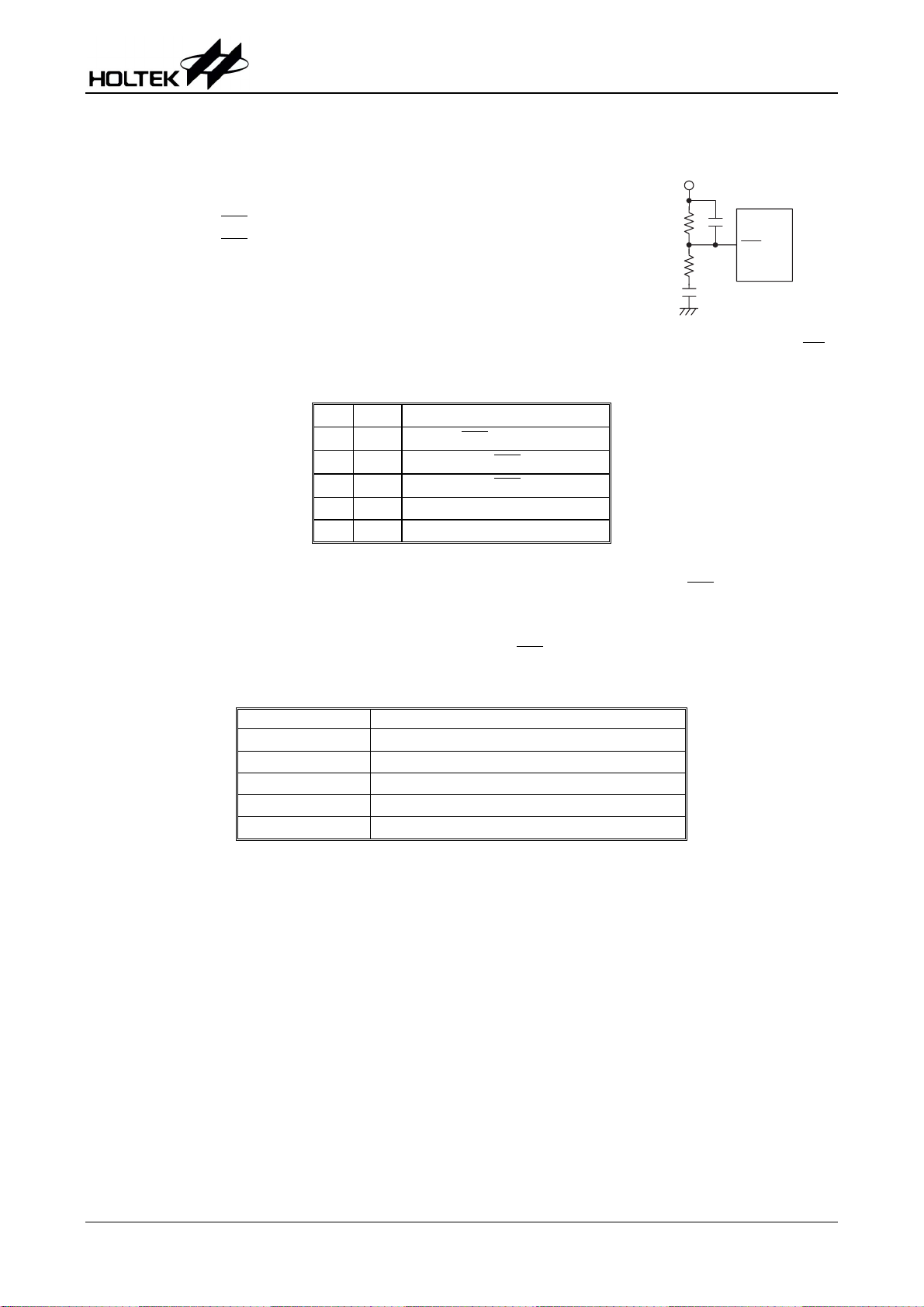

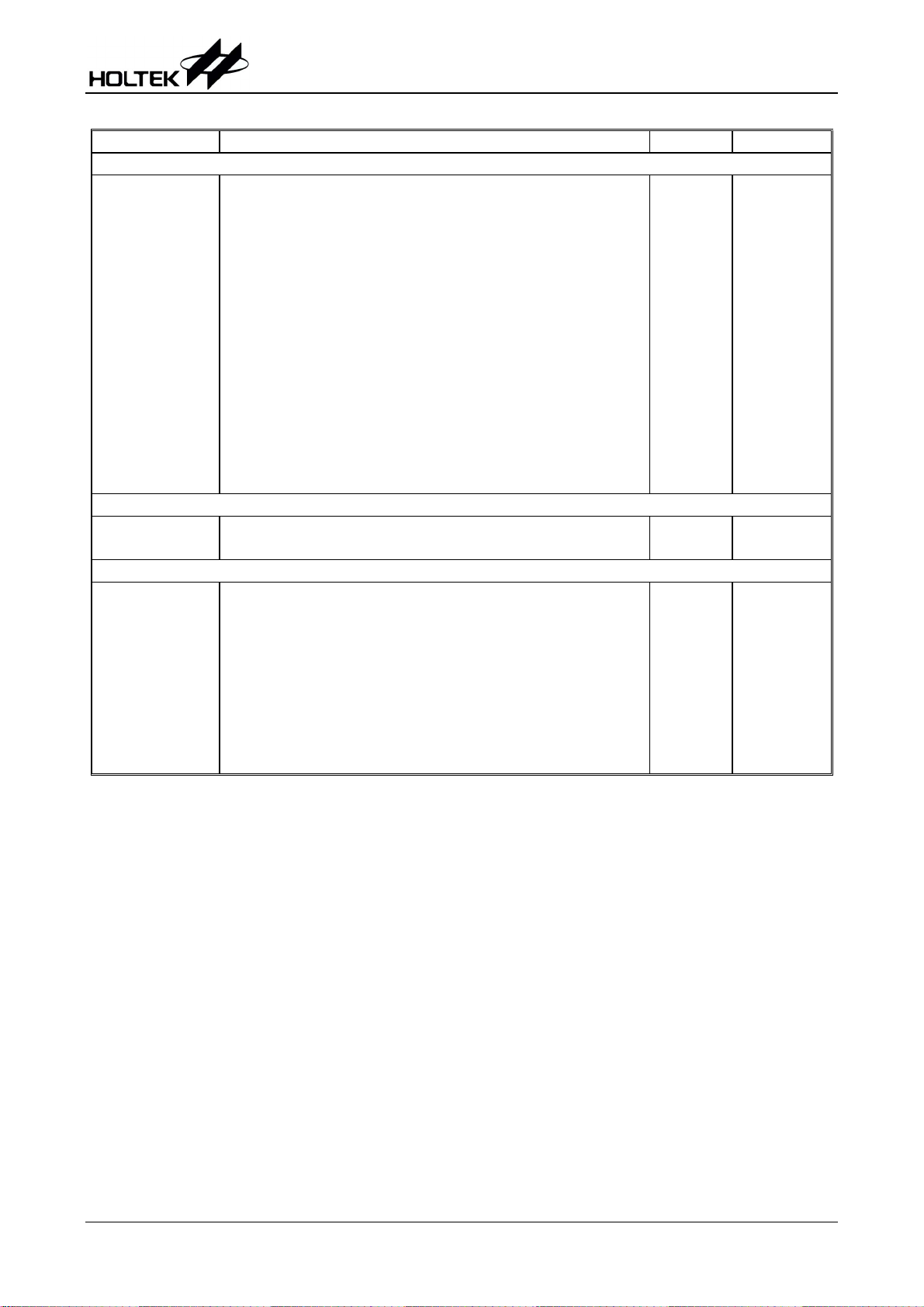

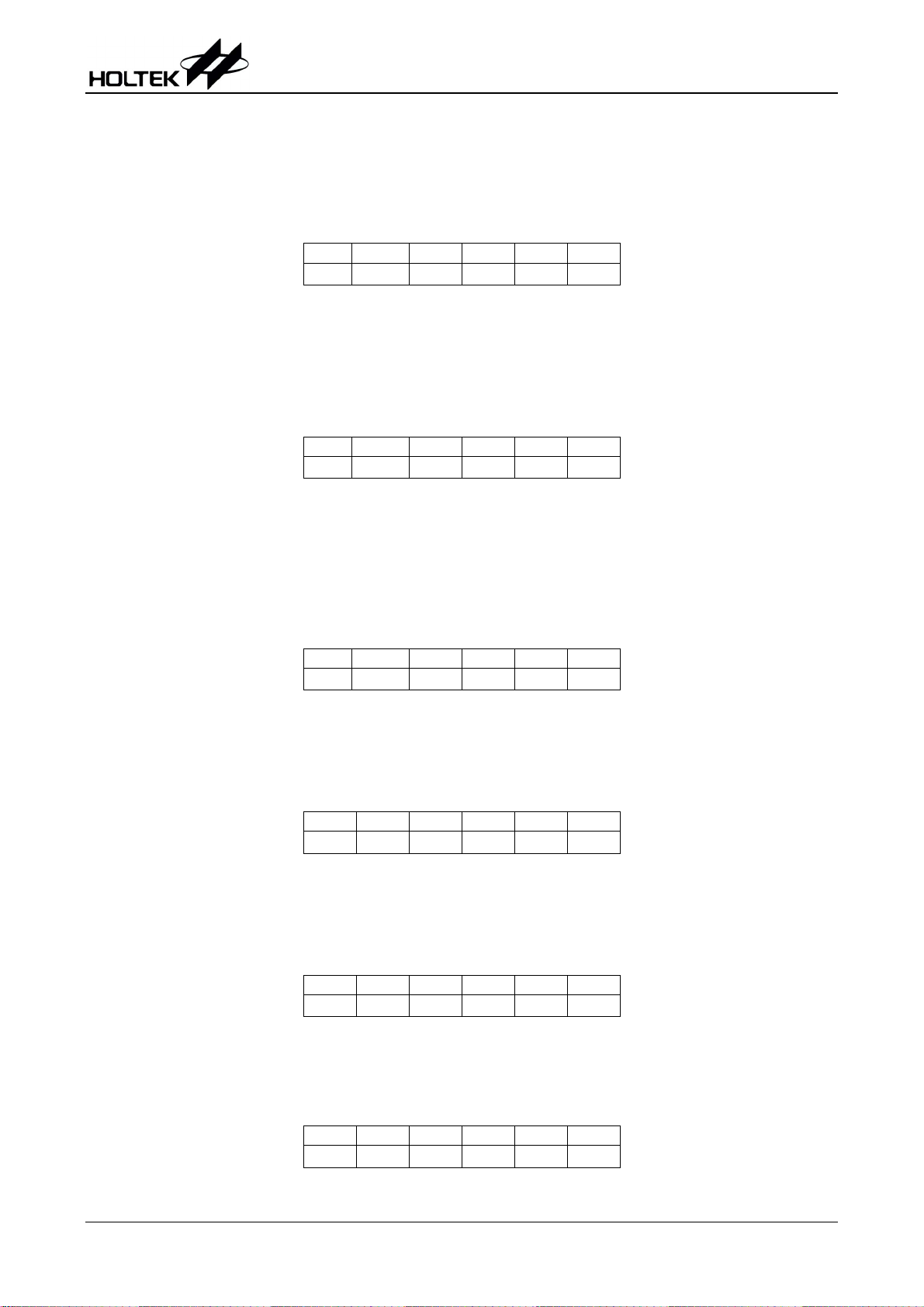

引脚图

P B 5 / A N 5

P B 4 / A N 4

P A 3 / P F D

P A 2

P A 1

P A 0

P B 3 / A N 3

P B 2 / A N 2

P B 1 / A N 1

P B 0 / A N 0

V S S

P C 0

H T 4 6 R 2 3 / H T 4 6 C 2 3

2 4 S K D I P - A / S O P - A

P B 5 / A N 5

P B 4 / A N 4

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

2 4

2 3

2 2

2 1

2 0

1 9

1 8

1 7

1 6

1 5

1 4

1 3

P B 6 / A N 6

P B 7 / A N 7

P A 4 / T M R

P A 5 / I N T

P A 6 / S D A

P A 7 / S C L

O S C 2

O S C 1

V D D

R E S

P D 0 / P W M 0

P C 1

P A 3 / P F D

P B 3 / A N 3

P B 2 / A N 2

P B 1 / A N 1

P B 0 / A N 0

1

2

3

P A 2

4

P A 1

5

P A 0

6

7

8

9

1 0

V S S

1 1

P C 0

1 2

P C 1

1 3

P C 2

1 4

H T 4 6 R 2 3 / H T 4 6 C 2 3

2 8 S K D I P - A / S O P - A

2 8

2 7

2 6

2 5

2 4

2 3

2 2

2 1

2 0

1 9

1 8

1 7

1 6

1 5

P B 6 / A N 6

P B 7 / A N 7

P A 4 / T M R

P A 5 / I N T

P A 6 / S D A

P A 7 / S C L

O S C 2

O S C 1

V D D

R E S

P D 1 / P W M 1

P D 0 / P W M 0

P C 4

P C 3

Rev. 1.70 3 2004-09-21

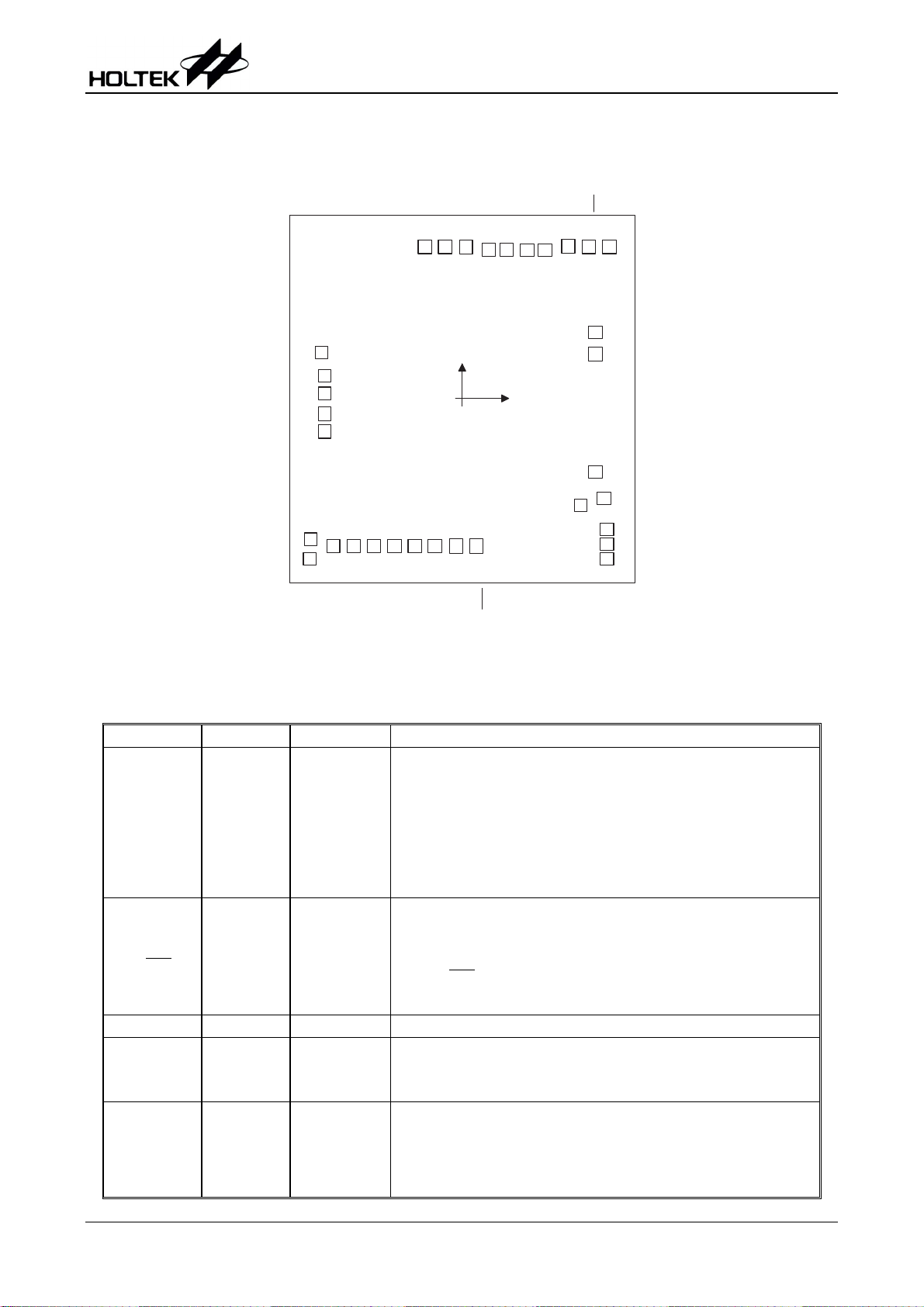

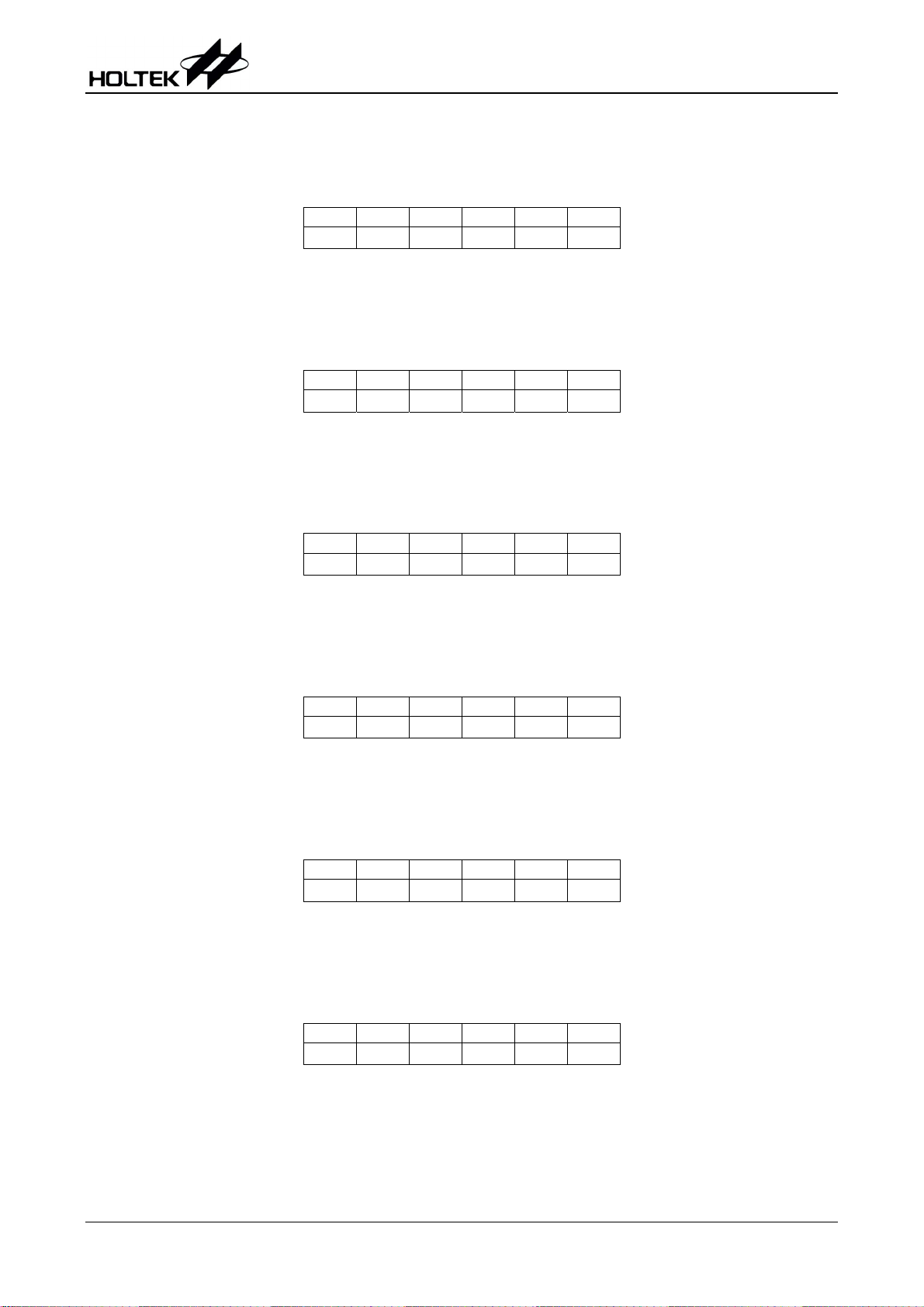

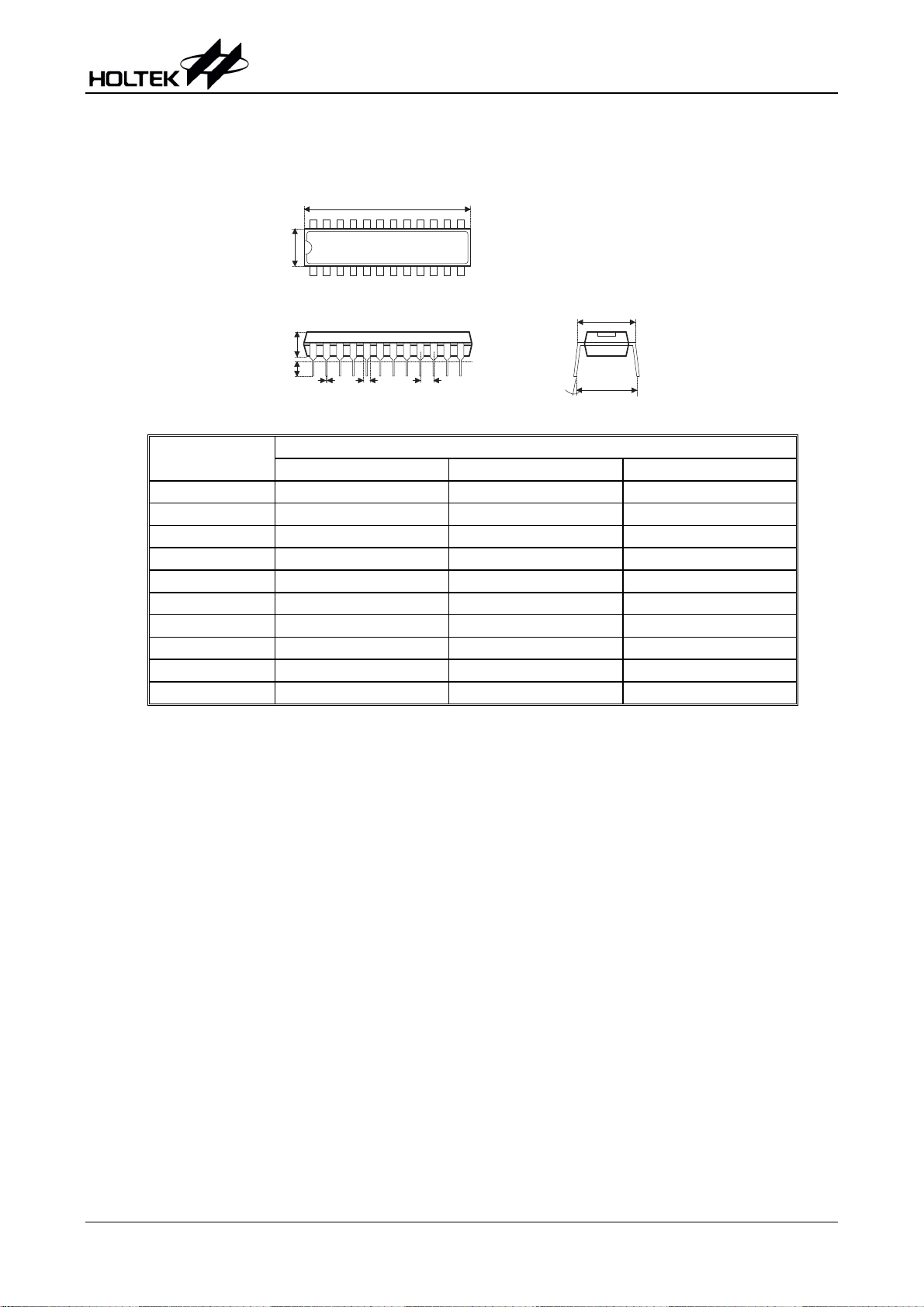

Pad 图

HT46C23

HT46R23/HT46C23

P A 4 / T M R

P A 3 / P F D

P B 4 / A N 4

P A 2

P A 1

3 2

3 3

3 1

3 0

P B 7 / A N 7

P B 6 / A N 5

P B 5 / A N 5

2 8

2 7

2 9

P A 6 / S D A

P A 5 / I N T

2 6

2 4

2 5

P A 0

P B 3 / A N 3

P B 2 / A N 2

P B 1 / A N 1

P B 0 / A N 0

V S S

V S S

1

2

3

4

5

6

9

8

7

P C 1

P C 0

1 2 1 3 1 4

1 1

1 0

P C 4

P C 3

P C 2

( 0 , 0 )

1 5

P D 0 / P W M 0

P D 1 / P W M 1

R E S

*IC 的衬底要连接到 PCB 板上的 VSS

引脚说明

引脚名称 输入/输出 掩膜选项 功能说明

PB0/AN0

PB1/AN1

PB2/AN2

PB3/AN3

PB4/AN4

PB5/AN5

PB6/AN6

PB7/AN7

PA0 -PA 2

PA3/PFD

PA4 /T MR

PA5 /

INT

PA6/SDA

PA7 /S CL

VSS

PC0~PC4

输入/输出 上拉电阻

输入/输出

— — 负电源,接地。

输入/输出 上拉电阻

上拉电阻

唤醒功能

PA3 或 PFD

I/O 或 I

8 位双向输入/输出口。可由软件设置为 CMOS 输出、带或

不带上拉电阻(由上拉电阻选项决定:端口选择)的斯密

特触发输入、或 A/D 输入。

一旦 PB 有一个口做为 A/D 输入(由软件设置),则其输入

/输出功能和上拉电阻会自动失效。

8 位双向输入/输出口。每一位可由掩膜选项设置为唤醒输

入。可由软件设置为 CMOS 输出、带或不带上拉电阻(由

上拉电阻选项决定:位选择)的斯密特触发输入。PFD、

TMR、

2

C

总线功能,则与 PA6 、PA7 相关的寄存器将被禁用。

分别与 PA3 、PA 4、PA5 共用引脚。一旦使用 I2C

INT

5 位双向输入/输出口。可由软件设置为 CMOS 输出、带或

不带上拉电阻(由上拉电阻选项决定:端口选择)的斯密

特触发输入。

2 3

2 2

2 1

1 9

P A 7 / S C L

O S C 2

O S C 1

V D D

2 0

V D D

T E S T 3

1 8

T E S T 2

1 7

1 6

T E S T 1

2 位双向输入/输出口。可由软件设置为 CMOS 输出、带或

PD0/PWM0

PD1/PWM1

输入/输出

上拉电阻

I/O 或 PWM

不带上拉电阻(由上拉电阻选项决定:端口选择)的斯密

特触发输入。PWM0/PWM1 输出与 PD0/PD1 共用引脚(由

PWM 选项决定)。

Rev. 1.70 4 2004-09-21

HT46R23/HT46C23

RES

VDD

OSC1

OSC2

输入 — 斯密特触发复位输入,低电平有效。

— — 正电源。

输入

输出

晶体或 RC

OSC1、OSC2 连接 RC 或晶体(由掩膜选项确定)以产生内部

系统时钟。在 RC 振荡方式下,OSC2 是系统时钟四分频的

输出口。

TEST1

TEST2

输入 — 测试模式下输入引脚,正常使用时不必连接。

TEST3

极限参数

电源供应电压………….VSS-0.3V~VSS+6.0V 储存温度………….-50℃~125℃

端口输入电压………….V

注:这里只强调额定功率,超过极限参数所规定的范围将对芯片造成损害,无法预期芯片在上述标示范围外的工作状态,而

且若长期在标示范围外的条件下工作,可能影响芯片的可靠性。

-0.3V~VDD+0.3V 工作温度………….-40℃~85℃

SS

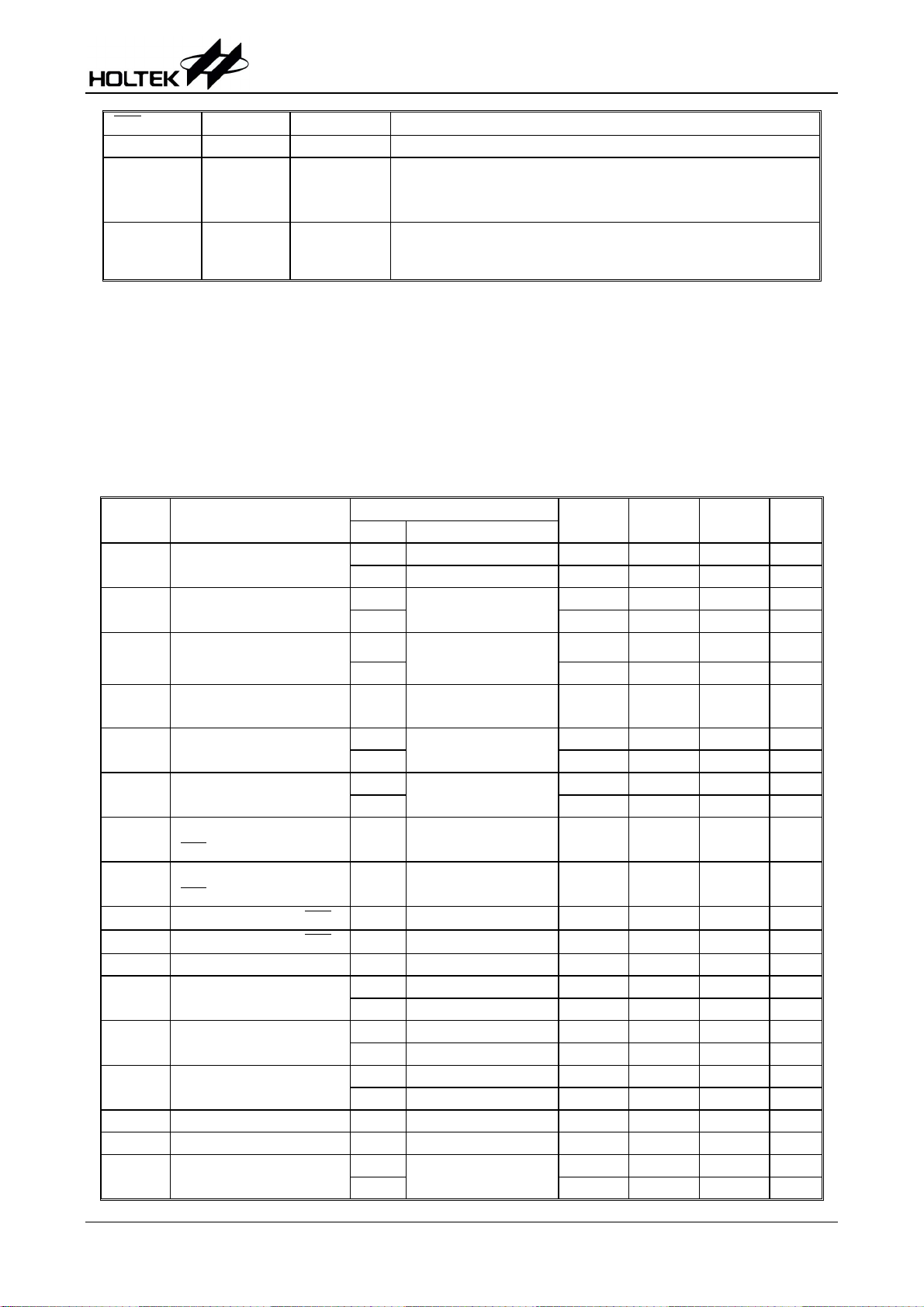

直流电气特性

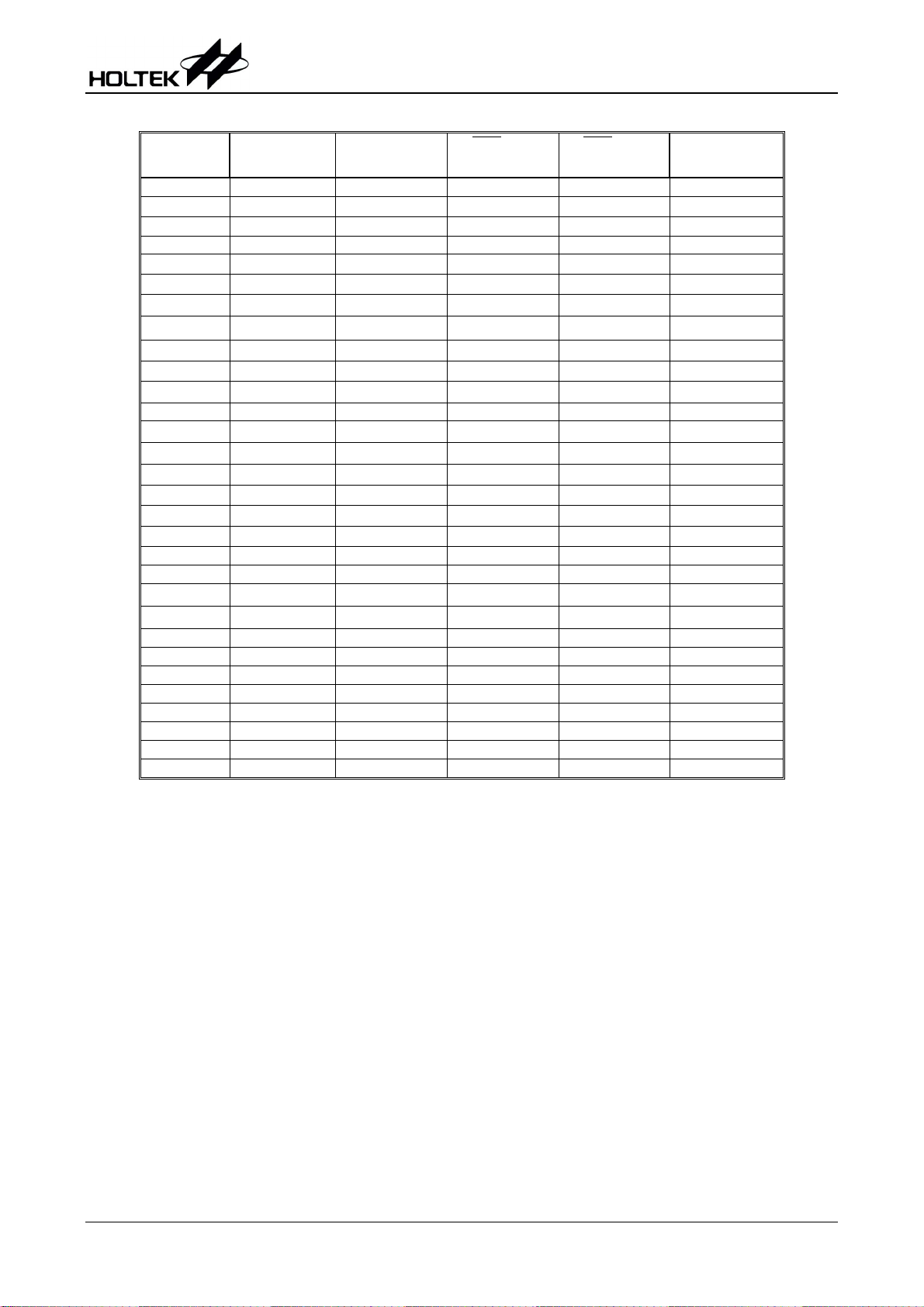

符号 参数

VDD

I

DD1

I

DD2

I

DD3

I

STB1

I

STB2

V

V

V

V

V

LVR

IOL

IOH

RPH

VAD

EAD

I

ADC

工作电压

工作电流(晶体振荡)

工作电流(RC 振荡)

工作电流

(晶体振荡,RC 振荡)

静态电流(看门狗打开)

静态电流(看门狗关闭)

输入/输出口、TMR、

IL1

IH1

IL2

IH2

的低电平输入电压

INT

输入/输出口、TMR、

的高电平输入电压

INT

低电平输入电压(

高电平输入电压(

低电压复位 — —

输入/输出口灌电流

输入/输出口源电流

上拉电阻

A/D 输入电压 — —

A/D 转换误差 — — —

打开 ADC 增加的功耗

RES

RES

V

—

—

3V

5V

3V

5V

5V

3V

5V

3V

5V

— —

— —

— —

)

— —

)

3V VOL=0.1VDD 4 8 — mA

5V V

3V VOH=0.9VDD -2 -4 — mA

5V V

3V

5V

3V

5V

测试条件

DD

f

SYS

f

SYS

无负载,f

ADC 关闭

无负载,f

ADC 关闭

无负载,f

ADC 关闭

无负载,系统 HALT

无负载,系统 HALT

=0.1VDD 10 20 — mA

OL

=0.9VDD -5 -10 — mA

OH

条件

最小 典型 最大 单位

=4MHz 2.2

=8MHz 3.3

SYS

=4MHz

—

—

SYS

=4MHz

—

—

=8MHz

SYS

—

— —

— —

— —

— —

0

0.7V

DD

0

0.9 V

DD

2.7 3 3.3 V

—

—

20 60 100

10 30 50

0

—

—

—

—

—

0.6 1.5 mA

2 4 mA

0.8 1.5 mA

2.5 4 mA

4 8 mA

—

—

—

—

—

±0.5 ±1 LSB

0.5 1 mA

1.5 3 mA

Ta=25℃

5.5 V

5.5 V

5 µA

10 µA

1 µA

2 µA

0.3 V

0.4 V

V

DD

V

V

DD

V

DD

V

V

DD

kΩ

kΩ

VDD V

Rev. 1.70 5 2004-09-21

HT46R23/HT46C23

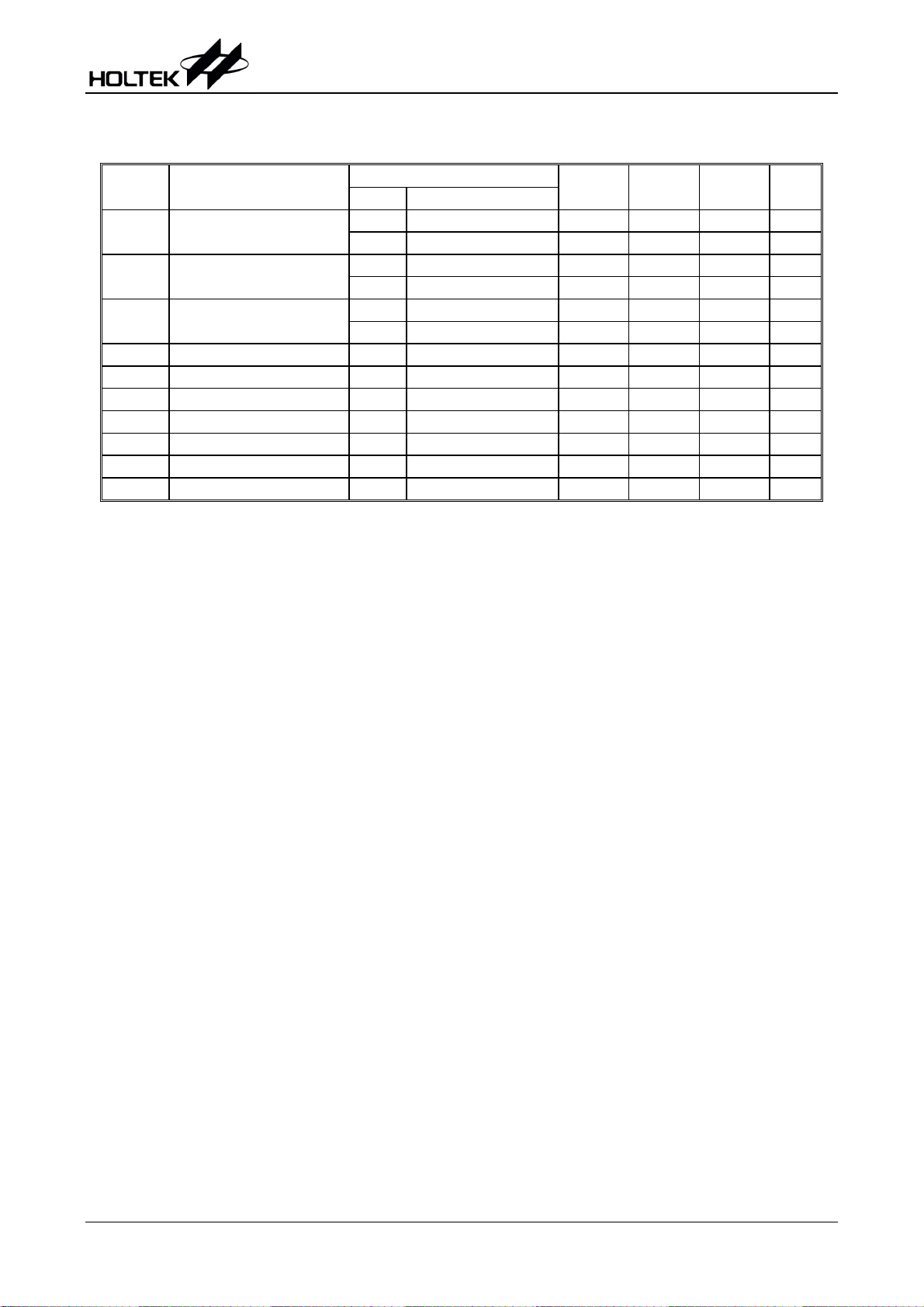

交流电气特性

符号 参数

f

SYS

f

TIMER

t

WDTOSC

t

RES

t

SST

t

INT

tAD

t

ADC

t

ADCS

t

IIC

注:*t

系统时钟

定时器输入频率

(TMR)

看门狗振荡器

外部复位低电平脉宽 — —

系统启动延迟时间 — 从 HALT 状态唤醒 —

中断脉冲宽度 — —

A/D 时钟周期 — —

A/D 转换时间 — — —

A/D 采样时间 — — —

2

I

C 总线时钟周期 — 外接 2kΩ上拉电阻

=1/f

SYS

SYS

V

—

—

—

—

3V

5V

测试条件

条件

DD

最小 典型 最大 单位

2.2V~5.5V 400 — 4000 kHz

3.3V~5.5V 400 — 8000 kHz

2.2V~5.5V 0 — 4000 kHz

3.3V~5.5V 0 — 8000 kHz

—

—

45 90 180 µs

32 65 130 µs

1

— —

1024

1

1

— —

— —

76

32

64

— —

—

—

—

Ta=25℃

µs

*t

SYS

µs

µs

tAD

tAD

*t

SYS

Rev. 1.70 6 2004-09-21

HT46R23/HT46C23

系统功能说明

指令执行时序

单片机的系统时钟由晶体振荡器或 RC 振荡器产生。该时钟在芯片内部被分成四个互不重叠的时钟周

期。一个指令周期包括四个系统时钟周期。

指令的读取和执行是以流水线方式进行的, 这种方式在一个指令周期进行读取指令操作,而在下一个

指令周期进行解码与执行该指令。因此,流水线方式使多数指令能在一个周期内执行完成。但如果渉及到

的指令要改变程序计数器的值,就需要花两个指令周期来完成这一条指令。

指令执行时序

程序计数器 — PC

程序计数器(PC)控制程序存储器 ROM 中指令执行的顺序,它可寻址整个 ROM 的范围。

取得指令码以后,程序计数器会自动加一,指向下一个指令码的地址。但如果执行跳转、条件跳跃、

向 PCL 赋值、子程序调用、初始化复位、内部中断、外部中断、子程序返回等操作时,PC 会载入与指令

相关的地址而非下一条指令地址。

当遇到条件跳跃指令且符合条件时,当前指令执行过程中读取的下一条指令会被丢弃,取而代之的是

一个空指令周期,随后才能取得正确的指令。反之,就会顺序执行下一条指令。

程序计数器的低字节(PCL)是一个可读写的寄存器(06H)。对 PCL 赋值将产生一个短跳转动作,跳

转的范围为当前页 256 个地址。

当遇到控制转移指令时,系统也会插入一个空指令周期。

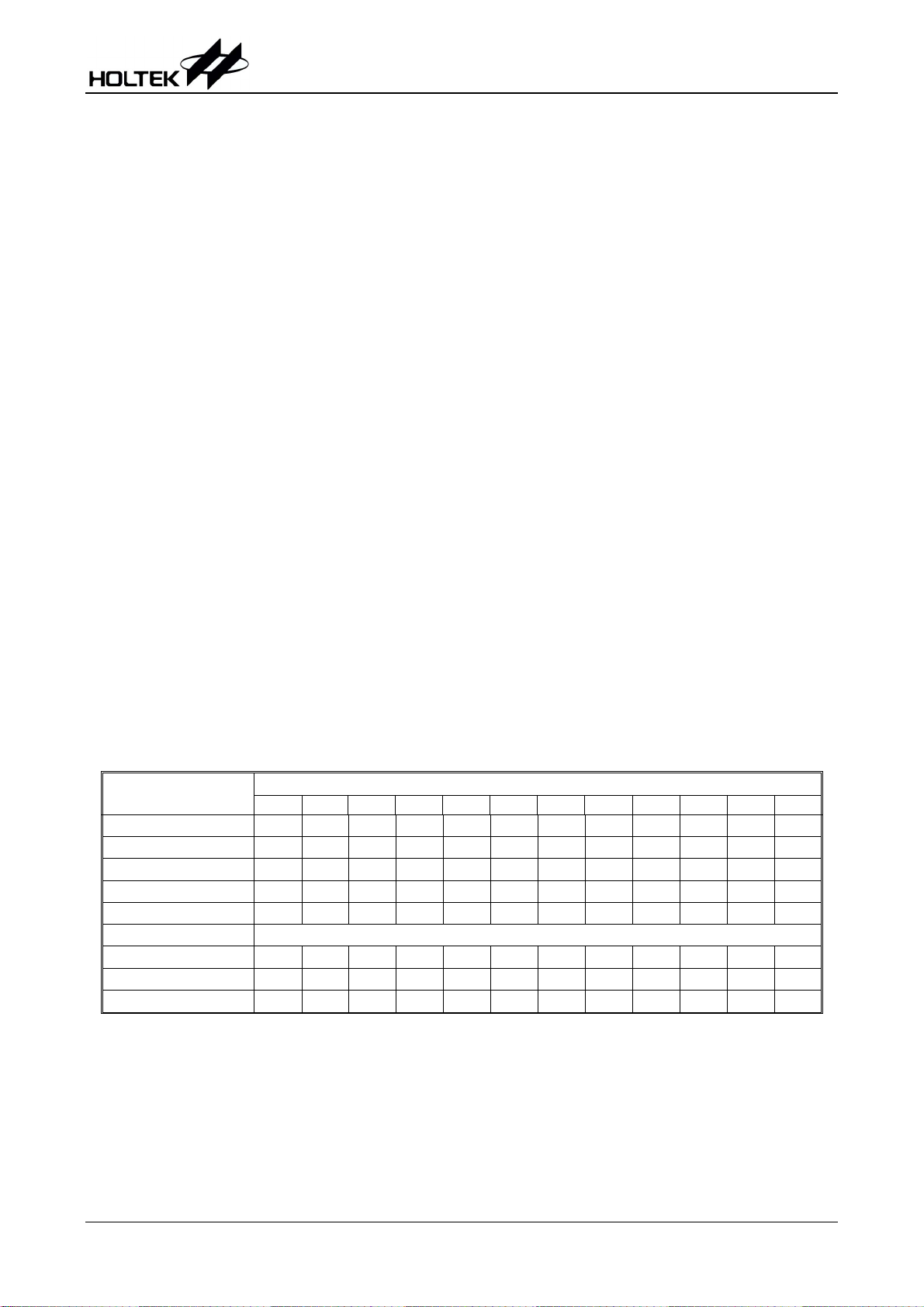

模式

初始化复位

外部中断

定时/计数器溢出

A/D 转换中断

I2C 总线中断

条件跳跃

装载 PCL

跳转、子程序调用

从子程序返回

注: *11 ~ *0 :程序计数器位 S11 ~ S0 :堆栈寄存器位

#11 ~ #0 :指令代码位 @7 ~ @0 :PCL 位

*11 *10 *9 *8 *7 *6 *5 *4 *3 *2 *1 *0

0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 1 0 0

0 0 0 0 0 0 0 0 1 0 0 0

0 0 0 0 0 0 0 0 1 1 0 0

0 0 0 0 0 0 0 1 0 0 0 0

*11 *10 *9 *8 @7 @6 @5 @4 @3 @2 @1 @0

#11 #10 #9 #8 #7 #6 #5 #4 #3 #2 #1 #0

S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1 S0

程序计数器

程序计数器

PC+2

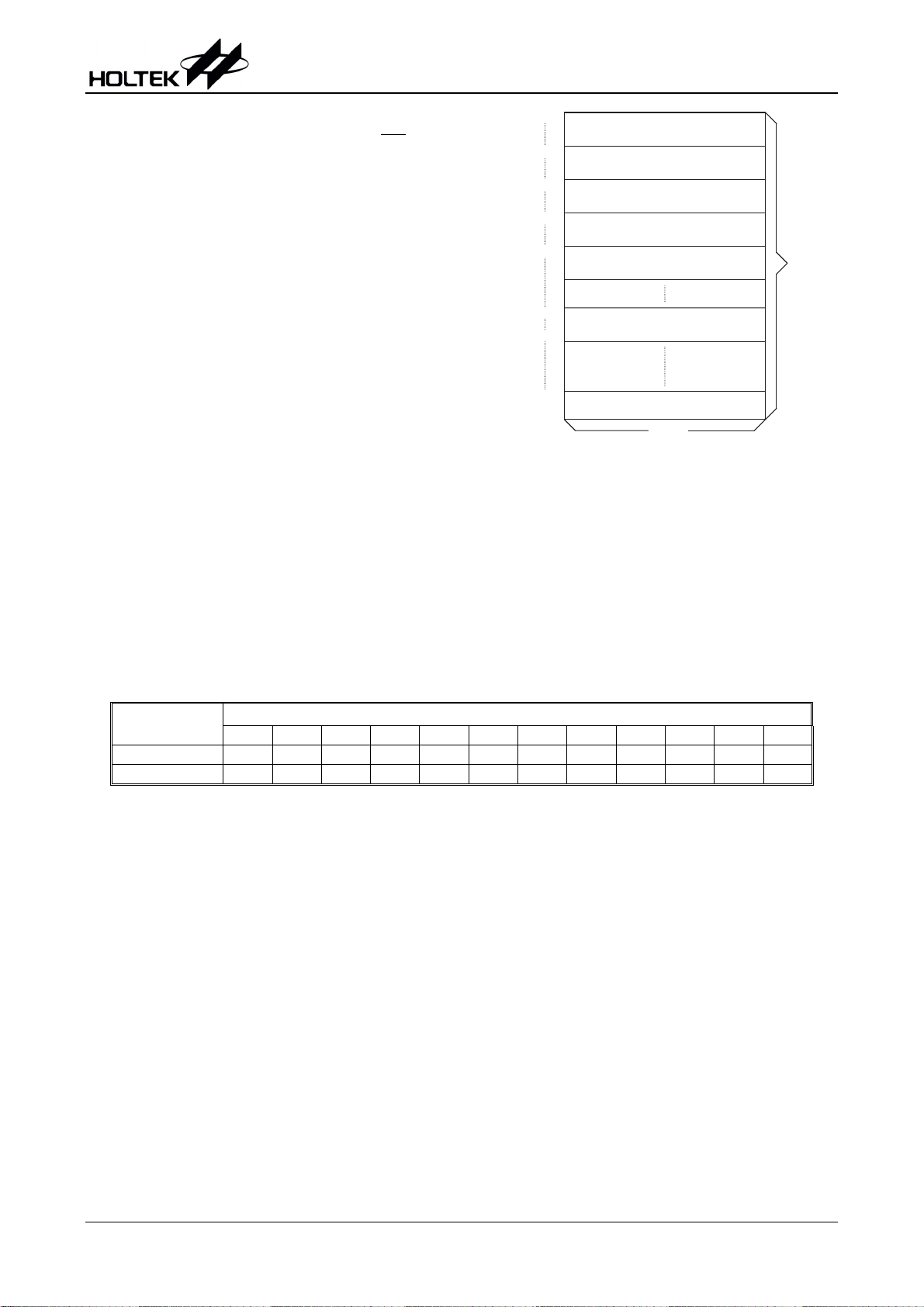

程序存储器 — ROM

程序存储器用来存放要执行的指令代码,以及一些数据、表格和中断入口。程序存储器有 4096×15 位,

程序存储器空间可以用程序计数器或表格指针进行寻址。

以下列出的程序存储器地址是系统专为特殊用途而保留的:

· 地址 000H

该地址为程序初始化保留。系统复位后,程序总是从 000H 开始执行。

Rev. 1.70 7 2004-09-21

HT46R23/HT46C23

· 地址 004H

该地址为外部中断服务程序保留。当

引脚有触发信号

INT

输入,如果中断允许且堆栈未满,则程序会跳转到 004H

地址开始执行。

· 地址 008H

该地址为定时/计数器中断服务程序保留。当定时/计数器

溢出,如果中断允许且堆栈未满,则程序会跳转到 008H

地址开始执行。

0 0 0 H

0 0 4 H

0 0 8 H

0 0 C H

0 1 0 H

D e v i c e I n i t i a l i z a t i o n P r o g r a m

E x t e r n a l I n t e r r u p t S u b r o u t i n e

T i m e r / E v e n t C o u n t e r I n t e r r u p t S u b r o u t i n e

A / D C o n v e r t e r I n t e r r u p t S u b r o u t i n e

H - B U S I n t e r r u p t S u b r o u t i n e

P r o g r a m

M e m o r y

· 地址 00CH

该地址为 A/D 转换中断服务程序保留。当 A/D 转换完成,

如果中断允许且堆栈未满,则程序会跳转到 00CH 地址

n 0 0 H

n F F H

L o o k - u p T a b l e ( 2 5 6 w o r d s )

开始执行。

· 地址 010H

该地址为 I

2

C 总线中断服务程序保留。当 I2C 总线从器件

地址匹配或收到一个完整的数据,如果中断允许且堆栈未

满,则程序会跳转到 010H 地址开始执行。

F 0 0 H

F F F H

N o t e : n r a n g e s f r o m 0 t o F

L o o k - u p T a b l e ( 2 5 6 w o r d s )

1 5 b i t s

· 表格区

ROM 空间的任何地址都可做为查表使用。查表指令“TA B RDC [m] ”(查当前页表格,1 页=256 个字)

和“TABRDL [m]”(查最后页表格),会把表格内容低字节传送给[m],而表格内容高字节传送到 TBLH

寄存器(08H)。只有表格内容的低字节被传送到目标地址中,而高字节被传送到表格内容高字节寄存

器 TBLH,并且 TBLH 的最高位始终为“0”。表格内容高字节寄存器 TBLH 是只读寄存器。表格指针

(TBLP)是可读/写寄存器(07H),用来指明表格地址。在查表之前,要先将表格地址写入 TBLP 中。

如果主程序和中断服务程序(ISR)都用到查表指令,主程序中 TBLH 的值可能会因为 ISR 中执行的

查表指令而发生变化,产生错误。也就是说,要避免在主程序和中断服务程序中都使用查表指令。但

如果必须这样做的话,我们可以在查表指令前先将中断禁止,在保存了 TBLH 的值后再开放中断以避

免发生错误。所有与表格有关的指令都需要两个指令周期的执行时间。这里提到的表格区都可以做为

正常的程序存储器来使用。

指令

*11 *10 *9 *8 *7 *6 *5 *4 *3 *2 *1 *0

表格区

TABRDC[m] P11 P10 P9 P8 @7 @6 @5 @4 @3 @2 @1 @0

TABRDL[m] 1 1 1 1 @7 @6 @5 @4 @3 @2 @1 @0

表格区

注:*11~*0:表格地址位 P11~P8:当前程序指针位 @7~@0:表格指针位

堆栈寄存器 — STACK

堆栈寄存器是特殊的存储器空间,用来保存 PC 的值。HT46x23 有 8 层堆栈,堆栈寄存器既不是数据

存储器的一部分,也不是程序存储器的一部分,而且它既不能读出,也不能写入。堆栈的使用是通过堆栈

指针(SP)来实现的,堆栈指针也不能读出或写入。当发生子程序调用或中断响应时,程序计数器(PC)

的值会被压入堆栈;在子程序调用结束或中断响应结束时(执行指令 RET 或 RETI),堆栈将原先压入堆栈

的内容弹出,重新装入程序计数器中。在系统复位后,堆栈指针会指向堆栈顶部。

如果堆栈已满,并且发生了不可屏蔽的中断,那么只有中断请求标志会被记录下来,而中断响应会被

抑制,直到堆栈指针(执行 RET 或 RETI 指令)发生递减,中断才会被响应。这个功能可以防止堆栈溢出,

使得程序员易于使用这种结构。同样,如果堆栈已满,并且发生了子程序调用,那么堆栈会发生溢出,首

先进入堆栈的内容将会丢失,只有最后的 8 个返回地址会被保留。

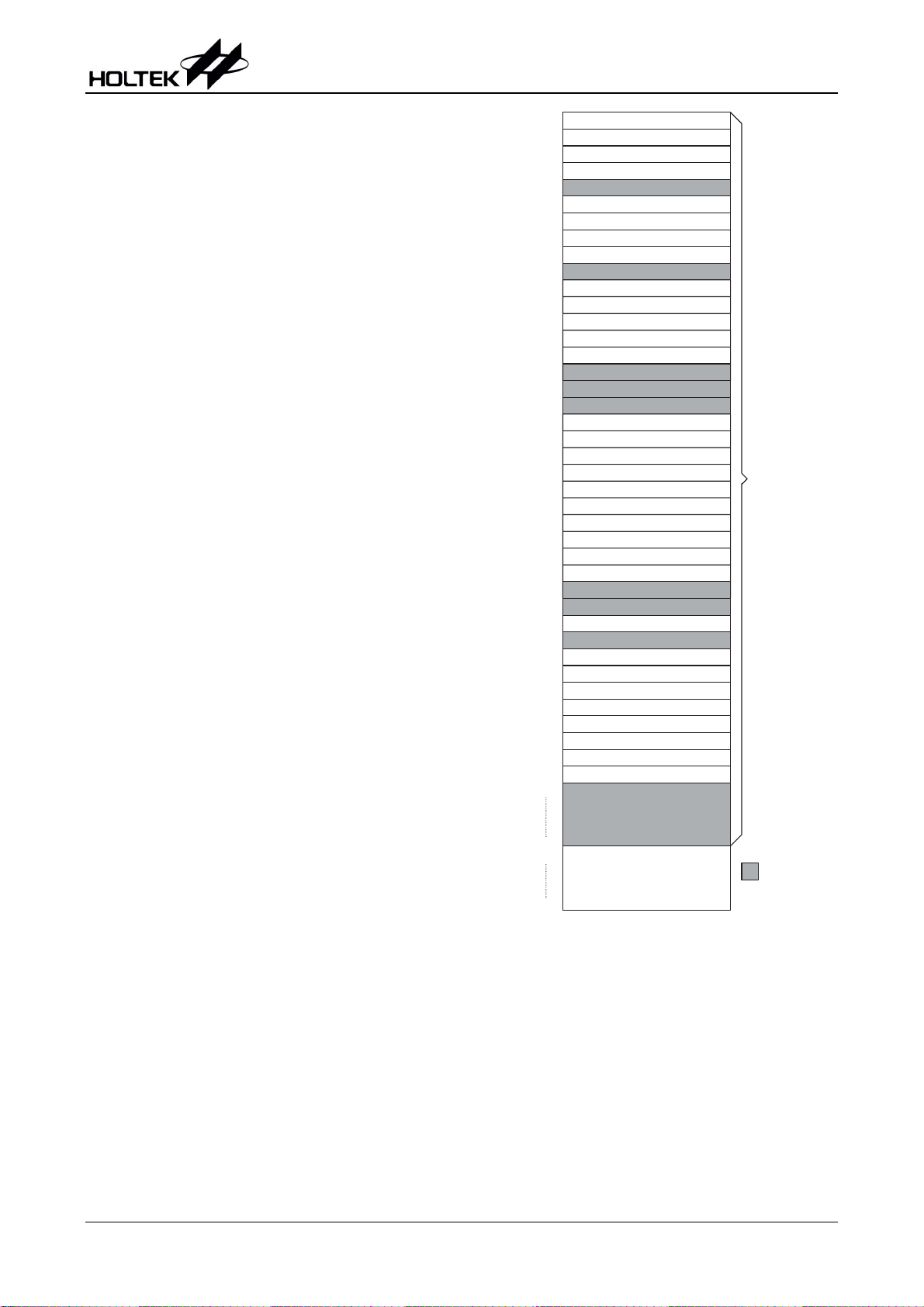

数据存储器 — RAM

数据存储器由 224×8 位组成,分为两个功能区间:特殊功能寄存器和通用数据存储器(192×8),数

据存储器单元大多数是可读/写的,但有些只读的。

特殊功能寄存器包括间接寻址寄存器(00H,02H),间接寻址指针寄存器(MP0;01H,MP1;03H),

累加器(ACC;05H),程序计数器低字节寄存器(PCL;06H),表格指针寄存器(TBLP;07H),表格内

容高字节寄存器(TBLH;08H),状态寄存器(STATUS;0AH),中断控制寄存器 0(INTC0;0BH),定

Rev. 1.70 8 2004-09-21

HT46R23/HT46C23

I n d i r e c t A d d r e s s i n g R e g i s t e r 0

时/计数器高字节(TMRH; 0CH ),定时/ 计数器低字节

(TMRL;0DH),定 时 /计数器控制寄存器(TMRC;0EH),

输入/输出寄存器(PA ;12H,PB;14H,PC;16H,PD;

18H),输 入 /输出控制寄存器(PA C;13H,PBC;15H,PCC;

17H,PDC;19H),PWM 数据寄存器(PWM0;1AH,PWM1;

1BH),中断控制寄存器 1(INTC1;1EH),I

2

地址寄存器(HADR;20H),I

21H),I

2

C 总线状态寄存器(HSR;22H),I2C 总线数据寄

C 总线控制寄存器(HCR;

2

C 总线从器件

存器(HDR;23H),A/D 转换结果低字节寄存器(ADRL;

24H),A/D 转换结果高字节寄存器(ADRH;25H),A/D

转换控制寄存器(ADCR;26H),A/D 时钟设置寄存器

(ACSR;27H)。其余在 40H 之前的空间保留给系统以后扩

展使用,读取这些地址的返回值为“00H”。通用数据寄存

器地址从 40H 到 FFH,用来存储数据和控制信息。

所有的数据存储器单元都能直接执行算术、逻辑、递增、

递减和循环操作。除了一些特殊位外,数据存储器的每一位

都可由“SET[m].i”置位或由“CLR[m].i”复位。而且都可

以通过间接寻址指针(MP0;01H/MP1;03H)进行间接寻

址。

间接寻址寄存器

地址 00H 和 02H 是间接寻址寄存器,并无实际的物理

区存在。任何对[00H]或[02H]的读/写操作,都是访问由 MP0

(01H)MP1(03H)或所指向的 RAM 单元。间接读取地

址 00H 或 02H 得到的值为 00H,间接写入此地址,不会产

生任何操作。间接寻址指针 MP0(01H)和 MP1(03H)是

8 位寄存器。

累加器

累加器(ACC)与算术逻辑单元(ALU)有密切关系。

它对应于 RAM 地址 05H,做为运算的立即数据。存储器之

间的数据传送必须经过累加器。

算术逻辑单元 — ALU

算术逻辑单元(ALU)是 执 行 8 位算术、逻辑运算的电

路,它提供有以下功能:

· 算术运算(ADD,ADC,SUB,SBC,DAA)

· 逻辑运算(AND,OR,XOR,CPL)

· 移位运算(RL,RR,RLC,RRC)

· 递增和递减(INC,DEC)

· 分支判断(SZ,SNZ,SIZ,SDZ…)

ALU 不仅可以储存数据运算的结果,还会改变状态寄存器的值。

状态寄存器 — STATUS

8 位的状态寄存器(0AH),由零标志位(Z)、进位标志位(C)、辅助进位标志位(AC)、溢出标志位

(OV)、暂停标志位(PDF)和看门狗定时器溢出标志位(TO)组成。该寄存器不仅记录状态信息,而且

还控制操作顺序。

除了 PDF 和 TO 标志外,状态寄存器的其它位都可以用指令改变。任何对状态寄存器的写操作都不会

改变 PDF 和 TO 的值。对状态寄存器的操作可能会导致与预期不一样的结果。TO 标志只受系统上电、看

门狗溢出、“CLR WDT” 指令或“HALT” 指令的影响。PDF 标志只受系统上电、“CLR WDT” 指令或

“HALT” 指令的影响。

标志位 Z、OV、AC 和 C 反映的是最近一次操作的状态。

0 0 H

0 1 H

I n d i r e c t A d d r e s s i n g R e g i s t e r 1

0 2 H

0 3 H

0 4 H

0 5 H

0 6 H

0 7 H

0 8 H

0 9 H

0 A H

0 B H

0 C H

0 D H

0 E H

0 F H

1 0 H

1 1 H

1 2 H

1 3 H

1 4 H

1 5 H

1 6 H

1 7 H

1 8 H

1 9 H

1 A H

1 B H

1 C H

1 D H

1 E H

1 F H

2 0 H

2 1 H

2 2 H

2 3 H

2 4 H

2 5 H

2 6 H

2 7 H

2 8 H

3 F H

4 0 H

F F H

G e n e r a l P u r p o s e

D A T A M E M O R Y

M P 0

M P 1

A C C

P C L

T B L P

T B L H

S T A T U S

I N T C 0

T M R H

T M R L

T M R C

P A

P A C

P B

P B C

P C

P C C

P D

P D C

P W M 0

P W M 1

I N T C 1

H A D R

H C R

H S R

H D R

A D R L

A D R H

A D C R

A C S R

( 1 9 2 B y t e s )

S p e c i a l P u r p o s e

D A T A M E M O R Y

: U n u s e d

R e a d a s " 0 0 "

Rev. 1.70 9 2004-09-21

HT46R23/HT46C23

在进入中断程序或子程序调用时,状态寄存器不会被自动压入堆栈。如果状态寄存器的内容是重要的,而

且子程序会影响状态寄存器的内容,那么程序员必须事先将 STATUS 的值保存好。

符号 位 功能

C 0

AC 1

Z 2

OV 3

PDF 4

TO 5

—

—

6

7

中断

HT46x23 提供一个外部中断、一个内部定时/计数器中断、一个 A/D 转换中断和一个 I

中断控制寄存器 0(INTC0;0BH)和中断控制寄存器 1(INTC1;1EH)包含了中断控制位和中断请求标

志,中断控制位用来设置中断允许/禁止。

寄存器 位 符号 功 能

INTC0

(0BH)

寄存器 位 符号 功 能

INTC1

(1EH)

只要有中断子程序被服务,其余的中断全部都被自动禁止(通过清除 EMI 位),这种做法的目的在于

防止中断嵌套。这时如果有其它中断发生,只有中断请求标志会被记录下来。如果在中断服务程序中有另

一个中断需要响应,程序员可以置位 EMI、INTC0 和 INTC1 所对应的位,以便进行中断嵌套。如果堆栈

已满,则中断并不会被响应,一直到堆栈指针(SP)发生递减后才会响应。如果需要中断立即得到响应,

应避免堆栈饱和。

如果在加法运算中结果产生了进位或在减法运算中结果不产生借位,

则 C 被置位;反之,C 被清除。它也可被循环移位指令影响。

如果在加法运算中低 4 位产生了进位或减法运算中低 4 位不产生借

位,则 AC 被置位;反之,AC 被清除。

如果算术或逻辑运算的结果为零,则 Z 被置位;反之,Z 被清除。

如果运算结果向最高位进位,但最高位并不产生进位输出,则 OV 被

置位;反之,OV 被清除

系统上电或执行“CLR WDT”指令,PDF 被清除;执行“HALT”指

令,PDF 被置位。

系统上电、执行“CLR WDT”或“HALT”指令,TO 被清除;WDT

定时溢出,TO 被置位。

未用,读出为“0”

未用,读出为“0”

状态寄存器

2

C 总线中断。

0 EMI

1 EEI

2 ETI

3 EADI

4 EIF

5 TF

6 ADF

7

0 EHI

1

2

3

4 HIF

5

6

7

总中断控制位(1=允许;0=禁止)

外部中断控制位(1=允许;0=禁止)

定时/计数器中断控制位(1=允许;0=禁止)

A/D 转换中断控制位(1=允许;0=禁止)

外部中断请求标志(1=有;0=无)

定时/计数器中断请求标志(1=有;0=无)

A/D 转换中断请求标志(1=有;0=无)

— 未用,读出为“0”

INTC0 寄存器

2

I

C 总线中断控制位(1=允许;0=禁止)

— 未用,读出为“0”

— 未用,读出为“0”

— 未用,读出为“0”

2

I

C 总线中断请求标志(1=有;0=无)

— 未用,读出为“0”

— 未用,读出为“0”

— 未用,读出为“0”

INTC1 寄存器

Rev. 1.70 10 2004-09-21

HT46R23/HT46C23

所有的中断都具有唤醒能力。当有中断被服务,系统会将程序计数器值压入堆栈,然后再跳转至中断

服务程序的入口。但这时只有程序计数器的内容被压入堆栈,如果其它寄存器和状态寄存器的内容会被中

断程序改变,从而会破坏主程序的控制流程的话,程序员应该事先将这些数据保存起来。

外部中断是由

如果中断允许,且堆栈未满,当发生外部中断时,会产生地址 04H 的子程序调用;而中断请求标志 EIF 和

总中断控制位 EMI 会被清除,以禁止其它中断响应。

内部定时/计数器中断是由定时/计数器溢出触发的,其中断请求标志(TF;INTC0 的第 5 位)会被置

位。如果中断允许,且堆栈未满,当发生定时/计数器中断时,会产生地址 08H 的子程序调用;而中断请

求标志 TF 和总中断控制位 EMI 会被清除,以禁止其它中断响应。

A/D 转换中断是由 A/D 转换完成触发的,其中断请求标志(ADF;INTC0 的第 6 位)会被置位。如果

中断允许,且堆栈未满,当发生 A/D 转换中断时,会产生地址 0CH 的子程序调用;而中断请求标志位 ADF

和总中断控制位 EMI 会被清除,以禁止其它中断响应。

2

I

C 总线中断是由从器件地址匹配(HAAS=“1”)或接收到完整的数据触发的,其中断请求标志位(HIF;

INTC1 的第 4 位)会被置位。如果中断允许,且堆栈未满,当发生 I

程序调用;而中断请求标志位 HIF 和总中断控制位 EMI 会被清除,以禁止其它中断响应。

在执行中断子程序期间,其它的中断请求会被屏蔽,直到执行 RETI 指令或 EMI 和相关中断控制位被

置位(当然,此时堆栈未满)。如果要从中断子程序返回,只要执行 RET 或 RETI 指令即可。其中,RETI

指令会自动置位 EMI,以允许中断服务,而 RET 则不会。

如果中断在两个连续的 T2 脉冲的上升沿之间发生,且中断响应允许,那么在下两个 T2 脉冲之间,

该中断会被服务。如果同时发生中断请求,其优先级如下表示;也可以通过设定各中断相关的控制位来改

变优先级。

中断控制寄存器 0(INTC0),由定时/计数器中断请求标志(TF)、外部中断请求标志(EIF)、A/D 转换中

断请求标志(ADF)、定时/计数器中断允许(ETI)、外部中断允许(EEI)、A/D 转换中断允许(EADI)和总中断

允许(EMI)组成,其对应于数据存储器地址 0BH。中断控制寄存器 1(INTC1),由 I

2

和 I

C 总线中断允许(EHI)组成,其对应于数据存储器地址 1EH。EMI、EEI、ETI、EADI 和 EHI 用来控制

中断的允许/禁止状态的。这些控制位可以用来屏蔽正在进行中断服务程序时发生的其它中断请求。一旦中

断请求标志(TF、EIF、ADF、HIF)被置位,会一直保留在 INTC0 和 INTC1 寄存器中,直到中断被响应或

用软件指令清除为止。

建议不要在中断服务程序中使用“CALL”指令来调用子程序。因为中断随时都可能发生,而且需要

立刻给予响应。如果只剩下一层堆栈,而中断不能被很好地控制,原先的控制序列很可能因为在中断子程

序中执行“CALL”指令而使堆栈溢出,从而发生混乱。

振荡电路

HT46x23 有两种振荡方式,外部 RC 振荡和外部晶体振荡,

可以通过掩膜选项设定,不管选用哪一种振荡方式,其信号都

可以做为系统时钟。HALT 模式会停止系统振荡器,并忽视任何

外部信号以降低功耗。

如果选用外部 RC 振荡方式,在 OSC1 与 VSS 之间需要接

一个外部电阻,其阻值为 30kΩ到 750kΩ;而 OSC2 上会输出系

统频率的 4 分频信号,可用于同步外部逻辑。RC 振荡方式是一

种低成本的方案,但是,RC 振荡频率会随着 VDD、温度和芯片自身参数的漂移而产生误差。因此,在需

要精确振荡频率做为计时操作的场合,并不适合使用 RC 振荡方式。

如果选用晶体振荡方式,在 OSC1 和 OSC2 之间需要连接一个晶体,用来提供晶体振荡器所需的反馈

和相移,除此之外,不再需要其它外部元件。另外,在 OSC1 和 OSC2 之间也可使用谐振器来取代晶体振

荡器,但是在 OSC1 和 OSC2 需要多连接两个电容(如果振荡频率小于 1MHz)。

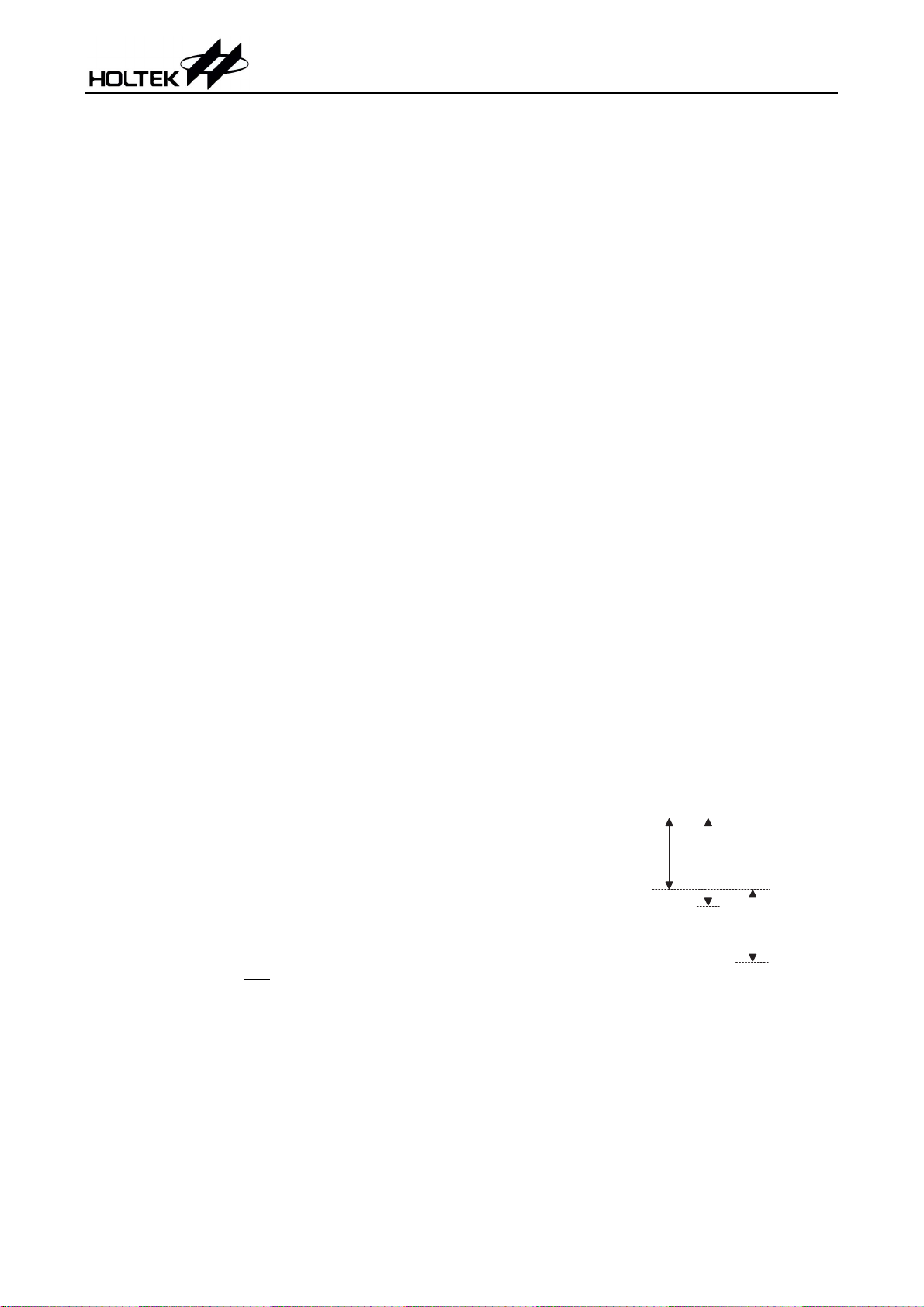

WDT 振荡器是一个内部 RC 振荡器,并不需要连接任何外部元件。当系统进入暂停模式时,系统时钟

Rev. 1.70 11 2004-09-21

引脚下降沿信号触发的,其中断请求标志位(EIF;INTC0 的第 4 位)会被置位。

INT

2

C 总线中断时,会产生地址 10H 的子

No. 中断源 优先级 中断向量

a

外部中断

b

定时/计数器中断

c

A/D 转换中断

2

d

I

C 总线中断

1 04H

2 08H

3 0CH

4 10H

2

C 总线中断请求标志(HIF)

O S C 1

O S C 2

C r y s t a l O s c i l l a t o r R C O s c i l l a t o r

V

D D

f

/ 4

S Y S

N M O S O p e n D r a i n

O S C 1

O S C 2

HT46R23/HT46C23

会停止,但 WDT 振荡器会继续工作,其振荡周期大约为 65µs/5V。如果要降低功耗,可在掩膜选项中关

闭 WDT 振荡器。

看门狗定时器

看门狗定时器的时钟来源有两种:看门狗振荡器或指令时钟(系统时钟 4 分频),由掩膜选项设置。看

门狗定时器主要用来防止程序运行故障和程序跳入一死循环而导致不可预测的结果。看门狗定时器可由掩

膜选项设置为打开或关闭,如果在关闭状态,所有与 WDT 有关的指令操作都是没有作用的。

看门狗定时器

如果 WDT 时钟源为内部 WDT 振荡(RC 振荡周期一般为 65µs),该频率(通过掩膜选项:WDT time out)

可再加 2

12~215

的分频系数。最小的 WDT 溢出周期大约是 300mS~600mS。溢出时间会因为温度、VDD 以

及芯片参数的变化而变化。如果再用 WDT 预分频器,则可以得到更长的溢出周期。如果 WDT 的溢出时

间(time out)选为 215,最大的溢出时间可达到 2.3s~4.7s(分频系数为 215~216)。

WDT 时钟源除了使用内部 WDT 振荡器输出外,还可以使用指令时钟(系统时钟 4 分频),只是在 HALT

时,WDT 会停止计数而失去保护功能;此时只能靠外部逻辑复位来重新启动系统。如果系统运用在强干

扰的环境中,建议选用内部 WDT 振荡器,因为 HALT 模式会使系统时钟停止,看门狗也就失去了保护的

功能。

在正常运行时,WDT 溢出会使系统复位并置位 TO 标志;但在 HALT 模式下,WDT 溢出只产生“热

复位”,只有程序计数器 PC 和堆栈指针 SP 被复位。要清除 WDT 的值可以有三种方法:外部复位(低电平

输入到

端)、清除看门狗指令或 HALT 指令。清除看门狗指令有“CLR WDT”和“ CLR WDT1”、“CLR

RES

WDT2”二组指令。这两组指令中,只能选择其中一组,由掩膜选项决定。如果选择“CLR WDT”,那么

只要执行“CLR WDT” 指令就会清除 WDT。如果选择“CLR WDT1”和“CLR WDT2”,那么二条指令

要交替使用才会清除 WDT,否则,WDT 会由于溢出而使系统复位。

如果 WDT 的分频系数选择 f

/212(由掩膜选项决定),则 WDT 的溢出周期为 fS/212~fS/213,因为“CLR

S

WDT”和“CLR WDT1”、“CLR WDT2”指令只能清除最后两级 WDT 分频器。

暂停模式 — HALT

暂停模式是由 HALT 指令来实现的,暂停模式时系统状态如下:

· 系统振荡器停振,但 WDT 振荡器会继续振荡(如果选择 WDT 振荡器)。

· RAM 和寄存器内容保持不变。

· WDT 被清除并重新开始计数(如果 WDT 时钟来源为 WDT 振荡器)。

· 所有输入/输出口都保持其原有状态。

· 置位 PDF 标志,清除 TO 标志。

以下操作可以使系统离开暂停模式:外部复位、中断、PA 口下降沿信号或看门狗定时器溢出。其中,

外部复位会使系统初始化,WDT 溢出则会发生“热复位”。通过检测 TO 和 PDF 标志,即可了解系统复位

的原因。PDF 标志可由系统上电或执行“CLR WDT”指令清除,由 HALT 指令置位。TO 标志由 WDT 溢

出置位,同时产生唤醒,但只有程序计数器 PC 和堆栈指针 SP 被复位,其它都保持其原有的状态。

PA 口唤醒和中断唤醒可做为正常运行的继续。PA 口的每一位都可以由掩膜选项设置为唤醒功能。如

果是由输入/输出口唤醒,程序会从下一条指令开始运行。如果是由中断唤醒,可能会发生两种情况:如果

中断禁止或中断允许但堆栈已满,程序将会从下一条指令开始运行;如果中断允许且堆栈未满,则会产生

一般的中断响应。如果在进入 HALT 模式之前,中断请求标志位已被置“1”,则中断唤醒功能被禁止。

当发生唤醒,系统需要额外花费 1024t

(系统时钟周期)的时间,才能重新正常运行,也就是说,唤

SYS

醒之后会插入一个等待周期。如果唤醒是由中断产生的话,则实际中断子程序的执行会延迟一个以上的周

Rev. 1.70 12 2004-09-21

HT46R23/HT46C23

期。如果唤醒导致下一条指令执行,那么在等待周期执行完成之后,会立即执行该指令。

为减小功耗,在进入暂停模式之前,应小心处理所有的输入/输出口状态。

复位

总共有三种方法会产生初始复位:

· 正常运行时由

· 在暂停模式由

引脚发生复位。

RES

引脚发生复位。

RES

· 正常运行时由看门狗定时器溢出发生复位。

暂停模式中的看门狗定时器溢出与其它系统复位状况不同,因为看门狗

定时器溢出会执行“热复位”,只有程序计数器 PC 和堆栈指针 SP 被复位,

而系统其它部分都保持原有状态。在其它复位状态下,某些寄存器不会改变。

在初始复位时,大部分寄存器会复位成初始的状态。通过检测 PDF 和 TO

标志,即可判断出各种不同的复位原因。

TO PDF 复位原因

0 0

u u

0 1

1 u

1 1

注:“u”表示不变

上电时

正常运行时

暂停模式下

RES

发生复位

发生复位

RES

发生复位

RES

正常运行时 WDT 溢出

暂停模式下 WDT 溢出

为了保证系统振荡器起振并稳定运行,系统复位(包括上电复位、WDT 溢出或由

状态唤醒时,系统启动定时器(SST)提供了一个额外的延迟时间,共 1024 个系统时钟周期。

系统复位时,SST 会被加在复位延时中;由暂停模式唤醒也会加入 SST 延迟。

系统复位(包括上电复位、正常运行时 WDT 溢出或由

端复位)需要额外增加一个加载掩膜选项

RES

(Option)的时间。

系统复位时各功能单元的状态如下所示:

PC 000H

中断 禁止

WDT

清除,在主系统复位后,WDT 开始计数

定时/计数器 停止

输入/输出口 输入模式

堆栈指针 SP 指向堆栈顶部

V

D D

0 . 0 1mF *

1 0 0 k

W

1 0 k

W

0 . 1mF *

复位电路

注:“* ”连线应该尽量靠近

引脚,以减小干扰影响

端复位)或由暂停

RES

R E S

RES

复位时序 复位电路结构

Rev. 1.70 13 2004-09-21

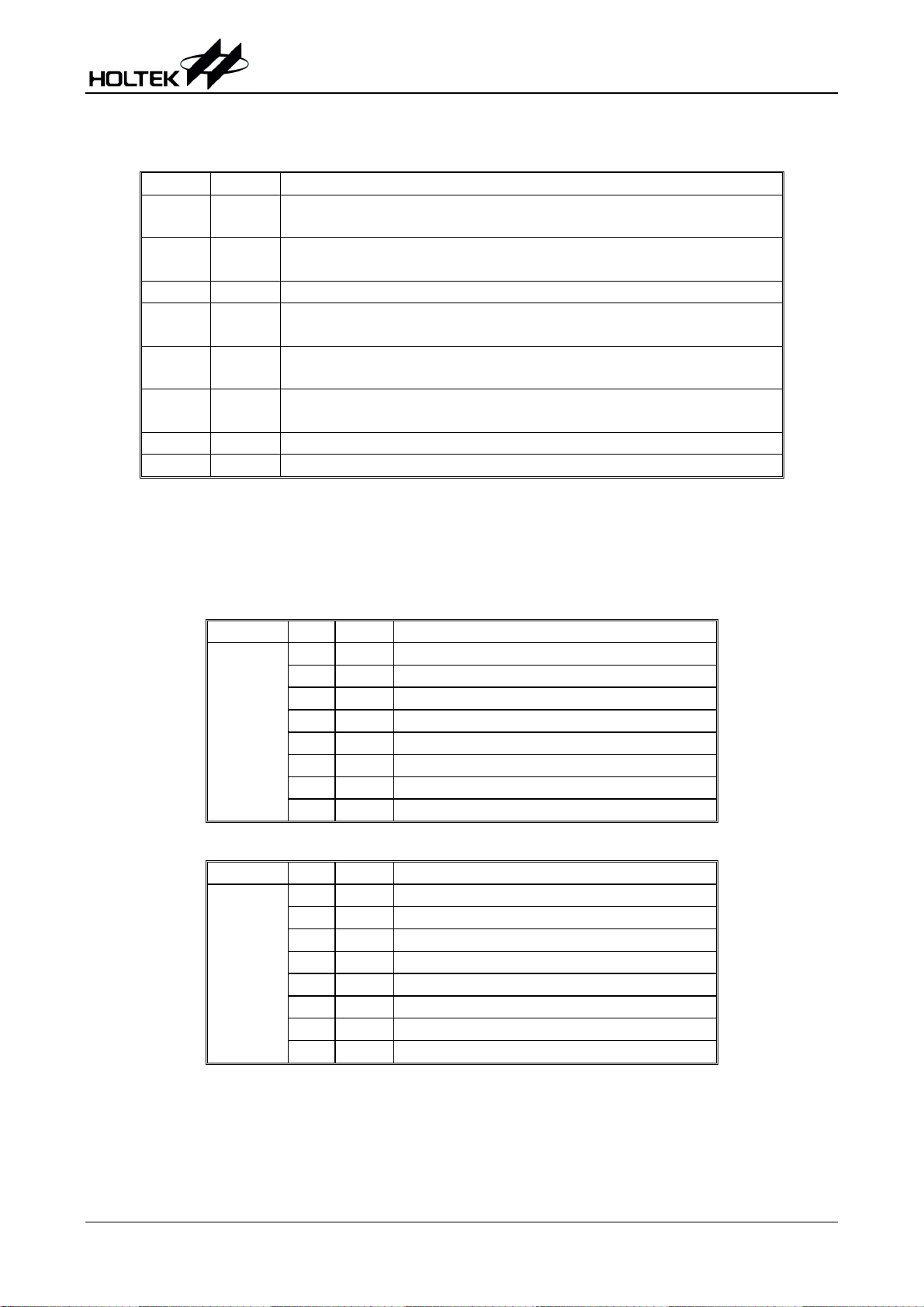

有关寄存器的状态如下:

寄存器

(上电复位)

TMRL xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx uuuu uuuu

TMRH xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx uuuu uuuu

TMRC 00-0 1000 00-0 1000 00-0 1000 00-0 1000 uu-u uuuu

PC 000H 000H 000H 000H 000H

MP0 xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu

MP1 xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu

ACC xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu

TBLP xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu

TBLH -xxx xxxx -uuu uuuu -uuu uuuu -uuu uuuu -uuu uuuu

STATUS --00 xxxx --lu uuuu --uu uuuu --01 uuuu --11 uuuu

INTC0 -000 0000 -000 0000 -000 0000 -000 0000 -uuu uuuu

INTC1 ---0---0 ---0---0 ---0---0 ---0---0 ---u---u

PA 1111 1111 1111 1111 1111 1111 1111 1111 uuuu uuuu

PAC 1111 1111 1111 1111 1111 1111 1111 1111 uuuu uuuu

PB 11111111 1111 1111 11111111 11111111 uuuu uuuu

PBC 11111111 11111111 11111111 11111111 uuuu uuuu

PC ---1 1111 ---1 1111 ---1 1111 ---1 1111 ---u uuuu

PCC ---1 1111 ---1 1111 ---1 1111 ---1 1111 ---u uuuu

PD ---- --11 ---- --11 ---- --11 ---- --11 ---- --uu

PDC ---- --11 ---- --11 ---- --11 ---- --11 ---- --uu

PWM0

PWM1

xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx uuuu uuuu

xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx uuuu uuuu

HADR xxxx xxx- xxxx xxx- xxxx xxx- xxxx xxx- uuuu uuuHCR 0--0 0--- 0--0 0--- 0--0 0--- 0--0 0--- u--u u--HSR 100- -0-1 100- -0-1 100- -0-1 100- -0-1 uuu- -u-u

HDR xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx uuuu uuuu

ADRL xx-- ---- xx-- ---- xx-- ---- xx-- ---- uu-- ---ADRH xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx uuuu uuuu

ADCR 0100 0000 0100 0000 0100 0000 0100 0000 uuuu uuuu

ACSR 1--- --00 1--- --00 1--- --00 1--- --00 u--- --uu

注: 1.“*”表示“热复位; 2.“u”表示不变化; 3.“x”表示不确定。

复位

WDT 溢出

(正常运行)

复位

RES

(正常运行)

复位

RES

(暂停模式)

HT46R23/HT46C23

WDT 溢出

(暂停模式)*

Rev. 1.70 14 2004-09-21

HT46R23/HT46C23

定时/计数器

HT46x23 有一个 16 位可编程向上计数的定时/计数器。定时/计数器的时钟来源可以是外部信号输入或

系统时钟。

P W M

( 6 + 2 ) o r ( 7 + 1 )

C o m p a r e

f

S Y S

8 - s t a g e p r e s c a l e r

8 - 1 M U X

P S C 2 ~ P S C 0

如果用做内部定时器方式,则只有一个时钟来源,即系统时钟 f

T M R

T M 1

T M 0

T O N

f

I N T

T o P D 0 / P D 1 C i r c u i t

T M 1

T M 0

T E

P u l s e W i d t h

M e a s u r e m e n t

M o d e C o n t r o l

定时/计数器

L o w B y t e

B u f f e r

1 6 - B i t

P r e l o a d R e g i s t e r

H i g h B y t e

1 6 - B i t T i m e r / E v e n t C o u n t e r

L o w B y t e

。外部信号输入可以用来计数外部

SYS

D a t a B u s

R e l o a d

O v e r f l o w t o I n t e r r u p t

1 / 2

P F D

事件、测量时间间隔、测量脉冲宽度或产生一个精确的时基信号。

有三个与定时/计数器有关的寄存器,TMRH(0CH)、TMRL([0DH])和 TMRC([0EH])。写入 TMRL 只

能将数据写到低字节缓冲器(8 位), 而写入 TMRH 会把指定数据和低字节缓冲器的数据分别写到 TMRH

和 TMRL 预置寄存器中,定时/计数器预置寄存器的内容只有在写入 TMRH 时才会被改变。读取 TMRH 会

把 TMRH 的内容送至目标单元,而 TMRL 的值被送至低字节缓冲器中。读 TMRL 将读取低字节缓冲器的

值。TMRC 是定时/计数器控制寄存器,用来定义定时/计数器一些选项。

符号(TMRC) 位 功能

定义预分频器级数,PSC2,PSC1,PSC0=

PSC0~PSC2 0~2

TE 3

TON 4

—

5

000:f

INT=fSYS

001/:f

010:f

011:f

100:f

101:f

110:f

111:f

INT=fSYS

INT=fSYS

INT=fSYS

INT=fSYS

INT=fSYS

INT=fSYS

INT=fSYS

定义定时/计数器 TMR 的触发方式

(0=上升沿作用,1=下降沿作用)

打开/关闭定时/计数器( 1=打开,0=关闭)

未用,读出为“0”

/2

/4

/8

/16

/32

/64

/128

定义工作模式:

TM0

TM1

01=事件计数模式(外部时钟)

6

10=定时模式(内部时钟)

7

11=脉冲宽度测量模式

00 =未用

TMRC 寄存器

TM0、TM1 用来定义定时/计数器的工作模式。外部事件计数模式是用来记录外部事件的,其时钟来

源为外部 TMR 引脚输入。定时器模式是一个常用模式,其时钟来源为内部时钟 f

量 TMR 引脚高/低电平的脉冲宽度,其时钟来源为内部时钟 f

INT

。

。脉宽测量模式可以测

INT

无论是定时模式还是外部事件计数模式,一旦开始计数,定时/计数器会从寄存器当前值向上计到

0FFFFH。一旦发生溢出,定时/计数器会从预置寄存器中重新加载初值,并开始计数;同时置位中断请求

标志(TF;INTC0 的第 5 位)。

Rev. 1.70 15 2004-09-21

HT46R23/HT46C23

在脉宽测量模式,当 TON 与 TE 是 1 时,只要 TMR 引脚有一个上升沿信号(如果 TE 是 0,则为下降

沿信号),定时/计数器就会开始计数,直到 TMR 脚电平恢复,同时 TON 被清零。测量的结果会保存在寄

存器中,直到有新的测量开始。换句话说,一次只能测量一个脉冲宽度。重新置位 TON 后,可以继续测

量。注意,在该模式下,定时/计数器是跳变触发而不是电平触发。当计数器溢出时,定时/计数器会从预

置寄存器中重新加载初值,并置位中断请求标志,这与其它两种模式一样。要启动计数器,只要置位

TON(TMRC 的第 4 位)。在脉宽测量模式下,TON 在测量结束后会被自动清除;但在另外两种模式中,TON

只能由指令来清除。定时/计数器溢出可以做为唤醒信号。不管是什么模式,只要写 0 到 ETI 即可禁止定时

/计数器中断服务。

在定时/计数器停止计数时,写数据到定时/计数器的预置寄存器中,同时会将该数据写入到定时/计数

器。但如果在定时/计数器运行时这么做,数据只能写入到预置寄存器中,直到发生溢出时才会将数据从预

置寄存器加载到定时/计数器寄存器。读取定时/计数器时,计数会被停止,以避免发生错误;计数停止会

导致计数错误,程序员必须注意到这一点。

TMRC 的第 0~2 位用来定义内部时钟预分频级数,定义如上表所示。定时/计数器的溢出信号可做为

PFD 输出。

输入/输出口

HT46x23 有 23 个双向输入/输出口,记为 PA 、PB、PC 和 PD,其分别对应 RAM 地址[12H]、[14H]、

[16H]和[18H],所有端口都可以进行输入/输出操作。输入时,端口没有锁存功能,输入信号必须在 MOV A,

[m](m=12H、14H、16H 或 18H)指令的 T2 上升沿到来前准备好;输出时,端口有锁存功能,端口上的数

据会保持不变直到执行下一个写入操作。

D a t a B u s

W r i t e C o n t r o l R e g i s t e r

C h i p R e s e t

R e a d C o n t r o l R e g i s t e r

W r i t e D a t a R e g i s t e r

( P D 0 o r P W M 0 )

( P D 1 o r P W M 1 )

R e a d D a t a R e g i s t e r

S y s t e m W a k e - u p

( P A o n l y )

I N T f o r P A 5 O n l y

T M R f o r P A 4 O n l y

P A 3

P F D

C o n t r o l B i t

Q

D

C K

Q

S

D a t a B i t

Q

D

Q

C K

S

P U

M

U

X

O P 0 ~ O P 7

输入/输出口

M

U

X

P F D E N

( P A 3 )

每个输入/输出口都有一个控制寄存器(PAC,PBC,PCC,PDC),用来控制输入/输出状态。利用控制

寄存器,可对 CMOS 输出、带或不带上拉电阻的斯密特触发输入通过软件动态地进行改变。做为输入时,

对应的控制寄存器应设置为“1”。输入信号来源也取决于控制寄存器,如果控制寄存器的值为“1”,那么

读取的是引脚状态;如控制寄存器的值为“0”,则读取的是内部锁存器的值。后者可能会在‘读-修改-写’

指令中发生。

做为输出时,只能采用 CMOS 输出。控制寄存器对应 RAM 地址 13H、15H、17H、19H。

系统复位之后,这些输入/输出口会是高电平或浮空状态(由上拉电阻选项决定)。每一个输入/输出锁存

位都能用“SET [m].i”或“CLR [m].i”指令置位或清除(m=12H、14H、16H 或 18H)。

有些指令会先输入数据,然后进行输出操作。例如:“ SET [m].i”,“CLR [m].i”,“ CPL [m]”,

“CPLA[m]”这些指令会先将整个端口状态读入 CPU 中,接着执行所定义的运算(位操作),然后再将结果

写入锁存器或累加器中。

V

D D

P A 0 ~ P A 2

P A 3 / P F D

P A 4 / T M R

P A 5 / I N T

P A 6 , P A 7

P B 0 / A N 0 ~ P B 7 / A N 7

P C 0 ~ P C 5

P D 0 / P W M 0

P D 1 / P W M 1

Rev. 1.70 16 2004-09-21

HT46R23/HT46C23

PA 的每一个口都具有唤醒系统的能力。PC 的高 3 位和 PD 的高 6 位没有实际的物理结构;读取这些

位会返回“0”,而写入则是一个空操作。

所有的输入/输出口都有上拉电阻选项。一旦选择了上拉电阻选项,输入/输出口就加了上拉电阻。如

果不选择上拉电阻,必须注意在输入模式下,输入/输出口会产生浮空状态。

PA3 与 PFD 共用引脚,如果选择 PFD 功能,则 PA3 在输出模式时的输出信号将是由定时/计数器的溢

出信号产生的 PFD 信号,而在输入模式始终保持其原来的功能。一旦选择 PFD 功能,PFD 的输出信号只

受 PA3 数据寄存器控制。向 PA 3 数据寄存器写入“1”,则输出 PFD 信号;向 PA 3 数据寄存器写入“0”,

则 PA3 输出为“0”。 PA3 的输入/输出功能如下所示:

I/O

模式

PA3

注:PFD 的输出频率是定时/计数器溢出频率的 1/2

PA5 、PA4 口分别与

INT

PB 口可以用做 A/D 转换输入,A/D 转换功能将在下面说明。PD0/PD1 与 PWM0/PWM1 共用引脚。如

果选择 PWM 功能,则 PD0/PD1 口会有 PWM 信号输出(PD0/PD1 为输出模式)。向 PD0/PD1 数据寄存器写

入“1”,则输出 PWM 信号;向 PD0/PD1 数据寄存器写入“0”,则 PD0 输出为“0”。PD0 的 I/O 输入/输

出如下所示:

I/O 模式 I/P(正常) O/P(正常) I/P(PWM) O/P(PWM)

PD0

PD1

建议用软件将未使用和没有外接的输入/输出口设置为输出模式,以防止这些端口在输入浮空时增加系

统的功耗。

PWM

HT46x23 有 2 个通道(6+2)/(7+1)位的 PWM 输出(由掩膜选项决定),与 PD0/PD1 共用引脚。PWM 通道

由数据寄存器 PWM0(1AH)和 PWM1(1BH)来控制输出。PWM 计数器的时钟来源为系统时钟(f

有 2 个 8 位寄存器。PWM 的输出波形如图所示。一旦 PD0/PD1 选择为 PWM 输出,并且 PD0/PD1 为输出

模式(PDC.0/PDC.1=“0”),则 向 PD0/PD1 寄存器写“1”能够产生 PWM 输出,向 PD0/PD1 寄存器写“0”

会使 PD0/PD1 输出保持为“0”。

f

/ 2

S Y S

I/P

(正常)

O/P

(正常)

I/P

(PFD)

逻辑输入 逻辑输出 逻辑输入

、TMR 共用引脚。

逻辑输入 逻辑输出 逻辑输入

O/P

(PFD)

PFD

(定时/计数器开启)

PWM0

PWM1

)。PWM

SYS

[ P W M ] = 1 0 0

P W M

[ P W M ] = 1 0 1

P W M

[ P W M ] = 1 0 2

P W M

[ P W M ] = 1 0 3

P W M

2 5 / 6 4

2 6 / 6 4

2 6 / 6 4

2 6 / 6 4

P W M m o d u l a t i o n p e r i o d : 6 4 / f

M o d u l a t i o n c y c l e 0

2 5 / 6 4 2 5 / 6 4 2 5 / 6 4

2 5 / 6 4

2 6 / 6 4

2 6 / 6 4

S Y S

M o d u l a t i o n c y c l e 1 M o d u l a t i o n c y c l e 2 M o d u l a t i o n c y c l e 3 M o d u l a t i o n c y c l e 0

P W M c y c l e : 2 5 6 / f

2 5 / 6 4

2 5 / 6 4

2 6 / 6 4 2 5 / 6 4

S Y S

(6+2)位模式 PWM

2 5 / 6 4

2 5 / 6 4

2 5 / 6 4

2 6 / 6 4

2 6 / 6 4

2 6 / 6 4

在(6+2)位 PWM 模式中,一个 PWM 周期被分为四个调制周期(调制周期 0~调制周期 3),每个调制周

Rev. 1.70 17 2004-09-21

HT46R23/HT46C23

+

+

期有 64 个 PWM 输入时钟。在(6+2)位 PWM 模式中,PWM 寄存器被分为 2 个部分。第一部分是直流分量,

由 PWM.7~PWM.2 控制;第二部分是交流分量,由 PWM.1~PWM.0 控制。

在(6+2)位 PWM 模式中,每个调制周期的占空比见下表:

参数 AC(0~3) 占空比

1DC

64

DC

64

5 0 / 1 2 8

5 1 / 1 2 8

5 1 / 1 2 8

5 2 / 1 2 8

f

/ 2

S Y S

[ P W M ] = 1 0 0

P W M

[ P W M ] = 1 0 1

P W M

[ P W M ] = 1 0 2

P W M

[ P W M ] = 1 0 3

P W M

调制周期 i

(i=0~3)

5 0 / 1 2 8

5 1 / 1 2 8

5 1 / 1 2 8

5 2 / 1 2 8

P W M m o d u l a t i o n p e r i o d : 1 2 8 / f

i<AC

i≥AC

5 0 / 1 2 8

5 0 / 1 2 8

5 1 / 1 2 8

5 1 / 1 2 8

S Y S

M o d u l a t i o n c y c l e 0

P W M c y c l e : 2 5 6 / f

S Y S

M o d u l a t i o n c y c l e 1 M o d u l a t i o n c y c l e 0

(7+1)位模式 PWM

在(7+1)位 PWM 模式中,一个 PWM 周期被分为两个调制周期(调制周期 0~调制周期 1),每个调制周

期有 128 个 PWM 输入时钟。在(7+1)位 PWM 模式中,PWM 寄存器被分为 2 个部分。第一部分是直流分

量,由 PWM.7~PWM.1 控制;第二部分是交流分量,由 PWM.0 控制。

在(7+1)位 PWM 模式中,每个调制周期的占空比见下表:

参数 AC(0~1) 占空比

1DC

调制周期 i

(i=0~1)

i<AC

i≥AC

128

DC

128

PWM 的调制频率、周期频率和占空比的关系总结如下:

PWM 调制频率 PWM 周期频率 PWM 占空比

f

/64(6+2 模式)

SYS

/128(7+1 模式)

f

SYS

/256 [PWM]/256

f

SYS

A/D 转换

HT46x23 有 8 个通道、10 位解析度(9 位精度)的 A/D 转换器。其参考电压为 VDD。与 A/D 转换有关

的寄存器有 4 个:ADRL(24H)、ADRH(25H)、ADCR(26H)和 ACSR(27H)。ADRH 和 ADRL 是 A/D 转换结

果的高字节和低字节寄存器,是只读寄存器。当完成 A/D 转换后,可从 ADRH 和 ADRL 读取 A/D 转换结

果。ADCR 是 A/D 转换控制寄存器,用来定义 A/D 通道数量、模拟输入通道选择、A/D 转换开始控制和

完成标志。如果要进行 A/D 转换,要先定义好 PB 口的设置,选择转换的模拟通道,然后给 START 控制

位一个上升沿信号和一个下降沿信号(0→1→0)。完成 A/D 转换后,

位会被清除,并且产生 A/D 转换

EOC

中断(如果 A/D 转换允许)。ACSR 是 A/D 时钟控制寄存器,用来选择 A/D 的时钟来源。

Rev. 1.70 18 2004-09-21

HT46R23/HT46C23

符号(ACSR) 位 功能

选择 A/D 转换时钟源:

ADCS0

ADCS1

—

2~6

TEST 7

A/D 转换控制寄存器用来控制 A/D 转换。ADCR 的第 2~0 位用来选择模拟输入通道,总共有 8 个通道

可以选择。ADCR 的第 5~3 位用来设置 PB 的工作模式,PB 可以做为模拟输入通道,或是数字输入/输出

口,由这 3 位来决定。如果 PB 选择为模拟输入,则其输入/输出功能和上拉电阻将失效,而 A/D 转换电路

会被使能。

位(ADCR 的第 6 位)是 A/D 转换结束标志位。通过检测这个标志位可以知道 A/D 转换是否

EOC

结束。ADCR 的 START 位用来开启 A/D 转换,给 START 位一个上升沿信号和一个下降沿信号可以开始

A/D 转换。为了确保 A/D 转换顺利完成,START 位应保持为“0”,直到

信号)。

符号(ADCR) 位 功能

ACS0

ACS1

ACS2

PCR0

PCR1

PCR2

EOC

START 7

ACS2 ACS1 ACS0

PCR2 PCR1 PCR0 7 6 5 4 3 2 1 0

0 0 0 PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0

0 0 1 PB7 PB6 PB5 PB4 PB3 PB2 PB1 A0

0 1 0 PB7 PB6 PB5 PB4 PB3 PB2 A1 A0

0 1 1 PB7 PB6 PB5 PB4 PB3 A2 A1 A0

1 0 0 PB7 PB6 PB5 PB4 A3 A2 A1 A0

1 0 1 PB7 PB6 PB5 A4 A3 A2 A1 A0

1 1 0 PB7 PB6 A5 A4 A3 A2 A1 A0

1 1 1 A7 A6 A5 A4 A3 A2 A1 A0

00=系统时钟/2

0

01=系统时钟/8

1

10=系统时钟/32

11=未定义

未用,读出为“0”

只做为内部测试用

ACSR 寄存器

EOC

0

1

选择模拟输入通道

2

定义 PB 口的设置

3

4

如果 PCR0、PCR1 和 PCR2 都为 0,则 A/D 转换电

5

路被关闭以减小功耗

6

A/D 转换结束标志(0:A/D 转换结束)

A/D 转换启始控制位

0→1→0:开始;

0→1:A/D 转换复位

ADCR 寄存器

模拟通道

0 0 0 A0

0 0 1 A1

0 1 0 A2

0 1 1 A3

1 0 0 A4

1 0 1 A5

1 1 0 A6

1 1 1 A7

模拟输入通道选择

PB 口的设置

位变为“0”(A/D 转换完成

Rev. 1.70 19 2004-09-21

HT46R23/HT46C23

ACSR 的第 7 位是内部测试用的,用户不能使用。ACSR 的第 1 位和第 0 位用来选择 A/D 转换的时钟

来源。

当 A/D 转换完成时,A/D 中断标志被置位。当 START 标志由“0”置为“1”时,

寄存器 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

ADRL D1 D0

— — — — — —

ADRH D9 D8 D7 D6 D5 D4 D3 D2

注:D0~D8 是 A/D 转换结果的低位~高位

M i n i m u m o n e i n s t r u c t i o n c y c l e n e e d e d

S T A R T

也置为“1”。

EOC

E O C B

P C R 2 ~ P C R 0

A C S 2 ~ A C S 0

0 0 0 B

0 0 0 B

P o w e r - o n

R e s e t

R e s e t A / D

c o n v e r t e r

1 : D e f i n e P B c o n f i g u r a t i o n

2 : S e l e c t a n a l o g c h a n n e l

A / D c l o c k m u s t b e f

N o t e :

A / D s a m p l i n g t i m e

3 2 t

A D

1 0 0 B

0 1 0 B

S t a r t o f A / D

c o n v e r s i o n

7 6 t

A / D c o n v e r s i o n t i m e

/ 2 , f

S Y S

/ 8 o r f

S Y S

E n d o f A / D

c o n v e r s i o n

A D

/ 3 2

S Y S

R e s e t A / D

c o n v e r t e r

A / D s a m p l i n g t i m e

3 2 t

A D

1 0 0 B

0 0 0 B

S t a r t o f A / D

c o n v e r s i o n

7 6 t

A / D c o n v e r s i o n t i m e

A D

E n d o f A / D

c o n v e r s i o n

0 0 0 B

1 . P B p o r t s e t u p a s I / O s

2 . A / D c o n v e r t e r i s p o w e r e d o f f

t o r e d u c e p o w e r c o n s u m p t i o n

d o n ' t c a r e

A/D 转换时序

下面举两个例子说明如何启动和实现 A/D 转换。第一个例子不断扫描 ADCR 寄存器的

A/D 转换是否完成;而第二个例子直接用中断的方法来判断 A/D 转换是否完成。

例 1:通过扫描

位判断 A/D 转换是否完成。

EOC

clr INTC0.3 ; 在中断控制寄存器中禁止A/D中断

mov a,00100000B

mov ADCR,a ; 在ADCR寄存器中设置Port PB0~PB3做为A/D输入

; 设置AN0进行A/D转换

mov a,00000001B

mov ACSR,a ; 设置ACSR寄存器,选择f

/8做为A/D转换时钟

SYS

Start_conversion:

clr ADCR.7

set ADCR.7 ; A/D转换复位

clr ADCR.7 ; 开始A/D转换

Polling_EOC:

sz ADCR.6 ; 扫描ADCR寄存器的

位判断A/D转换是否完成

EOC

jmp polling_EOC ; 继续扫描

mov a,ADRH ; 从ADRH寄存器读取A/D转换结果的高位字节

mov adrh_buffer,a ; 将结果放入用户定义的寄存器中

mov a,ADRL ; 从ADRL寄存器读取A/D转换结果的低位字节

mov adrl_buffer,a ; 将结果放入用户定义的寄存器中

:

EOC

位来判断

Rev. 1.70 20 2004-09-21

:

jmp start_conversion ; 开始下一次A/D转换

例 2:用中断方法判断 A/D 转换是否完成。

set INTC0.3 ; 在中断控制寄存器中设置A/D中断允许

mov a,00100000B

mov ADCR,a ; 在ADCR寄存器中设置Port PB0~PB3做为A/D输入

; 设置AN0进行A/D转换

mov a,00000001B

mov ACSR,a ; 设置ACSR寄存器,选择f

SYS

start_conversion:

clr .7

set ADCR.7 ; A/D转换复位

clr ADCR.7 ; 开始A/D转换

:

:

; 中断服务子程序

EOC_service routine:

mov a_buffer,a ; 将ACC保存到用户定义的寄存器中

mov a,ADRH ; 从ADRH寄存器读取A/D转换结果的高位字节

mov adrh_buffer,a ; 将结果放入用户定义的寄存器中

mov a,ADRL ; 从ADRL寄存器读取A/D转换结果的低位字节

mov adrl_buffer,a ; 将结果放入用户定义的寄存器中

clr ADCR.7

set ADCR.7 ; A/D转换复位

clr ADCR.7 ; 开始A/D转换

mov a,a_buffer ; 将ACC从暂存器中读出

reti

低电压复位—LVR

为了监控器件的工作电压,HT46x23 提供低电压复位功能。如果器

件的工作电压在 0.9V~V

之间,例如电池电压的变化,那么 LV R 会

LVR

自动使器件产生内部复位。

LVR 功能说明如下:

· 低电压

(0.9V~V

)的状态必须持续 1ms 以上。如果低电压的状态

LVR

没有持续 1ms 以上,那么 LVR 会忽视它而不去执行复位功能。

· LV R 通过与外部

V

之间的关系如下所示:

LVR

信号的“或”的功能来执行系统复位。VDD与

RES

HT46R23/HT46C23

/8做为A/D转换时钟

5 . 5 V

3 . 0 V

注:V

时,使得芯片正常运行的电压值

V

V

D D

O P R

5 . 5 V

V

L V R

2 . 2 V

0 . 9 V

是在系统时钟为 4MHz

OPR

Rev. 1.70 21 2004-09-21

HT46R23/HT46C23

注:*1:要保证系统振荡器起振并稳定运行,在系统进入正常运行以前,SST 提供额外的 1024 个系统时钟周期的延迟。

*2:因为低电压状态必须保持 1ms 以上,因此进入复位模式就要有 1ms 的延迟。

2

C 总线接口

I

HT46x23 提供 I

2

C 总线接口,I2C 总线是双向两线结构,数据线和时钟线分别为 SDA 和 SCL。SDA 和

SCL 是 NMOS 开漏输出,使用时必须外接上拉电阻。

2

I

C 总线有两种数据传输方式,一种为从器件发送模式(slave transmit mode),另一种为从器件接收模式

(slave receive mode)。有四个与 I

2

C 总线相关寄存器:HADR([20H])、HCR([21H])、HSR([22H])、HDR([23H])。

HADR 寄存器用来存放从器件地址,如果主控制器发送的调用地址与该从器件地址匹配,则表明该器件被

选中。HCR 是 I

接收模式。HSR 是 I

2

C 总线控制寄存器,用来控制 I2C 总线功能的开/关状态和 I2C 总线是工作于发送模式还是

2

C 总线状态寄存器,该寄存器反映了 I2C 总线的工作状态。HDR 是数据输入/输出寄

存器,发送和接收的数据都必须经过 HDR 寄存器。

Bit7~Bit1 Bit0

从地址 —

HADR 寄存器

注:“—”为未定义

标号(HCR) 位 功能

HEN 7

—

—

HTX 4

TXAK 3

—

打开/关闭I

6

未用,读出为“0”

5

未用,读出为“0”

定义发送/接收模式(0=接收模式;1=发送模式)

打开/关闭应答信号(0=应答;1=不应答)

0~2

未用,读出为“0”

2

C总线(0=关闭;1=打开)

HCR 寄存器

标号(HCR) 位 功能

HCF 7

HAAS 6

HBB 5

—

HCF在数据开始传送时清“0”;HCF被置“1”表示8位

数据已传送完毕。

HAAS在调用地址匹配时被置“1”,同时发生I2C 总线

中断且HIF被置位。

HBB在I2C总线忙时被置位;而当I2C总线空闲时,该位

将被清“0”。

4

未用,读出为“0”

Rev. 1.70 22 2004-09-21

HT46R23/HT46C23

—

SRW 2

3

未用,读出为“0”

当SRW被置“1”,表示主控制器要从I

2

C总线读数据,从

器件须将数据发送到主控制器;当SRW被清“0”,表示

主控制器要写数据到I2C总线,从器件必须从主控制器接

收数据。

—

RXAK 0

1

未用,读出为“0”

当主控制器收到8位数据,并发出应答信号时,RXAK被

清“0”;如果没有应答信号,则RXAK被置“1”。

HSR 寄存器

2

I

C 总线控制寄存器包括 3 位:HEN、HTX 和 TXAK。HEN 控制 I2C 总线打开/关闭,如果数据想通

2

过 I

C 总线传送,该位就必须置“1”。HTX 定义 I2C 总线是用于发送模式还是接收模式,如果要用于发送

模式,该位就必须置“1”。TXAK 定义应答信号,当器件接收到 8 位数据后,在第 9 个时钟时,器件将该

位送到 I

在数据传送结束后被置“1”。HAAS 当从器件地址匹配时被置“1”,同 时 I

如果中断允许且堆栈未满,则程序会跳到地址 10H 开始执行。写数据到 I

HAAS;如果地址不匹配,HAAS 被清“0”。HBB 置“ 1”表示 I

HBB 清“0” 表示 I

2

C 总线上,如果要继续接收下一个数据,在接收数据前该位必须清“0”。

2

I

C 总线状态寄存器包括 5 位:HCF、HAAS、HBB、SRW 和 RXAK。HCF 在开始传送数据时被清“0”;

2

C 总线中断请求标志被置“1”;

2

C 总线控制寄存器可以清除

2

C 总线忙,即系统检测到“START”信号;

2

C 总线空闲,即系统检测到“STOP”信号,此时 I2C 总线空闲。SRW 表示调用地址

匹配时,器件的读/写状态。当 HAAS 被置“1”,可以通过检测 SRW 来确定器件是工作在发送模式还是接

收模式。当 SRW 被置“1”,表示主控制器要从 I

器件为发送模式;当 SRW 被清“0”,表示主控制器要写数据到 I

2

C 总线读数据,从器件必须将数据写到 I2C 总线,即从

2

C 总线,从器件要从总线读取数据,即

从器件为接收模式。RXAK 清“0”,表示接收到一个应答信号。在发送模式,发送器件通过检测 RXAK

以确定接收器件是否要接收下一个数据,发送器件会一直写数据到 I

2

C 总线直到 RXAK 置“1”,同时发

送器件释放 SDA 线,这样主控制器可以发送 STOP 信号来释放总线。

HADR 寄存器的第 7~1 位定义从器件地址,开始数据传送时,主控制器通过发送从器件地址来选择器

件;第 0 位没有用,不需要定义。一旦 I

2

C 总线接上出现起始信号,所有的从器件都会接收连续的 8 位数

据,该数据的前 7 位是从器件地址,高位在前,低位在后。如果从器件地址匹配,系统会置位 HAAS,同

时产生 I

2

C 总线中断。进入中断服务程序后,系统要检测 HAAS 位,以确定 I2C 总线中断是来自从器件地

址匹配,还是来自 8 位数据传送完毕。8 位数据的最后一位是读/写控制位,该位会反映到 SRW。从器件通

过检测 SRW 以确定主控制器是要发送数据还是接收数据,并确定自己是作发送器还是接收器。

HDR 寄存器是 I

在接收数据前,要先从 HDR 虚拟读取数据。从 I

线开始传送数据前,需要先初始化 I

1:向 I

2:置位 I

3:置位 I

2

C 总线地址寄存器(HADR)写入从器件地址。

2

C 总线控制寄存器(HCR)的 HEN 位,以打开 I2C 总线。

2

C 总线中断控制寄存器 1(INTC1)的 EHI 位,以允许 I2C 总线中断。

2

C 总线的数据输入/输出寄存器。在发送数据前,要先将发送的数据写到 HDR 寄存器;

2

C 总线发送或接收数据都必须经过 HDR 寄存器。在 I2C 总

2

C 总线,在初始化 I2C 总线时,下面几点注意

起始信号

2

起始信号只能由主控制器产生。总线上的其它器件必须侦测起始信号以设定 I

C 总线的忙标志位

(HBB)。起始信号是指在 SCL 为高时,SDA 发生电平从高到低的变化。

从器件地址

发送起始信号后,主控制器必须发送从器件地址以选择要进行数据传输的从器件。所有在 I

2

C 总线上

的从器件都会接收到这个从器件地址(7 位),并与各自内部的从器件地址进行比较。如果从器件地址匹配,

该从器件会产生一个中断,并将接下来的一位数据(即第 8 位)保存到 SRW 位,并发出一个应答信号。当从

Rev. 1.70 23 2004-09-21

HT46R23/HT46C23

器件地址匹配时,还会置位状态标志(HAAS)。

在中断服务子程序中,通过检测 HAAS 位可以确定 I

位数据传送完毕。当是从器件地址匹配发生中断时,则器件必定是用于发送模式或接收模式,所以必须写

数据到 HDR 或从 HDR 虚拟读取数据以释放 SCL 口线。

SRW 位

SRW 表示主控制器是要从 I

2

C 总线上读取数据还是要将数据写到 I2C 总线上。从器件则通过检测该

位以确定自己是做为发送器还是接收器。SRW 置“1”,表示主控制器要从 I

数据写到 I

2

C 总线,即从器件做为发送器;SRW 清“0”,表示主控制器要写数据到 I2C 总线,从器件要从

总线读取数据,即从器件做为接收器。

应答位

当从器件地址匹配时,会发送一个应答信号。主控制器通过检测应答信号以判断从器件是否接接受了

调用。如果没有应答信号,主控制器必须发送停止(STOP)信号以结束通讯。当 I

位(HAAS)是高时,表示地址匹配,则从器件需检查 SRW,以确定自己是做为发送器还是做为接收器。

数据字节

在从器件发出应答信号后,就会进行数据传输,一个数据长度为 8 位,高位在前,低位在后。接收器

在接收到数据后会发出一个应答信号(“0”)以继续接收下一个数据。如果发送器没检测到应答信号,发送

器将释放 SDA 线,同时,主控制器将发出 STOP 信号以释放 I

中,发送器在发送数据之前必须将数据写到 HDR;接收器在接收数据之后必须从 HDR 读取数据。

接收应答位

当接收器想要继续接收下一个数据时,必须在第 9 个时钟发出应答信号(TXAK)。发送器检测应答信

号(RXAK)以是继续写数据到 I

2

C 总线,还是改变为接收模式并虚读 HDR 寄存器以释放 SDA 线,同时主

控制器发出停止信号。

2

C 总线中断是来自从器件地址匹配,还是来自 8

2

C 总线读数据,从器件必须将

2

C 总线状态寄存器的第 6

2

C 总线。所传送的数据存储在 HDR 寄存器

S t a r t

S C L

S D A

S C L

S D A

S = S t a r t ( 1 b i t )

S A = S l a v e A d d r e s s ( 7 b i t s )

S R = S R W b i t ( 1 b i t )

M = S l a v e d e v i c e s e n d a c k n o w l e d g e b i t ( 1 b i t )

D = D a t a ( 8 b i t s )

A = A C K ( R X A K b i t f o r t r a n s m i t t e r , T X A K b i t f o r r e c e i v e r 1 b i t )

P = S t o p ( 1 b i t )

S S A S R

1

1 0 1 0 0 1 00

M D A D A

0

S l a v e A d d r e s s

1

1

D a t a

0 1 0 1 0

S S A S R

S R W

M D A D A P

A C K

A C K S t o p

Rev. 1.70 24 2004-09-21

起始位 停止位

HT46R23/HT46C23

Rev. 1.70 25 2004-09-21

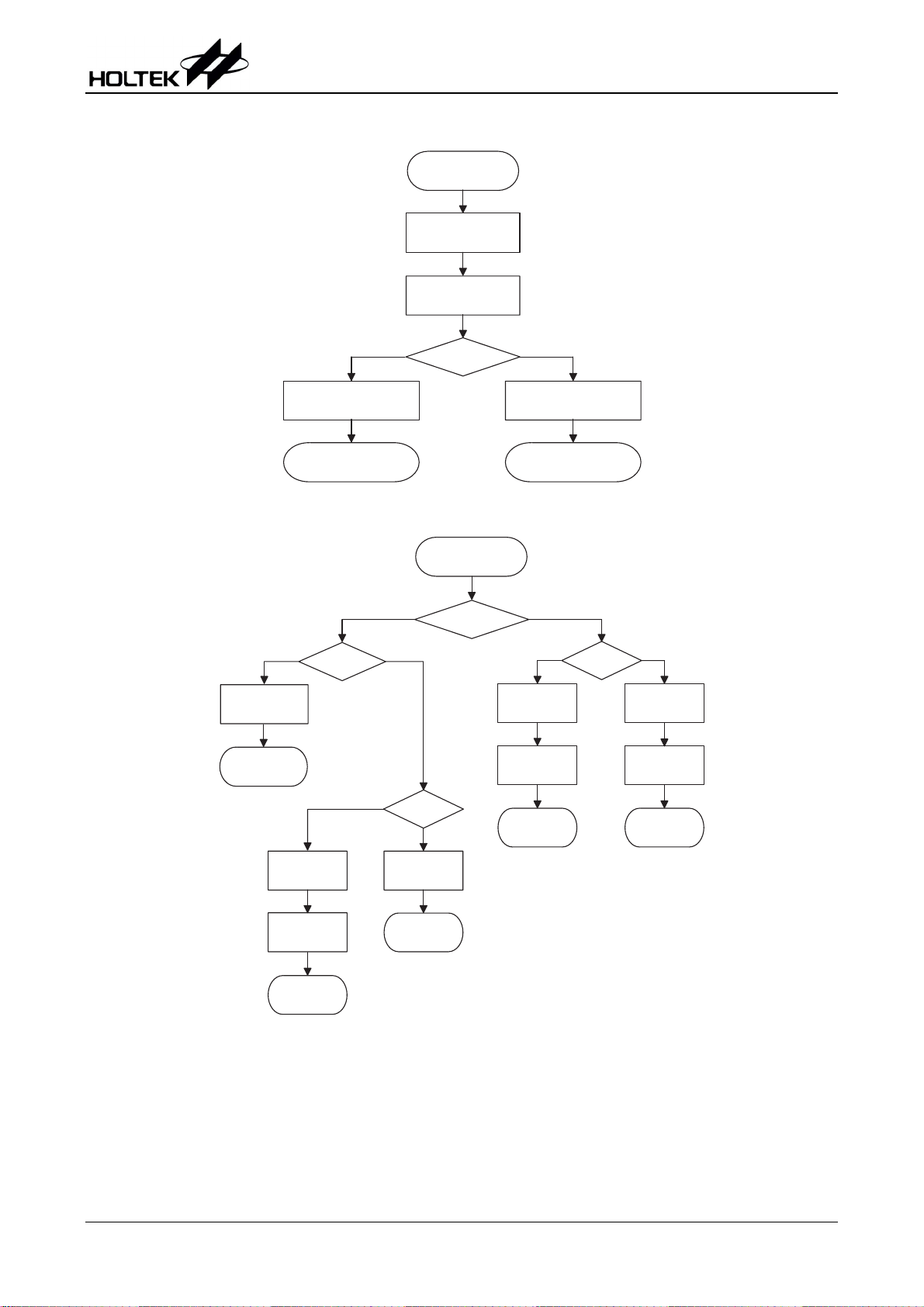

I2C 总线初始化程序流程图

HT46R23/HT46C23

S t a r t

W r i t e S l a v e

A d d r e s s t o H A D R

S E T H E N

I2C B u s

I n t e r r u p t = ?

E n a b l eD i s a b l e

2

C 总线中断服务程序流程图

I

R e a d f r o m H D R

R E T I

P o l l H I F t o d e c i d e

w h e n t o g o t o I

G o t o M a i n P r o g r a m

N o

C L R E H I

2

H T X = 1

?

C B u s I S R

N o

Y e s

Y e s

R X A K = 1

?

N o

S t a r t

H A A S = 1

?

S E T E H I

W a i t f o r I n t e r r u p t

G o t o M a i n P r o g r a m

Y e s

Y e s

S R W = 1

?

S E T H T X

W r i t e t o H D R

R E T I R E T I

N o

C L R H T X

C L R T X A K

D u m m y R e a d

F r o m H D R

C L R H T X

C L R T X A K

D u m m y R e a d

f r o m H D R

R E T I

W r i t e t o H D R

R E T I

Rev. 1.70 26 2004-09-21

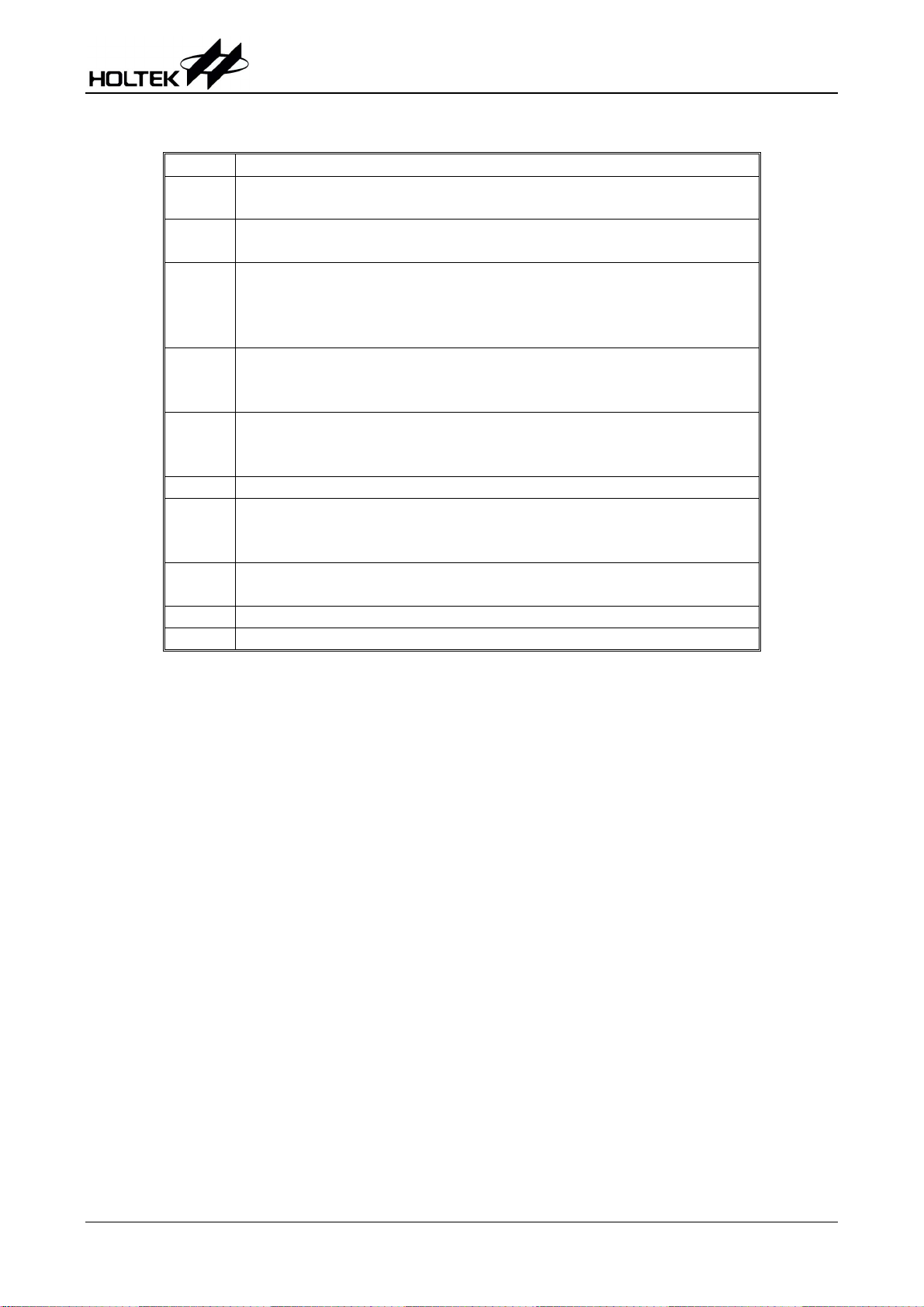

掩膜选项

下表列出了所有掩膜选项。所有选项必须正确定义,以保证统正常运行。

编号 选项

1

2

3

4

5

6

7

8

9

10

振荡类型选择。

该选项用来定义系统时钟来源为 RC 振荡还是晶体振荡。

WDT 时钟源选择。

有三种选择:内部 WDT 振荡、指令时钟或关闭。

清除 WDT 指令选择。

该选项用来定义清除 WDT 的指令条数。“1 条指令”表示“CLR WDT”

就能清除 WDT;“2 条指令”表示要同时使用“CLR WDT1”和“CLR

WDT2”才能清除 WDT。

唤醒选择。

该选项用来定义唤醒功能,外部输入/输出口(只有 PA )都具有将系统从

HALT 模式中唤醒的能力。

上拉选择。

该选项用来定义输入/输出口做为输入时,是否带有内部上拉电阻;

PA0 ~PA 7 可以按位定义。

PFD 选择:PA 3 是电平输出或 PFD 输出

PWM 选择:(7+1)或(6+2)模式

PD0:电平输出或 PWM 输出

PD1:电平输出或 PWM 输出

WDT 预分频选择。

有四种分频选择:2

低电压复位功能:打开/关闭

2

I

C 总线:打开/关闭

12、213、214、215

HT46R23/HT46C23

Rev. 1.70 27 2004-09-21

应用电路

V

D D

0 . 0 1mF *

V D D

1 0 0 k

W

0 . 1mF

1 0 k

O S C

C i r c u i t

S e e R i g h t S i d e

R E S

W

0 . 1mF *

V S S

O S C 1

O S C 2

H T 4 6 R 2 3 / H T 4 6 C 2 3

下表是不同晶体频率时,C1、C2 和 R1 的不同取值。

晶体或共振器 C1、C2 R1

4MHz 晶体 0pF 10kΩ

4MHz 共振器 10pF 12kΩ

3.58MHz 晶体 0pF 10kΩ

3.58MHz 共振器 25pF 10kΩ

2MHz 晶体和共振器 25pF 10kΩ

1MHz 晶体 35pF 27kΩ

480kHz 共振器 300pF 9.1kΩ

455kHz 共振器 300pF 10kΩ

429kHz 共振器 300pF 10kΩ

R1 的作用是在低电压的时候确保关闭振荡,此低电压值低于单片机的最低工作电压。需要注意的是如

果 LV R 使能,可以不加 R1。

注: 电阻和电容值选取的原则是使 VDD 保持稳定并在

“*”为了避免噪声干扰,连接

P A 0 ~ P A 2

P A 3 / P F D

P A 4 / T M R

P A 5 / I N T

P A 6 / S D A

P A 7 / S C L

P B 0 / A N 0

~

P B 7 / A N 7

P C 0 ~ P C 4

P D 0 / P W M 0

P D 1 / P W M 1

引脚的线请尽可能地短

RES

V

D D

4 7 0 p F

R

O S C

C 1

C 2

置为高以前把工作电压保持在允许的范围内。

RES

HT46R23/HT46C23

O S C 1

f

/ 4

S Y S

O S C 2

O S C 1

O S C 2

R 1

R C S y s t e m O s c i l l a t o r

< R

3 0 k

W

O S C

C r y s t a l S y s t e m O s c i l l a t o r

F o r t h e v a l u e s ,

s e e t a b l e b e l o w

O S C C i r c u i t

< 7 5 0 k

W

Rev. 1.70 28 2004-09-21

HT46R23/HT46C23

指令集摘要

助记符 说明 指令周期 影响标志位

算术运算

ADD A,[m]

ADDM A,[m]

ADD A,x

ADC A,[m]

ADCM A,[m]

SUB A,x

SUB A,[m]

SUBM A,[m]

SBC A,[m]

SBCM A,[m]

DAA [m]

ACC 与数据存储器相加,结果放入 ACC

ACC 与数据存储器相加,结果放入数据存储器

ACC 与立即数相加,结果放入 ACC

ACC 与数据存储器、进位标志相加,结果放入 ACC

ACC 与数据存储器、进位标志相加,结果放入数据存储器

ACC 与立即数相减,结果放入 ACC

ACC 与数据存储器相减,结果放入 ACC

ACC 与数据存储器相减,结果放入数据存储器

ACC 与数据存储器、进位标志相减,结果放入 ACC

ACC 与数据存储器、进位标志相减,结果放入数据存储器

将加法运算中放入 ACC 的值调整为十进制数,并将结果放

入数据存储器

逻辑运算

AND A,[m]

OR A,[m]

XOR A,[m]

ANDM A,[m]

ORM A,[m]

XORM A,[m]

AND A,x

OR A,x

XOR A,x

CPL [m]

CPLA [m]

ACC 与数据存储器做“与”运算,结果放入 ACC

ACC 与数据存储器做“或”运算,结果放入 ACC

ACC 与数据存储器做“异或”运算,结果放入 ACC

ACC 与数据存储器做“与”运算,结果放入数据存储器

ACC 与数据存储器做“或”运算,结果放入数据存储器

ACC 与数据存储器做“异或”运算,结果放入数据存储器

ACC 与立即数做“与”运算,结果放入 ACC

ACC 与立即数做“或”运算,结果放入 ACC

ACC 与立即数做“异或”运算,结果放入 ACC

对数据存储器取反,结果放入数据存储器

对数据存储器取反,结果放入 ACC

递增和递减

INCA [m]

INC [m]

DECA [m]

DEC [m]

递增数据存储器,结果放入 ACC

递增数据存储器,结果放入数据存储器

递减数据存储器,结果放入 ACC

递减数据存储器,结果放入数据存储器

移位

RRA [m]

RR [m]

RRCA [m]

RRC [m]

RLA [m]

RL [m]

RLCA [m]

RLC [m]

数据存储器右移一位,结果放入 ACC

数据存储器右移一位,结果放入数据存储器

带进位将数据存储器右移一位,结果放入 ACC

带进位将数据存储器右移一位,结果放入数据存储器

数据存储器左移一位,结果放入 ACC

数据存储器左移一位,结果放入数据存储器

带进位将数据存储器左移一位,结果放入 ACC

带进位将数据存储器左移一位,结果放入数据存储器

数据传送

MOV A,[m]

MOV [m],A

MOV A,x

将数据存储器送至 ACC

将 ACC 送至数据存储器

将立即数送至 ACC

位运算

CLR [m].i

SET [m].i

清除数据存储器的位

置位数据存储器的位

1 Z,C,AC,OV

(1)

Z,C,AC,OV

1

1 Z,C,AC,OV

1 Z,C,AC,OV

(1)

Z,C,AC,OV

1

1 Z,C,AC,OV

1 Z,C,AC,OV

(1)

Z,C,AC,OV

1

1 Z,C,AC,OV

(1)

Z,C,AC,OV

1

(1)

C

1

1 Z

1 Z

1 Z

(1)

Z

1

(1)

Z

1

(1)

Z

1

1 Z

1 Z

1 Z

(1)

Z

1

1 Z

1 Z

(1)

Z

1

1 Z

(1)

Z

1

1

(1)

1

无

无

1 C

(1)

C

1

1

(1)

1

无

无

1 C

(1)

C

1

1

(1)

1

1

(1)

1

(1)

1

无

无

无

无

无

Rev. 1.70 29 2004-09-21

HT46R23/HT46C23

助记符 说明 指令周期 影响标志位

转移

JMP addr

SZ [m]

SZA [m]

SZ [m].i

SNZ [m].i

SIZ [m]

SDZ [m]

SIZA [m]

SDZA [m]

CALL addr

RET

RET A,x

RETI

查表

TABRDC [m]

TABRDL [m]

其它指令

NOP

CLR [m]

SET [m]

CLR WDT

CLR WDT1

CLR WDT2

SWAP [m]

SWAPA [m]

HALT

注: x:立即数

m:数据存储器地址

A:累加器

i:第 0~7 位

addr:程序存储器地址

√:影响标志位

—:不影响标志位

(1)

:如果数据是加载到 PCL 寄存器,则指令执行周期会被延长一个指令周期(四个系统时钟)。

(2)

:如果满足跳跃条件,则指令执行周期会被延长一个指令周期(四个系统时钟);否则指令执行周期不会被延长。

(3):(1)和(2)

(4)

:如果执行 CLR WDT1 或 CLR WDT2 指令后,看门狗定时器被清除,则会影响 TO 和 PDF 标志位;否则不会

影响 TO 和 PDF 标志位。

无条件跳转

如果数据存储器为零,则跳过下一条指令

数据存储器送至 ACC,如果内容为零,则跳过下一条指令

如果数据存储器的第 i 位为零,则跳过下一条指令

如果数据存储器的第 i 位不为零,则跳过下一条指令

递增数据存储器,如果结果为零,则跳过下一条指令

递减数据存储器,如果结果为零,则跳过下一条指令

递增数据存储器,将结果放入 ACC,如果结果为零,则跳

过下一条指令

递减数据存储器,将结果放入 ACC,如果结果为零,则跳

过下一条指令

子程序调用

从子程序返回

从子程序返回,并将立即数放入 ACC

从中断返回

读取当前页的 ROM 内容,并送至数据存储器和 TBLH

读取最后页的 ROM 内容,并送至数据存储器和 TBLH

空指令

清除数据存储器

置位数据存储器

清除看门狗定时器

预清除看门狗定时器

预清除看门狗定时器

交换数据存储器的高低字节,结果放入数据存储器

交换数据存储器的高低字节,结果放入 ACC

进入暂停模式

2

(2)

1

(2)

1

(2)

1

(2)

1

(3)

1

(3)

1

(2)

1

(2)

1

2

2

2

2

(1)

2

(1)

2

1

(1)

1

(1)

1

无

无

无

无

无

无

无

无

无

无

无

无

无

无

无

无

无

无

1 TO,PDF

1 TO

1 TO

(1)

1

1

(4)

(4)

,PDF

,PDF

无

无

(4)

(4)

1 TO,PDF

Rev. 1.70 30 2004-09-21

HT46R23/HT46C23

ADC A, [m] 累加器与数据存储器、进位标志相加,结果放入累加器

说明: 本指令把累加器、数据存储器值以及进位标志相加,结果存放到累加器。

运算过程: ACCÅACC+[m]+C

影响标志位

TO PDF OV Z AC C

— — √ √ √ √

ADCM A, [m] 累加器与数据存储器、进位标志相加,结果放入数据存储器

说明: 本指令把累加器、数据存储器值以及进位标志相加,结果存放到存储器。

运算过程: [m]ÅACC+[m]+C

影响标志位

TO PDF OV Z AC C

— — √ √ √ √

ADD A, [m] 累加器与数据存储器相加,结果放入累加器

说明: 本指令把累加器、数据存储器值相加,结果存放到累加器。

运算过程: ACCÅACC+[m]

影响标志位

TO PDF OV Z AC C

— — √ √ √ √

ADD A, x 累加器与立即数相加,结果放入累加器

说明: 本指令把累加器值和立即数相加,结果存放到累加器。

运算过程: ACCÅACC+x

影响标志位

TO PDF OV Z AC C

— — √ √ √ √

ADDM A, [m] 累加器与数据存储器相加,结果放入数据存储器

说明: 本指令把累加器、数据存储器值相加,结果存放到数据存储器。

运算过程: [m]ÅACC+[m]

影响标志位

TO PDF OV Z AC C

— — √ √ √ √

AND A, [m] 累加器与数据存储器做“与”运算,结果放入累加器

说明: 本指令把累加器值、数据存储器值做逻辑与,结果存放到累加器。

运算过程: ACCÅACC “AND” [m]

影响标志位

TO PDF OV Z AC C

— — — √ — —

Rev. 1.70 31 2004-09-21

HT46R23/HT46C23

AND A, x 累加器与立即数做“与”运算,结果放入累加器

说明: 本指令把累加器值、立即数做逻辑与,结果存放到累加器。

运算过程: ACCÅACC “AND” x

影响标志位

TO PDF OV Z AC C

— — — √ — —

ANDM A, [m] 累加器与数据存储器做“与”运算,结果放入数据存储器

说明: 本指令把累加器值、数据存储器值做逻辑与,结果存放到数据存储器。

运算过程: ACCÅACC “AND” [m]

影响标志位

TO PDF OV Z AC C

— — — √ — —

CALL addr 子程序调用

说明: 本指令直接调用地址所在处的子程序,此时程序计数器加一,将此程序计数器值存到堆

栈寄存器中,再将子程序所在处的地址存放到程序计数器中。

运算过程: StackÅPC+1

PC Å addr

影响标志位

TO PDF OV Z AC C

— — — — — —

CLR [m] 清除数据存储器

说明: 本指令将数据存储器内的数值清零。

运算过程: [m] Å00H

影响标志位

TO PDF OV Z AC C

— — — — — —

CLR [m] . i 将数据存储器的第 i 位清“0”

说明: 本指令将数据存储器内第 i 位值清零。

运算过程: [m].i Å0

影响标志位

TO PDF OV Z AC C

— — — — — —

CLR WDT 清除看门狗定时器

说明: 本指令清除 WDT 计数器(从 0 开始重新计数),暂停标志位(PDF)和看门狗溢出标志位(TO)

也被清零。

运算过程: WDT Å 00H

PDF&TO Å 0

影响标志位

TO PDF OV Z AC C

0 0

— — — —

Rev. 1.70 32 2004-09-21

HT46R23/HT46C23

m

m

CLR WDT1 预清除看门狗定时器

说明: 必须搭配 CLR WDT2 一起使用,才可清除 WDT 计时器(从 0 开始重新计数)。当程序只

执行过该指令,没有执行 CLR WDT2 时,系统只会不会将暂停标志位(PDF)和计数溢出

位(TO)清零,PDF 与 TO 保留原状态不变。

运算过程: WDT Å 00H*

PDF&TO Å 0*

影响标志位

TO PDF OV Z AC C

0* 0*

CLR WDT2 预清除看门狗定时器

说明: 必须搭配 CLR WDT1 一起使用,才可清除 WDT 计时器(从 0 开始重新计数)。当程序只

执行过该指令,没有执行 CLR WDT1 时,系统只会不会将暂停标志位(PDF)和计数溢出

位(TO)清零,PDF 与 TO 保留原状态不变。

运算过程: WDT Å 00H*

PDF&TO Å 0*

影响标志位

TO PDF OV Z AC C

0* 0*

CPL [m] 对数据存储器取反,结果放入数据存储器

说明: 本指令是将数据存储器内保存的数值取反。

运算过程: [m] Å [

影响标志位

CPLA [m] 对数据存储器取反,结果放入累加器

说明: 本指令是将数据存储器内保存的值取反后,结果存放在累加器中。

运算过程: ACC Å [

影响标志位

]

TO PDF OV Z AC C

— — — √ — —

]

TO PDF OV Z AC C

— — — √ — —

— — — —

— — — —

Rev. 1.70 33 2004-09-21

HT46R23/HT46C23

DAA [m] 将加法运算后放入累加器的值调整为十进制数,并将结果放入数据存储器

说明 本指令将累加器高低四位分别调整为 BCD 码。如果低四位的值大于“9”或 AC=1,那

么 BCD 调整就执行对原值加“6”,并且内部进位标志 AC1= AC ,即 AC 求反;否则原

值保持不变。如果高四位的值大于“9”或 C=1,那么 BCD 调整就执行对原值加“6”

再加 AC1,并把 C 置位;否则 BCD 调整就执行对原值加 AC1,C 的值保持不变。结果

存放到数据存储器中,只有进位标志位(C)受影响。

操作 如果 ACC.3~ACC.0 > 9 或 AC=1

那么 [m].3~[m].0 Å(ACC.3~ACC.0 )+6,AC1=

否则 [m].3~[m].0 Å(ACC.3~ACC.0 ),AC1=0

并且

如果 ACC.7~ACC.4+AC1 > 9 或 C=1

那么 [m].7~[m].4 Å(ACC.7~ACC.4 )+6+ AC1,C=1

否则 [m].7~[m].4 Å(ACC.7~ACC.4 )+ AC1,C=C

影响标志位

TO PDF OV Z AC C

— — — — — √

DEC [m] 数据存储器的内容减 1,结果放入数据存储器

说明: 本指令将数据存储器内的数值减一再放回数据存储器。

运算过程: [m] Å [m]-1

影响标志位

TO PDF OV Z AC C

— — — √ — —

DECA [m] 数据存储器的内容减 1,结果放入累加器

说明: 本指令将存储器内的数值减一,再放到累加器。

运算过程: ACC Å [m]-1

影响标志位

TO PDF OV Z AC C

— — — √ — —

HALT 进入暂停模式

说明: 本指令终止程序执行并关掉系统时钟,RAM 和寄存器内的数值保持原状态,WDT 计数

器清“0”,暂停标志位(PDF)被设为 1, WDT 计数溢出位(TO)被清为 0。

运算过程: PC Å PC+1

PDF Å 1

TO Å 0

影响标志位

TO PDF OV Z AC C

0 1

— — — —

AC

Rev. 1.70 34 2004-09-21

INC [m] 数据存储器的内容加 1,结果放入数据存储器

说明: 本指令将数据存储器内的数值加一,结果放回数据存储器。

运算过程: [m] Å [m]+1

影响标志位

TO PDF OV Z AC C

— — — √ — —

INCA [m] 数据存储器的内容加 1,结果放入数据存储器

说明: 本指令是将存储器内的数值加一,结果放到累加器。

运算过程: ACC Å [m]+1

影响标志位

TO PDF OV Z AC C

— — — √ — —

JMP addr 无条件跳转

说明: 本指令是将要跳到的目的地直接放到程序计数器内。

运算过程: PC Å addr

影响标志位

TO PDF OV Z AC C

— — — — — —

MOV A, [m] 将数据存储器送至累加器

说明: 本指令是将数据存储器内的数值送到累加器内。

运算过程: ACC Å [m]

影响标志位

TO PDF OV Z AC C

— — — — — —

MOV A, x 将立即数送至累加器

说明: 本指令是将立即数送到累加器内。

运算过程: ACC Å x

影响标志位

TO PDF OV Z AC C

— — — — — —

MOV [m], A 将累加器送至数据存储器

说明: 本指令是将累加器值送到数据存储器内。

运算过程: [m] Å ACC

影响标志位

TO PDF OV Z AC C

— — — — — —

HT46R23/HT46C23

Rev. 1.70 35 2004-09-21

HT46R23/HT46C23

NOP 空指令

说明: 本指令不作任何运算,而只将程序计数器加一。

运算过程: PC Å PC+1

影响标志位

TO PDF OV Z AC C

— — — — — —

OR A, [m] 累加器与数据存储器做“或”运算,结果放入累加器

说明: 本指令是把累加器、数据存储器值做逻辑或,结果放到累加器。

运算过程: ACCÅACC “OR” [m]

影响标志位

TO PDF OV Z AC C

— — — √ — —

OR A, x 累加器与立即数做“或”运算,结果放入累加器

说明: 本指令是把累加器值、立即数做逻辑或,结果放到累加器。

运算过程: ACCÅACC “OR” x

影响标志位

TO PDF OV Z AC C

— — — √ — —

ORM A, [m] 累加器与数据存储器做“或”运算,结果放入数据存储器

说明: 本指令是把累加器值、存储器值做逻辑或,结果放到数据存储器。

运算过程: ACCÅACC “OR” [m]

影响标志位

TO PDF OV Z AC C

— — — √ — —

RET 从子程序返回

说明: 本指令是将堆栈寄存器中的程序计数器值送回程序计数器。

运算过程: PC Å Stack

影响标志位

TO PDF OV Z AC C

— — — — — —

RET A, x 从子程序返回,并将立即数放入累加器

说明: 本指令是将堆栈寄存器中的程序计数器值送回程序计数器,并将立即数送回累加器。

运算过程: PC Å Stack

ACC Å x

影响标志位

TO PDF OV Z AC C

— — — — — —

Rev. 1.70 36 2004-09-21

HT46R23/HT46C23

RETI 从中断返回

说明: 本指令是将堆栈寄存器中的程序计数器值送回程序计数器,与 RET 不同的是它使用在

中断程序结束返回时,它还会将中断控制寄存器 INTC 的 0 位(EMI)中断允许位置 1,允

许中断服务。

运算过程: PC Å Stack

EMI Å 1

影响标志位

TO PDF OV Z AC C

— — — — — —

RL [m] 数据存储器左移一位,结果放入数据存储器

说明: 本指令是将数据存储器内的数值左移一位,第 7 位移到第 0 位,结果送回数据存储器。

运算过程: [m].0 Å[m].7, [m].(i+1) Å[m].i; (i=0~6)

影响标志位

TO PDF OV Z AC C

— — — — — —

RLA [m] 数据存储器左移一位,结果放入累加器

说明: 本指令是将存储器内的数值左移一位,第 7 位移到第 0 位,结果送到累加器,而数据存

储器内的数值不变。

运算过程: ACC.0 Å[m].7, ACC.(i+1) Å[m].i; (i=0~6)

影响标志位

TO PDF OV Z AC C

— — — — — —

RLC [m] 带进位将数据存储器左移一位,结果放入数据存储器

说明: 本指令是将存储器内的数值与进位标志左移一位,第 7 位取代进位标志,进位标志移到

第 0 位,结果送回数据存储器。

运算过程: [m].(i+1) Å[m].i; (i=0~6)

[m].0 ÅC

C Å [m].7

影响标志位

TO PDF OV Z AC C

— — — — — √

RLCA [m] 带进位将数据存储器左移一位,结果放入累加器

说明: 本指令是将存储器内的数值与进位标志左移一位,第七位取代进位标志,进位标志移到

第 0 位,结果送回累加器。

运算过程: ACC.(i+1) Å[m].i; (i=0~6)

ACC.0 ÅC

C Å [m].7

影响标志位

TO PDF OV Z AC C

— — — — — √

Rev. 1.70 37 2004-09-21

HT46R23/HT46C23

m

RR [m] 数据存储器右移一位,结果放入数据存储器

说明: 本指令是将存储器内的数值循环右移,第 0 位移到第 7 位,结果送回数据存储器。

运算过程: [m].7 Å[m].0, [m].i Å[m].(i+1); (i=0~6)

影响标志位

TO PDF OV Z AC C

— — — — — —

RRA [m] 数据存储器右移一位,结果放入累加器

说明: 本指令是将数据存储器内的数值循环右移,第 0 位移到第 7 位,结果送回累加器,而数

据存储器内的数值不变。

运算过程: ACC.7 Å[m].0, ACC.i Å[m].(i+1); (i=0~6)

影响标志位

TO PDF OV Z AC C

— — — — — —

RRC [m] 带进位将数据存储器右移一位,结果放入数据存储器

说明: 本指令是将存储器内的数值加进位标志循环右移,第 0 位取代进位标志,进位标志移到

第 7 位,结果送回存储器。

运算过程: [m].i Å[m].(i+1); (i=0~6)

[m]. 7 ÅC

C Å [m].0

影响标志位

TO PDF OV Z AC C

— — — — — √

RRCA [m] 带进位将数据存储器右移一位,结果放入累加器

说明: 本指令是将数据存储器内的数值加进位标志循环右移,第 0 位取代进位标志,进位标志

移到第 7 位,结果送回累加器,数据存储器内的数值不变。

运算过程: ACC.i Å[m].(i+1); (i=0~6)

ACC.7 ÅC

C Å [m].0

影响标志位

TO PDF OV Z AC C

— — — — — √

SBC A,[m] 累加器与数据存储器、进位标志相减,结果放入累加器

说明: 本指令是把累加器值减去数据存储器值以及进位标志的取反,结果放到累加器。

运算过程: ACCÅACC+[

影响标志位

]+ C

TO PDF OV Z AC C

— — √ √ √ √

Rev. 1.70 38 2004-09-21

HT46R23/HT46C23

SBCM A,[m] 累加器与数据存储器、进位标志相减,结果放入数据存储器

说明: 本指令是把累加器值减去数据存储器值以及进位标志取反,结果放到数据存储器。

运算过程: [m]ÅACC+[m]+C

影响标志位

TO PDF OV Z AC C

— — √ √ √ √

SDZ [m] 数据存储器减 1,如果结果为“0”,则跳过下一条指令

说明: 本指令是把数据存储器内的数值减 1,判断是否为 0,若为 0 则跳过下一条指令,即如

果结果为零,放弃在目前指令执行期间所取得的下一条指令,并插入一个空周期用以取

得正确的指令(二个指令周期)。否则执行下一条指令(一个指令周期)。

运算过程: 如果[m]-1=0,跳过下一条指令执行再下一条。

影响标志位

TO PDF OV Z AC C

— — — — — —

SDZA [m] 数据存储器减 1,将结果放入累加器,如果结果为“0”,则跳过下一条指令

说明: 本指令是把数据存储器内的数值减 1,判断是否为 0,为 0 则跳过下一行指令并将减完

后数据存储器内的数值送到累加器,而数据存储器内的值不变,即若结果为 0,放弃在目

前指令执行期间所取得的下一条指令,并插入一个空周期用以取得正确的指令(二个指令

周期)。否则执行下一条指令(一个指令周期)。

运算过程: 如果[m]-1=0,跳过下一条指令执行再下一条。

ACC Å([m]-1)

影响标志位

TO PDF OV Z AC C

— — — — — —

SET [m] 置位数据存储器

说明: 本指令是把存储器内的数值每个位置为 1。

运算过程: [m] Å FFH

影响标志位

TO PDF OV Z AC C

— — — — — —

SET [m]. i 将数据存储器的第 i 位置“1”

说明: 本指令是把存储器内的数值的第 i 位置为 1。

运算过程: [m].i Å1

影响标志位

TO PDF OV Z AC C

— — — — — —

Rev. 1.70 39 2004-09-21

HT46R23/HT46C23

m

SIZ [m] 数据存储器加 1,如果结果为“0”,则跳过下一条指令

说明: 本指令是把数据存储器内的数值加 1,判断是否为 0。若 为 0,跳过下一条指令,即放弃

在目前指令执行期间所取得的下一条指令,并插入一个空周期用以取得正确的指令(二个

指令周期)。否则执行下一条指令(一个指令周期)。

运算过程: 如果 ([m]+1=0),跳过下一行指令;[m] Å[m]+1

影响标志位

TO PDF OV Z AC C

— — — — — —

SIZA 数据存储器加 1,将结果放入累加器,如果结果为“0”,则跳过下一条指令

说明: 本指令是把数据存储器内的数值加 1,判断是否为 0,若为 0 跳过下一条指令,即放弃

在目前指令执行期间所取得的下一条指令,并插入一个空周期用以取得正确的指令(二

个指令周期),并将加完后存储器内的数值送到累加器,而数据存储器的值保持不变。

否则执行下一条指令(一个指令周期)。

运算过程: 如果[m]+1=0,跳过下一行指令;ACC Å([m]+1)

影响标志位

TO PDF OV Z AC C

— — — — — —

SNZ [m]. i 如果数据存储器的第 i 位不为“0”,则跳过下一条指令

说明: 本指令是判断数据存储器内的数值的第 i 位,若不为 0,则程序计数器再加 1,跳过下一

行指令,放弃在目前指令执行期间所取得的下一条指令,并插入一个空周期用以取得正

确的指令(二个指令周期)。否则执行下一条指令(一个指令周期)。

运算过程: 如果 [m].i≠0,跳过下一行指令。

影响标志位

TO PDF OV Z AC C

— — — — — —

SUB A, [m] 累加器与数据存储器相减,结果放入累加器

说明: 本指令是把累加器值、数据存储器值相减,结果放到累加器。

运算过程: ACCÅACC+[

影响标志位

SUB A, x 累加器与立即数相减,结果放入累加器

说明: 本指令是把累加器值、立即数相减,结果放到累加器。

运算过程: ACCÅACC+

影响标志位

]+1

TO PDF OV Z AC C

— — √ √ √ √

x +1

TO PDF OV Z AC C

— — √ √ √ √

Rev. 1.70 40 2004-09-21

HT46R23/HT46C23

SUBM A, [m] 累加器与数据存储器相减,结果放入数据存储器

说明: 本指令是把累加器值、存储器值相减,结果放到存储器。

运算过程: [m]ÅACC+[m]+1

影响标志位

TO PDF OV Z AC C

— — √ √ √ √

SWAP [m] 交换数据存储器的高低字节,结果放入数据存储器

说明: 本指令是将数据存储器的低四位和高四位互换,再将结果送回数据存储器。

运算过程: [m].7~[m].4

影响标志位

SWAPA [m] 交换数据存储器的高低字节,结果放入累加器

说明: 本指令是将数据存储器的低四位和高四位互换,再将结果送回累加器。

运算过程: ACC.3~ACC.0Å [m].7~[m].4

ACC.7~ACC.4Å [m].3~[m].0

影响标志位

SZ [m] 如果数据存储器为“0”,则跳过下一条指令

说明: 本指令是判断数据存储器内的数值是否为 0,为 0 则跳过下一行指令,即放弃在目前指

令执行期间所取得的下一条指令,并插入一个空周期用以得正确的指令(二个指令周期)。

否则执行下一条指令(一个指令周期)。

运算过程: 如果 [m] = 0, 跳过下一行指令。

影响标志位

SZA [m] 数据存储器送至累加器,如果内容为“0”,则跳过下一条指令

说明: 本指令是判断存储器内的数值是否为 0,若为 0 则跳过下一行指令,即放弃在目前指令

执行期间所取得的下一条指令,并插入一个空周期用以得正确的指令(二个指令周期)。

并把存储器内值送到累加器,而存储器的值保持不变。否则执行下一条指令(一个指令周

期)。

运算过程: 如果[m] = 0,跳过下一行指令,并 ACCÅ [m]。

影响标志位

↔

[m].3~[m].0

TO PDF OV Z AC C

— — — — — —

TO PDF OV Z AC C

— — — — — —

TO PDF OV Z AC C

— — — — — —

TO PDF OV Z AC C

— — — — — —

Rev. 1.70 41 2004-09-21

HT46R23/HT46C23

SZ [m]. i 如果数据存储器的第 i 位为“0”,则跳过下一条指令

说明: 本指令是判断存储器内第 i 位值是否为 0,若为 0 则跳过下一行指令,即放弃在目前指

令执行期间所取得的下一条指令,并插入一个空周期用以得正确的指令(二个指令周期)。

否则执行下一条指令(一个指令周期)。

运算过程: 如果 [m].i = 0,跳过下一行指令。

影响标志位

TO PDF OV Z AC C

— — — — — —

TABRDC [m] 读取 ROM 当前页的内容,并送至数据存储器和 TBLH

说明: 本指令是将表格指针指向程序寄存器当前页,将低字节送到存储器,高字节直接送到

TBLH 寄存器内。

运算过程: [m] Å程序存储器低字节

TBLHÅ程序存储器高字节

影响标志位

TO PDF OV Z AC C

— — — — — —

TABRDL [m] 读取 ROM 最后一页的内容,并送至数据存储器和 TBLH

说明: 本指令是将 TABLE 指针指向程序寄存器最后页,将低字节送到存储器,高字节直接送

到 TBLH 寄存器内。

运算过程: [m] Å程序存储器低字节

TBLHÅ程序存储器高字节

影响标志位

TO PDF OV Z AC C

— — — — — —

XOR A, [m] 累加器与立即数做“异或”运算,结果放入累加器

说明: 本指令是把累加器值、 数据存储器值做逻辑异或,结果放到累加器。

运算过程: ACCÅACC “XOR” [m]

影响标志位

TO PDF OV Z AC C

— — — √ — —

XORM A, [m] 累加器与数据存储器做“异或”运算,结果放入数据存储器

说明: 本指令是把累加器值、数据存储器值做逻辑异或,结果放到数据存储器。

运算过程: [m]ÅACC “XOR” [m]

影响标志位

TO PDF OV Z AC C

— — — √ — —

XOR A, x 累加器与数据存储器做“异或”运算,结果放入累加器

说明: 本指令是把累加器值与立即数做逻辑异或,结果放到累加器。

运算过程: ACCÅACC “XOR” x

影响标志位

TO PDF OV Z AC C

— — — √ — —

Rev. 1.70 42 2004-09-21

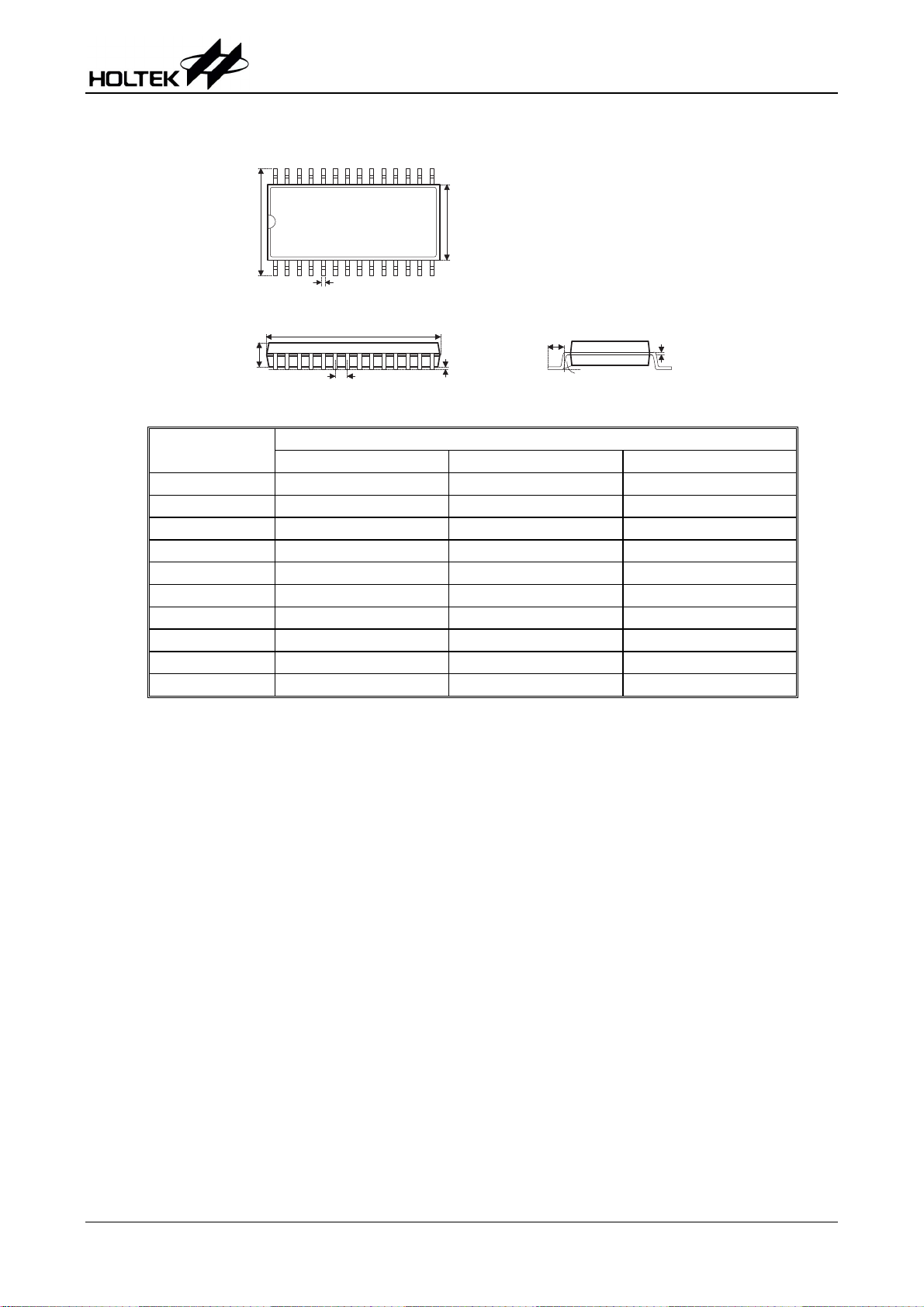

封装尺寸

24-pin SKDIP (300mil)外形尺寸

HT46R23/HT46C23

A

2 4

B

1

C

D

E

F G

1 3

1 2

H

a

I

符号

最小 典型 最大

A 1235

B 255

C 125

D 125

E 16

F 50

G

—

H 295

I 345

尺寸 (单位:mil)

—

—

—

—

—

—

100

—

—

1265

265

135

145

20

70

—

315

360

α 0° — 15°

Rev. 1.70 43 2004-09-21

28-pin SKDIP (300mil)外形尺寸

HT46R23/HT46C23

A

1

C

D

E

F

2 8

B

1 5

1 4

H

G

a

I

符号

尺寸 (单位:mil)

最小 典型 最大

A 1375

B 278

C 125

D 125

E 16

F 50

G

—

H 295

I 330

—

—

—

—

—

—

100

—

—

1395

298

135

145

20

70

—

315

375

α 0° — 15°

Rev. 1.70 44 2004-09-21

24-pin SOP (300mil)外形尺寸

HT46R23/HT46C23

2 4

A

1

C

C '

D

E F

1 3

B

1 2

G

H

a

符号

最小 典型 最大

A 394

B 290

C 14

C’ 590

D 92

E

—

F 4

G 32

H 4

尺寸 (单位:mil)

—

—

—

—

—

50

— —

—

—

419

300

20

614

104

—

38

12

α 0° — 10°

Rev. 1.70 45 2004-09-21

28-pin SOP (300mil)外形尺寸

HT46R23/HT46C23

2 8

A

1

C

C '

D

E

1 5

B

1 4

G

H

F

a

符号

尺寸 (单位:mil)

最小 典型 最大

A 394

B 290

C 14

C’ 697

D 92

E

—

F 4

G 32

H 4

—

—

—

—

—

50

— —

—

—

419

300

20

713

104

—

38

12

α 0° — 10°

Rev. 1.70 46 2004-09-21

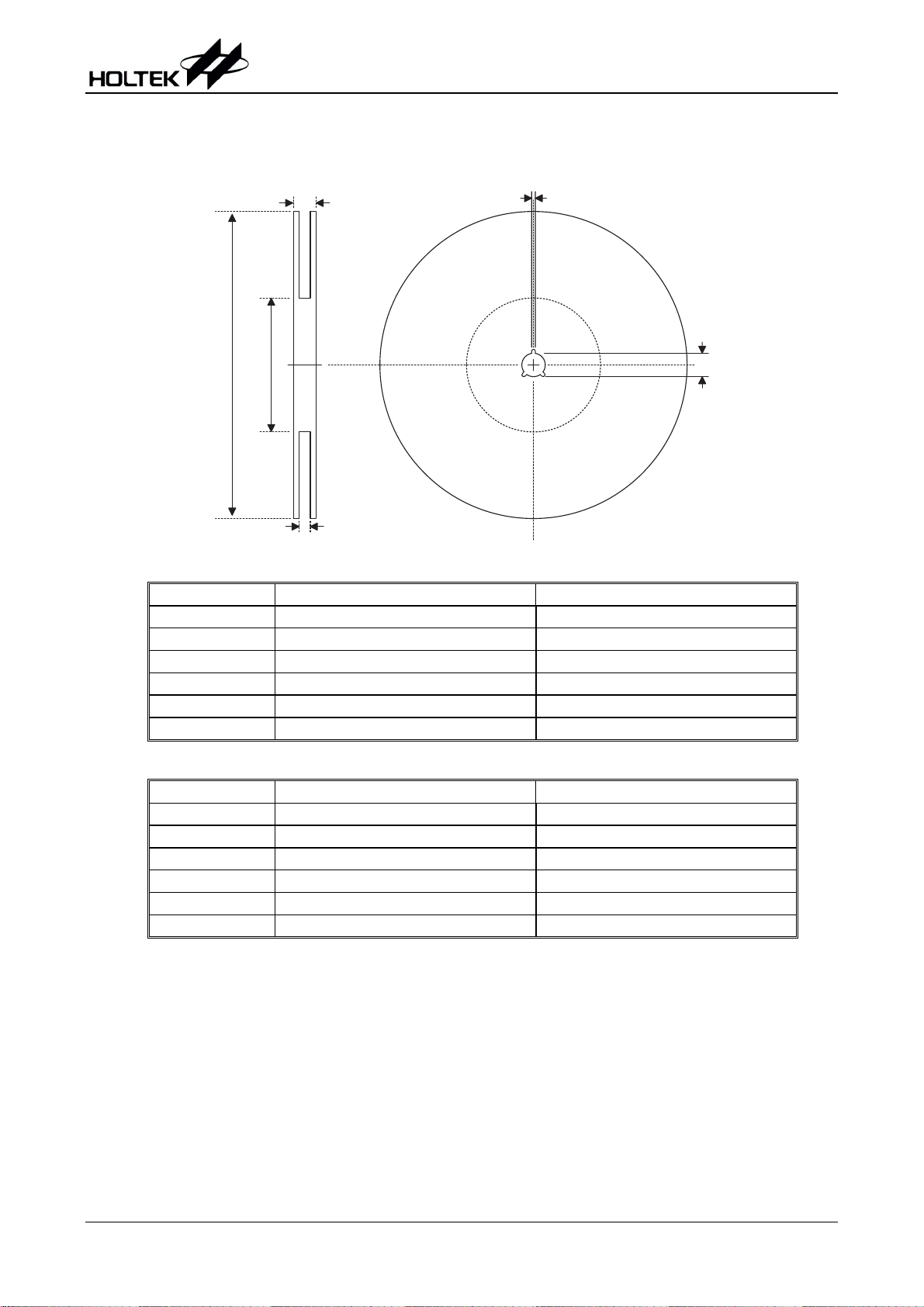

包装带和卷轴规格

卷轴尺寸

HT46R23/HT46C23

T 2

D

A

SOP 24W

符号 说明 尺寸 (单位:mm)

A

B

C

D

T1

T2

SOP 28W (300mil)

符号 说明 尺寸 (单位:mm)

A

B

C

D

T1

T2

B

T 1

卷轴外圈直径 330±1.0

卷轴内圈直径 62±1.5

轴心直径

12.75+0.15

缝宽

轮缘宽 24.4±0.2

卷轴宽

28.4+0.4

卷轴外圈直径 330±1.0

卷轴内圈直径 62±1.5

轴心直径

12.75+0.15

缝宽

轮缘宽 24.4±0.2

卷轴宽

28.4+0.4

C

2.0+0.6

2.0+0.6

Rev. 1.70 47 2004-09-21

运输带尺寸

HT46R23/HT46C23

D

E

P 1P 0

t

F

SOP 24W

符号 说明 尺寸 (单位:mm)

W

P

E

F

D

D1

P0

P1

A0

B0

K0

T

C

SOP 28W

符号 说明 尺寸 (单位:mm)

W

P

E

F

D

D1

P0

P1

A0

B0

K0

T

C

W

PD 1

A 0

B 0

C

K 0

运输带宽 24.0±0.3

空穴间距 12.0±0.1

穿孔位置 1.75±0.1

空穴至穿孔距离(宽度) 11.5±0.1

穿孔直径

空穴中之小孔直径

1.55+0.1

1.5+0.25

穿孔间距 4.0±0.1

空穴至穿孔距离(长度) 2.0±0.1

空穴长 10.9±0.1

空穴宽 15.9±0.1

空穴深 3.1±0.1

传输带厚度 0.35±0.05

覆盖带宽度

21.3

运输带宽 24.0±0.3

空穴间距 12.0±0.1

穿孔位置 1.75±0.1

空穴至穿孔距离(宽度) 11.5±0.1

穿孔直径

空穴中之小孔直径

1.5+0.1

1.5+0.25

穿孔间距 4.0±0.1

空穴至穿孔距离(长度) 2.0±0.1

空穴长 10.85±0.1

空穴宽 18.34±0.1

空穴深 2.97±0.1

传输带厚度 0.35±0.01

覆盖带宽度

21.3

Rev. 1.70 48 2004-09-21

盛群半导体股份有限公司(总公司)

新竹市科学工业园区研新二路 3 号

电话: 886-3-563-1999

传真: 886-3-563-1189

网站: www.holtek.com.tw

HT46R23/HT46C23

盛群半导体股份有限公司(台北业务处)

台北市南港区园区街 3 之 2 号 4 楼之 2

电话: 886-2-2655-7070

传真: 886-2-2655-7373

传真: 886-2-2655-7383 (International sales hotline)

盛扬半导体有限公司(上海业务处)

上海宜山路 889 号 2 号楼 7 楼 200233

电话: 021-6485-5560

传真: 021-6485-0313

网站: www.holtek.com.cn

盛扬半导体有限公司(深圳业务处)

深圳市深南中路赛格广场 43 楼 518031

电话: 0755-8346-5589

传真: 0755-8346-5590

ISDN: 0755-834-65591

盛扬半导体有限公司(北京业务处)

北京市西城区宣武门西大街甲 129 号金隅大厦 1721 室 100031

电话: 010-6641-0030, 6641-7751, 6641-7752

传真: 010-6641-0125

Holmate Semiconductor, Inc.(北美业务处)

46712 Fremont Blvd., Fremont, CA 94538

电话: 510-252-9880

传真: 510-252-9885

网站: www.holmate.com

Copyright 2004 by HOLTEK SEMICONDUCTOR INC.

使用指南中所出现的信息在出版当时相信是正确的,然而盛群对于说明书的使用不负任何责任。文中提

到的应用目的仅仅是用来做说明,盛群不保证或表示这些没有进一步修改的应用将是适当的,也不推荐

它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。盛群产品不授权使用于救生、维

生器件或系统中做为关键器件。盛群拥有不事先通知而修改产品的权利,对于最新的信息,请参考我们

的网址 http://www.holtek.com.tw

Rev. 1.70 49 2004-09-21

Loading...

Loading...